# Determining Minimum Acquisition Times for SAR ADCs When a DC Voltage is Applied to the Input

Keith Sanborn and Miro Oljaca

Data Acquisition Products

#### **ABSTRACT**

The input structure circuit of a successive-approximation register analog-to-digital converter (SAR ADC) in combination with the driving circuit forms a transfer function that can be used to determine minimum acquisition times for different types of applied input signals. This application report, which builds on *Determining Minimum Acquisition Times for SAR ADCs When a Step Function is Applied to the Input* (see Reference 1), investigates the situation when a dc voltage is applied to the input. First, the input structure of the ADC is examined along with the driving circuit. Next, a simple method is derived for calculating the minimum acquisition time for SAR ADCs when the input is a dc voltage. This method will then be compared with the minimum acquisition time derived in the previous application report (see Reference 1). Last of all, three different test cases are evaluated using both exact and approximated equations in order to support the derivations in this report.

#### Contents

| 1     | Introduction                                                                 |  |  |  |  |

|-------|------------------------------------------------------------------------------|--|--|--|--|

| 2     | SAR ADC Analog Input Equivalent Circuit                                      |  |  |  |  |

| 3     | Mathematical Analysis of the Equivalent Circuit                              |  |  |  |  |

| 4     | Minimum Acquisition Time                                                     |  |  |  |  |

| 5     | Test Cases                                                                   |  |  |  |  |

| 6     | Conclusion                                                                   |  |  |  |  |

| 7     | References                                                                   |  |  |  |  |

| Appen | dix A                                                                        |  |  |  |  |

| Appen | dix B                                                                        |  |  |  |  |

| Appen | dix C                                                                        |  |  |  |  |

|       | List of Figures                                                              |  |  |  |  |

| 1     | Typical SAR ADC Input Driving Circuit                                        |  |  |  |  |

| 2     | Simplified SAR ADC Input Driving Circuit                                     |  |  |  |  |

| 3     | SAR ADC Input Driving Circuit Represented as a Second-Order, Low-Pass Filter |  |  |  |  |

| 4     | Second-Order Filter with Voltages and Currents Defined                       |  |  |  |  |

| 5     | Plots of Equations (8), (9), and (10) versus Time                            |  |  |  |  |

| 6     | Case (a)                                                                     |  |  |  |  |

| 7     | Case (b)                                                                     |  |  |  |  |

| 0     | Cono (a)                                                                     |  |  |  |  |

All trademarks are the property of their respective owners.

Introduction www.ti.com

#### 1 Introduction

When it comes to designing the proper input driving circuit for analog-to-digital converters (ADCs), emphasis is typically placed on the calculation of the RC filter in front of the analog input and the selection of an operational amplifier (see Reference 2). The selection of the external RC components depends on the internal structure, sampling sequence, and charge injection of the SAR ADC (see Reference 3 through Reference 5). Knowledge of the internal input structure of the ADC, especially the value of the sampling capacitor, will assist users as they optimize the external RC components to obtain the maximum ac and dc performance from the device (see Reference 6).

The calculation of the external RC filter is simplified by assuming the analog input sampling switch resistance is negligible (see Reference 6). In the following analysis, the analog input sampling switch resistance will be included.

# 2 SAR ADC Analog Input Equivalent Circuit

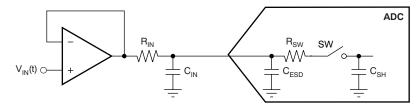

A typical analog input driving circuit for the ADC includes an operational amplifier (op amp) as well as an input RC filter composed of  $R_{\text{IN}}$  and  $C_{\text{IN}}$  as shown in Figure 1. The signal from the driving circuit charges the sampling capacitor  $C_{\text{SH}}$  through the sampling switch SW with an equivalent on-resistance  $R_{\text{SW}}$ . The input switch is composed of a CMOS transmission gate or similar structure. The equivalent on-resistance of the sampling switch is not linear and depends on the input signal level (see Reference 7). For this analysis, the average on-resistance of the switch measured over the full-scale input range (FSR) of the ADC will be used.

Figure 1. Typical SAR ADC Input Driving Circuit

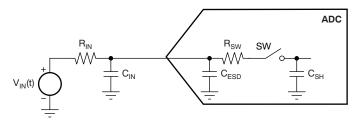

Furthermore, the op amp is assumed to have ideal characteristics. Therefore, it can be modeled as an ideal voltage source. By modeling the op amp in this fashion, the circuit from Figure 1 can be simplified to the one shown in Figure 2.

Figure 2. Simplified SAR ADC Input Driving Circuit

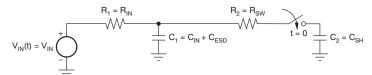

The ESD protection circuit at the input of the ADC has an equivalent capacitance  $C_{\text{ESD}}$ . This capacitance is the parallel combination of the protection circuit from the input pin to the power-supply rail and ground. The equivalent capacitance of  $C_{\text{ESD}}$  is typically between 4 pF and 10 pF. The input filter capacitance  $C_{\text{IN}}$ , on the other hand, usually ranges from 1 nF to 10 nF. If  $C_{\text{IN}} >> C_{\text{ESD}}$ , then  $C_{\text{ESD}}$  can be neglected. This analysis will represent the parallel combination of  $C_{\text{IN}}$  and  $C_{\text{ESD}}$  as capacitor  $C_{\text{1}}$  (see Figure 3).

In addition to treating the op amp in Figure 1 as ideal, this analysis investigates the case of the input signal pre-charging capacitor  $C_1$  to a constant dc voltage before the sampling switch SW closes. This situation can occur if the input signal  $V_{IN}(t)$  changes state during the conversion period of a SAR ADC with a single input channel. It may also occur with a multi-channel SAR ADC, such as the <u>ADS8331/32</u> (see Reference 8), when another channel is selected during the current conversion. Under these conditions, the input signal  $V_{IN}(t)$  can be represented as a constant dc voltage source with magnitude  $V_{IN}$ .

Moreover, the circuit in Figure 2 can be represented as a second-order, low-pass filter. The circuit for this case with updated variables is shown in Figure 3.

Figure 3. SAR ADC Input Driving Circuit Represented as a Second-Order, Low-Pass Filter

The worst-case transient response occurs when the difference in absolute magnitude between the initial voltage on capacitor  $C_1$  [voltage of  $V_{IN}(t)$ ] and the initial voltage on capacitor  $C_2$  is equal to the full-scale input range (FSR) of the SAR ADC. The case where the initial voltage on capacitor C1 [voltage of  $V_{IN(t)}$ ] is at V<sub>IN</sub> or the positive full-scale voltage (PFS), while the initial voltage on capacitor C<sub>2</sub> is at zero or the negative full-scale voltage (NFS) will be analyzed here. The analysis of this case yields similar results for the case where the initial voltage on capacitor C<sub>1</sub> [voltage of V<sub>IN(t)</sub>] is at zero or NFS while the initial voltage on capacitor  $C_2$  is at  $V_{IN}$  or PFS. This second case is left to the reader as an exercise.

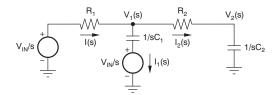

The FSR of a SAR ADC is the difference between the PFS and the NFS of the converter. In order to analyze the circuit in Figure 3 under worst-case conditions, the initial voltages on capacitors C<sub>1</sub> and C<sub>2</sub> are set to V<sub>IN</sub> and zero, respectively. Figure 4 shows the Laplace transform of the circuit in Figure 3 with the initial conditions, reference currents, and voltages that are used in the analysis.

Figure 4. Second-Order Filter with Voltages and Currents Defined

The primary goal of this analysis is to determine the minimum acquisition time (t<sub>ACO</sub>) for the voltage on capacitor C<sub>2</sub> to settle within 1/2 LSB of the input signal for an N-bit SAR ADC as a function of R<sub>1</sub>, C<sub>1</sub>, R<sub>2</sub>, and C2. In order for this analysis to be performed, an expression for the voltage V2 across capacitor C2 as a function of time must be derived. The next section in this application report focuses on this calculation.

#### 3 **Mathematical Analysis of the Equivalent Circuit**

The Laplace transform of voltage V<sub>2</sub> in Figure 4 is:

$$V_2(s) = A(s) \times V_{IN}$$

$$A(s) = \omega_n^2 \times \frac{1}{s} \times \frac{sa + 1}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

(2)

The calculations for Equation 1 and Equation 2 are shown in Appendix A. The inverse Laplace transform

$$A(t) = \frac{\sqrt{\zeta^2 \omega_n^2 - \omega_n^2} - \sqrt{\zeta^2 \omega_n^2 - \omega_n^2} \times \cosh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t}}{\sqrt{\omega_n^2 (\zeta^2 - 1)}}$$

$$+ \frac{a \times \omega_n^2 \times \sinh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t} - \zeta \times \omega_n \times \sinh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t}}{\sqrt{\omega_n^2 (\zeta^2 - 1)}}$$

(3

(3)

(1)

(9)

(10)

After simplifying, Equation 3 can be re-written as follows (see Appendix B for further details):

$$A(t) = 1 - \frac{1}{2\sqrt{\zeta^2 - 1}} \times \left[ \left( \zeta - a\omega_n + \sqrt{\zeta^2 - 1} \right) \times e^{-\omega_n(\zeta - \sqrt{\zeta^2 - 1})t} - \left( \zeta - a\omega_n - \sqrt{\zeta^2 - 1} \right) \times e^{-\omega_n(\zeta + \sqrt{\zeta^2 - 1})t} \right]$$

(4)

Equation 4, in turn, can be expressed as:

$$A(t) = 1 - \frac{1}{2\sqrt{\zeta^2 - 1}} \times \left[ (\zeta - a\omega_n + \sqrt{\zeta^2 - 1}) \times e^{-\frac{t}{\tau_1}} - (\zeta - a\omega_n - \sqrt{\zeta^2 - 1}) \times e^{-\frac{t}{\tau_2}} \right]$$

(5)

where time constants  $\tau_1$  and  $\tau_2$  are defined as Equation 6 and Equation 7, respectively:

$$\tau_1 = \frac{1}{\omega_n(\zeta - \sqrt{\zeta^2 - 1})} \tag{6}$$

$$\tau_2 = \frac{1}{\omega_n(\zeta + \sqrt{\zeta^2 - 1})} \tag{7}$$

In order to observe the effects of these two time constants, Equation 5 can be rewritten as:

$$A(t) = 1 - [k1(t) - k2(t)]$$

(8)

where:

k1(t) =

$$\frac{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}{2\sqrt{\zeta^2 - 1}} \times e^{-\frac{t}{\tau_1}}$$

and

$$k2(t) = \frac{\zeta - a\omega_n - \sqrt{\zeta^2 - 1}}{2\sqrt{\zeta^2 - 1}} \times e^{-\frac{t}{\tau_2}}$$

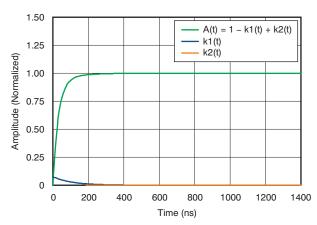

The plots of Equation 8, Equation 9, and Equation 10 as a function of time are shown in Figure 5.

The following values were used in Figure 5:  $R_1 = 100 \Omega$ ,  $R_2 = 800 \Omega$ ,  $C_1 = 1000 pF$ , and  $C_2 = 40 pF$ .

These component values set  $\bf a=100$  ns,  $\bf b=4$  ns, and  $\bf c=32$  ns. These values set  $\omega_n=17.678$  Mrad/s and  $\zeta=1.202$ . Furthermore, the time constants are calculated to be  $\tau_1=105.721$  ns and  $\tau_2=30.267$  ns.

Figure 5. Plots of Equations (8), (9), and (10) versus Time

As shown in Figure 5, k2(t) decays faster than k1(t) when  $\tau_2 << \tau_1$ . Under these conditions, Equation 8 can be approximated as a function with only time constant  $\tau_1$ , or:

$$A(t) \approx 1 - \frac{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}{2\sqrt{\zeta^2 - 1}} \times e^{\frac{t}{\tau_1}}$$

$$\tag{11}$$

## 4 Minimum Acquisition Time

In order for the voltage on capacitor  $C_2$  in Figure 3 to settle within 1/2 LSB of the input signal for an *N*-bit SAR ADC:

$$A(t) \ge 1 - \frac{1}{2^{N+1}} \tag{12}$$

If k1(t) >> k2(t) at the minimum acquisition time, then A(t) in Equation 12 may be approximated by Equation 11. When this approximation is done, the minimum acquisition time  $t_{ACQ}$  for an *N*-bit ADC is (see Appendix C for calculations):

$$t_{ACQ} \ge \frac{1}{\omega_n(\zeta - \sqrt{\zeta^2 - 1})} \times \left[ N \times \ln(2) + \ln\left(\frac{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}{\sqrt{\zeta^2 - 1}}\right) \right]$$

(13)

The minimum acquisition time t<sub>ACQ</sub> for an *N*-bit ADC from the application report *Determining Minimum Acquisition Times for SAR ADCs When a Step Function is Applied to the Input* (see Reference 1) is given in Equation 14.

$$t_{ACQ} \ge \frac{1}{\omega_n(\zeta - \sqrt{\zeta^2 - 1})} \times \left[ N \times \ln(2) + \ln\left(\frac{\zeta + \sqrt{\zeta^2 - 1}}{\sqrt{\zeta^2 - 1}}\right) \right]$$

(14)

The difference between Equation 13 and Equation 14 is shown in Equation 15:

$$t_{\text{ACQ\_STEP}} - t_{\text{ACQ\_DC}} = \frac{1}{\omega_n(\zeta - \sqrt{\zeta^2 - 1})} \times \ln\left(\frac{\zeta + \sqrt{\zeta^2 - 1}}{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}\right)$$

(15)

Here,  $t_{ACQ\_DC}$  and  $t_{ACQ\_STEP}$  are the minimum acquisition times in Equation 13 and Equation 14, respectively. Because the ratio in the natural logarithm term in Equation 15 is greater than one, the difference between the acquisition times is a positive quantity. This effect means the acquisition time when the input signal is a step function is greater than the acquisition time when the input signal is a constant dc source, with all other components in the system remaining the same.

### 5 Test Cases

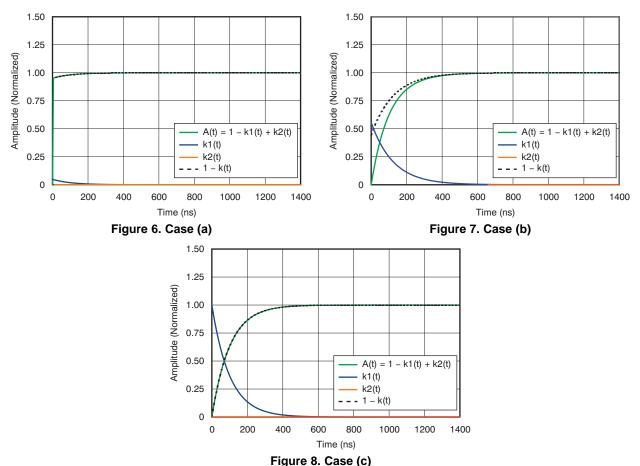

In order to evaluate if the approximation derived in Equation 11 is valid, the following test cases were analyzed for a 16-bit ADC (N = 16):

- (a)  $R_1C_1 = R_2C_2 \times 100$

- (b)  $R_1C_1 = R_2C_2$

- (c)  $R_1C_1 = R_2C_2 / 100$

The results of these cases are displayed in Table 1.

Test Cases www.ti.com

**Table 1. Results of Three Test Cases**

| Parameter                                             | (a)      | (b)      | (c)      | Units  |

|-------------------------------------------------------|----------|----------|----------|--------|

| R <sub>1</sub>                                        | 100      | 100      | 10       | Ω      |

| C <sub>1</sub>                                        | 1000     | 1000     | 100      | pF     |

| R <sub>2</sub>                                        | 20       | 2000     | 2000     | Ω      |

| C <sub>2</sub>                                        | 50       | 50       | 50       | pF     |

| $f_1 = \frac{1}{2\pi R_1 C_1}$                        | 1.59     | 1.59     | 159      | MHz    |

| $f_2 = \frac{1}{2\pi R_2 C_2}$                        | 159      | 1.59     | 1.59     | MHz    |

| $f_2/f_1$                                             | 100      | 1        | 0.01     |        |

| a <sup>(1)</sup>                                      | 100      | 100      | 1        | ns     |

| b <sup>(1)</sup>                                      | 5        | 5        | 0.5      | ns     |

| C <sup>(1)</sup>                                      | 1        | 100      | 100      | ns     |

| ω <sub>n(1)</sub>                                     | 100      | 10       | 100      | Mrad/s |

| ζ (1)                                                 | 5.300    | 1.025    | 5.075    |        |

| $\tau_1$                                              | 105.048  | 125.000  | 100.505  | ns     |

| $\tau_2$                                              | 0.952    | 80.000   | 0.995    | ns     |

| t <sub>ACQ</sub>                                      | 0.920    | 1.399    | 1.184    | μs     |

| k1(t <sub>ACQ</sub> )                                 | 0.000008 | 0.000008 | 0.000008 |        |

| k2(t <sub>ACQ</sub> )                                 | 0.000000 | 0.000000 | 0.000000 |        |

| A(t <sub>ACQ</sub> ) <sub>EQ08</sub><br>(Equation 8)  | 0.999992 | 0.999992 | 0.999992 |        |

| A(t <sub>ACQ</sub> ) <sub>EQ11</sub><br>(Equation 11) | 0.999992 | 0.999992 | 0.999992 |        |

| Error <sup>(2)</sup>                                  | 0.000000 | 0.000001 | 0.000000 | %      |

Refer to Appendix A for equations.

$$\begin{bmatrix} A(t_{ACQ})_{(Eq11)} - A(t_{ACQ})_{(Eq08)} \\ A(t_{ACQ})_{(Eq08)} \end{bmatrix} \times 100$$

(2) Error =

www.ti.com Conclusion

By using the acquisition times from Table 1, the final voltage on the sampling capacitor of the ADC from Figure 1 was calculated for each test case by using Equation 11 and Equation 8. The difference in the final voltage calculated with Equation 11 and Equation 8 for each test case is negligible (see Table 1 for details). This analysis clearly demonstrates that using the simplified Equation 11 to calculate the final voltage on the sampling capacitor does not introduce any significant error compared to using the exact formula (Equation 8). This assessment is further supported by the plots in Figure 6 through Figure 8. Another insight revealed by this analysis is that the acquisition times in Table 1 are less than the corresponding ones in the previous application report (see Reference 1).

### 6 Conclusion

This report analyzes the input structure along with the driving circuit of a SAR ADC. It provides a simple analytical method for calculating minimum acquisition times for SAR ADCs when a constant dc voltage is applied to the input. Three different test cases were calculated using exact equations as well as simplified ones. The difference in the final acquired voltage calculated with these two equations was negligible. Last of all, it was shown through calculations and test cases that the minimum acquisition time of a system with constant dc source will be less than the identical system using an input step function (see Reference 1).

References www.ti.com

#### 7 References

The following documents are available for download through the indicated web sites.

- Oljaca, M. and K. Sanborn. (2009). <u>Determining Minimum Acquisition Times for SAR ADCs When a Step Function is Applied to the Input.</u> Texas Instruments application report <u>SBAA173</u>.

Download at: http://www.ti.com.

- Oljaca, M. and B. Baker. (2008). <u>Start with the right op amp when driving SAR ADCs</u>. EDN. October 16, 2008. Pp. 43-58.

- Download at: http://www.edn.com/article/CA6602451.html

- 3. Downs, R. and M. Oljaca. (2005). <u>Designing SAR ADC drive circuitry</u>, <u>Part I: A detailed look at SAR ADC operation</u>. Analog Zone.

- Download at: http://www.analogzone.com/acqt0221.pdf

- 4. Downs, R. and M. Oljaca. (2005). <u>Designing SAR ADC drive circuitry</u>, <u>Part II: Input behavior of SAR ADCs</u>. Analog Zone.

- Download at: http://www.analogzone.com/acqt1003.pdf

- 5. Downs, R. and M. Oljaca. (2005). <u>Designing SAR ADC drive circuitry</u>, <u>Part III: Designing the optimal input drive circuit for SAR ADCs</u>. Analog Zone.

- Download at: http://www.analogzone.com/acqt0312.pdf

- 6. Baker, B. and M. Oljaca. (2007). External components improve SAR-ADC accuracy. EDN. June 7, 2007. Pp. 67-75.

- Download at: http://www.edn.com/article/CA6447231.html

- Oljaca, M. (2004). <u>Understand the limits of your ADC input circuit before starting conversions</u>. Analog Zone.

- Download at: http://www.analogzone.com/acqt1101.pdf

- 8. ADS8331/ADS8332 product data sheet, Texas Instruments literature number SBAS363.

8

# Appendix A

The voltage and currents in the circuit of Figure 4 can be described with the following equations:

$$V_1(s) = \frac{I_1(s)}{sC_1} + \frac{V_{IN}}{s}$$

(16)

$$V_2(s) = \frac{I_2(s)}{sC_2}$$

(17)

$$V_1(s) - V_2(s) = R_2 I_2(s)$$

(18)

$$\frac{V_{IN}}{s} - V_1(s) = R_1 I(s)$$

(19)

$$I(s) = I_1(s) + I_2(s)$$

(20)

Equation 16, Equation 17, and Equation 19 can be rewritten as:

$$I_1(s) = sC_1V_1(s) - C_1V_{IN}$$

(21)

$$I_2(s) = sC_2V_2(s)$$

(22)

$$I(s) = \frac{V_{IN}}{sR_1} - \frac{V_1(s)}{R_1}$$

(23)

Substituting Equation 21 through Equation 23 into Equation 20 yields:

$$V_{IN} = \frac{(s^2 R_1 C_1 + s) V_1(s) + s^2 R_1 C_2 V_2(s)}{s R_1 C_1 + 1}$$

(24)

Using Equation 22 in Equation 18 produces:

$$V_1(s) = (sR_2C_2 + 1)V_2(s)$$

(25)

Substituting Equation 25 into Equation 24 produces:

$$V_{IN} = \frac{s[(sR_1C_1 + 1)(sR_2C_2 + 1) + sR_1C_2]}{sR_1C_1 + 1} \times V_2(s)$$

(26)

By using these constants:

$$a = R_1C_1$$

$$b = R_1C_2$$

$$c = R_2C_2$$

Equation 26 can be simplified to:

$$(sa + 1)V_{IN} = s \left[ (sa + 1)(sc + 1) + sb \right] \times V_2(s)$$

(27)

Appendix A www.ti.com

The voltage  $V_2(s)$  can be described as a function of the constant dc source  $V_{IN}(t)$  with magnitude  $V_{IN}$  by rearranging Equation 27 to yield:

$$V_2(s) = \frac{1}{ac} \times \frac{1}{s} \times \frac{sa+1}{s^2 + s\frac{a+b+c}{ac} + \frac{1}{ac}} \times V_{IN}$$

(28)

The coefficients in Equation 28 can be represented as:

$$\frac{a+b+c}{ac}=2\zeta\omega_n$$

(29)

and

$$\frac{1}{ac} = \omega_n^2$$

(30)

Substituting Equation 29 and Equation 30 into Equation 28 produces:

$$V_2(s) = A(s) \times V_{IN}$$

(31)

where:

$$A(s) = \omega_n^2 \times \frac{1}{s} \times \frac{sa + 1}{s^2 + 2\zeta\omega_n s + \omega_n^2}$$

(32)

# Appendix B

The equation:

$$A(t) = \frac{\sqrt{\zeta^2 \omega_n^2 - \omega_n^2} - \sqrt{\zeta^2 \omega_n^2 - \omega_n^2} \times cosh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t}}{\sqrt{\omega_n^2 (\zeta^2 - 1)}} + \frac{a \times \omega_n^2 \times sinh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t} - \zeta \times \omega_n \times sinh(t \sqrt{\zeta^2 \omega_n^2 - \omega_n^2}) \times e^{-\zeta \omega_n t}}{\sqrt{\omega_n^2 (\zeta^2 - 1)}}$$

$$(33)$$

Can be reduced to:

$$A(t) = 1 - e^{-\zeta\omega_n t} \times \left[ \cosh\left(\omega_n \sqrt{\zeta^2 - 1} t\right) - \frac{a\omega_n - \zeta}{\sqrt{\zeta^2 - 1}} \times \sinh(\omega_n \sqrt{\zeta^2 - 1} t) \right]$$

(34)

The definitions of the hyperbolic sine and hyperbolic cosine terms are:

$$\sinh(x) = \frac{e^x - e^{-x}}{2}$$

$$cosh(x) = \frac{e^x + e^{-x}}{2}$$

(36)

The arguments of the hyperbolic sine and hyperbolic cosine terms in Equation 34 can be defined as:

$$x = \omega_n \sqrt{\zeta^2 - 1}t \tag{37}$$

Substituting Equation 37 into Equation 35 and Equation 36 yields:

$$sinh(\omega_n \sqrt{\zeta^2 - 1}t) = \frac{e^{\omega_n \sqrt{\zeta^2 - 1}t} - e^{-\omega_n \sqrt{\zeta^2 - 1}t}}{2}$$

(38)

and

$$\cosh(\omega_n \sqrt{\zeta^2 - 1}t) = \frac{e^{\omega_n \sqrt{\zeta^2 - 1}t} + e^{-\omega_n \sqrt{\zeta^2 - 1}t}}{2} \tag{39}$$

Using Equation 38 and Equation 39 in Equation 34 produces:

$$A(t) = 1 - e^{-\zeta \omega_n t} \times \left[ \frac{e^{\omega_n \sqrt{\zeta^2 - 1}t} + e^{-\omega_n \sqrt{\zeta^2 - 1}t}}{2} - \frac{a\omega_n - \zeta}{\sqrt{\zeta^2 - 1}} \times \frac{e^{\omega_n \sqrt{\zeta^2 - 1}t} - e^{-\omega_n \sqrt{\zeta^2 - 1}t}}{2} \right]$$

(40)

By re-arranging the terms, Equation 40 can be simplified to:

$$A(t) = 1 - \frac{1}{2\sqrt{\zeta^2 - 1}} \times \left[ \left( \zeta - a\omega_n + \sqrt{\zeta^2 - 1} \right) \times e^{-\omega_n(\zeta - \sqrt{\zeta^2 - 1})t} - \left( \zeta - a\omega_n - \sqrt{\zeta^2 - 1} \right) \times e^{-\omega_n(\zeta + \sqrt{\zeta^2 - 1})t} \right]$$

$$(41)$$

(35)

# Appendix C

For k1(t) >> k2(t), Equation 5 reduces to:

$$A(t)\approx 1-\frac{\zeta-a\omega_n+\sqrt{\zeta^2-1}}{2\sqrt{\zeta^2-1}}\times e^{-\frac{t}{\tau_1}}$$

(42)

In order for Equation 42 to satisfy the criteria in Equation 12 for minimum acquisition time t<sub>ACQ</sub>:

$$\frac{1}{2^{N+1}} \ge \frac{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}{2\sqrt{\zeta^2 - 1}} \times e^{\frac{t_{ACO}}{\tau_1}}$$

(43)

Re-arranging the terms in Equation 43 and solving for  $t_{\text{ACQ}}$  yields:

$$t_{ACQ} \ge \tau_1 \times \left[ N \times ln(2) + ln \left( \frac{\zeta - a\omega_n + \sqrt{\zeta^2 - 1}}{\sqrt{\zeta^2 - 1}} \right) \right]$$

(44)

Using Equation 6 to replace  $\tau_1$  in Equation 44 produces the inequality:

$$t_{\text{ACQ}} \ge \frac{1}{\omega_{\text{n}}(\zeta - \sqrt{\zeta^2 - 1})} \times \left[ N \times \ln(2) + \ln\left(\frac{\zeta - a\omega_{\text{n}} + \sqrt{\zeta^2 - 1}}{\sqrt{\zeta^2 - 1}}\right) \right]$$

(45)

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products                    |                        | Applications                     |                                   |

|-----------------------------|------------------------|----------------------------------|-----------------------------------|

| Audio                       | www.ti.com/audio       | Communications and Telecom       | www.ti.com/communications         |

| Amplifiers                  | amplifier.ti.com       | Computers and Peripherals        | www.ti.com/computers              |

| Data Converters             | dataconverter.ti.com   | Consumer Electronics             | www.ti.com/consumer-apps          |

| DLP® Products               | www.dlp.com            | Energy and Lighting              | www.ti.com/energy                 |

| DSP                         | dsp.ti.com             | Industrial                       | www.ti.com/industrial             |

| Clocks and Timers           | www.ti.com/clocks      | Medical                          | www.ti.com/medical                |

| Interface                   | interface.ti.com       | Security                         | www.ti.com/security               |

| Logic                       | logic.ti.com           | Space, Avionics and Defense      | www.ti.com/space-avionics-defense |

| Power Mgmt                  | power.ti.com           | Transportation and<br>Automotive | www.ti.com/automotive             |

| Microcontrollers            | microcontroller.ti.com | Video and Imaging                | www.ti.com/video                  |

| RFID                        | www.ti-rfid.com        | Wireless                         | www.ti.com/wireless-apps          |

| RF/IF and ZigBee® Solutions | www.ti.com/lprf        |                                  |                                   |

**TI E2E Community Home Page**

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated

e2e.ti.com