# Application Note

# MCU로의 절연 모듈레이터 디지털 인터페이스를 사용한 클록 에지 지 연 보상

Gizem Yuece, Alex Smith, Martin Staebler

#### 추상

서보 드라이브 및 로봇 애플리케이션에서 정확하고 낮은 지연 시간과 높은 잡음 내성 션트 기반 위상 전류 감지를 위해서는 고속 디지털 인터페이스를 지원하는 AMC1306M25와 같은 절연 델타-시그마 모듈레이터가 일반적으로 사용됩니다. 특히 높은 클록 주파수에서 안정적인 작동을 위해 적절한 라우팅, 종단 및 해당 MCU의 설정 및 홀드 시간 준수는 매우 중요합니다. MCU 타이밍 요구 사항을 충족하기 위해 일반적으로 사용되는 방법과 절충안은 모듈레이터 클록 주파수를 줄이는 것으로, 이렇게 하면 데이터 출력 속도도 감소합니다. 이 애플리케이션 노트는 모듈레이터의 최대 클록 속도까지 설정 및 홀드 타이밍 요구 사항을 충족하기 위해 클록 에지 보상 방법을 사용하는 설계를 보여줍니다. 따라서 시스템이 최대 데이터 속도에서 작동할수 있습니다. 애플리케이션 노트에서는 클록 에지 보상 옵션을 설명하고, C2000™ 및 Sitara™ MCU에 연결된 TI의 절연 모듈레이터 AMC130x를 사용한 측정 예시를 보여줍니다. 추가로, 디지털 인터페이스 타이밍을 검증하기 위한 계산 툴도 제공됩니다.

# 목차

| 1 머리말                                                                                                                                                                                                                                                   |                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 2 디지털 인터페이스 타이밍 사양의 설계 과제                                                                                                                                                                                                                               | 4                               |

| 3 클록 에지 지연 보상을 사용한 디자인 접근 방식                                                                                                                                                                                                                            |                                 |

| 3.1 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상                                                                                                                                                                                                                     |                                 |

| 3.2 하드웨어 구성 가능 위상 지연을 사용한 클록 신호 보상                                                                                                                                                                                                                      |                                 |

| 3.3 클록 반환을 통한 클록 신호 보상                                                                                                                                                                                                                                  |                                 |

| 3.4 MCU에서 클록 반전에 의한 클록 신호 보상                                                                                                                                                                                                                            |                                 |

| 4 테스트 및 검증                                                                                                                                                                                                                                              |                                 |

| 4.1 테스트 강비 및 소프트웨어                                                                                                                                                                                                                                      | 10                              |

| 4.2 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상 테스트                                                                                                                                                                                                                 | 10                              |

| 4.3 MCU에서 클록 반전에 의한 클록 신호 보상 테스트                                                                                                                                                                                                                        | 12                              |

| 4.4 계산 <del>툴을</del> 사용한 디지털 인터페이스 타이밍 검증                                                                                                                                                                                                               | 15                              |

| 5 결론                                                                                                                                                                                                                                                    |                                 |

| 6 참고 자료                                                                                                                                                                                                                                                 | 18                              |

| 7 Revision History                                                                                                                                                                                                                                      | 19                              |

|                                                                                                                                                                                                                                                         |                                 |

|                                                                                                                                                                                                                                                         | 0                               |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       |                                 |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램<br>그림 2-1. TMS320F28379D로의 간소화된 AMC1306M25 디지털 인터페이스                                                                                                                                  | 4                               |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램<br>그림 2-1. TMS320F28379D로의 간소화된 AMC1306M25 디지털 인터페이스<br>그림 2-2. AMC1306x 디지털 인터페이스 타이밍                                                                                                | 4<br>4                          |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램<br>그림 2-1. TMS320F28379D로의 간소화된 AMC1306M25 디지털 인터페이스<br>그림 2-2. AMC1306x 디지털 인터페이스 타이밍<br>그림 2-3. TMS320F28379D SDFM 타이밍 다이어그램 - 모드 0                                                 | 4<br>4<br>5                     |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램<br>그림 2-1. TMS320F28379D로의 간소화된 AMC1306M25 디지털 인터페이스<br>그림 2-2. AMC1306x 디지털 인터페이스 타이밍<br>그림 2-3. TMS320F28379D SDFM 타이밍 다이어그램 - 모드 0<br>그림 2-4. TMS320F28379D로의 AMC1305L25 디지털 인터페이스 | 4<br>4<br>5                     |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>5                     |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>5<br>6                |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7                |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7                |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7<br>7           |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7<br>7           |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7<br>7           |

| 그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램                                                                                                                                                                                       | 4<br>5<br>6<br>7<br>7<br>8<br>9 |

상표 www.ti.com

| 그림 4-3. 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상을 사용하는 AMC1306EVM 및 TMS320F28379D의 디지털 인<br>터페이스 타이밍 측정 결과                    | 12 |

|----------------------------------------------------------------------------------------------------------------------|----|

| 그림 4-4. 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상을 사용하는 AMC1306EVM 및 AM243x의 디지털 인터페이스<br>타이밍 측정 결과                            | 12 |

| 그림 4-5. 디지털 인터페이스 타이밍 검증의 테스트 설정                                                                                     | 13 |

| 그림 4-6. CCS의 클록 및 데이터 입력 테스트 신호(반전되지 않은 GPIO123)와 Sinc3 OSR 64 필터 출력                                                 | 14 |

| 그림 4-7. CCS의 클록 및 데이터 입력 테스트 신호(반전되지 않은 GPIO123)와 Sinc3 OSR 64 필터 출력                                                 | 14 |

| 그림 4-8. 소프트웨어 구성 가능 위상 지연을 사용한 클록 에지 보상으로 20MHz 클록 주파수에서 데이터 시트의 일반 사양에 대한<br>AMC1305L25로의 타이밍 다이어그램 C2000 디지털 인터페이스 |    |

| <b>표</b>                                                                                                             |    |

| 표 4-1. 테스트 강비 목록                                                                                                     | 10 |

| 표 4-2. 20MHz 클록 주파수에서 AMC1305L25를 사용한 C2000 MCU TMS320F28379D 디지털 인터페이스 타이밍에 대한 결과                                   | 15 |

| 표 4-3. 17MHz 클록에서 AMC1305L25를 사용하는 TMS320F28379D 디지털 인터페이스 타이밍                                                       | 15 |

| 표 4-4. 소프트웨어 구성 가능 위상 지연을 사용한 20MHz 클록에서 AMC1305L25를 사용하는 TMS320F28379D 디지털 인터페                                      |    |

| 이스 타이밍표 5-1. 클록 에지 보상 방법 비교                                                                                          | 16 |

| 표 5-1. 클록 에지 보상 방법 비교                                                                                                | 17 |

| 표 5-2. 내부 또는 외부 클록을 사용하는 모듈레이터에 권장되는 클록 에지 보상 방법                                                                     | 17 |

|                                                                                                                      |    |

# 상표

C2000<sup>™</sup>, Sitara<sup>™</sup>, OSR<sup>™</sup>, and Code Composer Studio<sup>™</sup> are trademarks of Texas Instruments. 모든 상표는 해당 소유권자의 자산입니다. www.ti.com 머리말

#### 1 머리말

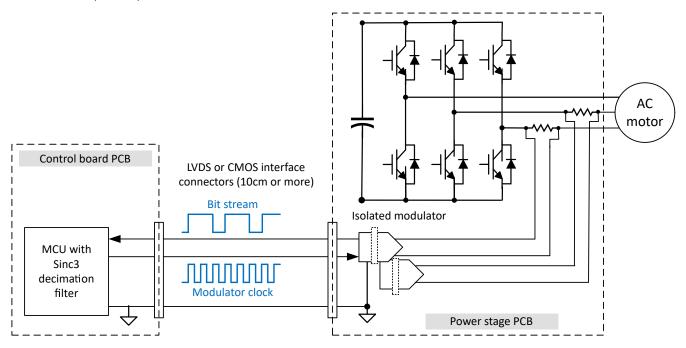

절연 델타-시그마 모듈레이터는 서보 드라이브 및 로봇 애플리케이션에서 션트 기반 위상 전류 감지에 일반적으로 사용됩니다. 정확하고 낮은 지연 시간의 절연 위상 전류 감지가 3상 인버터의 성능에 상당한 영향을 미치기 때문입니다. 델타-시그마모듈레이터는 탁월한 잡음 내성, 높은 정밀도, 낮은 지연 시간 위상 전류 측정을 가능하게 하는 MCU로의 LVDS 또는 CMOS인터페이스를 갖춘 디지털 비트 스트림을 제공합니다. 절연 모듈레이션에 대한 자세한 내용은 절연 증폭기와 절연 모듈레이터 비교 애플리케이션 노트를 참조하십시오.

종종 션트와 절연 델타-시그마 모듈레이터는 그림 1과 같이 전력계 PCB(인쇄 회로 보드)에 배치되는 반면 MCU는 별도의 제어 보드 PCB에 배치됩니다. PCB와 인터페이스 커넥터에 적절한 라우팅 체계는 디지털 신호 무결성을 위해 매우 중요합니다. 클록 및 데이터 라인 라우팅 및 종료에 대한 모범 사례는 모터 드라이브에서 절연 델타-시그마 모듈레이터를 사용한 더 나은 신호 무결성 (TI.com) 애플리케이션 보고서에서 설명합니다.

그림 1-1. MCU에서 아이솔레이터 모듈레이터까지의 디지털 인터페이스를 사용한 간소화된 3상 인버터 블록 다이어그램

모듈레이터 클록 에지와 디지털 비트 스트림 간 타이밍을 충족하기 위한 추가 설계 문제가 있을 수 있으며, 특히 신호 트레이스가 매우 길면 추가 버퍼 및 레벨 변환기가 사용됩니다. 그런 다음 모듈레이터 클록과 비트 신호의 추가 전파 지연으로 인해설계자가 최대 21MHz(AMC1306)에서 15MHz 등으로 모듈레이터 클록을 줄여 MCU에서 클록 에지와 비트 스트림 데이터간 타이밍을 충족해야 할 수 있습니다. 이 때문에 전체 위상 전류 측정 지연 시간은 선택한 변조기 클럭에 반비례하여 증가합니다. 예를 들어 오버샘플링 비율이 64인 일반적으로 사용되는 Sinc3 데시메이션 필터는 20MHz 모듈레이터 클록에서 측정지연(전파 지연)이 4.8us이며, 15MHz 모듈레이터 클록만 사용할 수 있는 경우 지연 시간은 6.4us로 증가합니다.

이 문서의 다음 섹션에서는 이 설계 과제를 극복하기 위한 디지털 타이밍 보상 방법에 대한 개요를 설명하며, 절연 모듈레이터를 사용한 설계가 가장 높은 정밀도뿐 아니라 가장 쉽게 측정할 수 있음을 보여줍니다.

# 2 디지털 인터페이스 타이밍 사양의 설계 과제

절연 델타-시그마 모듈레이터는 CMOS 인터페이스 또는 LVDS 인터페이스를 사용하여 외부와 내부에서 생성된 클록 신호모두에 대한 인터페이스 옵션을 제공합니다. 예를 들어, CMOS 인터페이스를 사용하는 AMC1306M25 또는 LVDS 인터페이스를 사용하는 AMC1305L25와 같이 외부에서 제공되는 클록 소스를 사용하는 장치의 경우 클록 신호가 MCU에서 델타시그마 모듈레이터의 클록 입력으로 라우팅되는 반면, 내부에서 제공되는 클록 소스를 사용하는 장치의 경우 출력 비트 스트림이 내부적으로 생성된 클록에 동기화됩니다. 예를 들어 AMC1303M2520이 있습니다. 또한 단일 와이어 데이터 및 클록 전송을 지원하는 맨체스터 코딩 출력 비트 스트림을 사용하는 절연 델타-시그마 모듈레이터 장치도 있습니다. 예를 들어 AMC1306E25가 있습니다. 모든 절연 델타-시그마 모듈레이터의 데이터 출력은 클록 에지로 동기적으로 이동하는 디지털 1및 0의 비트 스트림을 제공합니다.

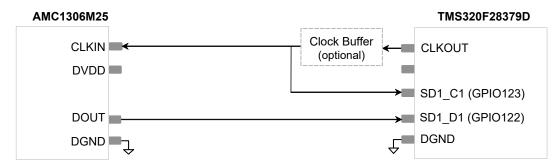

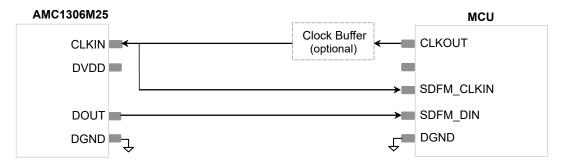

그림 2-1에서는 절연 델타-시그마 모듈레이터 AMC1306M25와 C2000 MCU TMS320F28379D 간에 3.3V I/O를 사용하는 CMOS 인터페이스의 간소화된 예를 보여줍니다. AMC1306M25에는 외부 제공 클록 소스가 필요하므로 클록 신호는 MCU TMS320F28379D에 의해 생성되며 델타-시그마 모듈레이터 클록 입력 CLKIN에 제공됩니다. 동시에, 생성된 클록 신호는 MCU SDFM(시그마-델타 필터 모듈) SD1\_C1(GPIO123)으로의 클록 입력으로도 라우팅됩니다. 시스템 설계에 따라 MCU와 절연 델타-시그마 모듈레이터 간의 클록 인터페이스에 포함된 클록 버퍼가 있을 수 있습니다. 델타-시그마 모듈레이터의 절연 데이터 출력 DOUT는 MCU SDFM(시그마-델타 필터 모듈) 데이터 입력 SD1\_D1(GPIO122)에 직접 연결됩니다.

그림 2-1. TMS320F28379D로의 간소화된 AMC1306M25 디지털 인터페이스

절연 델타-시그마 모듈레이터와 MCU 간의 유효한 통신은 설정 및 홀드 타이밍 요구 사항별로 각 장치 데이터 시트에 설명되어 있습니다. 설정 시간은 MCU에서 데이터 신호를 캡처하기 위해 클록 신호 전환 전에 데이터 신호가 유효하고 안정적이어야 하는 시간입니다. 홀드 시간은 클록 신호 전환이 발생한 후 신호가 유효하고 안정적이어야 하는 시간입니다. 위반이 발생하면 잘못된 데이터가 캡처될 수 있으므로 MCU 설정 및 홀드 시간 요구 사항을 따르는 것이 매우 중요합니다. 절연 델타-시그마 모듈레이터와 MCU의 디지털 인터페이스 설정과 홀드 타이밍 요구 사항이 호환되지 않는 경우 설계 문제가 발생할 수 있습니다.

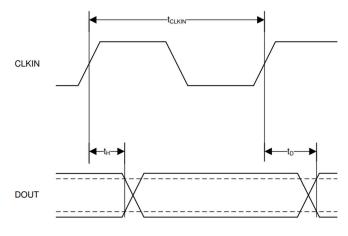

그림 2-2에는 데이터 홀드 시간 t<sub>h</sub>(MIN) = 3.5ns와 데이터 지연 시간 t<sub>d</sub>(MAX) = 15ns로 5MHz에서 21MHz의 권장 클록 주 파수(CLKIN)를 지원하는 AMC1306x의 설정 및 홀드 시간에 대한 디지털 인터페이스 타이밍이 나와 있습니다.

그림 2-2. AMC1306x 디지털 인터페이스 타이밍

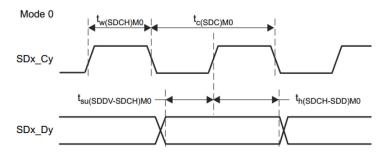

그림 2-3에는 모드 0에 대한 TMS320F28379D SDFM(시그마-델타 필터 모듈)의 타이밍 다이어그램이 나와 있습니다. SDX\_Dy에서의 데이터 입력은 SDFM 모듈의 SDX\_Cy 신호의 상승 클록 에지를 기준으로 최소 설정 시간  $t_{su(SDDV-SDCH)M0}$  및 최소 홀드 시간  $t_{h(SDCH-SDD)M0}$ 을 충족해야 합니다.

그림 2-3. TMS320F28379D SDFM 타이밍 다이어그램 - 모드 0

모드 0의 TMS320F28379D SDFM 모듈의 경우 적격 GPIO(3 샘플 윈도우)와 함께 SDFM 작동을 사용하는 것이 좋습니다. 이 모드는 입력 클록 신호(SDX\_Cy) 및 데이터 입력(SDX\_Dy)을 사용하여 무작위 노이즈 글리치로부터 보호하여 잘못된 콤퍼레이터 과전류 트립 및 잘못된 Sinc 필터 출력을 방지합니다. TMD320F28379D를 사용한 200MHz 시스템 클록에 대한 최소 설정 및 홀드 시간은 모두 10ns:  $t_{su(SDDV-SDCH)M0}(MIN)$  = 10ns 및  $t_{h(SDCH-SDD) M0}(MIN)$  = 10ns입니다.

이로 인해 AMC1306M25 최소 홀드 시간  $t_h(MIN)$  가 3.5ns이지만 SDFM 모듈이 SDX\_Cy 신호의 상승 클록 에지를 참조하여 데이터 입력 SDX\_Dy에서 올바른 수집을 유지하려면 10ns가 필요하다는 설계 과제가 발생합니다.

또 다른 과제는 클록 버퍼와 같은 디지털 인터페이스를 사용한 신호 체인에서 추가 부품의 전파 지연, 그리고 PCB의 트레이스 길이에 의해 발생하는 클록 및 데이터 신호의 전파 지연이 SDx\_Cy 입력과 SDx\_Dy 입력 사이의 타이밍에 영향을 미치고 데이터 입력의 올바른 수집 타이밍을 복잡하게 한다는 것입니다.

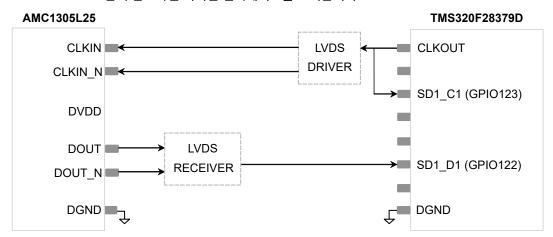

이는 AMC1305L25와 같은 LVDS 인터페이스를 사용하는 델타-시그마 모듈레이터에도 동일하게 적용됩니다. CMOS 인터페이스 유형을 사용하는 AMC1306M25 델타-시그마 모듈레이터의 유일한 차이점은 디지털 신호 체인에서 CMOS 인터페이스를 사용하는 MCU로의 LVDS 드라이버 및 리시버와 같은 추가 부품이 필요하여 추가적인 전파 지연을 유발한다는 것입니다. 그림 2-4은 LVDS 인터페이스를 사용하는 절연 델타-시그마 모듈레이터 AMC1305L25와 CMOS 인터페이스를 사용하는 MCU TMS320F28379D 간의 간소화된 디지털 인터페이스를 보여줍니다.

그림 2-4. TMS320F28379D로의 AMC1305L25 디지털 인터페이스

그림 2-5은 CMOS 인터페이스를 사용하는 AMC1303Mx에서 CMOS 인터페이스를 사용하는 TMS320F28379D까지 내부적으로 생성된 클록 소스를 사용하는 절연 델타-시그마 모듈레이터의 간소화된 디지털 인터페이스를 보여줍니다. AMC1303Mx의 내부적으로 생성된 클록 신호 CLKOUT는 MCU SDFM(시그마-델타 필터 모듈) SD1\_C1(GPIO123)으로의 입력입니다. 델타-시그마 모듈레이터의 절연 데이터 출력 DOUT는 SDFM의 MCU 데이터 입력 SD1\_D1(GPIO122)에 직접 연결됩니다.

그림 2-5. TMS320F28379D로의 AMC1303M2520 3.3V CMOS 디지털 인터페이스

내부 클록과 함께 절연 모듈레이터를 사용하는 경우 절연 델타-시그마 변조기와 MCU 설정 시간과 홀드 시간의 서로 다른 타이밍 사양으로 디지털 인터페이스 문제가 제한됩니다. 클록 및 데이터 신호가 동일한 길이로 라우팅되면 PCB의 트레이스 길이에 의해 도입된 클록 및 데이터 신호의 전파 지연은 무시할 수 있습니다. 일반적으로 모듈레이터가 MCU와 직접 인터페이스 하며, 버퍼 또는 레벨 시프터가 필요하지 않으므로 전파 지연이 추가됩니다.

AMC1303Mx 홀드 시간  $t_h(MIN)$ 는 7ns0I며, 10MHz 및 20MHz 클록 버전에서 지연 시간  $t_d(MAX)$ 는 15ns입니다. 문제는 AMC1303Mx 최소 홀드 시간  $t_h(MIN)$ 가 7ns0I지만, 설정 및 홀드 시간 위반 없이  $SDX_Dy$ 에서 데이터 입력을 정확하게 수 집하기 위해 SDFM 모듈에 10ns가 필요하다는 것입니다.

AMC1306E25와 같이 맨체스터로 인코딩된 비트 스트림 출력을 사용하는 절연 델타-시그마 모듈레이터의 경우 데이터 및 클록이 단일 와이어를 통해 전송됩니다. 따라서 수신 장치와 모듈레이터 클록 비교 시 설정 및 홀드 시간 요구 사항을 고려할 필요가 없습니다.

MCU 설정 및 홀드 시간 요구 사항을 충족하기 위해 일반적으로 사용되는 방법과 절충안은 클록 주파수를 줄이는 것입니다. 그러나 클록 주파수를 줄이면 절연 델타-시그마 모듈레이터의 데이터 출력 속도가 줄어들고 전류 측정의 지연 시간이 늘어납니다. 더 적합한 방법은 클록 에지 지연 보상을 사용하여 클록 신호의 클록 에지를 데이터 신호의 이상적인 샘플 지점으로 이동하여 설정 및 홀드 타이밍 요구 사항을 충족하는 것입니다. 이 방법을 사용하면 클록 주파수 제한이 사라져 절연 델타-시그마 모듈레이터와 시스템이 최대 성능으로 작동할 수 있습니다.

# 3 클록 에지 지연 보상을 사용한 디자인 접근 방식

안정적인 데이터 수집을 위한 MCU 설정 및 홀드 타이밍 요구 사항을 충족하고 더욱 최적화하려면 클록 에지 지연 보상을 사용하는 것이 좋습니다. 클록 에지 지연 보상은 아래와 같이 다양한 방법으로 구현되며 다음 섹션에서 자세히 알아볼 수 있습니다.

- 1. 소프트웨어 구성 가능 위상 지연을 사용한 추가 클록 신호

- 2. 하드웨어 구성 가능 위상 지연을 사용한 클록 신호

- 3. 클록 반화

- 4. MCU에서 클록 반전

# 3.1 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상

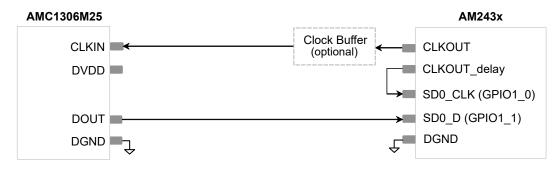

그림 3-1은 소프트웨어 구성 가능 위상 지연을 사용한 추가 위상 잠김 클록 신호를 사용하는 첫 번째 보상 방법을 보여줍니다. 이 보상 방법의 경우 위상 전환 클록 신호 CLKOUT\_delay는 SDFM(시그마-델타 필터 모듈)의 SD0\_CLK에 대한 클록 입력으로 사용됩니다. C2000 MCU와 같은 다른 유형의 델타-시그마 모듈레이터 및 MCU의 경우에도 보상 방법은 동일한 원칙을 따릅니다.

그림 3-1. 소프트웨어 구성 가능 클록 위상 지연을 사용한 AMC1306M25에서 AM243x로의 MCU 인터페이스

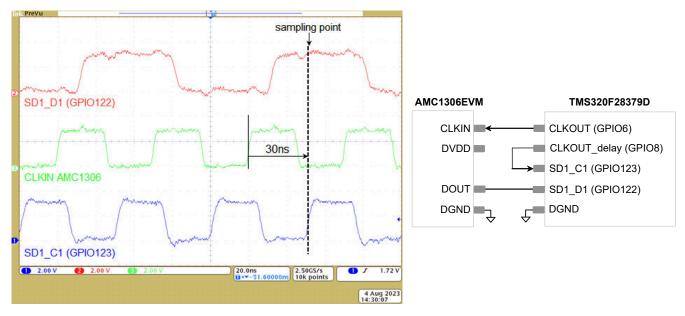

2차 위상 전환 클록 신호를 구현하면 가장 높은 수준의 자유도와 사용자 구성이 가능합니다. 즉, 다양한 절연 모듈레이터의 최소 홀드 시간  $t_h(MIN)$ 에 대한 다양한 값을 소프트웨어의 위상 변이 값만 간단히 변경하여 보상할 수 있습니다. SD0\_CLK 입력에서 클록 신호 상승 에지는 그림 3-2에서 볼 수 있듯이 클록 신호가 SDFM의 데이터 샘플링 지점을 준수하도록 위상 전환됩니다. 시그마 델타 모드의 AM243x PRU\_ICSSG PRU 타이밍 요구 사항은 최소 설정 시간  $t_{su(SD\_D-SD\_CLK)}(MIN)$  = 10ns 및 최소 홀드 시간  $t_{h(SD\_CLK-SD\_D)}(MIN)$  = 5ns에서 10ns입니다. AMC1306M25 최소 홀드 시간  $t_h(MIN)$ 가 3.5ns이지만 5ns가 필요할 수 있으므로 SDX\_CLK 신호의 상승 클록 에지를 참조하여 데이터 입력 SDX\_D에서 올바른 수집을 유지하려면 보상이 필요합니다. 이 보상 방법을 적용한 후에는 AM243x PRU\_ICSSG PRU 타이밍 요구 사항의 시그마 델타 모드에 대한 10ns 최소 설정 및 5ns 홀드 시간이 충족됩니다. 그림 3-2을 참조하십시오.

그림 3-2. SD0\_CLK에서 30ns 위상 전환 클록 신호 입력을 사용하는 AM243x SDFM 타이밍(GPIO1\_1)

# 3.2 하드웨어 구성 가능 위상 지연을 사용한 클록 신호 보상

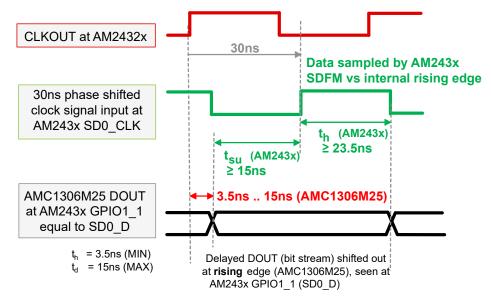

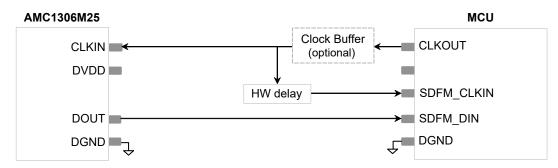

그림 3-3에 AMC1306M25와 MCU 간 디지털 인터페이스의 하드웨어 구성 가능 위상 지연을 사용한 클록 신호 보상이 나와 있습니다. 이 보상 방법을 사용하면 하드웨어의 위상 지연으로 인한 위상 전환 클록 신호가 MCU의 SDFM 모듈의 클록 입력 SDFM\_CLKIN에 연결됩니다. 이러한 유형의 보상은 시그마-델타 필터 모듈이 있는 모든 MCU에 사용되지만, 외부 클록 소스 및 CMOS 인터페이스가 있는 절연 델타-시그마 모듈레이터의 경우에만 권장됩니다.

그림 3-3. AMC1306M25 하드웨어 구성 가능 위상 지연에 의한 보상을 사용한 MCU로의 디지털 인터페이스

하드웨어에서 위상 지연을 구현하기 위해 로직 게이트 또는 버퍼를 사용하여 클록 신호에 전파 지연을 도입할 수 있습니다. 그러나, 하드웨어에서 지연을 구현할 때 지연 값은 자유도와 사용자 구성 가능성을 제한하는 하드웨어 블록의 전파 지연에 크게 좌우됩니다. 하드웨어 구성 가능 위상 지연을 사용한 클록 신호에 의한 보상의 작동 원리는 섹션 3.1에 설명된 것과 동일한 원리를 따릅니다.

### 3.3 클록 반환을 통한 클록 신호 보상

클록 반환을 통한 클록 신호 보상이 그림 3-4에 나와 있습니다. 이 보상 방법을 사용하면 AMC1306M25의 클록 입력인 CLKIN에 공급되는 클록 신호가 AMC1306M25의 CLKIN 핀에서 MCU의 SDFM 클록 입력 SDFM\_CLKIN으로 다시 라우 팅됩니다.

그림 3-4. AMC1306M25 클록 반환을 통한 보상을 사용한 MCU로의 디지털 인터페이스

이 방법을 사용하면 클럭 버퍼에 의한 전파 지연과 PCB 트레이스 길이에 의한 전파 지연이 클럭 및 데이터 신호에 대해 동일 하게 달성됩니다. 따라서 클럭 및 데이터 신호의 이러한 지연은 서로 상쇄됩니다.

그러나 데이터 홀드 시간  $t_h(MIN)$  = 3.5ns 및 데이터 지연 시간  $t_d(MAX)$  = 15ns에 대한 AMC1306M25 디지털 인터페이스 타이밍은 여전히 남습니다. 즉, PCB를 제작한 후 SDFM을 위한 MCU의 설정 및 홀드 타이밍 요구 사항이 충족되었는지 확인하기 위해 타이밍을 검사해야 합니다. 이러한 종류의 보상 방법은 외부 클록 소스 및 CMOS 인터페이스가 있는 절연 델타시그마 변조기에만 권장됩니다.

## 3.4 MCU에서 클록 반전에 의한 클록 신호 보상

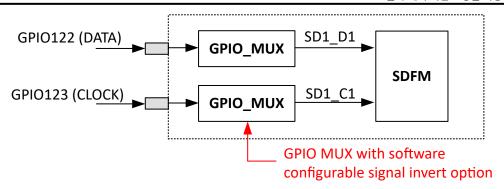

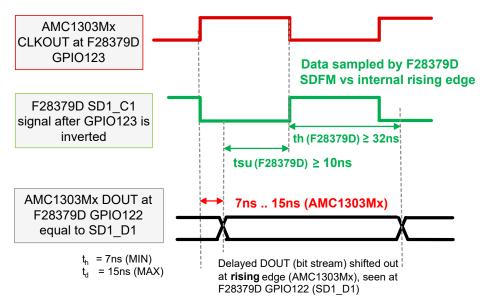

클록 신호 보상을 위한 마지막 방법은 MCU에서 클록 반전이며, 이는 외부 및 내부 클록 소스를 지원하는 델타-시그마 모듈레이터에 사용됩니다. 이 경우 선택한 MCU가 GPIO 입력을 반전할 수 있어야 합니다. SDFM(시그마 델타 필터 모듈) 이전의 TMS320F28379D GPIO 입력은 그림 3-5에 나와 있는 것처럼 모든 GPIO에서 입력 신호를 반전하도록 구성할 수 있습니다. 예를 들어 클록 입력 신호는 GPIO123에서 반전되므로 AMC1303Mx 클록 신호가 아닌 SD1\_C1 클록 신호가 반전됩니다. 따라서 SDFM은 그림 3-6에서 볼 수 있듯이 GPIO123의 입력에서 외부 클록 신호의 하강 에지가 아닌 입력 데이터 SD1\_D1을 샘플링합니다.

그림 3-5. TMS320F28379D SDFM/GPIO 블록 다이어그램

그림 3-6. GPIO123에서 반전 클록을 사용한 TMS320F28379D SDFM 타이밍

GPIO를 사용하여 클록 입력 신호를 반전하면 클록 기간 절반의 고정 지연이 클록 신호에 추가됩니다. 시스템 설정의 타이밍 사양 및 전파 지연에 따라, 이 추가 지연은 SDFM 인증 GPIO(3-샘플) 모드 0에 대한 최소 10ns의 TMS320F28379D 설정 및 홀드 타이밍을 충족하기에 충분할 수 있습니다. 그러나 이 클록 신호 보상 방법의 추가 지연 시간은 고정되어 있고 변경할 수 없으므로, 각 시스템 설계에서 SDFM 인증 GPIO(3-샘플) 모드 0을 위한 MCU의 설정 및 홀드의 결과 타이밍이 충족되었는지 확인해야 합니다.

이 보상 방법은 외부 클록 신호의 상승 및 하강 에지를 모두 소프트웨어로 데이터 수집 지점으로 설정할 수 있는 Sitara MCU 에도 적용됩니다.

테스트 및 검증 www.ti.com

# 4 테스트 및 검증

다음 섹션에서는 섹션 3.1에 설명된 소프트웨어 위상 지연을 사용한 추가 클록과 섹션 3.4에 설명된 클록 반전을 사용한 클록에지 보상 테스트 결과를 보여줍니다. 먼저 테스트 장비 및 소프트웨어에 대해 설명하고 클록 신호 보상 방법의 테스트 설정, 측정 및 테스트 결과를 설명합니다.

# 4.1 테스트 장비 및 소프트웨어

측정을 위한 주요 테스트 장비가 표 4-1에 나와 있습니다.

표 4-1. 테스트 장비 목록

| 설명                                                    | 부품 번호              |

|-------------------------------------------------------|--------------------|

| AMC1306 강화 절연 모듈레이터 평가 모듈                             | AMC1306EVM         |

| Delfino C2000™ Delfino™ MCU용 F28379D LaunchPad™ 개발 키트 | LAUNCHXL-F28379D   |

| Arm® 기반 MCU를 위한 AM243x 범용 LaunchPad™ 개발 키트            | LP-AM243           |

| 고속 오실로스코프                                             | Tektronix MSO 4104 |

| 단일 종단 프로브                                             | Tektronix P6139A   |

소프트웨어 개발 및 디버깅은 CCS(Code Composer Studio<sup>TM</sup>) 버전 12.4.0을 사용하여 수행됩니다. CCS는 텍사스 인스트루먼트의 MCU(마이크로컨트롤러)와 임베디드 프로세서 포트폴리오를 지원하는 IDE(통합 개발 환경)입니다. 내부 TI 테스트 소프트웨어는 C2000WARE - C2000 마이크로컨트롤러용 C2000Ware를 기반으로 TMS320F28379D에 사용되었습니다. Sitara AM243x Launchpad의 경우 Sitara™ 마이크로컨트롤러 MCU-PLUS-SDK-AM243X 버전 09.00.00.35용 AM243x SDK(소프트웨어 개발 키트)를 기반으로 내부 TI 테스트 소프트웨어가 사용되었습니다. C2000 및 Sitara의 특정구현 및 소프트웨어 지원은 TI E2E 지원 포럼을 참조하십시오.

#### 4.2 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상 테스트

이 측정은 소프트웨어 구성 가능 위상 지연과 함께 추가 클록 신호를 사용하여 설정 및 홀드 타이밍 요구 사항이 클록 신호 보상으로 충족되는지 확인합니다. 이 테스트는 C2000 TMS320F28379D Launchpad 및 Sitara AM243x Launchpad 모두에서 수행되고 검증되었습니다.

### 4.2.1 테스트 설정

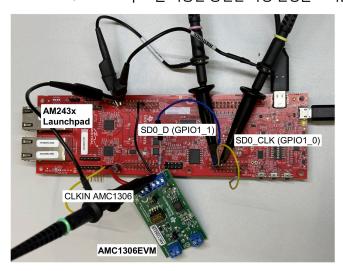

AMC1306EVM 및 C2000 TMS320F28379D Launchpad를 사용한 소프트웨어 구성 가능 위상 지연 측정과 함께 추가 클록 신호를 사용한 클록 신호 보상의 테스트 설정은 그림 4-1에 나와 있습니다. 이 측정을 위해 단일 종단 프로브를 사용하여 AMC1306EVM 클록 입력 CLKIN에서 클록 신호를 측정하고 SDFM의 MCU 데이터 입력 SD1\_D1(GPIO122)에서 측정된 델타-시그마 변조기의 데이터 출력인 DOUT을 측정합니다. 소프트웨어 프로그래머블 위상 지연을 사용하는 클록 신호는 MCU SDFM(시그마-델타 필터 모듈) SD1\_C1(GPIO123)의 클록 입력에서 측정됩니다. AMC1306EVM의 입력 핀 AINP와 AINN은 접지에 단락되어 50/50 1 및 0의 밀도가 출력됩니다. 아날로그 공급 AVDD는 EVM의 절연 변압기 회로를 사용하여 생성됩니다. 절연 모듈레이터 디지털 파워 공급 장치인 DVDD(3.3V)는 C2000 TMS320F28379D Launchpad로부터 제공됩니다.

www.ti.com 테스트 및 검증

그림 4-1. AMC1306EVM 및 C2000 TMS320F28379D Launchpad를 사용한 소프트웨어의 위상 지연에 의한 클록 신호 보상 테스트

그림 4-2는 해당 측정 지점과 Sitara AM243x Launchpad를 사용한 동일한 측정 설정을 보여줍니다.

그림 4-2. AMC1306EVM 및 Sitara AM243x Launchpad를 사용한 소프트웨어 구성 가능 위상 지연에 의한 클록 신호 보 상 테스트

#### 4.2.2 테스트 측정 결과

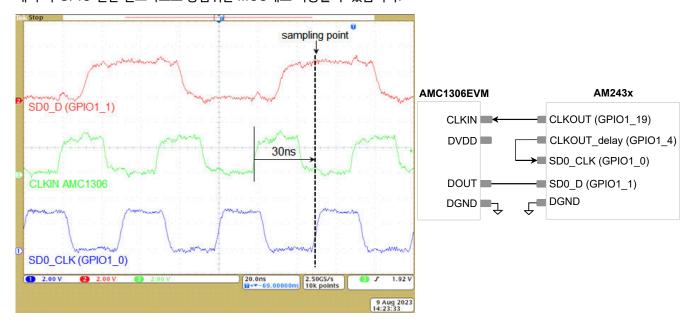

TMS320F28379D에서 내부 TI SDFM 소프트웨어 프로젝트를 실행했고, 여기서 두 GPIO인 GPIO122와 GPIO123이 SDFM 모드로 구성되었습니다. SDFM 데이터 필터는 오버샘플링 비율 64(OSR64)로 Sinc3용으로 구성됩니다. 테스트를 수행하기 위해 ePWM4 모듈로 50% 듀티 사이클을 가진 20MHz 클록 신호가 생성되고 AMC1306EVM의 CLKIN 핀에 공급됩니다. ePWM5 모듈은 50% 듀티 사이클 및 30ns 위상 편이를 사용하는 위상 동기 20MHz 클록 신호를 출력하도록 구성됩니다. 이 신호는 SD1\_C1(GPIO123)으로 공급됩니다. AMC1306EVM DOUT 데이터 비트 스트림은 상승 클록 에지에서만 변경되므로 AMC1306 데이터 시트의 섹션 7.11 스위칭 특성에 설명된 대로 클록 사이클당 한 번씩 변경됩니다.

그림 4-3은 오실로스코프 측정 및 인터페이스 다이어그램을 보여줍니다. AMC1306EVM CLKIN 핀에 공급되는 클록 신호는 채널 3에서 녹색 파형으로 표시되어 있습니다. AMC1306EVM에 의한 데이터 신호 출력은 채널 2에서 빨간색으로 표시된 SD1\_D1(GPIO122) 신호입니다. SD1\_C1(GPIO123)으로 공급되는 위상 전환 클록 신호는 채널 1에서 파란색으로 측정된 파형입니다. SDFM 모듈이 위상 전환 클록 신호 SD1\_C1(GPIO123)의 상승 에지를 기준으로 데이터 신호를 샘플링하면 결과 설정 시간은 약 18ns이며 결과 홀드 시간은 약 24ns입니다. 이를 통해 SDFM 인증 GPIO(3-샘플) 모드 0에 대한 최소

10ns의 TMS320F28379D 설정 및 홀드 타이밍이 충족됩니다. 또한 이 설계는 시스템 전파 지연의 변경(양극 또는 음극) 허용 오차를 가진 최적의 여유 값을 제공합니다.

그림 4-3. 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상을 사용하는 AMC1306EVM 및 TMS320F28379D의 디지털 인터페이스 타이밍 측정 결과

그림 4-4은 Sitara AM243x Launchpad를 사용하여 수행한 동일한 테스트에 대한 측정 결과를 보여줍니다. 결론적으로 소프 트웨어 구성 가능 위상 지연을 사용한 추가 클록 신호를 사용하는 클록 신호 보상은 MCU 설정 및 홀드 타이밍 요구 사항을 충 족하는 승인된 방법입니다. 이 방법은 위상 편이의 값을 구성할 수 있어 자유도가 가장 높으며, 위상 전환 클록 신호 구현을 위해 추가 GPIO 핀만 필요하므로 광범위한 MCU에도 사용할 수 있습니다.

그림 4-4. 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상을 사용하는 AMC1306EVM 및 AM243x의 디지털 인터 페이스 타이밍 측정 결과

#### 4.3 MCU에서 클록 반전에 의한 클록 신호 보상 테스트

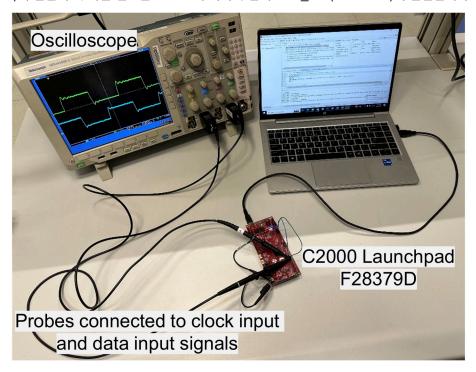

이 구성은 C2000 TMS320F28379D Launchpad에서 테스트되고 검증되었습니다.

www.ti.com *테스트 및 검증*

#### 4.3.1 테스트 설정

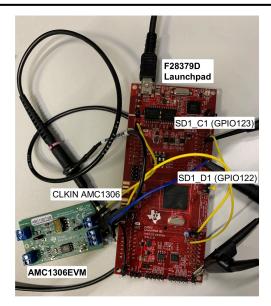

C2000 TMS320F28379D Launchpad를 사용하여 MCU에서 클록 반전을 통한 클록 신호 보상 테스트 설정은 그림 4-5에 나와 있습니다. 이 측정의 경우 MCU에서 2개의 테스트 신호를 생성합니다. 하나의 신호는 MCU SDFM의 클록 입력 SD1 C1(GPIO123)에 연결되고, 다른 신호는 SDFM의 데이터 입력 SD1 D1 (GPIO122)에 연결됩니다.

그림 4-5. 디지털 인터페이스 타이밍 검증의 테스트 설정

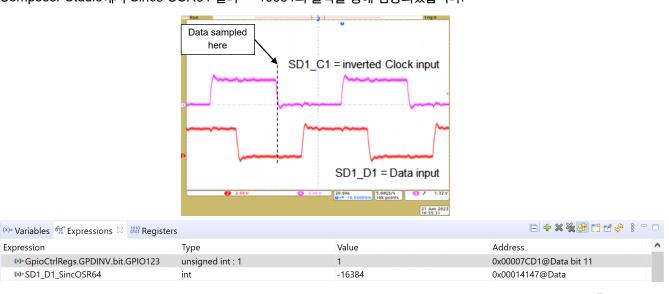

#### 4.3.2 테스트 측정 결과

TMS320F28379D에서 내부 TI SDFM 소프트웨어 프로젝트를 실행했고, 여기서 두 GPIO인 GPIO122와 GPIO123이 SDFM 모드로 구성되었습니다. SDFM 필터는 Sinc3 및 OSR™ 64 필터용으로 구성됩니다. Sinc3 OSR64 필터는 +16384에서 -16384의 최대 풀 스케일 범위로 16비트 2의 보수 정수를 출력합니다.

테스트를 수행하기 위해 50% 듀티 사이클의 90도 위상 전환 10MHz 클록 신호 2개가 각각 GPIO123(SD1\_C1)과 GPIO122(SD1\_D1)에 공급됩니다. AMC1306EVM DOUT 데이터 비트 스트림은 상승 클록 에지에서만 변경되므로 클록 사이클당 한 번입니다. 이 테스트에서 SD1\_D1 데이터는 절반 클록 사이클마다 0과 1 사이를 전환합니다. 이는 모든 클록 사이클에서 변경되는 AMC1306EVM DOUT 데이터 신호와 다릅니다.

이 특정 테스트 신호를 적용하므로 GPIO122(SD1\_D1)의 입력 데이터는 GPIO123의 상승 클록 에지에서 항상 논리 '1'이며 하강 에지에서 항상 논리 '0'입니다. 따라서 OSR 64 필터를 사용하는 Sinc3 필터의 출력은 SDFM에서 테스트 데이터가 샘 플링되는 클럭 에지에 따라 달라지며, Sinc3 OSR 64 필터 출력은 GPIO123에서 클록 반전이 없으면 16384(항상 샘플링 '1'), GPIO123에서 클록 반전이 있으면 -16384(항상 샘플링 '0')입니다.

### 4.3.2.1 테스트 결과 - GPIO123에서 클럭 입력의 클럭 반전 없음

그림 4-6은 GPIO123에 대한 입력인 클록 신호 SD1\_C1과 GPIO122에 대한 입력인 위상 전환 데이터 신호 SD1\_D1의 오 실로스코프 측정을 보여줍니다. 이 측정에서 GPIO123은 아래 그림과 같이 소프트웨어에 의해 반전되지 않습니다.

```

// Set 3-sample qualifier for GPIO122 and GPIO123 and do not invert GPIO123

GPIO_SetupPinOptions(122, GPIO_INPUT, GPIO_QUAL3); // GPIO123 not inverted

GPIO_SetupPinMux(122,GPIO_MUX_CPU1,7); // MUX position 7 for SD1_D1

GPIO_SetupPinMux(123,GPIO_MUX_CPU1,7); // MUX position 7 for SD1_C1

```

데이터 SD1\_D1은 SD1\_C1의 상승 에지에서 TMS320F28379D SDFM에서 샘플링됩니다. 이는 GPIO123에서 반전되지 않은 클록 신호의 상승 에지에 해당합니다. TMS320F28379D에서 샘플링된 데이터는 항상 논리 '1'이었으며, 아래 표시된 것처럼 CCS(Code Composer Studio™)의 Sinc3 OSR64 필터 = +16384의 출력을 통해 검증되었습니다.

테스트 및 검증 www.ti.com

그림 4-6. CCS의 클록 및 데이터 입력 테스트 신호(반전되지 않은 GPIO123)와 Sinc3 OSR 64 필터 출력

#### 4.3.2.2 테스트 결과 - GPIO123에서 클록 입력의 클록 반전

그림 4-7은 GPIO123에 대한 입력인 클록 신호 SD1 C1과 GPIO122에 대한 입력인 위상 전환 데이터 신호 SD1 D1을 보 여줍니다. 이 테스트 설정에서 GPIO123은 아래 그림과 같이 소프트웨어에 의해 반전됩니다.

```

// Set 3-sample qualifier for GPIO122 and GPIO123 and do not invert GPIO123

GPIO_SetupPinOptions(123, GPIO_INPUT, GPIO_INVERT | GPIO_QUAL3);

GPIO_SetupPinMux(122,GPIO_MUX_CPU1,7); // MUX position 7 for SD1_D1 GPIO_SetupPinMux(123,GPIO_MUX_CPU1,7); // MUX position 7 for SD1_C1

```

데이터 SD1\_D1은 이제 SD1\_C1의 하강 에지에서 F28379D SDFM에 의해 샘플링되며, 이는 GPIO123 입력에서 반전 클 록 신호의 상승 에지에 해당합니다. F28379D에서 샘플링된 데이터는 항상 논리 '0'이었으며, 아래 표시된 것처럼 Code Composer Studio에서 Sinc3 OSR64 필터 = -16384의 출력을 통해 검증되었습니다.

그림 4-7. CCS의 클록 및 데이터 입력 테스트 신호(반전되지 않은 GPIO123)와 Sinc3 OSR 64 필터 출력

결론적으로 소프트웨어에서 GPIO 입력의 클럭 입력을 반전하여 클럭 신호 보상 방법을 검증하였습니다. 클록을 반전하면 클 록 기간의 절반의 고정 지연이 클록 신호에 추가되며, 이는 SDFM 인증 GPIO(3-샘플) 모드 0에 대한 TMS320F28379D 설 정 및 10ns의 최소 타이밍을 충족하기에 충분할 수 있습니다. 그러나 SDFM 인증 GPIO(3-샘플) 모드 0에 대한 MCU의 설 정 및 유지의 결과 타이밍이 충족될 수 있는 경우 각 시스템 설계를 개별적으로 확인해야 합니다.

www.ti.com *테스트 및 검증*

### 4.4 계산 툴을 사용한 디지털 인터페이스 타이밍 검증

계산 둘은 MCU와 절연 델타-시그마 모듈레이터 간의 디지털 인터페이스 타이밍의 시뮬레이션 및 검증 목적으로 개발되었습니다. 가장 일반적으로 사용되는 절연 델타-시그마 모듈레이터인 AMC1306M25 및 AMC1305L25는 디지털 인터페이스 타이밍 분석을 위해 선택됩니다. AMC1305L25에는 LVDS 인터페이스 유형이 있으며 CMOS 인터페이스를 사용하여 MCU와 인터페이싱할 때 LVDS 드라이버와 LVDS 리시버가 필요합니다. 계산 툴에 설정과 홀드 시간 요구 사항만 입력되기 때문에 사용자가 MCU를 개별적으로 선택할 수 있습니다. 다음은 AMC1305L25와 C2000 MCU TMS320F28379D 간의 디지털 인터페이스 타이밍을 최적화하기 위해 계산 툴을 사용하는 방법을 단계별로 설명한 것입니다.

#### 4.4.1 보상 방법 없는 디지털 인터페이스

C2000 MCU TMS320F28379D는 200MHz 시스템 클록, 모드 0에서 SDFM GPIO 입력 인증(3-샘플 윈도우) 옵션으로 작동합니다. 최소 설정 및 유지 시간은 모두 10ns:  $t_{su(SDDV-SDCH)\ M0}(MIN)$  = 10ns 및  $t_{h(SDCH-SDD)M0}(MIN)$  = 10ns입니다. 또한 LVDS 드라이버 DSLVDS1047 및 LVDS 리시버 DSLVDS1048의 전파 지연이 참조를 위해 입력됩니다. 절연 델타 시그마 모듈레이터 클록 입력에서 데이터 시트에 지정된 최대 클록 주파수인 20MHz 클록 신호를 사용할 때, 표 2에 나와 있는 것처럼 AMC1305L25의 데이터 지연 시간  $t_D$ 가  $t_D(MIN)$  = 0ns로 데이터 시트에 제공된 최소 사양과 같을 경우 MCU 설정 시간 요구 사항이 위반됩니다.

표 4-2. 20MHz 클록 주파수에서 AMC1305L25를 사용한 C2000 MCU TMS320F28379D 디지털 인터페이스 타이밍 에 대한 결과

| " " '          |         |  |  |  |

|----------------|---------|--|--|--|

| MCU에서 최소 설정 시간 | 5.6 ns  |  |  |  |

| MCU에서 최대 설정 시간 | 23.3 ns |  |  |  |

| MCU에서 최소 홀드 시간 | 26.7 ns |  |  |  |

| MCU에서 최대 홀드 시간 | 44.4 ns |  |  |  |

# 4.4.2 일반적으로 사용되는 방법 - 클록 주파수 줄이기

MCU 타이밍 요구 사항을 충족하는 절충안은 모듈레이터 클록 주파수를 줄이는 것입니다. 이 예에서 17MHz 클록 주파수를 사용하면 MCU의 설정 및 홀드 타이밍 요구 사항을 충족할 수 있습니다. 표 4-3에 17MHz의 클록 주파수에서 최소 및 최대 값을 포함하여 계산된 설정 및 홀드 시간이 나와 있습니다. MCU 설정 시간 요구 사항에 대한 최소 설정 시간 여유는 0ns입니다. 즉, 시스템의 허용 오차로 인해 데이터가 잘못 수집될 수 있습니다. 클록 주파수를 더욱 줄여 시스템의 허용 오차에 대한 더 큰 여유를 달성할 수 있지만, 이는 시스템 성능에 부정적인 영향을 미칩니다.

# 표 4-3. 17MHz 클록에서 AMC1305L25를 사용하는 TMS320F28379D 디지털 인터페이스 타이밍

| MCU에서 최소 설정 시간 | 10.0 ns |

|----------------|---------|

| MCU에서 최대 설정 시간 | 27.7 ns |

| MCU에서 최소 홀드 시간 | 31.1 ns |

| MCU에서 최대 홀드 시간 | 48.8 ns |

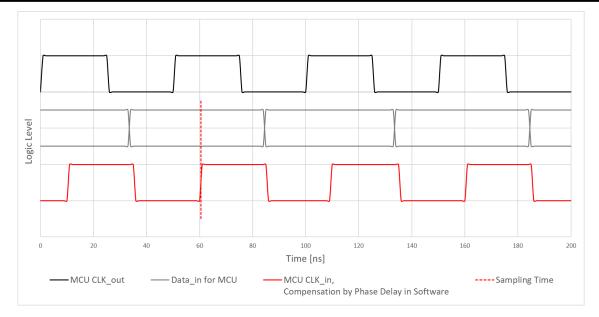

#### 4.4.3 소프트웨어 구성 가능 위상 지연을 사용한 클록 에지 보상

소프트웨어 구성 가능 위상 지연을 사용한 클록 에지 보상의 디지털 인터페이스가 그림 4-8에 나와 있습니다. 타이밍 다이어 그램은 클록 주파수가 20MHz인 클록 신호를 보여주며, 이는 첫 번째 신호로 절연 델타-시그마 모듈레이터로 공급되는 클록 신호를 나타냅니다. 타이밍 다이어그램에 표시된 두 번째 신호는 데이터 시트에 제시된 일반 사양에 대한 절연 델타-시그마 변조기의 데이터 출력을 나타냅니다. 세 번째 신호는 MCU SDFM의 클록 입력에 공급되는 첫 번째 신호를 기준으로 10ns로 이동한 20MHz 클록 신호 위상을 나타냅니다.

그림 4-8. 소프트웨어 구성 가능 위상 지연을 사용한 클록 에지 보상으로 20MHz 클록 주파수에서 데이터 시트의 일반 사양에 대한 AMC1305L25로의 타이밍 다이어그램 C2000 디지털 인터페이스

최소값과 최대값을 포함하여 계산된 설정 및 홀드 시간이 표 4-4에 나와 있습니다. 위상 지연을 소프트웨어에서 구성할 수 있으므로, 데이터 수집 타이밍이 데이터 신호의 중심에 오도록 위상 지연 값을 선택할 수 있습니다. 이를 통해 시스템의 허용 오차가 데이터 수집에 영향을 주지 않도록 설정 및 홀드 시간에 가능한 최대 여유 값을 사용할 수 있습니다. 계산 툴은 디지털 타이밍 인터페이스의 여유 값을 제공하므로 시스템의 허용 오차를 파악할 수 있습니다. 10ns의 선택된 위상 지연의 경우 최소설정 시간은 15.6ns로, MCU 설정 시간 요구 사항 10ns을 빼면 여유 값이 5.6ns입니다. 최소 유지 시간에 대한 여유 값도 이렇게 계산되며 6.7ns입니다.

표 4-4. 소프트웨어 구성 가능 위상 지연을 사용한 20MHz 클록에서 AMC1305L25를 사용하는 TMS320F28379D 디지털 인터페이스 타이밍

| 위상 지연          | 제안된 위상 지연 | 제안된 위상 지연 |       | 선택   | 백된 위상 지연 |

|----------------|-----------|-----------|-------|------|----------|

|                | 최소        | 4.4       | 4 ns  | 10.0 | 0 ns     |

|                | 최대        | 16        | 5.7ns |      |          |

| MCU에서 최소 설정 시간 |           | •         |       | 15.6 | 6 ns     |

| MCU에서 최대 설정 시간 |           |           |       | 33.0 | 3 ns     |

| MCU에서 최소 홀드 시간 |           |           |       | 16.7 | 7ns      |

| MCU에서 최대 홀드 시간 |           |           |       | 34.4 | 4 ns     |

# 5 결론

클록 에지 지연 보상은 모듈레이터 클록 주파수를 줄일 필요 없이 절연 델타-시그마 모듈레이터와 MCU 디지털 인터페이스를 통해 설정 및 홀드 시간 요구 사항을 충족하는 데 도움이 됩니다. 따라서 시스템이 최대 성능으로 작동할 수 있습니다.

클록 에지 지연 보상은 다음과 같은 여러 방법을 통해 구현할 수 있습니다.

- 소프트웨어 구성 가능 위상 지연을 사용한 추가 클록 신호

- 하드웨어 구성 가능 위상 지연을 사용한 클록 신호

- 클록 반환

- MCU의 클<del>록</del> 반전

소프트웨어 구성 가능 위상 지연 및 MCU의 클록 반전을 사용한 추가 클록 신호와 같은 보상 방법은 가장 일반적으로 사용되는 절연 델타-시그마 모듈레이터 변형에 대해 자세히 분석하고 AMC1306EVM 평가 모듈 및 C2000 TMS320F28379D Launchpad와 MCU로 선택한 Sitara AM243x Launchpad를 사용하여 검증했습니다. 테스트 결과는 CMOS 인터페이스와 SDFM을 사용한 MCU와 PRU를 사용할 때 SDFM이 없는 Sitara MCU의 경우 모두에 적용됩니다.

www.ti.com

표 5-1에는 각 클록 신호 보상 방법의 장점과 단점이 나와 있습니다. 다음 약어 SW 위상 지연 및 HW 위상 지연은 소프트웨어 구성 가능 위상 지연과 하드웨어 구성 가능 위상 지연을 사용한 보상에 사용됩니다.

#### 표 5-1. 클록 에지 보상 방법 비교

| 방법       | 장점                                                                                                                                        | 단점                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| SW 위상 지연 | <ul> <li>전파 지연의 보상</li> <li>최대 클록 주파수를 사용하여 가장 안정적으로 통신</li> <li>정확한 위상 지연 구현</li> <li>실행 시간 동안 변경할 수 있음</li> <li>추가 BOM 비용 없음</li> </ul> | 하나의 추가 MCU GPIO와 내부 위상 잠김 클록<br>소스 필요    추가 MCU 소프트웨어                                             |

| HW 위상 지연 | MCU 소프트웨어 변경 없음     추가 MCU GPIO가 필요하지 않음                                                                                                  | 구현된 하드웨어 지연 하드웨어에 따른 보상     하드웨어 구성 요소에 의한 위상 지연의 정밀도에서 허용 오차     실행 시간 동안 변경할 수 없음     추가 BOM 비용 |

| 클록 반환    | • 소프트웨어 및 하드웨어 작업 없음                                                                                                                      | <ul> <li>일부 구성에서 작동하지 않음</li> <li>레이아웃 조정</li> <li>더 긴 클록 신호는 과도 잡음에 더 민감</li> </ul>              |

| 클록 반전    | 간단한 구현을 통해 클록 기간의 절반의 보상으로 타이밍 차이 해결                                                                                                      | 일부 구성에서 작동하지 않음     클록 기간의 절반만으로 고정 보정     MCU가 GPIO 입력에서 클록 신호를 반전할 수 있어야 함                      |

클록 소스가 외부인지 내부인지, 그리고 CMOS 또는 LVDS 인터페이스에 따라 달라지는 델타-시그마 모듈레이터 유형에 따라, 특정 클록 신호 보상 방법이 다른 방법보다 더 나을 수 있습니다. 표 5-2은 일반적으로 사용되는 각 델타-시그마 모듈레이터 유형에 제안되는 보상 방법을 비교한 것입니다.

표 5-2. 내부 또는 외부 클록을 사용하는 모듈레이터에 권장되는 클록 에지 보상 방법

| 방법          | AMC1306M25<br>외부 클록(CMOS) | AMC1305L25<br>외부 클록(LVDS) | AMC1303M2520/10<br>내부 클록(CMOS) |

|-------------|---------------------------|---------------------------|--------------------------------|

| 소프트웨어 위상 지연 | +                         | +                         | 해당 없음                          |

| 하드웨어 위상 지연  | 0                         | 0                         | 0                              |

| 클록 반환       | 0                         | -                         | 해당 없음                          |

| 클록 반전       | 0                         | 0                         | +                              |

외부 클록이 필요한 모듈레이터의 경우, 클록 사이클의 고정된 절반이 요구 사항을 충족하면 소프트웨어 구성 가능 위상 지연을 사용한 클록 신호 보상이 최상의 성능을 발휘하고, 그 다음이 MCU에서 클록 반전입니다. 이러한 두 클록 신호 보상 방법 모두 MCU의 설정 및 홀드 타이밍 요구 사항을 충족하는 데 도움이 됩니다. 특히 높은 모듈레이터 클록 주파수에서 더 그렇습니다. 다음 계산 툴을 사용하여 델타-시그마 모듈레이터 AMC1306M25 및 AMC1305L25를 사용할 때 MCU의 설정 및 유지 타이밍 요구 사항을 검증할 수 있습니다.

참고 자료 www.ti.com

# 6 참고 자료

- 텍사스 인스트루먼트, 모터 드라이브에서 절연 델타-시그마 모듈레이터로 더 나은 신호 무결성 달성 애플리케이션 보고서

- 텍사스 인스트루먼트, 고전압 시스템을 위한 고성능 절연 ADC, 개요

- 텍사스 인스트루먼트, 절연 증폭기와 절연 모듈레이터 비교 백서

- 텍사스 인스트루먼트, AMC1306x, 높은 CMTI를 사용하는 소형, 고정밀, 강화 절연 델타 시그마 모듈레이터 데이터 시트

- 텍사스 인스트루먼트, AMC1305x 고정밀, 강화 절연 델타-시그마 모듈레이터 데이터 시트

- 텍사스 인스트루먼트, AMC1303x, 내부 클록을 사용하는 소형, 고정밀, 강화 절연 델타 시그마 모듈레이터 데이터 시트

- 텍사스 인스트루먼트, TMS320F2837xD 듀얼 코어 마이크로컨트롤러 데이터시트

- 텍사스 인스트루먼트, TMS320F2837xD 듀얼 코어 마이크로컨트롤러 기술 레퍼런스 매뉴얼

- 텍사스 인스트루먼트, AM243x Sitara™ 마이크로컨트롤러 데이터 시트

- 텍사스 인스트루먼트, MCU-PLUS-SDK-AM243X SDK(소프트웨어 개발 키트) 툴

www.ti.com Revision History

# 7 Revision History

| CI | hanges from Revision * (December 2023) to Revision A (January 2024) | Page |

|----|---------------------------------------------------------------------|------|

| •  | 문서 전체에서 표, 그림 및 상호 참조에 대한 번호 매기기 형식이 업데이트되었습니다                      | 1    |

| •  | 업데이트된 계산 툴 하이퍼링크                                                    | 15   |

# 중요 알림 및 고지 사항

TI는 기술 및 신뢰성 데이터(데이터시트 포함), 디자인 리소스(레퍼런스 디자인 포함), 애플리케이션 또는 기타 디자인 조언, 웹 도구, 안전 정보 및 기타 리소스를 "있는 그대로" 제공하며 상업성, 특정 목적 적합성 또는 제3자 지적 재산권 비침해에 대한 묵시적 보증을 포함하여(그러나 이에 국한되지 않음) 모든 명시적 또는 묵시적으로 모든 보증을 부인합니다.

이러한 리소스는 TI 제품을 사용하는 숙련된 개발자에게 적합합니다. (1) 애플리케이션에 대해 적절한 TI 제품을 선택하고, (2) 애플리케이션을 설계, 검증, 테스트하고, (3) 애플리케이션이 해당 표준 및 기타 안전, 보안, 규정 또는 기타 요구 사항을 충족하도록 보장하는 것은 전적으로 귀하의 책임입니다.

이러한 리소스는 예고 없이 변경될 수 있습니다. TI는 리소스에 설명된 TI 제품을 사용하는 애플리케이션의 개발에만 이러한 리소스를 사용할 수 있는 권한을 부여합니다. 이러한 리소스의 기타 복제 및 표시는 금지됩니다. 다른 모든 TI 지적 재산권 또는 타사 지적 재산권에 대한 라이선스가 부여되지 않습니다. TI는 이러한 리소스의 사용으로 인해 발생하는 모든 청구, 손해, 비용, 손실 및 책임에 대해 책임을 지지 않으며 귀하는 TI와 그 대리인을 완전히 면책해야 합니다.

TI의 제품은 ti.com에서 확인하거나 이러한 TI 제품과 함께 제공되는 TI의 판매 약관 또는 기타 해당 약관의 적용을 받습니다. TI가 이러한 리소스를 제공한다고 해서 TI 제품에 대한 TI의 해당 보증 또는 보증 부인 정보가 확장 또는 기타의 방법으로 변경되지 않습니다.

TI는 사용자가 제안했을 수 있는 추가 또는 기타 조건을 반대하거나 거부합니다.

주소: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated