# UCC25661 750kHz Wide V<sub>IN</sub>/V<sub>OUT</sub> Range LLC Controller Optimized for Light-Load **Efficiency**

### 1 Features

- Full-load switching frequency: 50kHz to 750kHz

- IPPC control enables wide input or wide output LLC (WLLC) operation

- Enhanced light load management:

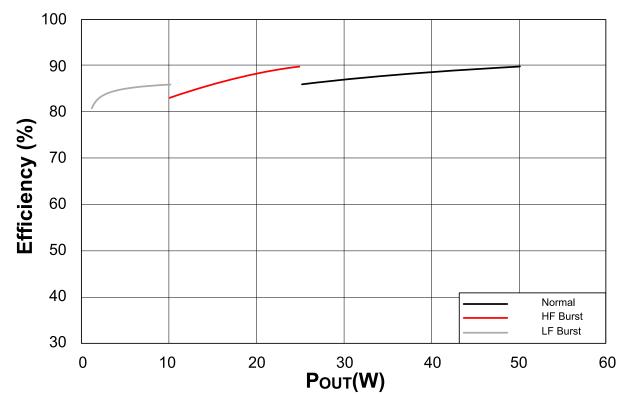

- High frequency pulse skip for improved light load efficiency

- Audible frequency range skip for reduced audible noise & soft on/off burst mode

- Low frequency burst for low standby power and integrated PFC on/off control

- Internal resonant-capacitor voltage synthesizer for enhanced signal reliability and high start-up frequency support

- Zero current switching (ZCS) avoidance to eliminate capacitive region operation

- Adaptive soft start with minimized inrush current and eliminating reverse recovery at start-up

- Integrated high-voltage start-up

- Integrated gate drive: +0.6/-1.2A

- Complete protections

- 50ns overcurrent protection (OCP), cycle-bycycle current limit

- Overvoltage protection (OVP), output-voltage

- Internal and external overtemperature protection (OTP)

- Input and VCCP UVLO with internal 19V VCCP Clamp

- Independently configured OCP and overload protection

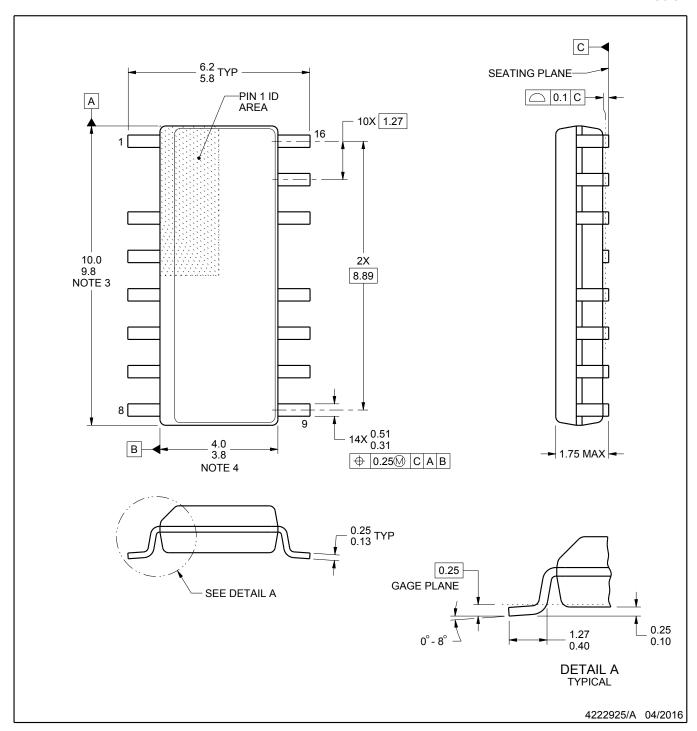

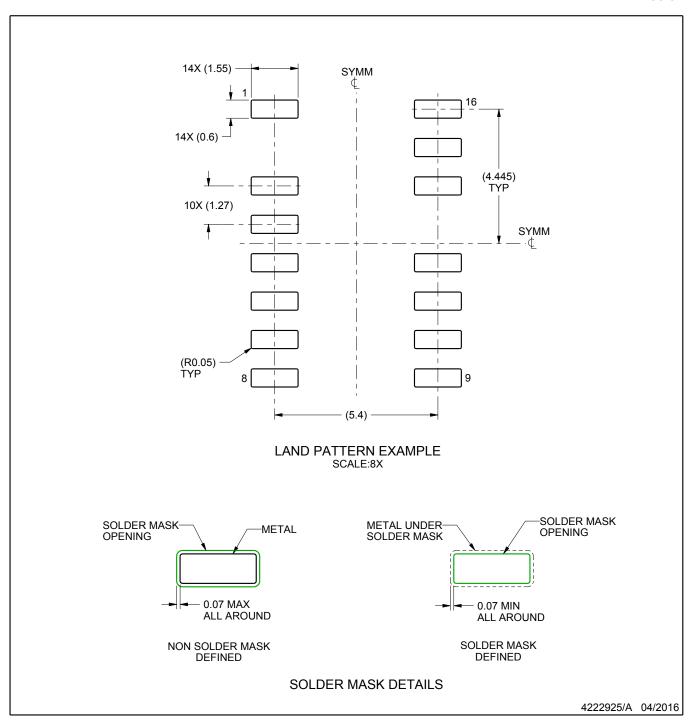

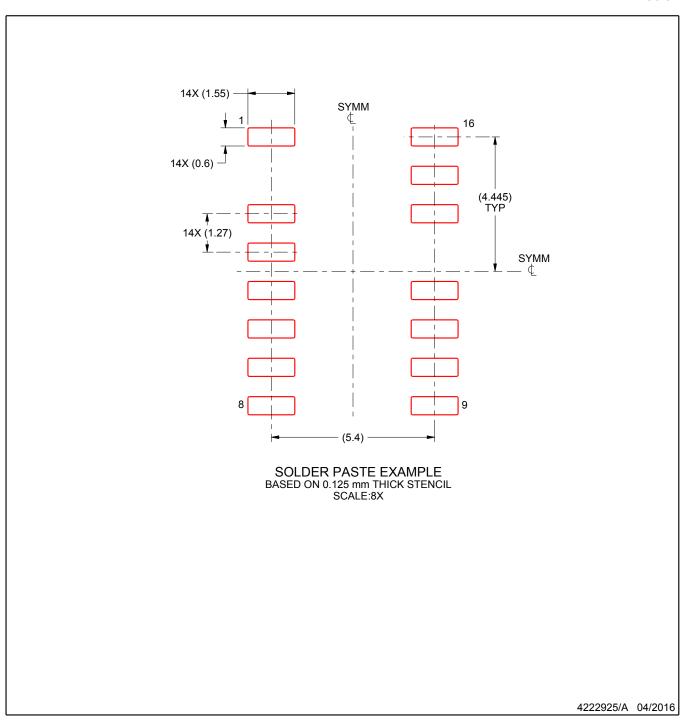

- SOIC-14 package with removed pins for highvoltage clearance

# 2 Applications

- SMPS power supply for TV

- Industrial AC/DC adapters

- Power tools

- Medical power supply

- Multifunctional printer

- Enterprise and cinema projector

- PC power supply

- Gaming console power supply

- Lighting

# 3 Description

The UCC25661 is a high-frequency LLC controller implementing input-power proportional control (IPPC) scheme, along with enhanced light-load management and multiple protection features.

IPPC widens the control range of the LLC converter and simplifies the design of wide input or outputvoltage range applications such as LED drivers, battery chargers. IPPC even work without a PFC for non-universal input applications.

The UCC25661 has enhanced light-load management that improves the efficiency while minimizing audible noise. To minimize standby power, the UCC25661 directly disables the PFC controller when operating in burst mode.

The automatic capacitive region avoidance scheme along with the adaptive soft start with reverse recovery avoidance scheme verifies that the device can never work in a mode where there is a potential to damage the FETs. The automatic capacitive region avoidance scheme makes the controller appropriate for working with a prebiased load.

The UCC25661 comes with robust protection to help you design a reliable power supply. The UCC25661 has options supporting high-voltage start-up, and OVP response. See details in Device Comparison table.

**Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| UCC25661    | DDB (SOIC, 16)         | 9.9mm × 3.9mm               |

- For all available packages, see Section 11.

- The package size (length × width) is a nominal value and includes pins, where applicable.

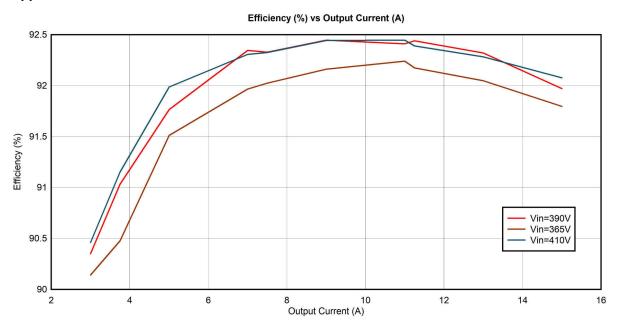

**Typical Efficiency Curve**

# **Table of Contents**

| 1 Features1                           | 7.4 Protections27                                     |

|---------------------------------------|-------------------------------------------------------|

| 2 Applications1                       | 7.5 Device Functional Modes30                         |

| 3 Description1                        | 8 Application and Implementation36                    |

| 4 Device Comparison Table4            | 8.1 Application Information                           |

| 5 Pin Configuration and Functions5    | 8.2 Typical Application36                             |

| 6 Specifications7                     | 8.3 Power Supply Recommendations49                    |

| 6.1 Absolute Maximum Ratings7         | 8.4 Layout49                                          |

| 6.2 ESD Ratings7                      | 9 Device and Documentation Support53                  |

| 6.3 Recommended Operating Conditions8 | 9.1 Receiving Notification of Documentation Updates53 |

| 6.4 Thermal Information8              | 9.2 Support Resources53                               |

| 6.5 Electrical Characteristics8       | 9.3 Trademarks53                                      |

| 6.6 Switching Characteristics11       | 9.4 Electrostatic Discharge Caution53                 |

| 6.7 Typical Characteristics12         | 9.5 Glossary53                                        |

| 7 Detailed Description16              | 10 Revision History53                                 |

| 7.1 Overview16                        | 11 Mechanical, Packaging, and Orderable               |

| 7.2 Functional Block Diagram18        | Information55                                         |

| 7.3 Feature Description19             |                                                       |

# **4 Device Comparison Table**

| Orderable Part Number            | UCC25661           |

|----------------------------------|--------------------|

| IPPC                             | •                  |

| Integrated high voltage startup  | •                  |

| Integrated X-capacitor discharge |                    |

| Extended gain range (EGR)        |                    |

| Output - voltage (OVP) latch     | •                  |

| Output - current (OCP) latch     | •                  |

| Soft on/off burst mode           |                    |

| OCP/OLP decoupling               | •                  |

| PFC on/off during LF Burst       |                    |

| ZCS fault                        | •                  |

| BLK OVP enable                   | •                  |

| LF burst frequency               | 1.6kHz -<br>3.2kHz |

# **5 Pin Configuration and Functions**

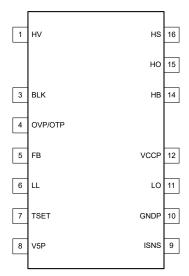

Figure 5-1. DDB Package, 16-Pin SOIC; Pins 2 and 13 Removed (Top View)

**Table 5-1. Pin Functions**

| F       | PIN I/O |       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|---------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO.     | - I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| HV      | 1       | I     | High-voltage (HV) start-up and X-capacitor discharge.  The HV pin is used to perform HV start-up. After start-up is completed, the HV pin is used for AC presence detection and X-capacitor discharge. This pin is connected to the rectified AC line or input bulk capacitor.                                                                                              |  |  |

|         | 2       | _     | Missing. HV spacer for creepage between high voltage and low voltage pins                                                                                                                                                                                                                                                                                                   |  |  |

| BLK     | 3       | I     | Bulk DC voltage sensing and input for feedforward control.  Connect BLK through a resistor divider between positive terminal of bulk capacitor and GNDP to set the LLC converter start and stop voltage thresholds. See Section 7.3.5.1 for more details.                                                                                                                   |  |  |

| OVP/OTP | 4       | 1     | Overvoltage protection and external over-temperature protection input.  Connect OVP/OTP to GNDP through an NTC resistor and to VCCP through zener diode.  See Section 7.3.5.3 for more details.                                                                                                                                                                             |  |  |

| FB      | 5       | I     | Feedback control input.  Connect FB to the collector pin of an optocoupler in the isolated feedback network. See Section 7.3.3 for more details.                                                                                                                                                                                                                            |  |  |

| LL      | 6       | ı     | Light load operation and burst mode threshold setting input.  Connect LL to the center node of resistor divider between V5P an GNDP. The impedance and voltage at LL pin is used to select the thresholds for high frequency and low frequency burst mode operation. See Section 7.5.3 for more details.                                                                    |  |  |

| TSET    | 7       | I/O   | VCR synthesizer time constants setting input and PFC on/off output.  TSET is used to set the minimum VCR time constants and the minimum switching frequency in IPPC mode by using a resistor divider as defined in Section 8.2.2.18. TSET also dual functions at the PFC disable pin and as an input to enforce low-frequency burst mode. See Section 8.2.2.18 for details. |  |  |

| V5P     | 8       | Р     | 5V Internal Regulator Output.  Connect a decoupling capacitor (recommend 1uF to 4.7uF) from V5P to GNDP. Place this capacitor close to the V5P. Chose the dielectric based on application need.                                                                                                                                                                             |  |  |

# **Table 5-1. Pin Functions (continued)**

| P    | PIN | 1/0 | Properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ISNS | 9   | I   | Resonant Circuit Current Sense Input. Connect ISNS pin to resonant capacitor through a series differentiator capacitor and a current sense resistor to GNDP. This pin senses the differentiated resonant capacitor voltage. This signal is internally used to:  Generate the control signal  OCP and cycle-by-cycle current limiting  Capacitive region avoidance  See Section 8.2.2.17 for more details.                                                                                          |

| GNDP | 10  | Р   | Ground reference pin. Connect GNDP to primary-side bulk capacitor negative terminal.                                                                                                                                                                                                                                                                                                                                                                                                               |

| LO   | 11  | 0   | Low-side switch gate driver output. Connect to low-side switch gate terminal with a minimal gate drive circuit loop area.                                                                                                                                                                                                                                                                                                                                                                          |

| VCCP | 12  | Р   | IC supply voltage pin.  Connect a low-ESR ceramic 2.2µF decoupling capacitor between VCCP and GNDP. A parallel combination of energy storage electrolytic and filter capacitors are typically used in addition.  For applications including an auxiliary bias winding on the LLC transformer, the VCCP pin is connected through a diode to the bias winding. For applications where HV start-up is disabled, VCCP is supplied by an auxiliary bias supply.  VCCP pin is internally clamped to 19V. |

|      | 13  | N/A | Missing pin. High-voltage spacer for creepage between high-voltage and low-voltage pins.                                                                                                                                                                                                                                                                                                                                                                                                           |

| НВ   | 14  | Р   | High-side gate driver bias input. Connect a capacitor (minimum of 0.1μF, maximum of 5μF) between HB and HS pins. See Section 8.3.2 for more details.                                                                                                                                                                                                                                                                                                                                               |

| НО   | 15  | 0   | High-side switch gate driver output. Connect to high-side switch gate terminal with a minimal gate drive circuit loop area.                                                                                                                                                                                                                                                                                                                                                                        |

| HS   | 16  | Р   | High-side gate driver return path and switching node connection input. Connect to the switching node of the half-bridge structure of the LLC converter. The voltage at this pin used to determine the adaptive dead time. See Section 7.3.4 for more details.                                                                                                                                                                                                                                      |

Please refer to section Section 8.2 for more details.

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

Over operating free-air temperature range (unless otherwise noted), all voltages are with respect to GND, currents are positive into and negative out of the specified terminal. (1)

|                                                   |                            | MIN      | MAX        | UNIT |

|---------------------------------------------------|----------------------------|----------|------------|------|

|                                                   | HV, HB                     | -0.3     | 700        | V    |

|                                                   | ISNS                       | -6.5     | 6.5        | V    |

| Innut valtage                                     | BLK, LL, TSET              | -0.55    | 5.5        | V    |

| Input voltage                                     | HB - HS                    | -0.3     | 25         | V    |

| 5V HO output voltage                              | VCCP                       | -0.55    | 30         | V    |

|                                                   | OVP/OTP                    | -0.55    | 5.5        | V    |

| 5V                                                | DC                         | -0.55    | 5.5        | V    |

| LIO quitaut valtaga                               | DC                         | HS - 0.3 | HB + 0.3   | V    |

| HO output voltage                                 | Transient, less than 100ns | HS – 2   | HB + 0.3   | V    |

| LO output voltage                                 | DC                         | -0.3     | VCCP+ 0.3  | V    |

|                                                   | Transient, less than 100ns | -2       | VCCP + 0.3 | V    |

| Floating ground slew rate                         | dV <sub>HS</sub> /dt       | -200     | 200        | V/ns |

| HO, LO pulsed current                             | lout_pulsed                | -0.6     | 1.2        | А    |

| Junction temperature range                        | T <sub>J</sub>             | -40      | 150        |      |

| Storage<br>temperature<br>range, T <sub>stg</sub> | T <sub>stg</sub>           | -65      | 150        | °C   |

| Load tomporature                                  | Soldering, 10 second       |          | 300        |      |

| Lead temperature                                  | Reflow                     |          | 260        |      |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                         |                                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, HV, HO, HS, HB<br>pins <sup>(1)</sup> | ±1000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all other pins <sup>(1)</sup>         | ±2000 | V    |

|                    |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup>      | ±500  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

All voltages are with respect to GND, -40 $^{\circ}$ C < T<sub>J</sub> = T<sub>A</sub> < 125 $^{\circ}$ C, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                      |                                        | MIN | NOM | MAX  | UNIT |

|----------------------|----------------------------------------|-----|-----|------|------|

| HV, HS               | Input voltage                          |     |     | 640  | V    |

| V <sub>VCCP</sub>    | Supply voltage                         |     | 15  | 18.5 | V    |

| HB - HS              | Driver bootstrap voltage               | 10  | 14  | 17.5 | V    |

| Св                   | Ceramic bypass capacitor from HB to HS | 0.1 |     | 5    | μF   |

| C <sub>VCCP</sub>    | VCCP pin decoupling capacitor          | 33  |     | 470  | μF   |

| I <sub>VCCPMAX</sub> | Maximum input current of VCCP          |     |     | 100  | mA   |

| T <sub>A</sub>       | Operating ambient temperature          | -40 |     | 125  | °C   |

#### **6.4 Thermal Information**

|                       |                                              | UCC25661 |      |

|-----------------------|----------------------------------------------|----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | D (SOIC) | UNIT |

|                       |                                              | 14 PINS  |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 74.7     | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.7     | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 31.8     | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 4.4      | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 31.4     | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

# 6.5 Electrical Characteristics

All voltages are with respect to GND, -40°C <  $T_J$  < 125°C, VCC = 15V, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                            | PARAMETER                                                                    | TEST CONDITIONS | MIN  | TYP  | MAX  | UNIT |

|----------------------------|------------------------------------------------------------------------------|-----------------|------|------|------|------|

| SUPPLY VOL                 | TAGE                                                                         |                 |      |      |      |      |

| VCC <sub>Short</sub>       | Below this threshold, use reduced start up current                           |                 | 0.6  | 1    | 1.4  | V    |

| VCC <sub>ReStartJfet</sub> | Below this threshold, re-enable JFET.                                        |                 |      | 10.2 |      | V    |

| VCC <sub>ReStart</sub>     | HV start-up is re-enabled when VCC is below this level during start-up phase |                 | 12.5 | 13   | 13.5 | V    |

| VCC <sub>StartSelf</sub>   | Startup when VCC is above this level                                         |                 | 13.5 | 14   | 14.5 | V    |

| VCC <sub>StartExt</sub>    | Startup when VCC is above this level                                         |                 | 10.5 | 10.9 | 11.3 | V    |

| VCC <sub>StopSwitchi</sub> | Switching Stopped below this threshold                                       |                 | 9    | 9.5  |      | V    |

| VCC <sub>UVLOr</sub>       | VCC under voltage lockout voltage (rising)                                   |                 | 7.25 | 7.5  | 7.82 | V    |

| VCC <sub>UVLOf</sub>       | VCC under voltage lockout voltage hysteresis                                 |                 | 6.5  | 6.8  | 7.1  | V    |

| VCC <sub>Hold_r</sub>      | Jfet stop voltage during startup programming phase                           |                 | 7.9  | 8.2  | 8.5  | V    |

| VCC <sub>Hold_f</sub>      | Jfet start voltage during startup programming phase                          |                 | 7.65 | 7.9  | 8.15 | V    |

| VCC <sub>Shunt</sub>       | VCC internal clamp voltage                                                   |                 |      | 19   |      | V    |

| IVCC <sub>Clamp</sub>      | VCC internal clamp current                                                   |                 |      | 15   |      | mA   |

# **6.5 Electrical Characteristics (continued)**

All voltages are with respect to GND, -40 $^{\circ}$ C < T<sub>J</sub> < 125 $^{\circ}$ C, VCC = 15V, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                            | PARAMETER                                                                                              | TEST CONDITIONS                              | MIN  | TYP  | MAX                                   | UNIT |

|----------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------|------|------|---------------------------------------|------|

| VCC_OV                     | VCC OVP threshold                                                                                      |                                              |      | 20.5 |                                       | V    |

| SUPPLY CUR                 | RENT                                                                                                   |                                              |      |      |                                       |      |

| CCSleep                    | Current drawn from VCC rail during burst off period                                                    |                                              |      | 800  |                                       | μA   |

| CCRun                      | Current drawn from VCC Pin while gate is switching. Excluding Gate Current                             | Dead time = 1µs maximum dead time            |      | 8    |                                       | mA   |

| CCLatchFault               | Current drawn from VCC pin in latched fault state <sup>(1)</sup>                                       |                                              |      |      | 1                                     | mA   |

| REGULATED                  | SUPPLY                                                                                                 |                                              |      |      | 1                                     |      |

| /FD                        | Regulated supply voltage (1)                                                                           | No load                                      | 4.75 | 5    | 5.25                                  | V    |

| V5P                        | Regulated supply voltage                                                                               | 10mA load                                    | 4.75 | 5    | 5.25                                  | V    |

| √5P <sub>UVLO</sub>        | V5P under voltage lock out voltage <sup>(1)</sup>                                                      |                                              |      | 4    |                                       | V    |

| V5PStartupCurrL            | Max current that can be drawn on the pin when VCCP< VCC <sub>StartSelf</sub> (1)                       | VCCP = 15V                                   |      | 6    |                                       | mA   |

| V5PCurrLimit               | V5P at IV5P = 15mA                                                                                     | VCCP = 15V                                   | 10.2 |      |                                       | mA   |

| HIGH VOLTA                 | GE STARTUP                                                                                             |                                              |      |      |                                       |      |

| VCC_Charge_Lo              | Reduced VCCP charge current from HV Pin                                                                | V <sub>HV</sub> = 20V, VCC = 0V,             | 0.23 | 0.44 | 0.65                                  | mA   |

| I <sub>VCC_Charge_Hi</sub> | Full VCCP charge current                                                                               | V <sub>HV</sub> = 20V, VCC = 4V,             | 7.5  | 10   | 13.8                                  | mA   |

| BULK VOLTA                 | GE SENSE                                                                                               |                                              |      |      | · · · · · · · · · · · · · · · · · · · |      |

| V <sub>BLKStartHys</sub>   | BLK voltage comparator hysteresis <sup>(1)</sup>                                                       |                                              | 0.09 | 0.1  | 0.11                                  | V    |

| $V_{BLKStop}$              | BLK voltage that forces LLC operation to stop                                                          |                                              | 0.98 | 1    | 1.02                                  | V    |

| BLKHys                     | BLK hysteresis current (Bulk Brown Out Isink)                                                          |                                              |      | 5    |                                       | μΑ   |

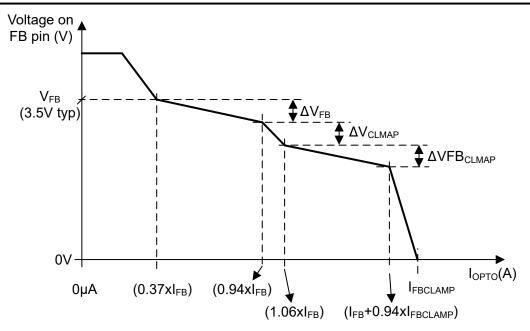

| FEEDBACK P                 | PIN                                                                                                    |                                              |      |      |                                       |      |

| R <sub>FBInternal</sub>    | Internal pull down resistor value                                                                      |                                              | 42.5 | 50   | 57.5                                  | kΩ   |

| FВ                         | FB internal current source                                                                             |                                              | 136  | 160  | 184                                   | μA   |

| $V_{FB}$                   | FB pin voltage when FB pin sink current is at (I <sub>FB</sub> - 50μA)                                 | lopto = 0.37 × IFB                           | 3.3  | 3.5  | 3.7                                   | V    |

| $\Delta V_{FB}$            | FB pin voltage variation when FB pin sink current ranges from (lopto = 0.37*IFB to lopto = 0.94*IFB)   |                                              |      |      | 0.6                                   | V    |

| $\Delta V_{clamp}$         | FB pin voltage variation when FB pin sink current ranges from (lopto = 0.94*IFB) to (lopto = 1.06*IFB) | (lopto = 0.94 × IFB) to (lopto = 1.06 × IFB) | 0.3  |      |                                       | V    |

| FBclamp                    | Maximum FB internal current source when FB is clamped                                                  |                                              | 150  | 175  | 200                                   | μΑ   |

| f <sub>-3dB</sub>          | Feedback chain -3dB cut off frequency (2)                                                              | VFBReplica from 4.5V to 0.5V                 | 1    |      |                                       | MHz  |

| $V_{FBOLP}$                | OLP protection <sup>(1)</sup>                                                                          |                                              |      | 4.75 |                                       | V    |

| TOLP <sub>Fault</sub>      | OLP protection time (1)                                                                                |                                              |      | 100  |                                       | ms   |

| RESONANT C                 | CURRENT SENSE                                                                                          |                                              |      |      |                                       |      |

| V <sub>ISNS_OCP</sub>      | OCP threshold during steady state                                                                      |                                              | 3.4  | 3.5  | 3.6                                   | V    |

| V <sub>ISNS_OCPn</sub>     | OCP negative threshold during steady state                                                             |                                              | -3.6 | -3.5 | -3.4                                  | V    |

# **6.5 Electrical Characteristics (continued)**

All voltages are with respect to GND, -40 $^{\circ}$ C < T<sub>J</sub> < 125 $^{\circ}$ C, VCC = 15V, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                                      | PARAMETER                                                                    | TEST CONDITIONS                          | MIN  | TYP   | MAX  | UNIT |

|--------------------------------------|------------------------------------------------------------------------------|------------------------------------------|------|-------|------|------|

| V <sub>ISNS_OCP_SS</sub>             | OCP threshold during soft start                                              |                                          | 2.9  | 3     | 3.1  | V    |

|                                      | OCP negative threshold during soft start                                     |                                          | -3.1 | -3    | -2.9 | V    |

| n <sub>OCP</sub>                     | Number of OCP cycles before OCP fault is tripped <sup>(1)</sup>              |                                          |      | 7     |      |      |

| n <sub>OCP_SS</sub>                  | Number of OCP cycles before OCP fault is tripped at start-up <sup>(2)</sup>  |                                          |      | 50    |      |      |

| V <sub>IpolarityHyst</sub>           | ISNS Polarity comparator hystereses                                          |                                          |      | 40    |      | mV   |

| V <sub>ISNS_ZCS</sub>                | ZCS comparator +Ve threshold after soft start                                |                                          |      | 150   |      | mV   |

| V <sub>ISNS_ZCSn</sub>               | ZCS comparator -Ve threshold, after soft start                               |                                          |      | -150  |      | mV   |

| V <sub>ISNS_MINCUR</sub><br>R_SS     | +Ve ISNS threshold during Soft Start                                         |                                          |      | 50    |      | mV   |

| V <sub>ISNS_MINCUR</sub><br>R_SSn    | -Ve ISNS threshold during Soft Start                                         |                                          |      | -50   |      | mV   |

| t <sub>leb</sub>                     | Leading edge blanking for ZCS and OCP comparators <sup>(1)</sup>             |                                          |      | 298   |      | ns   |

| TZCS <sub>Fault</sub>                | Fault detected when ZCS event persists for the indicated time <sup>(2)</sup> | ZCS Event persists                       |      | 10    |      | ms   |

| GATE DRIVER                          | ₹                                                                            |                                          |      |       |      |      |

| $V_{LOL}$                            | LO output low voltage                                                        | I <sub>sink</sub> = 20mA                 |      |       | 0.12 | V    |

| V <sub>RVCC</sub> - V <sub>LOH</sub> | LO output high voltage                                                       | I <sub>source</sub> = 20mA               |      |       | 0.3  | V    |

| V <sub>HOL</sub> - V <sub>HS</sub>   | HO output low voltage                                                        | I <sub>sink</sub> = 20mA                 |      |       | 0.12 | V    |

| V <sub>HB</sub> - V <sub>HOH</sub>   | HO output high voltage                                                       | I <sub>source</sub> = 20mA               |      |       | 0.35 | V    |

| V <sub>HB-</sub><br>HSUVLOFall       | High side gate driver UVLO falling threshold                                 |                                          | 6.4  | 7.25  | 8    | V    |

| V <sub>HB-</sub><br>HSUVLOHys        | High side gate driver UVLO threshold hysteresis                              |                                          | 0.78 | 0.9   | 1.05 | V    |

| I <sub>source_pk_HO</sub>            | HO peak source current (2)                                                   | At VCCP = 12V                            |      | -0.6  |      | Α    |

| source_pk_LO                         | LO peak source current (2)                                                   | At VCCP = 12V                            |      | -0.6  |      | Α    |

| sink_pk_HO                           | HO peak sink current <sup>(2)</sup>                                          | At VCCP = 12V                            |      | 1.2   |      | Α    |

| sink_pk_LO                           | LO peak sink current <sup>(2)</sup>                                          | At VCCP = 12V                            |      | 1.2   |      | Α    |

| BOOTSTRAP                            |                                                                              |                                          |      |       |      |      |

| BOOT_QUIESC                          | (HB - HS) quiescent current                                                  | HB - HS = 12V                            |      | 60    | 70   | μΑ   |

| BOOT_LEAK                            | HB to GND leakage current                                                    | V <sub>HB</sub> = 600V                   |      | 0.045 | 20   | μA   |

| ChargeBoot                           | Length of charge boot state <sup>(1)</sup>                                   |                                          | 230  | 265   | 300  | μs   |

| SSRamp                               | Soft Start Ramp time <sup>(1)</sup>                                          |                                          |      | 25    |      | ms   |

| OVP/OTP                              |                                                                              | 1                                        | 1    |       |      |      |

| /clamp_otp1                          | Clamp Voltage at 0mA <sup>(1)</sup>                                          | At 0mA current flowing through the clamp | 1.35 | 1.5   | 1.65 | V    |

| Vclamp_otp2                          | Clamp Voltage at 1mA <sup>(1)</sup>                                          | At 1mA current flowing through the clamp | 2.9  | 3.5   | 4.1  | V    |

| ОТР                                  | Current source on the BW/OTP pin                                             |                                          |      | 100   |      | uA   |

| V <sub>OVPpos</sub>                  | Output voltage OVP - threshold rising                                        |                                          |      | 3.5   |      | V    |

Product Folder Links: UCC25661

Submit Document Feedback

# 6.5 Electrical Characteristics (continued)

All voltages are with respect to GND, -40°C <  $T_J$  < 125°C, VCC = 15V, currents are positive into and negative out of the specified terminal, unless otherwise noted.

| PARAMETER                 |                                                                                        | TEST CONDITIONS    | MIN | TYP | MAX | UNIT |

|---------------------------|----------------------------------------------------------------------------------------|--------------------|-----|-----|-----|------|

| VOTP <sub>Neg</sub>       | OTP - threshold falling                                                                |                    |     | 0.8 |     | V    |

| OTP <sub>CompHys</sub>    | OTP comparator hysteresis                                                              |                    | 60  | 90  | 130 | mV   |

| OVP <sub>CompHys</sub>    | OVP comparator hysteresis                                                              |                    | 60  | 100 | 145 | mV   |

| OTPBlanking startup       | OTP blanking time at startup                                                           |                    |     | 50  |     | ms   |

| TOTP <sub>Fault</sub>     | OTP fault detection time                                                               |                    |     | 330 |     | us   |

| TOVP <sub>Fault</sub>     | OVP fault detection time <sup>(2)</sup>                                                |                    |     | 40  |     | us   |

| TSET                      | TSET                                                                                   |                    |     |     |     |      |

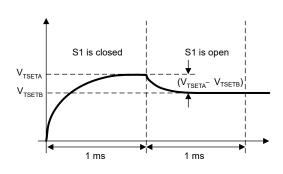

| I <sub>TSETPrgm</sub>     | TSET pin sourcing current for programming                                              |                    |     | 10  |     | uA   |

| Ш                         |                                                                                        |                    |     |     |     |      |

| I <sub>LLPrgm</sub>       | LL pin sourcing current for Burst mode transition threshold programming <sup>(2)</sup> |                    |     | 10  |     | uA   |

| t <sub>LLPrgm</sub>       | Burst mode transition threshold programming time <sup>(2)</sup>                        |                    |     | 2   |     | ms   |

| ADAPTIVE DEADTIME         |                                                                                        |                    |     |     |     |      |

| dV <sub>HS</sub> /dt      | Detectable slew rate (falling slope) (2)                                               |                    | 0.1 |     | 200 | V/ns |

| FAULT RECOVERY            |                                                                                        |                    |     |     |     |      |

| t <sub>PauseTimeOut</sub> | Paused timer (1)                                                                       |                    |     | 1   |     | S    |

| THERMAL SHUTDOWN          |                                                                                        |                    |     |     |     |      |

| $T_{J\_r}$                | Thermal shutdown temperature <sup>(1)</sup>                                            | Temperature rising | 125 | 150 |     | °C   |

| T <sub>J_H</sub>          | Thermal shutdown hysteresis (1)                                                        |                    |     | 20  |     | °C   |

<sup>1)</sup> Not tested in production. Verified by characterization

# **6.6 Switching Characteristics**

All voltages are with respect to GND, -40°C<  $T_J$  = $T_A$  < 125°C, VCC =15V, currents are positive into and negative out of the specified terminal, unless otherwise noted.

|                          | PARAMETER                                                             | TEST CONDITIONS               | MIN | TYP  | MAX | UNIT |

|--------------------------|-----------------------------------------------------------------------|-------------------------------|-----|------|-----|------|

| t <sub>r(LO)</sub>       | Rise time                                                             | 10% to 90%, 1 nF load         |     | 30   | 60  | ns   |

| t <sub>f(LO)</sub>       | Fall time                                                             | 10% to 90%, 1 nF load         |     | 20   | 30  | ns   |

| t <sub>r(HO)</sub>       | Rise time                                                             | 10% to 90%, 1 nF load         |     | 30   | 60  | ns   |

| t <sub>f(HO)</sub>       | Fall time                                                             | 10% to 90%, 1 nF load         |     | 15   | 50  | ns   |

| t <sub>DT(min)</sub>     | Minimum dead time (1)                                                 |                               |     | 60   |     | ns   |

| t <sub>DT(max)</sub>     | Maximum dead time (dead time fault)                                   | ZCS threshold is NOT detected |     | 1.2  |     | μs   |

| t <sub>DT(max_ZCS)</sub> | Maximum dead time (dead time fault)                                   | ZCS threshold is detected     |     | 1.31 |     | μs   |

| t <sub>ON(min)</sub>     | Minimum gate on time                                                  |                               |     | 300  |     | ns   |

| t <sub>ON(max)</sub>     | Maximum gate on time                                                  |                               |     | 11.9 |     | μs   |

| t <sub>Ipol(ZCS)</sub>   | Blanking time after which the IPOL signal can be used to terminate DT | ZCS threshold is detected     |     | 595  |     | ns   |

<sup>(1)</sup> Not tested in production. Ensured by design

<sup>(2)</sup> Not tested in production. Verified by design

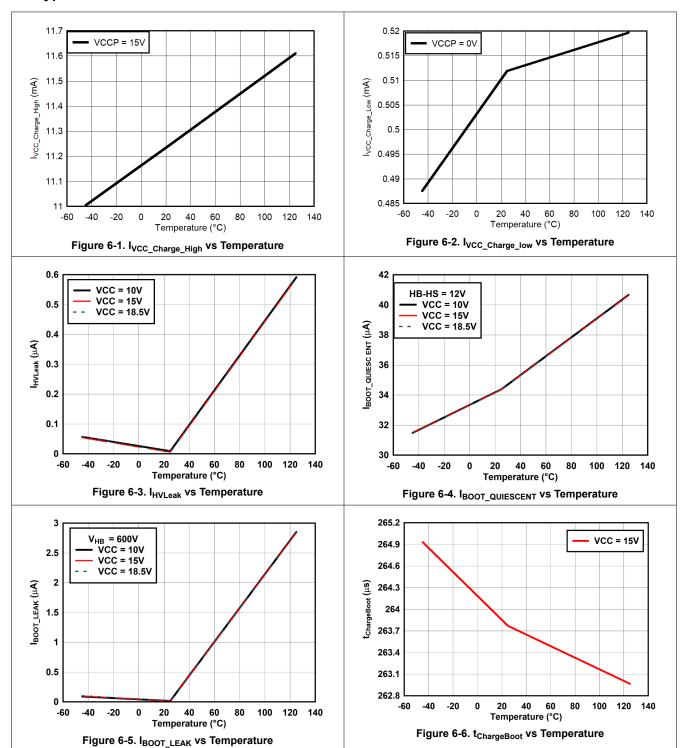

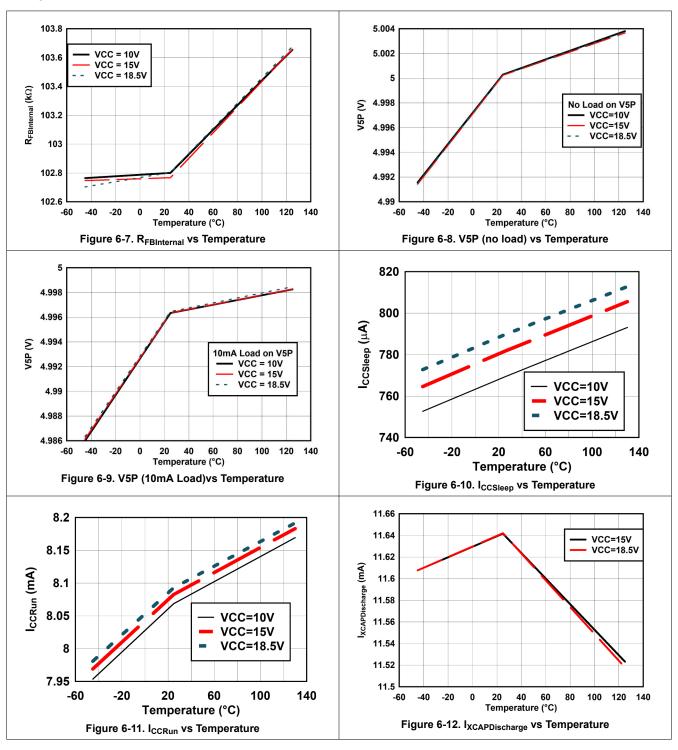

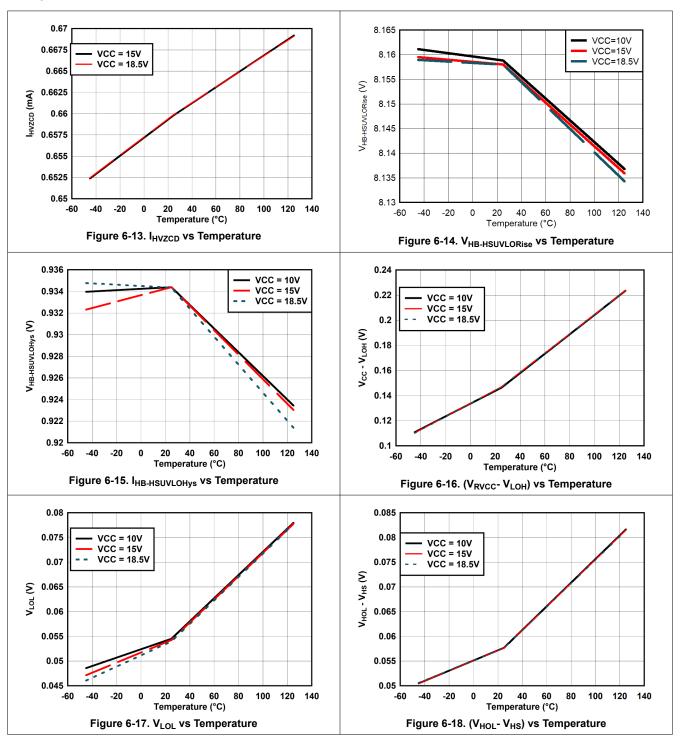

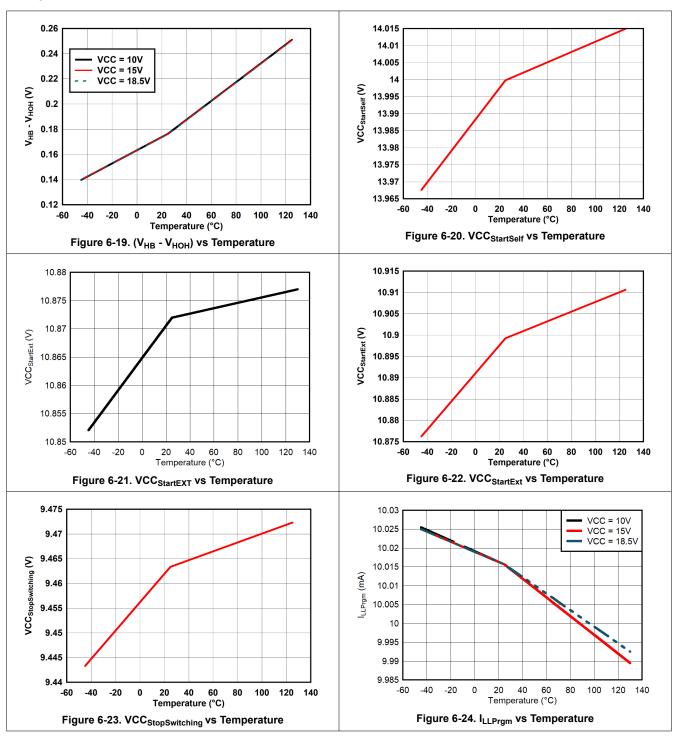

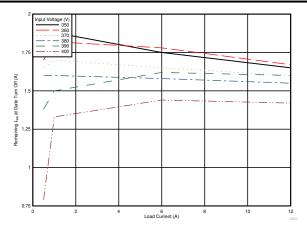

### **6.7 Typical Characteristics**

# 6.7 Typical Characteristics (continued)

## 6.7 Typical Characteristics (continued)

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# 6.7 Typical Characteristics (continued)

# 7 Detailed Description

### 7.1 Overview

The UCC25661 is a fully featured LLC resonant controller for isolated power supplies. UCC25661 incorporates high levels of integration and several design features to accommodate wide input and output voltage operation, high power density, and increased reliability of the LLC power stage.

The device novel control scheme input power proportional control (IPPC) offers excellent transient performance inherent in the current mode controls, while enabling a linear relationship between input power and control signal across wide input and output voltage variation. The IPPC control enables consistent light load, burst mode performance operation across a wide input and output voltage variation.

Some of the new features in UCC25661 are specified below:

- IPPC Control enables more stable burst mode and dynamic response under wide input/output voltage operation

- New operation modes to increase light load efficiency while reducing audible noise

- High-frequency (HF) pulse skip for improved light load efficiency

- Low-frequency (LF) burst mode for reduced stand by power consumption

- Programmable light load/burst mode thresholds to balance output ripple and efficiency

- Adaptive burst mode threshold adjustment to accommodate input voltage change

- Wide burst mode hysteresis to prevent oscillating in and out of burst mode

- Soft in and soft out of burst mode to further minimize audible noise plus option to force retention of burst mode

- Full-load switching frequency enables high power density designs: up to 750kHz

- · Combined resonant current sensing with internal control voltage generation, improves control robustness

- · Input voltage feed forward

- Integrated protections include:

- Fast cycle-by-cycle current limiting: 50ns

- OCP fault to protect under short circuit conditions

- Over Power Protection (OPP) to limit peak input power

- Zero Current Switching (ZCS) avoidance scheme to eliminate capacitive region operation

- Adaptive soft start for reduced inrush current and eliminating reverse recovery at start-up

- External OVP/OTP protection

- Input and bias supply (VCCP) UVLO

- Input voltage feed forward

- OCP/OLP decoupling allows protection thresholds sets independently

Copyright © 2025 Texas Instruments Incorporated Product Folder Links: *UCC25661*

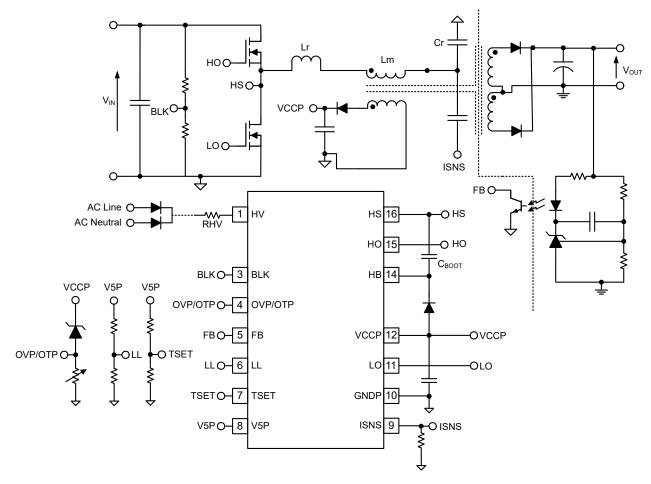

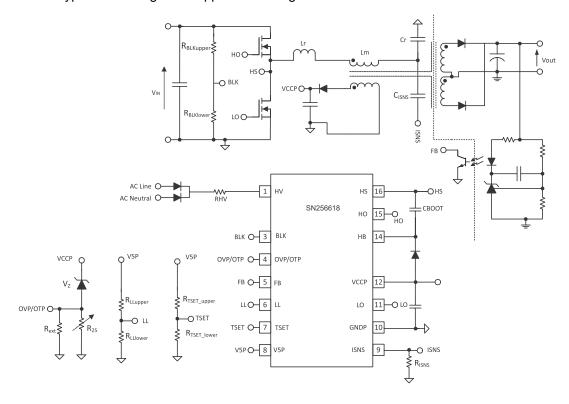

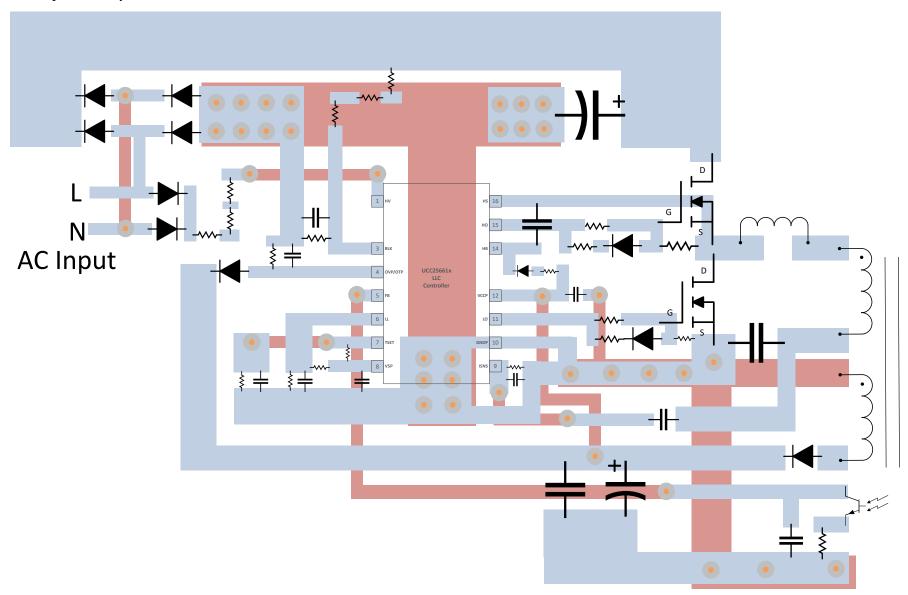

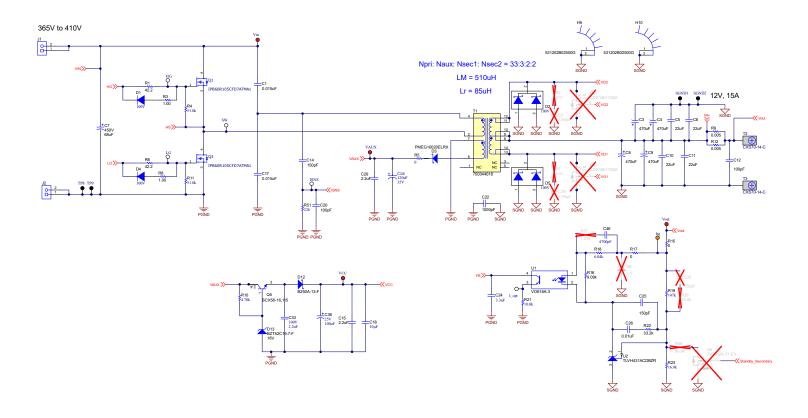

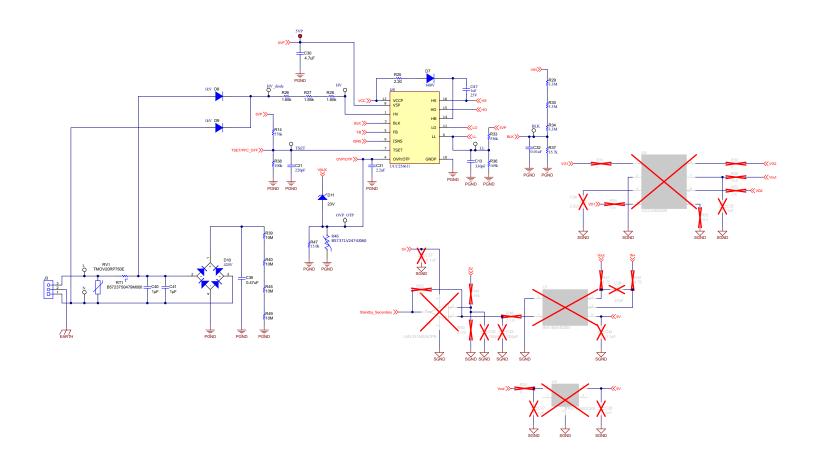

Figure 7-1. Simplified Application Schematic

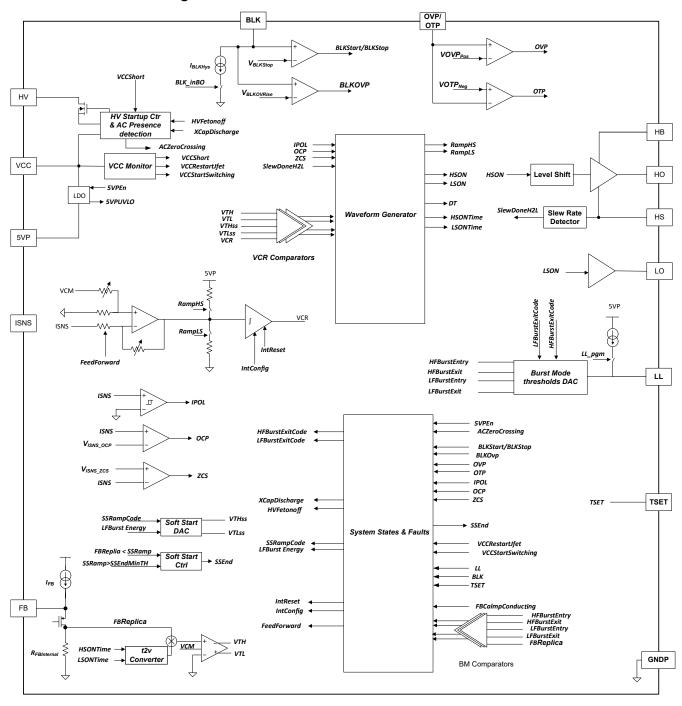

# 7.2 Functional Block Diagram

# 7.3 Feature Description

#### 7.3.1 Input Power Proportional Control

The previous generation of TI LLC controllers use a version of charge control called hybrid hysteresis control (HHC). An improved version of the HHC, called input power proportional control (IPPC), is used in the UCC25661 LLC controller. Compared to traditional direct frequency control, where the control signal is proportional to the switching frequency, traditional charge control methods deliver faster transient response while simplifying compensator design as the power stage transfer function becomes a first order system. In traditional charge control, the control signal is determined by both input current and switching frequency. IPPC significantly reduces the control signals dependency on switching frequency, thereby minimizing the impact of input and output voltage variations.

IPPC brings in the following advantages:

- Makes control signal proportional to input power.

- · Consistent burst mode and over load performance in wide LLC (WLLC) operation application.

- Retains faster load transient performance and improves line transient performance.

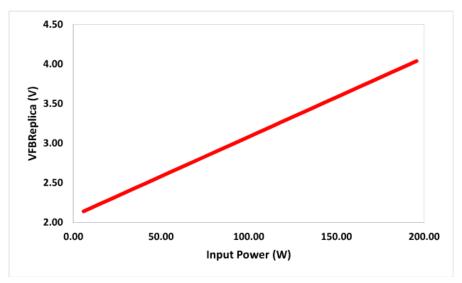

The UCC25661 measures the resonant tank current on the ISNS pin through an external differentiator formed by capacitor  $C_{ISNS}$  and resistor  $R_{ISNS}$ . The voltage on the ISNS pin is integrated in the VCR synthesizer block to form an internal VCR signal  $VCR\_synth$ . The VCR Synthesizer block applies feed forward gain based on the BLK pin voltage, applies ramp compensation to generate the compensated internal VCR signal. The compensated internal VCR signal is then compared with two sets of thresholds to control the high side switch turn-off ( $V_{TH}$ ) and low side switch turn-off ( $V_{TL}$ ). The thresholds  $V_{TH}$  and  $V_{TL}$  are generated from the internal control signal FBReplica and the high-side and low-side switch on-time from the previous half switching cycle. During the soft start, the  $V_{TH}$  and  $V_{TL}$  thresholds are generated based on the internal soft start ramp to minimize the resonant tank inrush current during start-up.

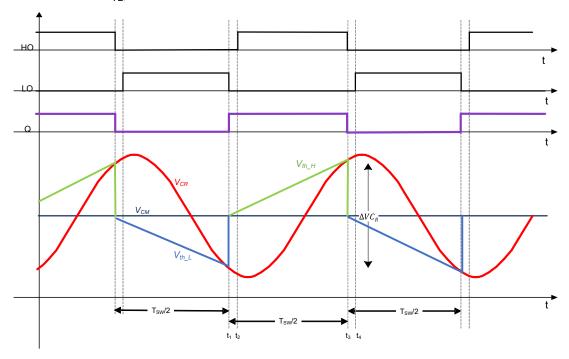

In Figure 7-2, the high-side and low-side switches are controlled based on the internal VCR signal and comparator thresholds  $V_{TH}$  and  $V_{TL}$ . When the VCR is higher than  $V_{TH}$ , the high-side switch is turned off. When VCR is lower than  $V_{TL}$ , the low-side switch is turned off.

Figure 7-2. IPPC Basic waveforms

Calculate the comparator thresholds V<sub>TH</sub> and V<sub>TL</sub> using the equations below. FBReplica is the internal voltage representation of the feedback pin (FB) current. Section 7.3.3 defines the feedback chain. T<sub>sw</sub> is the period of a switching cycle. k is a constant.

$$V_{TH} = (V_{CM} + k \times FBReplica \times Tsw \div 2)$$

(1)

$$V_{TL} = (V_{CM} - k \times FBReplica \times Tsw \div 2)$$

(2)

$$V_{TH} - V_{TL} = \Delta V_{CR} = k \times FBReplica \times Tsw$$

(3)

# 7.3.1.1 Voltage Feedforward

By implementing input voltage feed forward, the FBReplica is proportional to the input power and inversely proportional to the magnitude of the resonant tank capacitance. Rewriting the Equation 4 with input voltage feedforward applied.

$$FBReplica = \frac{2}{C_r} \times K_1 \times Pin_{avg} + K_2 \times I_{RAMP}$$

(4)

Where K<sub>1</sub> and K<sub>2</sub> are internal synthesizer gains. The input voltage to the LLC power stage is periodically sensed on the BLK pin. A periodic average of the input voltage is used to adjust the feed forward gain to make the control signal proportional to input power. More details are found in Section 7.3.2.

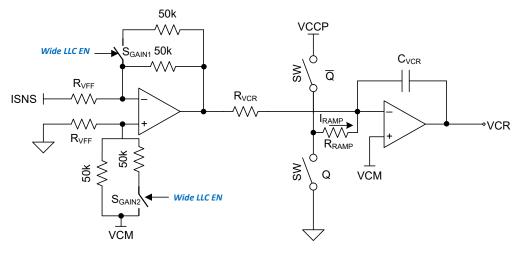

#### 7.3.2 VCR Synthesizer

The UCC25661 implements a VCR synthesizer which integrates the resonant tank current to form a internal representation of the resonant capacitor voltage. By implementing the VCR synthesizer internally, the UCC25661 provides for an ability to support very high frequency start-up with controlled inrush currents and feed forward gain stage. The internal VCR synthesizer also makes the controller less susceptible to external noise picked up on the ISNS pin, making the controller more robust.

Figure 7-3. VCR Synthesizer Block Diagram

The first stage of the VCR synthesizer consists of a programmable gain stage, used to implement the input voltage feed forward function.

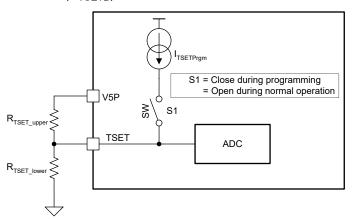

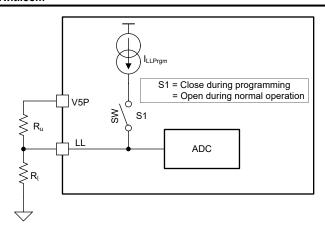

The second stage consists of a programmable integrator with ramp compensation. To accommodate a wide frequency range of LLC power stages, the time constant of the integrator is externally configurable at start-up to meet the needs of the design using the TSET pin. During start-up, TSET programming is done by an external resistor divider connected between V5P and GNDP. Connect the center node of the external divider to TSET pin. During the programming phase, a constant current  $I_{\mathsf{TSETPrgm}}$  is fed to the TSET pin and the resulting voltage

is measured through ADC ( $V_{TSETA}$ ). After  $I_{TSETPrgm}$  is turned off and the voltage of the TSET resistor divider is measured ( $V_{TSETB}$ ).

Figure 7-4. TSET Pin Programming

#### 7.3.2.1 TSET Programming

The voltage programmed for VTSETB voltage configures the minimum operating frequency for IPPC operation and the maximum dead time. The difference between VTSETA and VTSETB configures the integrator time constants that set the FBReplica magnitude for a given power output, enabling setting the overload power (OLP) and over-current protection (OCP) thresholds independently. In the table value TSET voltage values indicated are nominal values. Maximum and minimum range used for each TSET setting is within ± 48mV from nominal value.

**Table 7-1. TSET Programming Options**

| TSET OPTION NUMBER | TSET VOLTAGE (V) FOR 3.5V OCP | MINIMUM FREQUENCY<br>FOR IPPC OPERATION<br>(kHz) | INTEGRATOR TIME<br>CONSTANT (ns) | MAXIMUM DEAD-TIME (µs) |

|--------------------|-------------------------------|--------------------------------------------------|----------------------------------|------------------------|

| 17                 | 2.295                         | 698.6                                            | 68                               | 0.5                    |

| 16                 | 2.168                         | 591.6                                            | 80                               | 0.5                    |

| 15                 | 2.041                         | 501                                              | 93                               | 0.5                    |

| 14                 | 1.914                         | 424.3                                            | 112                              | 0.5                    |

| 13                 | 1.787                         | 359.3                                            | 132                              | 1                      |

| 12                 | 1.66                          | 304.3                                            | 156                              | 1                      |

| 11                 | 1.533                         | 256.7                                            | 184                              | 1                      |

| 10                 | 1.416                         | 218.2                                            | 214                              | 1                      |

| 9                  | 1.299                         | 184.8                                            | 257                              | 1                      |

| 8                  | 1.182                         | 156.5                                            | 304                              | 1                      |

| 7                  | 1.074                         | 132.5                                            | 359                              | 1                      |

| 6                  | 0.967                         | 112.2                                            | 424                              | 1                      |

| 5                  | 0.850                         | 95                                               | 490                              | 1                      |

| 4                  | 0.742                         | 80.5                                             | 588                              | 1                      |

| 3                  | 0.644                         | 68.1                                             | 694                              | 1                      |

| 2                  | 0.547                         | 57.7                                             | 820                              | 1                      |

| 1                  | 0.450                         | 48.9                                             | 968                              | 1                      |

| X <sup>(1)</sup>   | < 0.392                       | _                                                | X                                | _                      |

<sup>(1)</sup> Not recommended for use.

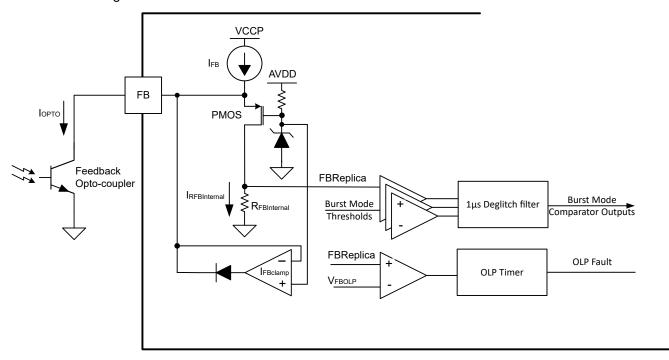

#### 7.3.3 Feedback Chain (Control Input)

Control of the output voltage is provided by a voltage regulator circuit located on the secondary side of the isolation barrier. The demand signal from the secondary-side regulator circuit is transferred across the isolation barrier using an optocoupler.

A constant current source  $I_{FB}$  is generated from VCCP voltage and connected to FB pin. A resistor RFB is also connected to the constant source current source with a PMOS in series. During normal operation, the PMOS is always on so that the FB pin voltage is equal to the Zener diode reference voltage plus the voltage drop on the PMOS source to gate.

Figure 7-5. Feedback Chain Block Diagram

$$I_{R_{FBInternal}} = I_{FB} - I_{OPTO}$$

(5)

The control signal FBReplica is depicted using Equation 6.

$$FBReplica = I_{R_{FBInternal}} \times R_{FBInternal}$$

(6)

From Equation 6, when  $I_{OPTO}$  increases,  $I_{RFBInternal}$  decreases, decreasing the FBReplica. In this way, the control signal is inverted. When  $I_{OPTO}$  continues to increase and reaches the value of  $I_{FB}$ , the FB pin voltage starts to drop because there is not enough current flow through the PMOS. FB pin pulled low impacts the system transient response, due to the extra delay introduced by charging the parasitic capacitor of the optocoupler to pull up the FB pin voltage. A FB pin voltage clamp circuit is used to prevent this scenario. When FB pin voltage drops below the FB pin clamp voltage threshold, an extra current source is turned on to clamp the FB voltage. The clamp strength is  $I_{FBClamp}$ . The FB pin clamp circuit improves the system transient performance from light load to heavy load. The FB pin clamp operation is shown in the figure below.

Figure 7-6. FB Pin Voltage versus FB Pin Current

### 7.3.4 Adaptive Dead-Time

The UCC25661 implements a high-speed, low latency, slew-rate detection block to optimize the dead time between high-side and low-side pulses. The adaptive dead-time block adjusts the dead time to prevent shoot through and excessive body diode conduction.

At the core of the adaptive dead time block is the slew rate detector block, capable of detecting slew rates up to 200V/ns, making UCC25661 an excellent choice for use in high frequency resonant converters.

In burst mode, during a ZCS prevention operation or in power stages where the slew rate can be slow, the resonant tank current polarity signal (Ipolarity comparator output) is used to augment the slew rate detector.

Taking advantage of the natural symmetric operation of LLC, only the dead time between high-side switch turn off and low-side switch turn on is determined by the slew rate detector. This dead time is copied and then applied to the dead time between low-side MOSFET turn off and high-side MOSFET turn on. There are a few exceptions where the dead time is not copied. The conditions are listed below:

- Missing slew rate detector signal in the previous High to Low transition.

- ZCS detection in the previous cycle.

Under the above-mentioned conditions, the Ipolarity comparator based on the ISNS signal is used to adjust the dead time during low to high transitions.

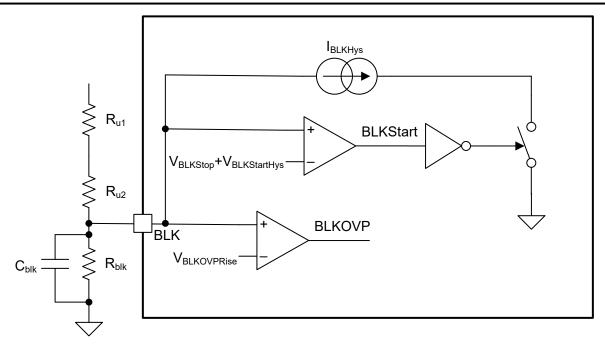

#### 7.3.5 Input Voltage Sensing

The input voltage sensing through BLK pin is used to implement multiple functions listed below:

- Input voltage brown-in and brown-output

- Input feedforward (explained in Section 7.3.1)

- Input voltage OVP

#### 7.3.5.1 Brownin and Brownout Thresholds and Options

UCC25661 provides programmable brownin and brownout thresholds. When the voltage on the BLK pin falls below  $V_{BLKStop}$ , the controller enters brownout state and stops switching. In the brownout state, an additional current sink is turned on to draw  $I_{BLKHys}$  form the BLK pin. Program the actual brownin voltage by changing the equivalent resistance externally connected to the pin externally.

Copyright © 2025 Texas Instruments Incorporated

Figure 7-7. BLK Pin Input Voltage Sensing Architecture

When brownout is detected, the controller stops switching. If BLK voltage rises above the brownin voltage, the controller immediately begins soft start and does not wait for fault idle time.

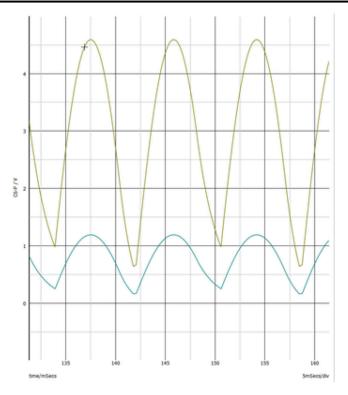

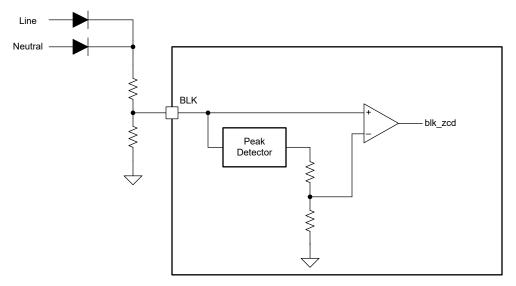

### 7.3.5.2 AC Input Zero Crossing Detection

Input zero crossing detection is only enabled when AC brownout option is selected for BLK pin sensing. With this option, the BLK pin detects the HV pin voltage through a resistor divider. The expected waveform is the divided down rectified AC voltage. Below shows an example using  $8M\Omega$  and  $100k\Omega$  for the BLK resistor divider at 70Vac input and 265Vac input.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

Figure 7-8. Input AC Zero Cross Detection using BLK pin

The method to determine AC presence uses a comparator that looks at the instantaneous BLK voltage and  $\frac{1}{2}$  of the BLK peak detector output. If the instantaneous BLK voltage falls below  $\frac{1}{2}$  the peak BLK voltage and then rises above  $\frac{1}{2}$  BLK peak voltage (with a hysteresis), AC presence is detected. Effectively, the X-capacitor discharge algorithm is looking for a rising edge on the BLK comparator output (blk\_zcd) to detect the presence of AC.

Figure 7-9. BLK ZCD Detection Block Diagram

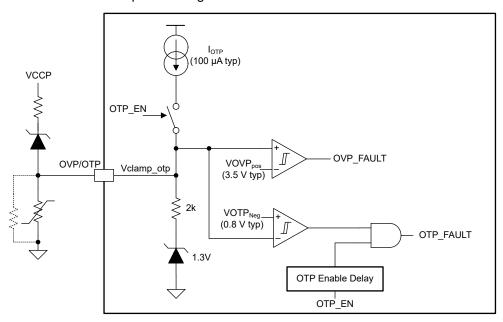

#### 7.3.5.3 Output OVP and External OTP

UCC25661 uses a multi-function pin (OVP/OTP) to monitor for output overvoltage and external over-temperature conditions. Output voltage is monitored through reflected voltage on bias winding and supply voltage VCCP.

A Zener diode is connected between VCCP and the OVP/OTP pin. Under normal operating conditions, the Zener does not conduct and the OVP/OTP pin voltage is the result of the NTC resistance and I<sub>OTP</sub> source current. If VCCP rises high enough to exceed the Zener breakdown voltage, the voltage on the OVP/OTP pin is pulled high because of the Zener current. If the voltage on OVP/OTP exceeds the VOVP<sub>pos</sub> threshold for 40us the controller detects a fault and stops switching.

Figure 7-10. OVP/OTP Protection Architecture

A NTC is connected from OVP/OTP to GNDP. An internal current source, IOTP, flows out of the OVP/OTP pin and into the NTC resistor. Based on the temperature of the NTC, the resulting voltage on the pin is compared to VOTP<sub>Neg</sub> to determine if an external over-temperature fault occurs. Upon detection of external over-temperature protection, UCC25661 moves to the fault state. After the 1s wait period, UCC25661 checks the OVP/OTP pin voltage. If the OVP/OTP pin voltage is higher than VOVP<sub>Pos</sub>, the UCC25661 attempts to restart. If restarting is not possible, the UCC25661 continues to wait in fault idle state. During burst mode, the over-temperature protection is disabled to minimize guiescent current. When transitioning from burst mode to normal switching, the OTP function is re-enabled.

#### 7.3.6 Resonant Tank Current Sensing

The ISNS pin senses the resonant tank current through a differentiator. Besides serving as over current protection pin, the ISNS pin is also an essential part of the control functions.

The ISNS pin has the following functions

- Input to the integrator that develops the control voltage, used for IPPC control

- OCP (cycle-by-cycle) protection

- Resonant current polarity detection

- ZCS prevention and dead-time management

- Reverse recovery avoidance at start-up

#### 7.4 Protections

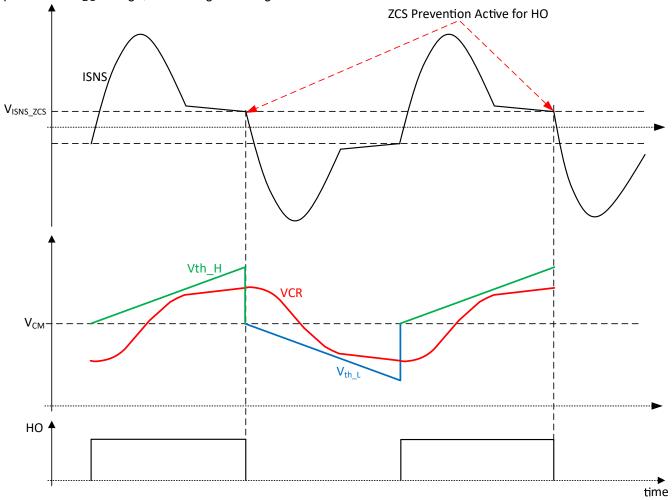

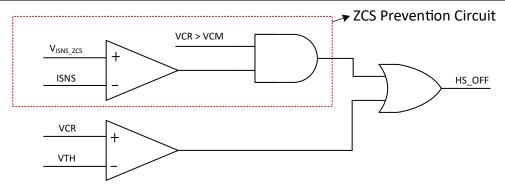

### 7.4.1 Zero Current Switching (ZCS) Protection

ZCS protection is a necessary function for LLC converters to avoid crossing over into the capacitive region of operation. In the capacitive region, the MOSFETs can be damaged due the reverse recovery of the body diode allowing both switches to briefly conduct current. In addition, the gain vs frequency relationship inverts in the capacitive region and can cause the converter to completely lose regulation of the power stage. The goal of the ZCS protection is to make sure that the MOSFET can be turned off before the current inverts thereby eliminating possibility of a hard reverse recovery of the MOSFET body diode. This can increase the reliability of the power stage. The minimum turn-off current is set at a threshold which can increase the chances of achieving ZVS or close to ZVS switching for switches under this condition. Coupled with the dead time engine which looks at both the slew done signal and the IPOL signal, we can make sure that the opposite MOSFET turns-on at the valley point of the V<sub>DS</sub> voltage, minimizing switching losses.

Figure 7-11. ZCS Protection

When operation nears the inductive/capacitive boundary, the resonant current decreases before the gate is turned off. If the ISNS waveform is less than the  $V_{ISNS\_ZCS}$  threshold, the gate pulse HO is terminated early instead of waiting for the VCR waveform to cross the VTH boundary. This early gate termination scheme is capable of leaving enough resonant current at the gate turn-off edge to drive the ZVS transition during the dead-time. Similar explanation holds good for the LO gate pulse.

Figure 7-12. ZCS Prevention Scheme When the High-Side MOSFET is On

The shape of the resonant current well below the resonant frequency poses some challenge for detecting the correct falling edge of the resonant current waveform. The UCC25661 implements additional logic to make sure that the correct falling edge of the ISNS signal is detected to avoid false tripping. To improve robustness against noise, the ISNS ZCS comparators are blanked at the rising edge of HO or LO gate. The same blanking time is used for both the VCR comparators and the ISNS ZCS comparators. When a ZCS event is detected, the internal soft start ramp voltage is slowly reduced. When the internal soft start ramps down, the switching frequency is also forced to increase, forcing the converter out of capacitive region. In the event of a persistent ZCS condition for a period of TZCSFault the UCC25661 controller ceases switching and move to the fault state.

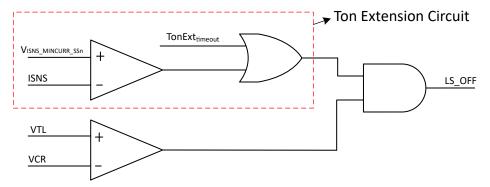

## 7.4.2 Minimum Current Turn-off During Soft Start

During start-up and for the first few switching cycles, the MOSFET on the primary side can experience body diode reverse recovery and hard switching. The experience is mainly due to the fact that at start-up the resonant capacitor can have DC bias voltage which is off from the steady state operating voltage of Vin/2. This leads to a asymmetry in the resonant tank current at start-up. In the first few cycles, asymmetry can be high enough that the current at the point of switch turn-off is in the wrong polarity.

For example, refer to Figure 7-13.

Figure 7-13. Ton Extension Scheme

Figure 7-14. ZCS Prevention During Startup

### 7.4.3 Cycle by Cycle Current Limit and Short Circuit Protection

The OCP and cycle-by-cycle current limiting feature in UCC25661 family provides a fast (<50ns) response to short circuit. The cycle-by-cycle protection helps to limit the peak stress in the power stage. When the ISNS voltage becomes greater than  $V_{ISNS\_OCP}$ , the present HO gate pulse is terminated. Correspondingly, during the second half cycle, the present LO pulse is terminated when the corresponding overcurrent limit is detected. If OCP is detected in 7 consecutive switching cycles ( $n_{OCP}$ ), the device moves to the fault state. During startup, if OCP condition is detected in 50 consecutive switching cycles ( $n_{OCP}$  SS), the device moves to fault state.

## 7.4.4 Overload (OLP) Protection

IPPC with feed forward creates a strong correlation between Pout versus the internal control signal FBReplica.

When the FBReplica goes above the  $V_{FBOLP}$  (for example,  $I_{opto}$  reduces to  $0\mu A$ ), the system starts to limit the input power and the OLP timer count increases. If the FBReplica stays above  $V_{FBOLP}$  for > ( $T_{OLP}$ ), the OLP fault is detected and the system enters into the fault restart sequence.

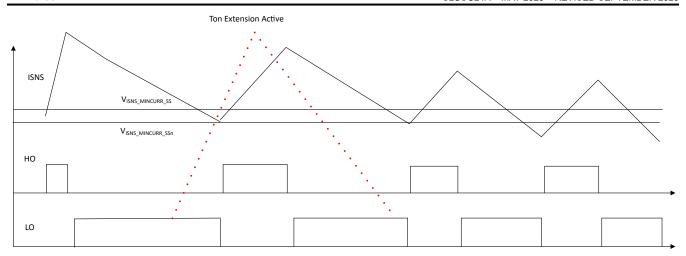

#### 7.4.5 VCC OVP Protection

An internal current limited clamp on the VCCP pin protects the VCCP pin and clamps the gate drive output voltage when the voltage applied to the VCCP pin exceeds the recommended max voltage. The clamp has maximum sink current IVCC<sub>Clamp</sub>. If the current going through the VCC<sub>Shunt</sub> exceeds IVCC<sub>Clamp</sub>, the result is the further increase in the VCCP pin voltage above VCC\_OV. If the increase, occurs UCC25661 moves to fault condition and retries after the 1s fault idle time.

Figure 7-15. VCC Clamp

#### 7.5 Device Functional Modes

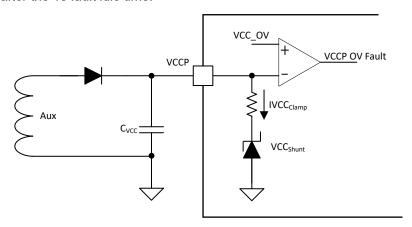

#### 7.5.1 Startup

## 7.5.1.1 With HV Start-up

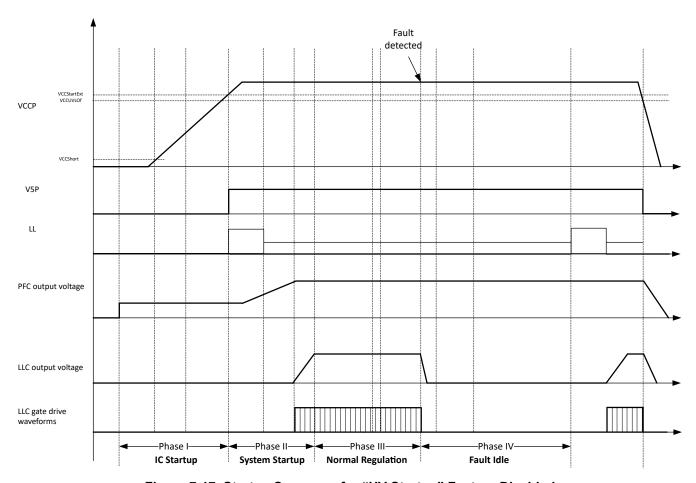

#### 7.5.1.1.1 First Time Start-up Sequence

- 1. When AC is plugged in, voltage is applied on HV pin. If VCCP voltage is below  $VCC_{Short}$ , VCCP pin is charged with  $I_{VCC\_Charge\_Low}$ . If VCCP voltage is higher than  $VCC_{Short}$ , VCCP pin is charged with  $I_{VCC\_Charge\_High}$ .

- 2. When VCCP voltage is higher than VCC<sub>UVLOr</sub>, an internal LDO regulates the V5P voltage until the device initialization is complete.

- 3. V5P is established. LL pin and TSET pin are used for burst mode and internal VCR Synthesizer programming.

- 4. If the HV start-up option is enabled, the TSET pin outputs high (means PFC OFF) to prevent PFC from turning on before VCCP is full established.

- 5. When VCCP is higher than *VCC*<sub>StartSelf</sub>, HV charge current stops. LLC start-up process begins. TSET voltage is kept lower than 1V, allowing PFC to startup.

- 6. If during stages 3 and 4, VCCP voltage drops below  $VCC_{ReStartUfet}$ , HV charge current enables again and VCCP gets charged with  $I_{VCC\_Charge\_High}$

- 7. Once LLC finishes start-up, HV charge current is disabled until VCCP drops below VCC<sub>ReStartUfet</sub>.

- 8. During normal operation if the VCCP voltage falls below *VCC*<sub>StopSwitching</sub>, a fault occurs and UCC25661 shuts down. Normal restart sequence is then followed.

Figure 7-16. Startup Sequence for HV Startup Feature Enabled

# 7.5.1.1.2 Restart Sequence

1. After a fault is detected, UCC25661 shuts down. For fault retry mode, after 1s idle time, UCC25661 retries (TSET outputs high when VCCP is still higher than  $VCC_{UVLOf}$ ).

www.ti.com

2. If VCCP voltage is below  $VCC_{Short}$ , VCCP pin is charged with  $I_{VCC\_Charge\_Low}$ . If VCCP voltage is higher than VCC<sub>Short</sub>, VCCP pin is charged with I<sub>VCC\_Charge\_High</sub>. If VCCP pin voltage is higher than VCC<sub>StartSelf</sub>, HV startup is not enabled (Phase I is skipped). V5P is established and LL pin is released for burst mode programming.

#### 7.5.1.2 Without HV Startup

When HV startup is disabled, the PFC on/off signal is disabled as well. The startup sequence is as follows:

- 1. When VCCP voltage is higher than VCC<sub>UVLOr</sub>, V5P is established

- 2. LL pin and TSET pin are used for burst mode and internal VCR integrator programming.

- 3. When VCC drops below VCC<sub>UVLOf</sub>, V5P turns off and system shuts down.

Figure 7-17. Startup Sequence for "HV Startup" Feature Disabled

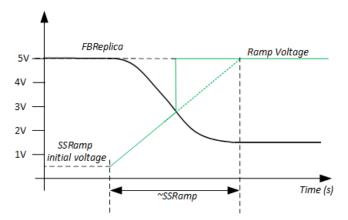

## 7.5.2 Soft Start Ramp

The soft start ramp is internally generated in the UCC25661. A fixed maximum soft start time of 25ms is internally generated to reduce inrush current at start-up, while allowing a fast output-voltage ramp up.

#### 7.5.2.1 Startup Transition to Regulation

In UCC25661, a new soft start is implemented to control the inrush current at startup. The new scheme helps avoiding any premature soft start termination and establishes smooth transition between soft start and closed loop regulation.

At start-up, internal soft start voltage (SSRamp) ramps up using a defined slope and the FBReplica is high as the output voltage is below the regulation voltage. A pick lower block identifies the two signals and uses the one that is lower of the two to control the turn-off of the power stage switches.

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

The soft start is exited only after the SSRamp is above a minimum threshold, avoiding any premature soft start exit, as shown in Figure 7-18.

Figure 7-18. Soft Start Operation

### 7.5.3 Light Load Management

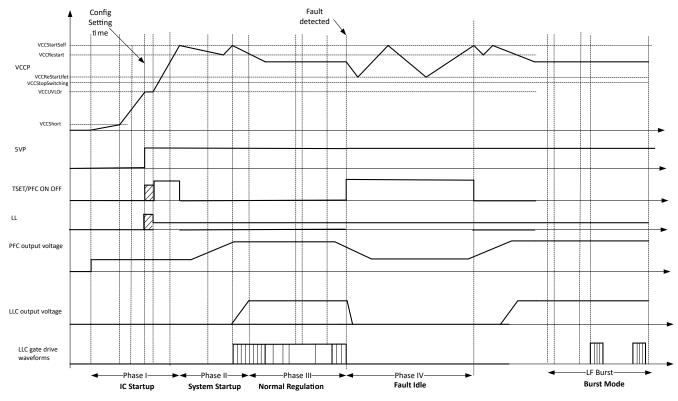

#### 7.5.3.1 Operating Modes (Burst Pattern)

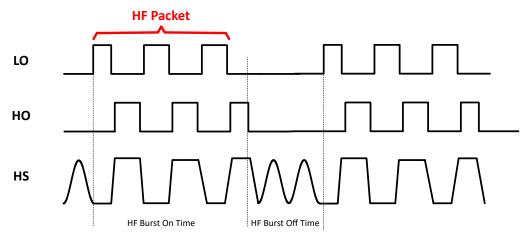

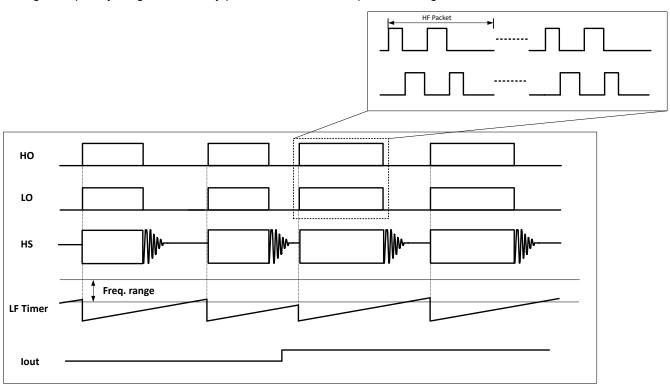

UCC25661 burst mode algorithm minimizes audible noise, while improving light load efficiency. This is accomplished by maintaining the burst packet frequency to either be above the audible range (> 25kHz) or to maintain the burst packet frequency to be at the very low end of the audible region (< 400Hz). UCC25661 employs two burst mode patterns; high-frequency (HF) pulse skip and low-frequency (LF) burst.

HF burst packet includes a fixed number of LO and HO pulses. The purpose of HF burst is to maintain the burst frequency higher than the audible frequency range. In the below image, the low-side gate is enabled on the 2nd valley of the switch node to begin delivery of the next HF burst packet.

Figure 7-19. High Frequency Pulse Skip Packet

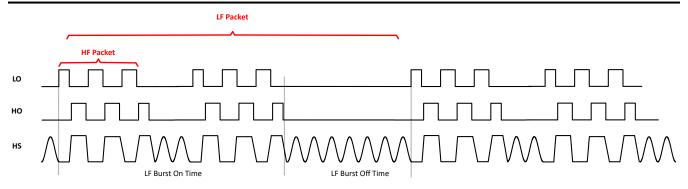

LF burst includes a number of HF burst packets and a LF burst off period.

Figure 7-20. Low Frequency Burst Packet

The number of HF burst packet is calculated to maintain the LF burst frequency within a frequency range. A set of target frequency range is internally provided, the default option is to regulate the LF burst around 200Hz.

Figure 7-21. Packet Size Regulation Inside LF Burst

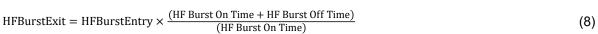

### 7.5.3.2 Mode Transition Management

Using the LL pin, the user configure the power level at which the UCC25661 enters the HF pulse skip and LF Burst mode. The two thresholds that can be set are the *HFBurstEntry* and *LFBurstEntry*. More details on how to configure the power level are in Section 7.5.3.3.

Figure 7-22 describes the entry and exit behavior of UCC25661 in burst mode.

- The *HFBurstEntry*, corresponds to the *FBReplica* voltage at the desired power level where the system enters HF Pulse skip.

- The LFBurstEntry corresponds to a modified FBReplica voltage at which the system enters LF Burst.

- When FBreplica is higher than HFBurstEntry, UCC25661 operates in normal switching.

- When FBreplica is less than HFBurstEntry but greater than LFBurstEntry, UCC25661 operates in HF pulse skip mode. In the HF pulse skip mode, the energy in each packet is still controlled by the control signal FBReplica.

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

- When FBreplica is less than LFBurstEntry, UCC25661 operates in LF burst mode. In the LF Burst mode, the energy in each packet is fixed at LFBurstEntry threshold.

- While operating in LF Burst mode, a new LF Burst segment is started when the *FBReplica* rises above the *LFBurstEntry* threshold. The segment is terminated when the desired number of packets are delivered and the *FBReplica* is below the *PacketStop* threshold.

- The desired number of packets in a LF Burst segment is computed to regulate the LF Burst operating frequency within 200Hz to 400Hz.

- In case of a sudden load drop, the LF Burst segment is immediately terminated to avoid output over voltage condition.

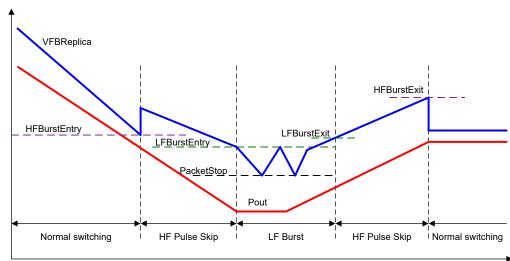

- Once in LFBurst, the *LFBurstExit* and *HFBurstExit* thresholds are continually calculated. The Equation 7 and Equation 8 describes this.

- As the FBReplica increases above the LFBurstExit, the UCC25661 goes back to working in HF Burst Mode.

- When the FBReplica rises above the HFBurstExit, the UCC25661 exits HFBurst and enters to normal switching.

- Every time the controller exits the HFBurst, a blanking time of 2ms is added to verify that the controller

does not reenter into Burst mode. During the blanking period, if the FBReplica falls below the PacketStop

threshold, the controller reenters LFBurst.

$$LFBurstExit = LFBurstEntry \times \frac{(LF Burst On Time + LF Burst Off Time)}{(LF Burst On Time)}$$

(7)

Figure 7-22. Burst Mode Determination from FBReplica Comparators

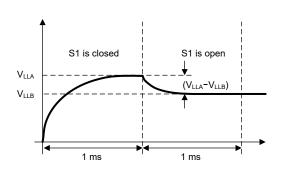

#### 7.5.3.3 Burst Mode Thresholds Programming