**TPS65987DDK** SLVSFN8B - SEPTEMBER 2020 - REVISED OCTOBER 2022

# TPS65987DDK USB Type-C® and USB PD Controller with Integrated Power Switches For USB4 and Thunderbolt 4 Devices

## 1 Features

- This device is certified by the USB-IF for PD3.0

- PD3.0 silicon is required for certification of new USB PD designs

- TID#: 5431

- Article on PD2.0 vs. PD3.0

- TPS65987DDK is a USB4 and Thunderbolt 4 (TBT4) Device PD3.0 controller

- This PD controller is only intended for use in USB4 device designs

- Refer to Intel Reference Design document number 631605

- If designing something other than a USB4 device, please refer to selection guide and getting started information at www.ti.com/usb-c and E2E guide

- Integrated fully managed power paths:

- Integrated two 5-20 V. 5-A. 25-mΩ bidirectional switches

- UL2367 cert #: 20190107-E169910

- IEC62368-1 cert #: US-34617-UL

- Integrated robust power path protection

- Integrated reverse current protection, undervoltage protection, overvoltage protection, and slew rate control for both 20-V/5-A power paths when configured to Sink

- Integrated undervoltage protection, overvoltage protection, and current limiting for inrush current protection for both 20-V/5-A power paths when configured to Source

- USB Type-C® Power Delivery (PD) controller

- 13 configurable GPIOs

- USB PD 3.0 certified

- USB Type-C specification certified

- Cable attach and orientation detection

- Integrated VCONN switch

- Physical layer and policy engine

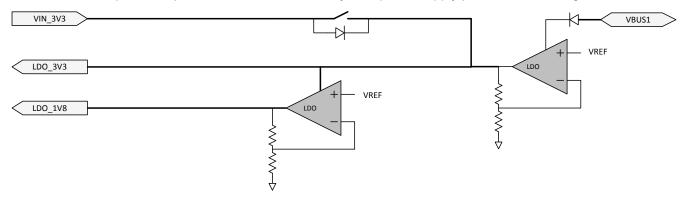

- 3.3-V LDO output for dead battery support

- Power supply from 3.3 V or VBUS source

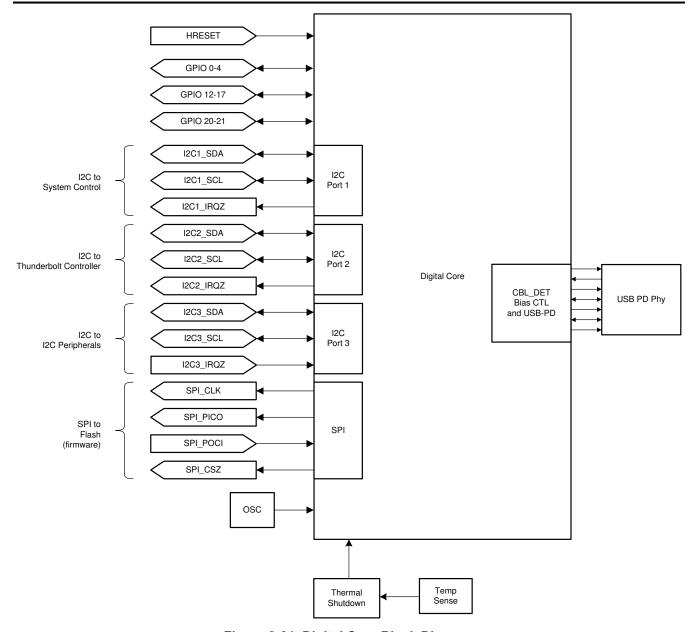

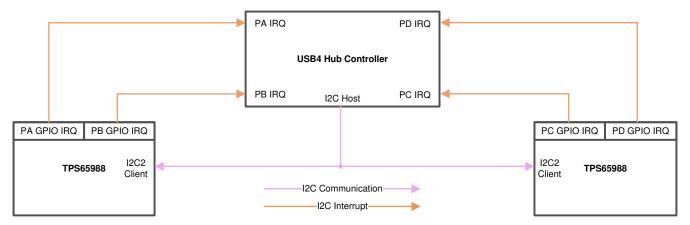

- 1 I2C primary or secondary port

- 1 I2C primary only port

- 1 I2C secondary only port

# 2 Applications

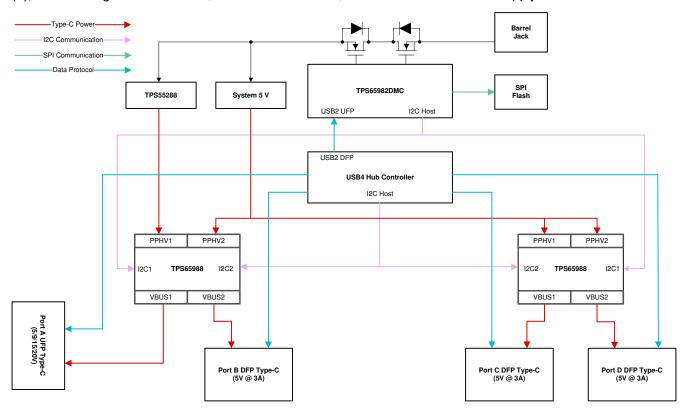

- **Docking systems**

- Monitors

- USB4 hubs

# 3 Description

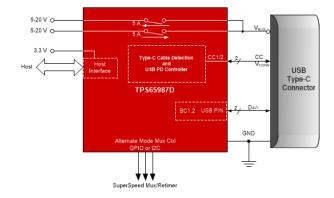

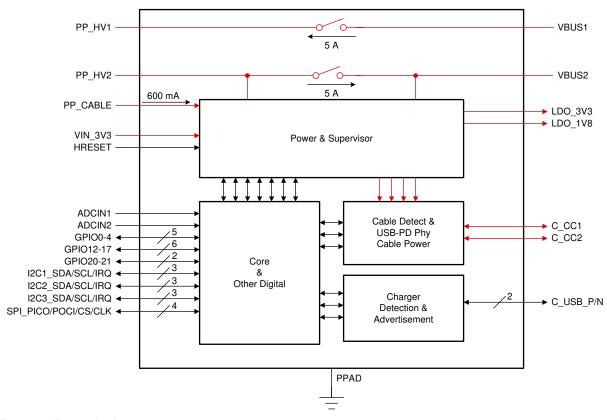

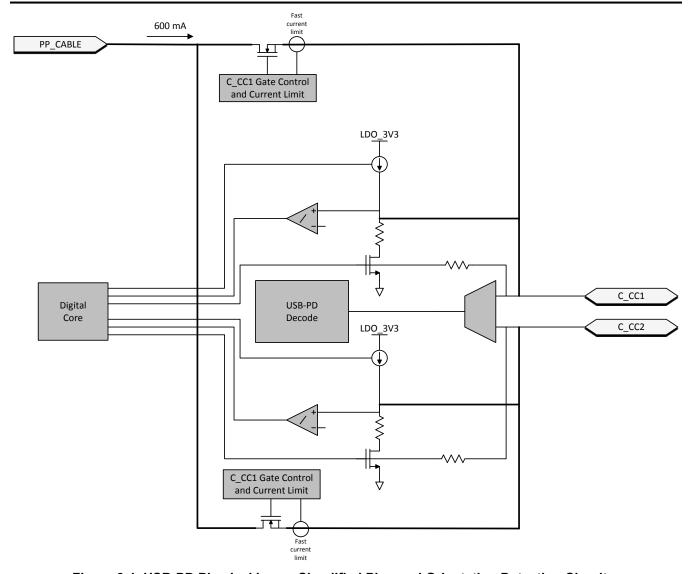

The TPS65987DDK is a highly integrated standalone USB Type-C and Power Delivery (PD) controller optimized for USB4 & TBT4 Device. The TPS65987DDK integrates fully managed power paths with robust protection for a complete USB-C PD solution. The TPS65987DDK is a stand-alone USB Type-C and Power Delivery (PD) controller providing cable plug and orientation detection for a single USB Type-C connector. Upon cable detection, the TPS65987DDK communicates on the CC wire using the USB PD protocol. When cable detection and USB PD negotiation are complete, the TPS65987DDK enables the appropriate power path and configures alternate mode settings for external multiplexers. This device is featured on Intel's Reference Design for USB4 & TBT4 Device end equipments ensuring the PD controller has proper system level interaction in these types of designs. This greatly reduces system design complexity and results in reduced time to market.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| TPS65987DDK | QFN (56)               | 7.00 mm x 7.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

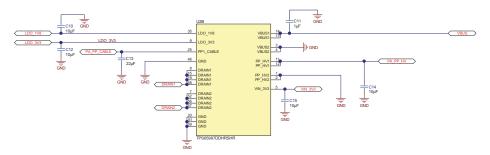

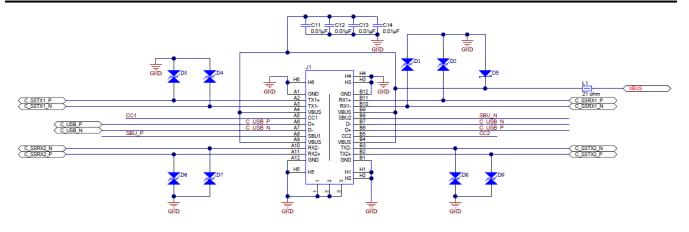

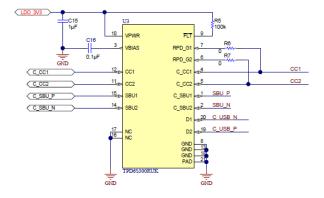

Simplified Schematic

# **Table of Contents**

| 2 Applications1                                          |                                             | 19 |

|----------------------------------------------------------|---------------------------------------------|----|

|                                                          | 8.4 Device Functional Modes                 | 39 |

| 3 Description1                                           | 9 Application and Implementation            | 42 |

| 4 Revision History2                                      | 9.1 Application Information                 |    |

| 5 Pin Configuration and Functions3                       | 9.2 Typical Applications                    |    |

| Specifications7                                          | 10 Power Supply Recommendations             |    |

| 6.1 Absolute Maximum Ratings7                            | 10.1 3.3-V Power                            |    |

| 6.2 ESD Ratings                                          | 10.2 1.8-V Power                            | 47 |

| 6.3 Recommended Operating Conditions7                    | 10.3 Recommended Supply Load Capacitance    | 47 |

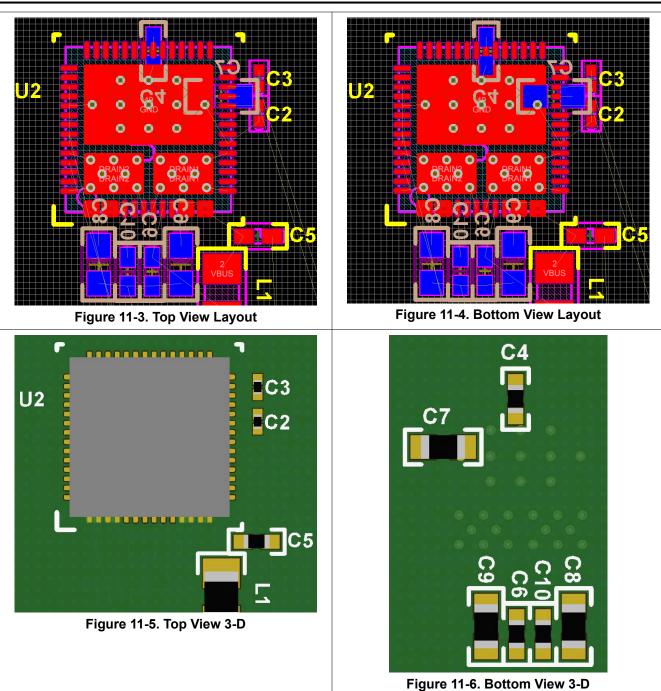

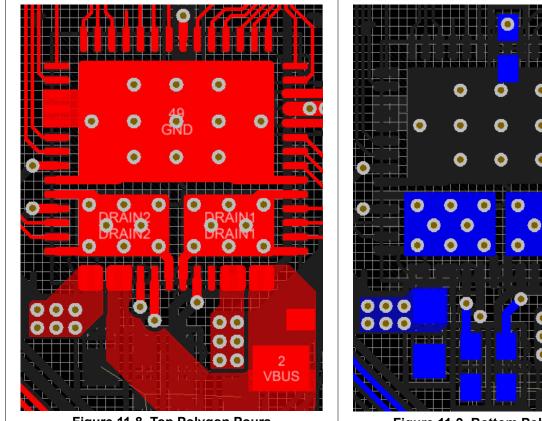

| 6.4 Thermal Information8                                 | 11 Layout                                   | 48 |

| 6.5 Power Supply Requirements and Characteristics8       | 11.1 Layout Guidelines                      |    |

| 6.6 Power Consumption Characteristics9                   | 11.2 Layout Example                         | 48 |

| 6.7 Power Switch Characteristics9                        | 11.3 Component Placement                    |    |

| 6.8 Cable Detection Characteristics11                    | 11.4 Routing PP_HV1/2, VBUS, PP_CABLE,      |    |

| 6.9 USB-PD Baseband Signal Requirements and              | VIN_3V3, LDO_3V3, LDO_1V8                   | 50 |

| Characteristics12                                        | 11.5 Routing CC and GPIO                    | 51 |

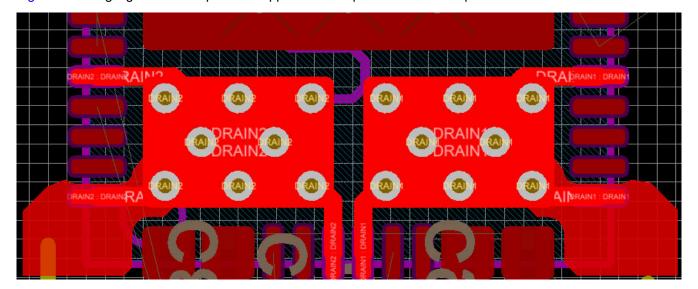

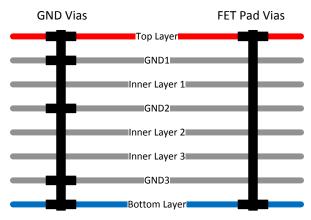

| 6.10 Thermal Shutdown Characteristics13                  | 11.6 Thermal Dissipation for FET Drain Pads | 52 |

| 6.11 Oscillator Characteristics                          | 12 Device and Documentation Support         | 55 |

| 6.12 I/O Characteristics                                 | 12.1 Device Support                         |    |

| 6.13 I <sup>2</sup> C Requirements and Characteristics14 | 12.2 Documentation Support                  | 55 |

| 6.14 SPI Controller Timing Requirements15                | 12.3 Support Resources                      |    |

| 6.15 HPD Timing Requirements16                           | 12.4 Trademarks                             | 55 |

| 6.16 Typical Characteristics16                           | 12.5 Electrostatic Discharge Caution        | 55 |

| 7 Parameter Measurement Information17                    | 12.6 Glossary                               |    |

| B Detailed Description18                                 | 13 Mechanical, Packaging, and Orderable     |    |

| 8.1 Overview                                             | Information                                 | 55 |

| 8.2 Functional Block Diagram19                           |                                             |    |

# **4 Revision History**

| Changes from Revision * (September 2020) to Revision A (August 2021)              | Page |

|-----------------------------------------------------------------------------------|------|

| Updated the Features list                                                         |      |

| Updated the document title                                                        |      |

| · Globally changed instances of legacy terminology to controller and peripheral w |      |

| Updated the <i>Description</i> section                                            |      |

| Changes from Povision * (Sentember 2020) to Povision A (August 2021)              | Page |

| CI | nanges from Revision * (September 2020) to Revision A (August 2021)                                  | Page |

|----|------------------------------------------------------------------------------------------------------|------|

| •  | Updated the Features list                                                                            | 1    |

| •  | Updated the document title                                                                           | 1    |

|    | Globally changed instances of legacy terminology to controller and peripheral where SPI is mentioned |      |

| •  | Updated the <i>Description</i> section                                                               | 1    |

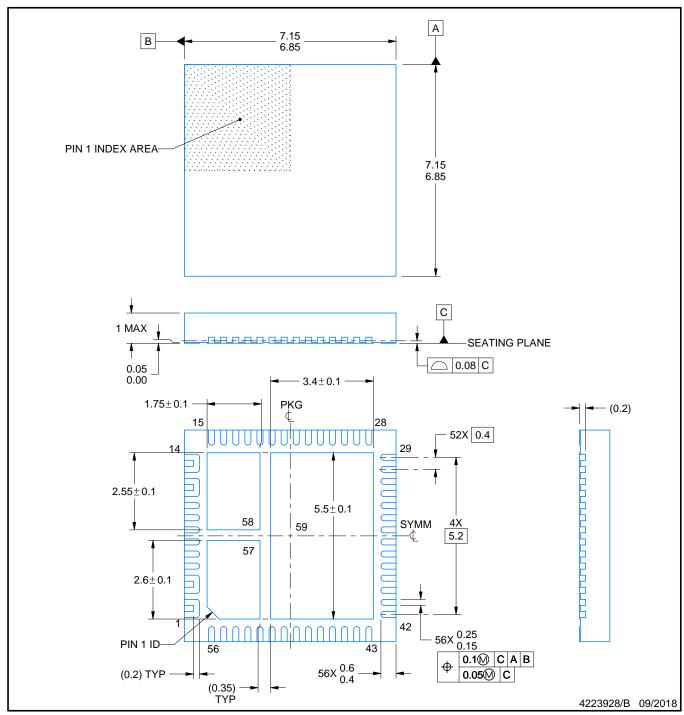

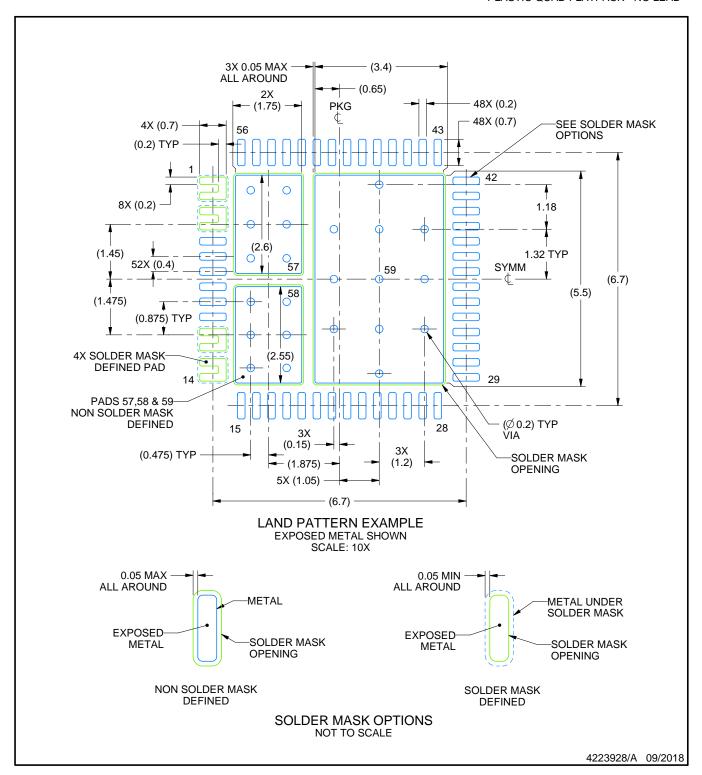

# **5 Pin Configuration and Functions**

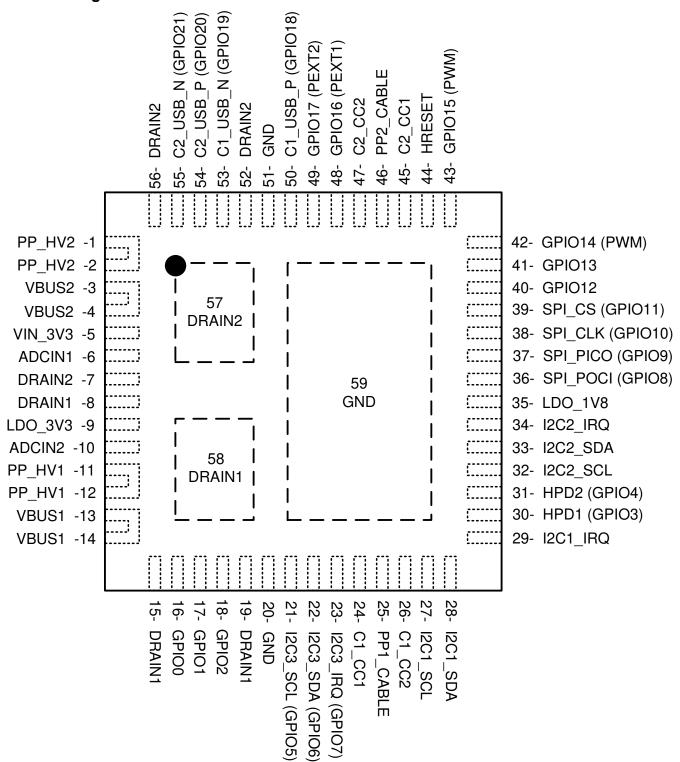

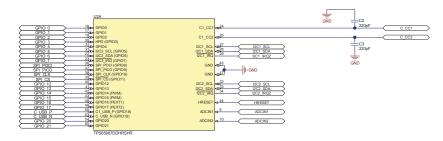

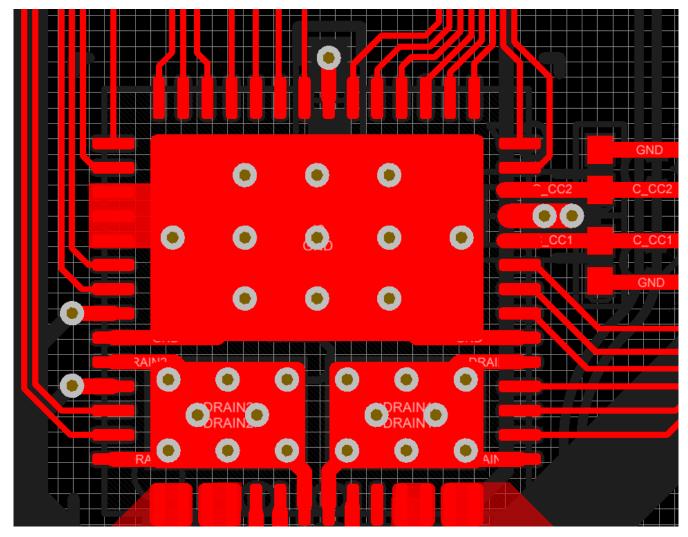

Figure 5-1. RSH Package 56-Pin QFN Top View

# **Table 5-1. Pin Functions**

| PII              | N                   |                     | 1. PIII FUIICIIOIIS        |                                                                                                                                                                                                              |

|------------------|---------------------|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.                 | TYPE <sup>(2)</sup> | RESET STATE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                  |

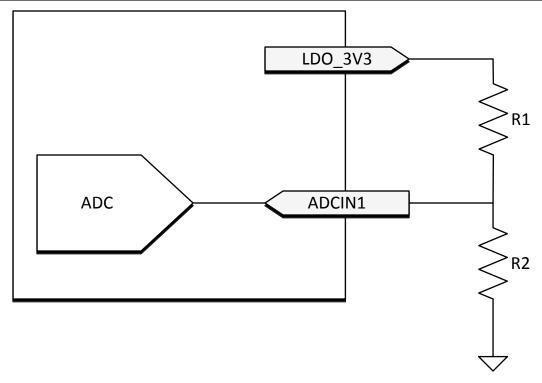

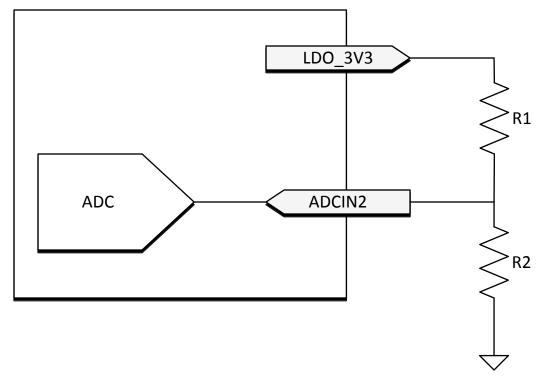

| ADCIN1           | 6                   | I                   | Input                      | Boot configuration Input. Connect to resistor divider between LDO_3V3 and GND.                                                                                                                               |

| ADCIN2           | 10                  | I                   | Input                      | I2C address configuration Input. Connect to resistor divider between LDO_3V3 and GND.                                                                                                                        |

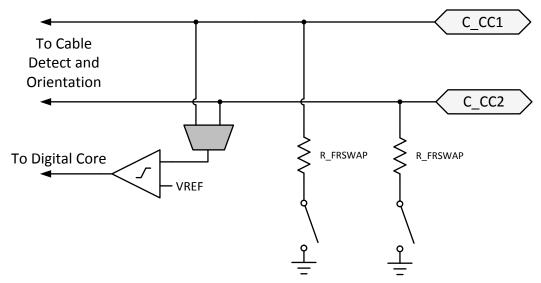

| C_CC1            | 24                  | I/O                 | High-Z                     | Output to Type-C CC or VCONN pin . Filter noise with capacitor to GND.                                                                                                                                       |

| C_CC2            | 26                  | I/O                 | High-Z                     | Output to Type-C CC or VCONN pin . Filter noise with capacitor to GND.                                                                                                                                       |

| C_USB_N (GPIO19) | 53                  | I/O                 | Input (High-Z)             | USB D- connection for BC1.2 support.                                                                                                                                                                         |

| C_USB_P (GPIO18) | 50                  | I/O                 | Input (High-Z)             | USB D+ connection for BC1.2 support.                                                                                                                                                                         |

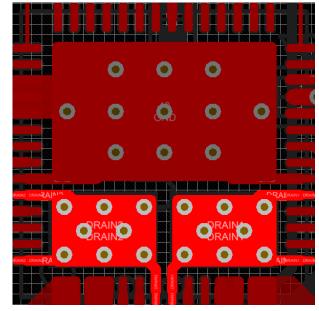

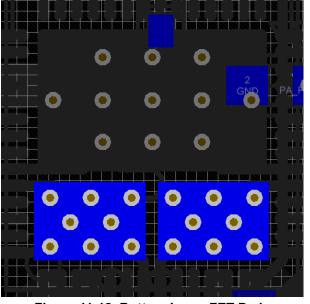

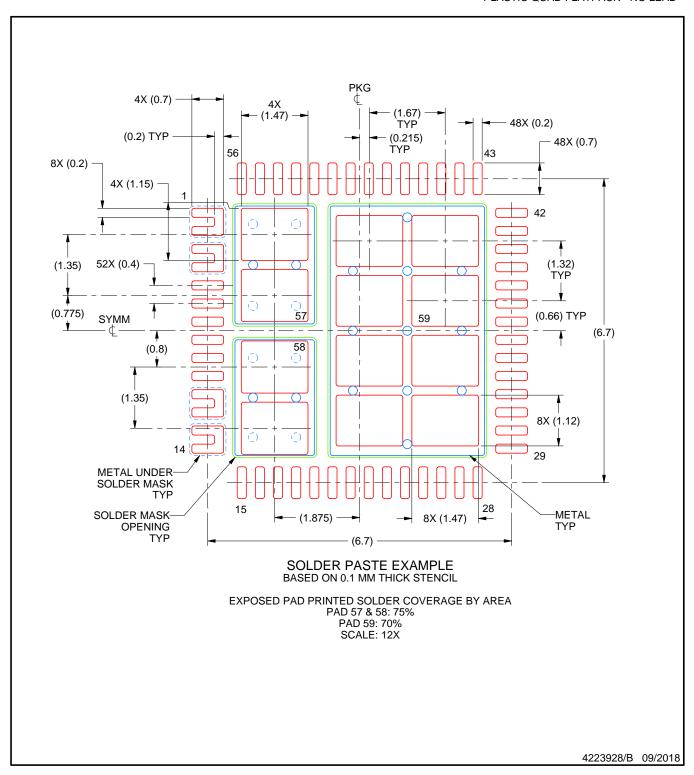

| DRAIN1           | 8, 15, 19, 58       | _                   | _                          | Drain of internal power path 1. Connect thermal pad 58 to as big of pad as possible on PCB for best thermal performance. Short the other pins to this thermal pad.                                           |

| DRAIN2           | 7, 52, 56, 57       | _                   | _                          | Drain of internal power path 2. Connect thermal pad 57 to as big of pad as possible on PCB for best thermal performance. Short the other pins to this thermal pad.                                           |

| GND              | 20, 45 , 46, 47, 51 | _                   | _                          | Unused pin. Tie to GND.                                                                                                                                                                                      |

| GPIO0            | 16                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 0. Float pin when unused. GPIO0 is asserted low during the TPS65987DDK boot process. Once device configuration and patches are loaded GPIO0 is released.                         |

| GPIO1            | 17                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 1. Ground pin with a $1\text{-M}\Omega$ resistor when unused in the application.                                                                                                 |

| GPIO2            | 18                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 2. Float pin when unused.                                                                                                                                                        |

| GPIO3 (HPD)      | 30                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 3. Configured as Hot Plug Detect (HPD) TX and RX when DisplayPort alternate mode is enabled. Float pin when unused.                                                              |

| GPIO4            | 31                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 4. Float pin when unused.                                                                                                                                                        |

| I2C3_SCL (GPIO5) | 21                  | I/O                 | Input (High-Z)             | I2C port 3 serial clock. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used. Float pin when unused.                                                                      |

| I2C3_SDA (GPIO6) | 22                  | I/O                 | Input (High-Z)             | I2C port 3 serial data. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used. Float pin when unused.                                                                       |

| Ī2C3_IRQ (GPIO7) | 23                  | I/O                 | Input (High-Z)             | I2C port 3 interrupt detection (port 3 operates as an I2C Master Only). Active low detection. Connect to the I2C slave's interrupt line to detect when the slave issues an interrupt. Float pin when unused. |

| GPIO12           | 40                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 12. Float pin when unused.                                                                                                                                                       |

| GPIO13           | 41                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 13. Float pin when unused.                                                                                                                                                       |

| GPIO14 (PWM)     | 42                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 14. May also function as a PWM output. Float pin when unused.                                                                                                                    |

| GPIO15 (PWM)     | 43                  | I/O                 | Input (High-Z)             | General Purpose Digital I/O 15. May also function as a PWM output. Float pin when unused.                                                                                                                    |

Table 5-1 Din Functions (continued)

| Table 5-1. Pin Functions (continued) |        |                     |                |                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------|--------|---------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PII                                  | 1      | TYPE <sup>(2)</sup> | RESET STATE(1) | DESCRIPTION                                                                                                                                                                                                                                               |  |  |

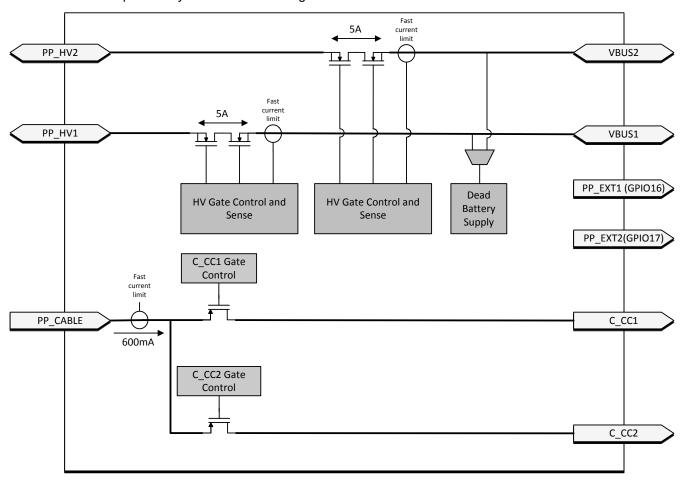

| GPIO16 (PP_EXT1)                     | NO. 48 | I/O                 | Input (High-Z) | General Purpose Digital I/O 16. May also function as single wire enable signal for external power path 1. Pull-down with external resistor when used                                                                                                      |  |  |

| GPIO17 (PP_EXT2)                     | 49     | I/O                 | Input (High-Z) | for external path control. Float pin when unused.  General Purpose Digital I/O 17. May also function as single wire enable signal for external power path 2. Pull-down with external resistor when used for external path control. Float pin when unused. |  |  |

| GPIO20                               | 54     | I/O                 | Input (High-Z) | General Purpose Digital I/O 20. Float pin when unused.                                                                                                                                                                                                    |  |  |

| GPIO21                               | 55     | I/O                 | Input (High-Z) | General Purpose Digital I/O 21. Float pin when unused.                                                                                                                                                                                                    |  |  |

| HRESET                               | 44     | I/O                 | Input          | Active high hardware reset input. Will reinitialize all device settings. Ground pin when HRESET functionality will not be used.                                                                                                                           |  |  |

| IZC1_IRQ                             | 29     | 0                   | High-Z         | I2C port 1 interrupt. Active low. Implement externally as an open drain with a pull-up resistance. Float pin when unused.                                                                                                                                 |  |  |

| I2C1_SCL                             | 27     | I/O                 | High-Z         | I2C port 1 serial clock. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used or unused.                                                                                                                                |  |  |

| I2C1_SDA                             | 28     | I/O                 | High-Z         | I2C port 1 serial data. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used or unused.                                                                                                                                 |  |  |

| I2C2_IRQ                             | 34     | 0                   | High-Z         | I2C port 2 interrupt. Active low. Implement externally as an open drain with a pull-up resistance. Float pin when unused.                                                                                                                                 |  |  |

| I2C2_SCL                             | 32     | I/O                 | High-Z         | I2C port 2 serial clock. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used or unused.                                                                                                                                |  |  |

| I2C2_SDA                             | 33     | I/O                 | High-Z         | I2C port 2 serial data. Open-drain output. Tie pin to I/O voltage through a 10-k $\Omega$ resistance when used or unused.                                                                                                                                 |  |  |

| LDO_1V8                              | 35     | PWR                 | _              | Output of the 1.8-V LDO for internal circuitry. Bypass with capacitor to GND                                                                                                                                                                              |  |  |

| LDO_3V3                              | 9      | PWR                 | _              | Output of the VBUS to 3.3-V LDO or connected to VIN_3V3 by a switch. Main internal supply rail. Used to power external flash memory. Bypass with capacitor to GND.                                                                                        |  |  |

| PP_CABLE                             | 25     | PWR                 | _              | 5-V supply input for port 1 C_CC pins. Bypass with capacitor to GND.                                                                                                                                                                                      |  |  |

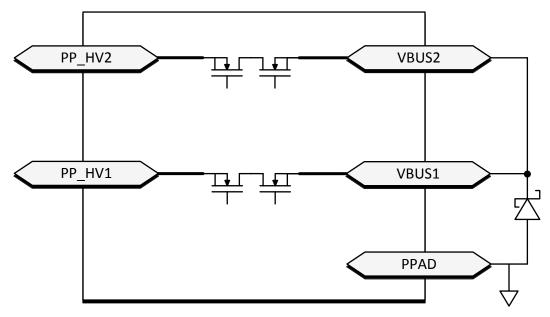

| PP_HV1                               | 11, 12 | PWR                 | _              | System side of first VBUS power switch. Bypass with capacitor to ground. Tie to ground when unused.                                                                                                                                                       |  |  |

| PP_HV2                               | 1, 2   | PWR                 | _              | System side of second VBUS power switch. Bypass with capacitor to ground. Tie to ground when unused.                                                                                                                                                      |  |  |

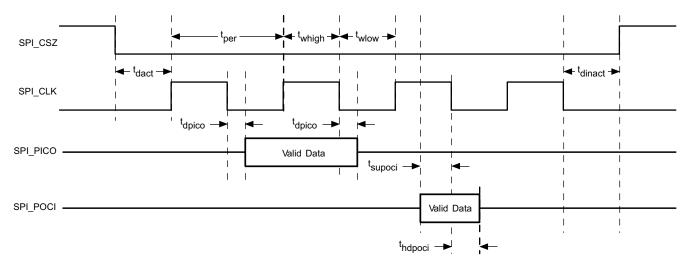

| SPI_CLK                              | 38     | I/O                 | Input          | SPI serial clock. Ground pin when unused.                                                                                                                                                                                                                 |  |  |

| SPI_POCI                             | 36     | I/O                 | Input          | SPI serial controller input from peripheral. Ground pin when unused.                                                                                                                                                                                      |  |  |

| SPI_PICO                             | 37     | I/O                 | Input          | SPI serial controller output to peripheral. Ground pin when unused.                                                                                                                                                                                       |  |  |

| SPI_CS                               | 39     | I/O                 | Input          | SPI chip select. Ground pin when unused.                                                                                                                                                                                                                  |  |  |

| VBUS1                                | 13, 14 | PWR                 | _              | Port side of first VBUS power switch. Bypass with capacitor to ground. Tie to VBUS2.                                                                                                                                                                      |  |  |

# **Table 5-1. Pin Functions (continued)**

| PIN                |      | TYPE <sup>(2)</sup> RESET STATE <sup>(1)</sup> |                                                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |  |  |

|--------------------|------|------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME               | NO.  | IIPE(=/                                        | RESET STATE                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    |  |  |

| VBUS2              | 3, 4 | PWR                                            | Port side of second VBUS power switch. Bypass with capacitor to ground. Tie to VBUS1. |                                                                                                                                                                                                                                                                                                                                                                |  |  |

| VIN_3V3            | 5    | PWR                                            | _                                                                                     | Supply for core circuitry and I/O. Bypass with capacitor to GND.                                                                                                                                                                                                                                                                                               |  |  |

| Thermal Pad (PPAD) | 59   | GND                                            | _                                                                                     | Ground reference for the device as well as thermal pad used to conduct heat. from the device. This connection serves two purposes. The first purpose is to provide an electrical ground connection for the device. The second purpose is to provide a low thermal-impedance path from the device die to the PCB. This pad must be connected to a ground plane. |  |  |

<sup>(1)</sup> Reset State indicates the state of a given pin immediately following power application, prior to any configuration from firmware.

(2) I = input, O = output, I/O = bidirectional, GND = ground, PWR = power, NC = no connect.

# **6 Specifications**

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                            |                                                     | MIN  | MAX               | UNIT |

|------------------------------------------------------------|-----------------------------------------------------|------|-------------------|------|

| Innut valtage(2)                                           | PP_CABLE                                            | -0.3 | 6                 | V    |

| Input voltage <sup>(2)</sup>                               | VIN_3V3                                             | -0.3 | 3.6               | V    |

|                                                            | LDO_1V8                                             | -0.3 | 2                 |      |

| Output voltage <sup>(2)</sup>                              | LDO_3V3                                             | -0.3 | 3.6               | V    |

|                                                            | ĪZCX_ĪRQ, SPI_PICO, SPI_CLK, SPI_CS, SWD_CLK        | -0.3 | LDO_3V3 + 0.3 (3) |      |

|                                                            | PP_HVx, VBUSx <sup>(4)</sup>                        | -0.3 | 24                |      |

| I/O voltage <sup>(2)</sup>                                 | I2Cx_SDA, I2Cx_SCL, SPI_POCI, GPIOn, HRESET, ADCINx | -0.3 | LDO_3V3 + 0.3 (3) | V    |

| i/O voitage (=/                                            | C_USB_P, C_USB_N                                    | -0.5 | 6                 | V    |

|                                                            | C_CC1, C_CC2                                        | -0.5 | 6                 |      |

| Operating junction temperature, T <sub>J</sub>             |                                                     | -10  | 125               | °C   |

| Operating junction temperature PPHV switch, T <sub>J</sub> |                                                     | -10  | 150               | °C   |

| Storage temperat                                           | ture, T <sub>stg</sub>                              | -55  | 150               | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to underside power pad. The underside power pad should be directly connected to the ground plane of the board.

- (3) Not to exceed 3.6 V.

- (4) For VBUSx a TVS with a break down voltage falling between the Recommended max and the Abs max value is recommended such as TVS2200.

# 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>          | ±1500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                               |                                                | MIN   | NOM MAX | UNIT     |  |

|-----------------------------------------------|------------------------------------------------|-------|---------|----------|--|

| Input voltage, V <sub>I</sub> <sup>(1)</sup>  | VIN_3V3                                        | 3.135 | 3.45    |          |  |

|                                               | PP_CABLE                                       | 2.95  | 5.5     | V        |  |

|                                               | PP_HV                                          | 4.5   | 22      |          |  |

|                                               | VBUS                                           | 4     | 22      |          |  |

| I/O voltage, V <sub>IO</sub> <sup>(1)</sup>   | C_USB_P, C_USB_N                               | 0     | LDO_3V3 | V        |  |

| I/O voltage, v <sub>IO</sub> V                | C_CC1, C_CC2                                   | 0     | 5.5     | <b>v</b> |  |

|                                               | GPIOn, I2Cx_SDA, I2Cx_SCL, SPI, ADCIN1, ADCIN2 | 0     | LDO_3V3 |          |  |

| Operating ambient temperature, T <sub>A</sub> |                                                | -10   | 75      | °C       |  |

| Operating junction temp                       | Operating junction temperature, T <sub>J</sub> |       | 125     |          |  |

(1) All voltage values are with respect to underside power pad. Underside power pad must be directly connected to ground plane of the board.

# **6.4 Thermal Information**

|                                  |                                                            | TPS65987DDK |      |

|----------------------------------|------------------------------------------------------------|-------------|------|

|                                  | THERMAL METRIC <sup>(1)</sup>                              | RSH (QFN)   | UNIT |

|                                  |                                                            | 56 PINS     |      |

| R <sub>θJA</sub> (2)             | Junction-to-ambient thermal resistance                     | 57.7        | °C/W |

| R <sub>θJC(top)</sub>            | Junction-to-case (top) thermal resistance                  | 65.4        | °C/W |

| R <sub>0JB</sub> (2)             | Junction-to-board thermal resistance                       | 30          | °C/W |

| Ψ <sub>J</sub> Τ <sup>(2)</sup>  | Junction-to-top characterization parameter                 | 34.1        | °C/W |

| Ψ <sub>JB</sub> <sup>(2)</sup>   | Junction-to-board characterization parameter               | 29.9        | °C/W |

| R <sub>θJC(bot_Controller)</sub> | Junction-to-case (bottom GND pad) thermal resistance       | 0.7         | °C/W |

| R <sub>θJC(bot_FET)</sub>        | Junction-to-case (bottom DRAIN 1/2 pad) thermal resistance | 5.6         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application (1) report.

Thermal metrics are not JDEC standard values and are based on the TPS65988 evaluation board.

# 6.5 Power Supply Requirements and Characteristics

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                                         | TEST CONDITIONS                                              | MIN   | TYP   | MAX      | UNIT |

|-------------------------|-------------------------------------------------------------------|--------------------------------------------------------------|-------|-------|----------|------|

| EXTERNAL                |                                                                   |                                                              |       |       |          |      |

| V <sub>IN_3V3</sub>     | Input 3.3-V supply                                                |                                                              | 3.135 | 3.3   | 3.45     | V    |

| PP_CABLE                | Input to power Vconn output on C_CC pins                          |                                                              | 2.95  | 5     | 5.5      | V    |

| PP_HV                   | Source power from PP_HV to VBUS                                   |                                                              | 4.5   | 5     | 22       | V    |

| VBUS                    | Sink power from VBUS to PP_HV                                     |                                                              | 4     | 5     | 22       | V    |

| C <sub>VIN_3V3</sub>    | Recommended capacitance on the VIN_3V3 pin                        |                                                              | 5     | 10    |          | μF   |

| C <sub>PP_CABLE</sub>   | Recommended capacitance on PPx_CABLE pins                         |                                                              | 2.5   | 4.7   |          | μF   |

| C <sub>PP_HV_SRC</sub>  | Recommended capacitance on PP_HVx pin when configured as a source |                                                              | 2.5   | 4.7   |          | μF   |

| C <sub>PP_HV_SNK</sub>  | Recommended capacitance on PP_HVx pin when configured as a sink   |                                                              | 1     | 47    | 120      | μF   |

| C <sub>VBUS</sub>       | Recommended capacitance on VBUSx pins                             |                                                              | 0.5   | 1     | 12       | μF   |

| INTERNAL                |                                                                   |                                                              | •     |       |          |      |

| V <sub>LDO_3V3</sub>    | Output voltage of LDO from VBUS to LDO_3V3                        | VIN_3V3 = 0 V, VBUS1 ≥ 4 V, 0 ≤<br>I <sub>LOAD</sub> ≤ 50 mA | 3.15  | 3.3   | 3.45     | V    |

| V <sub>DO_LDO_3V3</sub> | Drop out voltage of LDO_3V3 from VBUS                             | I <sub>LOAD</sub> = 50 mA                                    | 250   | 500   | 850      | mV   |

| I <sub>LDO_3V3_EX</sub> | Allowed External Load current on LDO_3V3 pin                      |                                                              |       |       | 25       | mA   |

| V <sub>LDO_1V8</sub>    | Output voltage of LDO_1V8                                         | 0 ≤ I <sub>LOAD</sub> ≤ 20 mA                                | 1.75  | 1.8   | 1.85     | V    |

| V <sub>FWD_DROP</sub>   | Forward voltage drop across VIN_3V3 to LDO_3V3 switch             | I <sub>LOAD</sub> = 50 mA                                    |       |       | 200      | mV   |

| C <sub>LDO_3V3</sub>    | Recommended capacitance on LDO_3V3 pin                            |                                                              | 5     | 10    | 25       | μF   |

| C <sub>LDO_1V8</sub>    | Recommended capacitance on LDO_1V8 pin                            |                                                              | 2.2   | 4.7   | 6        | μF   |

| SUPERVISORY             |                                                                   |                                                              |       |       | <u>'</u> |      |

| UV_LDO3V3               | Undervoltage threshold for LDO_3V3. Locks out 1.8-V LDOs.         | LDO_3V3 rising                                               | 2.2   | 2.325 | 2.45     | V    |

Submit Document Feedback

# 6.5 Power Supply Requirements and Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

|            | PARAMETER                                                                                  | TEST CONDITIONS            | MIN | TYP   | MAX   | UNIT |

|------------|--------------------------------------------------------------------------------------------|----------------------------|-----|-------|-------|------|

| UVH_LDO3V3 | Undervoltage hysteresis for LDO_3V3                                                        | LDO_3V3 falling            | 20  | 80    | 150   | mV   |

| UV_PCBL    | Undervoltage threshold for PP_CABLE                                                        | PP_CABLE rising            | 2.5 | 2.625 | 2.75  | V    |

| UVH_PCBL   | Undervoltage hysteresis for PP_PCABLE                                                      | PP_CABLE falling           | 20  | 50    | 80    | mV   |

| OV_VBUS    | Overvoltage threshold for VBUS. This value is a 6-bit programmable threshold               | VBUS rising                | 5   |       | 24    | V    |

| OVLSB_VBUS | Overvoltage threshold step for VBUS. This value is the LSB of the programmable threshold   | VBUS rising                |     | 328   |       | mV   |

| OVH_VBUS   | Overvoltage hysteresis for VBUS                                                            | VBUS falling, % of OV_VBUS | 1.4 | 1.65  | 1.9   | %    |

| UV_VBUS    | Undervoltage threshold for VBUS. This value is a 6-bit programmable threshold.             | VBUS falling               | 2.5 |       | 18.21 | V    |

| UVLSB_VBUS | Undervoltage threshold step for VBUS. This value is the LSB of the programmable threshold. | VBUS falling               |     | 249   |       | mV   |

| UVH_VBUS   | Undervoltage hysteresis for VBUS                                                           | VBUS rising, % of UV_VBUS  | 0.9 | 1.3   | 1.7   | %    |

# **6.6 Power Consumption Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                                     | PARAMETER          | TEST CONDITIONS                                                                                                     | MIN | TYP | MAX | UNIT |

|-------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>VIN_3V3</sub> <sup>(1)</sup> | Sleep (Sink)       | VIN_3V3 = 3.3 V, VBUS = 0 V, No cable connected, $T_j$ = 25°C, configured as sink, BC1.2 disabled                   |     | 45  |     | μΑ   |

|                                     | Sleep (Source/DRP) | VIN_3V3 = 3.3 V, VBUS = 0 V, No cable connected, T <sub>j</sub> = 25°C, configured as source or DRP, BC1.2 disabled |     | 55  |     | μΑ   |

| I <sub>VIN_3V3</sub> (1)            | Idle (Attached)    | VIN_3V3 = 3.3 V, Cable connected,<br>No active PD communication, T <sub>j</sub> = 25°C                              |     | 5   |     | mA   |

| I <sub>VIN_3V3</sub> (1)            | Active             | VIN_3V3 = 3.3 V, T <sub>j</sub> = 25°C                                                                              |     | 8   |     | mA   |

<sup>(1)</sup> Does not include current draw due to GPIO loading

# **6.7 Power Switch Characteristics**

|                    | PARAMETER                                                         | TEST CONDITIONS                                                                      | MIN | TYP | MAX | UNIT |

|--------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>PPCC</sub>  | PP CABLE to C CCn power switch                                    | 4.7 ≤ PP_CABLE ≤ 5.5                                                                 |     | 222 | 325 | mΩ   |

|                    | resistance                                                        | 2.95 ≤ PP_CABLE < 4.7                                                                |     | 269 | 414 | mΩ   |

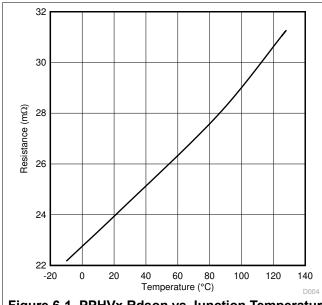

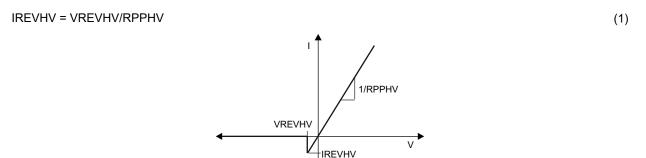

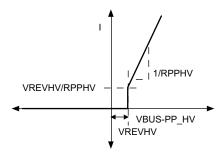

| R <sub>PPHV</sub>  | PP_HVx to VBUSx power switch resistance                           | Tj = 25°C                                                                            |     | 25  | 33  | mΩ   |

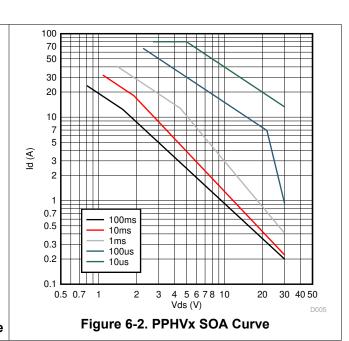

| I <sub>PPHV</sub>  | Continuous current capabillity of power path from PP_HVx to VBUSx |                                                                                      |     |     | 5   | Α    |

|                    | Continuous current capabillity of                                 | T <sub>J</sub> = 125°C                                                               |     |     | 320 | mA   |

| I <sub>PPCC</sub>  | power path from PP_CABLE to C_CCn                                 | T <sub>J</sub> = 85°C                                                                |     |     | 600 | mA   |

| I <sub>HVACT</sub> | Active quiescent current from PP_HV pin, EN_HV = 1                | Source Configuration, Comparator<br>RCP function enabled, I <sub>LOAD</sub> = 100 mA |     |     | 1   | mA   |

| I <sub>HVSD</sub>  | Shutdown quiescent current from PP_HV pin, EN_HV = 0              | V <sub>PPHV</sub> = 20 V                                                             |     |     | 100 | μΑ   |

# **6.7 Power Switch Characteristics (continued)**

|                     | ng free-air temperature range (unles<br>PARAMETER                                             | TEST CONDITIONS                                                                                                            | MIN   | TYP   | MAX   | UNIT |

|---------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

|                     |                                                                                               |                                                                                                                            | 1.140 | 1.267 | 1.393 | Α    |

|                     |                                                                                               |                                                                                                                            | 1.380 | 1.533 | 1.687 | Α    |

|                     |                                                                                               |                                                                                                                            | 1.620 | 1.800 | 1.980 | Α    |

|                     |                                                                                               |                                                                                                                            | 1.860 | 2.067 | 2.273 | Α    |

|                     |                                                                                               |                                                                                                                            | 2.100 | 2.333 | 2.567 | Α    |

|                     |                                                                                               |                                                                                                                            | 2.34  | 2.600 | 2.860 | Α    |

|                     |                                                                                               |                                                                                                                            | 2.580 | 2.867 | 3.153 | Α    |

|                     |                                                                                               |                                                                                                                            | 2.820 | 3.133 | 3.447 | Α    |

|                     |                                                                                               |                                                                                                                            | 3.060 | 3.400 | 3.74  | Α    |

|                     | Over Current Clamp Firmware                                                                   |                                                                                                                            | 3.300 | 3.667 | 4.033 | Α    |

| occ                 | Selectable Settings                                                                           |                                                                                                                            | 3.540 | 3.933 | 4.327 | Α    |

|                     |                                                                                               |                                                                                                                            | 3.780 | 4.200 | 4.620 | Α    |

|                     |                                                                                               |                                                                                                                            | 4.020 | 4.467 | 4.913 | Α    |

|                     |                                                                                               |                                                                                                                            | 4.260 | 4.733 | 5.207 | Α    |

|                     |                                                                                               |                                                                                                                            | 4.500 | 5.00  | 5.500 | Α    |

|                     |                                                                                               |                                                                                                                            | 4.740 | 5.267 | 5.793 | Α    |

|                     |                                                                                               |                                                                                                                            | 4.980 | 5.533 | 6.087 | Α    |

|                     |                                                                                               |                                                                                                                            | 5.220 | 5.800 | 6.380 | Α    |

|                     |                                                                                               |                                                                                                                            | 5.460 | 6.067 | 6.673 | Α    |

|                     |                                                                                               |                                                                                                                            | 5.697 | 6.330 | 6.963 | Α    |

| OCP                 | PP_HV Quick Response Current<br>Limit                                                         |                                                                                                                            |       | 10    |       | Α    |

| LIMPPCC             | PP_CABLE current limit                                                                        |                                                                                                                            | 0.6   | 0.75  | 0.9   | Α    |

| HV_ACC 1            | PP_HV current sense accuracy                                                                  | I = 100 mA, Reverse current blocking disabled                                                                              | 3.9   | 6     | 8.1   | A/V  |

| HV_ACC 1            | PP_HV current sense accuracy                                                                  | I = 200 mA                                                                                                                 | 4.8   | 6     | 7.2   | A/V  |

| HV_ACC 1            | PP_HV current sense accuracy                                                                  | I = 500 mA                                                                                                                 | 5.28  | 6     | 6.72  | A/V  |

| HV_ACC 1            | PP_HV current sense accuracy                                                                  | I ≥ 1 A                                                                                                                    | 5.4   | 6     | 6.6   | A/V  |

| ON_HV               | PP_HV path turn on time from<br>enable to VBUS = 95% of PP_HV<br>voltage                      | Configured as a source or as a sink with soft start disabled. PP_HV = 20 V, CVBUS = 10 $\mu$ F, I <sub>LOAD</sub> = 100 mA |       |       | 8     | ms   |

| ON_FRS              | PP_HV path turn on time from<br>enable to VBUS = 95% of PP_HV<br>voltage during an FRS enable | Configured as a source. PP_HV = 5 V,<br>CVBUS = 10 μF, I <sub>LOAD</sub> = 100 mA                                          |       |       | 150   | μs   |

| ON_CC               | PP_CABLE path turn on time from enable to C_CCn = 95% of the PP_CABLE voltage                 | PP_CABLE = 5 V, C_CCn = 500 nF,<br>I <sub>LOAD</sub> = 100 mA                                                              |       |       | 2     | ms   |

|                     |                                                                                               | I <sub>LOAD</sub> = 100 mA, setting 0                                                                                      | 0.270 | 0.409 | 0.45  | V/ms |

| 20                  | Configurable soft start slew rate for                                                         | I <sub>LOAD</sub> = 100 mA, setting 1                                                                                      | 0.6   | 0.787 | 1     | V/ms |

| SS                  | sink configuration                                                                            | I <sub>LOAD</sub> = 100 mA, setting 2                                                                                      | 1.2   | 1.567 | 1.7   | V/ms |

|                     |                                                                                               | I <sub>LOAD</sub> = 100 mA, setting 3                                                                                      | 2.3   | 3.388 | 3.6   | V/ms |

| ,                   | Reverse current blocking voltage                                                              | Diode Mode                                                                                                                 |       | 6     | 10    | mV   |

| V <sub>REVPHV</sub> | threshold for PP_HV switch                                                                    | Comparator Mode                                                                                                            |       | 3     | 6     | mV   |

| V <sub>SAFE0V</sub> | Voltage that is a safe 0 V per USB-PD specification                                           |                                                                                                                            | 0     |       | 0.8   | V    |

| SAFE0V              | Voltage transition time to VSAFE0V                                                            |                                                                                                                            |       |       | 650   | ms   |

# **6.7 Power Switch Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                                          | TEST CONDITIONS | MIN   | TYP | MAX  | UNIT |

|-----------------------|------------------------------------------------------------------------------------|-----------------|-------|-----|------|------|

| SRPOS                 | Maximum slew rate for positive voltage transitions                                 |                 |       |     | 0.03 | V/µs |

| SRNEG                 | Maximum slew rate for negative voltage transitions                                 |                 | -0.03 |     |      | V/µs |

| t <sub>STABLE</sub>   | EN to stable time for both positive and negative voltage transitions               |                 |       |     | 275  | ms   |

| V <sub>SRCVALID</sub> | Supply output tolerance beyond V <sub>SRCNEW</sub> during time t <sub>STABLE</sub> |                 | -0.5  |     | 0.5  | V    |

| V <sub>SRCNEW</sub>   | Supply output tolerance                                                            |                 | -5    |     | 5    | %    |

| t <sub>vconndis</sub> | Time from cable detach to VVCONNDIS                                                |                 |       |     | 250  | ms   |

| V <sub>VCONNDIS</sub> | Voltage at which V <sub>CONN</sub> is considered discharged                        |                 |       |     | 150  | mV   |

# **6.8 Cable Detection Characteristics**

|                        | PARAMETER                                                                                                                                           | TEST CONDITIONS                            | MIN   | TYP  | MAX   | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------|------|-------|------|

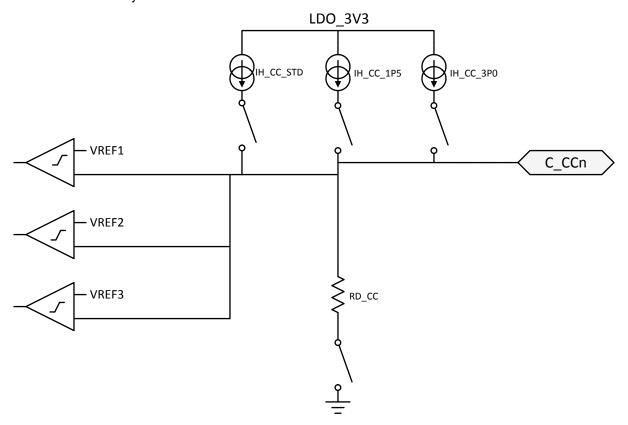

| I <sub>H_CC_USB</sub>  | Source Current through each C_CC pin when in a disconnected state and Configured as a Source advertising Default USB current to a peripheral device |                                            | 73.6  | 80   | 86.4  | μА   |

| I <sub>H_CC_1P5</sub>  | Source Current through each C_CC pin when in a disconnected state when Configured as a Source advertising 1.5-A to a UFP                            |                                            | 165.6 | 180  | 194.4 | μΑ   |

| I <sub>H_CC_3P0</sub>  | Source Current through each C_CC pin when in a disconnected state and Configured as a Source advertising 3.0-A to a UFP.                            | VIN_3V3 ≥ 3.135 V, V <sub>CC</sub> < 2.6 V | 303.6 | 330  | 356.4 | μΑ   |

| V <sub>D_CCH_USB</sub> | Voltage Threshold for detecting a Source attach when configured as a Sink and the Source is advertising Default USB current source capability       |                                            | 0.15  | 0.2  | 0.25  | ٧    |

| V <sub>D_CCH_1P5</sub> | Voltage Threshold for detecting a Source advertising 1.5-A source capability when configured as a Sink                                              |                                            | 0.61  | 0.66 | 0.7   | V    |

| V <sub>D_CCH_3P0</sub> | Voltage Threshold for detecting a Source advertising 3-A source capability when configured as a Sink                                                |                                            | 1.16  | 1.23 | 1.31  | V    |

| V <sub>H_CCD_USB</sub> | Voltage Threshold for detecting a Sink attach when configured as a Source and advertising Default USB current source capability.                    | IH_CC = IH_CC_USB                          | 1.5   | 1.55 | 1.65  | V    |

| V <sub>H_CCD_1P5</sub> | Voltage Threshold for detecting a Sink attach when configured as a Source and advertising 1.5-A source capability                                   | IH_CC = IH_CC_1P5                          | 1.5   | 1.55 | 1.65  | V    |

| V <sub>H_CCD_3P0</sub> | Voltage Threshold for detecting a Sink attach when configured as a Source and advertising 3.0-A source capability.                                  | IH_CC = IH_CC_3P0<br>VIN_3V3 ≥ 3.135 V     | 2.45  | 2.55 | 2.615 | V    |

| V <sub>H_CCA_USB</sub> | Voltage Threshold for detecting an active cable attach when configured as a Source and advertising Default USB current capability.                  |                                            | 0.15  | 0.2  | 0.25  | V    |

| V <sub>H_CCA_1P5</sub> | Voltage Threshold for detecting active cables attach when configured as a Source and advertising 1.5-A capability.                                  |                                            | 0.35  | 0.4  | 0.45  | V    |

# **6.8 Cable Detection Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                                                                        | TEST CONDITIONS    | MIN  | TYP | MAX  | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|------|-----|------|------|

| V <sub>H_CCA_3P0</sub> | Voltage Threshold for detecting active cables attach when configured as a Source and advertising 3-A capability. |                    | 0.75 | 0.8 | 0.85 | V    |

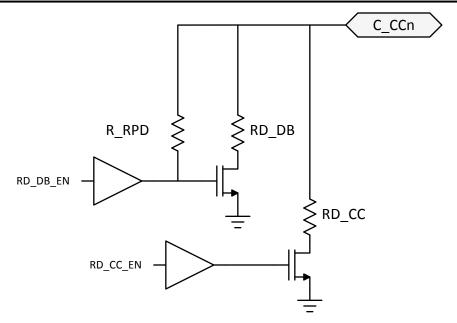

| R <sub>D_CC</sub>      | Pulldown resistance through each C_CC pin when in a disconnect state and configured as a Sink. LDO_3V3 powered.  | V = 1 V, 1.5 V     | 4.59 | 5.1 | 5.61 | kΩ   |

| R <sub>D_CC_OPEN</sub> | Pulldown resistance through each C_CC pin when in a disabled state. LDO_3V3 powered.                             | V = 0 V to LDO_3V3 | 500  |     |      | kΩ   |

| R <sub>D_DB</sub>      | Pulldown resistance through each C_CC pin when LDO_3V3 unpowered                                                 | V = 1.5 V, 2.0 V   | 4.08 | 5.1 | 6.12 | kΩ   |

| R <sub>FRSWAP</sub>    | Fast Role Swap signal pull down                                                                                  |                    |      |     | 5    | Ω    |

| V <sub>TH_FRS</sub>    | Fast role swap request detection voltage threshold                                                               |                    | 490  | 520 | 550  | mV   |

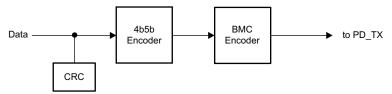

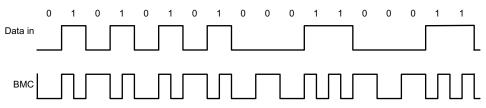

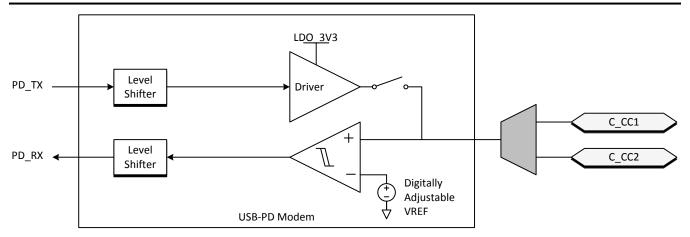

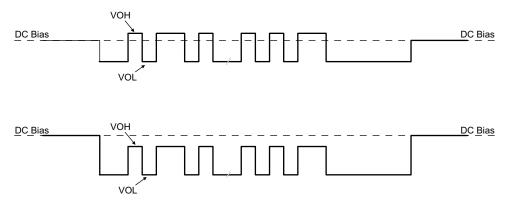

# 6.9 USB-PD Baseband Signal Requirements and Characteristics

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                                                                                                      | TEST CONDITIONS           | MIN  | TYP   | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------|-------|-----|------|

| COMMON            |                                                                                                                                                |                           |      |       |     |      |

| PD_BITRATE        | PD data bit rate                                                                                                                               |                           | 270  | 300   | 330 | Kbps |

| UI <sup>(2)</sup> | Unit interval (1/PD_BITRATE)                                                                                                                   |                           | 3.03 | 3.33  | 3.7 | μs   |

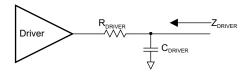

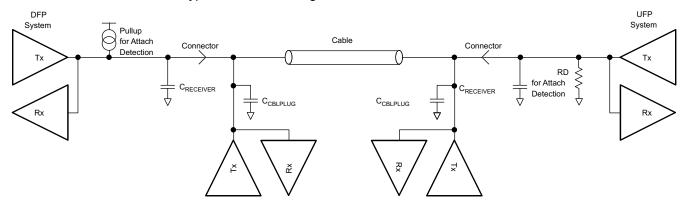

| CCBLPLUG (1)      | Capacitance for a cable plug (each plug on a cable may have up to this value)                                                                  |                           |      |       | 25  | pF   |

| ZCABLE            | Cable characteristic impedance                                                                                                                 |                           | 32   |       | 65  | Ω    |

| CRECEIVER (3)     | Receiver capacitance. Capacitance looking into C_CCn pin when in receiver mode.                                                                |                           |      | 100   |     | pF   |

| TRANSMITTER       |                                                                                                                                                |                           |      |       | ,   |      |

| ZDRIVER           | TX output impedance. Source output impedance at the Nyquist frequency of USB2.0 low speed (750kHz) while the source is driving the C_CCn line. |                           | 33   |       | 75  | Ω    |

| <sup>t</sup> rise | Rise time. 10 % to 90 % amplitude points, minimum is under an unloaded condition. Maximum set by TX mask.                                      |                           | 300  |       |     | ns   |

| FALL              | Fall time. 90 % to 10 % amplitude points, minimum is under an unloaded condition. Maximum set by TX mask.                                      |                           | 300  |       |     | ns   |

| V <sub>TX</sub>   | Transmit high voltage                                                                                                                          |                           | 1.05 | 1.125 | 1.2 | V    |

| RECEIVER          |                                                                                                                                                |                           |      | ,     |     |      |

| V <sub>RXTR</sub> | Rx receive rising input threshold                                                                                                              | Port configured as Source | 840  | 875   | 910 | mV   |

| V <sub>RXTR</sub> | Rx receive rising input threshold                                                                                                              | Port configured as Sink   | 504  | 525   | 546 | mV   |

| V <sub>RXTF</sub> | Rx receive falling input threshold                                                                                                             | Port configured as Sink   | 240  | 250   | 260 | mV   |

| V <sub>RXTF</sub> | Rx receive falling input threshold                                                                                                             | Port configured as Source | 576  | 600   | 624 | mV   |

| NCOUNT            | Number of transitions for signal detection (number to count to detect non-idle bus).                                                           |                           | 3    |       |     |      |

Product Folder Links: TPS65987DDK

## 6.9 USB-PD Baseband Signal Requirements and Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

|               | PARAMETER                                                                                               | TEST CONDITIONS                                                                         | MIN | TYP | MAX | UNIT |

|---------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-----|------|

| TTRANWIN      | Time window for detecting non-idle bus.                                                                 |                                                                                         | 12  |     | 20  | μs   |

| ZBMCRX        | Receiver input impedance                                                                                | Does not include pull-up or pulldown resistance from cable detect. Transmitter is Hi-Z. | 5   |     |     | МΩ   |

| TRXFILTER (4) | Rx bandwidth limiting filter. Time constant of a single pole filter to limit broadband noise ingression |                                                                                         | 100 |     |     | ns   |

- (1) The capacitance of the bulk cable is not included in the CCBLPLUG definition. It is modeled as a transmission line.

- (2) UI denotes the time to transmit an unencoded data bit not the shortest high or low times on the wire after encoding with BMC. A single data bit cell has duration of 1 UI, but a data bit cell with value 1 will contain a centrally place 01 or 10 transition in addition to the transition at the start of the cell.

- (3) CRECEIVER includes only the internal capacitance on a C\_CCn pin when the pin is configured to be receiving BMC data. External capacitance is needed to meet the required minimum capacitance per the USB-PD Specifications. TI recommends adding capacitance to bring the total pin capacitance to 300 pF for improved TX behavior.

- (4) Broadband noise ingression is because of coupling in the cable interconnect.

## 6.10 Thermal Shutdown Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                 | TEST CONDITIONS     | MIN | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------------------|---------------------|-----|-----|-----|------|

| T <sub>SD_MAIN</sub>  | Thermal Shutdown Temperature of the main thermal shutdown | Temperature rising  | 145 | 160 | 175 | °C   |

| T <sub>SDH_MAIN</sub> | Thermal Shutdown hysteresis of the main thermal shutdown  | Temperature falling |     | 20  |     | °C   |

| T <sub>SD_PWR</sub>   | Thermal Shutdown Temperature of the power path block      | Temperature rising  | 145 | 160 | 175 | °C   |

| T <sub>SDH_PWR</sub>  | Thermal Shutdown hysteresis of the power path block       | Temperature falling |     | 20  |     | °C   |

## **6.11 Oscillator Characteristics**

over operating free-air temperature range (unless otherwise noted)

|           | PARAMETER          | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-----------|--------------------|-----------------|------|-----|------|------|

| fosc_24M  | 24-MHz oscillator  |                 | 22.8 | 24  | 25.2 | MHz  |

| fosc_100K | 100-kHz oscillator |                 | 95   | 100 | 105  | kHz  |

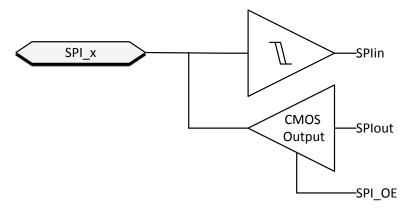

## 6.12 I/O Characteristics

|          | PARAMETER                | TEST CONDITIONS                    | MIN  | TYP MAX | UNIT |  |  |  |

|----------|--------------------------|------------------------------------|------|---------|------|--|--|--|

| SPI      |                          | ·                                  |      |         |      |  |  |  |

| SPI_VIH  | High-level input voltage | LDO_1V8 = 1.8 V                    | 1.3  |         | V    |  |  |  |

| SPI_VIL  | Low input voltage        | LDO_1V8 = 1.8 V                    |      | 0.63    | V    |  |  |  |

| SPI_HYS  | Input hysteresis voltage | LDO_1V8 = 1.8 V                    | 0.09 |         | V    |  |  |  |

| SPI_ILKG | Leakage current          | Output is Hi-Z, VIN = 0 to LDO_3V3 | -1   | 1       | μA   |  |  |  |

| SPI_VOH  | SPI output high voltage  | IO = -2 mA, LDO_3V3 = 3.3 V        | 2.88 |         | V    |  |  |  |

| SPI_VOL  | SPI output low voltage   | IO = 2 mA                          |      | 0.4     | V    |  |  |  |

| SWDIO    |                          | ·                                  |      |         |      |  |  |  |

| SWDCLK   |                          |                                    |      |         |      |  |  |  |

| GPIO     | GPIO                     |                                    |      |         |      |  |  |  |

| GPIO_VIH | High-level input voltage | LDO_1V8 = 1.8 V                    | 1.3  |         | V    |  |  |  |

# 6.12 I/O Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

|           | PARAMETER                   | TEST CONDITIONS                    | MIN  | TYP | MAX  | UNIT |

|-----------|-----------------------------|------------------------------------|------|-----|------|------|

| GPIO_VIL  | Low input voltage           | LDO_1V8 = 1.8 V                    |      |     | 0.63 | V    |

| GPIO_HYS  | Input hysteresis voltage    | LDO_1V8 = 1.8 V                    | 0.09 |     |      | V    |

| GPIO_ILKG | I/O leakage current         | INPUT = 0 V to VDD                 | -1   |     | 1    | μA   |

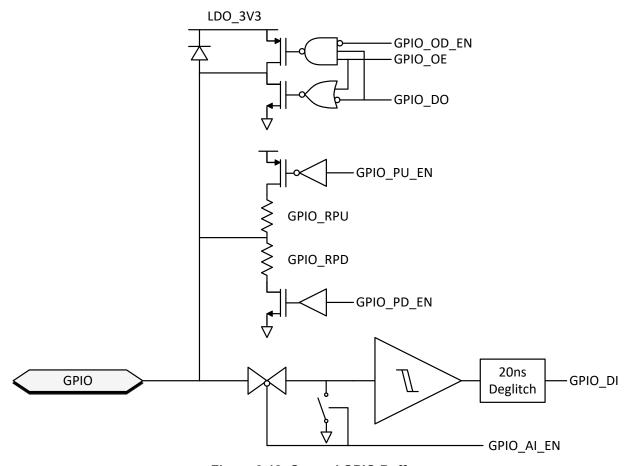

| GPIO_RPU  | Pullup resistance           | Pullup enabled                     | 50   | 100 | 150  | kΩ   |

| GPIO_RPD  | Pulldown resistance         | Pulldown enabled                   | 50   | 100 | 150  | kΩ   |

| GPIO_DG   | Digital input path deglitch |                                    |      | 20  |      | ns   |

| GPIO_VOH  | GPIO output high voltage    | IO = -2 mA, LDO_3V3 = 3.3 V        | 2.88 |     |      | V    |

| GPIO_VOL  | GPIO output low voltage     | IO = 2 mA, LDO_3V3 = 3.3 V         |      |     | 0.4  | V    |

| I2C_IRQx  |                             |                                    |      |     | '    |      |

| OD_VOL    | Low-level output voltage    | I <sub>OL</sub> = 2 mA             |      |     | 0.4  | V    |

| OD_LKG    | Leakage current             | Output is Hi-Z, VIN = 0 to LDO_3V3 | -1   |     | 1    | μA   |

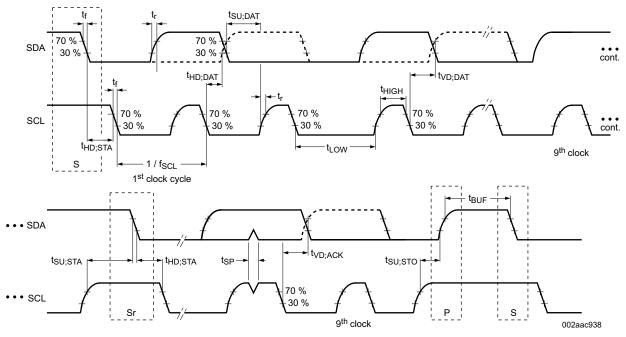

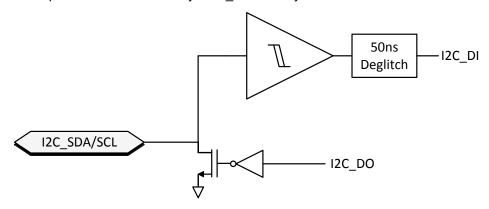

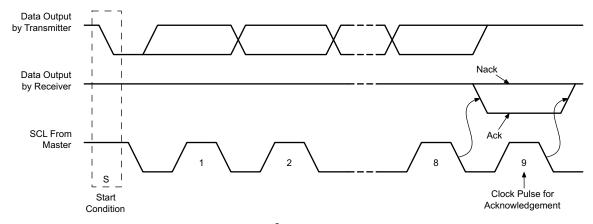

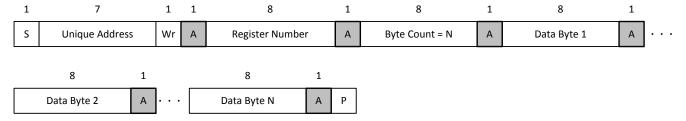

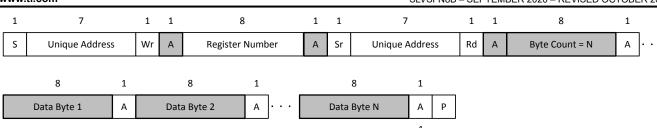

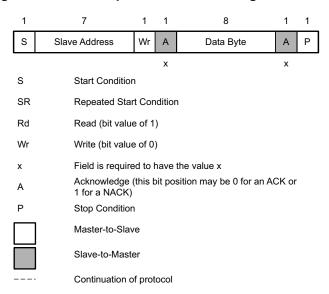

# 6.13 I<sup>2</sup>C Requirements and Characteristics

over operating free-air temperature range (unless otherwise noted).

|                     | PARAMETER                                                     | TEST CONDITIONS                          | MIN  | TYP MAX | UNIT |

|---------------------|---------------------------------------------------------------|------------------------------------------|------|---------|------|

| SDA AND<br>CHARACT  | SCL COMMON<br>ERISTICS                                        |                                          |      |         |      |

| I <sub>LEAK</sub>   | Input leakage current                                         | Voltage on Pin = LDO_3V3                 | -3   | 3       | μA   |

| V <sub>OL</sub>     | SDA output low voltage                                        | I <sub>OL</sub> = 3 mA, LDO_3V3 = 3.3 V  |      | 0.4     | V    |

| 1                   | SDA max output low current                                    | V <sub>OL</sub> = 0.4 V                  | 3    |         | mA   |

| I <sub>OL</sub>     | 3DA max output low current                                    | V <sub>OL</sub> = 0.6 V                  | 6    |         | mA   |

| \/                  | Input low signal                                              | LDO_3V3 = 3.3 V                          |      | 0.99    | V    |

| $V_{IL}$            | input low signal                                              | LDO_1V8 = 1.8 V                          |      | 0.54    | V    |

| V <sub>IH</sub>     | Input high signal                                             | LDO_3V3 = 3.3 V                          | 2.31 |         | V    |

| VIН                 | input nigh signal                                             | LDO_1V8 = 1.8 V                          | 1.3  |         | V    |

| \/                  | Input hysteresis                                              | LDO_3V3 = 3.3 V                          | 0.17 |         | V    |

| $V_{HYS}$           | input hysteresis                                              | LDO_1V8 = 1.8 V                          | 0.09 |         | V    |

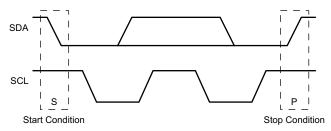

| t <sub>SP</sub>     | I <sup>2</sup> C pulse width suppressed                       |                                          |      | 50      | ns   |

| Cı                  | Pin capacitance                                               |                                          |      | 10      | pF   |

|                     | SCL STANDARD<br>ARACTERISTICS                                 |                                          |      |         |      |

| $f_{\sf SCL}$       | I <sup>2</sup> C clock frequency                              |                                          | 0    | 100     | kHz  |

| t <sub>HIGH</sub>   | I <sup>2</sup> C clock high time                              |                                          | 4    |         | μs   |

| t <sub>LOW</sub>    | I <sup>2</sup> C clock low time                               |                                          | 4.7  |         | μs   |

| t <sub>SU;DAT</sub> | I <sup>2</sup> C serial data setup time                       |                                          | 250  |         | ns   |

| t <sub>HD;DAT</sub> | I <sup>2</sup> C serial data hold time                        |                                          | 0    |         | ns   |

| t <sub>VD;DAT</sub> | I <sup>2</sup> C valid data time                              | SCL low to SDA output valid              |      | 3.45    | μs   |

| t <sub>VD;ACK</sub> | I <sup>2</sup> C valid data time of ACK condition             | ACK signal from SCL low to SDA (out) low |      | 3.45    | μs   |

| t <sub>OCF</sub>    | I <sup>2</sup> C output fall time                             | 10-pF to 400-pF bus                      |      | 250     | ns   |

| t <sub>BUF</sub>    | I <sup>2</sup> C bus free time between stop and start         |                                          | 4.7  |         | μs   |

| t <sub>SU;STA</sub> | I <sup>2</sup> C start or repeated Start condition setup time |                                          | 4.7  |         | μs   |

| t <sub>HD;STA</sub> | I <sup>2</sup> C Start or repeated Start condition hold time  |                                          | 4    |         | μs   |

Submit Document Feedback

# 6.13 I<sup>2</sup>C Requirements and Characteristics (continued)

over operating free-air temperature range (unless otherwise noted).

|                       | PARAMETER                                                     | TER TEST CONDITIONS MIN TYP MAX              |     | UNIT |     |     |

|-----------------------|---------------------------------------------------------------|----------------------------------------------|-----|------|-----|-----|

| t <sub>SU;STO</sub>   | I <sup>2</sup> C Stop condition setup time                    |                                              | 4   |      |     | μs  |

| SDA AND SO            | CL FAST MODE<br>RISTICS                                       |                                              |     |      | ·   |     |

| $f_{\sf SCL}$         | I <sup>2</sup> C clock frequency                              | Configured as Slave                          | 0   |      | 400 | kHz |

| $f_{\sf SCL\_MASTER}$ | I <sup>2</sup> C clock frequency                              | Configured as Master                         | 0   | 320  | 400 | kHz |

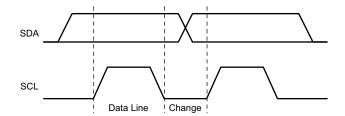

| t <sub>HIGH</sub>     | I <sup>2</sup> C clock high time                              |                                              | 0.6 |      |     | μs  |