TPS630241, TPS630242

**TPS63024**

# SLVSCK8A - NOVEMBER 2014-REVISED DECEMBER 2014

# TPS63024x High Current, High Efficiency Single Inductor Buck-Boost Converter

# **Features**

- Real Buck or Boost operation with automatic and seamless transition between Buck and Boost operation

- 2.3V to 5.5V input voltage range

- 1.5A Continuous Output Current : V<sub>IN</sub>≥ 2.5V,  $V_{OUT} = 3.3V$

- Adjustable and fixed output voltage

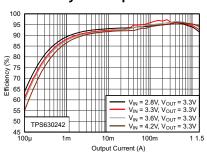

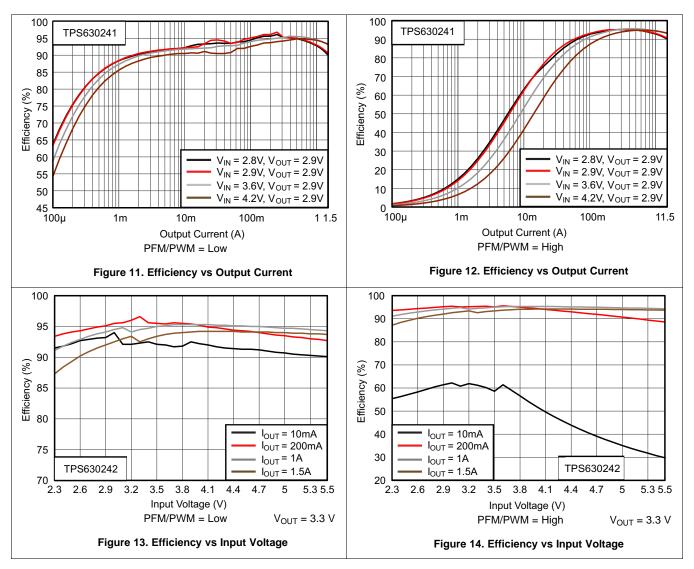

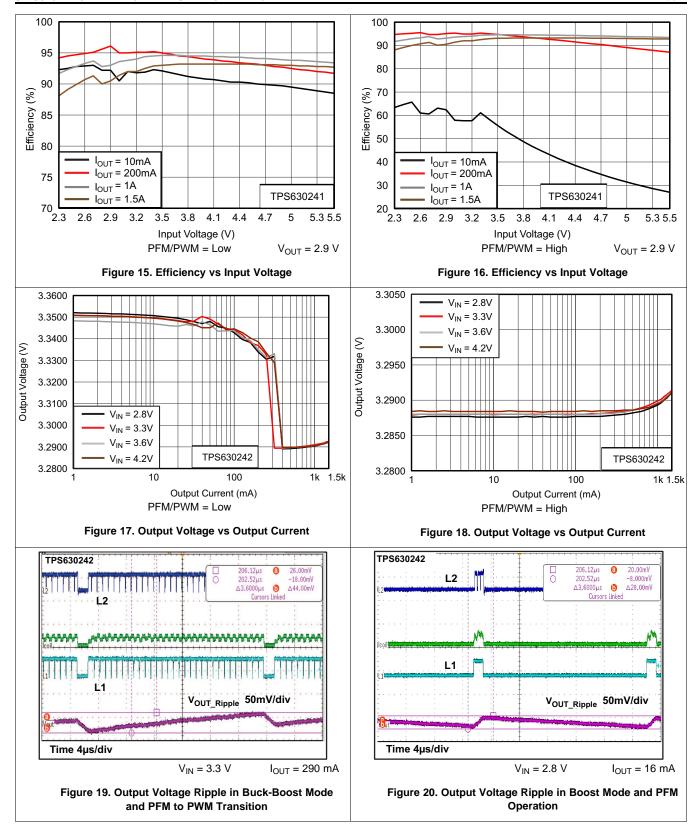

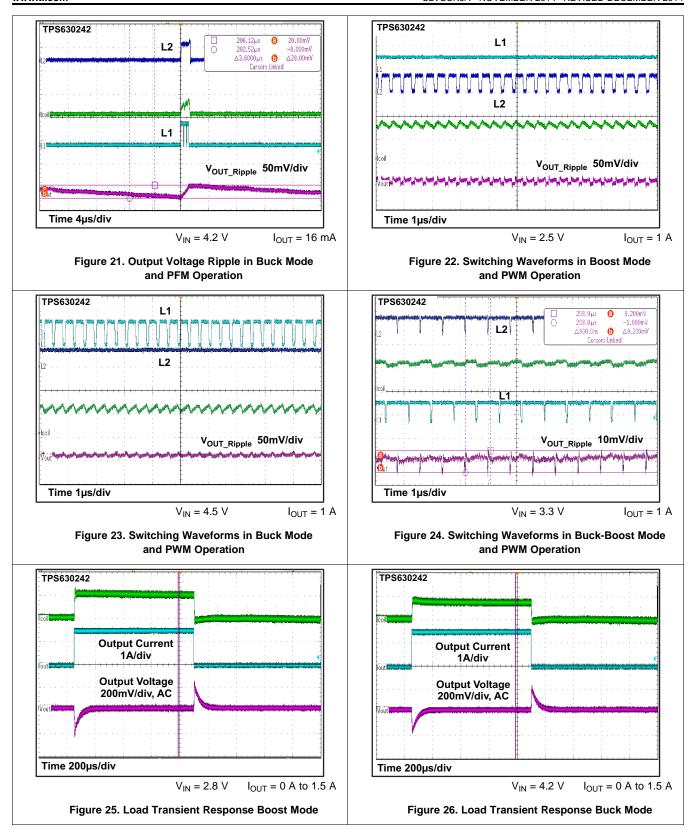

- Efficiency up to 95% in Buck or Boost mode and up to 97% when V<sub>IN</sub>=V<sub>OUT</sub>

- 2.5MHz typical switching frequency

- 35μA operating quiescent current

- Integrated Soft -Start

- Power Save Mode

- True shutdown function

- Output capacitor discharge function

- Over-Temperature Protection and Over current Protection

- Wide capacitance selection

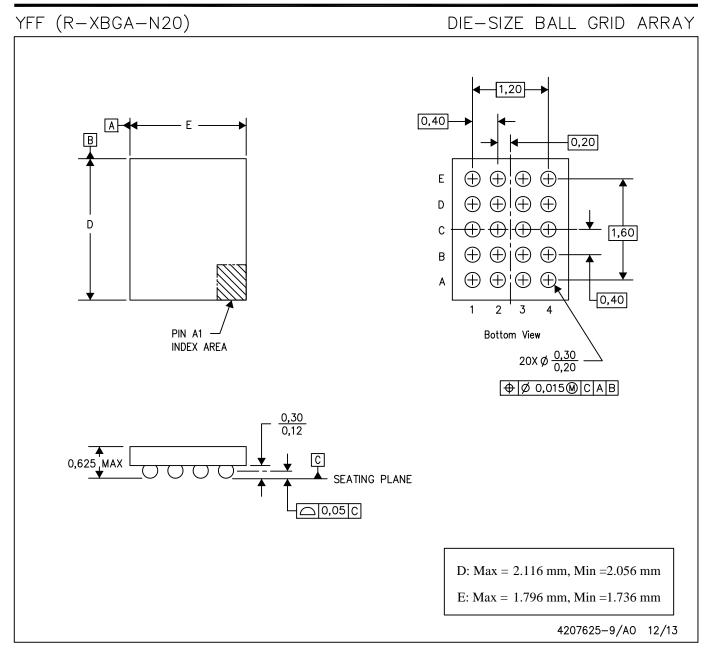

- Small 1.766 mm x 2.086mm, 20-pin WCSP

# **Applications**

- Cellular Phones, Smart Phones

- Tablets PC

- PC and Smart Phone accessories

- Point of load regulation

- **Battery Powered Applications**

# 3 Description

The TPS63024 are high efficiency, low quiescent current buck-boost converters suitable for application where the input voltage is higher or lower than the output. Output currents can go as high as 1.5A in boost mode and as high as 3A in buck mode. The maximum average current in the switches is limited to a typical value of 3A. The TPS63024 regulates the output voltage over the complete input voltage range by automatically switching between buck or boost mode depending on the input voltage ensuring a seamless transition between modes. The buck-boost converter is based on a fixed frequency, pulse-widthmodulation (PWM) controller using synchronous rectification to obtain highest efficiency. At low load currents, the converter enters Power Save Mode to maintain high efficiency over the complete load current range. There is a PFM/PWM pin that allows the user to choose between automatic PFM/PWM mode operation and forced PWM operation. During PWM mode a fixed-frequency of typically 2.5MHz is used. The output voltage is programmable using an external resistor divider, or is fixed internally on the chip. The converter can be disabled to minimize battery drain. During shutdown, the load disconnected from the battery. The device packaged in a 20-pin WCSP package measuring 1.766 mm x 2.086mm.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)     |

|-------------|------------|---------------------|

| TPS63024    |            |                     |

| TPS630241   | DSBGA (20) | 1.766 mm × 2.086 mm |

| TPS630242   |            |                     |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

# **Device Comparison**

|             | •          |

|-------------|------------|

| PART NUMBER | VOUT       |

| TPS63024    | Adjustable |

| TPS630241   | 2.9 V      |

| TPS630242   | 3.3 V      |

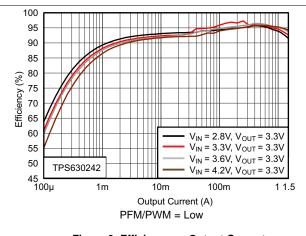

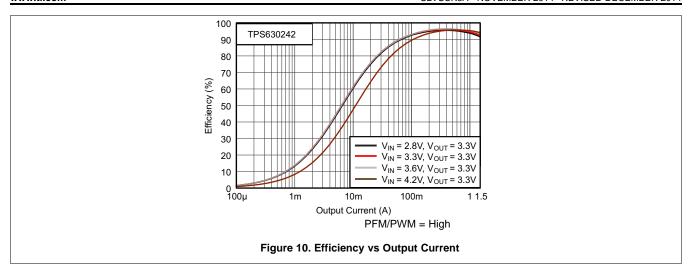

#### **Efficiency vs Output Current**

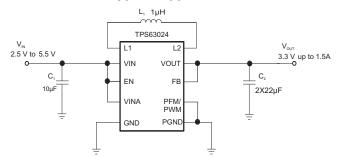

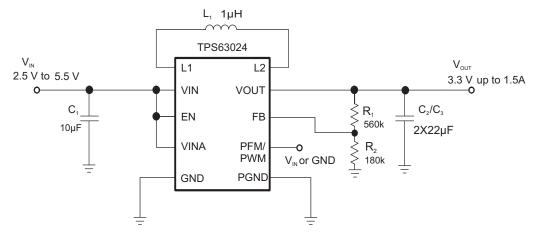

#### Typical Application

# **Table of Contents**

| 1 | Features 1                           |    | 7.4 Device Functional Modes          | 44               |

|---|--------------------------------------|----|--------------------------------------|------------------|

| • |                                      | 8  | Application and Implementation       |                  |

| 2 | Applications 1                       | 0  | • •                                  |                  |

| 3 | Description 1                        |    | 8.1 Application Information          |                  |

| 4 | Revision History2                    |    | 8.2 Typical Application              | 14               |

| 5 | Pin Configuration and Functions3     | 9  | Power Supply Recommendations         | 21               |

| 6 | Specifications                       | 10 | Layout                               | 21               |

| • | 6.1 Absolute Maximum Ratings         |    | 10.1 Layout Guidelines               | <mark>2</mark> 1 |

|   | 6.2 ESD Ratings                      |    | 10.2 Layout Example                  | <mark>2</mark> 1 |

|   | 6.3 Recommended Operating Conditions | 11 | Device and Documentation Support     | 22               |

|   | 6.4 Thermal Information              |    | 11.1 Device Support                  | 22               |

|   | 6.5 Electrical Characteristics5      |    | 11.2 Documentation Support           | 22               |

|   | 6.6 Timing Requirements              |    | 11.3 Related Links                   | 22               |

|   | 6.7 Typical Characteristics          |    | 11.4 Trademarks                      | 22               |

| 7 | Detailed Description 8               |    | 11.5 Electrostatic Discharge Caution | 22               |

| - | 7.1 Overview 8                       |    | 11.6 Glossary                        | 22               |

|   | 7.2 Functional Block Diagram         | 12 | Mechanical, Packaging, and Orderable |                  |

|   | 7.3 Feature Description9             |    | Information                          | 22               |

|   |                                      |    |                                      |                  |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Original (November 2014) to Revision A

Page

Added Specifications, Detailed Description section, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section; and, changed status to

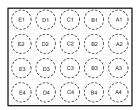

# 5 Pin Configuration and Functions

WCSP 20-Pin YFF (TOP VIEW)

#### **Pin Functions**

| PIN I/O |          | 1/0 | DESCRIPTION                                                                                         |

|---------|----------|-----|-----------------------------------------------------------------------------------------------------|

| NAME    | NO.      | 1/0 | DESCRIPTION                                                                                         |

| VOUT    | A1,A2,A3 | PWR | Buck-boost converter output                                                                         |

| FB      | A4       | IN  | Voltage feedback of adjustable version, must be connected to VOUT for fixed output voltage versions |

| L2      | B1,B2,B3 | PWR | Connection for Inductor                                                                             |

| PFM/PWM | B4       | IN  | set low for PFM mode, set high for forced PWM mode. It must not be left floating                    |

| PGND    | C1,C2,C3 | PWR | Power Ground                                                                                        |

| GND     | C4       | PWR | Analog Ground                                                                                       |

| L1      | D1,D2,D3 | PWR | Connection for Inductor                                                                             |

| EN      | D4       | IN  | Enable input. Set high to enable and low to disable. It must not be left floating.                  |

| VIN     | E1,E2,E3 | PWR | Supply voltage for power stage                                                                      |

| VINA    | E4       | PWR | Supply voltage for control stage.                                                                   |

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

over junction temperature range (unless otherwise noted)

|                        |                                                  | VALU | JE  |      |

|------------------------|--------------------------------------------------|------|-----|------|

|                        |                                                  | MIN  | MAX | UNIT |

| Voltage <sup>(2)</sup> | VIN, L1, EN, VINA, PFM/PWM                       | -0.3 | 7   | ٧    |

|                        | VOUT, FB                                         | -0.3 | 4   | V    |

|                        | L2 <sup>(3)</sup>                                | -0.3 | 4   | V    |

|                        | L2 <sup>(4)</sup>                                | -0.3 | 5.5 | V    |

| Input current          | Continuos average current into L1 <sup>(5)</sup> |      | 2.7 | Α    |

| T <sub>J</sub>         | Operating junction temperature                   | -40  | 125 | ڻ    |

| T <sub>stg</sub>       | Storage temperature range                        | -65  | 150 | C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values are with respect to network ground pin.

- (3) DC voltage rating.

- 4) AC transient voltage rating.

- (5) Maximum continuos average input current 3.5A, under those condition do not exceed 105°C for more than 25% operating time.

Copyright © 2014, Texas Instruments Incorporated

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±700  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions<sup>(1)</sup>

|                  |                                        | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>  | Input Voltage Range                    | 2.3 |     | 5.5 | ٧    |

| V <sub>OUT</sub> | Output Voltage                         | 2.5 |     | 3.6 | ٧    |

| L                | Inductance (2)                         | 0.5 | 1   | 1.3 | μΗ   |

| C <sub>out</sub> | Output Capacitance (3)                 | 16  |     |     | μF   |

| T <sub>A</sub>   | Operating ambient temperature          | -40 |     | 85  | °C   |

| TJ               | Operating virtual junction temperature | -40 |     | 125 | °C   |

- (1) Refer to the Application Information section for further information

- (2) Effective inductance value at operating condition. The nominal value given matches a typical inductor to be chosen to meet the inductance required.

- (3) Due to the dc bias effect of ceramic capacitors, the effective capacitance is lower then the nominal value when a voltage is applied. This is why the capacitance is specified to allow the selection of the nominal capacitor required with the dc bias effect for this type of capacitor. The nominal value given matches a typical capacitor to be chosen to meet the minimum capacitance required.

#### 6.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | TPS63024x<br>YFF<br>20 PINS | UNIT |

|----------------------|----------------------------------------------|-----------------------------|------|

| R <sub>0,JA</sub>    | Junction-to-ambient thermal resistance       | 53.8                        |      |

|                      |                                              |                             |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.5                         |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 10.1                        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.4                         | C/VV |

| ΨЈВ                  | Junction-to-board characterization parameter | 9.8                         |      |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A                         |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics

$V_{IN}=2.3V$  to 5.5V,  $T_{J}=-40$ °C to 125°C, typical values are at  $T_{A}=25$ °C (unless otherwise noted)

|                           | PARAMETER                              |                       | TEST CONDITIONS                                                              | MIN   | TYP   | MAX                                                                              | UNIT     |

|---------------------------|----------------------------------------|-----------------------|------------------------------------------------------------------------------|-------|-------|----------------------------------------------------------------------------------|----------|

| SUPPLY                    |                                        |                       |                                                                              |       |       |                                                                                  |          |

| V <sub>IN</sub>           | Input voltage range                    |                       |                                                                              | 2.3   |       | 5.5                                                                              | V        |

| V <sub>IN_Min</sub>       | Minimum input voltage to to            | ırn on into full load | $R_{LOAD} = 2.2\Omega$                                                       |       | 2.7   |                                                                                  | V        |

|                           |                                        | V <sub>IN</sub>       | I <sub>OUT</sub> =0mA, EN=V <sub>IN</sub> =3.6V,                             |       | 35    | 70                                                                               | μΑ       |

| $I_Q$                     | Quiescent current                      | V <sub>OUT</sub>      | V <sub>OUT</sub> =3.3V T <sub>J</sub> =-40°C to 85°C, not switching          |       |       | 12                                                                               | μА       |

| I <sub>sd</sub>           | Shutdown current                       |                       | EN=low, T <sub>J</sub> =-40°C to 85°C                                        |       | 0.1   | 2                                                                                | μΑ       |

| UVLO                      | Under voltage lockout thres            | shold                 | V <sub>IN</sub> falling                                                      | 1.6   | 1.7   | 5.5  70  12  2  2  0.4  0.2  3.6  1%  +3%  2.929  2.987  3.333  3.399  100  3.54 | V        |

| UVLO                      | Under voltage lockout hyst             | eresis                |                                                                              |       | 70    |                                                                                  | mV       |

|                           | Thermal shutdown                       |                       | Temperature rising                                                           |       | 140   |                                                                                  | °C       |

| LOGIC SIGNA               | ALS EN, PFM/PWM                        |                       |                                                                              |       |       |                                                                                  |          |

| V <sub>IH</sub>           | High level input voltage               |                       | V <sub>IN</sub> =2.3V to 5.5V                                                | 1.2   |       |                                                                                  | V        |

| V <sub>IL</sub>           | Low level input voltage                |                       | V <sub>IN</sub> =2.3V to 5.5V                                                |       |       | 0.4                                                                              | V        |

| I <sub>lkg</sub>          | Input leakage current                  |                       | PFM/PWM, EN=GND or V <sub>IN</sub>                                           |       | 0.01  | 0.2                                                                              | μА       |

| OUTPUT                    |                                        |                       |                                                                              |       |       |                                                                                  |          |

| V <sub>OUT</sub>          | Output Voltage range                   |                       |                                                                              | 2.5   |       | 3.6                                                                              | V        |

| $V_{FB}$                  | Feedback regulation voltage            | е                     | TPS63024                                                                     |       | 0.8   |                                                                                  | V        |

| $V_{FB}$                  | Feedback voltage accuracy              | 1                     | PWM mode, TPS63024                                                           | -1%   |       | 1%                                                                               |          |

| $V_{FB}$                  | Feedback voltage accuracy              | , (1)                 | PFM mode, TPS63024                                                           | -1%   | 1.3%  | +3%                                                                              |          |

| V <sub>OUT</sub>          | Output voltage accuracy                |                       | PWM mode, TPS630241                                                          | 2.871 | 2.9   | 2.929                                                                            | V        |

| V <sub>OUT</sub>          | Output voltage accuracy <sup>(1)</sup> |                       | PFM mode, TPS630241                                                          | 2.871 | 2.938 | 2.987                                                                            | V        |

| V <sub>OUT</sub>          | Output voltage accuracy                |                       | PWM mode, TPS630242                                                          | 3.267 | 3.3   | 3.333                                                                            | V        |

| V <sub>OUT</sub>          | Output voltage accuracy <sup>(1)</sup> |                       | PFM mode, TPS630242                                                          | 3.267 | 3.343 | 3.399                                                                            | V        |

| I <sub>PWM/PFM</sub>      | Output current to enter PFI            | // mode               | V <sub>IN</sub> =3V; V <sub>OUT</sub> = 3.3V                                 |       | 350   |                                                                                  | mA       |

| I <sub>FB</sub>           | Feedback input bias currer             | t                     | V <sub>FB</sub> = 0.8V                                                       |       | 10    | 100                                                                              | nA       |

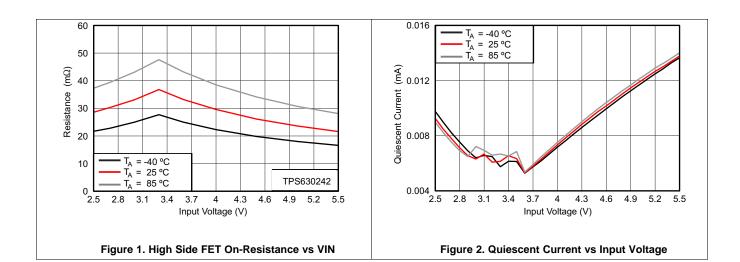

| D                         | High side FET on-resistance            | e                     | V <sub>IN</sub> =3.0V, V <sub>OUT</sub> =3.3V                                |       | 35    |                                                                                  | mΩ       |

| R <sub>DS_Buck(on)</sub>  | Low side FET on-resistance             | е                     | V <sub>IN</sub> =3.0V, V <sub>OUT</sub> =3.3V                                |       | 50    |                                                                                  | mΩ       |

| Б                         | High side FET on-resistance            | e                     | V <sub>IN</sub> =3.0V, V <sub>OUT</sub> =3.3V                                |       | 25    |                                                                                  | mΩ       |

| R <sub>DS_Boost(on)</sub> | Low side FET on-resistance             | е                     | V <sub>IN</sub> =3.0V, V <sub>OUT</sub> =3.3V                                |       | 50    |                                                                                  | mΩ       |

| I <sub>IN</sub>           | Average input current limit            | (2)                   | V <sub>IN</sub> =3.0V, V <sub>OUT</sub> =3.3V T <sub>J</sub> = 25°C to 125°C | 2.12  | 3     | 3.54                                                                             | Α        |

| f <sub>s</sub>            | Switching Frequency                    |                       |                                                                              |       | 2.5   |                                                                                  | MHz      |

| R <sub>ON_DISC</sub>      | Discharge ON-Resistance                |                       | EN=low                                                                       |       | 120   |                                                                                  | Ω        |

|                           | Line regulation                        |                       | V <sub>IN</sub> =2.8V to 5.5V, I <sub>OUT</sub> =1.5A                        |       | 7.4   |                                                                                  | mV/<br>V |

|                           | Load regulation                        |                       | V <sub>IN</sub> =3.6V,I <sub>OUT</sub> =0A to 1.5A                           |       | 2.5   |                                                                                  | mV/<br>A |

<sup>(1)</sup> Conditions: L=1 μH, C<sub>OUT</sub>= 2 x 22μF.

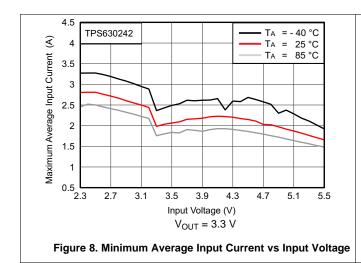

(2) For variation of this parameter with Input voltage and temperature see *Figure 8*. To calculate minimum output current in a specific working point see *Figure 8* and *Equation 1* trough *Equation 4*.

# 6.6 Timing Requirements

$V_{IN}$ = 2.3V to 5.5V,  $T_J$ = -40°C to 125°C, typical values are at  $T_A$ = 25°C (unless otherwise noted)

|                 | PARAMETER      | TEST CONDITIONS                                                                                  | MIN T | P MAX | UNIT |

|-----------------|----------------|--------------------------------------------------------------------------------------------------|-------|-------|------|

| OUTPUT          |                |                                                                                                  |       |       |      |

|                 | Softstart time | EN=low to high, Buck mode $V_{\rm IN}$ =3.6V, $V_{\rm OUT}$ =3.3V, $I_{\rm OUT}$ =1.5A           | 4     | 50    | μs   |

| t <sub>SS</sub> | Sotistart time | EN=low to high, Boost mode V <sub>IN</sub> =2.8V, V <sub>OUT</sub> =3.3V, I <sub>OUT</sub> =1.5A | 7     | 00    | μs   |

| t <sub>d</sub>  | Start up delay | Time from when EN=high to when device starts switching                                           | 1     | 00    | μs   |

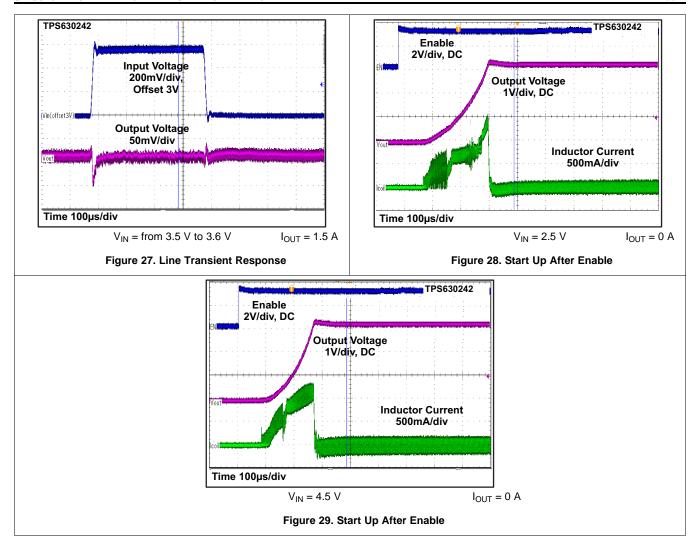

# 6.7 Typical Characteristics

# 7 Detailed Description

#### 7.1 Overview

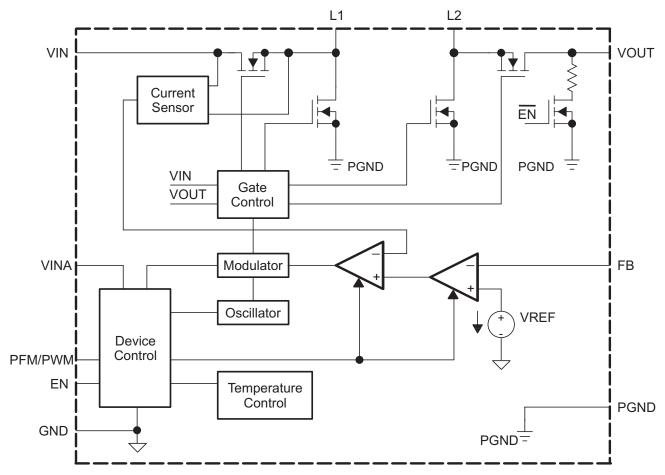

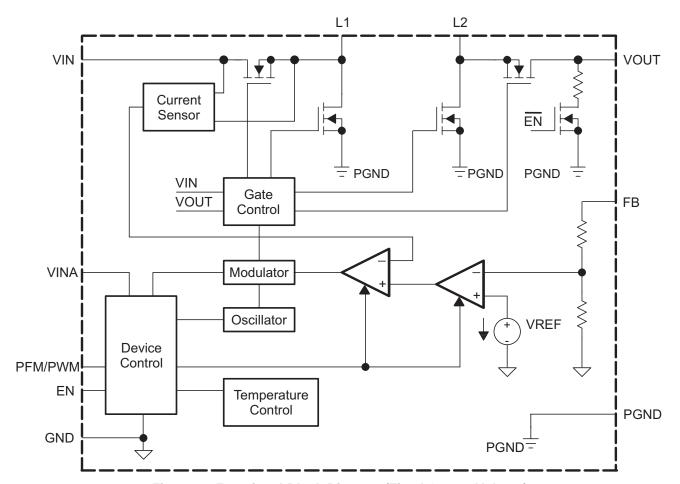

The TPS63024x use 4 internal N-channel MOSFETs to maintain synchronous power conversion at all possible operating conditions. This enables the device to keep high efficiency over the complete input voltage and output power range. To regulate the output voltage at all possible input voltage conditions, the device automatically switches from buck operation to boost operation and back as required by the configuration. It always uses one active switch, one rectifying switch, one switch is held on, and one switch held off. Therefore, it operates as a buck converter when the input voltage is higher than the output voltage, and as a boost converter when the input voltage is lower than the output voltage. There is no mode of operation in which all 4 switches are switching at the same time. Keeping one switch on and one switch off eliminates their switching losses. The RMS current through the switches and the inductor is kept at a minimum, to minimize switching and conduction losses. Controlling the switches this way allows the converter to always keep higher efficiency.

The device provides a seamless transition from buck to boost or from boost to buck operation.

# 7.2 Functional Block Diagram

Figure 3. Functional Block Diagram (Adjustable Output Voltage)

# **Functional Block Diagram (continued)**

Figure 4. Functional Block Diagram (Fixed Output Voltage)

# 7.3 Feature Description

# 7.3.1 Undervoltage Lockout (UVLO)

To avoid mis-operation of the device at low input voltages, an undervoltage lockout is included. UVLO shuts down the device at input voltages lower than typically 1.7V with a 70 mV hysteresis.

# 7.3.2 Output Discharge Function

When the device is disabled by pulling enable low and the supply voltage is still applied, the internal transistor use to discharge the output capacitor is turned on, and the output capacitor is discharged until UVLO is reached. This means, if there is no supply voltage applied the output discharge function is also disabled. The transistor which is responsible of the discharge function, when turned on, operates like an equivalent  $120\Omega$  resistor, ensuring typically less than 10ms discharge time for 20uF output capacitance and a 3.3V output.

#### 7.3.3 Thermal Shutdown

The device goes into thermal shutdown once the junction temperature exceeds typically 140°C.

# Feature Description (continued)

#### 7.3.4 Softstart

To minimize inrush current and output voltage overshoot during start up, the device has a Softstart. At turn on, the input current raises monotonically until the output voltage reaches regulation. During Softstart, the input current follows the current ramp charging the internal Softstart capacitor. The device smoothly ramps up the input current bringing the output voltage to its regulated value even if a large capacitor is connected at the output.

The Softstart time is measured as the time from when the EN pin is asserted to when the output voltage has reached 90% of its nominal value. There is typically a 100µs delay time from when the EN pin is asserted to when the device starts the switching activity. The Softstart time depends on the load current, the input voltage, and the output capacitor. The Softstart time in boost mode is longer then the time in buck mode. The total typical Softstart time is 1ms.

The inductor current is able to increase and always assure a soft start unless a real short circuit is applied at the output.

#### 7.3.5 **Short Circuit Protection**

The TPS63024x provides short circuit protection to protect itself and the application. When the output voltage does not increase above 1.2V, the device assumes a short circuit at the output and limits the input current to 3Å.

#### 7.4 Device Functional Modes

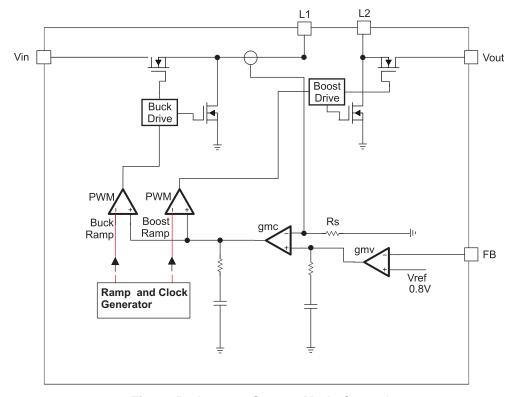

## 7.4.1 Control Loop Description

Figure 5. Average Current Mode Control

The controller circuit of the device is based on an average current mode topology. The average inductor current is regulated by a fast current regulator loop which is controlled by a voltage control loop. *Figure 5* shows the control loop.

The non inverting input of the transconductance amplifier, gmv, is assumed to be constant. The output of gmv defines the average inductor current. The inductor current is reconstructed by measuring the current through the high side buck MOSFET. This current corresponds exactly to the inductor current in boost mode. In buck mode the current is measured during the on time of the same MOSFET. During the off time, the current is reconstructed internally starting from the peak value at the end of the on time cycle. The average current and the feedback from the error amplifier gmv forms the correction signal gmc. This correction signal is compared to the buck and the boost sawtooth ramp giving the PWM signal. Depending on which of the two ramps the gmc output crosses either the Buck or the Boost stage is initiated. When the input voltage is close to the output voltage, one buck cycle is always followed by a boost cycle. In this condition, no more than three cycles in a row of the same mode are allowed. This control method in the buck-boost region ensures a robust control and the highest efficiency.

# **Device Functional Modes (continued)**

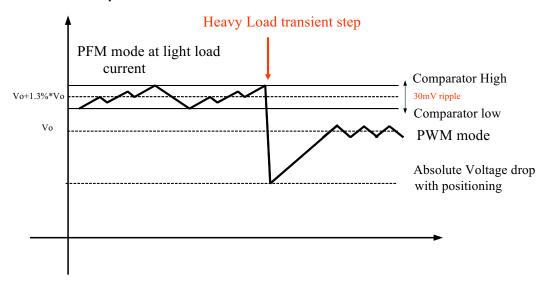

#### 7.4.2 Power Save Mode Operation

Figure 6. Power Save Mode Operation

Depending on the load current, in order to provide the best efficiency over the complete load range, the device works in PWM mode at load currents of approximately 350 mA or higher. At lighter loads, the device switches automatically into Power Save Mode to reduce power consumption and extend battery life. The PFM/PWM pin is used to select between the two different operation modes. To enable Power Save Mode, the PFM/PWM pin must be set low.

During Power Save Mode, the part operates with a reduced switching frequency and lowest supply current to maintain high efficiency. The output voltage is monitored with a comparator at every clock cycle by the thresholds comp low and comp high. When the device enters Power Save Mode, the converter stops operating and the output voltage drops. The slope of the output voltage depends on the load and the output capacitance. When the output voltage reaches the comp low threshold, at the next clock cycle the device ramps up the output voltage again, by starting operation. Operation can last for one or several pulses until the comp high threshold is reached. At the next clock cycle, if the load is still lower than about 350mA, the device switches off again and the same operation is repeated. Instead, if at the next clock cycle, the load is above 350mA, the device automatically switches to PWM mode.

In order to keep high efficiency in PFM mode, there is only one comparator active to keep the output voltage regulated. The AC ripple in this condition is increased, compared to the PWM mode. The amplitude of this voltage ripple in the worst case scenario is 50mV pk-pk, (typically 30mV pk-pk), with 20µF effective output capacitance. In order to avoid a critical voltage drop when switching from 0A to full load, the output voltage in PFM mode is typically 1.3% above the nominal value in PWM mode. This is called Dynamic Voltage Positioning and allows the converter to operate with a small output capacitor and still have a low absolute voltage drop during heavy load transients.

Power Save Mode is disabled by setting the PFM/PWM pin high.

# **Device Functional Modes (continued)**

#### 7.4.3 Current Limit

The current limit variation depends on the difference between the input and output voltage. The maximum current limit value is at the highest difference.

Given the curves provided in *Figure 8*, it is possible to calculate the output current reached in boost mode, using *Equation 1* and *Equation 2* and in buck mode using *Equation 3* and Equation 4.

Duty Cycle Boost

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

(1)

Output Current Boost

$$I_{OUT} = \eta \times I_{IN}(1-D)$$

(2)

Duty Cycle Buck

$$D = \frac{V_{OUT}}{V_{IN}}$$

(3)

Output Current Buck  $I_{OUT} = (\eta \times I_{IN}) / D$

where

- η = Estimated converter efficiency (use the number from the efficiency curves or 0.90 as an assumption)

- I<sub>IN</sub>= Minimum average input current (Figure 8)

#### 7.4.4 Supply and Ground

The TPS63024x provides two input pins (VIN and VINA) and two ground pins (PGND and GND).

The VIN pin supplies the input power, while the VINA pin provides voltage for the control circuits. A similar approach is used for the ground pins. GND and PGND are used to avoid ground shift problems due to the high currents in the switches. The reference for all control functions is the GND pin. The power switches are connected to PGND. Both grounds must be connected on the PCB at only one point, ideally, close to the GND pin.

# 7.4.5 Device Enable

The device starts operation when the EN pin is set high. The device enters shutdown mode when the EN pin is set low. In shutdown mode, the regulator stops switching, all internal control circuitry is switched off, and the load is disconnected from the input.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 8.1 Application Information

The TPS63024x are high efficiency, low quiescent current buck-boost converters suitable for application where the input voltage is higher, lower or equal to the output. Output currents can go as high as 1.5A in boost mode and as high as 3A in buck mode. The maximum average current in the switches is limited to a typical value of 3A.

# 8.2 Typical Application

Figure 7. 3.3-V Adjustable Version

#### 8.2.1 Design Requirements

The design guideline provides a component selection to operate the device within the recommended operating conditions.

Table 1 shows the list of components for the Application Characteristic Curves.

Table 1. Components for Application Characteristic Curves(1)

| REFERENCE | DESCRIPTION                   | MANUFACTURER              |

|-----------|-------------------------------|---------------------------|

|           | TPS63024                      | Texas Instruments         |

| L1        | 1 μH, 8.75A, 13mΩ, SMD        | XAL4020-102MEB, Coilcraft |

| C1        | 10 μF 6.3V, 0603, X5R ceramic | Standard                  |

| C2,C3     | 22 μF 6.3V, 0603, X5R ceramic | Standard                  |

| R1        | 560kΩ                         | Standard                  |

| R2        | 180kΩ                         | Standard                  |

(1) See Third-Party Products Discalimer

#### 8.2.2 Detailed Design Procedure

The first step is the selection of the output filter components. To simplify this process Table 2 outline possible inductor and capacitor value combinations.

#### 8.2.2.1 Output Filter Design

**Table 2. Matrix of Output Capacitor and Inductor Combinations**

|                                       |                                                    | •  |    |    |     |  |  |

|---------------------------------------|----------------------------------------------------|----|----|----|-----|--|--|

| NOMINAL                               | NOMINAL OUTPUT CAPACITOR VALUE [μF] <sup>(2)</sup> |    |    |    |     |  |  |

| INDUCTOR<br>VALUE [µH] <sup>(1)</sup> | 44                                                 | 47 | 66 | 88 | 100 |  |  |

| 0.680                                 |                                                    |    | +  | +  | +   |  |  |

| 1.0                                   | +(3)                                               | +  | +  | +  | +   |  |  |

| 1.5                                   |                                                    |    | +  | +  | +   |  |  |

- (1) Inductor tolerance and current de-rating is anticipated. The effective inductance can vary by 20% and -30%.

- (2) Capacitance tolerance and bias voltage de-rating is anticipated. The effective capacitance can vary by 20% and -50%.

- 3) Typical application. Other check mark indicates recommended filter combinations

#### 8.2.2.2 Inductor Selection

The inductor selection is affected by several parameter like inductor ripple current, output voltage ripple, transition point into Power Save Mode, and efficiency. See Table 3 for typical inductors.

Table 3. List of Recommended Inductors(1)

| INDUCTOR VALUE | COMPONENT SUPPLIER      | SIZE (LxWxH mm) | Isat/DCR                          |

|----------------|-------------------------|-----------------|-----------------------------------|

| 1 μΗ           | Coilcraft XAL4020-102ME | 4 X 4 X 2.10    | 4.5A/10mΩ                         |

| 1 μΗ           | Toko, DFE322512C        | 3.2 X 2.5 X 1.2 | $4.7A/34m\Omega$                  |

| 1 μH           | TDK, SPM4012            | 4.4 X 4.1 X 1.2 | 4.1A/38mΩ                         |

| 1 μH           | Wuerth, 74438334010     | 3 X 3 X 1.2     | $6.6\text{A}/42.10\text{m}\Omega$ |

| 0.6 μΗ         | Coilcraft XFL4012-601ME | 4 X 4 X 1.2     | 5A/17.40mΩ                        |

| 0.68µH         | Wuerth,744383340068     | 3 X 3 X 1.2     | 7.7A/36mΩ                         |

#### (1) See Third-Party Products Desclaimer

For high efficiencies, the inductor should have a low dc resistance to minimize conduction losses. Especially at high-switching frequencies, the core material has a high impact on efficiency. When using small chip inductors, the efficiency is reduced mainly due to higher inductor core losses. This needs to be considered when selecting the appropriate inductor. The inductor value determines the inductor ripple current. The larger the inductor value, the smaller the inductor ripple current and the lower the conduction losses of the converter. Conversely, larger inductor values cause a slower load transient response. To avoid saturation of the inductor, the peak current for the inductor in steady state operation is calculated using Equation 6. Only the equation which defines the switch current in boost mode is shown, because this provides the highest value of current and represents the critical current value for selecting the right inductor.

Duty Cycle Boost

$$D = \frac{V_{OUT} - V_{IN}}{V_{OUT}}$$

$$I_{PEAK} = \frac{Iout}{\eta \times (1 - D)} + \frac{Vin \times D}{2 \times f \times L}$$

(5)

where

- D =Duty Cycle in Boost mod

- f = Converter switching frequency (typical 2.5MHz)

- L = Inductor value

- $\eta$  = Estimated converter efficiency (use the number from the efficiency curves or 0.90 as an assumption)

- Note: The calculation must be done for the minimum input voltage which is possible to have in boost mode (6)

Calculating the maximum inductor current using the actual operating conditions gives the minimum saturation current of the inductor needed. It's recommended to choose an inductor with a saturation current 20% higher than the value calculated using *Equation 6*. Possible inductors are listed in *Table 3*.

#### 8.2.2.3 Capacitor Selection

#### 8.2.2.3.1 Input Capacitor

At least a  $10\mu F$  input capacitor is recommended to improve line transient behavior of the regulator and EMI behavior of the total power supply circuit. An X5R or X7R ceramic capacitor placed as close as possible to the VIN and PGND pins of the IC is recommended. This capacitance can be increased without limit. If the input supply is located more than a few inches from the TPS63024x converter additional bulk capacitance may be required in addition to the ceramic bypass capacitors. An electrolytic or tantalum capacitor with a value of 47  $\mu F$  is a typical choice.

#### 8.2.2.3.2 Output Capacitor

For the output capacitor, use of a small ceramic capacitors placed as close as possible to the VOUT and PGND pins of the IC is recommended. The recommended nominal output capacitance value is 20  $\mu$ F with a variance as outlined in *Table 2*.

There is also no upper limit for the output capacitance value. Larger capacitors causes lower output voltage ripple as well as lower output voltage drop during load transients.

# 8.2.2.4 Setting The Output Voltage

When the adjustable output voltage version TPS63024x is used, the output voltage is set by an external resistor divider. The resistor divider must be connected between VOUT, FB and GND. When the output voltage is regulated properly, the typical value of the voltage at the FB pin is 800mV. The current through the resistive divider should be about 10 times greater than the current into the FB pin. The typical current into the FB pin is  $0.1\mu$ A, and the voltage across the resistor between FB and GND, R<sub>2</sub>, is typically 800 mV. Based on these two values, the recommended value for R2 should be lower than  $180k\Omega$ , in order to set the divider current at  $4\mu$ A or higher. It is recommended to keep the value for this resistor in the range of  $180k\Omega$ . From that, the value of the resistor connected between VOUT and FB, R1, depending on the needed output voltage (V<sub>OUT</sub>), can be calculated using *Equation 7*:

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

(7)

#### 8.2.3 Application Curves

Figure 9. Efficiency vs Output Current

Submit Documentation Feedback

Copyright © 2014, Texas Instruments Incorporated

# 9 Power Supply Recommendations

The TPS63024x device family has no special requirements for its input power supply. The input power supply's output current needs to be rated according to the supply voltage, output voltage and output current of the TPS63024x.

# 10 Layout

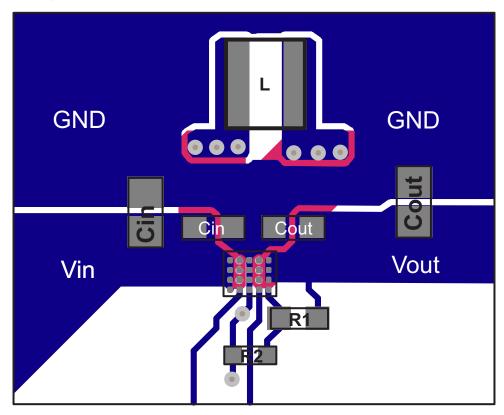

# 10.1 Layout Guidelines

The PCB layout is an important step to maintain the high performance of the TPS63024x devices.

- Place input and output capacitors as close as possible to the IC. Traces need to be kept short. Routing wide and direct traces to the input and output capacitor results in low trace resistance and low parasitic inductance.

- Use a common-power GND.

- The sense trace connected to FB is signal trace. Keep these traces away from L1 and L2 nodes.

# 10.2 Layout Example

Figure 30. TPS63024x Layout

# 11 Device and Documentation Support

# 11.1 Device Support

## 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

# 11.2 Documentation Support

## 11.2.1 Related Documentation

For related documentation see the following:

TPS63024EVM-553 User's Guide, TPS63024 High Current, High Efficiency Single Inductor Buck-Boost Converter, SLVUA24

#### 11.3 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 4. Related Links

| PARTS     | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|-----------|----------------|--------------|---------------------|---------------------|---------------------|

| TPS63024  | Click here     | Click here   | Click here          | Click here          | Click here          |

| TPS630241 | Click here     | Click here   | Click here          | Click here          | Click here          |

| TPS630242 | Click here     | Click here   | Click here          | Click here          | Click here          |

#### 11.4 Trademarks

All trademarks are the property of their respective owners.

#### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

23-May-2025

# **PACKAGING INFORMATION**

| Orderable part number | Status (1) | Material type | Package   Pins   | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|------------|---------------|------------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

| TPS630241YFFR         | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630241    |

| TPS630241YFFR.A       | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630241    |

| TPS630241YFFT         | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630241    |

| TPS630241YFFT.A       | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630241    |

| TPS630242YFFR         | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630242    |

| TPS630242YFFR.A       | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630242    |

| TPS630242YFFT         | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630242    |

| TPS630242YFFT.A       | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>630242    |

| TPS63024YFFR          | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>63024     |

| TPS63024YFFR.A        | Active     | Production    | DSBGA (YFF)   20 | 3000   LARGE T&R      | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>63024     |

| TPS63024YFFT          | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>63024     |

| TPS63024YFFT.A        | Active     | Production    | DSBGA (YFF)   20 | 250   SMALL T&R       | Yes             | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 125   | TPS<br>63024     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

# PACKAGE OPTION ADDENDUM

www.ti.com 23-May-2025

(4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

(5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

(6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com 28-Mar-2025

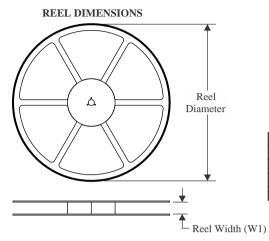

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS WHO SHOPE THE STATE OF THE

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

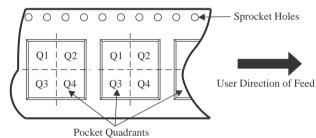

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS630241YFFR | DSBGA           | YFF                | 20 | 3000 | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

| TPS630241YFFT | DSBGA           | YFF                | 20 | 250  | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

| TPS630242YFFR | DSBGA           | YFF                | 20 | 3000 | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

| TPS630242YFFT | DSBGA           | YFF                | 20 | 250  | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

| TPS63024YFFR  | DSBGA           | YFF                | 20 | 3000 | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

| TPS63024YFFT  | DSBGA           | YFF                | 20 | 250  | 180.0                    | 8.4                      | 1.89       | 2.2        | 0.69       | 4.0        | 8.0       | Q1               |

www.ti.com 28-Mar-2025

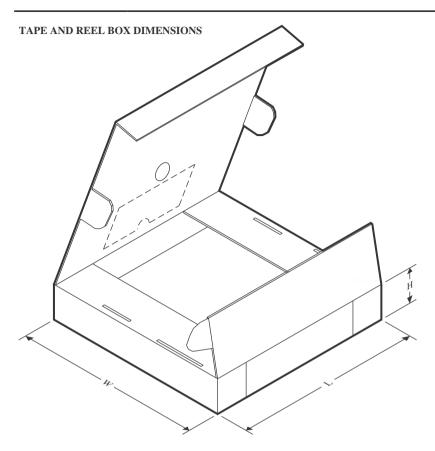

# \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS630241YFFR | DSBGA        | YFF             | 20   | 3000 | 182.0       | 182.0      | 20.0        |

| TPS630241YFFT | DSBGA        | YFF             | 20   | 250  | 182.0       | 182.0      | 20.0        |

| TPS630242YFFR | DSBGA        | YFF             | 20   | 3000 | 182.0       | 182.0      | 20.0        |

| TPS630242YFFT | DSBGA        | YFF             | 20   | 250  | 182.0       | 182.0      | 20.0        |

| TPS63024YFFR  | DSBGA        | YFF             | 20   | 3000 | 182.0       | 182.0      | 20.0        |

| TPS63024YFFT  | DSBGA        | YFF             | 20   | 250  | 182.0       | 182.0      | 20.0        |

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

NanoFree is a trademark of Texas Instruments.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated