TPS62736, TPS62737

SLVSBO4C -OCTOBER 2012-REVISED DECEMBER 2014

# TPS6273x Programmable Output Voltage Ultra-Low Power Buck Converter With Up to 50 mA / 200 mA Output Current

#### 1 Features

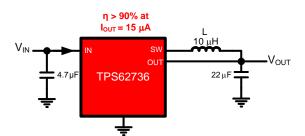

- Industry's Highest Efficiency at Low Output Currents: > 90% With I<sub>OUT</sub> = 15 μA

- Ultra-Low Power Buck Converter

- TPS62736 Optimized for 50-mA Output Current

- TPS62737 Optimized for 200-mA Output Current

- 1.3-V to 5-V Resistor Programmable Output Voltage Range

- 2-V to 5.5-V Input Operating Range

- 380-nA and 375-nA Quiescent Current During Active Operation for TPS62736 and TPS62737

- 10-nA Quiescent Current During Ship Mode Operation

- 2% Voltage Regulation Accuracy

- 100% Duty Cycle (Pass Mode)

- EN1 and EN2 Control

- Two Power-Off States:

- 1. Shipmode (Full Power-Off State)

- 2. Standby Mode Includes VIN\_OK Indication

- Input Power-Good Indication (VIN\_OK)

- Push-Pull Driver

- Resistor Programmable Threshold Level

# 2 Applications

- Ultra-Low Power Applications

- 2-Cell and 3-Cell Alkaline-Powered Applications

- Energy Harvesting

- Solar Chargers

- Thermal Electric Generator (TEG) Harvesting

- Wireless Sensor Networks (WSN)

- Low-Power Wireless Monitoring

- Environmental Monitoring

- Bridge and Structural Health Monitoring (SHM)

- Smart Building Controls

- Portable and Wearable Health Devices

- Entertainment System Remote Controls

#### 3 Description

The TPS6273x family provides a highly integrated ultra low power buck converter solution that is well suited for meeting the special needs of ultra-low power applications such as energy harvesting. The TPS6273x provides the system with an externally programmable regulated supply to preserve the overall efficiency of the power-management stage compared to a linear step-down converter. This regulator is intended to step-down the voltage from an energy storage element such as a battery or super capacitor to supply the rail to low-voltage electronics. The regulated output has been optimized to provide high efficiency across low-output currents (<10  $\mu$ A) to high currents (200 mA).

The TPS6273x integrates an optimized hysteretic controller for low-power applications. The internal circuitry uses a time-based sampling system to reduce the average quiescent current.

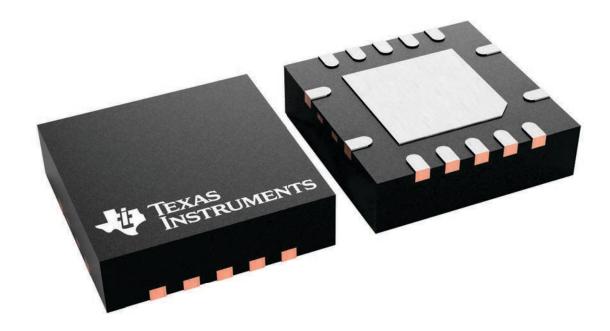

# **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TPS6273x    | VQFN (14) | 3.50 mm × 3.50 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

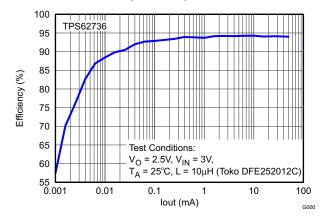

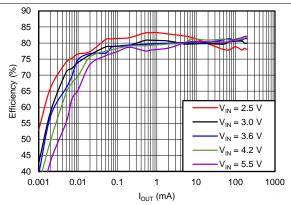

#### **Efficiency vs Output Current**

#### **Table of Contents**

| 1 | Features 1                           |    | 9.3 Feature Description              | 18               |

|---|--------------------------------------|----|--------------------------------------|------------------|

| 2 | Applications 1                       |    | 9.4 Device Functional Modes          | 20               |

| 3 | Description 1                        | 10 | Application and Implementation       | 21               |

| 4 | Revision History2                    |    | 10.1 Application Information         |                  |

| 5 | Description (continued)3             |    | 10.2 Typical Applications            | <mark>2</mark> 1 |

| 6 | Device Voltage Options3              | 11 | Power Supply Recommendations         | 28               |

| 7 | Pin Configuration and Functions 4    | 12 | Layout                               | 28               |

| 8 | Specifications5                      |    | 12.1 Layout Guidelines               | 28               |

| • | 8.1 Absolute Maximum Ratings         |    | 12.2 Layout Example                  | 28               |

|   | 8.2 Handling Ratings                 | 13 | Device and Documentation Support     | 29               |

|   | 8.3 Recommended Operating Conditions |    | 13.1 Device Support                  | 29               |

|   | 8.4 Thermal Information              |    | 13.2 Related Links                   | 29               |

|   | 8.5 Electrical Characteristics       |    | 13.3 Trademarks                      | 29               |

|   | 8.6 Typical Characteristics          |    | 13.4 Electrostatic Discharge Caution | 29               |

| 9 | Detailed Description                 |    | 13.5 Glossary                        | 29               |

|   | 9.1 Overview                         | 14 | Mechanical, Packaging, and Orderable | 20               |

|   | 9.2 Functional Block Diagram 18      |    | Information                          | 28               |

|   |                                      |    |                                      |                  |

# 4 Revision History

| Changes   | from Re    | vision I                                | R / luk | , 2013) | to F | Pavision  | C |

|-----------|------------|-----------------------------------------|---------|---------|------|-----------|---|

| Cilaliyes | II OIII NE | , , , , , , , , , , , , , , , , , , , , | D (July | / 2013/ | LO F | /6/12/011 | v |

**Page**

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section.

# Changes from Revision A (March 2013) to Revision B

Page

| • | Added the TPS62737 Pinout information                    | 4  |

|---|----------------------------------------------------------|----|

| • | Added graphs for TPS62737 to the Typical Characteristics | 13 |

|   | Added the TPS62737 Application Circuit.                  |    |

|   | Changed Figure 72                                        |    |

|   | Added Figure 73                                          |    |

#### Changes from Original (October 2012) to Revision A

Page

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

# 5 Description (continued)

To further assist users in the strict management of their energy budgets, the TPS6273x toggles the input power-good indicator to signal an attached microprocessor when the voltage on the input supply has dropped below a preset critical level. This signal is intended to trigger the reduction of load currents to prevent the system from entering an undervoltage condition. In addition, independent enable signals allow the system to control whether the converter is regulating the output, monitoring only the input voltage, or to shut down in an ultra-low quiescent sleep state.

The input power-good threshold and output regulator levels are programmed independently through external resistors.

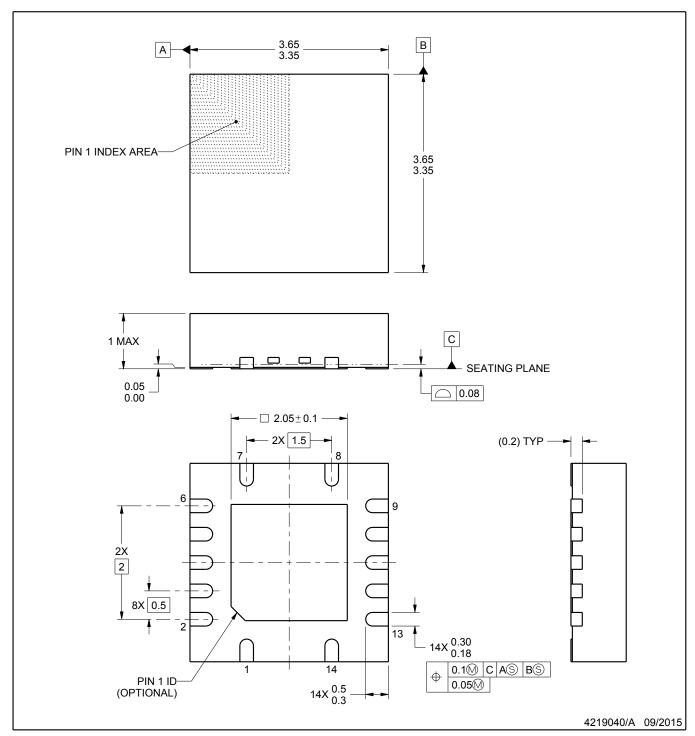

All the capabilities of TPS6273x are packed into a small footprint 14-lead 3.5-mm × 3.5-mm QFN package (RGY).

# 6 Device Voltage Options

| PART NO.                | OUTPUT VOLTAGE        | MAX OUTPUT CURRENT | INPUT UVLO |

|-------------------------|-----------------------|--------------------|------------|

| TPS62736 <sup>(1)</sup> | Resistor Programmable | 50 mA              | 2 V        |

| TPS62737 <sup>(1)</sup> | Resistor Programmable | 200 mA             | 2 V        |

<sup>(1)</sup> The RGY package is available in tape on reel. Add R suffix to order quantities of 3000 parts per reel, T suffix for 250 parts per reel.

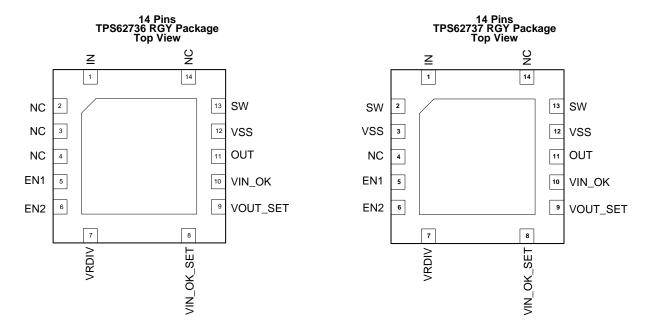

# 7 Pin Configuration and Functions

# **Pin Functions**

|             | PIN             |                 |        |                                                                                                                                                                   |  |  |

|-------------|-----------------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | TPS62736<br>RGY | TPS62737<br>RGY | TYPE   | DESCRIPTION                                                                                                                                                       |  |  |

| EN1         | 5               | 5               | Input  | Digital input for chip enable, standby, and ship-mode. EN1 = 1 sets ship mode                                                                                     |  |  |

| EN2         | 6               | 6               | Input  | independent of EN2. EN1=0, EN2 = 0 disables the buck converter and sets standby mode. EN1=0, EN2=1 enables the buck converter.  Do not leave either pin floating. |  |  |

| IN          | 1               | 1               | Input  | Input supply to the buck regulator                                                                                                                                |  |  |

| NC          | 2, 3, 4, 14     | 4, 14           | Input  | Connect to VSS                                                                                                                                                    |  |  |

| OUT         | 11              | 11              | Output | Step down (buck) regulator output                                                                                                                                 |  |  |

| SW          | 13              | 2, 13           | Input  | Inductor connection to switching node                                                                                                                             |  |  |

| Thermal Pad | 15              | 15              | Input  | Connect to VSS                                                                                                                                                    |  |  |

| VIN_OK      | 10              | 10              | Output | Push-pull digital output for power-good indicator for the input voltage. Pulled up to VIN pin.                                                                    |  |  |

| VIN_OK_SET  | 8               | 8               | Input  | Resistor divider input for VIN_OK threshold. Pull to VIN to disable. Do not leave pin floating.                                                                   |  |  |

| VOUT_SET    | 9               | 9               | Input  | Resistor divider input for VOUT regulation level                                                                                                                  |  |  |

| VRDIV       | 7               | 7               | Output | Resistor divider biasing voltage                                                                                                                                  |  |  |

| VSS         | 12              | 3, 12           | Input  | Ground connection for the device                                                                                                                                  |  |  |

# 8 Specifications

# 8.1 Absolute Maximum Ratings (1)(2)

over operating free-air temperature range (unless otherwise noted)

|          |                   |                                                                                      | MIN  | MAX | UNIT |

|----------|-------------------|--------------------------------------------------------------------------------------|------|-----|------|

|          | Pin voltage       | Input voltage range on IN, EN1, EN2, VRDIV, VIN_OK_SET, VOUT_SET, VIN_OK, OUT, SW,NC | -0.3 | 5.5 | V    |

| TPS62736 | Peak currents     | IN, OUT                                                                              |      | 100 | mA   |

| TPS62737 | Peak currents     | IN, OUT                                                                              |      | 370 | mA   |

| TJ       | Temperature range | Operating junction temperature range                                                 | -40  | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute—maximum—rated conditions for extended periods may affect device reliability.

# 8.2 Handling Ratings

|                    |                                                                                                                            |                                                                             | MIN  | MAX | UNIT |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------|-----|------|

| T <sub>stg</sub>   | Storage temperature rang                                                                                                   | ie e                                                                        | -65  | 150 | °C   |

|                    |                                                                                                                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | -1   | 1   | kV   |

| V <sub>(ESD)</sub> | Electrostatic discharge  Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2)  Machine Model (MM) | -500                                                                        | 500  | V   |      |

|                    |                                                                                                                            | Machine Model (MM)                                                          | -150 | 150 |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 8.3 Recommended Operating Conditions

|                                                        |                                                 | MIN | NOM | MAX | UNIT |

|--------------------------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| IN                                                     | IN voltage range                                | 2   |     | 5.5 | V    |

| 0                                                      | TPS62736 Input Capacitance                      | 4.7 |     |     |      |

| C <sub>IN</sub>                                        | TPS62737 Input Capacitance                      | 22  |     |     | μF   |

| C <sub>OUT</sub>                                       | Output Capacitance                              | 10  | 22  |     | μF   |

| R <sub>1</sub> +<br>R <sub>2</sub> +<br>R <sub>3</sub> | Total Resistance for setting reference voltage  |     | 13  |     | МΩ   |

|                                                        | TPS62736 Inductance                             | 4.7 | 10  |     |      |

|                                                        | TPS62737 Inductance                             | 10  |     |     | μH   |

| <b>-</b>                                               | TPS62736 Operating free air ambient temperature | -40 |     | 85  | 00   |

| T <sub>A</sub>                                         | TPS62737 Operating free air ambient temperature | -20 |     | 85  | °C   |

| TJ                                                     | Operating junction temperature                  | -40 |     | 105 | °C   |

#### 8.4 Thermal Information

|                  |                                                                                                                                                                     | TPS6273x |               |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|

|                  | Junction-to-ambient thermal resistance  Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter | RGY      | UNIT          |

|                  |                                                                                                                                                                     | 14 PINS  |               |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance                                                                                                                              | 33.7     |               |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance                                                                                                                           | 37.6     |               |

| $\theta_{JB}$    | Junction-to-board thermal resistance                                                                                                                                | 10.1     | 0 <b>0</b> AA |

| Ψлт              | Junction-to-top characterization parameter                                                                                                                          | 0.4      | °C/W          |

| ΨЈВ              | Junction-to-top characterization parameter 0.4                                                                                                                      |          |               |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance                                                                                                                        | 2.9      |               |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report (SPRA953).

<sup>(2)</sup> All voltage values are with respect to VSS/ground terminal

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 8.5 Electrical Characteristics

Over recommended ambient temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of  $V_{IN}$  = 4.2 V,  $V_{OUT}$  = 1.8 V External components,  $C_{IN}$  = 4.7  $\mu F$  for TPS62736 and 22  $\mu F$  for TPS62737,  $L_{BUCK}$  = 10  $\mu H$ ,  $C_{OUT}$  = 22  $\mu F$ .

|                         | PARAMETER                                                                                | TEST CONDITIONS                                                                                               | MIN   | TYP  | MAX                   | UNIT  |

|-------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------|------|-----------------------|-------|

| QUIESCENT               | CURRENTS                                                                                 |                                                                                                               |       |      |                       |       |

|                         | TPS62736 Buck enabled state (EN1 = 0, EN2 = 1)                                           |                                                                                                               |       | 380  | 550                   |       |

|                         | TPS62736 Buck disabled VIN_OK active state (EN1 = 0, EN2 = 0)                            |                                                                                                               |       | 340  | 520                   | nA    |

|                         | TPS62736 Ship mode state (EN1 = 1, EN2 = x)                                              | V 2V No load on V                                                                                             |       | 10   | 65                    |       |

| IQ                      | TPS62737 Buck enabled state (EN1 = 0, EN2 = 1)                                           | V <sub>IN</sub> = 2 V, No load on V <sub>OUT</sub>                                                            |       | 375  | 600                   |       |

|                         | TPS62737 Buck disabled VIN_OK active state (EN1 = 0, EN2 = 0)                            |                                                                                                               |       | 345  | 560                   | nA    |

|                         | TPS62737 Ship mode state (EN1 = 1, EN2 = x)                                              |                                                                                                               |       | 11   | 45                    |       |

| OUTPUT                  |                                                                                          |                                                                                                               |       |      |                       |       |

| $V_{BIAS}$              | Output regulation reference                                                              |                                                                                                               | 1.205 | 1.21 | 1.217                 | V     |

|                         | TPS62736 Output regulation (Spec does not include the resistor accuracy error)           | I <sub>OUT</sub> = 10 mA;<br>1.3 V < V <sub>OUT</sub> < 3.3 V                                                 | -2%   | 0%   | 2%                    |       |

|                         | TPS62737 Output regulation (Spec does not include the resistor accuracy error)           | I <sub>OUT</sub> = 100 mA;<br>1.3 V < V <sub>OUT</sub> < 3.3 V;                                               | -2%   | 0%   | 2%                    |       |

|                         | TPS62736 Output line regulation                                                          | I <sub>OUT</sub> = 100 μA;<br>V <sub>IN</sub> = 2.4 V to 5.5 V                                                |       | 0.01 |                       | 0//\/ |

|                         | TPS62737 Output line regulation                                                          | I <sub>OUT</sub> = 10 mA;<br>V <sub>IN</sub> = 2.3 V to 5.5 V                                                 |       | 0.31 |                       | %/V   |

| V <sub>OUT</sub>        | TPS62736 Output load regulation                                                          | $I_{OUT}$ = 100 $\mu$ A to 50 mA, $V_{IN}$ = 2.2 V                                                            |       | 0.01 |                       | %/mA  |

|                         | TPS62737 Output load regulation                                                          | I <sub>OUT</sub> = 100 μA to 200 mA,<br>V <sub>IN</sub> = 2.2 V; -20°C < T <sub>A</sub> < 85°C                |       | 0.01 |                       | %/mA  |

|                         | TPS62736 Output ripple                                                                   | $V_{IN}$ = 4.2V, $I_{OUT}$ = 1 mA, $C_{OUT}$ = 22 $\mu F$                                                     |       | 20   |                       | mVpp  |

|                         | TPS62737 Output ripple                                                                   | $V_{IN} = 4.2 \text{ V}, I_{OUT} = 1 \text{ mA},$<br>$C_{OUT} = 22 \mu\text{F}$                               |       | 40   |                       | mVpp  |

|                         | Programmable voltage range for output voltage threshold                                  | I <sub>OUT</sub> = 10 mA                                                                                      | 1.3   |      | V <sub>IN</sub> - 0.2 | V     |

|                         | TPS62736 Drop-out-voltage when $V_{\text{IN}}$ is less than $V_{\text{OUT}(\text{SET})}$ | $V_{IN} = 2.1 \text{ V}, V_{OUT(SET)} = 2.5 \text{ V},$ $I_{OUT} = 10 \text{ mA}, 100\% \text{ duty cycle}$   |       | 24   | 30                    | mV    |

| $V_{DO}$                | TPS62737 Drop-out-voltage when $V_{\text{IN}}$ is less than $V_{\text{OUT}(\text{SET})}$ | $V_{IN} = 2.1 \text{ V}, V_{OUT(SET)} = 2.5 \text{ V}, \\ I_{OUT} = 100 \text{ mA}, 100\% \text{ duty cycle}$ |       | 180  | 220                   | mV    |

|                         | Startup time with EN1 low and EN2 transition to high                                     | TPS62736, C <sub>OUT</sub> = 22 μF                                                                            |       | 400  |                       | μs    |

| <sup>T</sup> START-STBY | (Standby Mode)                                                                           | TPS62737, C <sub>OUT</sub> = 22 μF                                                                            |       | 300  |                       | μs    |

| t <sub>START-SHIP</sub> | Startup time with EN2 high and EN1 transition from high to low (Ship Mode)               | C <sub>OUT</sub> = 22 μF                                                                                      |       | 100  |                       | ms    |

# **Electrical Characteristics (continued)**

Over recommended ambient temperature range, typical values are at  $T_A$  = 25°C. Unless otherwise noted, specifications apply for conditions of  $V_{IN}$  = 4.2 V,  $V_{OUT}$  = 1.8 V External components,  $C_{IN}$  = 4.7  $\mu F$  for TPS62736 and 22  $\mu F$  for TPS62737,  $L_{BUCK}$  = 10  $\mu H$ ,  $C_{OUT}$  = 22  $\mu F$ .

|                                                                                     | PARAMETER                                                | TEST CONDITIONS                                                                                         | MIN                   | TYP  | MAX | UNIT |

|-------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|------|-----|------|

| POWER SW                                                                            | тсн                                                      |                                                                                                         |                       |      |     |      |

| D                                                                                   | TPS62736 High-side switch ON resistance                  | V <sub>IN</sub> = 3 V                                                                                   |                       | 2.4  | 3   | Ω    |

|                                                                                     | TPS62736 Low-side switch ON resistance                   | V <sub>IN</sub> = 3 V                                                                                   |                       | 1.1  | 1.5 | Ω    |

| K <sub>DS(on)</sub>                                                                 | TPS62737 High-side switch ON resistance                  | V <sub>IN</sub> = 2.1 V                                                                                 |                       | 1.8  | 2.2 | Ω    |

|                                                                                     | TPS62737 Low-side switch ON resistance                   | V <sub>IN</sub> = 2.1 V                                                                                 |                       | 0.9  | 1.3 | Ω    |

|                                                                                     | TPS62736 Cycle-by-cycle current limit                    | 2.4 V < V <sub>IN</sub> < 5.25 V;<br>1.3 V < V <sub>OUT</sub> < 3.3 V                                   | 68                    | 86   | 100 | mA   |

| I <sub>LIM</sub>                                                                    | TPS62737 Cycle-by-cycle current limit                    | 2.4 V < V <sub>IN</sub> < 5.25 V;<br>1.3 V < V <sub>OUT</sub> < 3.3 V;<br>-20°C < T <sub>A</sub> < 85°C | 295                   | 340  | 370 | mA   |

| f <sub>SW</sub>                                                                     | Max switching frequency                                  |                                                                                                         |                       | 2    |     | MHz  |

| INPUT                                                                               |                                                          |                                                                                                         |                       |      |     |      |

| V <sub>IN-UVLO</sub>                                                                | Input under voltage protection                           | V <sub>IN</sub> falling                                                                                 | 1.91                  | 1.95 | 2   | V    |

| V <sub>IN-OK</sub>                                                                  | Input power-good programmable voltage range              |                                                                                                         | 2                     |      | 5.5 | V    |

| V                                                                                   | TPS62736 Accuracy of V <sub>IN-OK</sub> setting          | V :                                                                                                     | -2%                   |      | 2%  |      |

| fsw INPUT VIN-UVLO VIN-OK VIN-OK-ACC VIN-OK-HYS VIN_OK-OH VIN_OK-OL EN1 and EN2 VIH | TPS62737 Accuracy of V <sub>IN-OK</sub> setting          | V <sub>IN</sub> increasing                                                                              | -3%                   |      | 3%  |      |

| V <sub>IN-OK-HYS</sub>                                                              | Fixed hysteresis on VIN_OK threshold, OK_HYST            | V <sub>IN</sub> increasing                                                                              |                       | 40   |     | mV   |

| V <sub>IN_OK-OH</sub>                                                               | V <sub>IN-OK</sub> output high threshold voltage         | Load = 10 µA                                                                                            | V <sub>IN</sub> - 0.2 |      |     | V    |

| V <sub>IN_OK-OL</sub>                                                               | V <sub>IN-OK</sub> output low threshold voltage          |                                                                                                         |                       |      | 0.1 | V    |

| EN1 and EN                                                                          | 2                                                        |                                                                                                         | •                     |      |     |      |

| V <sub>IH</sub>                                                                     | Voltage for EN High setting. Relative to V <sub>IN</sub> | V 42V                                                                                                   | V <sub>IN</sub> - 0.2 |      |     | V    |

| V <sub>IL</sub>                                                                     | Voltage for EN Low setting                               | V <sub>IN</sub> = 4.2 V                                                                                 |                       |      | 0.2 | V    |

#### 8.6 Typical Characteristics

Table 1. Table of Graphs for TPS62736

| Unless otherwise      | noted, graphs were taken using Figure 62 v | with L = Toko 10 μH DFE252012C | FIGURE    |

|-----------------------|--------------------------------------------|--------------------------------|-----------|

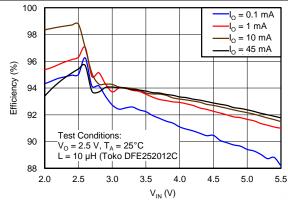

|                       | V 25 V Efficiency                          | vs Output Current              | Figure 1  |

|                       | V <sub>O</sub> = 2.5 V Efficiency          | vs Input Voltage               | Figure 2  |

| _                     | V 4.9.V.Efficiency                         | vs Output Current              | Figure 3  |

| η                     | V <sub>O</sub> = 1.8 V Efficiency          | vs Input Voltage               | Figure 4  |

|                       | V <sub>O</sub> = 1.3 V Efficiency          | vs Output Current              | Figure 5  |

|                       | V <sub>O</sub> = 1.3 V Eniciency           | vs Input Voltage               | Figure 6  |

|                       |                                            | vs Output Current              | Figure 7  |

|                       | $V_0 = 2.5 \text{ V}$                      | vs Input Voltage               | Figure 8  |

|                       |                                            | vs Temperature                 | Figure 9  |

|                       |                                            | vs Output Current              | Figure 10 |

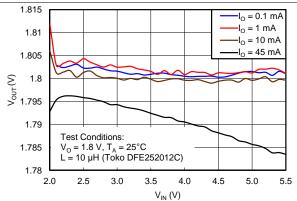

| V <sub>OUT</sub> (DC) | V <sub>O</sub> = 1.8 V                     | vs Input Voltage               | Figure 11 |

|                       |                                            | vs Temperature                 | Figure 12 |

|                       |                                            | vs Output Current              | Figure 13 |

|                       | $V_0 = 1.3 \text{ V}$                      | vs Input Voltage               | Figure 14 |

|                       |                                            | vs Temperature                 | Figure 15 |

|                       | V <sub>O</sub> = 2.5 V                     |                                | Figure 16 |

| OUT MAX (DC)          | V <sub>O</sub> = 1.8 V                     | vs Input Voltage               | Figure 17 |

|                       | V <sub>O</sub> = 1.3 V                     |                                | Figure 18 |

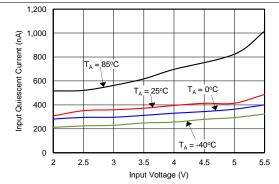

|                       | EN1 = 1, EN2 = 0 (Ship Mode)               |                                | Figure 19 |

| nput IQ               | EN1 = 0, EN2 = 0 (Standby Mode)            | vs Input Voltage               | Figure 20 |

|                       | EN1 = 0, EN2 = 1 (Active Mode)             |                                | Figure 21 |

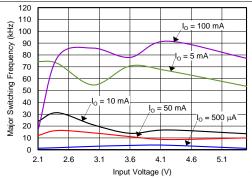

| Puritohing Fraguency  | V 25 V                                     | vs Output Current              | Figure 23 |

| Switching Frequency   | V <sub>O</sub> = 2.5 V                     | vs Input Voltage               | Figure 24 |

| Output Bianla         | V 25 V                                     | vs Output Current              | Figure 25 |

| Output Ripple         | V <sub>O</sub> = 2.5 V                     | vs Input Voltage               | Figure 26 |

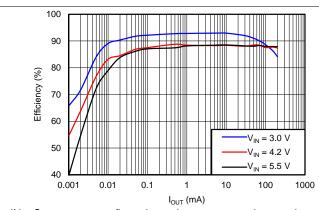

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 1. Efficiency vs Output Current,  $V_{OUT} = 2.5 \text{ V}$

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 2. Efficiency vs Input Voltage,  $V_{OUT} = 2.5 \text{ V}$

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 3. Efficiency vs Output Current, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

$\operatorname{OUT}$  = sourcemeter configured as current source to sink current and  $\operatorname{VCOMP}$  >  $\operatorname{VOUT}$

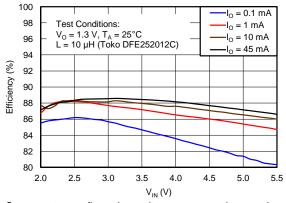

Figure 5. Efficiency vs Output Current, V<sub>OUT</sub> = 1.3 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 4. Efficiency vs Input Voltage, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 6. Efficiency vs Input Voltage, V<sub>OUT</sub> = 1.3 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

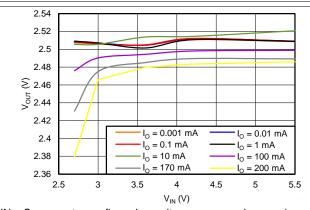

Figure 7. Output Voltage vs Output Current. V<sub>OUT</sub> = 2.5 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 8. Output Voltage vs Input Voltage,  $V_{OUT} = 2.5 \text{ V}$

Submit Documentation Feedback

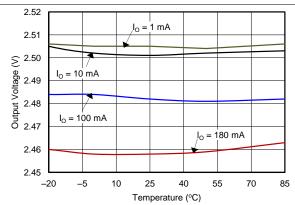

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Thermal stream provided temperature variation

Figure 9. Output Voltage vs Temperature,  $V_{OUT} = 2.5 \text{ V}$

IN = Sourcemeter configured as voltage source and measuring

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 11. Output Voltage vs Input Voltage, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

${\sf OUT}$  = sourcemeter configured as current source to sink current and  ${\sf VCOMP}$  >  ${\sf VOUT}$

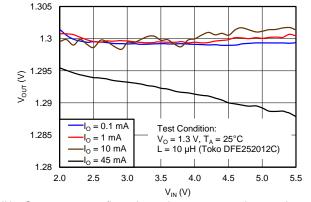

Figure 13. Output Voltage vs Output Current, V<sub>OUT</sub> = 1.3 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

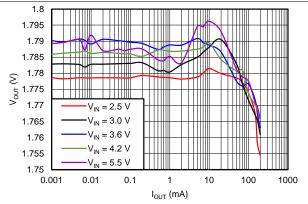

Figure 10. Output Voltage vs Output Current, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

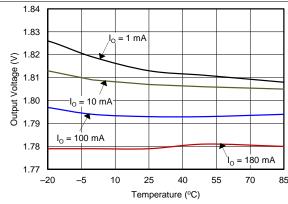

Thermal stream provided temperature variation

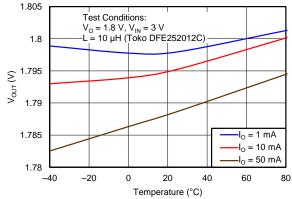

Figure 12. Output Voltage vs Temperature, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 14. Output Voltage vs Input Voltage, V<sub>OUT</sub> = 1.3 V

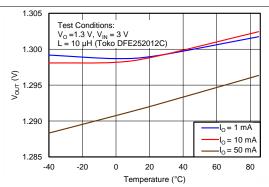

VOUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Thermal stream provided temperature variation

Figure 15. Output Voltage vs Temperature, V<sub>OUT</sub> = 1.3 V

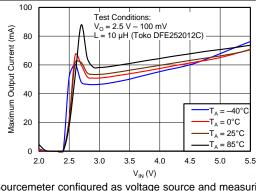

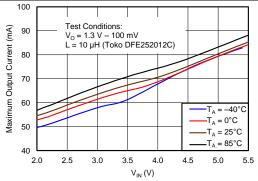

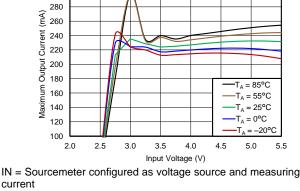

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

Figure 16. Maximum Output Current vs Input Voltage,  $V_{OUT} = 2.5 \text{ V}$

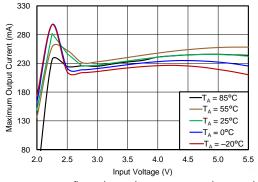

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

Figure 17. Maximum Output Current vs Input Voltage,  $V_{OUT} = 1.8 \text{ V}$

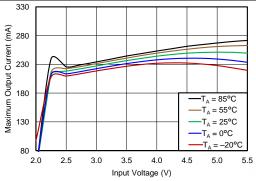

IN = Sourcemeter configured as voltage source and measuring current

${\sf OUT}$  = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

Figure 18. Maximum Output Current vs Input Voltage,  $\label{eq:Vout} V_{OUT} = 1.3 \ V$

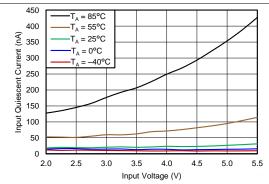

IN = Sourcemeter configured as voltage source and measuring current

OUT = open; EN1 = high; EN2 = x

Thermal stream provided temperature variation

Figure 19. Input Quiescent Current vs Input Voltage Ship Mode

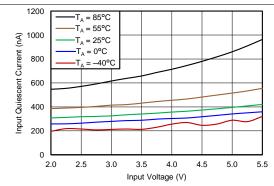

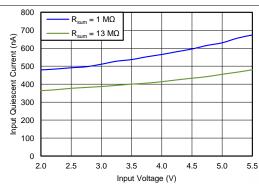

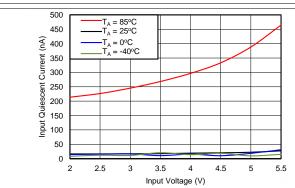

IN = Sourcemeter configured as voltage source and measuring current

OUT = open; EN1 = EN2 = low

Thermal stream provided temperature variation

Figure 20. Input Quiescent Current vs Input Voltage Standby Mode

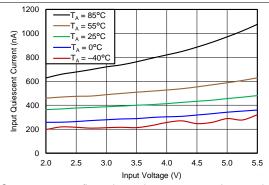

OUT = sourcemeter configured as voltage source > VOUT to prevent switching

Thermal stream provided temperature variation

Figure 21. Input Quiescent Current vs Input Voltage Active Mode

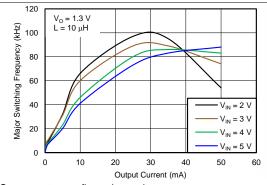

IN = Sourcemeter configured as voltage source

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 23. Major Switching Frequency vs Output Current

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as voltage source > VOUT to prevent switching

Thermal stream provided temperature variation

Figure 22. Input Quiescent Current vs Input Voltage Active Mode where  $R_{\text{SUM}}$  = R1 + R2 + R3

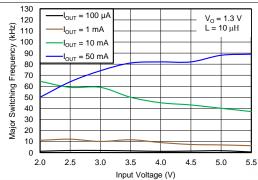

IN = Sourcemeter configured as voltage source

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 24. Major Switching Frequency vs Input Voltage

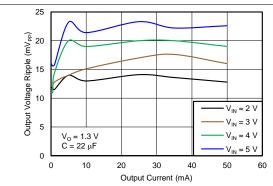

IN = Sourcemeter configured as voltage source

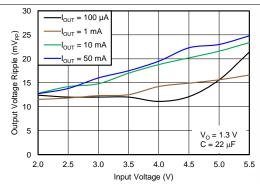

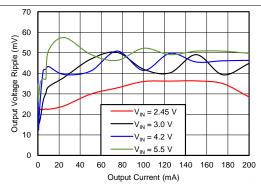

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Scope probe with small ground lead used to measure ripple across COUT

Figure 25. Output Voltage Ripple vs Output Current

IN = Sourcemeter configured as voltage source

$\ensuremath{\mathsf{OUT}}$  = sourcemeter configured as current source to sink current and VCOMP > VOUT

Scope probe with small ground lead used to measure ripple across COUT

Figure 26. Output Voltage Ripple vs Input Voltage

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

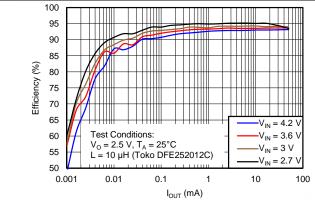

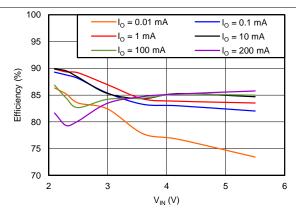

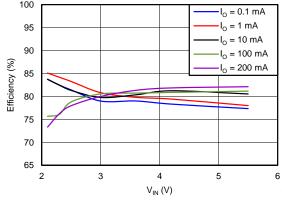

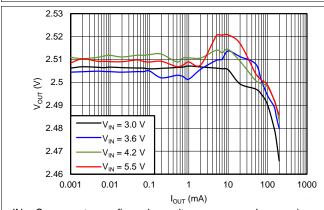

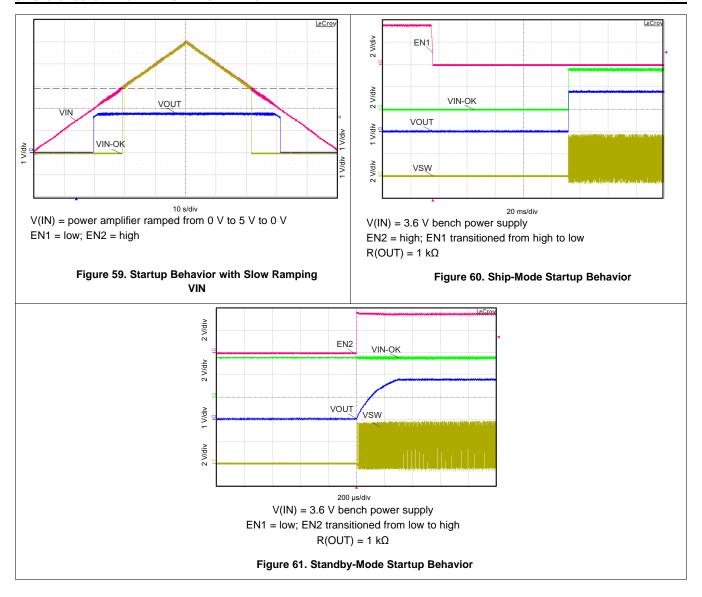

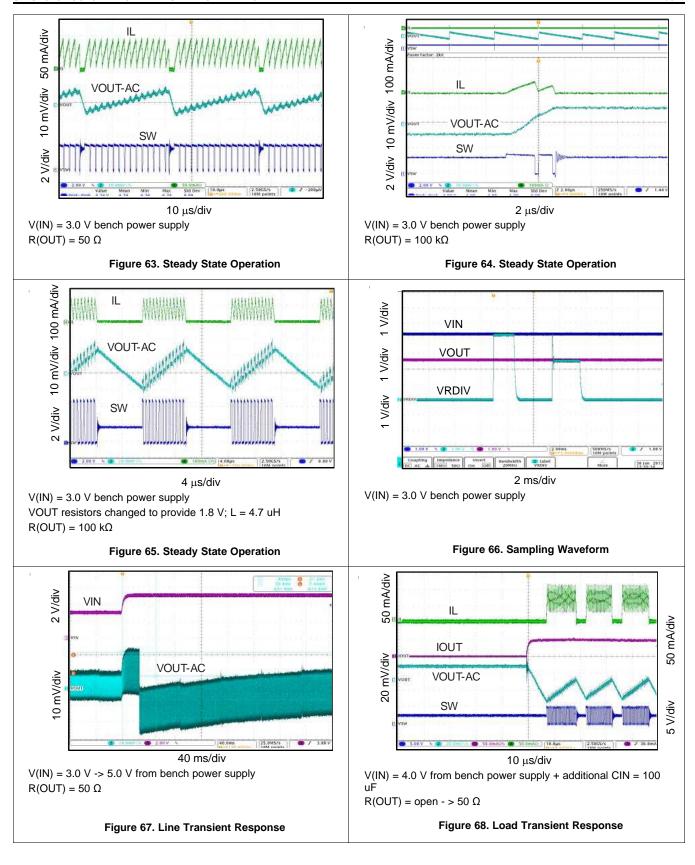

#### Table 2. Table of Graphs for TPS62737

| Unless otherwise no       | oted, graphs were taken using Figure 52 v | vith L = Toko 10 μH DFE252012C | FIGURE    |

|---------------------------|-------------------------------------------|--------------------------------|-----------|

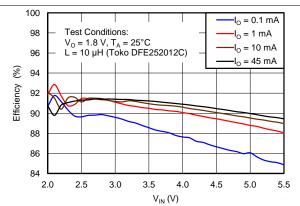

|                           | V 2 F V F#isionsv                         | vs Output Current              | Figure 27 |

|                           | V <sub>O</sub> = 2.5 V Efficiency         | vs Input Voltage               | Figure 28 |

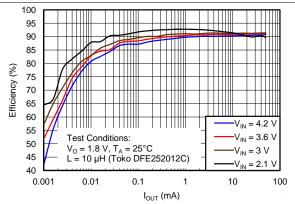

| n                         | V 4.9.V.Efficiency                        | vs Output Current              | Figure 29 |

| η                         | V <sub>O</sub> = 1.8 V Efficiency         | vs Input Voltage               | Figure 30 |

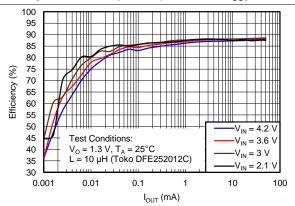

|                           | V 4.2.V.Efficiency                        | vs Output Current              | Figure 31 |

|                           | V <sub>O</sub> = 1.3 V Efficiency         | vs Input Voltage               | Figure 32 |

|                           |                                           | vs Output Current              | Figure 33 |

|                           | $V_0 = 2.5 \text{ V}$                     | vs Input Voltage               | Figure 33 |

|                           |                                           | vs Temperature                 | Figure 35 |

|                           |                                           | vs Output Current              | Figure 36 |

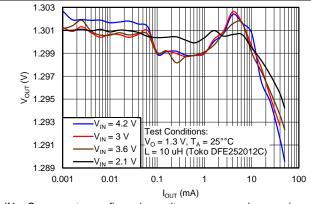

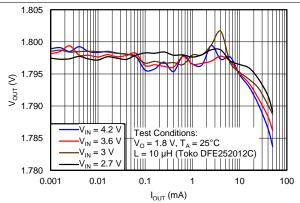

| V <sub>OUT</sub> (DC)     | V <sub>O</sub> = 1.8 V                    | vs Input Voltage               | Figure 37 |

|                           |                                           | vs Temperature                 | Figure 38 |

|                           |                                           | vs Output Current              | Figure 39 |

|                           | V <sub>O</sub> = 1.3 V                    | vs Input Voltage               | Figure 40 |

|                           |                                           | vs Temperature                 | Figure 41 |

|                           | V <sub>O</sub> = 2.5 V                    |                                | Figure 42 |

| I <sub>OUT</sub> MAX (DC) | V <sub>O</sub> = 1.8 V                    | vs Input Voltage               | Figure 43 |

|                           | V <sub>O</sub> = 1.3 V                    |                                | Figure 44 |

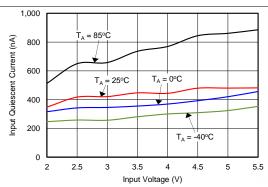

|                           | EN1 = 1, EN2 = 0 (Ship Mode)              |                                | Figure 45 |

| Input IQ                  | EN1 = 0, EN2 = 0 (Standby Mode)           | vs Input Voltage               | Figure 46 |

|                           | EN1 = 0, EN2 = 1 (Active Mode)            |                                | Figure 47 |

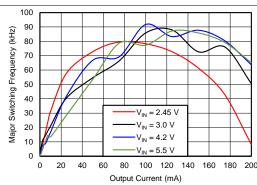

| Cuitabina Fraguenay       | V 4.9.V                                   | vs Output Current              | Figure 48 |

| Switching Frequency       | V <sub>O</sub> = 1.8 V                    | vs Input Voltage               | Figure 49 |

| Outrost Diamia            | V 4.0.V                                   | vs Output Current              | Figure 51 |

| Output Ripple             | V <sub>O</sub> = 1.8 V                    | vs Input Voltage               | Figure 51 |

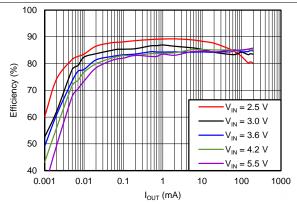

$\ensuremath{\mathsf{IN}}=\ensuremath{\mathsf{Source}}$  measuring current

$\ensuremath{\mathsf{OUT}}$  = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 27. Efficiency vs Output Current,  $V_{OUT} = 2.5 \text{ V}$

$\ensuremath{\mathsf{IN}}=\ensuremath{\mathsf{Source}}$  measuring current

$\mbox{OUT} = \mbox{sourcemeter}$  configured as current source to sink current and VCOMP > VOUT

Figure 28. Efficiency vs Input Voltage,  $V_{OUT} = 2.5 \text{ V}$

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 29. Efficiency vs Output Current, V<sub>OUT</sub> = 1.8 V

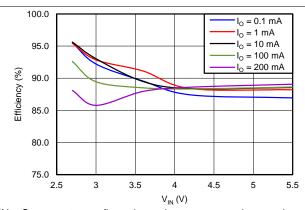

IN = Sourcemeter configured as voltage source and measuring current

${\sf OUT}$  = sourcemeter configured as current source to sink current and  ${\sf VCOMP}$  >  ${\sf VOUT}$

Figure 31. Efficiency vs Output Current,  $V_{OUT} = 1.3 \text{ V}$

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 30. Efficiency vs Input Voltage, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 32. Efficiency vs Input Voltage, V<sub>OUT</sub> = 1.3 V

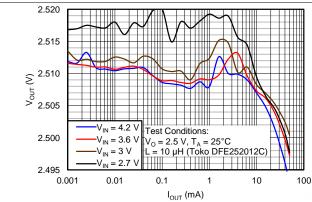

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

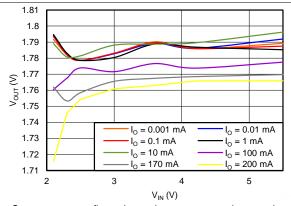

Figure 33. Output Voltage vs Output Current. V<sub>OUT</sub> = 2.5 V

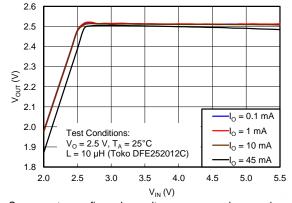

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 34. Output Voltage vs Input Voltage,  $V_{OUT} = 2.5 \text{ V}$

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

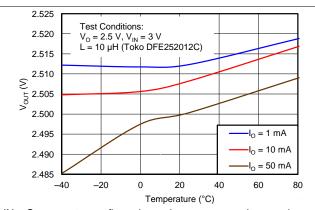

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Thermal stream provided temperature variation

Figure 35. Output Voltage vs Temperature, V<sub>OUT</sub> = 2.5 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 37. Output Voltage vs Input Voltage, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

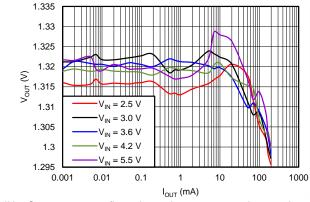

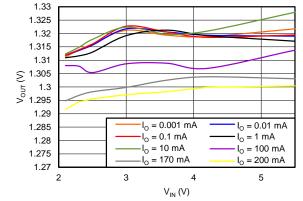

Figure 39. Output Voltage vs Output Current, V<sub>OUT</sub> = 1.3 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 36. Output Voltage vs Output Current, V<sub>OUT</sub> = 1.8 V

$\ensuremath{\mathsf{IN}}=\ensuremath{\mathsf{Source}}$  measuring current

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Thermal stream provided temperature variation

Figure 38. Output Voltage vs Temperature, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring current

$\mbox{OUT} = \mbox{sourcemeter}$  configured as current source to sink current and VCOMP > VOUT

Figure 40. Output Voltage vs Input Voltage, V<sub>OUT</sub> = 1.3 V

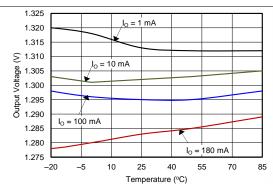

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Thermal stream provided temperature variation

Figure 41. Output Voltage vs Temperature, V<sub>OUT</sub> = 1.3 V

OUT = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

300

Figure 42. Maximum Output Current vs Input Voltage V<sub>OUT</sub> = 2.5 V

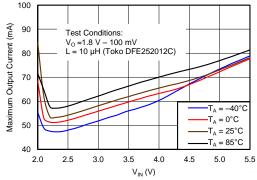

IN = Sourcemeter configured as voltage source and measuring

OUT = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

Figure 43. Maximum Output Current vs Input Voltage, V<sub>OUT</sub> = 1.8 V

IN = Sourcemeter configured as voltage source and measuring

OUT = sourcemeter configured as current source to increasingly sink current until V(OUT) < VOUT - 100 mV

Thermal stream provided temperature variation

Figure 44. Maximum Output Current vs Input Voltage, V<sub>OUT</sub> = 1.3 V

IN = Sourcemeter configured as voltage source and measuring current

OUT = open; EN1 = high; EN2 = x

Thermal stream provided temperature variation

Figure 45. Input Quiescent Current vs Input Voltage Ship Mode

IN = Sourcemeter configured as voltage source and measuring current

OUT = open; EN1 = EN2 = low

Thermal stream provided temperature variation

Figure 46. Input Quiescent Current vs Input Voltage Standby Mode

Submit Documentation Feedback

Copyright © 2012-2014, Texas Instruments Incorporated

OUT = sourcemeter configured as voltage source > VOUT to prevent switching

Thermal stream provided temperature variation

# Figure 47. Input Quiescent Current vs Input Voltage Active Mode

IN = Sourcemeter configured as voltage source

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 49. Major Switching Frequency vs Input Voltage

IN = Sourcemeter configured as voltage source

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Figure 48. Major Switching Frequency vs Output Current

IN = Sourcemeter configured as voltage source

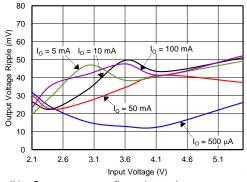

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Scope probe with small ground lead used to measure ripple across COUT

Figure 50. Output Voltage Ripple vs Output Current

IN = Sourcemeter configured as voltage source

OUT = sourcemeter configured as current source to sink current and VCOMP > VOUT

Scope probe with small ground lead used to measure ripple across COUT

Figure 51. Output Voltage Ripple vs Input Voltage

Submit Documentation Feedback

# 9 Detailed Description

#### 9.1 Overview

The TPS6273x family provides a highly integrated ultra low power buck converter solution that is well suited for meeting the special needs of ultra-low power applications such as energy harvesting. The TPS6273x provides the system with an externally programmable regulated supply in order to preserve the overall efficiency of the power-management stage compared to a linear step down converter. This regulator is intended to step-down the voltage from an energy storage element such as a battery or super capacitor in order to supply the rail to low-voltage electronics. The regulated output has been optimized to provide high efficiency across low-output currents (<10 µA) to high currents (200 mA).

The TPS6273x integrates an optimized hysteretic controller for low-power applications. The internal circuitry uses a time-based sampling system to reduce the average quiescent current.

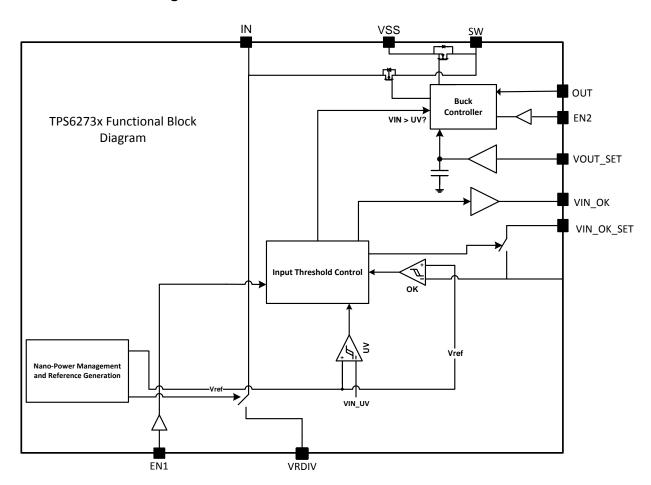

#### 9.2 Functional Block Diagram

# 9.3 Feature Description

#### 9.3.1 Step-Down (Buck) Converter Operation

The buck regulator in the TPS6273x takes input power from VIN, steps it down and provides a regulated voltage at the OUT pin. It employs pulse frequency modulation (PFM) control to regulate the voltage close to the desired reference voltage. The reference voltage is set by the user programmed resistor divider. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is controlled to maintain high efficiency of the converter across a wide input current range. The TPS62736 converter delivers an average output current of 50mA with a peak inductor current of 100 mA. The TPS62737 converter delivers an average output current of 200 mA with a peak inductor current of 370 mA. The buck regulator is disabled when

#### Feature Description (continued)

the voltage on VIN reaches the UVLO condition. The UVLO level is continuously monitored. The buck regulator continues to operate in pass (100% duty cycle) mode, passing the input voltage to the output, as long as VIN is greater than UVLO and less than VIN minus I<sub>OUT</sub> times R<sub>DS(on)</sub> of the high-side FET (that is, VIN - I<sub>OUT</sub> x R<sub>DS(on)</sub>-Hs). In order to save power from being dissipated through other ICs on this supply rail while allowing for a faster wake up time, the buck regulator can be enabled and disabled through the EN2 pin for systems that desire to completely turn off the regulated output.

#### 9.3.2 Programming OUT Regulation Voltage and VIN\_OK

To set the proper output-regulation voltage and input voltage power-good comparator, the external resistors must be carefully selected. Figure 62 illustrates an application diagram which uses the minimal resistor count for setting both VOUT and VIN\_OK. Note that VBIAS is nominally 1.21 V per the electrical specification table. Referring to Figure 52, the OUT DC set point is given by Equation 1.

$$VOUT = VBIAS\left(\frac{R_1 + R_2 + R_3}{R_1 + R_2}\right) \tag{1}$$

The VIN\_OK setting is given by Equation 2.

$$VIN\_OK = VBIAS\left(\frac{R_1 + R_2 + R_3}{R_1}\right)$$

(2)

The sum of the resistors is recommended to be no greater than 13 M $\Omega$ , that is, RSUM = R1 + R2 + R3 = 13 M $\Omega$ . Due to the sampling operation of the output resistors, lowering RSUM only increases quiescent current slightly as can be seen in Figure 22. Higher resistors may result in poor output voltage regulation and/or input voltage power-good threshold accuracies due to noise pickup through the high-impedance pins or reduction of effective resistance due to parasitic resistance created from board assembly residue. See *Layout* for more details.

If it is preferred to separate the VOUT and VIN\_OK resistor strings, two separate strings of resistors could be used as shown in Figure 62. The OUT DC set point is then given by Equation 3.

$$VOUT = VBIAS\left(\frac{R_3 + R_4}{R_4}\right)$$

(3)

The VIN\_OK setting is then given by Equation 4.

$$VIN\_OK = VBIAS\left(\frac{R_1 + R_2}{R_1}\right)$$

(4)

If it is preferred to disable the VIN\_OK setting, the VIN\_OK\_SET pin can be tied to VIN. To set VOUT in this configuration, use Equation 3. To tighten the DC set point accuracy, use external resistors with better than 1% resistor tolerance. Because output voltage ripple has a large effect on input line regulation and the output load regulation, using a larger output capacitor will improve both line and load regulation.

#### 9.3.3 Nano-Power Management and Efficiency

Copyright © 2012-2014, Texas Instruments Incorporated

The high efficiency of the TPS6273x is achieved through the proprietary Nano-Power management circuitry and algorithm. This feature essentially samples and holds all references in order to reduce the average quiescent current. That is, the internal circuitry is only active for a short period of time and then off for the remaining period of time at the lowest feasible duty cycle. A portion of this feature can be observed in Figure 66 where the VRDIV node is monitored. Here, the VRDIV node provides a connection to the input (larger voltage level) and generates the output reference (lower-voltage level) for a short period of time. The divided down value of input voltage is compared to VBIAS and the output voltage reference is sampled and held to get the VOUT\_SET point. Because this biases a resistor string, the current through these resistors is only active when the Nano-Power management circuitry makes the connection — hence, reducing the overall quiescent current due to the resistors. This process repeats every 64 ms. Similarly, the VIN\_OK level is monitored every 64 ms, as shown in Figure 55.

#### **Feature Description (continued)**

The efficiency versus output current and efficiency versus input voltage are plotted for three different output voltages for both the TPS62736 and TPS62737 devices in *Typical Characteristics*. All data points were captured by averaging the overall input current. This must be done, due to the periodic biasing scheme implemented through the Nano-Power management circuitry. The input current efficiency data was gathered using a source meter set to average over at least 25 samples and at the highest accuracy sampling rate. Each data point takes a long period of time to gather in order to properly measure the resulting input current when calculating the efficiency.

#### 9.4 Device Functional Modes

#### 9.4.1 Enable Controls

There are two enable pins implemented in the TPS6273x in order to maximize the flexibility of control for the system. The EN1 pin is considered to be the chip enable. If EN1 is set to a 1 then the entire chip is placed into ship mode. If EN1 is 0 then the chip is enabled. EN2 enables and disables the switching of the buck converter. When EN2 is low, the internal circuitry remains ON and the VIN\_OK indicator still functions. This can be used to disable down-stream electronics in case of a low input-supply condition. When EN2 is 1, the buck converter operates normally.

**Table 3. Enable Functionality Table**

| EN1 PIN | EN2 PIN | FUNCTIONAL STATE                                                                   |

|---------|---------|------------------------------------------------------------------------------------|

| 0       | 0       | Partial standby mode. Buck switching converter is off, but VIN_OK indication is on |

| 0       | 1       | Buck mode and VIN_OK enabled                                                       |

| 1       | Х       | Full standby mode. Switching converter and VIN_OK indication is off (ship mode)    |

#### 9.4.2 Startup Behavior

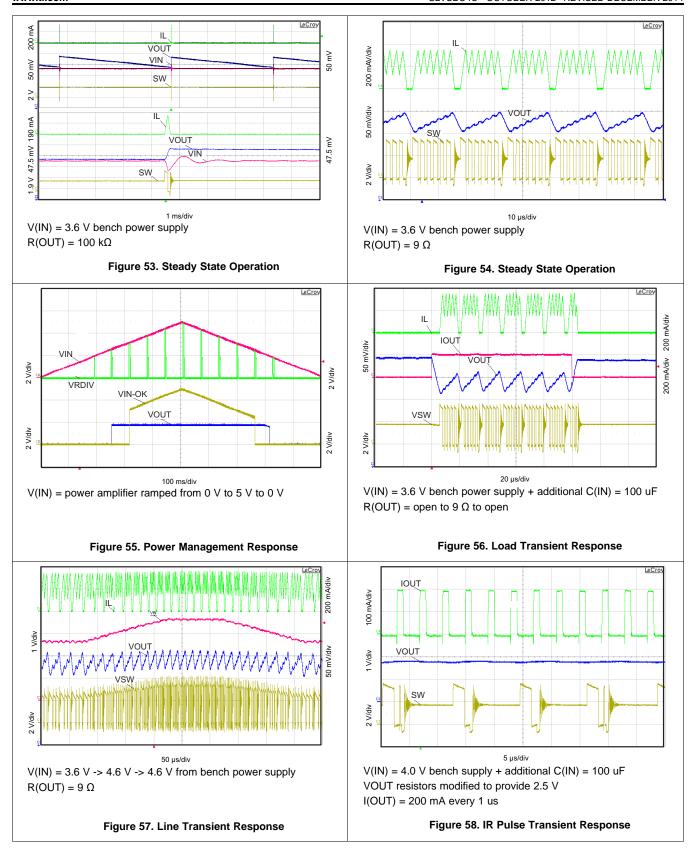

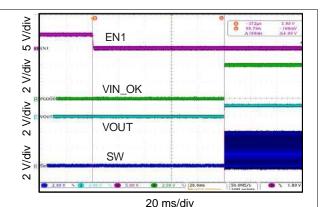

The TPS6273x has two startup responses: 1) from the ship-mode state (EN1 transitions from high to low), and 2) from the standby state (EN2 transitions from low to high). The first startup response out of the ship-mode state has the longest time duration due to the internal circuitry being disabled. This response is shown in Figure 70 for the TPS62736 and Figure 60 for the TPS62737. The startup time takes approximately 100 ms due to the internal Nano-Power management circuitry needing to complete the 64 ms sample and hold cycle.

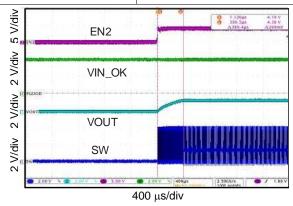

Startup from the standby state is shown in Figure 71 for the TPS62736 and Figure 61 for the TPS62737. This response is much faster due to the internal circuitry being pre-enabled. The startup time from this state is entirely dependent on the size of the output capacitor. The larger the capacitor, the longer it will take to charge during startup. The TPS6273x can startup into a prebiased output voltage.

# 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 10.1 Application Information

The TPS62736/7 are step down DC-DC converters. Their low quiescent currents make them ideal for battery powered systems that are operated at low duty cycles in order to achieve low total power levels.

#### 10.2 Typical Applications

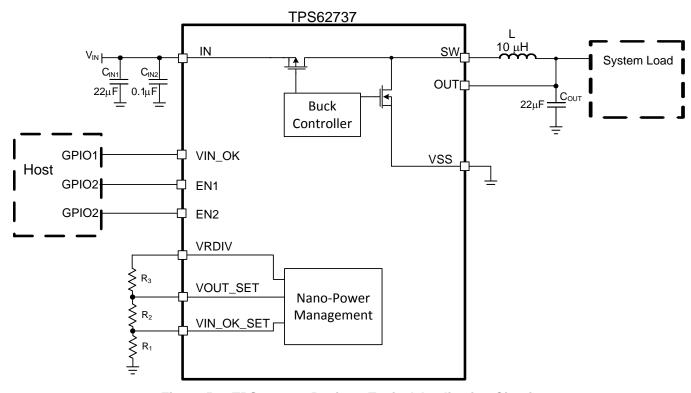

#### 10.2.1 TPS62737 3-Resistor Typical Application Circuit

Figure 52. TPS62737 3-Resistor Typical Application Circuit

#### 10.2.1.1 Design Requirements

A 1.8-V, up to 200 mA regulated power rail is needed. The VIN\_OK comparator should indicate when the input voltage drops below 2.9 V. No large load transients are expected.

#### 10.2.1.2 Detailed Design Procedure

The recommended 10- $\mu$ H inductor (TOKO DFE252012C) and 22- $\mu$ F input capacitor are used. Since no large load transients are expected, the minimum 22- $\mu$ F output capacitor is used. Had a large load transient been expected, we would have sized the capacitor using ITRAN = COUT x  $\Delta$ VOUT /  $\Delta$ TIME where  $\Delta$ VOUT is amount of VOUT droop allowed for the time of the transient.

First set RSUM = R1 + R2 + R3 = 13 M $\Omega$  then solve Equation 2 for R1 = VBIAS x RSUM / VIN\_OK = 1.21 V x 13 M $\Omega$  / 2.9 V = 5.42 M $\Omega$   $\rightarrow$  5.49 M $\Omega$  as the closest 1 % resistor.

Submit Documentation Feedback

#### **Typical Applications (continued)**

Then solve Equation 2 for R2 = VBIAS x RSUM / VOUT - R1 = 1.21 V x 13 M $\Omega$  / 1.8 V - 5.42 M $\Omega$  = 3.32 M $\Omega$   $\rightarrow$  3.4 M $\Omega$  as the closest 1% resistor.

Finally R3 = RSUM - R1 - R2 = 13 M $\Omega$  - 5.42 M $\Omega$  - 3.32 M $\Omega$  = 4.26 M $\Omega$   $\rightarrow$  4.32 M $\Omega$  as the closest 1% resistor.

These values yield VOUT = 1.79 V and VIN\_OK threshold = 2.91 V.

If using 4 resistors, see *Resistor Selection* for guidance on sizing the resistors.

#### 10.2.1.2.1 Inductor Selection

The internal-control circuitry is designed to control the switching behavior with a nominal inductance of 10  $\mu$ H  $\pm$  20%. The saturation current of the inductor' should be at least 25% higher than the maximum cycle-by-cycle current limit per the electrical specs table ( $I_{LIM}$ ) in order to account for load transients. Because this device is a hysteretic controller, it is a naturally stable system (single order transfer function). However, the smaller the inductor value is, the faster the switching currents are. The speed of the peak current detect circuit sets the inductor of the TPS62736 lower bound to 4.7  $\mu$ H. When using a 4.7  $\mu$ H, the peak inductor current will increase when compared to that of a 10- $\mu$ H inductor. The steady-state operation with a 4.7- $\mu$ H inductor with a 50-mA load for the TPS62736 is shown in Figure 65.

A list of inductors recommended for this device is shown in Table 4.

INDUCTANCE (µH) **DIMENSIONS (mm) PART NUMBER MANUFACTURER** 2.0 x 2.5 x 1.2 DFE252012C-H-100M 10 Toko 10 4.0 x 4.0 x 1.7 LPS4018-103M Coilcraft 4.7 (TPS62736 only) 2.0 x 2.5 x 1.2 DFE252012R-H-4R7M Toko

**Table 4. Recommended Inductors**

#### 10.2.1.2.2 Output Capacitor Selection

The output capacitor is chosen based on transient response behavior and ripple magnitude. The lower the capacitor value, the larger the ripple will become and the larger the droop will be in the case of a transient response. It is recommended to use at least a 22-µF output capacitor for most applications.

#### 10.2.1.2.3 Input Capacitor Selection

The bulk input capacitance is recommended to be a minimum of 4.7  $\mu$ F  $\pm$  20% for the TPS62736 and 22  $\mu$ F  $\pm$  20% for the TPS62737. This bulk capacitance is used to suppress the lower frequency transients produced by the switching converter. There is no upper bound to the input-bulk capacitance. In addition, a high-frequency bypass capacitor of 0.1  $\mu$ F is recommended in parallel with the bulk capacitor. The high-frequency bypass is used to suppress the high-frequency transients produced by the switching converter.

#### 10.2.1.2.4 Resistor Selection

Equation 1 to Equation 4 are the equations for sizing the external resistors to set the VIN\_OK threshold and VOUT regulation value. The spreadsheet at SLVC489 can help size the external resistors.

#### 10.2.1.3 Application Curves

See efficiency, line regulation, and load regulation curves at Figure 30, Figure 37, and Figure 36.

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

#### 10.2.2 TPS62736 4-Resistor Typical Application Circuit

Figure 62. TPS62736 4-Resistor Typical Application Circuit

#### 10.2.2.1 Design Requirements

A 2.5-V, up to 50-mA regulated power rail is needed. The VIN\_OK comparator should indicate when the input voltage drops below 2.9 V. No large load transients are expected.

#### 10.2.2.2 Detailed Design Procedure

The recommended 10- $\mu$ H inductor (TOKO DFE252012C) and 4.7- $\mu$ F input capacitor are used. Since no large load transients are expected, the minimum 22- $\mu$ F output capacitor is used. Had a large load transient been expected, we would have sized the capacitor using ITRAN = COUT x  $\Delta$ VOUT /  $\Delta$ TIME where  $\Delta$ VOUT is amount of VOUT droop allowed for the time of the transient.

First set RSUM = R1 + R2 = R3 + R4 = 13 M $\Omega$  then solve Equation 4 for R1 = VBIAS x RSUM / VIN\_OK = 1.21 V x 13 M $\Omega$  / 2.9 V = 5.42 M $\Omega$   $\rightarrow$  5.36 M $\Omega$  as the closest 1 % resistor.

Then R2 = RSUM - R1 = 13 M $\Omega$  - 5.42 M $\Omega$  = 7.58 M $\Omega$   $\rightarrow$  7.5 M $\Omega$  as the closest 1% resistor.

Solve Equation 3 for R4 = VBIAS x RSUM / VOUT = 1.21 V x 13 M $\Omega$  / 2.5 V = 6.29 M $\Omega$   $\rightarrow$  6.34 M $\Omega$  as the closest 1% resistor.

Finally R3 = RSUM - R3 = 13 M $\Omega$  - 6.29 M $\Omega$  = 6.71 M $\Omega$   $\rightarrow$  6.81 M $\Omega$  as the closest 1% resistor.

These values yield VOUT = 2.51 V and VIN\_OK threshold = 2.90 V.

If using 3 resistors, see *Resistor Selection* for guidance on sizing the resistors.

#### 10.2.2.3 Application Curves

See efficiency, load regulation and line regulation graphs at Figure 1, Figure 7 and Figure 8 respectively.

Submit Documentation Feedback

Copyright © 2012–2014, Texas Instruments Incorporated

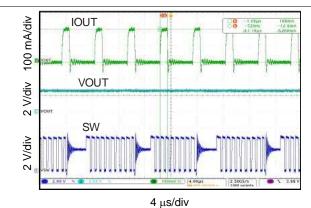

V(IN) = 4.0 V from bench power supply + additional CIN = 100 uF

I(OUT) = 200 mA every 1us

V(IN) = 4.0 V from bench power supply VOUT resistors modified to provide 1.8 V EN2 = high, EN1 transitioned high to low

Figure 70. Ship-Mode Startup Behavior

V(IN) = 4.0 V from bench power supply VOUT resistors modified to provide 1.8 V EN1 = low, EN2 transitioned low to high

Figure 71. Standby-Mode Startup Behavior

# 11 Power Supply Recommendations

The TPS62736 / 7 ICs require a low impedance power source (e.g. battery, wall adapter) capable of providing between 2.0 V and 5.5 V and up to 100 mA / 370 mA respectively. When the voltage at IN is less than or equal to VOUT, the IC stops switching, turns on the high side FET and provides VOUT = VIN - ILOAD x RDS(on)-HighSideFET.

#### 12 Layout

#### 12.1 Layout Guidelines

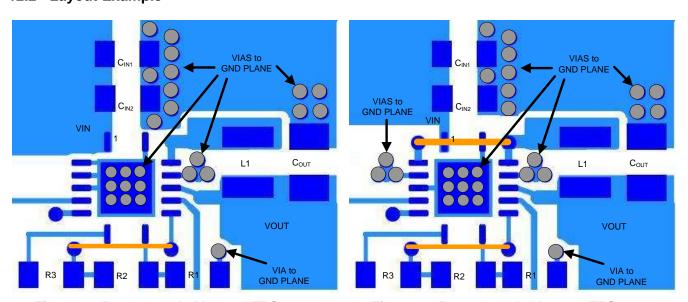

To minimize switching noise generation, the step-down converter (buck) power stage external components must be carefully placed. The most critical external component for a buck power stage is its input capacitor. The bulk input capacitor ( $C_{\text{IN1}}$ ) and high frequency decoupling capacitor ( $C_{\text{IN2}}$ ) must be placed as close as possible between the power stage input (IN pin 1) and ground (VSS pin 12). Next, the inductor (L1) must be placed as close as possible between the switching node (SW pin 13) and the output voltage (OUT pin 11). Finally, the output capacitor ( $C_{\text{OUT}}$ ) should be placed as close as possible between the output voltage (OUT pin 11) and GND (VSS pin 12). In the diagram below, the input and output capacitor grounds are connected to VSS pin 12 through vias to the bottom-layer ground plane of the PCB.

To minimize noise pickup by the high impedance voltage setting nodes (VIN\_OK\_SET pin 8 and VOUT\_SET pin 9), the external resistors (R1, R2 and R3) should be placed so that the traces connecting the midpoints of the string are as short as possible. In the diagram below, the connection to VOUT\_SET is by a bottom layer trace.

The remaining pins are either NC pins, that should be connected to the PowerPAD™ as shown below, or digital signals with minimal layout restrictions.

In order to maximize efficiency at light load, the use of voltage level setting resistors > 1 M $\Omega$  is recommended. However, during board assembly, contaminants such as solder flux and even some board cleaning agents can leave residue that may form parasitic resistors across the physical resistors and/or from one end of a resistor to ground, especially in humid, fast airflow environments. This can result in the voltage regulation and threshold levels changing significantly from those expected per the installed resistor values. Therefore, it is highly recommended that no ground planes be poured near the voltage setting resistors. In addition, the boards must be carefully cleaned, possibly rotated at least once during cleaning, and then rinsed with de-ionized water until the ionic contamination of that water is well above 50 M $\Omega$ . If this is not feasible, then it is recommended that the sum of the voltage setting resistors be reduced to at least 5 times below the measured ionic contamination.

#### 12.2 Layout Example

Figure 72. Recommended Layout, TPS62736

Figure 73. Recommended Layout, TPS62737

Submit Documentation Feedback

# 13 Device and Documentation Support

#### 13.1 Device Support

#### 13.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 13.2 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

Table 5. Related Links

| PARTS    | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT & COMMUNITY |

|----------|----------------|--------------|---------------------|---------------------|---------------------|

| TPS62736 | Click here     | Click here   | Click here          | Click here          | Click here          |

| TPS62737 | Click here     | Click here   | Click here          | Click here          | Click here          |

#### 13.3 Trademarks

PowerPAD is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 13.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 13.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

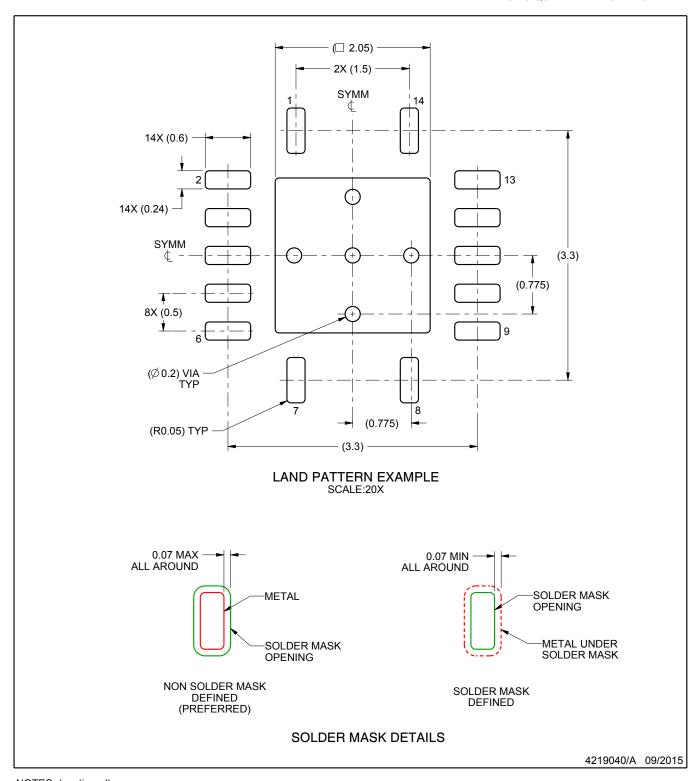

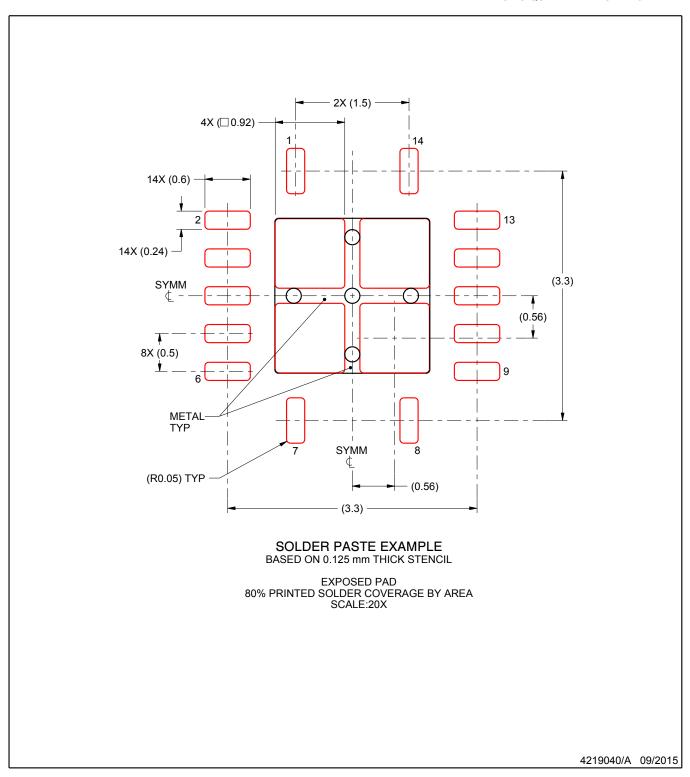

# 14 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

www.ti.com

24-Jul-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|-----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                 |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                 |                       |      | (4)           | (5)                 |              |              |

| TPS62736RGYR          | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYR.A        | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYR.B        | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | -    | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYRG4        | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYRG4.A      | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYT          | Active | Production    | VQFN (RGY)   14 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62736RGYT.A        | Active | Production    | VQFN (RGY)   14 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 62736        |

| TPS62737RGYR          | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 62737        |

| TPS62737RGYR.A        | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 62737        |

| TPS62737RGYR.B        | Active | Production    | VQFN (RGY)   14 | 3000   LARGE T&R      | -    | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 62737        |

| TPS62737RGYT          | Active | Production    | VQFN (RGY)   14 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 62737        |

| TPS62737RGYT.A        | Active | Production    | VQFN (RGY)   14 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 105   | 62737        |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No. RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 24-Jul-2025

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 18-Jun-2025

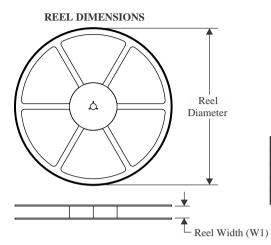

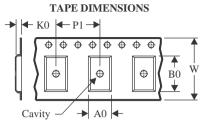

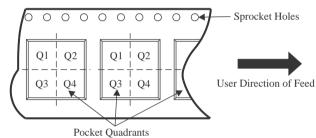

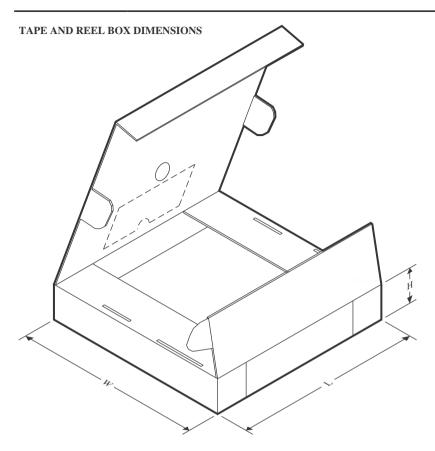

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |