**TPS546A24S** SLUSF28 - NOVEMBER 2023

# TPS546A24S 2.95-V to 18-V, 10-A, Up to 4 × Stackable, Synchronous SWIFT™ Step-Down Converter with PMBus® and Extended Write Protection

#### 1 Features

- Integrated extended security feature

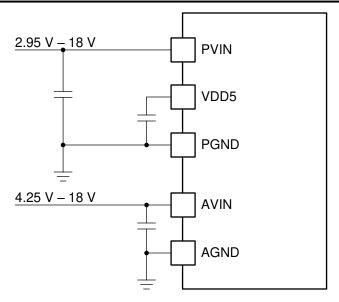

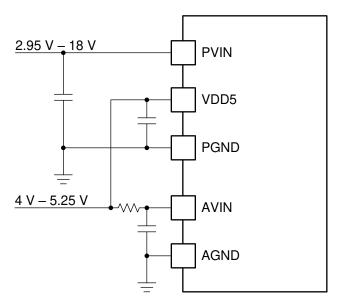

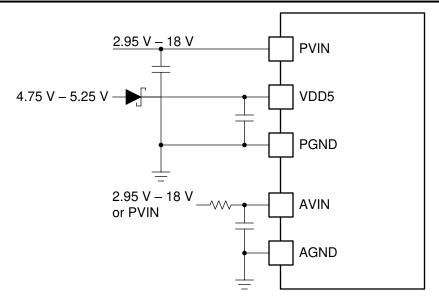

- Split rail support: 2.95-V to 18-V PVIN; 2.95-V to 18-V AVIN (4-V<sub>IN</sub> VDD5 for switching)

- Integrated 5.5-m $\Omega$ /1.8-m $\Omega$  MOSFETs

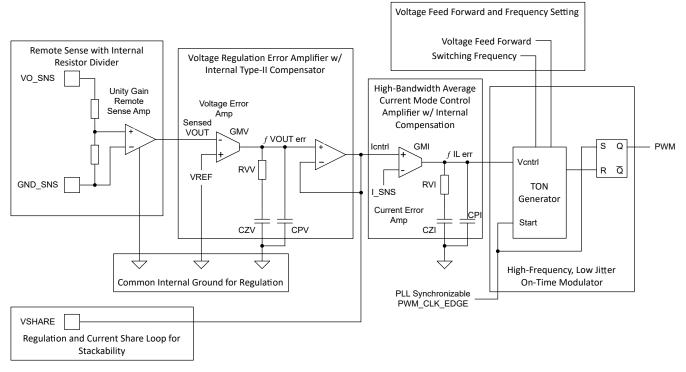

- Average current mode control with selectable internal compensation

- 2 ×, 3 ×, 4 × stackable with current sharing up to 40 A, supporting a single address per output

- Selectable 0.5-V to 5.5-V output through pin strap or 0.25-V to 5.5-V using PMBus VOUT COMMAND

- Extensive PMBus command set with telemetry for V<sub>OUT</sub>, I<sub>OUT</sub>, and internal die temperature

- Differential remote sensing with an internal FB divider for  $< 1\% V_{OUT}$  error, -40°C to +150°C T<sub>J</sub>

- AVS and margining capabilities through PMBus

- MSEL pins pin programming PMBus defaults

- 12 selectable switching frequencies from 225 kHz to 1.5 MHz (8 pin strap options)

- Frequency sync in, sync out

- Supports prebiased output

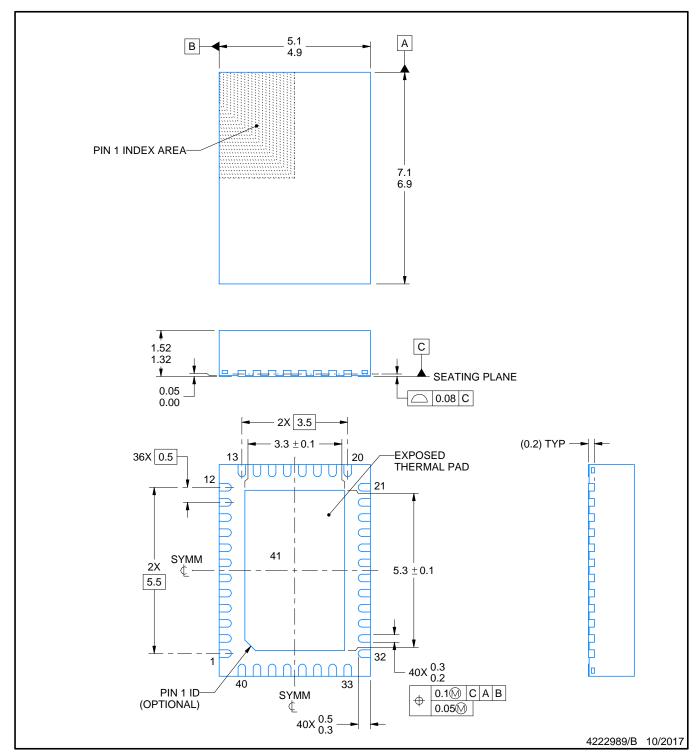

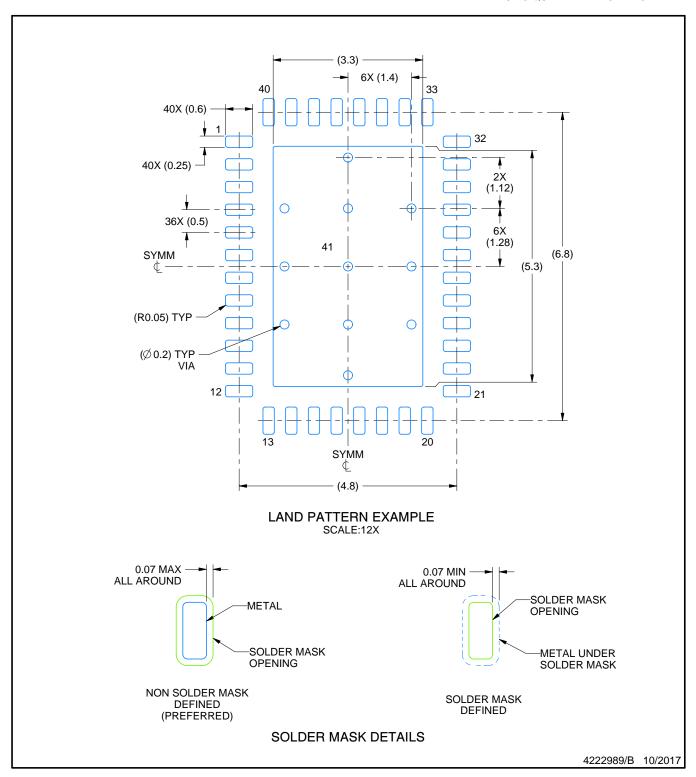

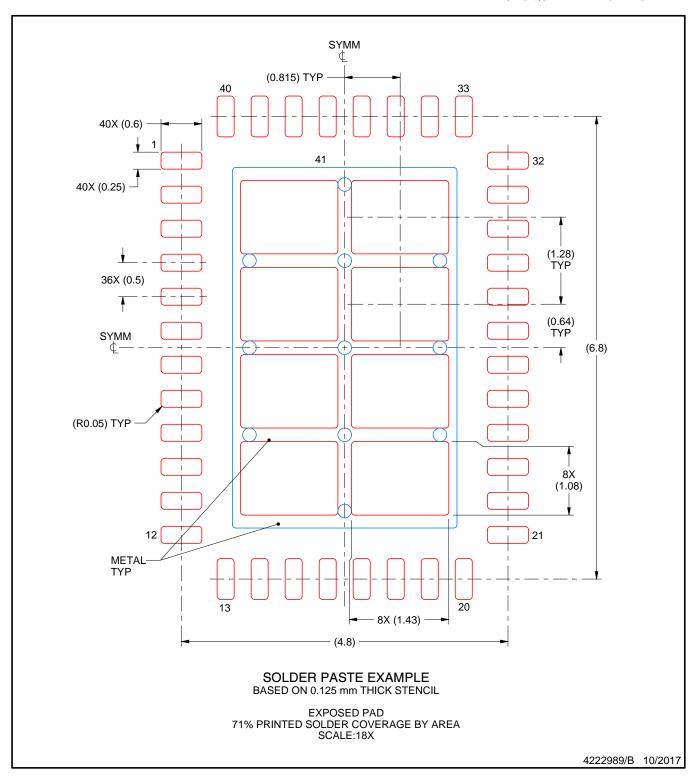

- 7-mm × 5-mm × 1.5-mm, 40-pin QFN

- Drop-in compatible with TPS546A24A

- Create a Custom Design Using the TPS546A24S with WEBENCH® Power Designer

## 2 Applications

- Data center switches, rack servers

- Active antenna system, remote radio and baseband unit

- Automated test equipment, CT, PET, and MRI

- ASIC, SoC, FPGA, DSP core, and I/O voltage

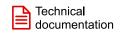

Simplified Application

## 3 Description

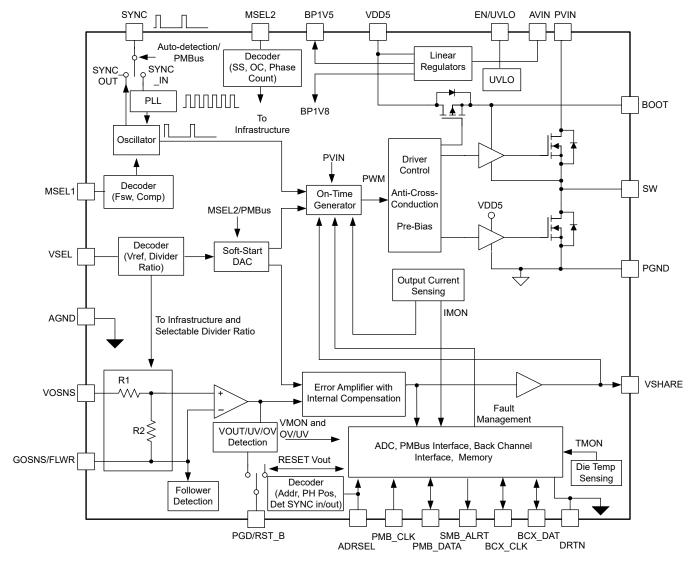

The TPS546A24S is a highly integrated, non-isolated DC/DC converter that expands on the TPS546A24A by adding manufacturer-specific PMBus commands and Extended Write Protect and Passkey. This feature improves security against malicious access to the PMBus by restricting Write capability with greater resolution than the standard Write Protect command. TPS546A24S is capable of high frequency operation and 10-A current output from a 7-mm × 5-mm package. Two, three, and four TPS546A24S devices can be interconnected to provide up to 40 A on a single output. The device has an option to overdrive the internal 5-V LDO with an external 5-V supply through the VDD5 pin to improve efficiency and reduce power dissipation of the converter.

The TPS546A24S uses a proprietary fixed-frequency current-mode control with input feedforward and selectable internal compensation components for minimal size and stability over a wide range of output capacitances.

The PMBus® interface with 1-MHz clock support gives a convenient, standardized digital interface for converter configuration as well as monitoring of key parameters including output voltage, output current, and internal die temperature. Response to fault conditions can be set to restart, latch off, or ignore, depending on system requirements. Back-channel communication between stacked devices enables all TPS546A24S converters powering a single output rail to share a single address to simplify system software/ firmware design. Key parameters including output voltage, switching frequency, soft-start time, and overcurrent fault limits can also be configured through BOM selection without PMBus communication to support program free power up.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TPS546A24S  | RVF (LQFN-CLIP, 40)    | 7.00 mm × 5.00 mm           |

- For more information, see Section 10. (1)

- The package size (length × width) is a nominal value and includes pins, where applicable.

## **Table of Contents**

| Features                             | 1  | 6.6 Register Maps                              | 45                     |

|--------------------------------------|----|------------------------------------------------|------------------------|

| Applications                         | 1  | 7 Application and Implementation               |                        |

| Description                          |    | 7.1 Application Information                    | 153                    |

| Pin Configuration and Functions      | 2  | 7.2 Typical Application                        |                        |

| Specifications                       | 5  | 7.3 Power Supply Recommendations               | 163                    |

| 5.1 Absolute Maximum Ratings         | 5  | 7.4 Layout                                     | 163                    |

| 5.2 ESD Ratings                      |    | 8 Device and Documentation Support             |                        |

| 5.3 Recommended Operating Conditions | 5  | 8.1 Device Support                             | 166                    |

| 5.4 Thermal Information              | 5  | 8.2 Documentation Support                      |                        |

| 5.5 Electrical Characteristics       | 6  | 8.3 Receiving Notification of Documentation Up | dates1 <mark>66</mark> |

| 5.6 Typical Characteristics          | 14 | 8.4 Support Resources                          | 166                    |

| Detailed Description                 |    | 8.5 Trademarks                                 | 166                    |

| 6.1 Overview                         |    | 8.6 Electrostatic Discharge Caution            | 167                    |

| 6.2 Functional Block Diagram         | 17 | 8.7 Glossary                                   | 167                    |

| 6.3 Feature Description              |    | 9 Revision History                             |                        |

| 6.4 Device Functional Modes          | 33 | 10 Mechanical, Packaging, and Orderable        |                        |

| 6.5 Programming                      |    | Information                                    | 168                    |

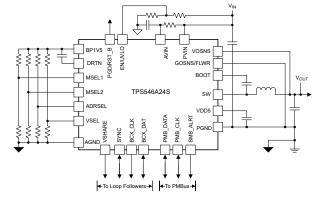

# 4 Pin Configuration and Functions

Figure 4-1. 40-Pin LQFN-CLIP With Exposed Thermal Pad RVF Package (Top View)

## **Table 4-1. Pin Functions**

|     | PIN       | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME      | (1)  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

| 1   | PGD/RST_B | I/O  | Open-drain power good or (21h) VOUT_COMMAND RESET#. As determined by user-programmable RESET# bit in (EDh) MFR_SPECIFIC_29 (MISC_OPTIONS). The default pin function is an open-drain power-good indicator. When configured as RESET#, an internal pullup can be enabled or disabled by the PULLUP# bit in (EDh) MFR_SPECIFIC_29 (MISC_OPTIONS). |

| 2   | PMB_DATA  | I/O  | PMBus DATA pin. See Current PMBus Specifications.                                                                                                                                                                                                                                                                                               |

| 3   | PMB_CLK   | ı    | PMBus CLK pin. See Current PMBus Specifications.                                                                                                                                                                                                                                                                                                |

| 4   | BP1V5     | 0    | Output of the 1.5-V internal regulator. This regulator powers the digital circuitry and must be bypassed with a minimum of 1 $\mu$ F to DRTN with an X5R or better ceramic capacitor rated for a minimum of 6 V. BP1V5 is not designed to power external circuit.                                                                               |

| 5   | DRTN      | _    | Digital bypass return for bypass capacitor for BP1V5. Internally connected to AGND. Do not connect to PGND or AGND.                                                                                                                                                                                                                             |

| 6   | SMB_ALRT  | 0    | SMBus alert pin. See SMBus specification.                                                                                                                                                                                                                                                                                                       |

| 7   | воот      | I    | Bootstrap pin for the internal flying high side driver. Connect a typical 100-nF X5R or better ceramic capacitor rated for a minimum of 10 V from this pin to SW. To reduce the voltage spike at SW, an optional BOOT resistor of up to 8 $\Omega$ can be placed in series with the BOOT capacitor to slow down turn-on of the high-side FET.   |

| 8   |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 9   |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 10  | sw        | I/O  | Switched power output of the device. Connect the output averaging filter and bootstrap to this group of pins.                                                                                                                                                                                                                                   |

| 11  |           |      | рию.                                                                                                                                                                                                                                                                                                                                            |

| 12  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 13  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 14  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 15  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 16  | PGND      | _    | Power stage ground return. These pins are internally connected to the thermal pad.                                                                                                                                                                                                                                                              |

| 17  | I SIND    |      | Tower stage ground return. These pins are internally connected to the thermal page.                                                                                                                                                                                                                                                             |

| 18  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 19  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 20  |           |      |                                                                                                                                                                                                                                                                                                                                                 |

| 21  |           |      | Input power to the power stage. Low-impedance bypassing of these pins to PGND is critical. PVIN to                                                                                                                                                                                                                                              |

| 22  |           |      | PGND must be bypassed with X5R or better ceramic capacitors rated for at least 1.5x the maximum                                                                                                                                                                                                                                                 |

| 23  | PVIN      |      | PVIN voltage. In addition, a minimum of one 0402 2.2-nF - 10-nF X7R or better ceramic capacitance rated for at least 1.5x the maximum PVIN voltage must placed as close to the PVIN and PGND pins or                                                                                                                                            |

| 24  |           |      | under the PVIN pins to reduce the high-frequency bypass impedance.                                                                                                                                                                                                                                                                              |

| 25  |           |      | leavet account the controller Division with a minimum 4 of VCD as bottom countries are after rated for                                                                                                                                                                                                                                          |

| 26  | AVIN      | I    | Input power to the controller. Bypass with a minimum 1-µF X5R or better ceramic capacitor rated for at least 1.5x the maximum AVIN voltage to AGND. If AVIN is connected to the same input as PVIN or VDD5, a minimum 10-µs R-C filter between PVIN or VDD5 and AVIN is recommended to reduce switching noise on AVIN.                          |

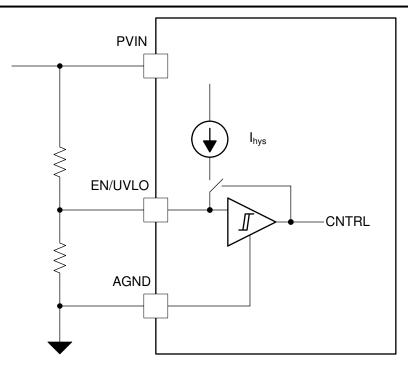

| 27  | EN/UVLO   | ı    | Enable switching as the PMBus CONTROL pin. EN/UVLO can also be connected to a resistor divider to program input voltage UVLO.                                                                                                                                                                                                                   |

| 28  | VDD5      | 0    | Output of the 5-V internal regulator. This regulator powers the driver stage of the controller and must be bypassed with a minimum of 4.7-µF X5R or better ceramic capacitor rated for a minimum of 10 V to PGND at the thermal pad. Low impedance bypassing of this pin to PGND is critical.                                                   |

| 29  | MSEL2     | I    | Connect this pin to a 1% tolerance or better resistor divider between BP1V5 and AGND for different options of soft-start time, overcurrent fault limit, and multi-phase information. See <i>Programming MSEL2</i> or <i>Programming MSEL2</i> for a Loop Follower Device (GOSNS Tied to BP1V5) if GOSNS is tied to BP1V5.                       |

| 30  | VSEL      | ı    | Connect this pin to a 1% tolerance or better resistor divider between BP1V5 and AGND for different options of internal voltage feedback divider and default output voltage. See <i>Programming VSEL</i> .                                                                                                                                       |

# **Table 4-1. Pin Functions (continued)**

|     | PIN         | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME        | (1)  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31  | ADRSEL      | ı    | Connect this pin to a 1% tolerance or better resistor divider between BP1V5 and AGND for different options of PMBus addresses and frequency sync (including determination of SYNC pin as SYNC IN or SYNC OUT function). See <i>Programming ADRSEL</i> .                                                                                                                                                                                                                                                                                                                                                                |

| 32  | MSEL1       | ı    | Connect this pin to a 1% tolerance or better resistor divider between BP1V5 and AGND for different options of switching frequency and internal compensation parameters. See <i>Programming MSEL1</i> .                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 33  | VOSNS       | I    | The positive input of the remote sense amplifier. For a stand-alone device or the loop controller device in a multi-phase configuration, connect VOSNS pin to the output voltage at the load. For the loop follower device in a multi-phase configuration, the remote sense amplifier is not required for output voltage sensing or regulation and this pin can be left floating. If used to monitor another voltage with the Phased $READ\_VOUT$ command, VOSNS must be maintained between 0 V and 0.75 V with a <1-k $\Omega$ resistor divider due to the internal resistance to GOSNS, which is connected to BP1V5. |

| 34  | GOSNS/FLWR  | I    | The negative input of the remote sense amplifier for loop controller device or must be pulled up high to indicate loop follower. For a standalone device or the loop controller device in a multi-phase configuration, connect the GOSNS pin to the ground at the load. For the loop follower device in a multi-phase configuration, the GOSNS pin must be pulled up to BP1V5 to indicate the device a loop follower.                                                                                                                                                                                                  |

| 35  | VSHARE      | I/O  | Voltage sharing signal for multi-phase operation. For standalone device, the VSHARE pin must be left floating. VSHARE can by bypassed to AGND with up to 50 pF of capacitance.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 36  | NC          | _    | Not internally connected. Connect to PGND at the thermal pad.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 37  | AGND        | _    | Analog ground return for controller. Connect the AGND pin directly to the thermal pad on the PCB board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 38  | SYNC        | I/O  | For frequency synchronization, can be programmed as SYNC IN or SYNC OUT pin by ADRSEL pin or the <i>(E4h) MFR_SPECIFIC_20 (SYNC_CONFIG)</i> PMBus Command. The SYNC pin can be left floating when not used.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 39  | BCX_CLK     | I/O  | Clock for back-channel communications between stacked devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 40  | BCX_DAT     | I/O  | Data for back-channel communications between stacked devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _   | Thermal pad | _    | Package thermal pad, internally connected to PGND. The thermal pad must have adequate solder coverage for proper operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

(1) I = input, O = output

## **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                       |                                                                              | MIN  | MAX  | UNIT |

|---------------------------------------|------------------------------------------------------------------------------|------|------|------|

| Input voltage                         | PVIN                                                                         | -0.3 | 18   | V    |

| Input voltage                         | PVIN, < 2-ms transient                                                       | -0.3 | 19   | V    |

|                                       | PVIN – SW (PVIN to SW differential)                                          | -0.3 | 24   |      |

| Input voltage                         | PVIN – SW (PVIN to SW differential, < 10-ns transient because of SW ringing) | -5   | 24   | V    |

|                                       | AVIN                                                                         | -0.3 | 20   | V    |

|                                       | BOOT                                                                         | -0.3 | 35   | V    |

| Input voltage                         | BOOT – SW (BOOT to SW differential)                                          | -0.3 | 5.5  | V    |

|                                       | EN/UVLO, VOSNS, SYNC, VSEL, MSEL1, MSEL2, ADRSEL                             | -0.3 | 5.5  | V    |

|                                       | VSHARE, GOSNS/FLWR                                                           | -0.3 | 1.98 | V    |

|                                       | PMB_CLK, PMB_DATA, BCX_CLK, BCX_DAT                                          | -0.3 | 5.5  | V    |

| Output voltage                        | SW                                                                           | -1   | 24   | V    |

| Output voltage                        | SW < 10-ns transient                                                         | -5   | 24   | V    |

| Output valtage                        | VDD5, SMB_ALRT, PGD/RST_B                                                    | -0.3 | 5.5  | V    |

| Output voltage                        | BP1V5                                                                        | -0.3 | 1.65 | V    |

| T <sub>J</sub> operating junction ten | nperature                                                                    | -40  | 150  | °C   |

| T <sub>stg</sub> Storage temperature  | 9                                                                            | -55  | 150  | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 5.2 ESD Ratings

|        |                                                                   |                                                                       | VALUE | UNIT |

|--------|-------------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|

|        | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000                                                                 | V     |      |

| V(ESD) | V <sub>(Fob)</sub>   Electrostatic discharge                      | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±1500 | v    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. .

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                       |                                               | MIN  | NOM | MAX | UNIT |

|-----------------------|-----------------------------------------------|------|-----|-----|------|

| V <sub>AVIN</sub>     | Controller input voltage                      | 2.95 | 12  | 18  | V    |

| V <sub>PVIN</sub>     | Power stage input voltage                     | 2.95 | 12  | 18  | V    |

| V <sub>SW(peak)</sub> | Peak Switch Node Voltage with respect to PGND |      |     | 18  | V    |

| T <sub>J</sub>        | Junction temperature                          | -40  |     | 150 | °C   |

## **5.4 Thermal Information**

|                       |                                                           | TPS546X24S |      |

|-----------------------|-----------------------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                             | PQFN (RVF) | UNIT |

|                       |                                                           | 40 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance JEDEC              | 25.3       | °C/W |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance EVM <sup>(3)</sup> | 12         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance                 | 26.3       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance                      | 8.5        | °C/W |

## **5.4 Thermal Information (continued)**

|                       |                                              | TPS546X24S |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PQFN (RVF) | UNIT |

|                       |                                              | 40 PINS    |      |

| ΨЈТ                   | Junction-to-top characterization parameter   | 2.0        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 9.3        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.0        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## **5.5 Electrical Characteristics**

$T_J = -40$ °C to 150°C,  $V_{PVIN} = V_{AVIN} = 12$  V,  $f_{SW} = 550$  kHz; zero power dissipation (unless otherwise noted)

|                                | PARAMETER                                                          | TE                           | ST CONDITIONS             | MIN   | TYP  | MAX   | UNIT |

|--------------------------------|--------------------------------------------------------------------|------------------------------|---------------------------|-------|------|-------|------|

| INPUT SUPPLY                   | ,                                                                  |                              |                           |       |      |       |      |

| V <sub>AVIN</sub>              | Input supply voltage range                                         |                              |                           | 2.95  |      | 16    | V    |

| V <sub>PVIN</sub>              | Power stage voltage range                                          |                              |                           | 2.95  |      | 16    | V    |

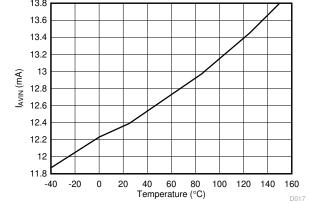

| I <sub>AVIN</sub>              | Input operating current                                            | Converter not switch         | ching                     |       | 12.5 | 17    | mA   |

| AVIN UVLO                      |                                                                    |                              |                           |       |      |       |      |

|                                | Analog input voltage UVLO for power on reset (PMBus communication) | enable threshold             |                           |       | 2.5  | 2.7   | V    |

| V <sub>AVINuvlo</sub>          | Analog input voltage UVLO for disable                              |                              |                           |       |      |       | V    |

|                                | Analog input voltage UVLO hysteresis                               |                              |                           |       | 250  |       | mV   |

| t <sub>delay(uvlo_PMBus)</sub> | Delay from AVIN UVLO<br>to PMBus ready to<br>communicate           | AVIN = 3 V                   |                           |       | 10   |       | ms   |

| PVIN UVLO                      |                                                                    |                              |                           |       |      |       |      |

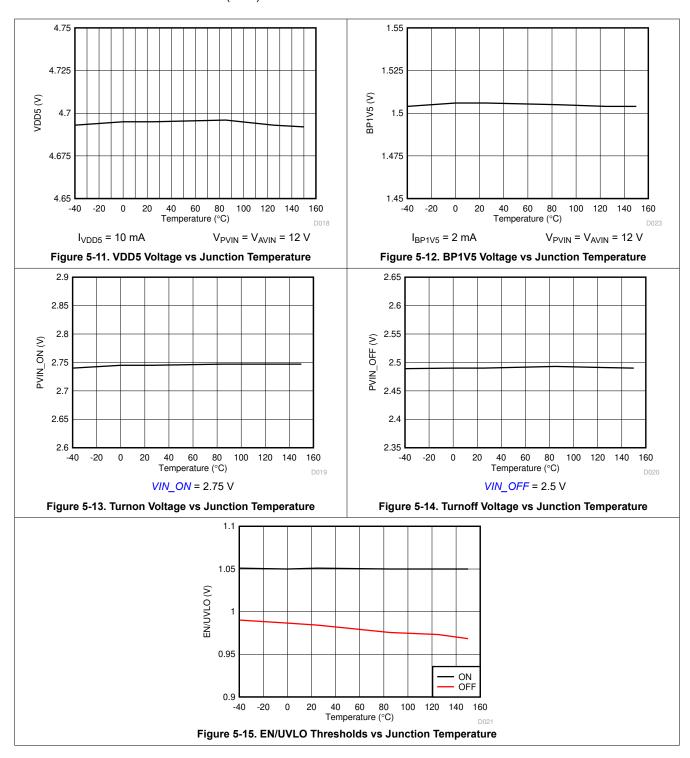

|                                |                                                                    | Factory default setting      |                           |       | 2.75 |       |      |

| VIN_ON                         | Power input turn on voltage                                        | Programmable range           |                           | 2.75  |      | 15.75 | V    |

|                                |                                                                    | Resolution                   |                           |       | 0.25 |       |      |

|                                |                                                                    | Accuracy                     |                           | -5%   | % 5% |       |      |

|                                |                                                                    | Factory default setting      |                           |       | 2.5  |       |      |

| VIN OFF                        |                                                                    | Programmable ran             | ge                        | 2.5   |      | 15.5  | V    |

| VIN_OFF                        | Power input turnoff voltage                                        | Resolution                   |                           |       | 0.25 |       |      |

|                                |                                                                    | Accuracy                     |                           | -5%   |      | 5%    |      |

| ENABLE AND I                   | UVLO                                                               | •                            |                           |       |      |       |      |

| V                              | EN/UVLO Voltage rising threshold                                   |                              |                           |       | 1.05 | 1.1   | V    |

| $V_{ENuvlo}$                   | EN/UVLO Voltage falling threshold                                  |                              |                           | 0.9   |      |       |      |

| V <sub>ENhys</sub>             | EN/UVLO Voltage hysteresis                                         | No external resisto          | rs on EN/UVLO             |       | 70   |       | mV   |

|                                | EN/UVLO hysteresis current                                         | V <sub>EN/UVLO</sub> = 1.1 V |                           | 4.5   | 5.5  | 6.5   | uA   |

| IENhys                         | EN/UVLO hysteresis current                                         | V <sub>EN/UVLO</sub> = 0.9 V |                           |       | -100 | -5    | nA   |

| REMOTE SENS                    | E AMPLIFIER                                                        | 1                            |                           |       |      |       |      |

| Z <sub>RSA</sub>               | Remote sense input impedance                                       | VOSNS -<br>GOSNS = 1V        | VOSNS to GOSNS            | 85    | 130  | 165   | kΩ   |

| V <sub>IRNG(GOSNS)</sub>       | GOSNS input range for regulation accuracy (1)                      | VOSNS - GOSNS<br>0.5         | S = 1V, VOUT_SCALE_LOOP ≤ | -0.05 |      | 0.05  | V    |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> EVM thermal resistance measured on TPS546D24SEVM-2PH. 8-layer, 2-oz Cu per layer evaluation board.

$T_J$  = -40°C to 150°C,  $V_{PVIN}$  =  $V_{AVIN}$ = 12 V,  $f_{SW}$  = 550 kHz; zero power dissipation (unless otherwise noted)

|                                                                         | PARAMETER                                                | TE                         | ST CONDITIONS                                                               | MIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TYP MAX | UNIT |

|-------------------------------------------------------------------------|----------------------------------------------------------|----------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|

| V <sub>IRNG(VOSNS)</sub>                                                | VOSNS input range for regulation accuracy <sup>(1)</sup> | GOSNS = AGND,              | VOUT_SCALE_LOOP ≤ 0.5                                                       | -0.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5.5     | V    |

| REFERENCE                                                               | VOLTAGE AND ERROR AMPL                                   | IFIER                      |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |

|                                                                         |                                                          | Default setting            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.4     | V    |

| $V_{REF}$                                                               | Reference voltage <sup>(1)</sup>                         |                            |                                                                             | 0.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         | V    |

|                                                                         |                                                          | Reference voltage          | resolution <sup>(1)</sup>                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-12    | V    |

|                                                                         |                                                          | V <sub>OUT</sub> = 1000 mV |                                                                             | 0.992                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.008   | V    |

|                                                                         |                                                          | V <sub>OUT</sub> = 500 mV  | $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}^{(2)}$ | 0.492                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.508   | V    |

|                                                                         |                                                          |                            |                                                                             | 1.490                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.510   | V    |

|                                                                         |                                                          |                            |                                                                             | 0.994                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.006   | V    |

| V <sub>OUT(ACC)</sub>                                                   | Output voltage accuracy                                  | V <sub>OUT</sub> = 500 mV  | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 125^{\circ}\text{C}^{(2)}$   | 0.494                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.506   | V    |

|                                                                         |                                                          |                            |                                                                             | 1.492                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | V    |

|                                                                         |                                                          |                            |                                                                             | 0.995                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.005   | V    |

|                                                                         |                                                          |                            | $0^{\circ}\text{C} \le \text{T}_{\text{J}} \le 85^{\circ}\text{C}^{(2)}$    | 0.495                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | V    |

| $V_{\text{REF}} \begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ | 1.507                                                    | V                          |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |

| 0                                                                       |                                                          |                            |                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200     | μS   |

| G <sub>mEA</sub>                                                        | Resolution <sup>(1)</sup>                                | Four settings: 25 u        | S, 50 uS, 100 uS, 200 uS                                                    | -0.1       5.5         0.4       0.25       0.75         2-12       0.992       1.008         0.492       0.508       1.490       1.510         0.994       1.006       0.494       0.506       1.492       1.508         0.995       1.005       0.495       0.505       1.493       1.507       25       200         25       8       1       5       315       5         1.25       18.75       1.25       6.25       193.75       6.25         25       200       25       17       1       5       315       5         800       1600       1600       1600       1600       1600       1600       1600       1600       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10       10 <td></td> |         |      |

|                                                                         | Unloaded Bandwidth <sup>(1)</sup>                        |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8       | MHz  |

| R <sub>pEA</sub>                                                        |                                                          |                            |                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 315     | kΩ   |

|                                                                         | Resolution <sup>(1)</sup>                                |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5       |      |

| Cintea                                                                  |                                                          |                            |                                                                             | 1.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18.75   | pF   |

|                                                                         | Resolution <sup>(1)</sup>                                |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.25    | pF   |

| C <sub>DEA</sub>                                                        |                                                          |                            |                                                                             | 6.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 193.75  | pF   |

| r=                                                                      | Resolution <sup>(1)</sup>                                |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6.25    | ]    |

| CURRENT GN                                                              | / AMPLIFIER                                              | '                          |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |      |

|                                                                         |                                                          |                            |                                                                             | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200     | μS   |

| G <sub>mBUF</sub>                                                       | Resolution <sup>(1)</sup>                                | Four settings: 25 µ        | S, 50 μS, 100 μS, 200 μS                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 25      | ]    |

|                                                                         | Unloaded bandwidth <sup>(1)</sup>                        |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 17      | MHz  |

| R <sub>pBUE</sub>                                                       |                                                          |                            |                                                                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 315     | kΩ   |

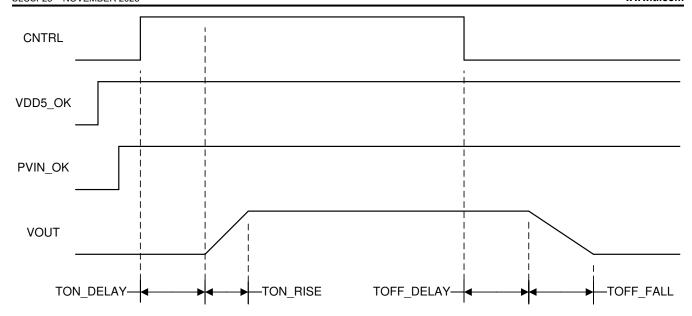

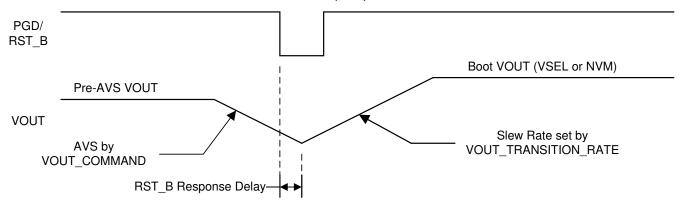

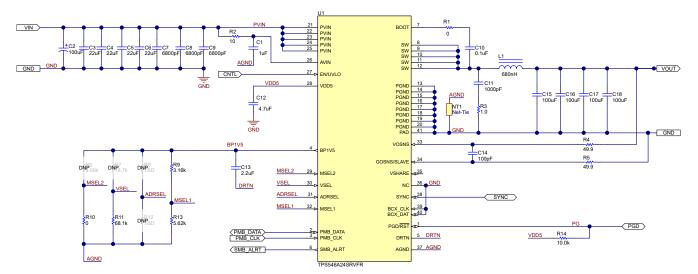

| poor                                                                    | Resolution <sup>(1)</sup>                                |                            |                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5       |      |