# TPS4812-Q1 100V Low Io Automotive High-Side Switch Controller With Bi-directional IMON, Low Power Mode, Load Wakeup, I<sup>2</sup>t, and Diagnostics

#### 1 Features

- AEC-Q100 automotive qualified for grade 1 temperature

- 3.5V to 95V input range (100V absolute maximum)

- Reverse input and output protection down to -65V

- Integrated 12V charge pump

- Low  $I_{O} = 20\mu A$  in low power mode ( $\overline{LPM} = Low$ )

- Low 1µA shutdown current (EN/UVLO = Low)

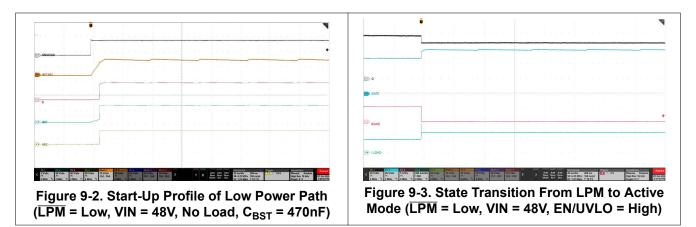

- Dual gate drive: GATE: 0.5A src/2A sink G: 100µA src/0.39A sink

- Accurate I<sup>2</sup>t overcurrent protection (IOC) with adjustable circuit breaker timer (I2t)

- Accurate and fast (5µs) short-circuit protection

- Fast transition (5µs) from low power mode to active mode using adjustable load wakeup threshold or LPM trigger with WAKE indication

- Accurate analog bi-directional current monitor output (IMON, I DIR): ±2% at 30mV V<sub>SNS</sub>

- NTC based overtemperature sensing (TMP) and monitoring output (ITMPO)

- Fault indication (FLT) during short circuit fault, I<sup>2</sup>t, charge pump UVLO, overtemperature

- TPS48120-Q1 (I<sup>2</sup>t enabled), TPS48121-Q1 (I<sup>2</sup>t disabled)

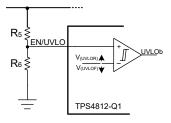

- Accurate (±2%) and adjustable undervoltage lockout (UVLO)

## 2 Applications

- Power distribution box

- Body control module

- DC/DC converter

- Battery management system

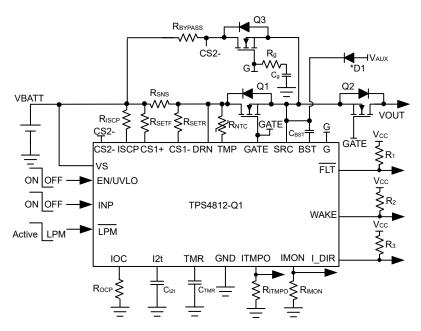

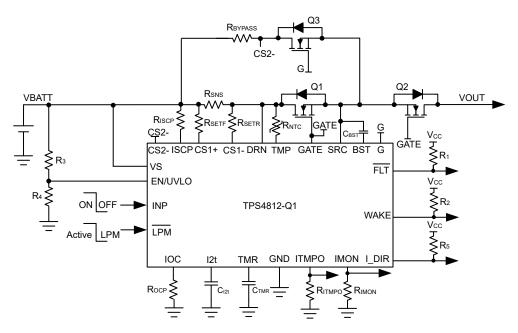

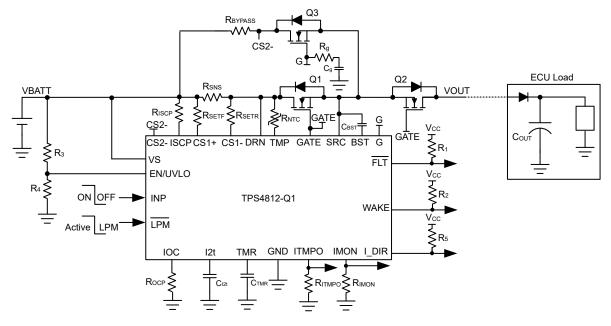

**TPS48120-Q1 Application Circuit Driving PAAT Loads With Load Wakeup**

## 3 Description

TPS4812-Q1 is a family of low IQ smart high side drivers with protection and diagnostics. With wide operating voltage range of 3.5V to 95V, 100V absmax the device is suitable for 12V, 24V and 48V automotive system designs.

It has two integrated gate drives with 0.5A source and 2A sink (GATE) and 100µA source and 0.39A sink (G). With LPM Low, the low power path is kept ON and the main FETs are turned OFF with IQ of 20µA (typ). Auto Load wakeup threshold adjusted using R<sub>BYPASS</sub> resistor placed across DRN and CS2-. IQ reduces to 1µA (typ) with EN/UVLO low.

The device has accurate bi-directional current sensing (±2%) output (IMON, I DIR) with adjustable I<sup>2</sup>t based overcurrent and short circuit protection using an external R<sub>SNS</sub> resistor and FLT indication. Auto-retry and latch-off fault behavior can be configured. The device also has NTC based temperature sensing (TMP) and monitoring output (ITMPO) output for overtemperature detection of external FETs.

The TPS4812-Q1 is available in 23-pin VQFN package.

### **Package Information**

| PART NUMBER                 | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-----------------------------|------------------------|-----------------------------|

| TPS48120-Q1,<br>TPS48121-Q1 | RGE (VQFN, 23)         | 4.00mm × 4.00mm             |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

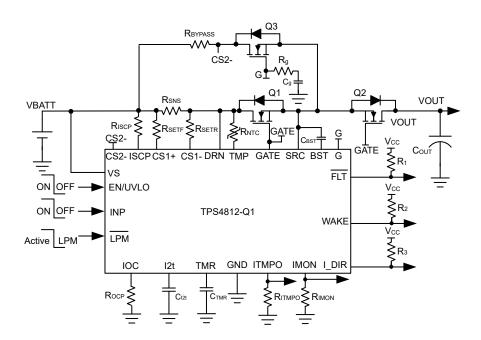

**TPS48120-Q1 Application Circuit Driving PAAT Loads With Load Wakeup and Bulk Capacitor** Charging

## **Table of Contents**

| 1 Features1                           | 9 Application and Implementation39                     |

|---------------------------------------|--------------------------------------------------------|

| 2 Applications1                       | 9.1 Application Information39                          |

| 3 Description1                        | 9.2 Typical Application 1: Driving Power at all times  |

| 4 Device Comparison3                  | (PAAT) Loads With Automatic Load Wakeup39              |

| 5 Pin Configuration and Functions4    | 9.3 Typical Application 2: Driving Power at all times  |

| 6 Specifications7                     | (PAAT) Loads With Automatic Load Wakeup and            |

| 6.1 Absolute Maximum Ratings7         | Output Bulk Capacitor Charging45                       |

| 6.2 ESD Ratings                       | 9.4 Power Supply Recommendations48                     |

| 6.3 Recommended Operating Conditions7 | 9.5 Layout49                                           |

| 6.4 Thermal Information8              | 10 Device and Documentation Support51                  |

| 6.5 Electrical Characteristics8       | 10.1 Receiving Notification of Documentation Updates51 |

| 6.6 Switching Characteristics10       | 10.2 Support Resources51                               |

| 6.7 Typical Characteristics12         | 10.3 Trademarks51                                      |

| 7 Parameter Measurement Information14 | 10.4 Electrostatic Discharge Caution51                 |

| 8 Detailed Description17              | 10.5 Glossary51                                        |

| 8.1 Overview                          | 11 Revision History51                                  |

| 8.2 Functional Block Diagram18        | 12 Mechanical, Packaging, and Orderable                |

| 8.3 Feature Description19             | Information51                                          |

| 8.4 Device Functional Modes33         |                                                        |

## **4 Device Comparison**

## Table 4-1. Device Comparison

| Device name /Feature        | TPS48120-Q1 | TPS48121-Q1 |

|-----------------------------|-------------|-------------|

| I <sup>2</sup> T Protection | Yes         | No          |

Copyright © 2024 Texas Instruments Incorporated

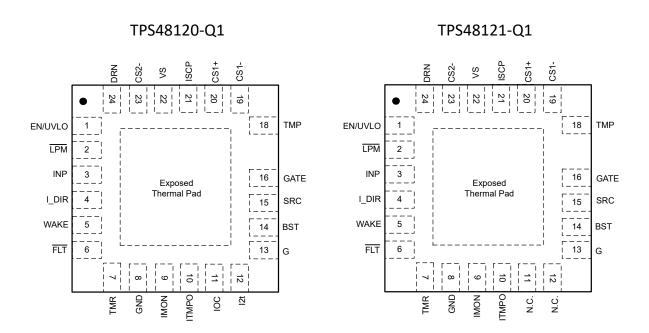

# **5 Pin Configuration and Functions**

Figure 5-1. RGE Package, 23-Pin VQFN (Transparent Top View)

Table 5-1. Pin Functions

|         | PIN         |                 |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------|-------------|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | TPS48120-Q1 | TPS48121-<br>Q1 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EN/UVLO | 1           | 1               | ı                   | EN/UVLO input. A voltage on this pin above $V_{(UVLOR)}$ 1.21V enables normal operation. If EN/UVLO is below $V_{(UVLOF)}$ then Gate drives are turned OFF. Forcing this pin below $V_{(ENF)}$ 0.3V shuts down the device reducing quiescent current to approximately 1µA (typ). Optionally connect to the input supply through a resistive divider to set the undervoltage lockout. When EN/UVLO is left floating an internal pull down of 100nA pulls EN/UVLO low and keeps the device in OFF state. |

| LРM     | 2           | 2               | I                   | Mode control input.  When driven high, the device enters into active mode. When driven low, the devices enter into low power mode.  If low power mode is not required, $\overline{\text{LPM}}$ pin can be tied to EN/UVLO pin.  When $\overline{\text{LPM}}$ is left floating an internal pull down of 100nA pulls $\overline{\text{LPM}}$ low.                                                                                                                                                        |

| INP     | 3           | 3               | I                   | Input signal for external FET control.  CMOS compatible input reference to GND that sets the state of GATE pin.  INP has an internal weak pull down of 100nA to GND to keep GATE pulled to SRC when INP is left floating.                                                                                                                                                                                                                                                                              |

| I_DIR   | 4           | 4               | I                   | Open drain I_DIR output.  This pin is asserted low by device when current through CS1+ and CS1– flows in reverse direction.                                                                                                                                                                                                                                                                                                                                                                            |

## **Table 5-1. Pin Functions (continued)**

|       |             | іа              | DIE 5-1.            | Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-------------|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PIN         |                 | (1)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NAME  | TPS48120-Q1 | TPS48121-<br>Q1 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WAKE  | 5           | 5               | 0                   | Open drain WAKE output.  This pin is asserted low by device when device enters into active mode (when LPM is driven high or when a load wakeup event has occurred).                                                                                                                                                                                                                                                                                                                                                    |

| FLT   | 6           | 6               | 0                   | Open drain fault output.  FLT goes low during charge pump UVLO, Main FET SCP, I²t timer trigger, NTC based external FET overtemperature fault.  This pin asserts low after the voltage on the I2t pin has reached the fault threshold of 2V. This pin indicates the main FET is about to turn off due to an overload condition. This pin asserts low along with GATE turn off during short-circuit.  The FLT pin does not go to a high impedance state until the overcurrent condition and the auto-retry time expire. |

| TMR   | 7           | 7               | ı                   | Auto-retry or latch timer input after overcurrent fault.<br>A capacitor across TMR pin to GND sets the times for retry periods. Leave open for fastest setting.<br>Connect resistor across $C_{TMR}$ from TMR pin to GND for latch-off functionality.                                                                                                                                                                                                                                                                  |

| GND   | 8           | 8               | G                   | Connect GND to system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IMON  | 9           | 9               | 0                   | Analog bi-directional current monitor output.  This pin sources a scaled down ratio of current through the external current sense resistor R <sub>SNS</sub> . A resistor from this pin to GND converts current proportional to voltage.  If unused, leave floating or can be connected to ground.                                                                                                                                                                                                                      |

| ITMPO | 10          | 10              | 0                   | Analog temperature output.  Analog voltage feedback provides a voltage proportional to thermistor temperature.  If unused, leave floating.                                                                                                                                                                                                                                                                                                                                                                             |

| IOC   | 11          | _               | I                   | Overcurrent detection setting. A resistor across IOC to GND sets the over current comparator threshold. IOC pin can also be driven externally using MCU.                                                                                                                                                                                                                                                                                                                                                               |

| N.C.  | _           | 11              | _                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I2t   | 12          | _               | 0                   | I2t timer input. A capacitor across I2t pin to GND sets the times for overcurrent (t <sub>OC</sub> ).                                                                                                                                                                                                                                                                                                                                                                                                                  |

| N.C.  | _           | 12              | _                   | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| G     | 13          | 13              | 0                   | Gate of external bypass FET.  100µA peak source and 0.39A sink capacity.  Connect to the gate of the external bypass FET.                                                                                                                                                                                                                                                                                                                                                                                              |

| BST   | 14          | 14              | 0                   | High side bootstrapped supply.  An external capacitor with a minimum value of 0.1µF should be connected between this pin and SRC. Voltage swing on this pin is 12V to (VIN + 12V).                                                                                                                                                                                                                                                                                                                                     |

| SRC   | 15          | 15              | 0                   | Source connection of the external FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GATE  | 16          | 16              | 0                   | High current gate driver pull-up and pull-down.  0.5A peak source and 2A sink capacity.  This pin pulls GATE up to BST and down to SRC. For the fastest tun-on and turn-off, tie this pin directly to the gate of the external high side MOSFET in main path.                                                                                                                                                                                                                                                          |

Product Folder Links: TPS4812-Q1

## **Table 5-1. Pin Functions (continued)**

|      | PIN         |                 |                     |                                                                                                                                                                                                                                                   |  |

|------|-------------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME | TPS48120-Q1 | TPS48121-<br>Q1 | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                       |  |

| ТМР  | 18          | 18              | I                   | Temperature input. Analog connection to external NTC thermistor Connect TMP pin directly to VS if this feature is not used                                                                                                                        |  |

| CS1- | 19          | 19              | I                   | Main path current sense negative input. Connect a resistor (R <sub>SETR</sub> ) across CS1– to the external current sense resistor to set IMON gain in reverse direction.                                                                         |  |

| CS1+ | 20          | 20              | I                   | Main path current sense positive input.  Connect a resistor (R <sub>SETF</sub> ) across CS1+ to the external current sense resist to set IMON gain in forward direction.  Connect CS1+ and CS1- to VBATT if main FET current sensing is not used. |  |

| ISCP | 21          | 21              | 1                   | Short-circuit detection threshold setting. Connect ISCP to DRN if short-circuit protection is not desired.                                                                                                                                        |  |

| VS   | 22          | 22              | Р                   | Supply pin of the controller.                                                                                                                                                                                                                     |  |

| CS2- | 23          | 23              | I                   | Bypass path current sense negative input.                                                                                                                                                                                                         |  |

| DRN  | 24          | 24              | I                   | Main path SCP sense negative input.  Connect DRN+ and CS2– together to VBATT after RSNS if bypass path is not used.                                                                                                                               |  |

| GND  | Thermal Pad | _               | _                   | Connect exposed thermal pad to GND plane.                                                                                                                                                                                                         |  |

<sup>(1)</sup> I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## **6 Specifications**

### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                                                            | MIN               | MAX                        | UNIT |

|------------------------|----------------------------------------------------------------------------|-------------------|----------------------------|------|

| Input pins             | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP to GND                                | -65               | 100                        | V    |

| Input pins             | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP to SRC                                | -65               | 100                        | V    |

| Input pins             | SRC to GND                                                                 | -65               | 100                        | V    |

| Input pins             | GATE, G, BST to SRC                                                        | -0.3              | 19                         | V    |

| Input pins             | TMR to GND                                                                 | -0.3              | 5.5                        | V    |

| Input pins             | IOC to GND, TPS48120-Q1 only                                               | -1                | 5.5                        | V    |

| Input pins             | EN/UVLO, INP, <u>IPM;</u> V <sub>(VS)</sub> > 0 V                          | -1                | 100                        | V    |

| Input pins             | EN/UVLO, INP, <del>IPM;</del> V <sub>(VS)</sub> ≤ 0 V                      | V <sub>(VS)</sub> | (100 + V <sub>(VS)</sub> ) | V    |

| Input pins             | CS1+ to CS1-                                                               | -0.3              | 0.4                        | V    |

| Input pins             | DRN to CS2-                                                                | -5                | 100                        | V    |

| Output pins            | FLT, I_DIR, WAKE to GND                                                    | -1                | 20                         | V    |

| Output pins            | IMON to GND                                                                | -1                | 5.5                        | V    |

| Output pins            | I2t, ITMPO to GND, TPS48120-Q1 only                                        | -1                | 7.5                        | V    |

| Output pins            | ITMPO to GND, TPS48121-Q1 only                                             | -1                | 7.5                        | V    |

| Output pins            | GATE, G, BST to GND                                                        | -65               | 112                        | V    |

| Sink current           | I <sub>(FLT)</sub> , I <sub>(I_DIR)</sub> , I <sub>(WAKE)</sub>            |                   | 10                         | mA   |

| Sink current           | $I_{(CS1+)}$ to $I_{(CS1-)}$ , 1msec ; $I_{(DRN)}$ to $I_{(CS2-)}$ , 1msec |                   | 100                        | mA   |

| Operating junction ten | nperature, T <sub>j</sub> <sup>(2)</sup>                                   | -40               | 150                        | °C   |

| Storage temperature,   | $T_{stg}$                                                                  | -40               | 150                        | C    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|  |                                            |                                 |                                 |                         | VALUE | UNIT |

|--|--------------------------------------------|---------------------------------|---------------------------------|-------------------------|-------|------|

|  |                                            |                                 | Human body model (HBM), per AEC | Q100-002 <sup>(1)</sup> | ±2000 |      |

|  | V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per | Corner pins                     | ±750                    | V     |      |

|  |                                            | AEC Q100-011                    | Other pins                      | ±500                    |       |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)(1)

|                    |                                             | MIN | NOM MAX | UNIT |

|--------------------|---------------------------------------------|-----|---------|------|

| Input pins         | VS, CS1+, CS1-, DRN, CS2-, ISCP, TMP to GND | -60 | 95      | V    |

| Input pins         | EN/UVLO, INP, LPM                           | 0   | 95      | V    |

| Input pins         | IOC, TMR to GND, , TPS48120-Q1 only         | 0   | 5       | V    |

| Input pins         | TMR to GND, TPS48121-Q1 only                | 0   | 5       | V    |

| Output pins        | I2t, IMON, ITMPO to GND, TPS48120-Q1 only   | 0   | 5       | V    |

| Output pins        | IMON, ITMPO to GND, TPS48121-Q1 only        | 0   | 5       | V    |

| Output pins        | FLT, WAKE, I_DIR to GND                     | 0   | 15      | V    |

| External capacitor | VS, SRC to GND                              | 22  |         | nF   |

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

## **6.3 Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)(1)

|                    |                                               | MIN | NOM MAX | UNIT |

|--------------------|-----------------------------------------------|-----|---------|------|

| External capacitor | BST to SRC                                    | 0.1 |         | μF   |

| External capacitor | I2t to GND                                    | 10  |         | nF   |

| External capacitor | TMR to GND                                    | 1   |         | nF   |

| Tj                 | Operating junction temperature <sup>(2)</sup> | -40 | 150     | °C   |

<sup>(1)</sup> Recommended Operating Conditions are conditions under which the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

#### **6.4 Thermal Information**

|                       |                                              | TPS4812x-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGE (VQFN)  | UNIT |

|                       |                                              | 23 PINS     |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 43          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 38.3        | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 20.8        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.8         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 20.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

$T_J = -40$  °C to +125°C.  $V_{(VS)} = 48$  V,  $V_{(BST-SRC)} = 12$  V,  $V_{(SRC)} = 0$  V

|                        | PARAMETER                                                     | TEST CONDITIONS                                                             | MIN  | TYP  | MAX   | UNIT |

|------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------|------|------|-------|------|

| SUPPLY VOLT            | TAGE (VS)                                                     |                                                                             |      |      |       |      |

| VS                     | Operating input voltage                                       |                                                                             | 3.5  |      | 95    | V    |

| V <sub>(S_PORR)</sub>  | Input supply POR threshold, rising                            |                                                                             | 2.06 | 2.6  | 3.12  | V    |

| V <sub>(S_PORF)</sub>  | Input supply POR threshold, falling                           |                                                                             | 2    | 2.5  | 3.01  | V    |

|                        | Total System Quiescent current, I <sub>(GND)</sub>            | $V_{(EN/UVLO)} = V_{(\overline{LPM})} = 2 V$                                |      | 430  | 525   | μΑ   |

|                        | Total System Quiescent current, I <sub>(GND)</sub>            | V <sub>(EN/UVLO)</sub> = V <sub>(LPM)</sub> = 2 V<br>TPS48121-Q1 Only       |      | 370  | 470   | μΑ   |

|                        | Total System Quiescent current, I <sub>(GND)</sub>            | $V_{(EN/UVLO)} = 2V, V_{(\overline{LPM})} = 0 V$                            |      | 20   | 24    | μΑ   |

| I <sub>(SHDN)</sub>    | SHDN current, I <sub>(GND)</sub>                              | V <sub>(SRC)</sub> = 48 V, V <sub>(EN/UVLO)</sub> = 0 V, V <sub>(SRC)</sub> |      | 0.9  | 3.4   | μΑ   |

| I <sub>(REV_VS)</sub>  | I <sub>(VS)</sub> leakage current during Reverse<br>Polarity  | 0 V ≤ V <sub>(VS)</sub> ≤ - 65 V                                            |      |      | 60    | μΑ   |

| I <sub>(REV_SRC)</sub> | I <sub>(SRC)</sub> leakage current during Reverse<br>Polarity | 0 V ≤ V <sub>(VS)</sub> ≤ - 65 V                                            |      |      | 27    | μΑ   |

| ENABLE, UNI            | DERVOLTAGE LOCKOUT (EN/UVLO) AND                              | OVER VOLTAGE PROTECTION INPUT                                               | (OV) |      |       |      |

| V <sub>(UVLOR)</sub>   | UVLO threshold voltage, rising                                |                                                                             | 1.16 | 1.2  | 1.245 | V    |

| V <sub>(UVLOF)</sub>   | UVLO threshold voltage, falling                               |                                                                             | 1.09 | 1.11 | 1.16  | V    |

| V <sub>(ENR)</sub>     | Enable threshold voltage for low lq shutdown, rising          |                                                                             |      |      | 1     | V    |

| V <sub>(ENF)</sub>     | Enable threshold voltage for low Iq shutdown, falling         |                                                                             | 0.3  |      |       | V    |

| I <sub>(EN/UVLO)</sub> | Enable input leakage current                                  | V <sub>(EN/UVLO)</sub> = 48 V                                               |      |      | 500   | nA   |

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

## **6.5 Electrical Characteristics (continued)**

$T_{.1} = -40$  °C to +125°C.  $V_{(VS)} = 48$  V,  $V_{(BST-SRC)} = 12$  V,  $V_{(SRC)} = 0$  V

|                              | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                                     | MIN   | TYP  | MAX  | UNIT |

|------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| CHARGE PUMP                  | (BST-SRC)                                                                                                 |                                                                                                                     |       |      |      |      |

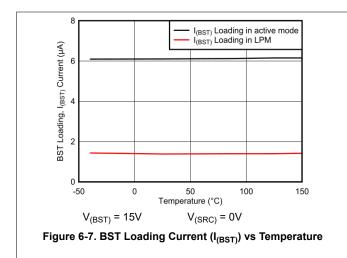

| I <sub>(BST_LPM)</sub>       | Charge Pump Supply current in LPM                                                                         | V <sub>(BST - SRC)</sub> = 10 V, V <sub>(EN/UVLO)</sub> = 2<br>V, V <sub>(LPM)</sub> = 0 V                          | 175   | 360  | 575  | μA   |

| I <sub>(BST_AM)</sub>        | Charge Pump Supply current in active mode                                                                 | $V_{(BST-SRC)} = 12 \text{ V}, V_{(EN/UVLO)} = 2 \text{ V}, V_{(\overline{LPM})} = 2 \text{ V}$                     | 300   | 540  | 775  | μΑ   |

| .,                           | V <sub>(BST - SRC)</sub> UVLO voltage threshold, rising                                                   | V <sub>(EN/UVLO)</sub> = 2 V                                                                                        | 7     | 7.6  | 8.4  | V    |

| V <sub>(BST UVLO)</sub>      | V <sub>(BST – SRC)</sub> UVLO voltage threshold, falling                                                  | V <sub>(EN/UVLO)</sub> = 2 V                                                                                        | 6     | 6.6  | 7.2  | V    |

| VCP <sub>(AM_LOW)</sub>      | Charge Pump Turn ON voltage in active mode                                                                | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(LPM)</sub> = 2 V                                                              | 9.5   | 10.4 | 12.3 | ٧    |

| VCP <sub>(AM_HIGH)</sub>     | Charge Pump Turnoff voltage in active mode                                                                | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(LPM)</sub> = 2 V                                                              | 10.42 | 11.3 | 13   | ٧    |

| VCP <sub>(LPM_LOW)</sub>     | Charge Pump Turn ON voltage in low power mode                                                             | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(LPM)</sub> = 0 V                                                              | 8.3   | 9.3  | 10.6 | ٧    |

| VCP <sub>(LPM_HIGH)</sub>    | Charge Pump Turnoff voltage in low power mode                                                             | V <sub>(EN/UVLO)</sub> = 2 V, V <sub>(LPM)</sub> = 0 V                                                              | 9.02  | 10.3 | 11.8 | V    |

| VCP <sub>(VS_3V)</sub>       | Charge Pump Voltage at V <sub>(VS)</sub> = 3 V                                                            | V <sub>(EN/UVLO)</sub> = 2 V                                                                                        | 8     |      |      | V    |

| $V_{(G\_GOOD)}$              | G Drive Good rising threshold<br>w.r.t BST when bypass comparator<br>reference changes from 2 V to 200 mV |                                                                                                                     |       | 2.3  |      | V    |

| I <sub>(SRC)</sub>           | SRC pin leakage current                                                                                   | $V_{(EN/UVLO)} = 2 \text{ V}, V_{(INP)} = 0, V_{(\overline{LPM})} = 2$                                              |       | 1    | 1.57 | μΑ   |

| GATE DRIVER C                | OUTPUTS (GATE, G)                                                                                         |                                                                                                                     |       |      |      |      |

| I <sub>(GATE)</sub>          | Peak Source Current                                                                                       |                                                                                                                     |       | 0.5  |      | Α    |

| I <sub>(GATE)</sub>          | Peak Sink Current                                                                                         |                                                                                                                     |       | 2    |      | Α    |

| I <sub>(G)</sub>             | Gate charge (sourcing) current, on state                                                                  |                                                                                                                     |       | 100  |      | μA   |

| I <sub>(G)</sub>             | G Peak Sink Current                                                                                       |                                                                                                                     |       | 390  |      | mA   |

| CURRENT SENS                 | SE AND CURRENT MONITOR (CS1+, CS                                                                          | 1–, IMON, I_DIR)                                                                                                    |       |      | '    |      |

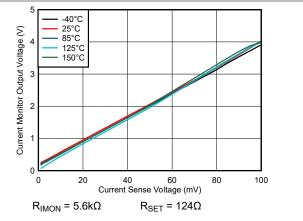

| V <sub>(OS_SET)</sub>        | Input referred offset (V <sub>SNS</sub> to V <sub>(IMON)</sub> scaling)                                   |                                                                                                                     | -140  |      | 140  | μV   |

| V <sub>(GE_SET)</sub>        | Gain error (V <sub>SNS</sub> to V <sub>(IMON)</sub> scaling)                                              |                                                                                                                     | -1    |      | 1    | %    |

| V <sub>(IMON_Acc)</sub>      | IMON accuracy                                                                                             | V <sub>SNS</sub> = ±6 mV                                                                                            | -5    |      | 5    | %    |

| V <sub>(IMON_Acc)</sub>      | IMON accuracy                                                                                             | V <sub>SNS</sub> = ±10 mV                                                                                           | -5    |      | 5    | %    |

| V <sub>(IMON_Acc)</sub>      | IMON accuracy                                                                                             | V <sub>SNS</sub> = ±15 mV                                                                                           | -2    | ,    | 2    | %    |

| V <sub>(IMON_Acc)</sub>      | IMON accuracy                                                                                             | V <sub>SNS</sub> = ±30 mV                                                                                           | -2    |      | 2    | %    |

|                              | (12t) AND SHORT CIRCUIT PROTECTIO                                                                         | ON (IOC, I2t, ISCP, DRN)                                                                                            |       |      | '    |      |

| V <sub>(OCP)</sub>           | OCP threshold accuracy                                                                                    | 15 mV ≥ V <sub>(OCP)</sub> ≥ 100 mV                                                                                 | -7.5  |      | 7.5  | %    |

| I <sup>2</sup> (I2t_Acc)     | I <sup>2</sup> current accuracy on I2t pin                                                                | 15 mV ≥ $V_{(OCP)}$ ≥ 100 mV<br>$V_{SNS}$ = $V_{(OCP)}$ + 50% of $V_{(OCP)}$                                        | -15   |      | 15   | %    |

| I <sup>2</sup> (I2t_Acc)     | I <sup>2</sup> current accuracy on I2t pin                                                                | 15 mV $\geq$ V <sub>(OCP)</sub> $\geq$ 100 mV<br>V <sub>SNS</sub> = V <sub>(OCP)</sub> + 100% of V <sub>(OCP)</sub> | -10   |      | 10   | %    |

| I <sup>2</sup> (I2t_Acc)     | I <sup>2</sup> current accuracy on I2t pin                                                                | 15 mV ≥ $V_{(OCP)}$ ≥ 100 mV<br>$V_{SNS} = V_{(OCP)} + 200\%$ of $V_{(OCP)}$                                        | -10   |      | 10   | %    |

| V <sub>(I2t_OC)</sub>        | I2t pin voltage threshold for overcurrent shutdown                                                        |                                                                                                                     | 1.93  | 2    | 2.09 | V    |

| I <sub>(I2t_Charge)</sub>    | Charging current on I2t pin to V <sub>(I2t_OFFSET)</sub>                                                  |                                                                                                                     |       | 5100 |      | μΑ   |

| R <sub>(I2t_Discharge)</sub> | Internal switch discharge resistance                                                                      |                                                                                                                     |       | 1200 |      | Ω    |

## **6.5 Electrical Characteristics (continued)**

$T_J$  = -40 °C to +125°C.  $V_{(VS)}$  = 48 V,  $V_{(BST-SRC)}$  = 12 V,  $V_{(SRC)}$  = 0 V

|                                                               | PARAMETER                                                                                                | TEST CONDITIONS                                                                                                                                               | MIN  | TYP  | MAX  | UNIT |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>(I2t_OFFSET)</sub>                                     | I2t pin offset voltage                                                                                   |                                                                                                                                                               | 490  | 500  | 415  | mV   |

| V <sub>(REF_OC)</sub>                                         | IOC pin reference voltage                                                                                |                                                                                                                                                               | 190  | 200  | 205  | mV   |

| V <sub>(SCP)</sub>                                            | SCP threshold accuracy                                                                                   | $V_{(SNS\_SCP)}$ = 20 mV,<br>R <sub>(ISCP)</sub> = 732 $\Omega$                                                                                               | 19   | 20   | 21   | mV   |

| $V_{(SCP)}$                                                   | SCP threshold accuracy                                                                                   | $V_{(SNS\_SCP)}$ = 100 mV,<br>$R_{(ISCP)}$ = 3.92 k $\Omega$                                                                                                  | 95   | 100  | 105  | mV   |

| I <sub>SCP</sub>                                              | SCP Input Bias current                                                                                   |                                                                                                                                                               | 24.4 | 25   | 25.2 | μΑ   |

| LOAD WAKEUP                                                   | COMPARATOR (CS2-, DRN)                                                                                   |                                                                                                                                                               |      |      |      |      |

| V <sub>(LPM_SCP)</sub>                                        | Short-circuit threshold in LPM                                                                           |                                                                                                                                                               | 1.72 | 2    | 2.17 | V    |

| V <sub>(LWU)</sub>                                            | Load wakeup current threshold                                                                            |                                                                                                                                                               | 177  | 200  | 218  | mV   |

| AUTO-RETRY OR                                                 | LATCH-OFF TIMER (TMR)                                                                                    |                                                                                                                                                               |      |      |      |      |

| I <sub>(TMR_SRC_FLT)</sub>                                    | TMR source current                                                                                       |                                                                                                                                                               | 2    | 2.5  | 3    | μA   |

| I <sub>(TMR_SNK)</sub>                                        | TMR sink current                                                                                         |                                                                                                                                                               | 2    | 2.5  | 3    | μA   |

| V <sub>(TMR_HIGH)</sub>                                       | Voltage at TMR pin for AR counter rising threshold                                                       |                                                                                                                                                               | 1.04 | 1.23 | 1.42 | V    |

| V <sub>(TMR_LOW)</sub>                                        | Voltage at TMR pin for AR counter falling threshold                                                      |                                                                                                                                                               | 0.15 | 0.25 | 0.39 | V    |

| N <sub>(A-R Count)</sub>                                      |                                                                                                          |                                                                                                                                                               |      | 32   |      |      |

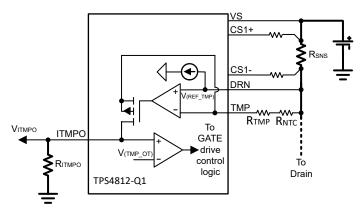

| TEMPERATURE N                                                 | MONITOR (CS1-, TMP, ITMPO)                                                                               |                                                                                                                                                               |      |      |      |      |

| V <sub>(REF_TMP)</sub>                                        | Temperature amplifier internal reference voltage                                                         |                                                                                                                                                               | 475  | 500  | 525  | mV   |

| V <sub>(ITMPO)</sub>                                          | Temperature monitor output voltage at $150^{\circ}$ C $R_{(NTC)} = 10 \text{ k}\Omega$ at $25^{\circ}$ C | $R_{(TMP)}$ = 330 Ω,<br>$R_{(NTC)}$ = 309 Ω at 150°C,<br>$R_{(ITMPO)}$ = 2.55 kΩ                                                                              | -6   |      | 6.64 | %    |

| V <sub>(ITMPO)</sub>                                          | Temperature monitor output voltage at 150 °C $R_{(NTC)}$ = 47 k $\Omega$ at 25 °C                        | $R_{(TMP)}$ = 1 kΩ,<br>$R_{(NTC)}$ = 520 Ω at 150°C,<br>$R_{(ITMPO)}$ = 6.19 kΩ                                                                               | -6   |      | 6.67 | %    |

| I <sub>(TMP)</sub>                                            | TMP leakage current                                                                                      |                                                                                                                                                               |      |      | 100  | nΑ   |

| V <sub>(TMP_OT)</sub>                                         | Over temperature threshold                                                                               |                                                                                                                                                               | 1.9  | 2    | 2.06 | V    |

| INPUT CONTROL                                                 | S (INP, INP_G, LPM), & FAULT FLAG (F                                                                     | FLT)                                                                                                                                                          |      |      | ·    |      |

| $R_{(\overline{FLT})}$ , $R_{(WAKE)}$ , $R_{(I}$              | FLT, WAKE, I_DIR Pull-down resistance                                                                    |                                                                                                                                                               |      | 70   |      | Ω    |

| I <sub>(FLT)</sub> , I <sub>(WAKE)</sub> , I <sub>(I_DI</sub> | FLT, WAKE, I_DIR leakage current                                                                         | $0 \text{ V} \le V_{(\overline{FLT})} \le 20 \text{ V},$<br>$0 \text{ V} \le V_{(WAKE)} \le 20 \text{ V},$<br>$0 \text{ V} \le V_{(I\_DIR)} \le 20 \text{ V}$ |      |      | 400  | nA   |

| $V_{(INP\_H)}$ , $V_{(\overline{LPM}\_H)}$                    |                                                                                                          |                                                                                                                                                               |      |      | 2    | V    |

| $V_{(INP\_L)}$ , $V_{(\overline{LPM}\_L)}$                    |                                                                                                          |                                                                                                                                                               | 0.72 |      |      | V    |

| V <sub>(INP_Hys)</sub> , V <sub>(LPM_H</sub> ys)              | INP, LPM Hysteresis                                                                                      |                                                                                                                                                               |      | 400  |      | mV   |

| I <sub>(INP)</sub> , I <sub>(EPM)</sub>                       | INP, LPM leakage current                                                                                 |                                                                                                                                                               |      |      | 200  | nA   |

## **6.6 Switching Characteristics**

$T_J$  = -40 °C to +125°C.  $V_{(VS)}$  = 48 V,  $V_{(BST-SRC)}$  = 12 V,  $V_{(SRC)}$  = 0 V

|                          | PARAMETER                                | TEST CONDITIONS                                                                  | MIN | TYP  | MAX | UNIT |

|--------------------------|------------------------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>GATE(INP_H)</sub> | INP Turn ON propogation Delay            | INP $\uparrow$ to GATE $\uparrow$ , $C_{L(GATE)} = 47 \text{ nF}$                |     | 1.2  | 2.5 | μs   |

| t <sub>GATE(INP_L)</sub> | INP Turn OFF propogation Delay           | INP $\downarrow$ to GATE $\downarrow$ , $C_{L(GATE)} = 47 \text{ nF}$            |     | 0.35 | 1.5 | μs   |

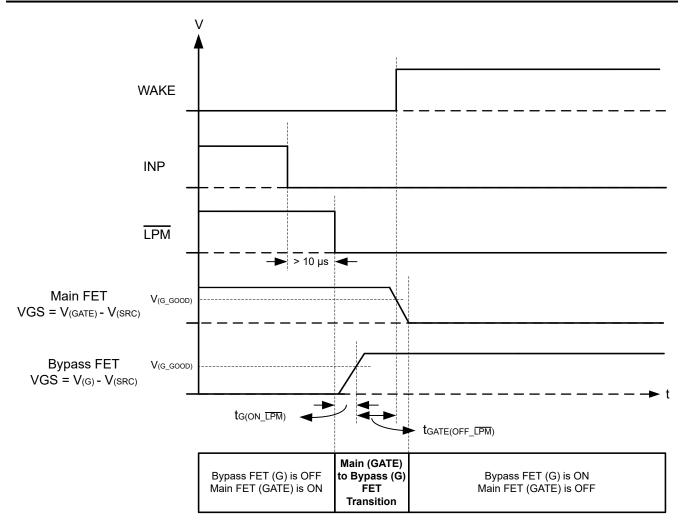

| t <sub>G_ON(LPM)</sub>   | Active mode to LPM mode transition delay | $\overline{\text{LPM}} \downarrow \text{to G} \uparrow, C_{L(G)} = 1 \text{ nF}$ |     | 1.8  | 9   | μs   |

Product Folder Links: TPS4812-Q1

## **6.6 Switching Characteristics (continued)**

$T_J$  = -40 °C to +125°C.  $V_{(VS)}$  = 48 V,  $V_{(BST-SRC)}$  = 12 V,  $V_{(SRC)}$  = 0 V

|                                              | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                                                                                  | MIN | TYP | MAX | UNIT |

|----------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>GATE_OFF(LPM)</sub>                   | Active mode to LPM mode transition delay                                                   | $\begin{array}{c} \overline{LPM}\downarrow, \ G\uparrow \ (above\ V_{(G\_GOOD)})\ to \\ GATE\ \downarrow,\ WAKE\uparrow \ (low\ to\ High\ Z)\ ,\ C_{L(GATE)}=47\ nF \end{array}$ |     | 37  | 51  | μs   |

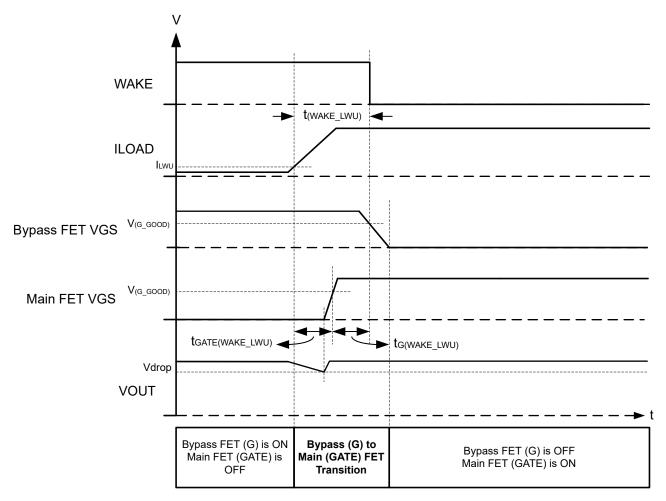

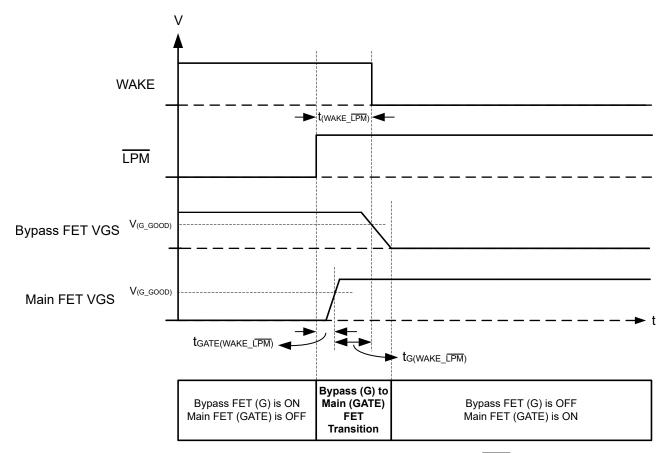

| t <sub>GATE(WAKE_LPM)</sub>                  | LPM Mode to Active mode transition delay with LPM trigger                                  | $\overline{\text{LPM}} \uparrow \text{ to GATE } \uparrow, \ C_{\text{L(GATE)}} = 47 \text{ nF}$                                                                                 |     | 3.8 | 6   | μs   |

| t <sub>G(WAKE_LPM)</sub>                     | LPM Mode to Active mode transition delay with LPM trigger                                  | $\overline{\text{LPM}} \uparrow$ , GATE $\uparrow$ (above $V_{(G\_GOOD)}$ ) to G $\downarrow$ , WAKE $\downarrow$ , $C_{L(G)}$ = 47 nF, $V_{(LPM)}$ = 0 V                        |     | 9   | 15  | μs   |

| t <sub>GATE(WAKE_LWU)</sub>                  | GATE turn ON propagation delay during Load wakeup                                          | $V_{(DRN-CS2-)}\uparrow V_{(LWU)}$ to GATE $\uparrow$ , $C_{L(GATE)}=47$ nF, $V_{(\overline{LPM})}=0$ V                                                                          |     | 4   | 5.5 | μs   |

| t <sub>G(WAKE_LWU)</sub>                     | G turn OFF propagation delay during Load wakeup                                            | $V_{(DRN-CS2-)} \uparrow V_{(LWU)}$ , GATE $\uparrow$ (above $V_{(G\_GOOD)}$ ) to $G \downarrow$ , WAKE $\downarrow$ , $C_{L(G)} = 47$ nF, $V_{(\overline{LPM})} = 0$ V          |     | 9   | 15  | μs   |

| t <sub>GATE(EN_OFF)</sub>                    | EN Turn OFF Propogation Delay                                                              | EN $\downarrow$ to GATE $\downarrow$ ,<br>C <sub>L(GATE)</sub> = 47 nF, $\overline{LPM}$ = High                                                                                  |     | 3.1 | 4.5 | μs   |

| t <sub>GATE(UVLO_OFF)</sub>                  | UVLO Turn OFF Propogation Delay                                                            | UVLO $\downarrow$ to GATE $\downarrow$ ,<br>C <sub>L(GATE)</sub> = 47 nF, $\overline{\text{LPM}}$ = High                                                                         |     | 4   | 6.5 | μs   |

| t <sub>GATE</sub> (UVLO_ON)                  | UVLO to GATE Turn ON Propogation<br>Delay with CBT pre-biased > VPORF<br>and INP kept high |                                                                                                                                                                                  |     | 8.5 | 25  | μs   |

| t <sub>GATE(VS_OFF)</sub>                    | GATE Turn OFF Propogation Delay<br>with VS falling < VPORF and INP, EN/<br>UVLO kept high  | VS $\downarrow$ (cross VPORF) to GATE $\downarrow$ ,<br>$C_{L(GATE)} = 47 \text{ nF}$ ,<br>INP = EN/UVLO = 2V, $\overline{LPM}$ = High                                           |     | 25  | 40  | μs   |

| t <sub>SC</sub>                              | Short Circuit Protection propogation<br>Delay in Active Mode                               | $V_{(CS1+-CS1-)} \uparrow V_{(SCP)}$ to GATE $\downarrow$ , $C_{L(GATE)} = 47$ nF, $V_{(\overline{LPM})} = 2$ V                                                                  |     | 3.9 | 5   | μs   |

| t <sub>LPM_SC</sub>                          | Short Circuit Protection propogation<br>Delay in LPM (Powerup into LPM with<br>short)      | $V_{(DRN-CS2-)} \uparrow V_{(LPM\_SCP)}$ to GATE $\uparrow$ , $C_{L(GATE)} = 47 \text{ nF}, V_{(LPM)} = 0 \text{ V}$                                                             |     | 3.1 | 4.5 | μs   |

| t <sub>GATE(FLT_ASSERT)</sub>                | FLT assertion delay during short circuit                                                   | $V_{(CS1+-CS1-)}\uparrow V_{(SCP)}$ to $\overline{FLT}$ $\downarrow$                                                                                                             |     | 15  | 21  | μs   |

| t <sub>GATE(FLT_DE_ASSER</sub> T)            | FLT de-assertion delay during short circuit                                                | $V_{(CS1+-CS1-)} \downarrow V_{(SCP)}$ to $\overline{FLT}$ $\uparrow$                                                                                                            |     | 3.8 |     | μs   |

| t <sub>GATE(FLT_ASSERT_B</sub><br>STUVLO)    | FLT assertion delay during GATE<br>Drive UVLO                                              | $V_{(GATE-SRC)} \downarrow V_{(BSTUVLOR)}$ to $\overline{FLT} \downarrow$                                                                                                        |     | 30  |     | μs   |

| t <sub>GATE(FLT_DE_ASSER</sub><br>T_BSTUVLO) | FLT de-assertion delay during GATE Drive UVLO                                              | $V_{(GATE-SRC)} \uparrow V_{(BSTUVLOR)}$ to $\overline{FLT} \uparrow$                                                                                                            |     | 15  |     | μs   |

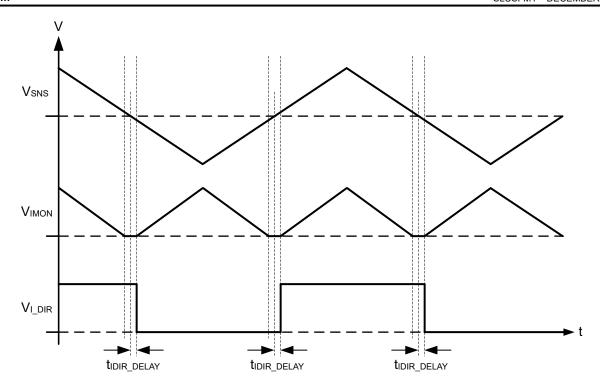

| t <sub>(IDIR_DELAY)</sub>                    | Delay for current direction indication on I_DIR pin                                        | $V_{(SNS)} \uparrow or \downarrow to V_{(I\_DIR)} \uparrow or \downarrow$                                                                                                        |     | 6.5 | 10  | μs   |

Product Folder Links: TPS4812-Q1

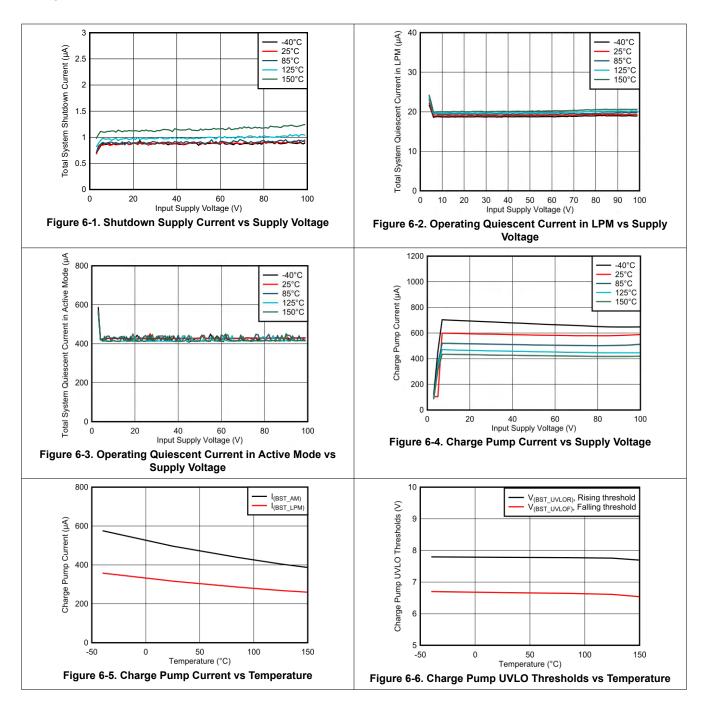

### 6.7 Typical Characteristics

## **6.7 Typical Characteristics (continued)**

Figure 6-8. Current Monitor Voltage ( $V_{(IMON)}$ ) vs Sense Voltage ( $V_{SNS}$ )

## **7 Parameter Measurement Information**

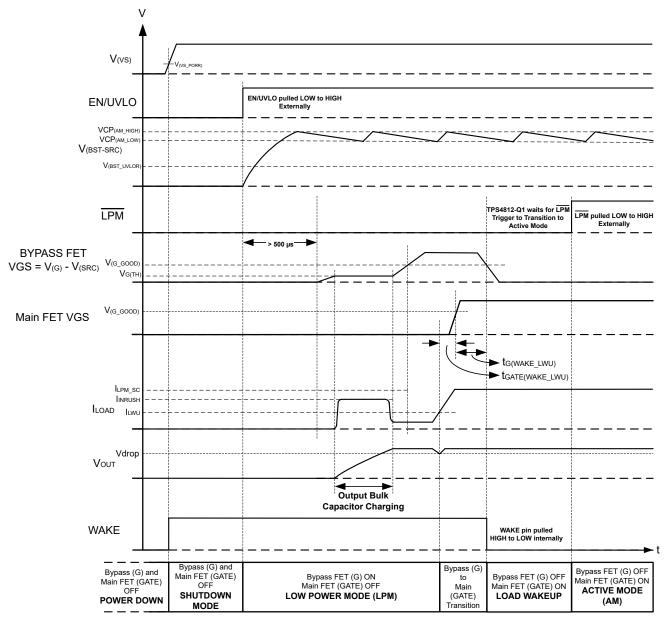

Figure 7-1. System Wake to Active Mode From Low Power Mode by Load Wakeup

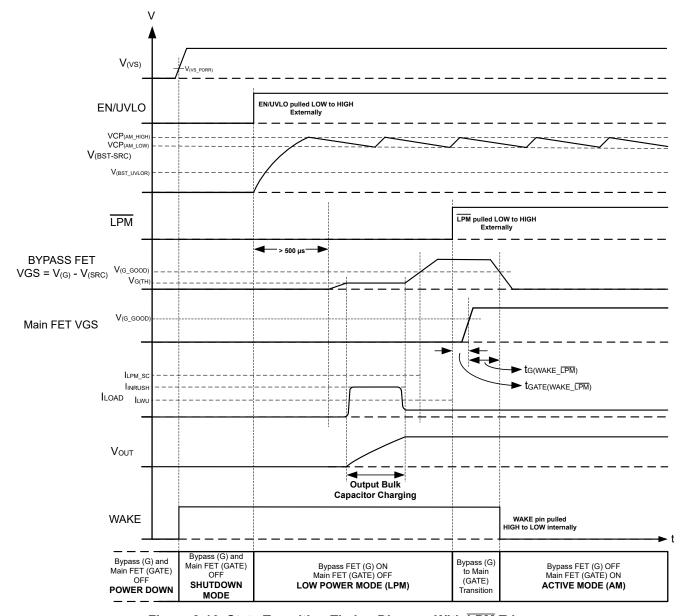

Figure 7-2. System Wake to Active Mode From Low Power Mode by LPM External Trigger

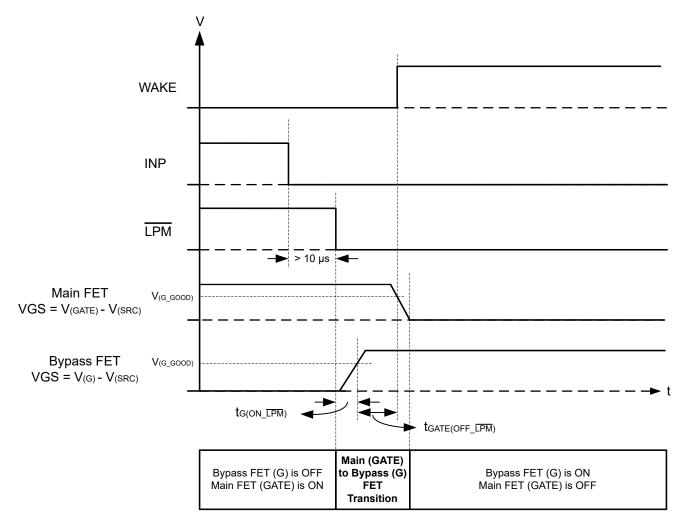

Figure 7-3. Active Mode to Low Power Mode by LPM Trigger

## 8 Detailed Description

#### 8.1 Overview

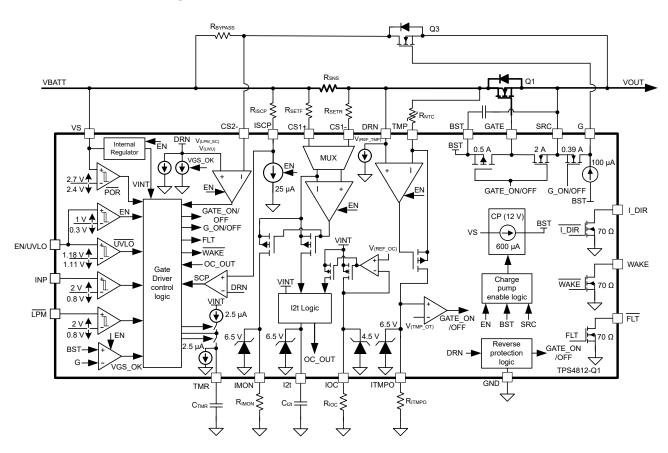

TPS4812-Q1 is a family of low  $I_Q$  smart high side drivers with protection and diagnostics. The TPS4812-Q1 has wide operating voltage range of 3.5V to 95V and 100V absolute-maximum rating. The device is suitable for 12V, 24V, and 48V automotive system designs.

TPS4812-Q1 has two integrated gate drives with 0.5A peak source and 2A sink gate driver to drive FETs in main path and 100µA source and 0.39A sink capacity for the low power path. The strong gate drive (GATE) enables power switching using parallel FETs in high current system designs where INP pin can be used as the GATE control input.

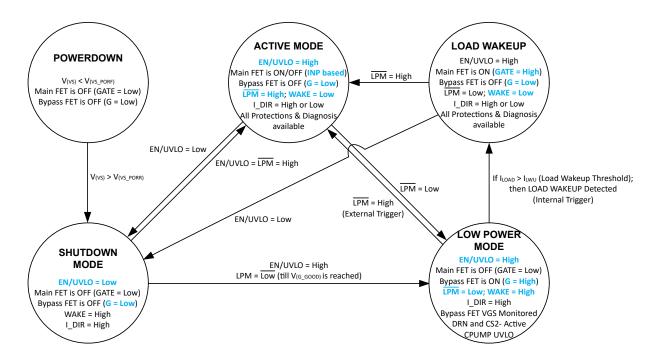

In the low power mode with  $\overline{\text{LPM}}$  = Low, the low power path FET (G drive) is kept ON and the main FETs (GATE drive) are turned OFF. The device consumes low I<sub>Q</sub> of 20µA (typ) in this mode. Auto load wakeup threshold and output bulk capacitor charging current can be programmed using R<sub>BYPASS</sub> resistor placed across DRN and CS2–pins in low power path. I<sub>Q</sub> reduces to 1µA (typical) with EN/UVLO pulled low. The device features WAKE output pin to indicate the mode of operation (Active/Low power mode).

The device has accurate current sensing ( $\pm 2\%$  at 30mV VSNS) output (IMON) enabling systems for energy management. The device has integrated accurate and adjustable I<sup>2</sup>t based overcurrent and short circuit protection by using an external R<sub>SNS</sub> resistor. Auto-retry and latch-off fault behavior can be configured.

TPS4812-Q1 indicate fault on open drain FLT output during overcurrent, short circuit, charge pump under voltage and external FET overtemperature conditions.

TPS4812-Q1 has integrated reverse polarity protection down to –65V and do not need any external components to protect the ICs during an input reverse polarity fault.

The device features NTC based temperature sensing (TMP) and monitor output (ITMPO) output to sense overtemperature of external FETs enabling robust thermal system designs.

The TPS4812x-Q1 is available in a 23-pin QFN package.

## 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Charge Pump and Gate Driver Output (VS, GATE, BST, SRC)

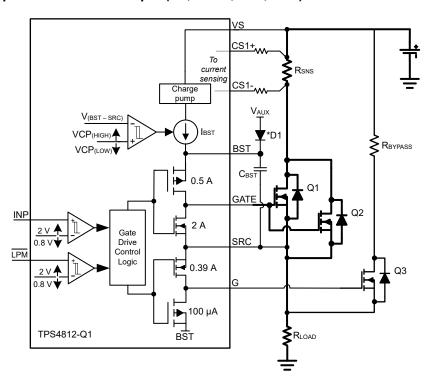

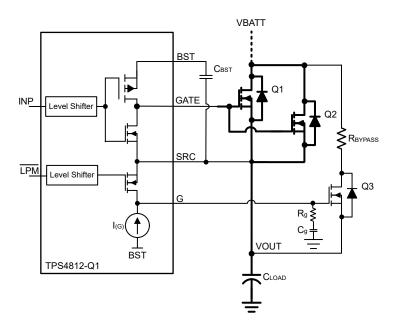

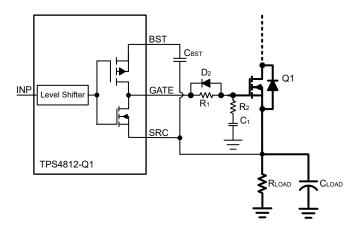

Figure 8-1. Gate Driver

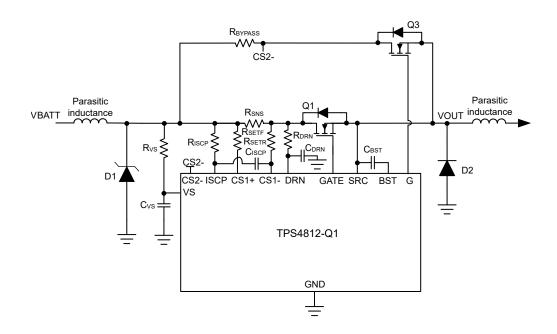

Figure 8-1 shows a simplified diagram of the charge pump and gate driver circuit implementation. The device houses a strong 0.5A/2A peak source/sink gate driver (GATE) for main FETs Q1, Q2, and  $100\mu A/0.39A$  peak source/sink current gate driver (G) for bypass FET Q3. The strong gate drivers enable paralleling of FETs in high power system designs ensuring minimum transition time in saturation region. A 12V in active mode,  $600\mu A$  charge pump is derived from VS terminal and charges the external boot-strap capacitor,  $C_{BST}$  that is placed across the gate driver (BST and SRC).

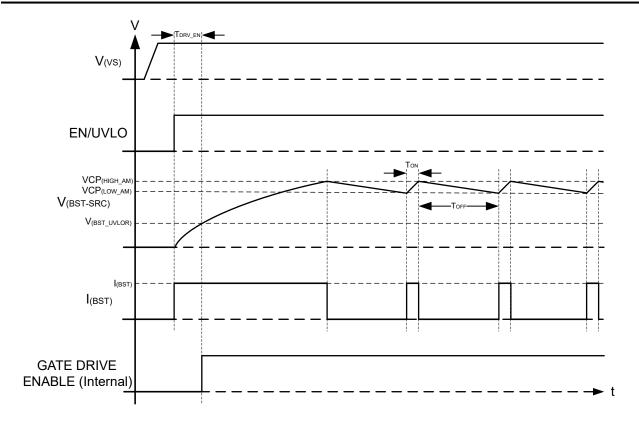

VS is the supply pin to the controller. With VS applied and EN/UVLO pulled high, the charge pump turns ON and charges the  $C_{BST}$  capacitor. After the voltage across  $C_{BST}$  crosses  $V_{(BST\_UVLOR)}$ , the GATE driver section is activated. The device has a 1V (typical) UVLO hysteresis to ensure chattering less performance during initial GATE turn ON. Choose  $C_{BST}$  based on the external FET  $Q_G$  and allowed dip during FET turn ON. In active mode, the charge pump remains enabled until the BST to SRC voltage reaches  $VCP_{(HIGH\_AM)}$ , typically, at which point the charge pump is disabled decreasing the current draw on the VS pin. The charge pump remains disabled until the BST to SRC voltage discharges to  $VCP_{(LOW\_AM)}$  typically at which point the charge pump is enabled.

The voltage between BST and SRC continue to charge and discharge between  $VCP_{(HIGH\_AM)}$  and  $VCP_{(LOW\_AM)}$  in active mode as shown in Figure 8-2:

Figure 8-2. Charge Pump Operation

Use Equation 1 to calculate the initial gate driver enable delay:

$$T_{DRV\_EN} = \frac{C_{BST} \times V_{(BST\_UVLOR)}}{600 \,\mu\text{A}} \tag{1}$$

Where,

C<sub>BST</sub> is the charge pump capacitance connected across BST and SRC pins.

$V_{(BST\ UVLOR)} = 7.6V (typ).$

If  $T_{DRV\_EN}$  needs to be reduced then pre-bias BST terminal externally using an external VAUX or input supply through a low leakage diode D1 as shown in Figure 8-3. With this connection,  $T_{DRV\_EN}$  reduces to 350 $\mu$ s.

Figure 8-3. TPS4812-Q1 Application Circuit With External Supply to BST

#### Note

$V_{AUX}$  can be supplied by external supply ranging between 8.1V and 15V. Input supply VS can also be connected to BST via D1 diode for reducing  $T_{DRV\ EN}$ .

#### 8.3.2 Capacitive Load Driving

Certain end equipment like automotive power distribution unit and zonal controller power different loads including other ECUs. These ECUs can have large input capacitances. If power to the ECUs is switched on in uncontrolled way, large inrush currents can occur and potentially damaging the power FETs.

To limit the inrush current during capacitive load switching, the following system design techniques can be used with TPS4812-Q1 device.

#### 8.3.2.1 Using Low-Power Bypass FET (G Drive) for Load Capacitor Charging

In high-current applications where several FETs are connected in parallel, the gate slew rate control for the main FETs is not recommended due to unequal distribution of inrush currents among the FETs resulting in over sizing of the FETs.

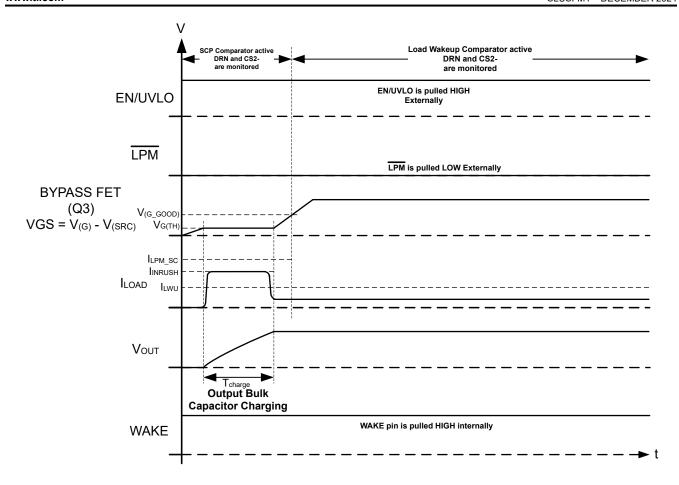

The TPS4812-Q1 integrates gate driver (G) with a dedicated control input ( $\overline{\text{LPM}}$ ) and bypass comparator between DRN and CS2– pins. This feature can be used to drive a separate low power bypass FET and pre-charge the capacitive load with inrush current limiting. Figure 8-4 shows the low power bypass FET implementation for capacitive load charging using TPS4812-Q1. An external capacitor  $C_g$  reduces the gate turn ON slew rate and controls the inrush current.

Figure 8-4. Capacitor Charging Using Gate (G) Slew Rate Control of Low-Power Bypass FET

During power-up with EN/UVLO pulled high and  $\overline{LPM}$  pulled low, the device turns ON bypass FET (G) by pulling G high with 100µA of source current and the main FETs (GATE) is kept OFF. In this low power mode (LPM), TPS4812-Q1 senses voltage between DRN and CS2– pins along with VGS of bypass FET (G to SRC). The voltage across DRN and CS2– is compared initially with  $V_{(LPM\_SCP)}$  threshold (2V typical) to detect powerup into short fault event until  $V_{(G\_GOOD)}$  threshold is reached.

After  $V_{(G\_GOOD)}$  threshold is reached, the voltage between DRN and CS2– is compared against  $V_{(LWU)}$  threshold (200mV typ) for load wakeup event. With this scheme capacitor charging current ( $I_{INRUSH}$ ) can be set at higher than load wakeup threshold ( $I_{LWU}$ ) and power-up into short event can also be detected reliably as shown in Figure 8-5.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

Figure 8-5. Timing Diagram for Bulk Capacitor Charging Using Bypass Path

#### **Setting the Load Wakeup Trigger Threshold:**

During normal operation, the series resistor  $R_{BYPASS}$  is used to set load wakeup current threshold. After  $V_{(G\_GOOD)}$  threshold is reached, the voltage between DRN and CS2– is compared against  $V_{(LWU)}$  threshold (200mV typ) for load wakeup event.

RBYPASS can be selected using Equation 2:

$$R_{\text{BYPASS}} = \frac{V_{\text{(LWU)}}}{I_{\text{LWU}}}$$

(2)

#### **Setting the INRUSH Current:**

Use Equation 3 to calculate the I<sub>INRUSH</sub>:

$$I_{INRUSH} = C_{LOAD} \times \frac{V_{BATT}}{T_{charge}}$$

(3)

Where,

C<sub>LOAD</sub> is the load capacitance.

$V_{BATT}$  is the input voltage and  $T_{charge}$  is the charge time.

$I_{INRUSH}$  should be always less than wakeup in short in low power mode ( $I_{LPM\_SC}$ ) current which can be calculated using Equation 4:

$$I_{LPM\_SC} = \frac{V_{(LPM\_SCP)}}{R_{BYPASS}}$$

(4)

Use Equation 5 to calculate the required  $C_q$  value.

$$C_{g} = \frac{C_{LOAD} \times I_{(G)}}{I_{INRUSH}}$$

(5)

Where,

$I_{(G)}$  is 100µA (typical),

A series resistor  $R_g$  must be used in conjunction with  $C_g$  to limit the discharge current from  $C_g$  during turn-off. The recommended value for  $R_g$  is between  $220\Omega$  to  $470\Omega$ .

After the output capacitor is charged, main FETs can be controlled (GATE drive) and bypass FET (G drive) can be turned OFF by driving  $\overline{\text{LPM}}$  high externally. The main FETs (G drive) can now be turned ON by driving INP high.

Figure 8-6 shows application circuit to charge large output capacitors using low power bypass path in high current applications.

Figure 8-6. TPS4812-Q1 Application Circuit for Capacitive Load Driving Using Low-Power Bypass FET (Q<sub>3</sub>) and Series Resistor (R<sub>BYPASS</sub>)

#### 8.3.2.2 Using Main FET (GATE Drive) Gate Slew Rate Control

In the applications where low power bypass path is not used, the cap charging can be done using main FET GATE drive control.

For limiting inrush current during turn-ON of the main FET with capacitive loads, use  $R_1$ ,  $R_2$ ,  $C_1$ , and  $D_2$  as shown in Figure 8-7. The  $R_1$  and  $C_1$  components slow down the voltage ramp rate at the gate of main FET. The FET source follows the gate voltage resulting in a controlled voltage ramp across the output capacitors.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

Figure 8-7. Inrush Current Limiting in Main Path

Use the Equation 6 to calculate the inrush current during turn-ON of the FET.

$$I_{INRUSH} = C_{LOAD} \times \frac{V_{BATT}}{T_{charge}}$$

(6)

$$C_1 = \frac{0.63 \times V_{(BST - SRC)} \times C_{LOAD}}{R_1 \times I_{INRUSH}}$$

(7)

Where,

C<sub>LOAD</sub> is the load capacitance.

VBATT is the input voltage and  $T_{\text{charge}}$  is the charge time.

$V_{(BST-SRC)}$  is the charge pump voltage (12V).

Use a damping resistor  $R_2$  (~10 $\Omega$ ) in series with  $C_1$ . Equation 8 can be used to compute required  $C_1$  value for a target inrush current. A 100k $\Omega$  resistor for  $R_1$  can be a good starting point for calculations.

D<sub>2</sub> ensures fast turn OFF of GATE drive by bypassing R<sub>1</sub>.

$C_1$  results in an additional loading on  $C_{BST}$  to charge during turn-ON. Use Equation 8 to calculate the required  $C_{BST}$  value:

$$C_{BST} = \frac{Q_{g(total)}}{\Delta V_{BST}} + 10 \times C_1$$

(8)

Where,

Q<sub>a(total)</sub> is the total gate charge of the FET.

$\Delta V_{BST}$  (1V typical) is the ripple voltage across BST to SRC pins.

#### 8.3.3 Overcurrent and Short-Circuit Protection

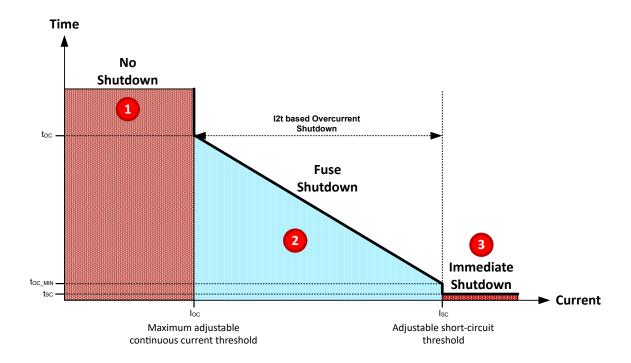

TPS4812-Q1 features integrated accurate  $I^2t$  functionality for the implementation of a robust and flexible overcurrent protection mechanism. This  $I^2t$  functionality features an intelligent circuit breaking aimed at protecting PCB traces, connectors and wire harness from overheating, with no impact on load transients like inrush currents and bulk capacitor charging.

The device also features accurate and configurable short-circuit protection threshold ( $I_{SC}$ ) with fixed response time ( $t_{SC}$  = 5us max).

Figure 8-8 shows the overall current-time characteristics.

- $\bullet \quad \text{Configurable I$^2$t based overcurrent protection (I$_{OC}$) threshold and adjustable response time (t$_{OC}$ and t$_{OC\_MIN}$)}$

- Adjustable short-circuit threshold (I<sub>SC</sub>) with internally fixed fast response (t<sub>SC</sub>)

Figure 8-8. Configurable Current vs Time characteristics curve for TPS4812-Q1

#### 8.3.3.1 I<sup>2</sup>t-Based Overcurrent Protection

The I2t profile for TPS4812-Q1 is set by two parameters which are I2t start overcurrent threshold, IOC and I<sup>2</sup>t ampere squared second factor (melting point or breaking point). The overcurrent protection time t<sub>OC</sub> is determined based on set I2t factor when load current is higher than set IOC threshold.

### Setting I<sup>2</sup>t Protection Starting Threshold, R<sub>IOC</sub>

The  $I^2$ t protection starting threshold  $I_{OC}$  is set using an external resistor  $R_{IOC}$  across IOC and GND pins.

Use Equation 9 to calculate the required  $R_{IOC}$  value:

$$R_{IOC}\left(\Omega\right) = \frac{V_{(REF\_OC)}}{K \times (I_{OC})^2} \tag{9}$$

Where.

V<sub>(REF OC)</sub> is internal reference voltage of 200mV.

I<sub>OC</sub> is the overcurrent level.

The scaling factor, K can be calculated by Equation 10:

Scaling factor

$$\left(K\right) = \frac{\left(0.1 \times \frac{R_{SNS}}{R_{SET}}\right)^2}{I_{BIAS}}$$

(10)

Where,

I<sub>BIAS</sub> is internal reference current of 5μA.

R<sub>SFT</sub> is the resistor connected across CS1+ and input battery supply.

R<sub>SNS</sub> is the current sense resistor.

#### Setting I<sup>2</sup>t Profile, C<sub>I2t</sub>

The device senses the voltage across the external current sense resistor (R<sub>SNS</sub>) through CS1+ and CS1-. When sensed voltage across R<sub>SNS</sub> exceeds I<sub>OC</sub> threshold set by R<sub>IOC</sub> resistor, C<sub>I2t</sub> capacitor starts charging with current proportional to I<sub>LOAD</sub> <sup>2</sup> – I<sub>OC</sub> <sup>2</sup> current.

The time to turn OFF the gate drive at maximum overcurrent limit (I<sub>OC MAX</sub>) can be determined using Equation 11:

$$t_{OC\_MIN}(s) = \frac{12T factor}{I_{OC\_MAX} \times I_{OC\_MAX}}$$

(11)

#### Note

The maximum overcurrent limit (I<sub>OC MAX</sub>) can 5% to 10% below short-circuit protection threshold (I<sub>SC</sub>).

Use Equation 12 to calculate the required  $C_{12t}$  value.

$$C_{I2t}\left(F\right) = \frac{K \times t_{OC\_MIN}}{V(I2t\_OC) - V(I2t\_OFFSET)} \times \left[I_{OC\_MAX}^2 - I_{OC}^2\right]$$

(12)

Where.

$V_{(12t OC)}$  is  $I^2$ t trip threshold voltage of 2V (typ).

$V_{(I2t\ OFFSET)}$  is offset voltage of 500mV (typ) on I2t pin during normal operation.

t<sub>OC MIN</sub> is the desired overcurrent response time at maximum overcurrent threshold I<sub>OC MAX</sub>.

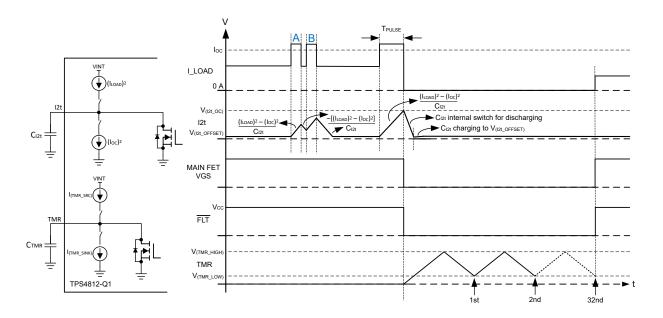

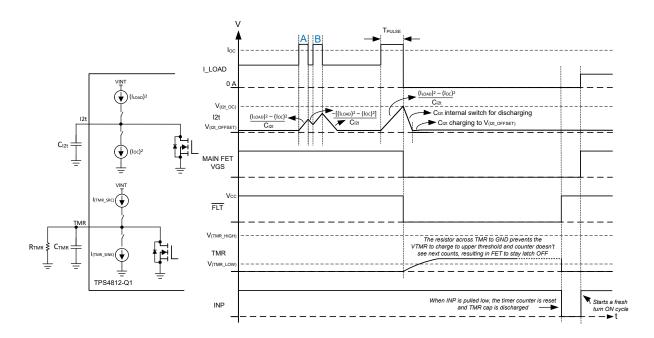

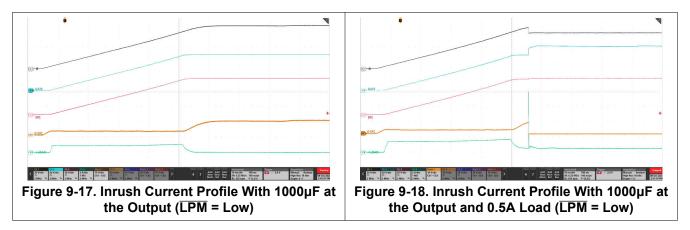

#### 8.3.3.1.1 I<sup>2</sup>t-Based Overcurrent Protection With Auto-Retry