**TPS389006** SNVSC50 - JUNE 2023

# TPS389006 Multichannel Overvoltage and Undervoltage I<sup>2</sup>C Programmable Voltage **Supervisor and Monitor**

## 1 Features

Texas

INSTRUMENTS

- **Functional Safety-Compliant**

- Development target for Functional Safety applications

- Documentation to aid IEC 61508 system design

- Systematic capability up to SIL 3

- Hardware capability up to SIL 3 \_

- Monitor state-of-the art SOCs

- ±6 mV threshold accuracy (-40°C to +125°C)

- Input voltage range: 2.5 V to 5.5 V

- Undervoltage lockout (UVLO): 2.48 V

- Low standby quiescent current: 200 µA

- 6 channels with 2 remote sense

- Fixed window threshold levels

- 5 mV steps from 0.2 V to 1.475 V

- 20 mV steps from 0.8 V to 5.5 V

- Miniature solution and minimal component cost

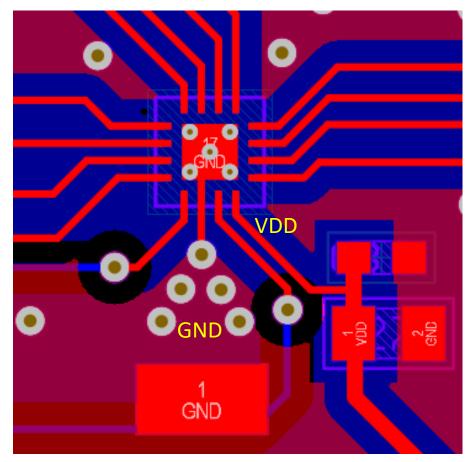

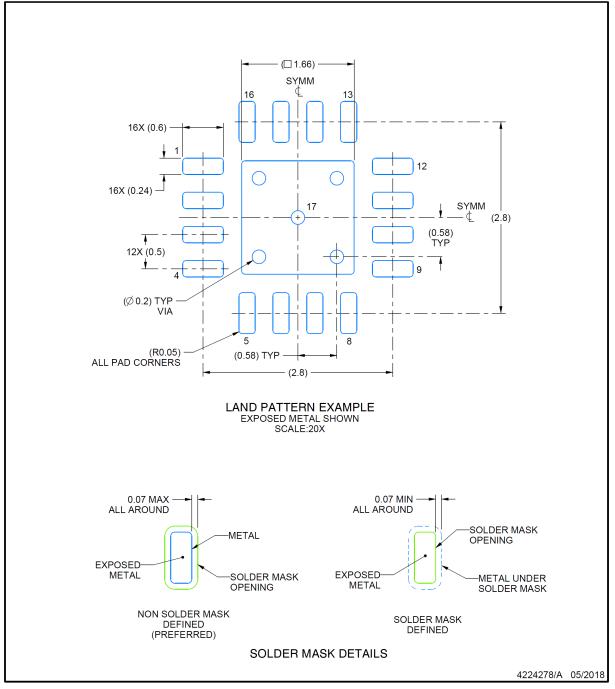

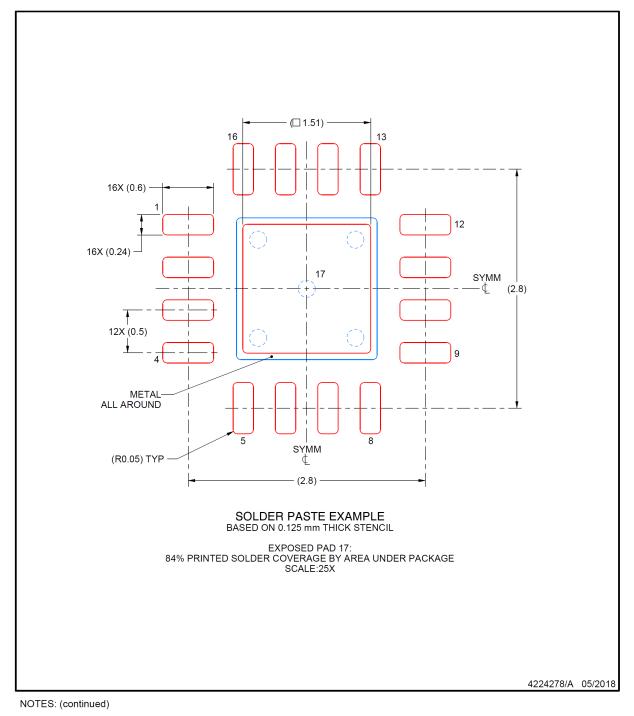

- 3 mm x 3 mm QFN package

- Adjustable glitch immunity via l<sup>2</sup>C

- User adjustable voltage threshold levels via I<sup>2</sup>C

- Designed for safety applications

- Active-low open-drain NIRQ output

- Built-in 8-bit ADC for real-time voltage readouts

- Cyclic Redundancy Checking (CRC)

- Packet Error Checking (PEC)

- Sequence and fault logging

- Sync function for rail tagging

- Connect with a multichannel sequencer for sequencing functionality

## 2 Applications

- Medical robotics

- Industrial robotics

- Server switches

- Motor drivers

## **3 Description**

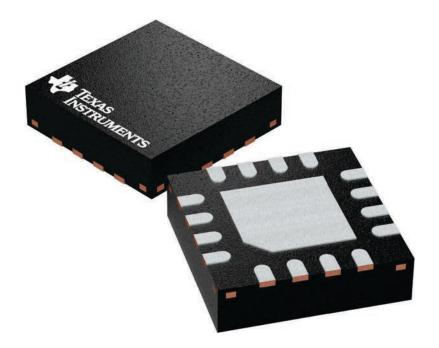

The TPS389006 device is a SIL-3 compliant sixchannel window supervisor IC with two remote sense pins available in a 16-pin 3 mm x 3 mm QFN package. This high accuracy multichannel voltage supervisor is designed for systems that operate on low-voltage supply rails and have narrow margin supply tolerances.

Remote sense pins enable a highly accurate voltage measurement on the high current core rail by accounting for voltage drop across PCB traces. I<sup>2</sup>C functionality gives flexibility in selecting thresholds, reset delays, glitch filters, and pin functionality. The internal glitch immunity and noise filters eliminate the need for external RC components to reduce false resets resulting from power transients. In addition, device does not require any external resistors for setting overvoltage and undervoltage reset thresholds, which further optimizes overall accuracy, cost, solution size, and improves reliability for safety systems.

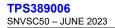

This device offers CRC error checking, sequence logging during turn ON or turn OFF, and a builtin ADC for voltage readouts to provide redundant error checking. In addition, TPS389006 offers a sync feature for tagging rails as they come up. The TPS389006 device also pairs with TI's power-supply sequencer TPS38700 to ensure proper power-on sequence in addition to voltage monitoring for SIL-3 level compliance.

#### **Device Information**

| PART NUMBER | PACKAGE (1) | BODY SIZE (NOM) |

|-------------|-------------|-----------------|

| TPS389006   | WQFN (16)   | 3 mm x 3 mm     |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

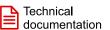

## **TPS389006 Typical Circuit**

## **Table of Contents**

| 1 Features                           | 1              |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        | 1              |

| 4 Revision History                   |                |

| 5 Device Comparison                  | 3              |

| 6 Pin Configuration and Functions    |                |

| 7 Specifications                     | <mark>5</mark> |

| 7.1 Absolute Maximum Ratings         | <mark>5</mark> |

| 7.2 ESD Ratings                      | <mark>5</mark> |

| 7.3 Recommended Operating Conditions |                |

| 7.4 Thermal Information              |                |

| 7.5 Electrical Characteristics       | <mark>6</mark> |

| 7.6 Timing Requirements              | <mark>8</mark> |

| 7.7 Typical Characteristics          | 10             |

| 8 Detailed Description               | 11             |

| 8.1 Overview                         | 11             |

| 8.2 Functional Block Diagram         | 12             |

| 8.3 Feature Description              | 13             |

| 8.4 Device Functional Modes          |                |

|                                      |                |

| 8.5 Register Maps                               | 29  |

|-------------------------------------------------|-----|

| 9 Application and Implementation                |     |

| 9.1 Application Information                     |     |

| 9.2 Typical Application                         |     |

| 10 Power Supply Recommendations                 |     |

| 10.1 Power Supply Guidelines                    |     |

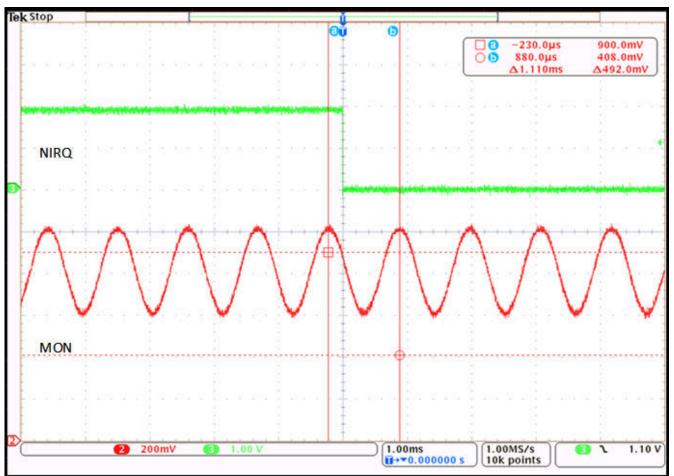

| 11 Layout                                       |     |

| 11.1 Layout Guidelines                          |     |

| 11.2 Layout Example                             | 106 |

| 12 Device and Documentation Support             |     |

| 12.1 Device Nomenclature                        |     |

| 12.2 Documentation Support                      | 108 |

| 12.3 Receiving Notification of Documentation Up |     |

| 12.4 Support Resources                          |     |

| 12.5 Trademarks                                 |     |

| 12.6 Electrostatic Discharge Caution            |     |

| 12.7 Glossary                                   |     |

| 13 Mechanical, Packaging, and Orderable         |     |

| Information                                     | 108 |

|                                                 |     |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE      | REVISION | NOTES           |

|-----------|----------|-----------------|

| June 2023 | *        | Initial Release |

## **5 Device Comparison**

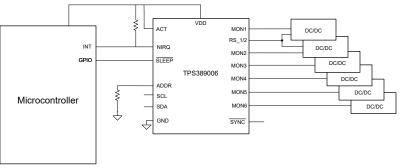

Figure 5-1 shows the device nomenclature of the TPS389006. Contact TI sales representatives or go online to TI's E2E forum for details and availability of other options; minimum order quantities apply.

See Section 12.1 for more information regarding the device ordering codes. Table 12-1 and Table 12-2 show how to decode the function of the device based on its part number.

Figure 5-1. TPS389006 Device Nomenclature

## **6** Pin Configuration and Functions

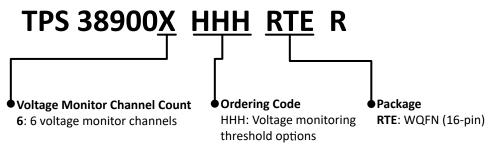

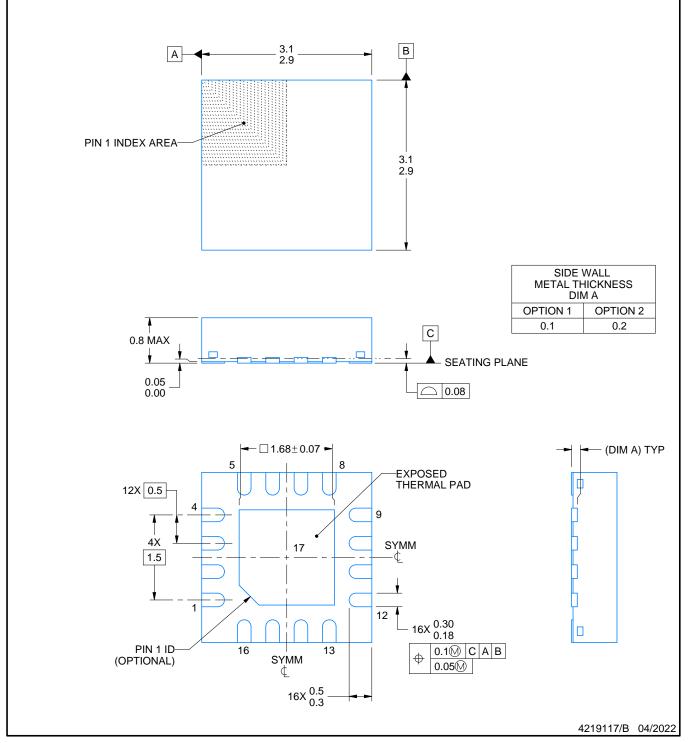

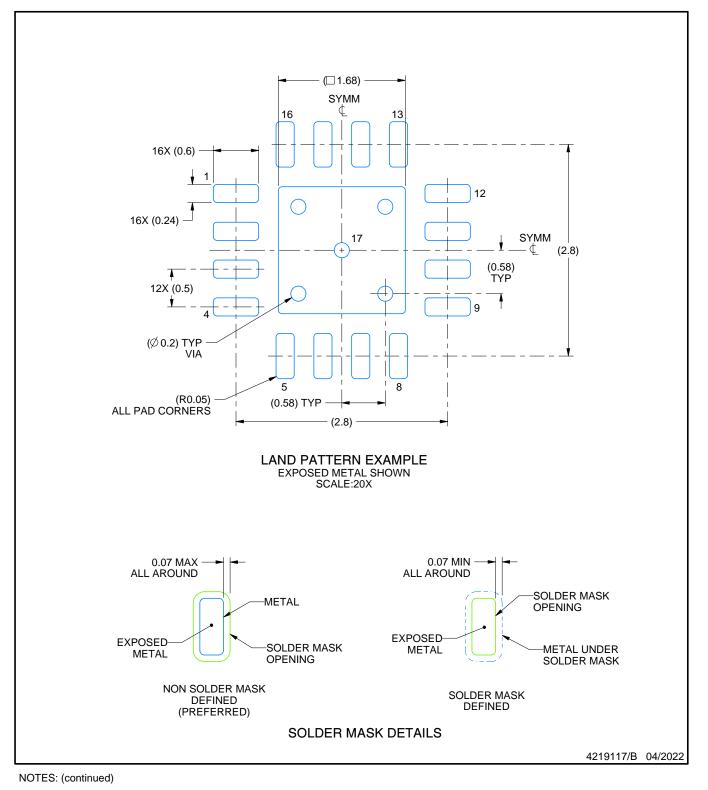

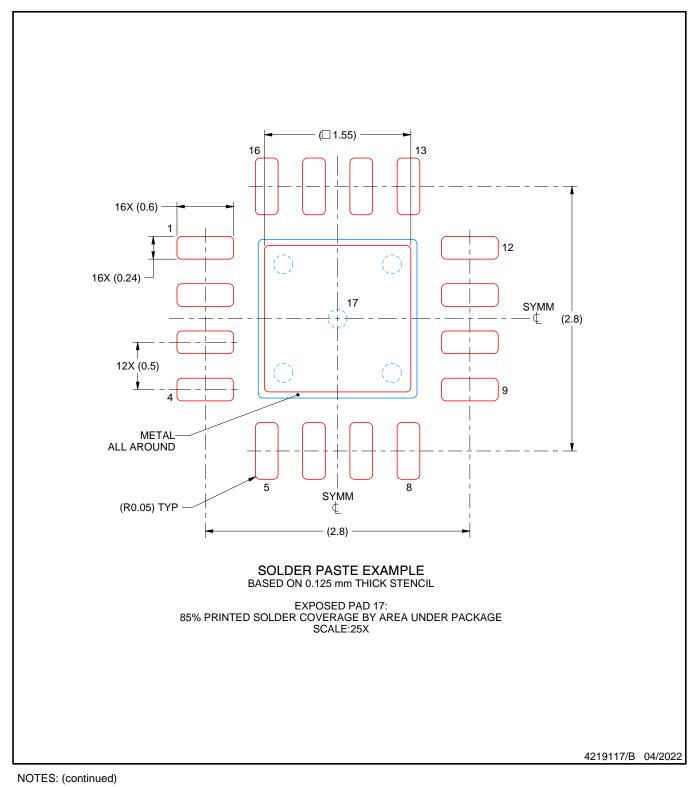

## Figure 6-1. RTE Package 16-Pin WQFN TPS389006 Top View

### Table 6-1. Pin Functions

|     | PIN       |     |                                                          |

|-----|-----------|-----|----------------------------------------------------------|

| NO. | TPS389006 | I/O | DESCRIPTION                                              |

| NO. | NAME      |     |                                                          |

| 1   | MON3      | I   | Voltage monitor channel 3                                |

| 2   | MON6      | I   | Voltage monitor channel 6                                |

| 3   | MON4      | I   | Voltage monitor channel 4                                |

| 4   | MON5      | I   | Voltage monitor channel 5                                |

| 5   | ACT       | I   | Active high device enable                                |

| 6   | GND       | -   | Power ground                                             |

| 7   | SLEEP     | I   | Active low sleep enable                                  |

| 8   | VDD       | -   | Power supply rail                                        |

| 9   | SYNC      | I/O | Sequence logging synchronization across multiple devices |

| 10  | MON2      | I   | Voltage monitor channel 2                                |

| 11  | RS_1/2    | I   | Voltage monitor channel 1/2 remote sense                 |

| 12  | MON1      | I   | Voltage monitor channel 1                                |

| 13  | NIRQ      | 0   | Active-low open-drain interrupt output                   |

| 14  | ADDR      | I   | I <sup>2</sup> C address select pin                      |

| 15  | SDA       | I/O | I <sup>2</sup> C data pin                                |

| 16  | SCL       | I   | I <sup>2</sup> C clock pin                               |

| 17  | GND       | -   | Exposed power ground pad                                 |

## **7** Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                            |                                                | MIN                         | MAX     | UNIT |

|----------------------------|------------------------------------------------|-----------------------------|---------|------|

| Voltage                    | VDD                                            | -0.3                        | 6       | V    |

| Voltage                    | NIRQ                                           | -0.3                        | 6       | V    |

| Voltage                    | ACT, SLEEP, SYNC, SCL, SDA                     | -0.3                        | VDD+0.3 | V    |

| Voltage                    | ADDR                                           | -0.3                        | 2       | V    |

| Voltage                    | MONx                                           | -0.3                        | 6       | V    |

| Current                    | NIRQ                                           |                             | ±10     | mA   |

|                            | Continuous total power dissipation             | See the Thermal Information |         |      |

| Temperature <sup>(2)</sup> | Operating junction temperature, T <sub>J</sub> | -40                         | 150     | °C   |

|                            | Operating free-air temperature, T <sub>A</sub> | -40                         | 125     | °C   |

|                            | Storage temperature, T <sub>stg</sub>          | -65                         | 150     | °C   |

(1) Stresses beyond values listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) As a result of the low dissipated power in this device, it is assumed that  $T_J = T_A$ .

## 7.2 ESD Ratings

|                                               |                                            |                         |             | VALUE | UNIT |

|-----------------------------------------------|--------------------------------------------|-------------------------|-------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic<br>discharge | Human-body model (HBM), per ANSI/ESDA/JEDE | C JS-001 <sup>(1)</sup> | ±2000       |       |      |

|                                               | Charged-device model (CDM), per AEC        | All pins                | ±500        | V     |      |

| uischarge                                     |                                            | Q100-011                | Corner pins | ±750  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification

## 7.3 Recommended Operating Conditions

|                                         |                                      | MIN | NOM MAX | UNIT |

|-----------------------------------------|--------------------------------------|-----|---------|------|

| VDD                                     | Supply pin voltage                   | 2.5 | 5.5     | V    |

| NIRQ                                    | Pin voltage                          | 0   | 5.5     | V    |

| I <sub>NIRQ</sub>                       | Pin Currents                         | 0   | ±1      | mA   |

| ADDR                                    | Address pin voltage                  | 0   | 1.8     | V    |

| MONx                                    | Monitor Pins                         | 0   | 5.5     | V    |

| ACT, <u>SLEEP,</u><br>SYNC, SCL,<br>SDA | Pin Voltage                          | 0   | VDD     | V    |

| R <sub>UP</sub> <sup>(1)</sup>          | Pull-up resistor (Open Drain config) | 10  | 100     | kΩ   |

## 7.4 Thermal Information

|                       |                                              | TPS389006  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                       |                                              | PINS       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 53.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 51.4       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 17.2       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 20.7       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.9        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

At 2.6 V <= VDD <= 5.5 V, NIRQ Voltage = 10 k $\Omega$  to V<sub>DD</sub>, NIRQ load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, typical conditions at VDD = 3.3 V.

|                            | PARAMETER                                                                                                        | TEST CONDITIONS           | MIN  | TYP  | MAX   | UNIT |

|----------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------|------|------|-------|------|

| COMMON PA                  | RAMETERS                                                                                                         |                           |      |      |       |      |

| VDD                        | Input supply voltage                                                                                             |                           | 2.6  |      | 5.5   | V    |

|                            | Rising Threshold                                                                                                 |                           | 2.67 |      | 2.81  | V    |

| VDD <sub>UVLO</sub>        | Falling Threshold                                                                                                |                           | 2.48 |      | 2.60  | V    |

| V <sub>POR</sub>           | Power on Reset Voltage <sup>(2)</sup>                                                                            |                           |      |      | 1.65  | V    |

| I <sub>DD_Active</sub>     | Supply current into VDD pin (MON =<br>LF/HF active)<br>ACT = High, Sleep = High                                  | VDD <= 5.5V               |      | 1.55 | 2     | mA   |

| DD_Sleep                   | Supply current into VDD pin (MON =<br>LF/HF active)<br>ACT = High ,Sleep = Low,I2C = Sleep<br>power bit set to 1 | VDD <= 5.5V               |      | 1.55 | 2     | mA   |

| I <sub>DD_Idle</sub>       | Supply current into VDD pin (MON =<br>OVLF active)<br>ACT = Low, Idle state-I2C active and<br>OVLF mon           | VDD <= 5.5V<br>>10ms BIST |      | 200  | 280   | μA   |

| I <sub>DD_Deep</sub> Sleep | Supply current into VDD pin (MON<br>= HF active), ACT = High,Sleep =<br>Low,I2C = Sleep power bit set to 0       | VDD <= 5.5V               |      | 275  | 380   | μA   |

| V <sub>MONX</sub>          | MON voltage range                                                                                                |                           | 0.2  |      | 5.5   | V    |

| I <sub>MONX</sub>          | Input current MONx pins                                                                                          | V <sub>MON</sub> = 5V     |      |      | 20    | μA   |

| MONX_ADJ                   | Input current for ADJ version (1x)                                                                               | V <sub>MON</sub> = 5V     |      |      | 0.1   | μA   |

| VMON_LF                    | 1x mode (No scaling)                                                                                             |                           | 0.2  |      | 1.475 | V    |

|                            | with 4x scaling                                                                                                  |                           | 0.8  |      | 5.5   | V    |

| VMON HF                    | 1x mode (No scaling)                                                                                             |                           | 0.2  |      | 1.475 | V    |

|                            | with 4x scaling                                                                                                  |                           | 0.8  |      | 5.5   | V    |

| Threshold                  | 1x mode (No scaling) LSB                                                                                         |                           |      | 5    |       | mV   |

| granularity_H<br>F         | 4x mode (With scaling) LSB                                                                                       |                           |      | 20   |       | mV   |

| LPF cutoff LF              | Range of Programmable values (I <sup>2</sup> C selectable)                                                       | Low Freq channel          | 250  |      | 4000  | Hz   |

| LPF cutoff<br>HF           |                                                                                                                  | High Freq channel         |      | 4    |       | Mhz  |

## 7.5 Electrical Characteristics (continued)

At 2.6 V <= VDD <= 5.5 V, NIRQ Voltage = 10 k $\Omega$  to V<sub>DD</sub>, NIRQ load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, typical conditions at VDD= 3.3 V.

|                       | PARAMETER                                                                      | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT |

|-----------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

|                       |                                                                                | 0.2V≤V <sub>MONX</sub> ≤1.0V                                           | 6    |      | 6    | mV   |

| A                     |                                                                                | 1.0V <v<sub>MONX≤1.475V</v<sub>                                        | -7.5 |      | 7.5  | mV   |

| Accuracy_HF           | VMON                                                                           | 1.475V <v<sub>MONX≤2.95V</v<sub>                                       | -0.6 |      | 0.6  | %    |

|                       |                                                                                | VMONX>2.95V                                                            | -0.7 |      | 0.7  | %    |

|                       | Hysteresis on UV,OV pin(Hysteresis is with respect of the tripoint ((UV),(OV)) | 0.2V≤V <sub>MONX</sub> ≤1.475V                                         |      | 5    | 11   |      |

| V <sub>HYS_HF</sub>   |                                                                                | 1.475V <v<sub>MONX≤2.95V</v<sub>                                       |      | 9    | 16   | mV   |

|                       | (1)                                                                            | VMONX>2.95V                                                            |      | 17   | 28   | mV   |

| MON_OFF               | OFF Voltage threshold                                                          | Monitored falling edge of V <sub>MON</sub>                             | 140  |      | 215  | mV   |

| LKG                   | Output leakage current -NIRQ                                                   | VDD=V <sub>NIRQ</sub> =5.5V                                            |      |      | 300  | nA   |

| ACT_L                 | Logic Low input                                                                | DEV_CONFIG.SOC_IF1=1                                                   |      |      | 0.36 | V    |

| ACT_H                 | Logic high input                                                               | DEV_CONFIG.SOC_IF1=1                                                   | 0.84 |      |      | V    |

| SLEEP_L               | Logic Low input                                                                | DEV_CONFIG.SOC_IF1=1                                                   |      |      | 0.36 | V    |

| SLEEP_H               | Logic high input                                                               | DEV_CONFIG.SOC_IF1=1                                                   | 0.84 |      |      | V    |

| SYNC_L                | Input High                                                                     | DEV_CONFIG.SOC_IF1=1                                                   |      |      | 0.36 | V    |

| SYNC_H                | Input Low                                                                      | DEV_CONFIG.SOC_IF1=1                                                   | 0.84 |      |      | V    |

| SYNC_PU               | Internal Pull-up                                                               |                                                                        | 25   |      | 100  | kΩ   |

| SYNC_OL               | with 10kΩ external pull up                                                     |                                                                        |      |      | 0.1  | V    |

| ACT                   | Internal Pull down                                                             |                                                                        |      | 100  |      | kΩ   |

| SLEEP                 | Internal Pull down                                                             |                                                                        |      | 100  |      | kΩ   |

|                       | Steps/Resolution                                                               | 0.2V <v<sub>MONX≤1.475V</v<sub>                                        |      | 5    |      |      |

| UV,OV                 |                                                                                | 0.8V <v<sub>MONX&lt;5.5V</v<sub>                                       |      | 20   |      | mV   |

| V <sub>OL</sub>       | Low level output voltage-NIRQ                                                  | NIRQ ,5.5V/5mA                                                         |      |      | 100  | mV   |

| I <sub>lkg(OD)</sub>  | Open-Drain output leakage current-<br>NIRQ                                     | NIRQ pin in High Impedance,V <sub>NIRQ</sub> = 5.5, Not asserted state |      |      | 90   | nA   |

| I <sub>ADDR</sub>     | ADDR pin current                                                               |                                                                        |      | 20   |      | μA   |

|                       |                                                                                | R=5.36k                                                                |      | 0x30 |      |      |

|                       |                                                                                | R=16.2k                                                                |      | 0x31 |      |      |

|                       |                                                                                | R=26.7k                                                                |      | 0x32 |      |      |

| I <sup>2</sup> C ADDR |                                                                                | R=37.4k                                                                |      | 0x33 |      |      |

|                       | (Hex format)                                                                   | R=47.5k                                                                |      | 0x34 |      |      |

|                       |                                                                                | R=59.0k                                                                |      | 0x35 |      |      |

|                       |                                                                                | R=69.8k                                                                |      | 0x36 |      |      |

|                       |                                                                                | R=80.6k                                                                |      | 0x37 |      |      |

| TSD                   | Thermal Shutdown                                                               |                                                                        |      | 155  |      | °C   |

| TSD Hys               | Thernal Shutdown Hysterisis                                                    |                                                                        |      | 20   |      | °C   |

| RS                    | Remote sense range                                                             |                                                                        | -100 |      | 100  | mV   |

| ADC SPECIFI           | CATION                                                                         |                                                                        |      |      | 1    |      |

| Vin                   | Input Range                                                                    |                                                                        | 0.2  |      | 5.5  | V    |

|                       | Developing                                                                     | 1x mode (No scaling)                                                   |      | 5    |      | mV   |

| Res_LF                | Resolution                                                                     | 4x mode                                                                |      | 20   |      | mV   |

| f <sub>S</sub>        | Sample Rate                                                                    |                                                                        |      | 125  |      | ksps |

| V <sub>HYS_LF</sub>   | Hysteresis LF faults                                                           | 1x mode (No scaling)                                                   |      | 10   | 15   | mV   |

| V <sub>HYS_LF</sub>   | Hysteresis LF faults                                                           | 4x mode                                                                |      | 40   | 55   | mV   |

## 7.5 Electrical Characteristics (continued)

At 2.6 V <= VDD <= 5.5 V, NIRQ Voltage = 10 k $\Omega$  to V<sub>DD</sub>, NIRQ load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, typical conditions at VDD= 3.3 V.

|                | PARAMETER                       | TEST CONDITIONS      | MIN | TYP MA | X UI | NIT |

|----------------|---------------------------------|----------------------|-----|--------|------|-----|

| Accuracy_LF    | VMON                            | 1x mode (No scaling) | -12 | +'     | 2 n  | nV  |

|                |                                 | 4x mode              | -40 | +4     | 0 n  | nV  |

| 12C ELECTRI    | I2C ELECTRICAL SPECIFICATIONS   |                      |     |        |      |     |

| C <sub>B</sub> | Capacitive load for SDA and SCL |                      |     | 40     | 0 F  | ρF  |

| SDA,SCL        | Low Threshold                   | DEV_CONFIG.SOC_IF1=0 |     | 0      | 8    | V   |

| SDA,SCL        | High Threshold                  | DEV_CONFIG.SOC_IF1=0 | 2.0 |        |      | V   |

(1) Hysteresis is with respect of the tripoint  $(V_{IT-(UV)}, V_{IT+(OV)})$ .

(2)  $V_{POR}$  is the minimum  $V_{DDX}$  voltage level for a controlled output state.

## 7.6 Timing Requirements

At 2.6 V  $\leq$  VDD  $\leq$  5.5 V, NIRQ Voltage = 10 k $\Omega$  to VDD, NIRQ load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, typical conditions at VDD = 3.3 V.

|                         |                                                                                     |                        | MIN | NOM | MAX   | UNIT |

|-------------------------|-------------------------------------------------------------------------------------|------------------------|-----|-----|-------|------|

| COMMON F                | PARAMETERS                                                                          |                        |     |     | •     |      |

| t <sub>BIST</sub>       | POR to ready with BIST, TEST_CFG.AT_POR=1                                           | includes OTP load      |     |     | 12    | ms   |

| t <sub>NBIST</sub>      | POR to ready without BIST, TEST_CFG.AT_POR=0                                        | includes OTP load      |     |     | 2     | ms   |

| BIST                    | BIST time,TEST_CFG.AT_POR=1 or<br>TEST_CFG.AT_SHDN=1                                |                        |     |     | 10    | ms   |

| t <sub>I2C_ACT</sub>    | I <sup>2</sup> C active from BIST complete                                          |                        |     |     | 0     | μs   |

| t <sub>SEQ_Range</sub>  | Sequence timestamp range, ACT or SLEEP edge to max counter                          |                        |     |     | 4     | s    |

| t <sub>SEQ_LSB</sub>    | Sequence timestamp resolution                                                       |                        |     | 50  |       | μs   |

| t <sub>MON_ACT</sub>    | Monitoring active from ACT rising edge                                              |                        |     |     | 10    | μs   |

| t <sub>SEQ_ACT</sub>    | Sequence tagging active from ACT or SLEEP edge                                      |                        |     |     | 12    | μs   |

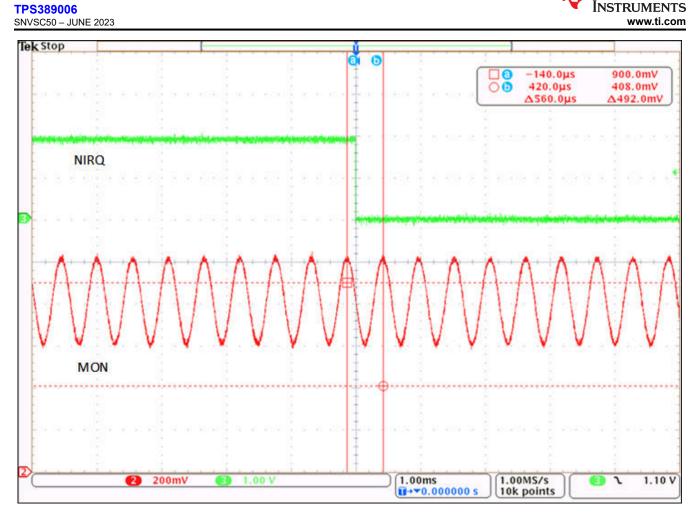

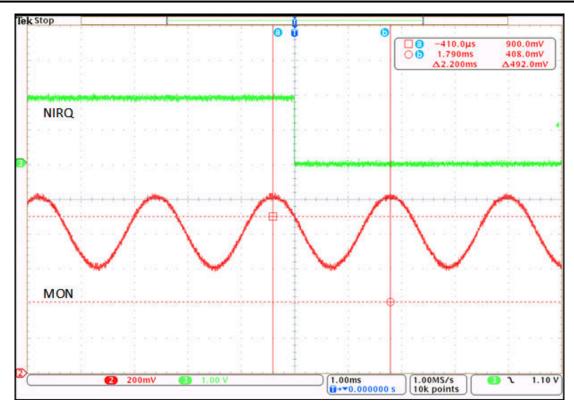

| t <sub>NIRQ</sub>       | Fault detection to NIRQ assertion latency (except OV/UV faults)                     |                        |     |     | 25    | μs   |

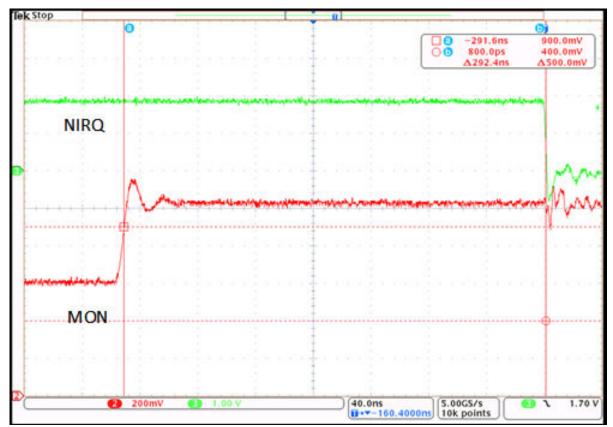

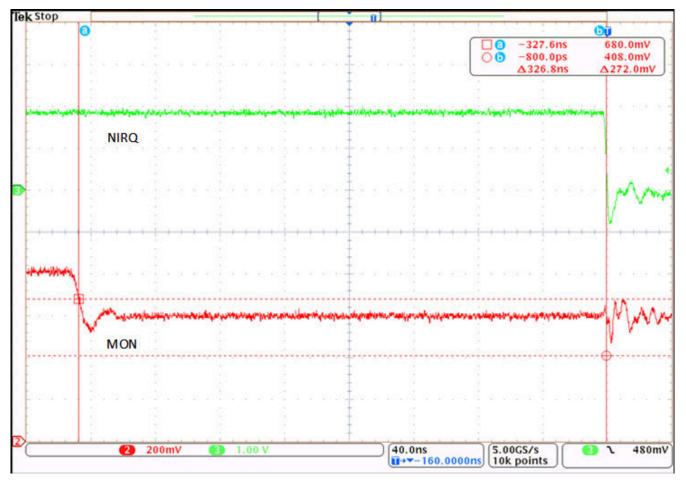

| t <sub>PD_NIRQ_1X</sub> | HF fault Propagation detect delay (default deglitch filter) includes digitial delay | VIT_OV/UV +/-<br>100mV |     |     | 650   | ns   |

| t <sub>PD_NIRQ_4X</sub> | HF fault Propagation detect delay (default deglitch filter) includes digitial delay | VIT_OV/UV +/-<br>400mV |     |     | 750   | ns   |

| t <sub>SEQ_ACC</sub>    | Accuracy of sequence timestamp                                                      |                        | -5  |     | 5     | %    |

| t <sub>GI_R</sub>       | UV & OV debounce range via I2C                                                      | FLT_HF(N)              | 0.1 |     | 102.4 | μs   |

## 7.6 Timing Requirements (continued)

At 2.6 V  $\leq$  VDD  $\leq$  5.5 V, NIRQ Voltage = 10 k $\Omega$  to VDD, NIRQ load = 10 pF, and over the operating free-air temperature range of – 40°C to 125°C, unless otherwise noted. Typical values are at T<sub>J</sub> = 25°C, typical conditions at VDD = 3.3 V.

|                     |                                                       |                                                | MIN  | NOM | MAX  | UNIT |

|---------------------|-------------------------------------------------------|------------------------------------------------|------|-----|------|------|

| I2C TIMIN           | IG CHARACTERISTICS                                    |                                                |      |     |      |      |

| f <sub>SCL</sub>    | Serial clock frequency                                | Standard mode                                  |      |     | 100  | kHz  |

| f <sub>SCL</sub>    | Serial clock frequency                                | Fast mode                                      |      |     | 400  | kHz  |

| f <sub>SCL</sub>    | Serial clock frequency                                | Fast mode +                                    |      |     | 1    | MHz  |

| t <sub>LOW</sub>    | SCL low time                                          | Standard mode                                  | 4.7  |     |      | μs   |

| t <sub>LOW</sub>    | SCL low time                                          | Fast mode                                      | 1.3  |     |      | μs   |

| t <sub>LOW</sub>    | SCL low time                                          | Fast mode +                                    | 0.5  |     |      | μs   |

| t <sub>HIGH</sub>   | SCL high time                                         | Standard mode                                  | 4    |     |      | μs   |

| t <sub>HIGH</sub>   | SCL high time                                         | Fast mode +                                    | 0.26 |     |      | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                       | Standard mode                                  | 250  |     |      | ns   |

| t <sub>SU;DAT</sub> | Data setup time                                       | Fast mode                                      | 100  |     |      | ns   |

| t <sub>SU;DAT</sub> | Data setup time                                       | Fast mode +                                    | 50   |     |      | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                        | Standard mode                                  | 10   |     | 3450 | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                        | Fast mode                                      | 10   |     | 900  | ns   |

| t <sub>HD;DAT</sub> | Data hold time                                        | Fast mode +                                    | 10   |     |      | ns   |

| t <sub>SU;STA</sub> | Setup time for a Start or Repeated Start condition    | Standard mode                                  | 4.7  |     |      | μs   |

| t <sub>SU;STA</sub> | Setup time for a Start or Repeated Start condition    | Fast mode                                      | 0.6  |     |      | μs   |

| t <sub>SU;STA</sub> | Setup time for a Start or Repeated Start condition    | Fast mode +                                    | 0.26 |     |      | μs   |

| t <sub>HD:STA</sub> | Hold time for a Start or Repeated Start condition     | Standard mode                                  | 4    |     |      | μs   |

| t <sub>HD:STA</sub> | Hold time for a Start or Repeated Start condition     | Fast mode                                      | 0.6  |     |      | μs   |

| t <sub>HD:STA</sub> | Hold time for a Start or Repeated Start condition     | Fast mode +                                    | 0.26 |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition      | Standard mode                                  | 4.7  |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition      | Fast mode                                      | 1.3  |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition      | Fast mode +                                    | 0.5  |     |      | μs   |

| t <sub>su;sтo</sub> | Setup time for a Stop condition                       | Standard mode                                  | 4    |     |      | μs   |

| t <sub>su;sтo</sub> | Setup time for a Stop condition                       | Fast mode                                      | 0.6  |     |      | μs   |

| t <sub>su;sтo</sub> | Setup time for a Stop condition                       | Fast mode +                                    | 0.26 |     |      | μs   |

| trDA                | Rise time of SDA signal                               | Standard mode                                  |      |     | 1000 |      |

| trDA                | Rise time of SDA signal                               | Fast mode                                      | 20   |     | 300  | ns   |

| trDA                | Rise time of SDA signal                               | Fast mode +                                    |      |     | 120  | ns   |

| tfDA                | Fall time of SDA signal                               | Standard mode                                  |      |     | 300  | ns   |

| tfDA                | Fall time of SDA signal                               | Fast mode                                      | 1.4  |     | 300  | ns   |

| tfDA                | Fall time of SDA signal                               | Fast mode +                                    | 6.5  |     | 120  | ns   |

| trCL                | Rise time of SCL signal                               | Standard mode                                  |      |     | 1000 | ns   |

| trCL                | Rise time of SCL signal                               | Fast mode                                      | 20   |     | 300  | ns   |

| trCL                | Rise time of SCL signal                               | Fast mode +                                    |      |     | 120  | ns   |

| tfCL                | Fall time of SCL signal                               | Standard mode                                  |      |     | 300  | ns   |

| tfCL                | Fall time of SCL signal                               | Fast mode                                      | 6.5  |     | 300  | ns   |

| tfCL                | Fall time of SCL signal                               | Fast mode +                                    | 6.5  |     | 120  | ns   |

| tSP                 | Pulse width of SCL and SDA spikes that are suppressed | Standard mode,<br>Fast mode and Fast<br>mode + |      |     | 50   | ns   |

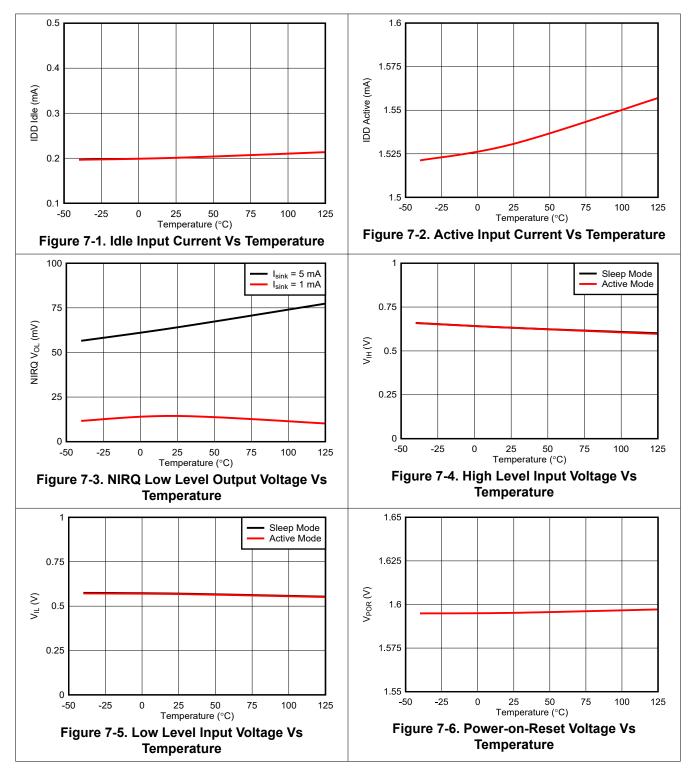

## 7.7 Typical Characteristics

At  $T_J = 25^{\circ}C$ ,  $V_{DD} = 3.3$  V, and  $R_{PU} = 10$  k $\Omega$ , unless otherwise noted.

## 8 Detailed Description

## 8.1 Overview

The TPS389006 family of devices has six channels that can be configured for over voltage, under voltage or both in a window configuration. The TPS389006 features highly accurate window threshold voltages (up to  $\pm 6 \text{ mV}$ ) and a variety of voltage thresholds which can be factory configured or set on boot up by I<sup>2</sup>C commands.

The TPS389006 includes the resistors used to set the overvoltage and undervoltage thresholds internal to the device. These internal resistors allow for lower component counts and greatly simplifies the design because no additional margins are needed to account for the accuracy of external resistors.

The TPS389006 also has a sequence logging feature to monitor and assign timestamps/log for the power rails turning on and off. It can perform sequence logging on a single device or across multiple devices on a board. It uses the <u>SYNC</u> pin to communicate across multiple devices. When either the ACT or <u>SLEEP</u> pin transistions from low to high or high to low, the sequence logging function becomes active until the expiry of the sequence timeout (SEQ\_TOUT). During the sequence timeout, the UV faults can be masked (Automask - AMSK).

The TPS389006 is designed to assert active low output signals (NIRQ) when the monitored voltage is outside the safe window. The factory configuration can have the interrupts disabled for over voltage and under voltage faults, sequence timeout, BIST enabled at POR, sequence fault interrupts disabled, and over voltage and under voltage deglitch settings depending on the OTP.

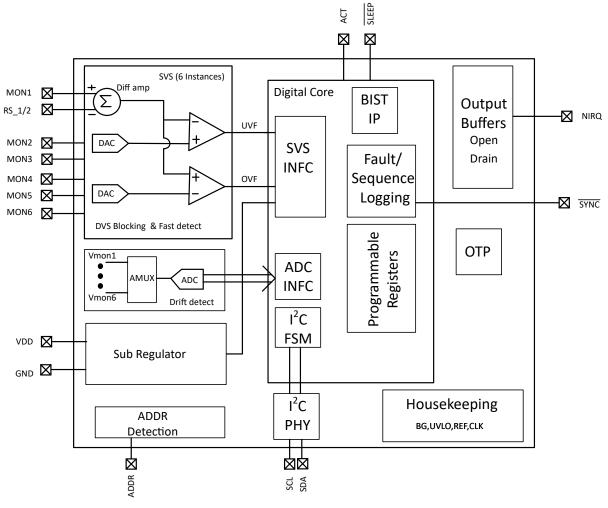

## 8.2 Functional Block Diagram

## 8.3 Feature Description

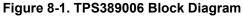

## 8.3.1 I<sup>2</sup>C

The TPS389006 device follows the I<sup>2</sup>C protocol (up to 1MHz) to manage communication with host devices such as a MCU or System on Chip (SoC). I<sup>2</sup>C is a two wire communication protocol implmented using two signals, clock (SCL) and data (SDA). The host device is the primary controller of communication. TPS389006 device responds over the data line during read or write operations as defined by I<sup>2</sup>C protocol. Both SCL and SDA signals are open drain topology and can be used in a wired-OR configuration with other devices to share the communication bus. Both SCL and SDA pins need an external pull up resistor to supply voltage (10 k $\Omega$  recommended).

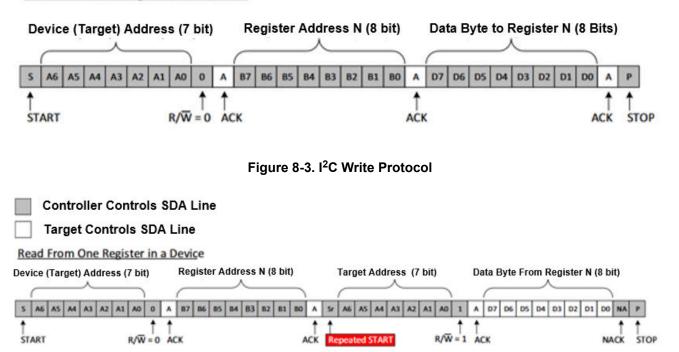

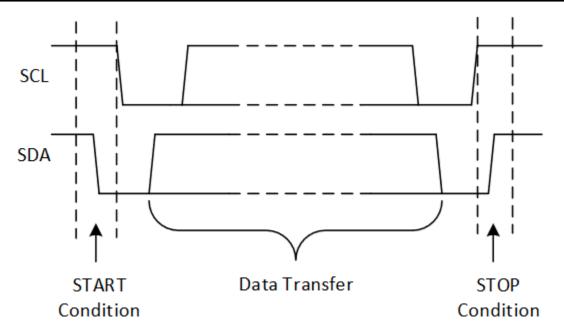

Figure 8-2 shows the timing relationship between SCL and SDA lines to transfer 1 byte of data. SCL line is always controlled by host. To transfer 1 byte data, host needs to send 9 clocks on SCL. 8 clocks for data and 1 clock for ACK or NACK. SDA line is controlled by either the host or TPS389006 device based on the read or write operation. Figure 8-2 and Figure 8-3 highlight the communication protocol flow and which device controls SDA line at various instances during active communication.

Figure 8-2. SCL to SDA Timing for 1 Byte Data Transfer

**Controller Controls SDA Line**

Target Controls SDA Line

## Write to One Register in a Device

## Figure 8-4. I<sup>2</sup>C Read Protocol

Before initiating communication over  $I^2C$  protocol, host needs to confirm the  $I^2C$  bus is available for communication. Monitor the SCL and SDA lines, if any line is pulled low, the  $I^2C$  bus is occupied. Host needs to wait until the bus is available for communication. Once the bus is available for communication, the host can initiate read or write operation by issuing a START condition. Once the  $I^2C$  communication is complete, release the bus by issuing STOP command. Figure 8-5 shows how to implement START and STOP condition.

## Figure 8-5. I<sup>2</sup>C START and STOP Condition

| Table 8-1 shows the different functionality available when programming with $I^2C$ . |  |

|--------------------------------------------------------------------------------------|--|

| Table 8.1. User Programmable 12C Eurotions                                           |  |

| Table                                          | Table 8-1. User Programmable I <sup>2</sup> C Functions                            |  |  |  |  |  |

|------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|--|--|

| FUNCTIONS                                      | DESCRIPTION                                                                        |  |  |  |  |  |

| Thresholds for OV/UV- fast loop                | Adjustable in 5 mV steps from 0.2 V to 1.475 V and 20 mV steps from 0.8 V to 5.5 V |  |  |  |  |  |

| Thresholds for drift -positive and negative    | Adjustable in 5 mV steps from 0.2 V to 1.475 V and 20 mV steps from 0.8 V to 5.5 V |  |  |  |  |  |

| Voltage Monitoring scaling                     | 1 or 4                                                                             |  |  |  |  |  |

| Glitch (debounce) immunity for OV/UV-fast loop | 0.1 us to 102.4 us                                                                 |  |  |  |  |  |

| Enable sequence timeout                        | 1 ms to 4 s                                                                        |  |  |  |  |  |

| Sleep sequence timeout                         | 1 ms to 4 s                                                                        |  |  |  |  |  |

| SYNC pulse width                               | 50 us to 2600 us                                                                   |  |  |  |  |  |

| Expected ON/OFF Sequence on ACT                | Used for sequence logging                                                          |  |  |  |  |  |

| Expected ON/OFF Sequence on Sleep              | Used for sequence logging                                                          |  |  |  |  |  |

| Auto Mask OFF-ON-OFF via ACT                   | Selectable for each MON channel                                                    |  |  |  |  |  |

| Auto Mask OFF-ON-OFF via SLEEP                 | Selectable for each MON channel                                                    |  |  |  |  |  |

| Packet error checking for I <sup>2</sup> C     | Enabling or Disabling                                                              |  |  |  |  |  |

| Force NIRQ assertion                           | Controlled by I <sup>2</sup> C register                                            |  |  |  |  |  |

| Individual channel MON                         | Enable or Disable                                                                  |  |  |  |  |  |

| Interrupt disable functions                    | BIST, PEC, TSD, CRC                                                                |  |  |  |  |  |

## 8.3.2 Auto Mask (AMSK)

In the case of power up AMSK\_ON and AMSK\_EXS registers apply. It masks interrupts till the MON voltage crosses the UVLF threshold or sequence timeout expires whichever is sooner. In the case of power down AMSK\_OFF and AMSK\_ENS registers apply. It masks interrupts till the MON voltage is below the OFF threshold and then the OVLF interrupts are active.

Table 8-2 summarizes the auto-mask operation for the ACT and SLEEP transitions.

#### Copyright © 2023 Texas Instruments Incorporated

### Table 8-2. Transition Table

| TRANSITION                        | AUTO-MASK APPLIED | AUTO-MASK APPLIES<br>TO         | AUTO-MASK INACTIVE                                         | INTERRUPTS ACTIVE<br>FOR MON CHANNELS<br>NOT IN AUTO-MASK |  |  |  |

|-----------------------------------|-------------------|---------------------------------|------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| ACT (Low -> High)                 | AMSK_ON           | IEN_UVLF, IEN_UVHF,<br>IEN_OVHF | SEQ_TOUT expires or rail crosses UVLF                      | At ACT=High                                               |  |  |  |

| ACT (High -> Low)                 | AMSK_OFF          | IEN_UVLF, IEN_UVHF,<br>IEN_OVHF | Auto-mask active in<br>transition till SEQ_TOUT<br>expires | Until SEQ_TOUT expires                                    |  |  |  |

| SLEEP (Low -> High) ACT<br>= High | AMSK_EXS          | IEN_UVLF, IEN_UVHF,<br>IEN_OVHF | SEQ_TOUT expires or rail crosses UVLF                      | Always active                                             |  |  |  |

| SLEEP (High -> Low) ACT<br>= High | AMSK_ENS          | IEN_UVLF, IEN_UVHF,<br>IEN_OVHF | Auto-mask active                                           | Always active                                             |  |  |  |

## 8.3.3 PEC

TPS389006 supports Packet Error Checking (PEC). It uses a CRC-8 represented by the polynomial  $C(x)=x^8 + x^2 + x + 1$ , with CRC initial value set to 0x00. The PEC calculation includes all bytes in the transmission, including address, command and data. The PEC calculation does not include ACK or NACK bits or START,STOP or REPEATED START conditions. The device which acts as a peripheral and supports PEC must be prepared to perform the transfer with or without a PEC, verify the correctness of the PEC if present and only process the message if PEC is correct.

- If PEC is enabled by EN\_PEC, and the PEC byte is present in the write transaction, the device will NACK and assert NIRQ if PEC byte is incorrect.

- If PEC is enabled by EN\_PEC, and the PEC byte is not present in the write transaction

-If REQ\_PEC =0, missing PEC is treated as good PEC and register write succeeds. NIRQ is not asserted.

-If REQ\_PEC =1, missing PEC is treated as incorrect PEC and register write fails. NIRQ is asserted.

## 8.3.4 VDD

The TPS389006 is designed to operate from an input voltage supply range between 2.5 V to 5.5 V. An input supply capacitor is not required for this device; however, if the input supply is noisy good analog practice is to place a  $1-\mu$ F capacitor between the VDD pin and the GND pin.

$V_{DD}$  needs to be at or above  $V_{DD(MIN)}$  for at least the start-up delay ( $t_{SD}$ +  $t_D$ ) for the device to be fully functional.

#### 8.3.5 MON

The TPS389006 combines two comparators with a precision reference voltage and a trimmed resistor divider per monitor (MON) channel. This configuration optimizes device accuracy because all resistor tolerances are accounted for in the accuracy and performance specifications. Both comparators also include built-in hysteresis that provides noise immunity and ensures stable operation.

Although not required in most cases, for noisy applications good analog design practice is to place a 1-nF to 10-nF bypass capacitor at the MON input in order to reduce sensitivity to transient voltages on the monitored signal. Specific deglitch times can also be set independently for each MON via I<sup>2</sup>C registers

When monitoring VDD supply voltage, the MON pin can be connected directly to VDD. The output (NIRQ) is high impedance when voltage at the MON pin is between upper and lower boundary of threshold.

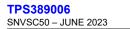

#### 8.3.6 NIRQ

In a typical TPS389006 application, the NIRQ output is connected to a reset or enable input of a processor [such as a digital signal processor (DSP), application-specific integrated circuit (ASIC), or other processor type] or the enable input of a voltage regulator such as a DC-DC converter or low-dropout regulator (LDO).

The TPS389006 has an open drain active low output that requires a pull-up resistor to hold these lines high to the required voltage logic. Connect the pull-up resistor to the proper voltage rail to enable the output to be connected to other devices at the correct interface voltage levels. The pull-up resistor value is determined by

$V_{OL}$ , output capacitive loading, and output leakage current. These values are specified in *Section 7*. The open drain output can be connected as a wired-OR logic with other open drain signals such as another TPS389006 NIRQ pin.

### 8.3.7 ADC

The ADC used in the TPS389006 runs on a 1Mhz clock with an effective sampling rate of 1/8 MHz (= 125 kHz). Initially, the ADC records with a resolution of 12 bits (1LSB = 0.41667mV) which is later round off to 8-bit data for I<sup>2</sup>C transaction. (1LSB = 5mV) The ADC uses ping-pong architecture in which it requires 2us for both sampling and conversion per channel with a total of 2 sampling channels. While CH0 performs coarse conversion, CH1 does fine conversion and vice versa.

Digitized 8-bit data is updated once the fine conversion is completed, which occurs once every 8  $\mu$ s. Each I<sup>2</sup>C transaction initiated for reading 8-bit MON\_LVL data (the ADC data of a particular channel), 8-bit data is paused from updating until the I<sup>2</sup>C transaction completes.

Voltage scaling is done using a resistor ladder, but for differential mode channels, a chopping circuit is used to get the average of both of the voltages (VMON + VMON\_RS)/2 since VMON\_RS can be negative and can't be converted into an ADC code. VMON – VMON\_RS is calculated digitally by subtracting ((VMON + VMON\_RS) /2) from VMON and then multiplying by 2.

The MONX channels can be configured in 1x (0.2V to 1.475V) or 4x mode (0.8V to 5.5V). For differential mode channels configured in 1x mode, (MON1 and MON2) the ADC range is limited up to 1.7V. To configure an ADC channel above 1.7 V, please use 4x mode.

Real time voltage measurements use Equation 1.

V<sub>IvI</sub> = ((ADC[7:0] \* 5mV) + 0.2) \* (VRANGE\_MULT)

(1)

- 1. ADC[7:0] is translated to a corresponding decimal value. The value of ADC[7:0] corresponding to MON1-MON6 can be read from registers 0x40-0x45 of Section 8.5.1.

- 2. VRANGE\_MULT corresponds to the selected monitor voltage multiplier set in register 0x1F of Section 8.5.2.

- 3. VRANGE\_MULT is set to a decimal 1 or 4 value depending on monitored value.

#### 8.3.8 Time Stamp

Time stamp measurement use Equation 2. The time stamps are used for sequence logging purposes to determine the order in which the rails are turned on or off.

$t_{stamp} = 50 \mu s^* CLOCK[15:0]$

(2)

1. CLOCK[15:0] translated to corresponding decimal value. The value of CLOCK[15:0] corresponding to MON1-MON6 can be read from registers 0x90-0x9B of BANK0.

## 8.4 Device Functional Modes

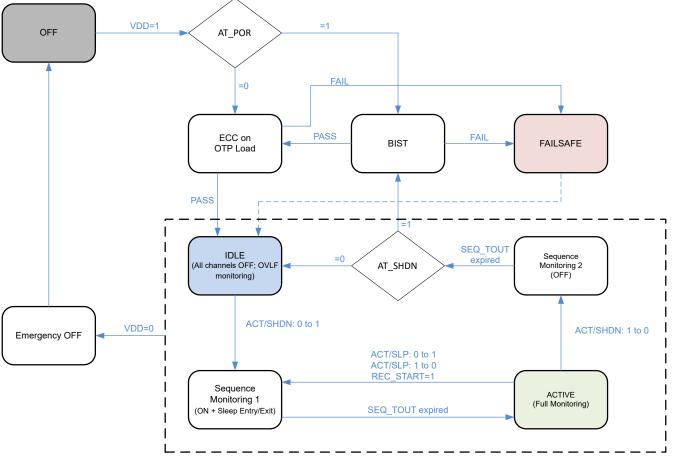

Figure 8-6. TPS389006 State Diagram

## 8.4.1 Built-In Self Test and Configuration Load

Built-In Self Test (BIST) is performed:

- 1. At Power On Reset (POR), if TEST\_CFG.AT\_POR=1

- 2. When exiting ACTIVE state due to ACT transitioning from  $1\rightarrow 0$ , if TEST\_CFG.AT\_SHDN=1

Configuration load from OTP is assisted by ECC (supporting SEC-DED). This is to protect against data integrity issues and to maximize system availability.

During BIST, NIRQ is de-asserted (asserted in case of failure), input pins are ignored, <u>SYNC</u> is tri-stated, and the I<sup>2</sup>C block is inactive with SDA and SCL de-asserted. The BIST includes device testing to meet the Functional Safety goals outlined in functional safety documentation. Once BIST is completed without failure, I<sup>2</sup>C is immediately active and the device enters the IDLE sate after loading the configuration data from OTP. If BIST fails and/or ECC reports Double-Error Detection (DED; meant for detecting multiple bit flips when loading data from memory), NIRQ is asserted, the device enters FAILSAFE state, and a best effort attempt is made to keep the I<sup>2</sup>C function active. TEST INFO register may provide additional information on the test results.

The detailed behavior upon success/failure of the BIST is controlled by INT\_TEST and IEN\_TEST registers. Reporting of the BIST results is carried out through:

- NIRQ pin: pulled low depending on the test result and BIST\_C and BIST bits in IEN\_TEST

- I\_BIST\_C and BIST bits in INT\_TEST register depending on IEN\_TEST settings

- VMON\_STAT.ST\_BIST\_C register bit

- TEST\_INFO[3:0] register bits

#### 8.4.1.1 Notes on BIST Execution

Upon Power-On-Reset, the TPS389006 needs to make a decision whether to run BIST or not, based on the value of the TEST\_CFG.AT\_POR register bit. Assuming that ECC on this register is performed after BIST has checked the ECC logic itself, it is not possible to guarantee its data integrity before running BIST.

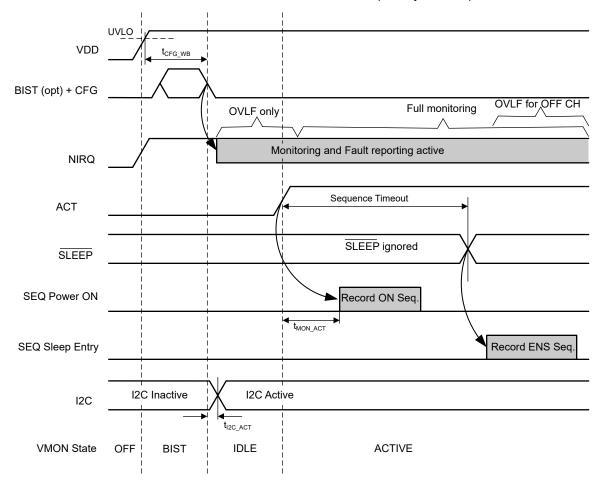

#### 8.4.2 TPS389006 Power ON

When the TPS389006 is powered ON, BIST is optionally executed (depending on TEST\_CFG.AT\_POR register bit); I<sup>2</sup>C and fault reporting (through NIRQ) become active as soon as BIST is completed and configuration is loaded from OTP (assisted by ECC, supporting SEC-DED).

The details of the configuration load ECC and BIST results are reported in TEST\_INFO register.

Upon detection of the ACT rising edge, the TPS389006 starts the sequence timeout timer and the monitoring of the power ON sequence. <u>SLEEP</u> is ignored until ACT is High and the sequence timeout has expired. The TPS389006 will then act on <u>SLEEP</u> transitions to monitor/record Sleep Entry/Exit sequences.

Figure 8-7. TPS389006 Power ON Signaling and Internal States

BIST completion can be detected through interrupt or register polling:

- Interrupt: INT\_TEST.I\_BIST\_C flag is set and NIRQ is asserted if IEN\_TEST.BIST\_C=1

- Polling: VMON\_STAT register can be polled to read the ST\_BIST\_C bit

## 8.4.3 General Monitoring

TPS389006 has multiple monitoring modes including IDLE, ACTIVE, SLEEP, and DEEP SLEEP. These modes refer to the monitoring states of the device shown in Table 8-3.

## 8.4.3.1 IDLE Monitoring

The TPS389006 is in IDLE state when ACT is Low and BIST is completed.

In this state, all monitored channels are expected to be in the OFF state (below the OFF threshold).

For the enabled channels in OFF state, only the Over-voltage Low Frequency (OVLF) thresholds are monitored to ensure the reliability limits are not violated.

### 8.4.3.2 ACTIVE Monitoring

The TPS389006 is in ACTIVE state when ACT is High.

VMON monitors high frequency channel levels (copmarator sense path) and low frequency channel levels (ADC sense path) against Under-Voltage High Frequency (UVHF), Over-Voltage High Frequency (OVHF), Under-Voltage Low Frequency (UVLF), and Over-Voltage Low Frequency (OVLF) thresholds.

Some channels can be connected to rails which are controlled by user software. Such channels can be in the OFF state (below the OFF threshold) when the TPS389006 is in an ACTIVE state, and have the UVLF/UVHF interrupts normally disabled. Once these rails are turned ON, the TPS389006 host enables the channels UVLF/UVHF interrupts to allow full monitoring. Similarly, before these rails are turned OFF, the TPS389006 host disables the channels UVLF/UVHF interrupts to avoid false UV violations during the ramp down. As these channels are not part of the sequencing initiated by ACT or SLEEP, their UVLF/UVHF/OVHF interrupts cannot be automatically enabled/disabled using the auto-mask registers. While in the OFF state, only the OVLF thresholds are monitored to ensure the reliability limits are not violated.

Other enabled channels can be in OFF state as a result of the SLEEP  $1 \rightarrow 0$  transition sequence. Those channels are identified by the AMSK\_ENS auto-mask register, used to avoid UVLF interrupts (as well as UVHF and OVHF interrupts) during the transition. For those channels in the OFF state and identified by the AMSK\_ENS register, only the OVLF thresholds are monitored to ensure the reliability limits are not violated.

| Table 0-0: modes of Operation Caninary |                                   |       |                                            |             |               |  |

|----------------------------------------|-----------------------------------|-------|--------------------------------------------|-------------|---------------|--|

| Mode                                   | Pin/Bit Condition                 | lq    | Monitored- Triggers NIRQ if CHx<br>enabled | Status only | ADC/Telemetry |  |

| ACTIVE                                 | ACT=High,<br>Sleep=High           | 1.5mA | OVLF, UVLF, OVHF, UVHF                     | OFF         | Enabled       |  |

| IDLE                                   | ACT=Low, Sleep=X                  | 230uA | OVLF                                       | OFF         | Disabled      |  |

| SLEEP                                  | CHx not assigned to<br>Sleep      |       | OVLF, UVLF, OVHF, UVHF                     | OFF         |               |  |

| ACT=High,<br>SLEEP=Low                 | CHx assigned to<br>Sleep (AMSK=1) | 1.5mA | OVLF                                       | OFF         | Enabled       |  |

| Sleep Power bit=1                      | CHx assigned to<br>Sleep (AMSK=0) |       | OVLF, UVLF, OVHF, UVHF                     | OFF         |               |  |

| DEEP SLEEP                             | CHx not assigned to<br>Sleep      |       | OVHF, UVHF                                 | -           |               |  |

| ACT=High,<br>SLEEP=Low                 | CHx assigned to<br>Sleep (AMSK=1) | 330uA | No monitoring                              | -           | Disabled      |  |

| Sleep Power bit=0                      | CHx assigned to<br>Sleep (AMSK=0) |       | OVHF, UVHF                                 | -           |               |  |

| Table 8-3. Mo | odes of Opera | tion Summary |

|---------------|---------------|--------------|

|---------------|---------------|--------------|

## 8.4.3.3 Sequence Monitoring 1

In addition to voltage monitoring, voltage rails sequences are also monitored on ACT and SLEEP changes, or on setting SEQ\_REC\_CTL.REC\_START=1.

Sequence Monitoring 1 is a transitional state entered when:

- 1. ACT transitions  $0 \rightarrow 1$

- 2. SLEEP transitions  $0 \rightarrow 1$ , if ACT=1

- 3. SLEEP transitions  $1 \rightarrow 0$ , if ACT=1

- 4. Host sets SEQ\_REC\_CTL.REC\_START=1

The first three transitions trigger the same set of actions, with the TPS389006 always ending in the ACTIVE state. However, the registers used to log and check the sequencing information are different.

The fourth method to start sequence monitoring (register bit set by the host) gives the flexibility to the host to decide when and where to track a sequence while the external signals are static. This is useful, for example, when software shutdown is initiated using FORCE\_SHUTDOWN[1:0].

The following sections describe the actions for the first three cases explicitly for clarity.

#### 8.4.3.3.1 ACT Transitions $0 \rightarrow 1$

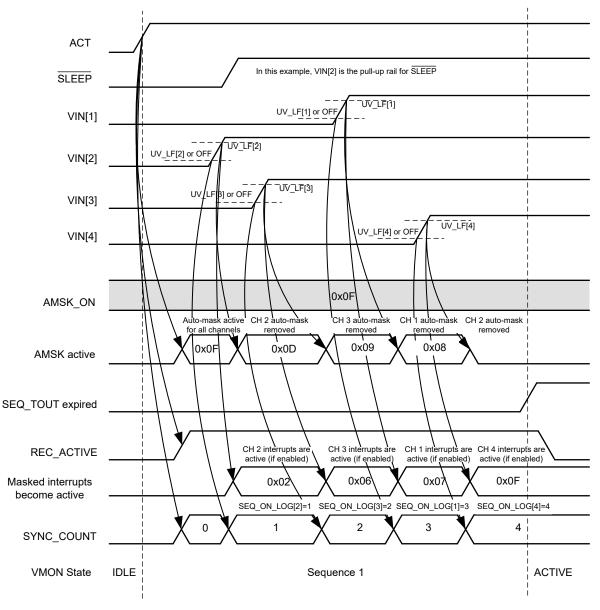

#### Figure 8-8. ACT 0→1 Transition

- 1. The TPS389006 takes several actions on the ACT  $0 \rightarrow 1$  transition:

- a. The synchronization counter is reset to 0.

- b. The REC\_ACTIVE bit is set, and SEQ[1:0] bits are updated to 00b.

- c. If the sequence overwrite bit is enabled (EN\_SEQ\_OW=1), the sequence logging registers (SEQ\_ON\_LOG[N]) are overwritten with new data. If there was data in the registers that was not read by the host (SEQ\_ON\_RDY still set), the sequence overwrite flag (SEQ\_ON\_OW) gets set.

- d. If the timestamps overwrite bit is enabled (EN\_TS\_OW=1), the timestamp logging registers (SEQ\_TIME\_xSB[N]) are overwritten with new data. If there was data in the registers that was not read by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set.

- e. If the sequence overwrite bit is disabled (EN\_SEQ\_OW=0) and there was data in the registers SEQ\_ON\_LOG[N] that was not read and acknowledged by the host (SEQ\_ON\_RDY still set), the sequence overwrite flag (SEQ\_ON\_OW) is set and does not overwrite the registers with new data.

- f. If the timestamp overwrite bit is disabled (EN\_TS\_OW=0) and there was data in the registers SEQ\_TIME\_xSB[N] that was not read and acknowledged by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set and does not overwrite the registers with new data.

- g. The internal sequence timer is (re)started.

- All TPS389006 inputs selected with auto-mask register AMSK\_ON start with masked (disabled) interrupts for Under-Voltage Low Frequency (UVLF), Under-Voltage High Frequency (UVHF), and Over-Voltage High Frequency (OVHF) conditions.

- As each rail passes the UVLF threshold (UV\_LF[N]), automatically (and expected to happen within about 5-10 µs) the relevant UV and OV interrupts are unmasked and enabled/disabled according to the IEN\_UVLF, IEN\_UVHF, and IEN\_OVHF registers.

- As each rail passes the UVLF or OFF threshold (depending on SEQ\_UP\_THLD.OFF\_UV[N] register setting), the rail is tagged with a counter corresponding to the order of rising edge transition. A timestamp is also logged.

- a. the tag value stored in the relevant status register SEQ\_ON\_LOG[N] if allowed as per overwrite settings and status. also, the timestamp of the event is stored in registers SEQ\_TIME\_MSB[N] and SEQ\_TIME\_LSB[N] as allowed by the overwrite settings and status.

- b. the SEQ\_ON\_LOG[N] register is compared to the expected sequence order value defined in register SEQ\_EXP[N], and an interrupt is generated if different and if the relevant interrupt enable bit is set (IEN\_SEQ\_ON). Note that if overwrite settings and recording status do not allow writing new data to the logging registers, then the comparison cannot be performed and no interrupt will be generated.

- 5. After a timeout, tagging stops.

- a. Clear the REC\_ACTIVE bit.

- b. If rails are up with the correct sequence, TPS389006 is in ACTIVE state and starts normal monitoring.

- c. If any rail has a tag not matching the configured value in SEQ\_ON\_EXP[N] register, NIRQ is asserted. The TPS389006 continues normal monitoring.

- d. If SLEEP is low, the TPS389006 will not start recording the Sleep Entry sequence, as sequence recording is started on ACT and SLEEP transitions, or when initiated through I<sup>2</sup>C command.

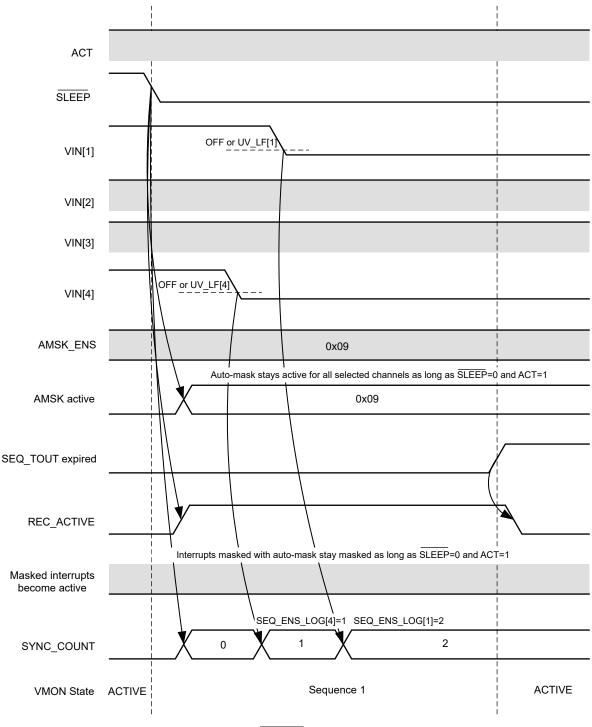

## 8.4.3.3.2 SLEEP Transition 1→0

## Figure 8-9. SLEEP $1 \rightarrow 0$ Transition

- 1. The TPS389006 takes several actions on the  $\overline{\text{SLEEP}}$  1 $\rightarrow$ 0 transition:

- a. The synchronization counter is reset to 0.

- b. The REC\_ACTIVE bit is set, and SEQ[1:0] bits are updated to 11b.

- c. If the sequence overwrite bit is enabled (EN\_SEQ\_OW=1), the sequence logging registers (SEQ\_ENS\_LOG[N]) are overwritten with new data. If there was data in the registers that was not read by the host (SEQ\_ENS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set.

- d. If the timestamp overwrite bit is enabled (EN\_TS\_OW=1), the timestamp logging registers (SEQ\_TIME\_xSB[N]) are overwritten with new data. If there was data in the registers that was not read by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set.

- e. If the sequence overwrite bit is disabled (EN\_SEQ\_OW=0) and there was data in the registers SEQ\_ENS\_LOG[N] that was not read and acknowledged by the host (SEQ\_ENS\_RDY still set), the sequence overwrite flag (SEQ\_ENS\_OW) is set, and the registers are not overwritten with new data.

- f. If the timestamp overwrite bit is disabled (EN\_TS\_OW=0) and there was data in the registers SEQ\_TIME\_xSB[N] that was not read and ackowledged by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set, and the registers are not overwritten with new data.

- g. The internal sequence timer is (re)started.

- Relevant TPS389006 inputs selected with auto-mask register AMSK\_ENS are set with masked interrupts for UVLF, UVHF and OVHF conditions.

- 3. As each rail passes the OFF or UVLF threshold (depending on SEQ\_DN\_THLD.OFF\_UV[N] register setting), the rail is tagged with a counter corresponding to the order of falling edge transition. A timestamp is also logged.

- a. The tag value is stored in the relevant status register SEQ\_ENS\_LOG[N] if allowed as per overwrite settings and status. Also, the timestamp of the event is stored in registers SEQ\_TIME\_MSB[N] and SEQ\_TIME\_LSB[N] as allowed by the overwrite settings and status.

- b. The SEQ\_ENS\_LOG[N] register is compared to the expected sequence order value defined in register SEQ\_ENS\_EXP[N], and an interrupt is generated if different and if the relevant interrupt enable bit is set (IEN\_SEQ\_ENS). Note that if overwrite settings and recording status do not allow writing new data to the logging registers, then the comparison cannot be performed and no interrupt will be generated.

- 4. After timeout, tagging stops.

- a. The REC\_ACTIVE bit is cleared.

- b. If rails are down with the correct sequence, TPS389006 is in ACTIVE state and continues normal monitoring (only OVLF thresholds are monitored for enabled channels in OFF state).

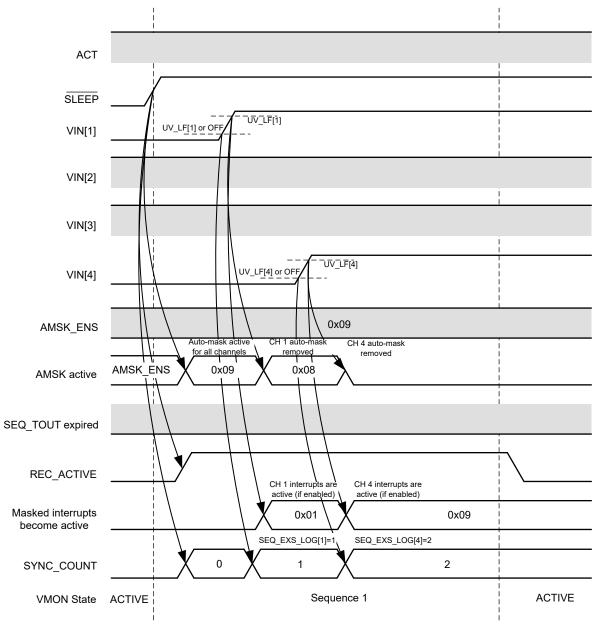

## 8.4.3.3.3 $\overline{\text{SLEEP}}$ Transition 0 ${\rightarrow}1$

Figure 8-10. SLEEP  $0 \rightarrow 1$  Transition

- 1. The TPS389006 takes several actions on the  $\overline{\text{SLEEP}} 0 \rightarrow 1$  transition:

- a. The synchronization counter is reset to 0.

- b. The REC\_ACTIVE bit is set, and SEQ[1:0] bits are updated to 10b.

- c. If the sequence overwrite bit is enabled (EN\_SEQ\_OW=1), the sequence logging registers (SEQ\_EXS\_LOG[N]) are overwritten with new data. If there was data in the registers that was not read by the host (SEQ\_EXS\_RDY still set), the sequence overwrite flag (SEQ\_EXS\_OW) is set.

- d. If the timestamp overwrite bit is enabled (EN\_TS\_OW=1), the timestamp logging registers (SEQ\_TIME\_xSB[N]) are overwritten with new data. If there was data in the registers that was not read by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set.

- e. If the sequence overwrite bit is disabled (EN\_SEQ\_OW=0) and there was data in the registers SEQ\_EXS\_LOG[N] that was not read and acknowledged by the host (SEQ\_EXS\_RDY still set), the sequence overwrite flag (SEQ\_EXS\_OW) is set, and the registers are not overwritten with new data.

**TPS389006** SNVSC50 – JUNE 2023

- f. If the timestamp overwrite bit is disabled (EN\_TS\_OW=0) and there was data in the registers SEQ\_TIME\_xSB[N] that was not read and acknowledged by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set, and the registers are not overwritten with new data.

a. The internal sequence timer is (re)started.

- 2. Relevant TPS389006 inputs selected with auto-mask register AMSK\_EXS are set with masked (disabled) interrupts for UVLF, UVHF, and OVHF conditions.

- As each rail passes the UVLF threshold (UV\_LF[N]), automatically (and expected to happen within about 5-10 µs) the relevant UV and OV interrupts are unmasked and enabled/disabled according to the IEN\_UVLF, IEN\_UVHF, and IEN\_OVHF registers.

- 4. As each rail passes the UVLF or OFF threshold (depending on SEQ\_UP\_THLD.OFF\_UV[N] register setting), the rail is tagged with a counter corresponding to the order of rising edge transition. A timestamp is also logged.

- a. The tag value is stored in the relevant status register SEQ\_EXS\_LOG[N] if allowed as per overwrite settings and status. Also, the timestamp of the event is stored in registers SEQ\_TIME\_MSB[N] and SEQ\_TIME\_LSB[N] as allowed by the overwrite settings and status.

- b. The SEQ\_EXS\_LOG[N] register is compared to the expected sequence order value defined in register SEQ\_EXS\_EXP[N], and an interrupt is generated if different and if relevant interrupt enable bit is set (IEN\_SEQ\_EXS). Note that if overwrite settings and recording status do not allow writing new data to the logging registers, then the comparison cannot be performed and no interrupt will be generated.

- 5. After a timeout, tagging stops.

- a. The REC\_ACTIVE bit is cleared.

- b. If rails are up with the correct sequence, TPS389006 is in ACTIVE state and starts normal monitoring.

- c. If any rail has a tag not matching the configured value in SEQ\_EXS\_EXP[N] register, NIRQ is asserted. TPS389006 continues normal monitoring.

## 8.4.3.4 Sequence Monitoring 2

Sequence Monitoring 2 is very similar to Sequence Monitoring 1, however, an extra step is taken when exiting this transitioning state depending on the TEST\_CFG.AT\_SHDN register bit.

Sequence Monitoring 2 is entered when ACT transitions  $1\rightarrow 0$ . The actions taken are described in Section 8.4.3.4.1.

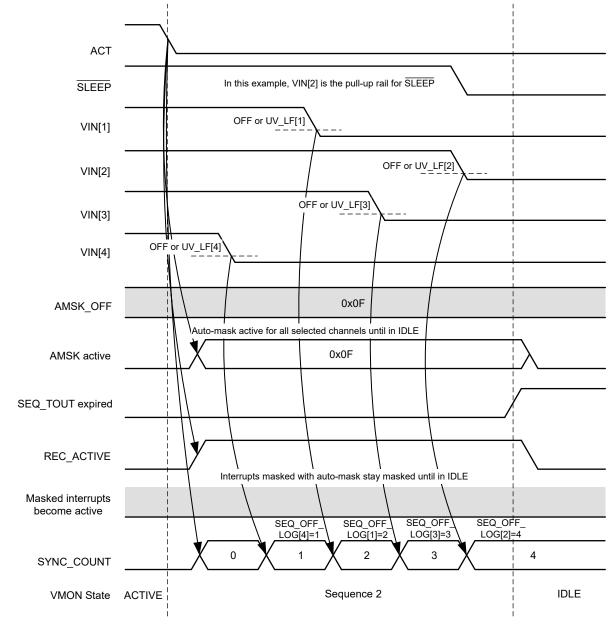

#### 8.4.3.4.1 ACT Transition $1 \rightarrow 0$

Figure 8-11. ACT  $1 \rightarrow 0$  Transition

- 1. The TPS389006 takes several actions on the ACT  $1\rightarrow 0$  transition:

- a. The synchronization counter is reset to 0.

- b. The REC\_ACTIVE bit is set, and SEQ[1:0] bits are updated to 01b.

- c. If the sequence overwrite bit is enabled (EN\_SEQ\_OW=1), the sequence logging registers (SEQ\_OFF\_LOG[N]) are overwritten with new data. If there was data in the registers that was not read by the host (SEQ\_OFF\_RDY still set), the sequence overwrite flag (SEQ\_OFF\_OW) is set.

- d. If the timestamp overwrite bit is enabled (EN\_TS\_OW=1), the timestamp logging registers (SEQ\_TIME\_xSB[N]) are overwritten with new data. If there was data in the registers that was not read by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set.

- e. If the sequence overwrite bit is disabled (EN\_SEQ\_OW=0) and there was data in the registers SEQ\_OFF\_LOG[N] that was not read and acknowledged by the host (SEQ\_OFF\_RDY still set), the sequence overwrite flag (SEQ\_OFF\_OW) is set, and the registers are not overwritten with new data.

- f. If the timestamp overwrite bit is disabled (EN\_TS\_OW=0) and there was data in the registers SEQ\_TIME\_xSB[N] that was not read and acknowledged by the host (TS\_RDY still set), the timestamp overwrite flag (TS\_OW) is set, and the registers are not overwritten with new data.

g. The internal sequence timer is (re)started

- g. The internal sequence timer is (re)started.

- All TPS389006 inputs selected with auto-mask register AMSK\_OFF are set with masked (disabled) interrupts for UVLF, UVHF, and OVHF conditions.

- As each rail passes the OFF or UVLF threshold (depending on SEQ\_DN\_THLD.OFF\_UV[N] register setting), the rail is tagged with a counter corresponding to the order of falling edge transition. A timestamp is also logged.

- a. The tag value is stored in the relevant status register SEQ\_OFF\_LOG[N] if allowed as per overwrite settings and status. Also, the timestamp of the event is stored in registers SEQ\_TIME\_MSB[N] and SEQ\_TIME\_LSB[N] as allowed by the overwrite settings and status.

- b. The SEQ\_OFF\_LOG[N] register is compared to the expected sequence order value defined in register SEQ\_OFF\_EXP[N], and an interrupt is generated if different and if relevant interrupt enable bit is set (IEN\_SEQ\_OFF). Note that if overwrite settings and recording status do not allow writing new data to the logging registers, then the comparison cannot be performed and no interrupt will be generated.

- 4. After timeout, tagging stops.

- a. The REC\_ACTIVE bit is cleared.

- b. If rails are down with the correct sequence, proceed to check TEST\_CFG.AT\_SHDN register bit.

- c. If any rail has a tag not matching the configured value in SEQ\_OFF\_EXP[N] register, NIRQ is asserted. TPS389006 proceeds to check TEST\_CFG.AT\_SHDN register bit.

- 5. If TEST\_CFG.AT\_SHDN register bit is set, BIST is executed (next state depends on BIST results).

- 6. If TEST\_CFG.AT\_SHDN register bit is no set, the TPS389006 enters IDLE state.

## 8.5 Register Maps

The register map is designed to support up to 16 channels through register banks, with the following organization:

- Bank 0 Status Register Set Summary:

- Vendor info and usage registers (bank independent)

- Interrupt registers

- Status registers

- Bank selection register (bank independent)

- Protection registers (bank independent)

- Device configuration registers (bank independent)

- Bank 1 Channel 1-8 Configuration Register Set Summary:

- Vendor info and usage registers (bank independent)

- Control registers (device global registers)

- Monitor configuration registers (channel specific registers)

- Sequence configuration registers (both device global and channel specific registers)

- Bank selection register (bank independent)

- Protection registers (bank independent)

- Device configuration registers (bank independent)

Bank independent registers are accessible at the same address irrespective of the current bank selection. Access to other registers requires the proper bank being selected.

All registers are 8-bit wide, and are loaded at boot with the default value described here or with the OTP value programmed at the factory.

Unused registers addresses are reserved for future use and support up to 16 channels.

Write accesses to protected registers (see PROT1/2 details), invalid registers, or valid registers with invalid data, should be NACK'd.

### 8.5.1 BANK0 Registers

Table 8-4 lists the memory-mapped registers for the BANK0 registers. All register offset addresses not listed in

Table 8-4 should be considered as reserved locations and the register contents should not be modified.

|         |                | Table          | 9 8-4. BA     | NK0 Reg     | isters      | r              |                 |                 |                 |

|---------|----------------|----------------|---------------|-------------|-------------|----------------|-----------------|-----------------|-----------------|

| Address | Acronym        | Bit 7          | Bit 6         | Bit 5       | Bit 4       | Bit 3          | Bit 2           | Bit 1           | Bit 0           |

| 0x10    | INT_SRC        | F_OTHE<br>R    |               | RS          | SVD         |                | TEST            | CONTRO<br>L     | MONITO<br>R     |

| 0x11    | INT_MONITOR    | SEQ_ON         | SEQ_OF<br>F   | SEQ_EX<br>S | SEQ_EN<br>S | OV_LF          | OV_HF           | UV_LF           | UV_HF           |

| 0x12    | INT_UVHF       | RS             | VD            |             |             | UVH            | IF[N]           |                 |                 |

| 0x14    | INT_UVLF       | RS             | SVD           |             |             | UVL            | .F[N]           |                 |                 |

| 0x16    | INT_OVHF       | RS             | SVD           |             |             | OVH            | IF[N]           |                 |                 |