# TPS25772-Q1 Automotive Dual USB Type-C<sup>®</sup> Power Delivery Controller with Buck-Boost Regulator

# 1 Features

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: -40°C to +125°C ambient operating temperature range

- Device HBM ESD classification level 2

- Device CDM ESD classification level C2b

- Enhanced connector pin ESD protection

- USB power delivery (PD) controller with programmable power supply (PPS) support

- Wide V\_{IN}: 5.5V to 18V (40V maximum)

- Integrated buck-boost with 4 power switches supporting up to 65W USB PD output power

- V<sub>BUS</sub> output: 3.3–21V with ±20mV step size

- I<sub>BUS</sub> output: 0–3A with ±50mA current limit step size

- V<sub>BUS</sub> short circuit to V<sub>BAT</sub> and GND protection

- V<sub>BUS</sub> cable droop compensation

- MFi overcurrent protection

- Switching frequency: 300, 400, 450kHz

- DC/DC sync in/out with dithering

- USB port configuration options

- 1 USB-PD port (TPS25762-Q1)

- 1 USB-PD port with DisplayPort<sup>™</sup> over USB-C<sup>™</sup> (DP alternate mode) (TPS25763-Q1)

2 USB PD ports (TDS25772, Q4)

- 2 USB-PD ports (TPS25772-Q1)

- Compliant to USB

- USB Type-C<sup>®</sup> power delivery Rev 3.1

- TPS25762-Q1: USB–IF certification with PPS, TID: 9509

- TPS25772-Q1: USB–IF certification with PPS, TID: 9161

- CC logic, V<sub>CONN</sub> source and discharge

USB cable polarity detection

- Battery charging specification v1.2 (BC1.2)

- DCP: dedicated charging port

- Legacy fast charging

- 2.7V divider-3 mode

- 1.2V divider mode

- high voltage DCP Protocol

- Microcontroller core allows

- Firmware updates

- Intelligent power sharing across charging ports

- Supply voltage and temperature-dependent

- power management

- Short to V<sub>BUS</sub> and V<sub>BAT</sub> protection

- V<sub>BUS</sub>

- Px\_DP and Px\_DM

- Px\_CC1 and Px\_CC2

- HotRod<sup>™</sup> QFN package with wettable flank

# 2 Applications

- Automotive USB Charge

- Automotive Media Hub

- Automotive Head Unit

- Automotive Rear Seat Entertainment

# **3 Description**

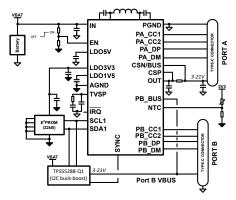

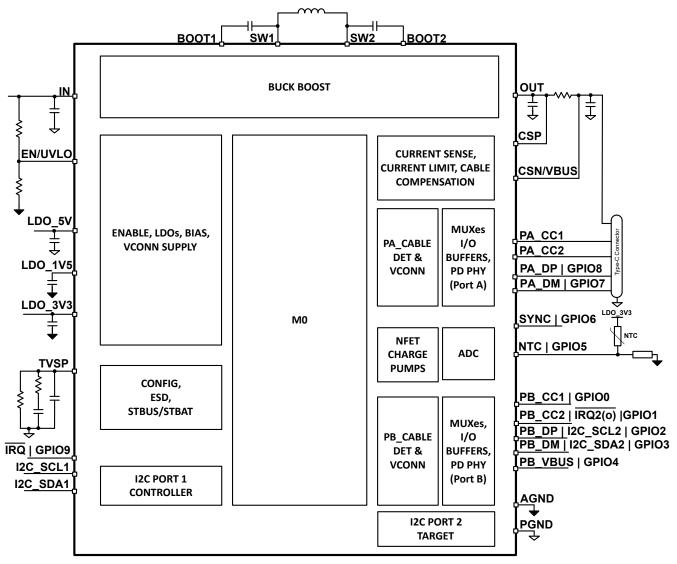

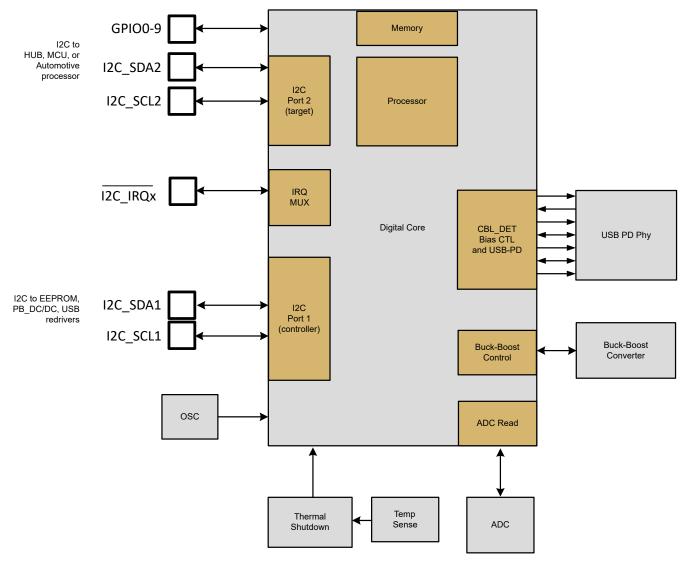

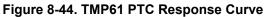

The TPS25772-Q1 is a fully integrated dual-port USB Type-C® Power Delivery (PD) solution with integrated buck-boost converter for automotive dual USB port applications. Functionality includes: integrated Buck-Boost converter with 4 power switches; an ARM® Cortex®-M0; USB port controller with Type-C cable plug and orientation detection; USB Battery Charging Specification Version 1.2 (BC1.2) detection; USB Endpoint PHY; device power management and supervisory circuitry; and connector pin over-voltage and short-circuit protection;

An intelligent System Power Management (SPM) Engine maximizes delivered USB power while protecting the system from automotive battery transient and over-temperature conditions.

Device configuration settings are selected through an intuitive graphical user interface (GUI).

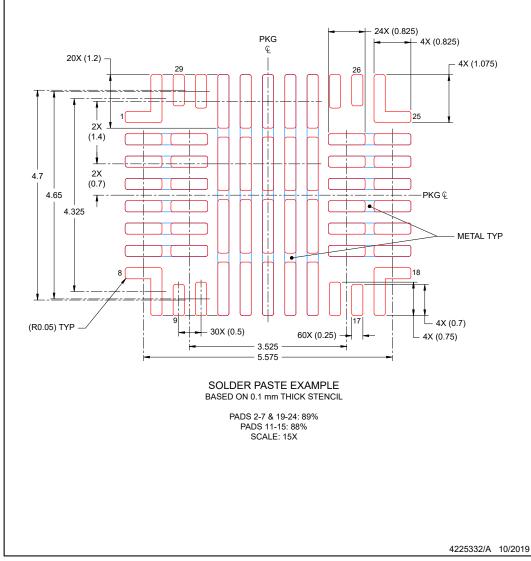

#### Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TPS25772-Q1 | RQL (QFN-29)           | 6.00mm x 5.00mm             |

- (1) For more information, see Mechanical, Packaging, and Orderable Information

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

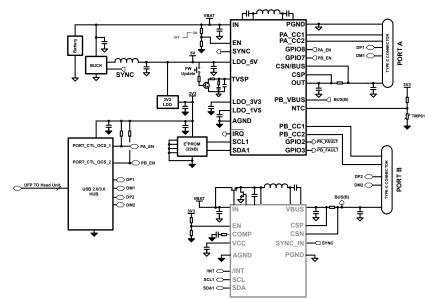

**TPS25772-Q1 Simplified Schematic**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features                                |                |

|-------------------------------------------|----------------|

| 2 Applications                            | 1              |

| 3 Description                             |                |

| 4 Device Comparison Table                 | 3              |

| 5 Pin Configuration and Functions         | 4              |

| 6 Specifications                          | 6              |

| 6.1 Absolute Maximum Ratings              | 6              |

| 6.2 ESD Ratings                           |                |

| 6.3 Recommended Operating Conditions      | <mark>8</mark> |

| 6.4 Recommended Components                |                |

| 6.5 Thermal Information                   |                |

| 6.6 Buck-Boost Regulator                  | 9              |

| 6.7 CC Cable Detection Parameters         | 13             |

| 6.8 CC VCONN Parameters                   |                |

| 6.9 CC PHY Parameters                     |                |

| 6.10 Thermal Shutdown Characteristics     | 15             |

| 6.11 Oscillator Characteristics           |                |

| 6.12 ADC Characteristics                  | 16             |

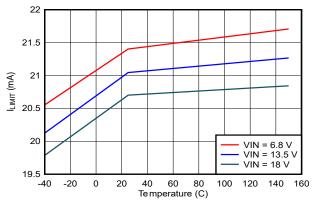

| 6.13 TVSP Parameters                      | 16             |

| 6.14 Input/Output (I/O) Characteristics   |                |

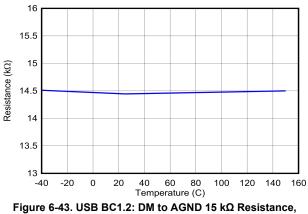

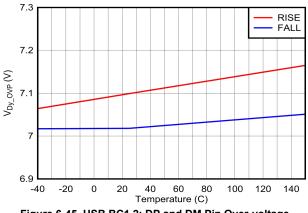

| 6.15 BC1.2 Characteristics                |                |

| 6.16 I2C Requirements and Characteristics | 18             |

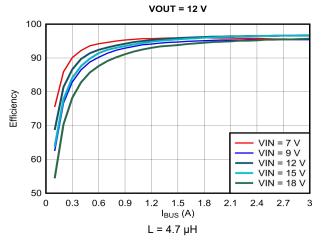

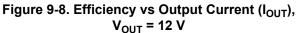

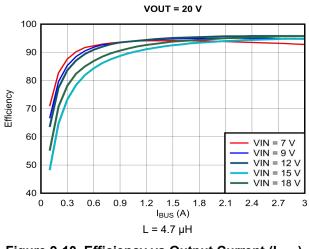

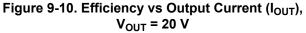

| 6.17 Typical Characteristics                         | 21 |

|------------------------------------------------------|----|

| 7 Parameter Measurement Information                  | 29 |

| 8 Detailed Description                               |    |

| 8.1 Overview                                         |    |

| 8.2 Functional Block Diagram                         |    |

| 8.3 Feature Description                              |    |

| 8.4 Device Functional Modes                          |    |

| 9 Application and Implementation                     |    |

| 9.1 Application Information                          |    |

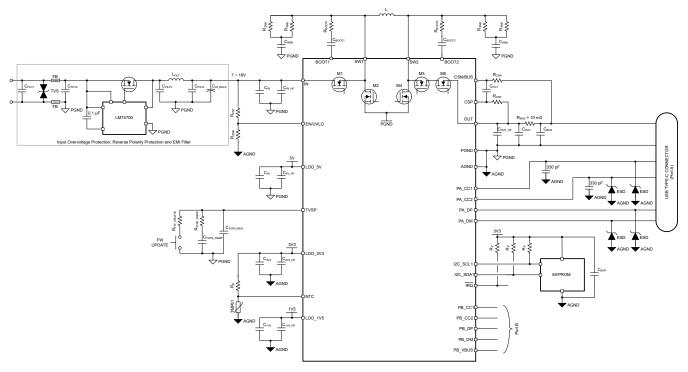

| 9.2 Typical Application                              |    |

| 9.3 Power Supply Recommendations                     |    |

| 9.4 Layout                                           |    |

| 10 Device and Documentation Support                  |    |

| 10.1 Documentation Support                           |    |

| 10.2 Receiving Notification of Documentation Updates |    |

| 10.3 Support Resources                               |    |

| ••                                                   |    |

| 10.4 Trademarks                                      |    |

| 10.5 Electrostatic Discharge Caution                 |    |

| 10.6 Glossary                                        |    |

| 11 Revision History                                  | 84 |

| 12 Mechanical, Packaging, and Orderable              |    |

| Information                                          | 86 |

# 4 Device Comparison Table

| PART NUMBER | Orderable Device      | Port A           |            | Port A<br>Output<br>Power | Port B<br>Output<br>Power | DP Alternate<br>Mode | Astable VIN<br>Boot<br>Support   | Configurable<br>Boot Mode <sup>(2)</sup> |  |                                  |     |

|-------------|-----------------------|------------------|------------|---------------------------|---------------------------|----------------------|----------------------------------|------------------------------------------|--|----------------------------------|-----|

| TPS25762-Q1 | TPS25762CQRQLRQ1      |                  |            |                           |                           |                      | VIN-<br>dependent <sup>(1)</sup> | Yes                                      |  |                                  |     |

|             | TPS25762CAQRQLR<br>Q1 |                  | n/a n/a No |                           | n/a                       | No                   | Yes                              | No                                       |  |                                  |     |

|             | TPS25762DQRQLRQ1      | 1                |            |                           | Yes                       | Yes                  |                                  |                                          |  |                                  |     |

| TPS25772-Q1 | TPS25772CQRQLRQ1      | USB-PD<br>USB-PD | USB-PD     | USB-PD                    | 65 W                      |                      |                                  | 65 W                                     |  | VIN-<br>dependent <sup>(1)</sup> | Yes |

|             | TPS25772CAQRQLR<br>Q1 |                  | USB-PD     | 65 W                      |                           | No                   | Yes                              | No                                       |  |                                  |     |

|             | TPS25772DQRQLRQ1      | 1                |            |                           |                           |                      | Yes                              | Yes                                      |  |                                  |     |

| TPS25763-Q1 | TPS25763DQRQLRQ1      | 1                | n/a        |                           | n/a                       | Yes                  | Yes                              | Yes                                      |  |                                  |     |

Assured device boot up during a stable VIN (for example, cold crank) conditions when VIN oscillation minimum voltage is ≧7.6V until boot is completed. Refer to application brief TPS257x2-Q1 Startup with an Astable Supply Voltage.

2. Refer to Section 8.3.2.

# **5** Pin Configuration and Functions

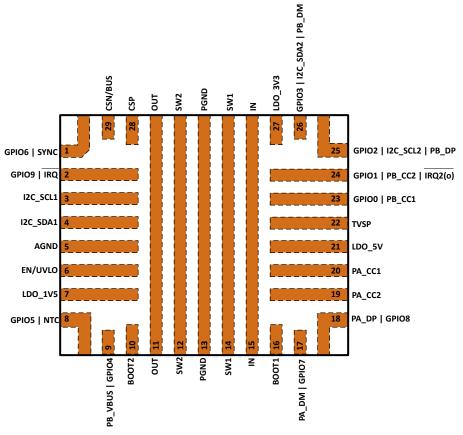

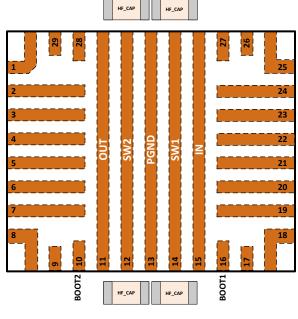

Figure 5-1. RQL Package 29-Pin (VQFN) Top View

### Table 5-1. Pin Descriptions

| PIN                            |     | DESCRIPTION                                                                                                                                                                                                               |  |  |  |

|--------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                           | NO. | DESCRIPTION                                                                                                                                                                                                               |  |  |  |

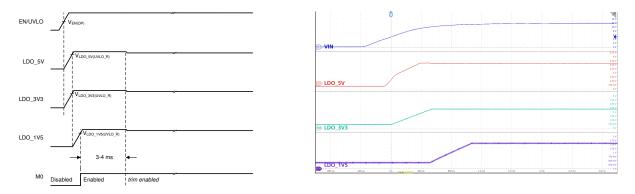

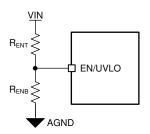

| EN/UVLO                        | 6   | Enable pin. For EN/UVLO < 0.3 V, the TPS25772-Q1 is in a low current shutdown mode. For EN/UVLO > 1.3 V, the full functionality is enabled, provided LDO_5V exceeds the LDO_5V UVLO threshold.                            |  |  |  |

| IN                             | 15  | The input supply pin to the IC. Connect $V_{IN}$ to a supply voltage between 5.5 V and 18 V (40-V ABS MAX transient).                                                                                                     |  |  |  |

| PGND                           | 13  | Power ground of the IC. The high current ground connection to the low-side gate drivers.                                                                                                                                  |  |  |  |

| SW1                            | 14  | The buck side switching node.                                                                                                                                                                                             |  |  |  |

| SW2                            | 12  | The boost side switching node.                                                                                                                                                                                            |  |  |  |

| BOOT1                          | 16  | An external capacitor is required between the BOOT1 and the SW1 pins to provide bias to the high-side MOSFET gate drivers.                                                                                                |  |  |  |

| BOOT2                          | 10  | An external capacitor is required between the BOOT2 and the SW2 pins to provide bias to the high-side MOSFET gate drivers.                                                                                                |  |  |  |

| AGND                           | 5   | Analog ground of the IC.                                                                                                                                                                                                  |  |  |  |

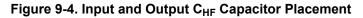

| OUT                            | 11  | Output of the buck-boost regulator. Connect to bulk capacitance.                                                                                                                                                          |  |  |  |

| CSP                            | 28  | Positive input of the current sense amplifier.                                                                                                                                                                            |  |  |  |

| CSN/BUS                        | 29  | Negative input of the current sense amplifier. This is the PA_VBUS supply.                                                                                                                                                |  |  |  |

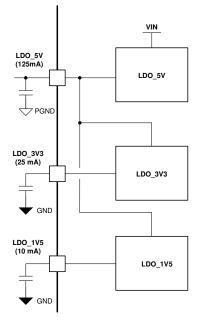

| LDO_5V                         | 21  | Output of internal 5 V LDO for buck-boost low-side FET drivers, and Px_VCONN supply. Connect bypass capacitor to PGND. May be overdriven from external 5-V supply.                                                        |  |  |  |

| LDO_3V3                        | 27  | Output of internal 3.3-V LDO for analog circuitry and GPIO drivers. Connect bypass capacitor to AGND.                                                                                                                     |  |  |  |

| LDO_1V5                        | 7   | Output of internal 1.5-V LDO for digital circuitry. Connect bypass capacitor to AGND.                                                                                                                                     |  |  |  |

| I2C_SCL1                       | 3   | Controller I2C Clock Input/Output.                                                                                                                                                                                        |  |  |  |

| I2C_SDA1                       | 4   | Controller I2C Data Input/Output.                                                                                                                                                                                         |  |  |  |

| GPIO2 (I2C_SCL2 or PB_DP)      | 25  | Multifunction pin. GPIO; target I2C Clock Input; or Port B USB data line DP input depending upon firmware configuration.                                                                                                  |  |  |  |

| GPIO3 (I2C_SDA2<br>or PB_DM)   | 26  | Multifunction pin. GPIO; target I2C Data Input; or Port B USB data line DM input depending upon firmware configuration.                                                                                                   |  |  |  |

| IRQ (GPIO9)                    | 2   | Multifunction pin. Interrupt I/O and fault flag for I2C1 or I2C2; or GPIO depending upon firmware configuration. Reports fault conditions set by application configuration firmware.                                      |  |  |  |

| PA_CC1                         | 20  | Analog input/output. Port A Type-C current advertisement, VCONN, and USB PD modem. Connect to Port A Type-C connector CC1 pin.                                                                                            |  |  |  |

| PA_CC2                         | 19  | Analog input/output. Port A Type-C current advertisement, VCONN, and USB PD modem. Connect to Port A Type-C connector CC2 pin.                                                                                            |  |  |  |

| PA_DP (GPIO8)                  | 18  | Multifunction pin. BC1.2 USB 2.0 D+ data line input/output. Connect to Port A Type-C USB data line DP connector pins. May also be used as GPIO depending upon firmware configuration.                                     |  |  |  |

| PA_DM (GPIO7)                  | 17  | Multifunction pin. BC1.2 USB 2.0 D- data line input/output. Connect to Port A Type-C USB data line DM connector pins. May also be used as GPIO depending upon firmware configuration.                                     |  |  |  |

| PB_CC1 ( GPIO0 )               | 23  | Multifunction pin. Port B Type-C current advertisement, VCONN, and USB PD modem. Connect to Port B Type-C connector CC1 pin; May also be used as GPIO when port B is disabled in firmware configuration.                  |  |  |  |

| PB_CC2 ( GPIO1 or<br>IRQ2(0) ) | 24  | Multifunction pin. Port B Type-C current advertisement, VCONN, and USB PD modem. Connect to Port B Type-C connector CC2 pin; May also be used as GPIO or Interrupt I/O when port B is disabled in firmware configuration. |  |  |  |

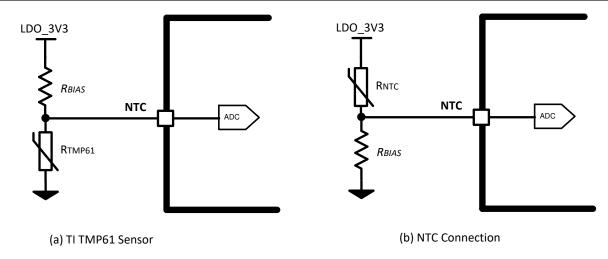

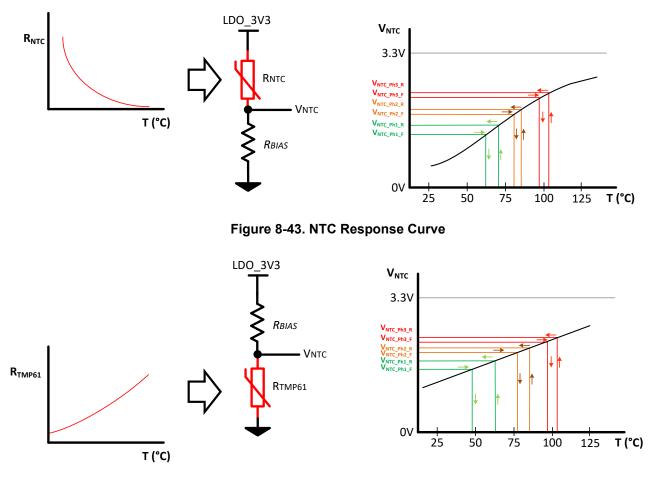

| GPIO5 (NTC)                    | 8   | Multifunction pin. GPIO; thermistor input (can use either negative temperature coefficient resistor or positive temperature coefficient resistor).                                                                        |  |  |  |

| GPIO6 (SYNC)                   | 1   | Multifunction pin. GPIO; SYNC(o) - clock out to synchronize external DC/DC regulators to internal DC/DC switching frequency; SYNC(i) - clock input to synchronize internal DC/DC to an external clock.                    |  |  |  |

| PB_VBUS (GPIO4)                | 9   | Multifunction pin. PB_VBUS voltage monitor; or GPIO when port B is disabled in firmware configuration                                                                                                                     |  |  |  |

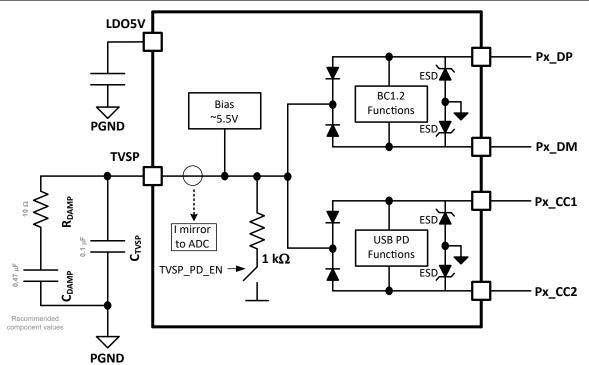

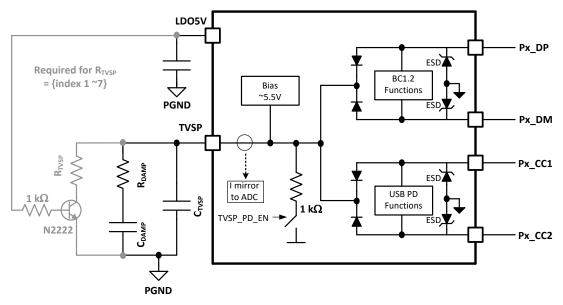

| TVSP                           | 22  | Transient voltage protection and firmware setting pin. See TVSP Device Configuration and ESD Protection for boot configuration and R-C network component values.                                                          |  |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range of -40°C to  $150^{\circ}$ C and AGND = PGND (unless otherwise noted)<sup>(1)</sup> (2)

|                      |                                          | MIN  | MAX                | UNIT |

|----------------------|------------------------------------------|------|--------------------|------|

| Input voltage range  | IN <sup>(3) (4)</sup> to PGND            | -0.3 | 40                 | V    |

| Input voltage range  | IN with respect to SW1                   | -0.3 | 25                 | V    |

| Input voltage range  | EN/UVLO <sup>(5)</sup> to AGND           | -0.3 | internally limited | V    |

| Input voltage range  | BOOT1 with respect to SW1                | -0.3 | 6                  | V    |

| Input voltage range  | BOOT2 with respect to SW2 <sup>(6)</sup> | -0.3 | 6                  | V    |

| Input voltage range  | SW1 <sup>(7)</sup> to PGND               | -0.3 | 24                 | V    |

| Input voltage range  | SW2 <sup>(8)</sup> to PGND               | -0.3 | 24                 | V    |

| Input voltage range  | SW2 to OUT                               |      | 17.5               | V    |

| Input voltage range  | CSP to PGND                              | -0.3 | 24                 | V    |

| Input voltage range  | CSN/BUS to PGND                          | -0.3 | 24                 | V    |

| Input voltage range  | CSP to CSN                               | -0.3 | 0.3                | V    |

| Input voltage range  | AGND to PGND                             | -0.3 | 0.3                | V    |

| Output voltage range | OUT to PGND                              | -0.3 | 24                 | V    |

| Output voltage range | LDO_5V to PGND                           | -0.3 | 6                  | V    |

| Output voltage range | LDO_3V3 to AGND                          | -0.3 | 6                  | V    |

| Output voltage range | LDO_1V5 to AGND                          | -0.3 | 2                  | V    |

| I/O voltage range    | TVSP to PGND                             | -0.3 | 30                 | V    |

| I/O voltage range    | I2C_SCL1 to AGND                         | -0.3 | 6                  | V    |

| I/O voltage range    | I2C_SDA1 to AGND                         | -0.3 | 6                  | V    |

| I/O voltage range    | GPIO9, IRQ1 to AGND                      | -0.3 | 6                  | V    |

| I/O voltage range    | PA_CC1 to AGND                           | -0.3 | 30                 | V    |

| I/O voltage range    | PA_CC2 to AGND                           | -0.3 | 30                 | V    |

| I/O voltage range    | PA_DM to AGND                            | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO7 to AGND                            | -0.3 | 6                  | V    |

| I/O voltage range    | PA_DP to AGND                            | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO8 to AGND                            | -0.3 | 6                  | V    |

| I/O voltage range    | PB_CC1 to AGND                           | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO0 to AGND                            | -0.3 | 6                  | V    |

| I/O voltage range    | PB_CC2 to AGND                           | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO1, IRQ2 to AGND                      | -0.3 | 6                  | V    |

| I/O voltage range    | PB_DP to AGND                            | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO2, I2C_SCL2 to AGND                  | -0.3 | 6                  | V    |

| I/O voltage range    | PB_DM to AGND                            | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO3, I2C_SDA2 to AGND                  | -0.3 | 6                  | V    |

| I/O voltage range    | PB_BUS to AGND                           | -0.3 | 30                 | V    |

| I/O voltage range    | GPIO4                                    | -0.3 | 6                  | V    |

| I/O voltage range    | GPIO5, NTC to AGND                       | -0.3 | 6                  | V    |

| I/O voltage range    | GPIO6, SYNC to AGND                      | -0.3 | 6                  | V    |

# 6.1 Absolute Maximum Ratings (continued)

Over the recommended operating junction temperature range of -40°C to 150°C and AGND = PGND (unless otherwise noted)<sup>(1)</sup> (2)

|                                               |                                                                      | MIN     | MAX               | UNIT |

|-----------------------------------------------|----------------------------------------------------------------------|---------|-------------------|------|

| Input current                                 | EN/UVLO                                                              | 0       | 2                 | mA   |

| Output current                                | Positive source current on PA_CC1, PA_CC2, PB_CC1, PB_CC2            | i       | nternally limited | А    |

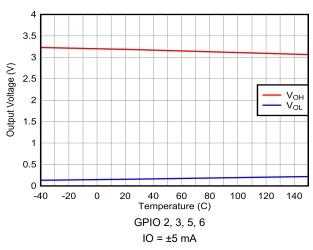

| Output current                                | GPIO 2, 3, 5, 6, 7, 8                                                |         | 0.0010            | А    |

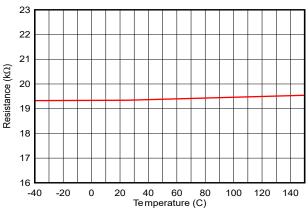

| Output current                                | GPIO 0, 1, 4, 9                                                      |         | 0.005             | А    |

| Output current                                | positive sink current for I2C_SDA1, I2C_SCL1,<br>I2C_SDA2, I2C2_SCL2 | i       | nternally limited | А    |

| Output current                                | positive source current for LDO_5V, LDO_3V3, LDO_1V5                 | i       | nternally limited | А    |

| T <sub>A</sub> Operating ambient tempera      | ture                                                                 | -40 125 |                   | °C   |

| T <sub>J</sub> Operating junction temperature |                                                                      | -40     | 150               | °C   |

| T <sub>STG</sub> Storage temperature          | T <sub>STG</sub> Storage temperature                                 |         | 150               | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) All voltage values are with respect to PGND or AGND. Connect the PGND pin directly to the Ground plane of the board. The PGND and AGND traces can be connected near the AGND pin.

(3) When the buck-boost is operating and  $V_{IN}$  exceeds 18 V, the positive slew rate  $dV_{IN}/dt$  must not exceed 200V/ms.

(4) When applying V<sub>IN</sub>, the time from V<sub>IN</sub> exceeding 5 V to V<sub>IN</sub> exceeding 25 V must not be less than 2 μs and can be achieved by properly sizing the input EMI filter.

(5) EN/UVLO pin is internally clamped to 10V. Ensure input current rating is not exceeded by connecting current limit resistor.

(6) BOOT2 with respect to SW2 during OUT overvoltage conditions can be -15 V due to internal clamp.

(7) SW1 can undershoot PGND by -1 V during negative switching transients as up to 10A (peak) may flow through the body diode. Typical duration ~20 ns. SW1 can overshoot OUT by 1 V during positive transients. Typical duration ~ 20 ns.

(8) SW2 can undershoot PGND by -2 V during switching transients as up to 10A (peak) may flow through the body diode. Typical duration ~20 ns. SW2 can overshoot OUT by 1 V during positive transients. Typical duration ~20 ns.

# 6.2 ESD Ratings

|                    |                         |                                                    |                                                                                                | VALUE                | UNIT |

|--------------------|-------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per<br>AEC Q100-002        |                                                                                                | ±2000 <sup>(1)</sup> | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per<br>AEC Q100-011    |                                                                                                | ±750 <sup>(2)</sup>  | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | IEC61000-4-2 Air-gap discharge<br>150 pF, 330 Ω.   | OUT, CSP, CSN/BUS, PA_CC1,<br>PA_CC2, PA_DP, PA_DM,<br>PB_CC1, PB_CC2, PB_DP,<br>PB_DM, PB_BUS | ±2000 <sup>(3)</sup> | v    |

| V <sub>(ESD)</sub> | Electrostatic discharge | IEC61000-4-2 Contact discharge<br>150 pF, 330 Ω.   | OUT, CSP, CSN/BUS, PA_CC1,<br>PA_CC2, PA_DP, PA_DM,<br>PB_CC1, PB_CC2, PB_DP,<br>PB_DM, PB_BUS | ±2000 <sup>(3)</sup> | v    |

| V <sub>(ESD)</sub> | Electrostatic discharge | ISO 10605 Contact discharge<br>330 pF, 330 Ω.      | OUT, CSP, CSN/BUS, PA_CC1,<br>PA_CC2, PA_DP, PA_DM,<br>PB_CC1, PB_CC2, PB_DP,<br>PB_DM, PB_BUS | ±2000 <sup>(3)</sup> | v    |

| V <sub>(ESD)</sub> | Electrostatic discharge | ISO 10605 Air-gap discharge 330 pF, 330 $\Omega$ . | OUT, CSP, CSN/BUS, PA_CC1,<br>PA_CC2, PA_DP, PA_DM,<br>PB_CC1, PB_CC2, PB_DP,<br>PB_DM, PB_BUS | ±2000 <sup>(3)</sup> | v    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

(2) The passing level per AEC-Q100 Classification C2b.

(3) Test conducted on Texas Instruments evaluation board.

# 6.3 Recommended Operating Conditions

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise noted)

|                 |                                                                  |                                            | MIN  | MAX   | UNIT |

|-----------------|------------------------------------------------------------------|--------------------------------------------|------|-------|------|

| VI              | Input voltage range (up to 65W output)                           | IN                                         | 6.8  | 18    | V    |

| VI              | Input voltage range (up to 30W output)                           | IN                                         | 5.5  | 18    | V    |

| VI              | Input voltage range                                              | EN/UVLO                                    | 0    | 7 (2) | V    |

| lı              | Input current                                                    | EN/UVLO                                    | 0    | 1     | mA   |

| VI              | Input voltage range                                              | LDO_5V when overdriven by external supply  | 4.75 | 5.5   | V    |

| VI              | Input voltage range                                              | CSP, CSN/BUS                               | 0    | 22    | V    |

| VI              | Input voltage range                                              | PB_VBUS (GPIO4 when configured as PB_VBUS) | 3    | 22    | V    |

| Vo              | Output voltage range                                             | OUT                                        | 0    | 21    | V    |

| V <sub>IO</sub> | I/O voltage range                                                | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2          | 0    | 5.5   | V    |

| V <sub>IO</sub> | I/O voltage range                                                | PA_DP, PA_DM, PB_DP, PB_DM                 | 0    | 3.6   | V    |

| V <sub>IO</sub> | I/O voltage range                                                | I2C_SDAn, I2C_SCLn, IRQn (n=1<br>or 2)     | 0    | 5.5   | V    |

| V <sub>IO</sub> | I/O voltage range                                                | GPIOn (n = 0 - 9)                          | 0    | 3.6   | V    |

| V <sub>IO</sub> | I/O voltage range                                                | NTC monitor (GPIO5), SYNC<br>(GPIO6)       | 0    | 3.6   | V    |

| lo              | Output current <sup>(1)</sup>                                    | IOUT                                       |      | 5     | А    |

| I <sub>O</sub>  | Output current                                                   | PA_CC1, PA_CC2, PB_CC1,<br>PB_CC2          |      | 225   | mA   |

| lo              | Output current (from LDO_3V3)                                    | GPIOn (n = 0 - 9)                          |      | 10    | mA   |

| fsw             | Buck-boost converter switching<br>frequency driven from SYNC pin |                                            | 250  | 500   | kHz  |

| T <sub>A</sub>  | Ambient operating temperature                                    |                                            | -40  | 125   | °C   |

| TJ              | Operating junction temperature                                   |                                            | -40  | 150   | °C   |

(1) Average LC filtered output current from buck-boost power stage. Operation with I<sub>OUT</sub> > 3A with V<sub>OUT</sub> > 10 V may result in thermal shutdown.

(2) EN/UVLO MAX specification applies when current into pin is not externally limited.

# 6.4 Recommended Components

over operating free-air temperature range (unless otherwise noted)

|                                         | PARAMETER <sup>(1)</sup>                    | VOLTAGE RATING | MIN  | TYP | MAX | UNIT |

|-----------------------------------------|---------------------------------------------|----------------|------|-----|-----|------|

| C <sub>IN</sub>                         | Capacitance on VIN                          | 40 V           | 22   | 47  |     | μF   |

| C <sub>LDO_5V</sub>                     | Capacitance on LDO_5V (supplied internally) | 10 V           | 4.7  |     | 10  | μF   |

| C <sub>LDO_5V</sub>                     | Capacitance on LDO_5V (supplied externally) | 10 V           | 10   | 47  | 100 | μF   |

| C <sub>LDO_3V3</sub>                    | Capacitance on LDO_3V3                      | 6.3 V          | 4.7  |     | 10  | μF   |

| C <sub>LDO_1V5</sub>                    | Capacitance on LDO_1V5                      | 6.3 V          | 4.7  |     | 10  | μF   |

| C <sub>Px_CCy</sub>                     | Capacitance on Px_CCy pins <sup>(2)</sup>   | 6.3 V          | 200  | 330 | 480 | pF   |

| C <sub>BOOT1</sub> , C <sub>BOOT2</sub> | Boot charge capacitance                     | 10 V           | 0.08 | 0.1 | 0.3 | μF   |

| R <sub>Snubber_SW1</sub>                | RC snubber resistor on SW1                  | 35 V, 0.25 W   |      | 1.1 |     | Ω    |

| C <sub>Snubber_SW1</sub>                | RC snubber capacitor on SW1                 | 35 V           |      | 1   |     | nF   |

| R <sub>Snubber_SW2</sub>                | RC snubber resistor on SW2                  | 35 V, 0.25 W   |      | 1.1 |     | Ω    |

| C <sub>Snubber_SW2</sub>                | RC snubber capacitor on SW2                 | 35 V           |      | 3.3 |     | nF   |

# 6.4 Recommended Components (continued)

over operating free-air temperature range (unless otherwise noted)

| PA                                                                       | PARAMETER <sup>(1)</sup>                                                  |       | MIN   | TYP  | MAX   | UNIT |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-------|-------|------|-------|------|

| C <sub>OUT</sub>                                                         | Capacitance on OUT <sup>(4)</sup>                                         | 35 V  | 30    | 33   | 40    | μF   |

| C <sub>BUS</sub>                                                         | Capacitance on PA_VBUS                                                    | 35 V  | 100   | 120  | 150   | μF   |

| L                                                                        | Inductor <sup>(4)</sup>                                                   |       | 3.3   | 4.7  | 5.6   | μH   |

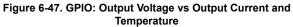

| NTC                                                                      | Thermistor                                                                |       | 47    |      | 100   | kΩ   |

| R <sub>EN/UVLO</sub>                                                     | Enable/UVLO pull up resistance                                            |       | 47    |      |       | kΩ   |

| TVPS pin components<br>(C <sub>TVSP</sub>    (Damper <sub>R + C</sub> )) | C <sub>TVSP</sub> Capacitance on TVSP pin                                 | 40 V  | 0.08  | 0.1  | 0.12  | μF   |

| TVPS pin components<br>(C <sub>TVSP</sub>    (Damper <sub>R + C</sub> )) | Damper resistor R of R + C network in Parallel with $C_{TVSP}$            | 0.25W | 8     | 10   | 12    | Ω    |

| TVPS pin components<br>(C <sub>TVSP</sub>    (Damper <sub>R + C</sub> )) | Damper capacitor C of R + C<br>network in Parallel with C <sub>TVSP</sub> | 40 V  | 0.376 | 0.47 | 0.564 | μF   |

| ESR <sub>CTVSP</sub>                                                     | TVSP Capacitor ESR (eq series resistance)                                 |       |       | 10   |       | mΩ   |

| ESL <sub>CTVSP</sub>                                                     | TVSP Capacitor ESL (eq series inductance)                                 |       |       | 1    |       | nH   |

(1) Capacitance values do not include any derating factors. For example, if 5.0 µF is required and the external capacitor value reduces by 50% at the required operating voltage, then the required external capacitor value is 10 µF.

(2) This includes all capacitance to the Type-C receptacle.

(3) Maximum capacitance allowed on TVSP pin to ensure proper decode of device configuration during boot.

(4) See applications section for recommended L and C<sub>OUT</sub> combinations.

# 6.5 Thermal Information

|                       |                                              | TPS25772-Q1 |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | Hot Rod     | UNIT |

|                       |                                              | 29 PINS     |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 33.3        |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.1        |      |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 7.3         | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3         |      |

| Ψјв                   | Junction-to-board characterization parameter | 7.2         |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.6 Buck-Boost Regulator

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the -40°C to 150°C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, V<sub>EN/UVLO</sub> = 2V unless otherwise stated. <sup>(1)</sup>

|                         | PARAMETER                                     | TEST CONDITION                                                               | MIN  | TYP  | MAX  | UNIT |

|-------------------------|-----------------------------------------------|------------------------------------------------------------------------------|------|------|------|------|

| SUPPLY VOLTA            | GE (VIN)                                      |                                                                              |      |      |      |      |

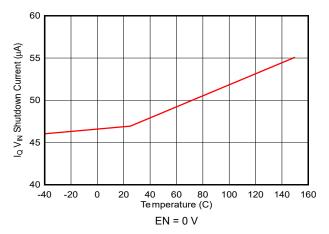

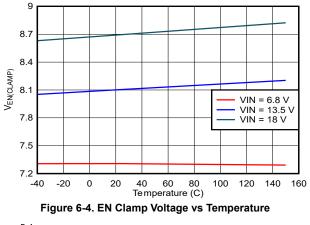

| IQ                      | V <sub>IN</sub> shutdown current              | V <sub>EN/UVLO</sub> = 0 V                                                   |      |      | 130  | μA   |

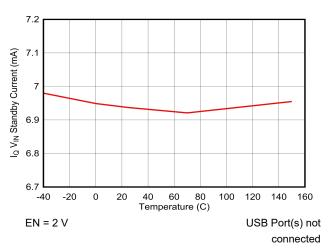

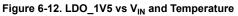

| I <sub>Q</sub>          | V <sub>IN</sub> operating current             | $V_{EN/UVLO} = 2V, V_{OUT} = 5 V, I_{OUT} = 0$                               |      | 8    |      | mA   |

| I <sub>Q</sub>          | V <sub>IN</sub> operating current             | V <sub>EN/UVLO</sub> = 1V, V <sub>OUT</sub> = 0 V, I <sub>OUT</sub> = 0<br>A |      |      | 4.5  | mA   |

| Ι <sub>Q</sub>          | V <sub>IN</sub> operating current             | V <sub>EN/UVLO</sub> = 2V, V <sub>OUT</sub> = 0 V, I <sub>OUT</sub> = 0<br>A |      |      | 8    | mA   |

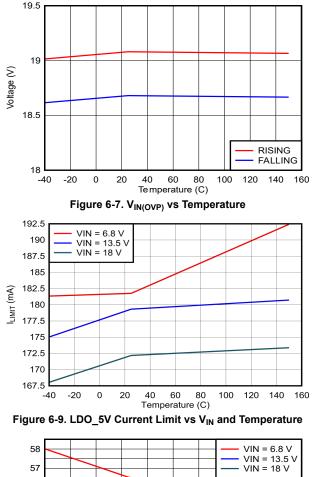

| V <sub>IN(OVP_R)</sub>  | V <sub>IN</sub> rising overvoltage threshold  | V <sub>IN</sub> rising.                                                      | 18.4 | 19.2 | 20   | V    |

| V <sub>IN(OVP_F)</sub>  | V <sub>IN</sub> falling overvoltage threshold | V <sub>IN</sub> falling.                                                     | 18.0 | 18.8 | 19.6 | V    |

|                         | hysteresis                                    |                                                                              |      | 0.4  |      | V    |

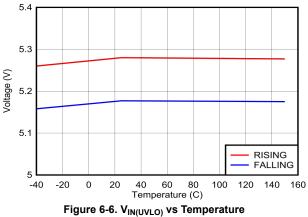

| V <sub>IN(UVLO_R)</sub> | V <sub>IN</sub> undervoltage lockout rising   | V <sub>IN</sub> rising.                                                      | 5.14 | 5.30 | 5.46 | V    |

| VIN(UVLO_F)             | V <sub>IN</sub> undervoltage lockout falling  | V <sub>IN</sub> falling.                                                     | 5.04 | 5.20 | 5.36 | V    |

Copyright © 2024 Texas Instruments Incorporated

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the  $-40^{\circ}$ C to  $150^{\circ}$ C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, V<sub>EN/UVLO</sub> = 2V unless otherwise stated. <sup>(1)</sup>

|                               | PARAMETER                                         | TEST CONDITION                                                                                                                                             | MIN   | TYP  | MAX   | UNIT |

|-------------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

|                               | hysteresis                                        |                                                                                                                                                            |       | 0.1  |       | V    |

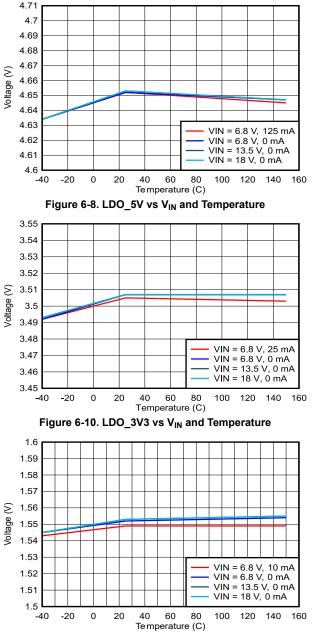

| LDO_5V OUTPUT                 |                                                   |                                                                                                                                                            |       |      |       |      |

| V <sub>LDO_5V</sub>           | LDO_5V Output Regulation voltage                  | $7V \le V_{IN} \le 18 \text{ V}, 0 < I_{LDO_{5V}} < 125\text{mA}, V_{EN} = 2 \text{ V}.$                                                                   | 4.5   | 4.63 | 4.75  | V    |

| V <sub>LDO_5V(UVLO_R)</sub>   | LDO_5V Undervoltage lockout rising                |                                                                                                                                                            | 4.29  | 4.4  | 4.51  | V    |

| V <sub>LDO_5V(UVLO_F)</sub>   | LDO_5V Undervoltage lockout falling               |                                                                                                                                                            | 4.09  | 4.2  | 4.31  | V    |

|                               | Undervoltage hysteresis                           |                                                                                                                                                            |       | 200  |       | mV   |

| V <sub>LDO_5V_DO</sub>        | drop out voltage                                  | V <sub>IN</sub> = 5.5 V; I <sub>LDO_5V</sub> = 125mA                                                                                                       | 4.3   |      |       | V    |

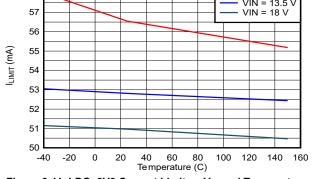

| I <sub>LDO_5V(ILIMIT)</sub>   | LDO_5V current limit                              | $V_{LDO\_V5V} = 0 \text{ to } 3.5 \text{ V},$<br>$R_{LDO\_V5V\_LOAD} = 1 \Omega$                                                                           | 125   | 200  | 400   | mA   |

| LDO_3V3 OUTPUT                |                                                   |                                                                                                                                                            |       |      |       |      |

| V <sub>LDO_3V3</sub>          | LDO_3V3 Output regulation voltage                 | $ \begin{array}{l} 7V \leq V_{IN} \leq 18 \ V, \ V_{EN} = 2 \ V, \\ V_{LDO\_5V(UVLO)} < V_{LDO\_5V} < 5.5 \ V, \ 0 \\ < I_{LDO\_3V3} < 25 mA \end{array} $ | 3.4   | 3.5  | 3.6   | V    |

| V <sub>LDO_3V3</sub> (UVLO_R) | LDO_3V3 Undervoltage lockout<br>rising            |                                                                                                                                                            | 3.2   | 3.3  | 3.4   | V    |

| V <sub>LDO_3V3</sub> (UVLO_F) | LDO_3V3 Undervoltage lockout falling              |                                                                                                                                                            | 3.05  | 3.15 | 3.25  | V    |

|                               | Undervoltage hysteresis                           |                                                                                                                                                            |       | 150  |       | mV   |

| V <sub>LDO_3V3_DO</sub>       | drop out voltage                                  | VIN = 4.5 V, I <sub>LDO_3V3</sub> = 30mA                                                                                                                   | 3.3   |      |       | V    |

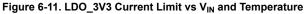

| ILDO_3V3(ILIMIT)              | LDO_3V3 current limit                             | $V_{LDO_{3V3}} = 0$ to 2.5 V, $R_{LDO_{3V3}LOAD}$<br>= 1 $\Omega$                                                                                          | 35    | 50   | 80    | mA   |

| LDO_1V5 OUTPUT                |                                                   |                                                                                                                                                            |       |      |       |      |

| V <sub>LDO_1V5</sub>          | LDO_1V5 Output Regulation voltage                 | 4.5 < V <sub>LDO_5V</sub> < 5.5V, 0 < I <sub>LDO_1V5</sub> < 10 mA                                                                                         | 1.49  | 1.55 | 1.65  | V    |

| V <sub>LDO_1V5</sub> (UVLO_R) | LDO_1V5 Undervoltage lockout rising               |                                                                                                                                                            | 1.44  | 1.49 | 1.54  | V    |

| V <sub>LDO_1V5</sub> (UVLO_F) | LDO_1V5 Undervoltage lockout<br>falling           |                                                                                                                                                            | 1.37  | 1.42 | 1.47  | V    |

|                               | Undervoltage hysteresis                           |                                                                                                                                                            |       | 70   |       | mV   |

| I <sub>LDO_1V5(ILIMIT)</sub>  | LDO_1V5 current limit                             | $V_{LDO_1V5} = 0$ to 1.2 V, $R_{LDO_1V5_LOAD}$<br>= 1 $\Omega$                                                                                             | 15    | 20   | 28    | mA   |

| EN/UVLO                       |                                                   |                                                                                                                                                            |       |      |       |      |

| V <sub>EN(LDO_V5V_R)</sub>    | EN input level required to turn on internal LDOs  | EN/UVLO rising                                                                                                                                             |       |      | 1.05  | V    |

| V <sub>EN(LDO_V5V_F)</sub>    | EN input level required to turn off internal LDOs | EN/UVLO falling                                                                                                                                            | 0.3   |      |       | V    |

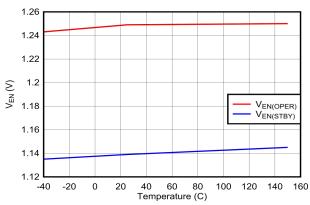

| V <sub>EN(OPER)</sub>         | EN input level required to start operation        | EN/UVLO rising Precision EN                                                                                                                                | 1.2   | 1.25 | 1.3   | V    |

| V <sub>EN(STBY)</sub>         | EN input level required to stop operation         | EN/UVLO falling                                                                                                                                            | 1.1   | 1.15 | 1.2   | V    |

| V <sub>EN(HYS)</sub>          | Hysteresis                                        |                                                                                                                                                            |       | 100  |       | mV   |

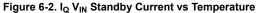

| V <sub>EN(CLAMP)</sub>        | EN input clamp voltage                            | $V_{EN/UVLO} > V_{EN(CLAMP)}$ , 10 µA < I <sub>EN/</sub><br><sub>UVLO</sub> < 1 mA                                                                         | 6     | 9    | 12    | V    |

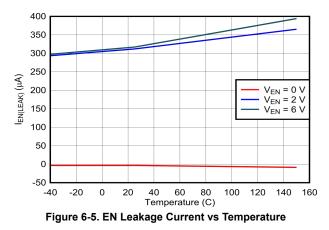

| I <sub>EN(LEAK)</sub>         | Leakage current into EN pin                       | 0 V < V <sub>EN</sub> < 6 V                                                                                                                                |       |      | 1     | μA   |

| OUTPUT VOLTAGE                | E                                                 |                                                                                                                                                            |       |      |       |      |

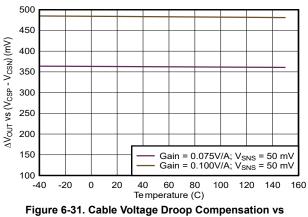

| V <sub>CSN/BUS(3V)</sub>      | V <sub>CNS/BUS</sub> regulation accuracy at 3V    | $0 \le I_{OUT} \le 3A$                                                                                                                                     | 2.9   | 3    | 3.1   | V    |

| V <sub>CSN/BUS(5V)</sub>      | V <sub>CNS/BUS</sub> regulation accuracy at 5V    | $0 \le I_{OUT} \le 3A$                                                                                                                                     | 4.85  | 5    | 5.15  | V    |

| V <sub>CSN/BUS(21V)</sub>     | V <sub>CNS/BUS</sub> regulation accuracy at 21V   | $0 \le I_{OUT} \le 3A$                                                                                                                                     | 20.48 | 21   | 21.53 | V    |

| V <sub>CSN/BUS_STP</sub>      | Output voltage step size (12-bit DAC)             |                                                                                                                                                            |       | 10   |       | mV   |

| VDAC Resolution               | Resolution of V <sub>BUS</sub> DAC                |                                                                                                                                                            |       | 12   |       | Bits |

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the -40°C to 150°C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, V<sub>EN/UVLO</sub> = 2V unless otherwise stated. <sup>(1)</sup>

| -                            | herwise stated.V <sub>IN</sub> = 13.5 V, V <sub>EI</sub><br>PARAMETER | TEST CONDITION                                                                                                   | MIN  | TYP  | MAX  | UNIT |

|------------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| IDISCHG                      | CSN/BUS discharge current when transitioning to VSafe0V               | $V_{CSP} = V_{CSN/BUS}$ . $V_{CSN/BUS} = 3V$ .<br>Measure current into BUS.                                      | 40   |      |      | mA   |

| t <sub>DISCHG</sub>          | CSN/BUS discharge time when<br>transitioning to VSafe5V               | V <sub>BUS</sub> = 21 V (max), CBULK =<br>220 μF, time to discharge BUS to <<br>5.5 V (per USB PD specification) |      |      | 275  | ms   |

| t <sub>DISCHG</sub>          | CSN/BUS discharge time when<br>transitioning to VSafe0V               | V <sub>BUS</sub> = 21 V (max), CBULK =<br>220 μF, time to discharge BUS to <<br>0.8 V (per USB PD specification) |      |      | 650  | ms   |

| R <sub>DISCHG</sub>          | Weak discharge resistance on BUS pin when not sourcing VBUS           | EN = 2V; measure BUS to PGND resistance.                                                                         | 60   | ·    | 135  | kΩ   |

| R <sub>BUS-GND(PWR)</sub>    | BUS to GND resistance, R <sub>DISCH</sub> disabled, not sourcing VBUS | EN = 2V measure BUS to PGND resistance.                                                                          | 120  |      | 500  | kΩ   |

| R <sub>BUS-GND</sub> (UNPWR) | BUS to GND resistance, unpowered                                      | VIN = EN = 0V measure BUS to<br>PGND resistance.                                                                 |      | 2    |      | kΩ   |

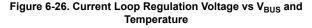

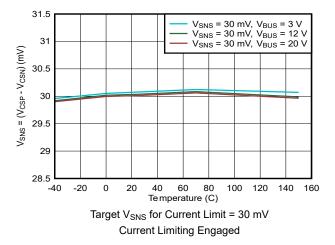

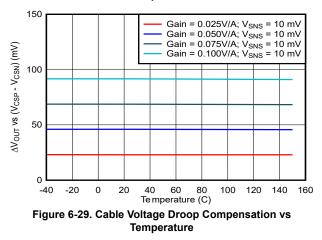

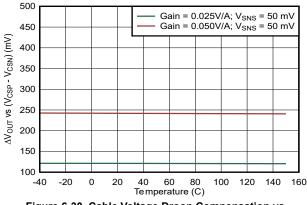

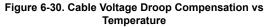

| CABLE VOLTAGE                | DROP COMPENSATION                                                     |                                                                                                                  |      |      |      |      |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs I <sub>OUT</sub>                         | Gain setting = 0.1V/A: $V_{CSP}$ - $V_{CSN/BUS}$ = 50 mV                                                         | 465  | 500  | 535  | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs I <sub>OUT</sub>                         | Gain setting = 0.1V/A: $V_{CSP}$ - $V_{CSN/BUS}$ = 10 mV                                                         | 85   | 100  | 115  | mV   |

| Vout_cdc                     | $\Delta V_{OUT}$ increase vs I <sub>OUT</sub>                         | Gain stetting = 0.075V/A: V <sub>CSP</sub> - V <sub>CSN/BUS</sub> = 50 mV                                        | 346  | 375  | 404  | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs I <sub>OUT</sub>                         | Gain setting = 0.075V/A: $V_{CSP} - V_{CSN/BUS} = 10 \text{ mV}$                                                 | 61   | 75   | 89   | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs $I_{OUT}$                                | Gain setting = 0.05V/A: V <sub>CSP</sub> - V <sub>CSN/BUS</sub> = 50 mV                                          | 227  | 250  | 273  | mV   |

| Vout_cdc                     | $\Delta V_{OUT}$ increase vs $I_{OUT}$                                | Gain setting = 0.05V/A: $V_{CSP}$ - $V_{CSN/BUS}$ = 10 mV                                                        | 37   | 50   | 63   | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs I <sub>OUT</sub>                         | Gain setting = 0.025V/A: V <sub>CSP</sub> - V <sub>CSN/BUS</sub> = 50 mV                                         | 109  | 125  | 141  | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs $I_{OUT}$                                | Gain setting = 0.025V/A: V <sub>CSP</sub> - V <sub>CSN/BUS</sub> = 10 mV                                         | 14   | 25   | 36   | mV   |

| V <sub>OUT_CDC</sub>         | $\Delta V_{OUT}$ increase vs $I_{OUT}$                                | Gain setting = 0V/A: 0 mV $\leq$ V <sub>CSP</sub> - V <sub>CSN/BUS</sub> $\leq$ 50 mV                            | -5   |      | 20   | mV   |

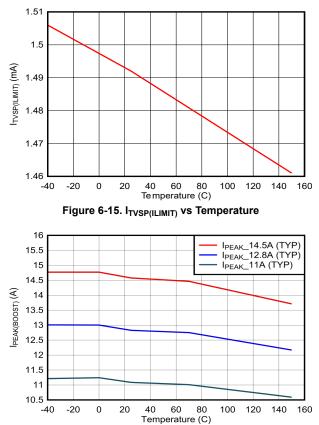

| BUCK-BOOST PE                | AK CURRENT LIMITS                                                     | 1                                                                                                                | 1    |      |      |      |

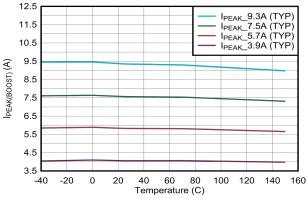

| I <sub>PEAK(BOOST)</sub>     | Boost peak current limit (in boost mode)                              |                                                                                                                  | 12.3 | 14.5 | 16.7 | А    |

| I <sub>PEAK(BOOST)</sub>     | Boost peak current limit (in boost mode)                              |                                                                                                                  | 10.8 | 12.8 | 14.7 | А    |

| I <sub>PEAK(BOOST)</sub>     | Boost peak current limit (in boost mode)                              |                                                                                                                  | 9.3  | 11.0 | 12.6 | А    |

| IPEAK(BOOST)                 | Boost peak current limit (in boost mode)                              |                                                                                                                  | 7.9  | 9.3  | 10.6 | А    |

| I <sub>PEAK(BOOST)</sub>     | Boost peak current limit (in boost mode)                              |                                                                                                                  | 6.3  | 7.5  | 8.6  | А    |

| I <sub>PEAK(BOOST)</sub>     | Boost peak current limit (in boost mode)                              |                                                                                                                  | 4.8  | 5.7  | 6.5  | А    |

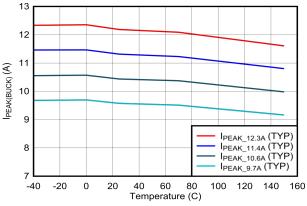

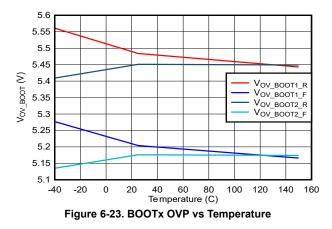

| I <sub>PEAK(BUCK)</sub>      | Buck peak current limit (in buck mode)                                |                                                                                                                  | 8.2  | 9.7  | 11.2 | А    |

| I <sub>PEAK(BUCK)</sub>      | Buck peak current limit (in buck mode)                                |                                                                                                                  | 9.0  | 10.6 | 12.1 | А    |

| I <sub>PEAK(BUCK)</sub>      | Buck peak current limit (in buck mode)                                |                                                                                                                  | 9.7  | 11.4 | 13.1 | А    |

| I <sub>PEAK(BUCK)</sub>      | Buck peak current limit (in buck mode)                                |                                                                                                                  | 10.4 | 12.3 | 14.1 | А    |

| I <sub>PEAK(BUCK)</sub>      | Buck peak current limit (in buck mode)                                |                                                                                                                  | 5.3  | 6.2  | 7.2  | А    |

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the -40°C to 150°C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, V<sub>EN/UVLO</sub> = 2V unless otherwise stated. <sup>(1)</sup>

|                            | PARAMETER                                         | N/UVLO = 2V unless otherwise stat                                                                           | MIN  | TYP   | MAX  | UNIT |

|----------------------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| PEAK(BUCK)                 | Buck peak current limit (in buck mode)            |                                                                                                             | 6    | 7.1   | 8.2  | A    |

| PEAK(BUCK)                 | Buck peak current limit (in buck mode)            |                                                                                                             | 6.8  | 8.0   | 9.1  | А    |

| PEAK(BUCK)                 | Buck peak current limit (in buck mode)            |                                                                                                             | 7.5  | 8.8   | 10.1 | А    |

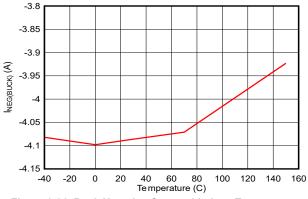

| NEG(BUCK)                  | Buck negative current limit (in buck mode)        |                                                                                                             | -4.6 | - 3.8 | -3   | А    |

| OUT CURRENT D              | AC                                                |                                                                                                             |      |       |      |      |

| IDAC_Resolution            |                                                   |                                                                                                             |      | 8     |      | Bits |

|                            |                                                   |                                                                                                             |      |       |      |      |

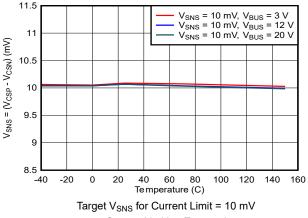

| LIMIT_LO                   | Current limit accuracy                            | 1 A $\leq$ I <sub>OUT</sub> $\leq$ 3 A, V <sub>CSN/BUS</sub> $<$ 2.5 V;<br>R <sub>S</sub> = 10 m $\Omega$ . | -250 |       | 250  | mA   |

| LIMIT_LO                   | Current limit accuracy < 1 A                      | 1 A $\leq$ I <sub>OUT</sub> $\leq$ 3 A, V <sub>CSN/BUS</sub> $\geq$ 2.5<br>V; R <sub>S</sub> = 10 mΩ        | -150 |       | 150  | mA   |

| I <sub>LIMIT_</sub> HI     | Current limit accuracy > 3 A                      | I <sub>OUT</sub> > 3 A, V <sub>CSN/BUS</sub> < 2.5 V; R <sub>S</sub> = 10 mΩ                                | -20  |       | 20   | %    |

| I <sub>LIMIT_HI</sub>      | Current limit accuracy > 3 A                      | I <sub>OUT</sub> > 3 A, V <sub>CSN/BUS</sub> ≥ 2.5 V; R <sub>S</sub> = 10 mΩ                                | -5   |       | 5    | %    |

| ILIMIT_MIN                 | Minimum programmable current limit                |                                                                                                             | 1    |       |      | А    |

| ICL STEP                   | Current limit step size                           | $1 \text{ A} \le I_{\text{OUT}} \le 5 \text{ A}; \text{ R}_{\text{S}} = 10 \text{ m}\Omega$                 |      | 50    |      | mA   |

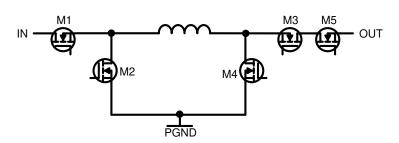

| FREQUENCY                  | •                                                 |                                                                                                             |      |       |      |      |

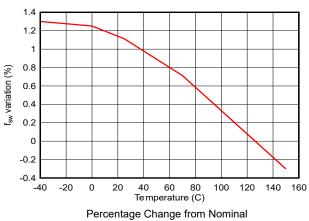

| fsw(1)                     | Switching Frequency 1                             |                                                                                                             | 285  | 300   | 315  | kHz  |

|                            | Switching Frequency 2                             |                                                                                                             | 380  | 400   | 420  | kHz  |

| fSW(2)                     |                                                   |                                                                                                             |      |       |      |      |

|                            | Switching Frequency 3                             |                                                                                                             | 428  | 450   | 473  | kHz  |

| FREQUENCY DITH             |                                                   |                                                                                                             |      |       |      |      |

| FS <sub>SS</sub>           | Positive frequency deviation during dither        |                                                                                                             | 8    | 10    | 12   | %    |

|                            | Negative frequency deviation during dither        |                                                                                                             | -12  | -10   | -8   | %    |

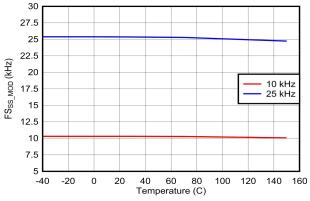

| FS <sub>SS_MOD</sub>       | Modulation frequency of dither                    | DITHER_FREQ = 0                                                                                             | 9    | 10    | 11   | kHz  |

| FS <sub>SS_MOD</sub>       | Modulation frequency of dither                    | DITHER_FREQ = 1                                                                                             | 22.5 | 25    | 27.5 | kHz  |

| OVERVOLTAGE P              | ROTECTION                                         |                                                                                                             |      |       |      |      |

| V <sub>CSN/BUS_OVP_R</sub> | Fixed output overvoltage threshold at CSN/BUS pin |                                                                                                             | 22.0 | 23    | 24   | V    |

| V <sub>CSN/BUS_OVP_F</sub> | Falling                                           |                                                                                                             | 20.5 | 21.5  | 22.5 | V    |

|                            | Hysteresis                                        |                                                                                                             |      | 1.5   |      | V    |

| POWER SWITCHE              | S                                                 | ·                                                                                                           |      |       | 11   |      |

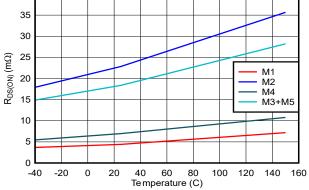

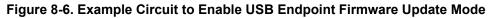

| R <sub>DS(ON)</sub>        | M1                                                | V <sub>IN</sub> = 12V; (V <sub>BOOT1</sub> - V <sub>SW1</sub> ) = 4.5V;<br>I <sub>SW1</sub> = -1 A          |      | 4.5   |      | mΩ   |

| R <sub>DS(ON)</sub>        | M2                                                | V <sub>IN</sub> = 12V; I <sub>SW1</sub> = 1 A                                                               |      | 20    |      | mΩ   |

| R <sub>DS(ON)</sub>        | M4                                                | V <sub>IN</sub> = 12V; I <sub>SW2</sub> = 1 A                                                               |      | 6     |      | mΩ   |

| R <sub>DS(ON)</sub>        | M3 + M5                                           | $V_{IN} = V_{OUT} = 12V$ : $(V_{BOOT2} - V_{SW2}) = 4.5V$ , $I_{SW2} = -1$ A                                |      | 18    |      | mΩ   |

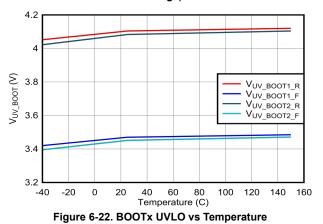

| V <sub>UV_BOOT1_R</sub>    | BOOT1 to SW1 rising UVLO threshold                |                                                                                                             | 3.5  | 4     | 4.4  | V    |

| V <sub>UV_BOOT1_F</sub>    | BOOT1 to SW1 falling UVLO threshold               |                                                                                                             | 2.9  | 3.4   | 3.7  | V    |

|                            | BOOT1 to SW1 UVLO hysteresis                      |                                                                                                             |      | 680   |      | mV   |

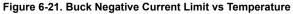

| V <sub>OV_BOOT1_R</sub>    | BOOT1 to SW1 rising OVP<br>threshold              |                                                                                                             | 4.6  | 5.3   | 5.9  | V    |

| V <sub>OV_BOOT1_F</sub>    | BOOT1 to SW1 falling OVP<br>threshold             |                                                                                                             | 4.3  | 5     | 5.6  | V    |

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the -40°C to 150°C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, V<sub>EN/UVLO</sub> = 2V unless otherwise stated. <sup>(1)</sup>

|                         | PARAMETER                             | TEST CONDITION | MIN | TYP | MAX | UNIT |

|-------------------------|---------------------------------------|----------------|-----|-----|-----|------|

|                         | BOOT 1 OVP hysteresis                 |                | 250 | 300 | 350 | mV   |

| V <sub>UV_BOOT2_R</sub> | BOOT2 to SW2 rising UVLO<br>threshold |                | 3.5 | 4   | 4.4 | V    |

| V <sub>UV_BOOT2_F</sub> | BOOT2 to SW2 falling UVLO threshold   |                | 2.9 | 3.4 | 3.7 | V    |

|                         | BOOT2 to SW2 UVLO hysteresis          |                |     | 680 |     | mV   |

| V <sub>OV_BOOT2_R</sub> | BOOT2 to SW2 rising OVP<br>threshold  |                | 4.6 | 5.3 | 5.9 | V    |

| V <sub>OV_BOOT2_F</sub> | BOOT2 to SW2 falling OVP threshold    |                | 4.3 | 5   | 5.6 | V    |

|                         | BOOT2 OVP hysteresis                  |                | 250 | 300 | 350 | mV   |

| BUCK-BOOST C            | HARACTERISTICS                        | ·              |     |     |     |      |

| t <sub>ss</sub>         | Soft-start time                       |                |     | 6   |     | ms   |

(1) All minimum and maximum limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

#### 6.7 CC Cable Detection Parameters

Typical values correspond to TJ = 25°C. Minimum and maximum limits apply over the -40°C to 150°C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, EN = 2 V, unless otherwise stated.

|                        | PARAMETER                                                                                                                                                                                                 | TEST CONDITIONS                                              | MIN  | TYP  | MAX | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|-----|------|

| Type-C Source (R       | p pull-up)                                                                                                                                                                                                |                                                              |      |      |     |      |

| V <sub>OC_3.3</sub>    | Unattached Px_CCy open circuit voltage while Rp enabled, no load                                                                                                                                          | R <sub>CC</sub> = 47 kΩ                                      | 1.85 |      |     | V    |

| V <sub>OC_5</sub>      | Attached Px_CCy open circuit voltage while Rp enabled, no load                                                                                                                                            | R <sub>CC</sub> = 47 kΩ                                      | 2.95 |      |     | V    |

| I <sub>Rev</sub>       | Unattached reverse current on<br>Px_CCy                                                                                                                                                                   | $V_{CCy}$ = 5.5V, $V_{CCx}$ = 0V, measure current into CCy   |      |      | 10  | μA   |

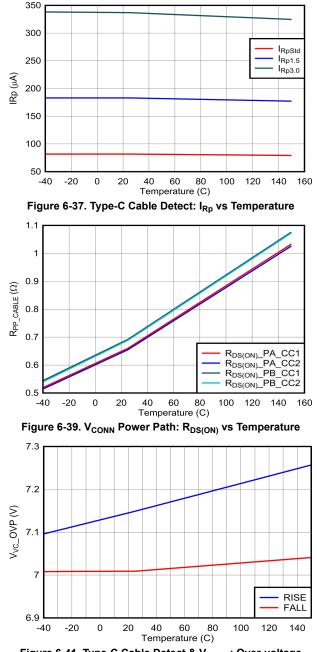

| I <sub>RpStd</sub>     | current source - Standard                                                                                                                                                                                 | $0 < V_{CCy} < 1.0$ V, measure $I_{CCy}$                     | 64   | 80   | 96  | μA   |

| I <sub>Rp1.5</sub>     | current source - 1.5A                                                                                                                                                                                     | $0 < V_{CCy} < 1.5$ V, measure I <sub>CCy</sub>              | 166  | 180  | 194 | μA   |

| I <sub>Rp3.0</sub>     | current source - 3.0A                                                                                                                                                                                     | $0 < V_{CCy} < 2.45$ V, measure $I_{CCy}$                    | 304  | 330  | 356 | μA   |

| Type-C Sink (Rd p      | ull-down)                                                                                                                                                                                                 |                                                              |      |      |     |      |

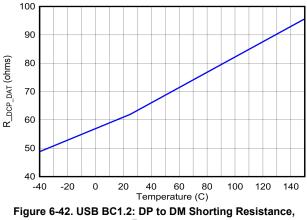

| R <sub>SNK</sub>       | Rd pulldown resistance                                                                                                                                                                                    | $0V \le V_{Px_CCy} \le 2.1 V$ , measure resistance on Px_CCy | 4.6  |      | 5.6 | kΩ   |

| R <sub>VCONN_DIS</sub> | VCONN discharge resistance                                                                                                                                                                                | $0V \le V_{Px_CCy} \le 5.5 V$ , measure resistance on Px_CCy | 4.0  |      | 6.6 | kΩ   |

| Common (Source         | and Sink)                                                                                                                                                                                                 |                                                              |      |      |     |      |

| t <sub>CC</sub>        | deglitch time for comparators on Px_CCy, this applies for V <sub>SRC1</sub> , V <sub>SRC2</sub> , V <sub>SRC3</sub> , V <sub>SNK1</sub> , V <sub>SNK2</sub> , V <sub>SNK3</sub> , and V <sub>SNK4</sub> . |                                                              |      | 2.56 |     | ms   |

# 6.8 CC VCONN Parameters

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the  $-40^{\circ}$ C to  $150^{\circ}$ C junction temperature range unless otherwise stated. V<sub>IN</sub> = 13.5 V, EN = 2 V unless otherwise stated.

| P                     | ARAMETER | TEST CONDITIONS                                                                                   | MIN | TYP | MAX | UNIT |

|-----------------------|----------|---------------------------------------------------------------------------------------------------|-----|-----|-----|------|

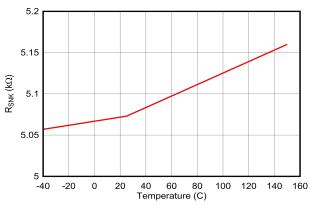

| R <sub>PP_CABLE</sub> |          | V <sub>LDO_5V</sub> = 5V, I <sub>L</sub> = 200 mA,<br>measure resistance from<br>LDO_5V to Px_CCy |     |     | 1.2 | Ω    |

# 6.8 CC VCONN Parameters (continued)

Typical values correspond to  $T_J = 25^{\circ}$ C. Minimum and maximum limits apply over the  $-40^{\circ}$ C to  $150^{\circ}$ C junction temperature range unless otherwise stated.  $V_{IN} = 13.5$  V, EN = 2 V unless otherwise stated.

|                           | PARAMETER                                                                                                                  | TEST CONDITIONS                                                                                           | MIN | TYP | MAX | UNIT |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| 1                         | short circuit current limit                                                                                                | setting 0, $V_{LDO_5V}$ = 5V,<br>R <sub>L</sub> =10m $\Omega$ , measure I <sub>Px_CCy</sub>               | 30  | 50  | 70  | mA   |

| ILIMVC                    | Short circuit current innit                                                                                                | setting 1, $V_{LDO_5V}$ = 5V,<br>R <sub>L</sub> =10m $\Omega$ , measure I <sub>Px_CCy</sub>               | 235 | 275 | 315 | ША   |

| I <sub>CCyLKG</sub>       | Leakage current into Px_Cy pins                                                                                            | VCONN disabled, $T_J \le 125 \text{ °C}$ , $V_{Px_CCy} = 5.5 \text{ V}$ ,<br>measure $I_{Px_CCy}$         | -1  | 0   | 10  | μA   |

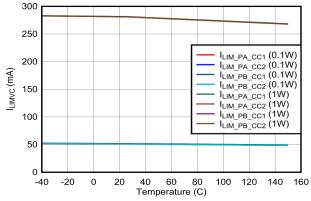

| V <sub>VC_OVP</sub>       | Over-voltage protection<br>threshold for Px_CCy                                                                            | $V_{LDO_{5V}}$ rising                                                                                     | 5.6 | 5.9 | 6.2 | V    |

| V <sub>VC_RCP</sub>       | Reverse current protection<br>threshold for Px_CCy,<br>sourcing VCONN through<br>CCx                                       | $V_{LDO_{5V}}$ = 5 V, $V_{CCx}$ rising, setting 1.                                                        | 230 | 310 | 390 | mV   |

| V <sub>VC_RCP</sub>       | Reverse current protection<br>threshold for Px_CCy,<br>sourcing VCONN through<br>CCx                                       | $V_{LDO_{5V}}$ = 5 V, $V_{CCx}$ rising, setting 2.                                                        | 60  | 155 | 250 | mV   |

| tpp_cable_fsd             | Time to disable Px_Cy<br>VCONN after $V_{LDO_5V} >$<br>$V_{VC_OVP}$ or $V_{CCx} - \overline{V}_{LDO_5V} >$<br>$V_{VC_RCP}$ | C <sub>L</sub> =0                                                                                         |     | 1.5 |     | μs   |

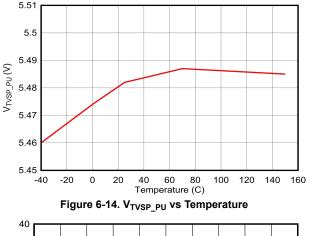

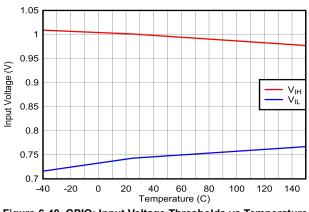

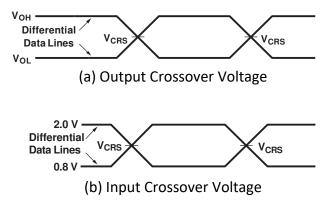

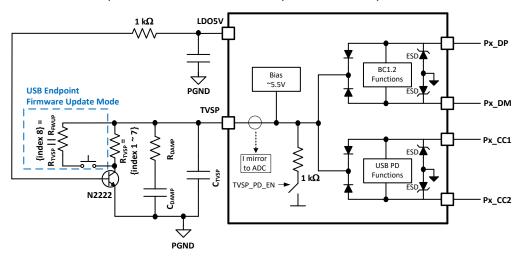

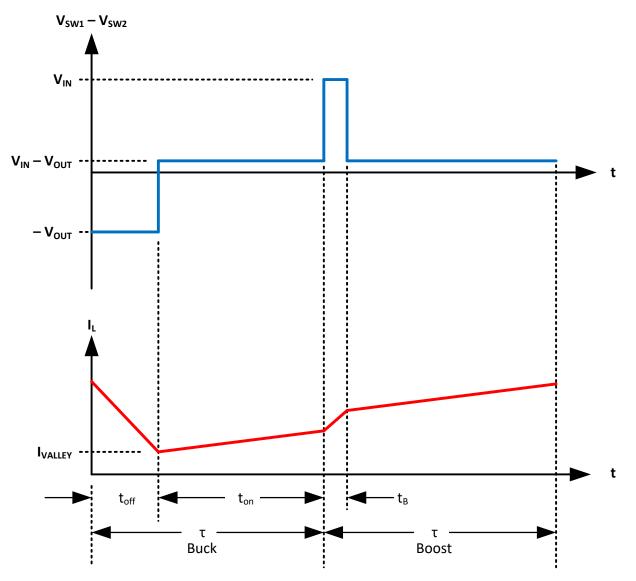

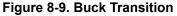

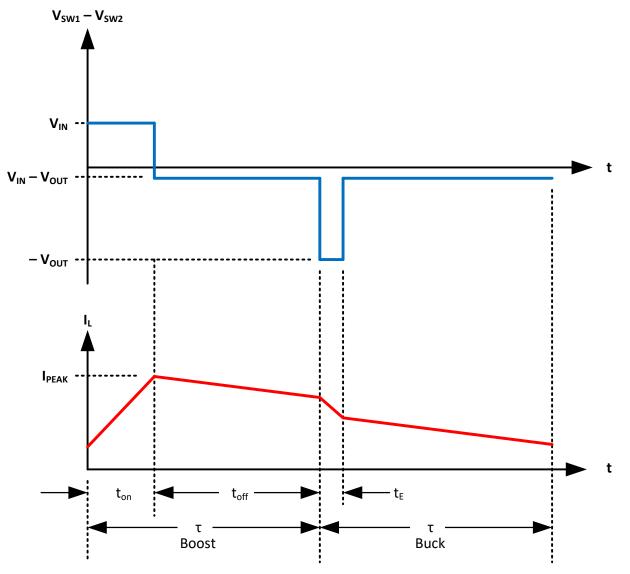

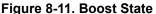

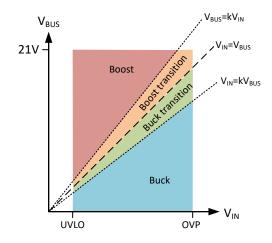

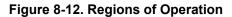

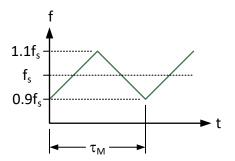

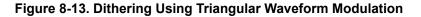

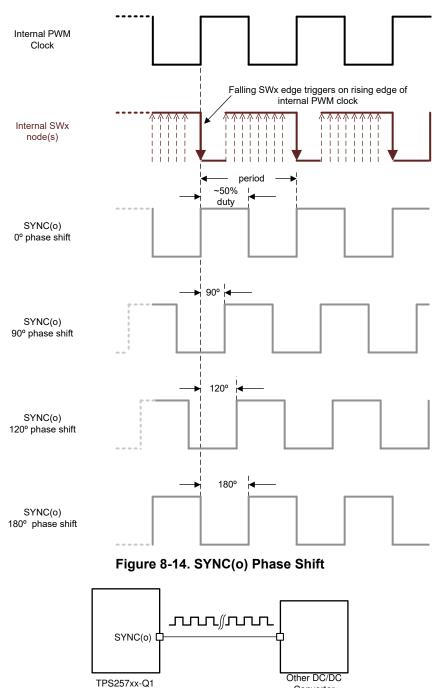

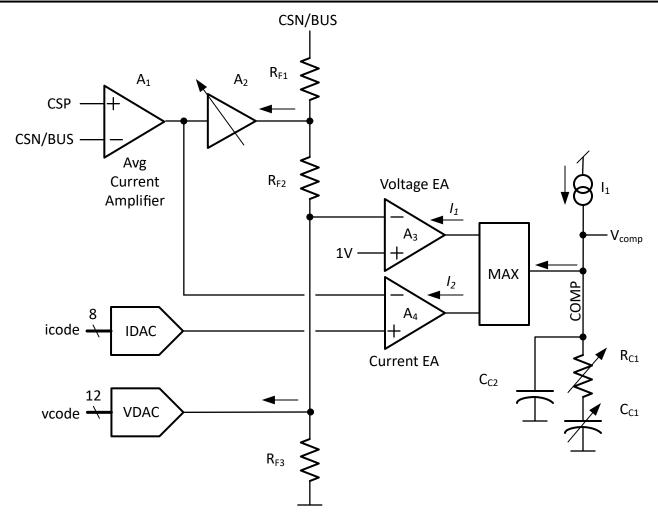

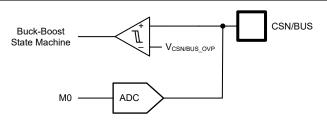

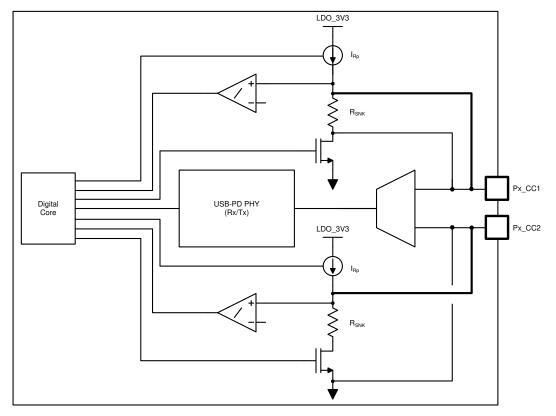

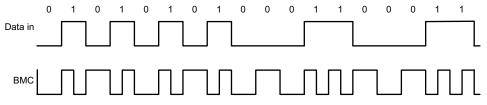

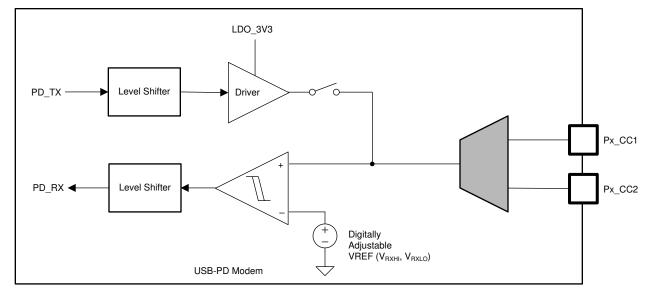

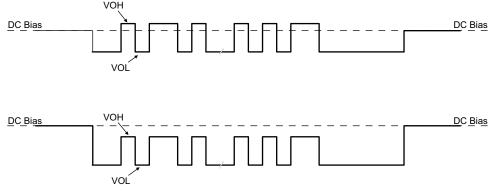

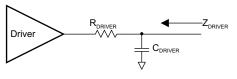

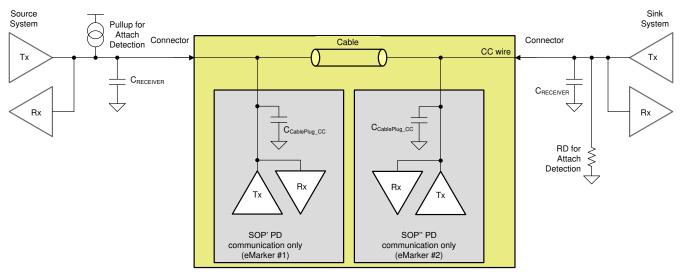

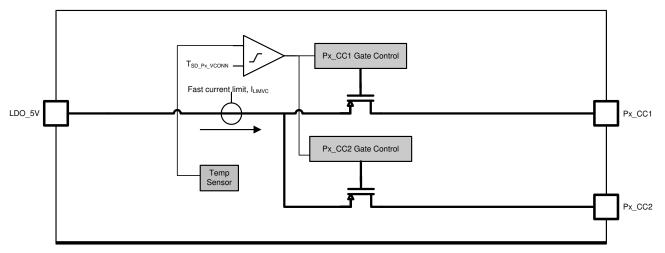

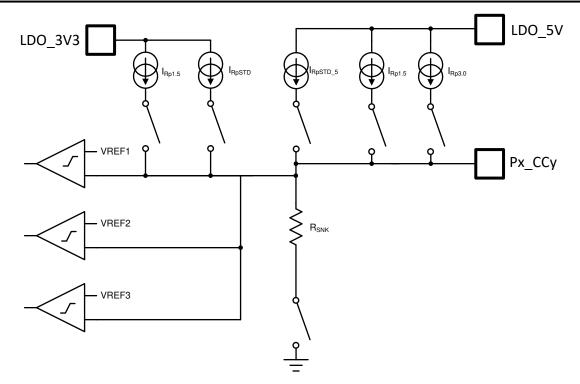

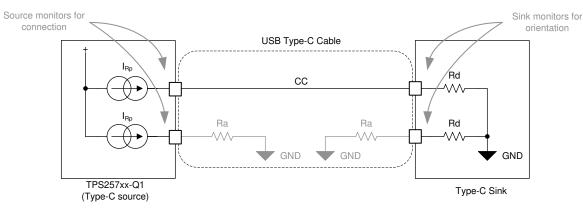

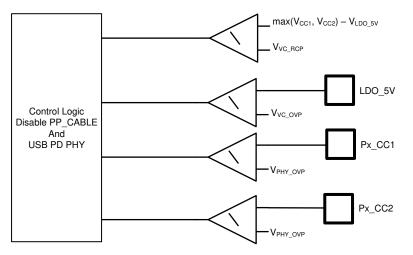

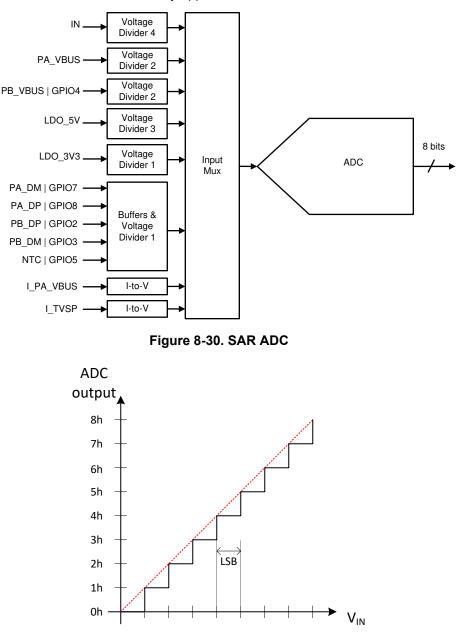

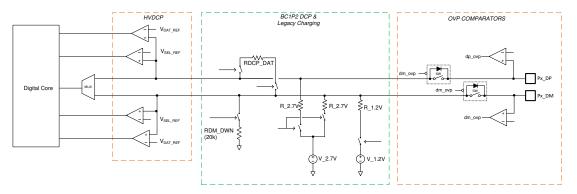

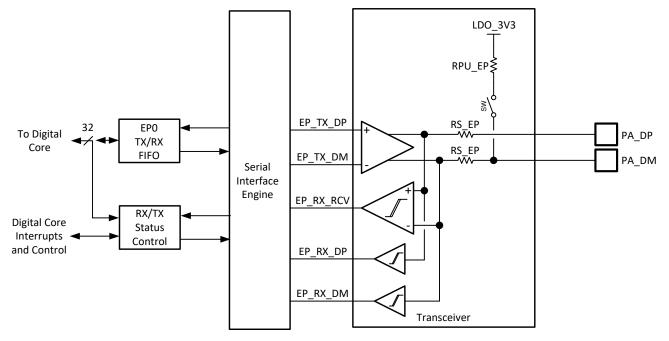

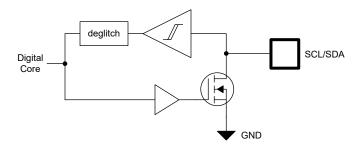

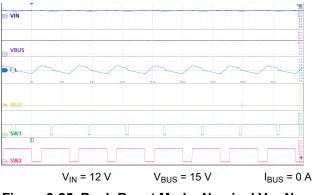

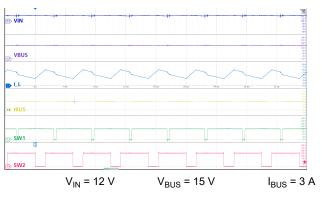

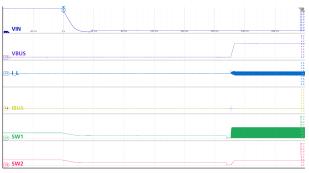

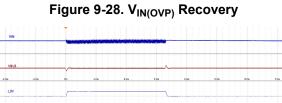

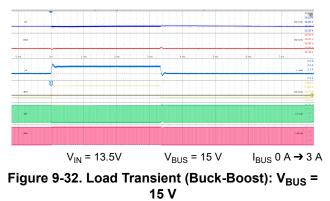

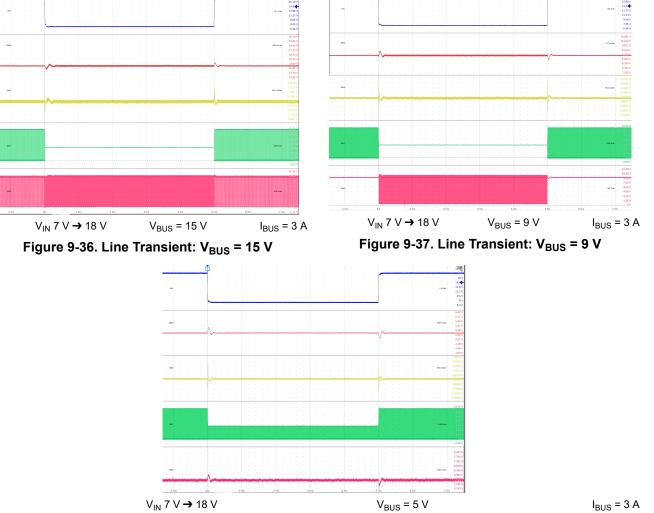

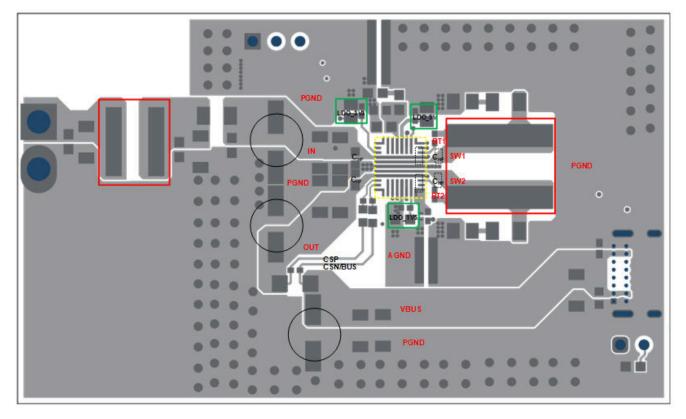

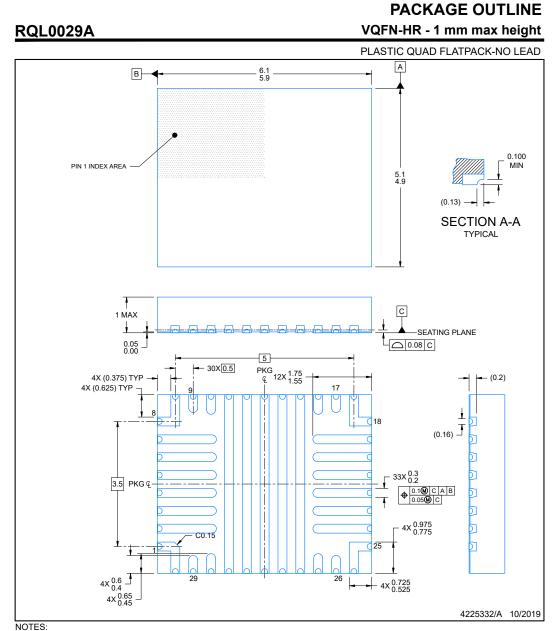

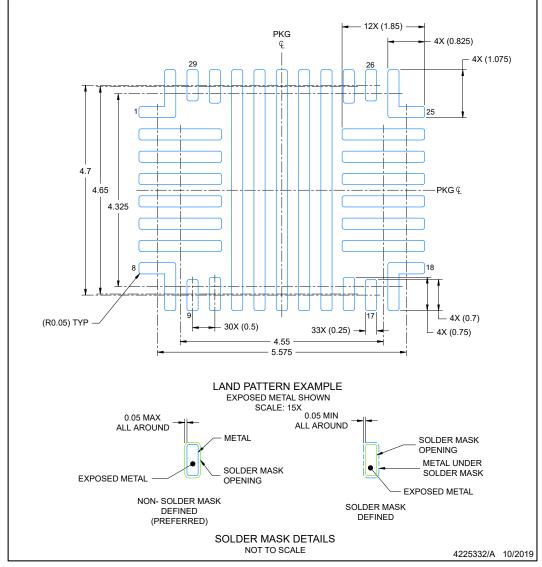

| t <sub>PP_CABLE_off</sub> | from disable signal to<br>Px_CCy at 10% of final<br>value                                                                  | I <sub>L</sub> = 200 mA, V <sub>LDO_5V</sub> = 5V,<br>C <sub>L</sub> =0                                   | 100 | 225 | 300 | μs   |