Sample &

Buy

**TPS22993**

SLVSCA3A-NOVEMBER 2013-REVISED MARCH 2014

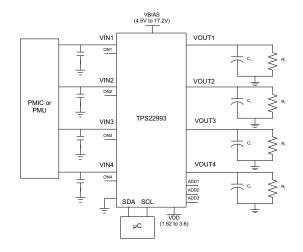

# TPS22993 Quad Channel Load Switch with GPIO and I<sup>2</sup>C Control

#### Features 1

Texas

Input Voltage: 1.0V to 3.6V

**INSTRUMENTS**

- Low ON-State Resistance ( $V_{BIAS} = 7.2V$ )

- R<sub>ON</sub> = 15mΩ at V<sub>IN</sub> = 3.3V

- R<sub>ON</sub> = 15m $\Omega$  at V<sub>IN</sub> = 1.8V

- R<sub>ON</sub> = 15m $\Omega$  at V<sub>IN</sub> = 1.5V

- R<sub>ON</sub> = 15mΩ at V<sub>IN</sub> = 1.05V

- VBIAS voltage range: 4.5V to 17.2V

- Suitable for 2S/3S/4S Li-ion Battery Topologies

- 1.2A Max Continuous Current per Channel

- Quiescent Current

- Single Channel < 9µA</li>

- All Four Channels < 17µA</li>

- Shutdown Current (all four channels) < 6µA

- Four 1.2V Compatible GPIO Control Inputs

- I<sup>2</sup>C Configuration (per channel)

- On/Off Control

- Programmable Slew Rate Control (5 options)

- Programmable ON-delay (4 options)

- Programmable Output Discharge (4 options)

- I<sup>2</sup>C SwitchALL<sup>™</sup> Command for Multichannel/Multi-chip Control

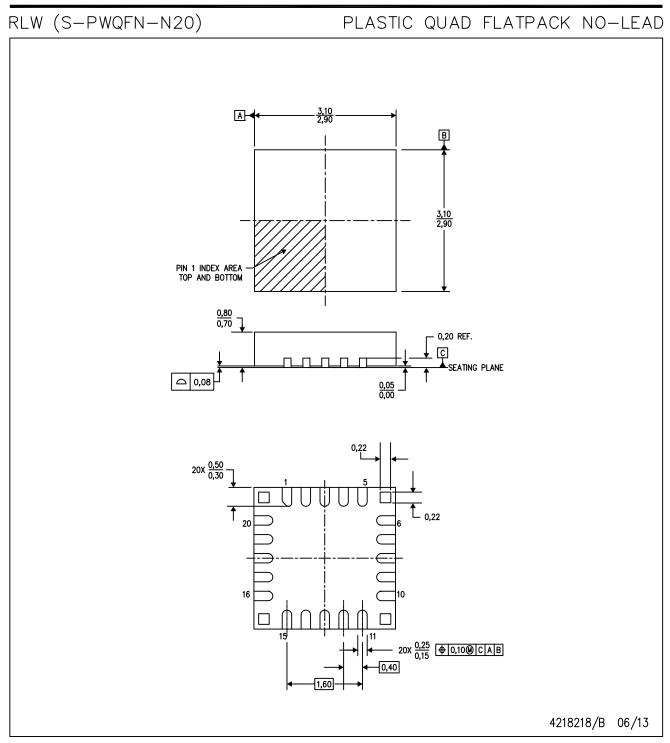

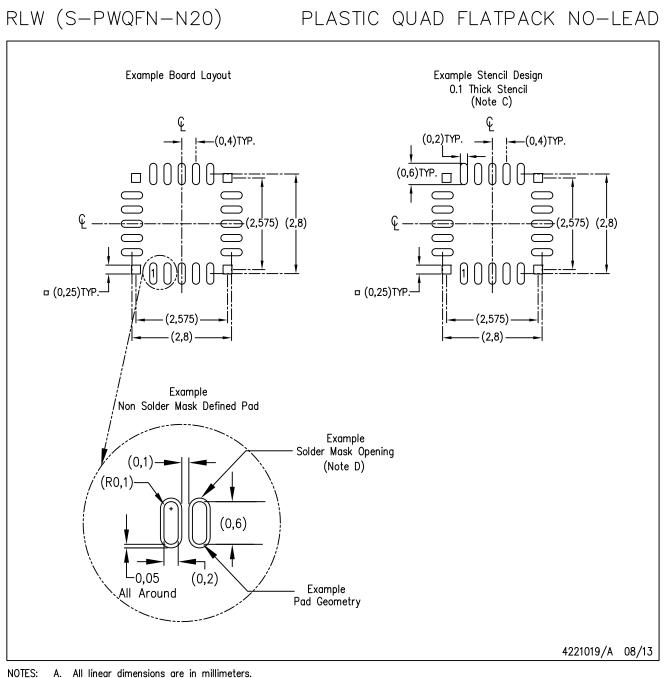

- QFN-20 package, 3mm x 3mm, 0.75mm height

## 2 Applications

- Ultrabook™

- Ultrathin PC

- Notebook PC

- Tablets

- Servers

- All-In-One PC

#### 3 Description

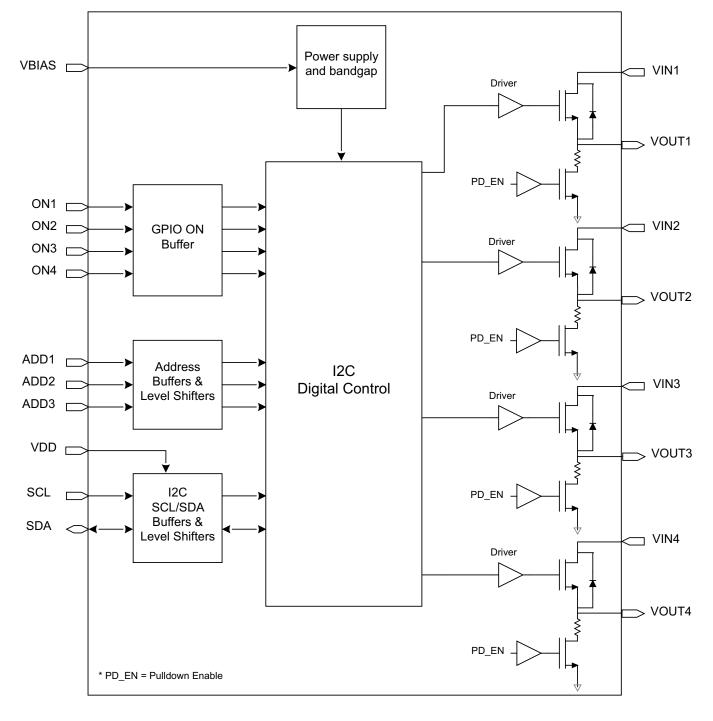

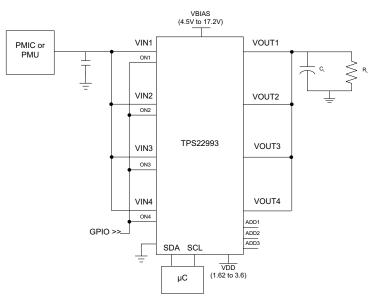

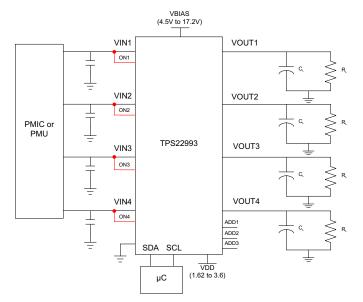

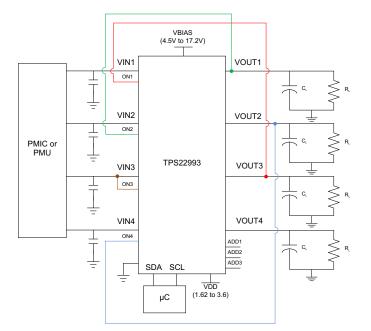

The TPS22993 is a multi-channel, low RON load switch with user programmable features. The device contains four N-channel MOSFETs that can operate over an input voltage range of 1.0V to 3.6V. The switch can be controlled by I<sup>2</sup>C making it ideal for usage with processors that have limited GPIO available. The rise time of the TPS22993 device is internally controlled in order to avoid inrush current. The TPS22993 has five programmable slew rate options, four ON-delay options, and four quick output discharge (QOD) resistance options.

The channels of the device can be controlled via either GPIO or I<sup>2</sup>C. The default mode of operation is GPIO control through the ONx terminals. The I<sup>2</sup>C slave address terminals can be tied high or low to assign seven unique device addresses.

The TPS22993 is available in a space-saving RLW package (0.4mm pitch) and is characterized for operation over the free-air temperature range of -40°C to 85°C.

| Device Information             |           |           |  |  |  |

|--------------------------------|-----------|-----------|--|--|--|

| ORDER NUMBER PACKAGE BODY SIZE |           |           |  |  |  |

| TPS22993PRLWR                  | WQFN (20) | 3mm x 3mm |  |  |  |

## Simplified Schematic

## **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications1                         |

| 3 | Des  | cription1                          |

| 4 | Sim  | plified Schematic1                 |

| 5 | Rev  | ision History2                     |

| 6 | Terr | ninal Configuration and Functions  |

| 7 | Spe  | cifications 4                      |

|   | 7.1  | Recommended Operating Conditions 4 |

|   | 7.2  | Absolute Maximum Ratings 5         |

|   | 7.3  | Handling Ratings 5                 |

|   | 7.4  | Thermal Information5               |

|   | 7.5  | Electrical Characteristics 6       |

|   | 7.6  | Switching Characteristics 8        |

|   | 7.7  | Typical Characteristics9           |

|   |      |                                    |

| 8  | Para | metric Measurement Information    | 14   |

|----|------|-----------------------------------|------|

| 9  | Deta | iled Description                  | 15   |

|    | 9.1  | Block Diagram                     | . 15 |

|    | 9.2  | Register Map                      | . 16 |

| 10 | Арр  | lication and Implementation       | 18   |

|    | 10.1 | Application Information           | . 18 |

|    | 10.2 | Typical Applications              | . 23 |

| 11 | Layo | out                               | 29   |

|    | -    | Board Layout                      |      |

| 12 | Devi | ice and Documentation Support     | 31   |

|    | 12.1 | Trademarks                        | . 31 |

|    | 12.2 | Electrostatic Discharge Caution   | . 31 |

|    | 12.3 | Glossary                          | . 31 |

| 13 | Мес  | hanical, Packaging, and Orderable |      |

|    |      | mation                            | 31   |

## 5 Revision History

| CI | Changes from Original (November 2013) to Revision A |  |   |

|----|-----------------------------------------------------|--|---|

| •  | Revised document to full version.                   |  | 1 |

#### **Device Comparison Table**

| TPS22993                                                    |               |  |  |  |

|-------------------------------------------------------------|---------------|--|--|--|

| R <sub>ON</sub> TYPICAL AT 3.3 V (V <sub>BIAS</sub> = 7.2V) | 15 mΩ         |  |  |  |

| RISE TIME <sup>(1)</sup>                                    | Programmable  |  |  |  |

| ON DELAY <sup>(1)</sup>                                     | Programmable  |  |  |  |

| QUICK OUTPUT DISCHARGE <sup>(1)(2)</sup>                    | Programmable  |  |  |  |

| MAXIMUM OUTPUT CURRENT (per channel)                        | 1.2 A         |  |  |  |

| GPIO ENABLE                                                 | Active High   |  |  |  |

| OPERATING TEMP                                              | –40°C to 85°C |  |  |  |

(1)

See Application Information section. This feature discharges output of the switch to GND through an internal resistor, preventing the output from floating. See Application (2)information section.

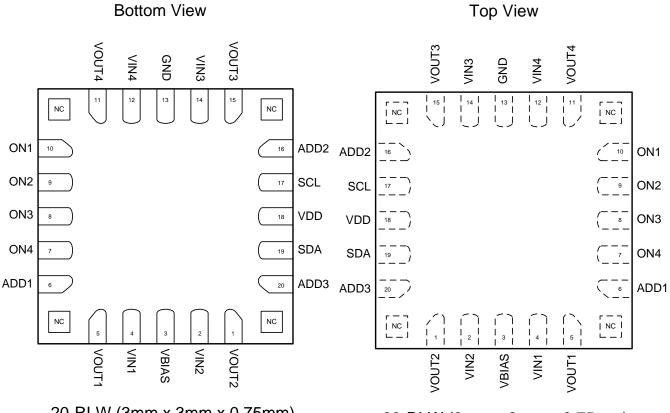

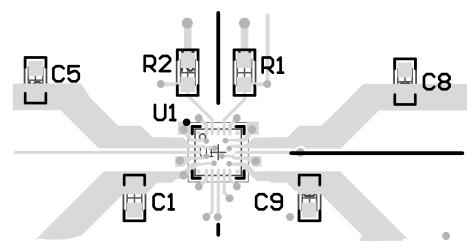

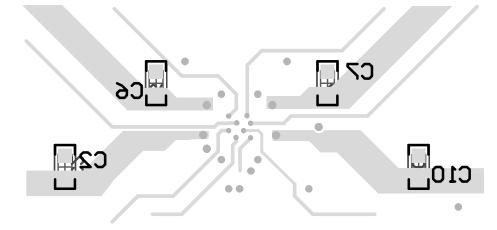

#### **Terminal Configuration and Functions** 6

20-RLW (3mm x 3mm x 0.75mm)

20-RLW (3mm x 3mm x 0.75mm)

www.ti.com

NSTRUMENTS

**EXAS**

#### **Terminal Functions**

| T€  | erminal       | I/O | DESCRIPTION                                                                                                                                |  |  |  |

|-----|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME          | 1/0 | DESCRIPTION                                                                                                                                |  |  |  |

| NC  | NO<br>CONNECT | -   | Attached terminal to PCB. Leave the terminals floating or tie to GND.                                                                      |  |  |  |

| 1   | VOUT2         | 0   | Channel 2 output.                                                                                                                          |  |  |  |

| 2   | VIN2          | I   | Channel 2 input.                                                                                                                           |  |  |  |

| 3   | VBIAS         | I   | Bias voltage. Power supply to the device. Recommended voltage range for this terminal is 5.2V to 14V. See Application Information section. |  |  |  |

| 4   | VIN1          | Ι   | Channel 1 input.                                                                                                                           |  |  |  |

| 5   | VOUT1         | 0   | Channel 1 output.                                                                                                                          |  |  |  |

| 6   | ADD1          | Ι   | Device address terminal. Tie high or low. See Application Information section.                                                             |  |  |  |

| 7   | ON4           | Ι   | Active high channel 4 control input. Do not leave floating.                                                                                |  |  |  |

| 8   | ON3           | Ι   | Active high channel 3 control input. Do not leave floating.                                                                                |  |  |  |

| 9   | ON2           | Ι   | Active high channel 2 control input. Do not leave floating.                                                                                |  |  |  |

| 10  | ON1           | Ι   | Active high channel 1 control input. Do not leave floating.                                                                                |  |  |  |

| 11  | VOUT4         | 0   | Channel 4 output.                                                                                                                          |  |  |  |

| 12  | VIN4          | I   | Channel 4 input.                                                                                                                           |  |  |  |

| 13  | GND           | -   | Device ground.                                                                                                                             |  |  |  |

| 14  | VIN3          | Ι   | Channel 3 input.                                                                                                                           |  |  |  |

| 15  | VOUT3         | 0   | Channel 3 output.                                                                                                                          |  |  |  |

| 16  | ADD2          | Ι   | Device address terminal. Tie high or low. See Application Information section.                                                             |  |  |  |

| 17  | SCL           | Ι   | Serial clock input.                                                                                                                        |  |  |  |

| 18  | VDD           | I   | $I^2C$ device supply input. Tie this terminal to the $I^2C$ SCL/SDA pull-up voltage. See Application Information section.                  |  |  |  |

| 19  | SDA           | I/O | Serial data input/output.                                                                                                                  |  |  |  |

| 20  | ADD3          | Ι   | Device address terminal. Tie high or low. See Application Information section.                                                             |  |  |  |

## 7 Specifications

## 7.1 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                                               | MIN              | MAX              | UNIT |

|-------------------|-----------------------------------------------|------------------|------------------|------|

| V <sub>INx</sub>  | Input voltage for VIN1, VIN2, VIN3, VIN4      | 1.0              | 3.6              | V    |

| V <sub>BIAS</sub> | Supply voltage for VBIAS                      | 4.5              | 17.2             | V    |

| V <sub>DD</sub>   | Supply voltage for VDD                        | 1.62             | 3.6              | V    |

| V <sub>ADDx</sub> | Input voltage for ADD1, ADD2, ADD3            | 0                | 3.6              | V    |

| V <sub>ONx</sub>  | Input voltage for ON1, ON2, ON3, ON4          | 0                | 5                | V    |

| V <sub>OUTx</sub> | Output voltage for VOUT1, VOUT2, VOUT3, VOUT4 | 0                | $V_{\text{INx}}$ | V    |

| C <sub>INx</sub>  | Input capacitor on VIN1, VIN2, VIN3, VIN4     | 1 <sup>(1)</sup> |                  | μF   |

(1) Refer to application section.

## 7.2 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                                              |                                                   | VALUE |     | UNIT <sup>(2)</sup> |

|------------------------------------------------------------------------------|---------------------------------------------------|-------|-----|---------------------|

|                                                                              |                                                   | MIN   | MAX |                     |

| V <sub>INx</sub>                                                             | Input voltage for VIN1, VIN2, VIN3, VIN4          | -0.3  | 4   | V                   |

| V <sub>BIAS</sub>                                                            | Supply voltage for VBIAS                          | -0.3  | 20  | V                   |

| V <sub>OUTx</sub>                                                            | Output voltage for VOUT1, VOUT2, VOUT3, VOUT4     | -0.3  | 4   | V                   |

| V <sub>DD</sub> , V <sub>SCL</sub> ,<br>V <sub>SDA</sub> , V <sub>ADDx</sub> | Input voltage for VDD, SCL, SDA, ADD1, ADD2, ADD3 | -0.3  | 4   | V                   |

| V <sub>ONx</sub>                                                             | Input voltage for ON1, ON2, ON3, ON4              | -0.3  | 6   | V                   |

| I <sub>MAX</sub>                                                             | Maximum continuous switch current per channel     |       | 1.2 | А                   |

| T <sub>A</sub>                                                               | Operating free-air temperature <sup>(3)</sup>     | -40   | 85  | °C                  |

| TJ                                                                           | Maximum junction temperature                      | 125   | 125 | °C                  |

| T <sub>LEAD</sub>                                                            | Maximum lead temperature (10-s soldering time)    |       | 300 | °C                  |

Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground terminal.

(3) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature [TA(max)] is dependent on the maximum operating junction temperature [T<sub>J(max)</sub>], the maximum power dissipation of the device in the application [PD(max)], and the junction-to-ambient thermal resistance of the part/package in the application ( $_{\theta JA}$ ), as given by the following equation: T<sub>A(max)</sub> = T<sub>J(max)</sub> - ( $_{\theta JA} \times P_{D(max)}$ )

## 7.3 Handling Ratings

|                    |                                                                              |                                       | MIN | MAX  | UNIT |

|--------------------|------------------------------------------------------------------------------|---------------------------------------|-----|------|------|

| T <sub>stg</sub>   | torage temperature                                                           |                                       |     | 150  | °C   |

| ESD <sup>(1)</sup> |                                                                              | Human-Body Model (HBM) <sup>(2)</sup> |     | 2000 | V    |

| ESD                | Electrostatic discharge protection Charged-Device Model (CDM) <sup>(3)</sup> |                                       |     | 500  | V    |

(1) Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

(2) Level listed above is the passing level per ANSI/ESDA/JEDEC JS-001. JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(3) Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## 7.4 Thermal Information

|                         | THERMAL METRIC <sup>(1)(2)</sup> Junction-to-ambient thermal resistance         Junction-to-case(top) thermal resistance         Junction-to-board thermal resistance         Junction-to-board thermal resistance         Junction-to-top characterization parameter         Junction-to-board characterization parameter | TPS22993              |      |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|

|                         |                                                                                                                                                                                                                                                                                                                            | RLW<br>(20 TERMINALS) | UNIT |

| Θ <sub>JA</sub>         | Junction-to-ambient thermal resistance                                                                                                                                                                                                                                                                                     | 58                    |      |

| Θ <sub>JC(top)</sub>    | Junction-to-case(top) thermal resistance                                                                                                                                                                                                                                                                                   | 24                    |      |

| $\Theta_{JB}$           | Junction-to-board thermal resistance                                                                                                                                                                                                                                                                                       | 10                    | °C/W |

| $\Psi_{JT}$             | Junction-to-top characterization parameter                                                                                                                                                                                                                                                                                 | 0.7                   | 0/00 |

| $\Psi_{JB}$             | Junction-to-board characterization parameter                                                                                                                                                                                                                                                                               | 10                    |      |

| Θ <sub>JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance                                                                                                                                                                                                                                                                                | N/A                   |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) For thermal estimates of this device based on PCB copper area, see the TI PCB Thermal Calculator.

## 7.5 Electrical Characteristics

The specification applies over the operating ambient temperature  $-40^{\circ}C \le T_A \le 85^{\circ}C$  (Full) (unless otherwise noted). Typical values are for  $T_A = 25^{\circ}C$ .  $V_{BIAS} = 7.2V$  (unless otherwise noted).

|                                              | $\frac{\text{for } T_A = 25^{\circ}\text{C. } V_{\text{BIAS}} = 7.2\text{V}}{\text{PARAMETER}}$ | TEST CONDITION                                                                                            | 6                         | TA       | MIN TYP | MAX | UNIT |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------|----------|---------|-----|------|--|

| POWER SUF                                    | PLIES CURRENTS AND LEAKA                                                                        | GES                                                                                                       |                           |          |         |     |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{BIAS} = 4.5V$         |          | 14.8    | 26  |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{BIAS} = 5.2V$         |          | 14.9    | 26  |      |  |

|                                              | Quiescent current for VBIAS                                                                     | I <sub>OUT1,2,3,4</sub> = 0 A,<br>V <sub>IN1,2,3,4</sub> = 3.6 V,                                         | $V_{BIAS} = 7.2V$         | 1 [      | 16.2    | 28  |      |  |

|                                              | (all four channels)                                                                             | V <sub>ON1,2,3,4</sub> = 3.6 V,                                                                           | $V_{BIAS} = 10.8V$        | Full     | 16.6    | 30  | μA   |  |

|                                              |                                                                                                 | $V_{DD} = 0 V$                                                                                            | V <sub>BIAS</sub> = 12.6V |          | 16.7    | 30  |      |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>BIAS</sub> = 17.2V |          | 16.8    | 30  |      |  |

| Q, VBIAS                                     |                                                                                                 |                                                                                                           | $V_{BIAS} = 4.5V$         |          | 7.7     | 15  |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{BIAS} = 5.2V$         | 1        | 7.8     | 15  |      |  |

|                                              | Quiescent current for VBIAS                                                                     | $I_{OUT1,2,3,4} = 0A,$<br>$V_{IN1} = V_{ON1} = 3.6V,$                                                     | $V_{BIAS} = 7.2V$         | 1 [      | 8.5     | 16  |      |  |

|                                              | (single channel)                                                                                | $V_{IN2,3,4} = V_{ON2,3,4} = 0V,$                                                                         | V <sub>BIAS</sub> = 10.8V | Full     | 8.7     | 16  | μA   |  |

|                                              |                                                                                                 | $V_{DD} = 0V$                                                                                             | V <sub>BIAS</sub> = 12.6V | 1        | 8.8     | 16  |      |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>BIAS</sub> = 17.2V | 1        | 8.9     | 16  |      |  |

| I <sub>Q, VDD</sub><br>I <sub>DYN, VDD</sub> |                                                                                                 | I <sub>OUT1,2,3,4</sub> = 0A,                                                                             | V <sub>DD</sub> = 1.8V    |          | 0.6     | 2   |      |  |

| I <sub>Q, VDD</sub>                          | Quiescent current for VDD                                                                       | $V_{IN1,2,3,4} = V_{ON1,2,3,4} = 3.6V,$<br>$f_{SCL} = 0Hz$                                                | V <sub>DD</sub> = 3.6V    | Full     | 1.2     | 2   | μΑ   |  |

|                                              | Average dynamic current for                                                                     | I <sub>OUT1,2,3,4</sub> = 0A,                                                                             | V <sub>DD</sub> = 1.8V    |          |         | 20  |      |  |

| I <sub>DYN, VDD</sub>                        | VDD during I <sup>2</sup> C communication                                                       | $V_{IN1,2,3,4} = V_{ON1,2,3,4} = 3.6V,$<br>$f_{SCL} = 1MHz$                                               | V <sub>DD</sub> = 3.6V    | Full     |         | 35  | μA   |  |

|                                              | Average dynamic current for                                                                     |                                                                                                           | $V_{BIAS} = 5.2V$         |          |         | 85  |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{BIAS} = 7.2V$         |          |         | 85  |      |  |

|                                              | VBIAS (all four channels)<br>during I <sup>2</sup> C communication                              |                                                                                                           | $V_{BIAS} = 10.8V$        | Full     |         | 85  | μA   |  |

| I <sub>DYN, VBIAS</sub>                      |                                                                                                 |                                                                                                           | $V_{BIAS} = 12.6V$        |          |         | 85  |      |  |

|                                              |                                                                                                 | $\begin{split} &I_{OUT1,2,3,4}=0A,\\ &V_{1N1}=V_{ON1}=3.6V,\\ &V_{1N2,3,4}=V_{ON2,3,4}=0V, \end{split}$   | $V_{BIAS} = 5.2V$         | - Full - |         | 75  | μΑ   |  |

|                                              | Average dynamic current for<br>VBIAS (single channel) during<br>I <sup>2</sup> C communication  |                                                                                                           | $V_{BIAS} = 7.2V$         |          |         | 75  |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{BIAS} = 10.8V$        |          |         | 75  |      |  |

|                                              |                                                                                                 | f <sub>SCL</sub> =1MHz V <sub>BIAS</sub> = 12.6V                                                          |                           |          |         | 75  |      |  |

| I <sub>SD, VBIAS</sub>                       | Shutdown current for VBIAS (all four channels)                                                  | V <sub>ON1,2,3,4</sub> = 0V, V <sub>OUT1,2,3,4</sub> = 0V, V <sub>DD</sub> :<br>V <sub>BIAS</sub> = 17.2V | = 3.6V,                   | Full     | 5.7     | 13  | μΑ   |  |

| I <sub>SD, VDD</sub>                         | Shutdown current for VDD                                                                        | $V_{ON1,2,3,4} = 0V, V_{OUT1,2,3,4} = 0V, V_{DD} = 3.6V$                                                  |                           | Full     | 1.2     | 2   | μA   |  |

|                                              |                                                                                                 |                                                                                                           | $V_{INx} = 3.3V$          |          | 0.009   | 4   |      |  |

|                                              |                                                                                                 | $V_{ONx} = 0V, V_{OUTx} = 0V, V_{DD} = 3.6V$                                                              | V <sub>INx</sub> = 1.8V   | - Full - | 0.006   |     | μΑ   |  |

| I <sub>SD, VINx</sub>                        | Shutdown current for VINx                                                                       |                                                                                                           | V <sub>INx</sub> = 1.5V   |          | 0.006   | 3   |      |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>INx</sub> = 1.05V  |          | 0.006   | 2.5 |      |  |

| I <sub>ONx</sub>                             | Leakage current for ONx                                                                         | V <sub>ONx</sub> = 5V                                                                                     | in the                    | Full     | 0.01    | 0.1 | μA   |  |

| I <sub>ADDx</sub>                            | Leakage current for ADDx                                                                        | V <sub>ADDx</sub> = 3.6V                                                                                  |                           | Full     | 0.01    | 0.2 | μA   |  |

| I <sub>SCL</sub>                             | Leakage current for SCL                                                                         | V <sub>SCL</sub> = 3.6V                                                                                   |                           | Full     | 0.01    |     | μA   |  |

| I <sub>SDA</sub>                             | Leakage current for SDA                                                                         | V <sub>SDA</sub> = 3.6V                                                                                   |                           | Full     | 0.01    | 0.2 | μΑ   |  |

|                                              | E CHARACTERISTICS                                                                               |                                                                                                           |                           |          |         |     |      |  |

|                                              |                                                                                                 |                                                                                                           |                           | 25°C     | 15      | 20  |      |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>IN</sub> = 3.3V    | Full     |         | 22  | mΩ   |  |

|                                              |                                                                                                 |                                                                                                           |                           | 25°C     | 15      | 20  |      |  |

|                                              |                                                                                                 |                                                                                                           | $V_{IN} = 2.5V$           | Full     |         | 22  | mΩ   |  |

|                                              |                                                                                                 |                                                                                                           |                           | 25°C     | 15      |     | mΩ   |  |

| R <sub>ON</sub>                              | On-state resistance                                                                             | $V_{BIAS} = 7.2V, I_{OUT} = -200mA$                                                                       | V <sub>IN</sub> = 1.8V    | Full     |         | 23  |      |  |

|                                              |                                                                                                 |                                                                                                           |                           | 25°C     | 15      |     |      |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>IN</sub> = 1.5V    | Full     | 10      | 20  | mΩ   |  |

|                                              |                                                                                                 |                                                                                                           | V <sub>IN</sub> = 1.05V   | 25°C     | 15      |     |      |  |

|                                              |                                                                                                 |                                                                                                           |                           | 20 0     | 10      | 20  | mΩ   |  |

## **Electrical Characteristics (continued)**

The specification applies over the operating ambient temperature  $-40^{\circ}C \le T_A \le 85^{\circ}C$  (Full) (unless otherwise noted). Typical values are for  $T_A = 25^{\circ}C$ .  $V_{BIAS} = 7.2V$  (unless otherwise noted).

|                                                                                                                                                                                                                              | PARAMETER                                                                 | TEST CONDITIO                                | NS                        | T <sub>A</sub> | MIN                 | ТҮР       | MAX                 | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------|---------------------------|----------------|---------------------|-----------|---------------------|------|

|                                                                                                                                                                                                                              |                                                                           |                                              |                           | 25°C           |                     | 18        | 25                  | 0    |

|                                                                                                                                                                                                                              |                                                                           |                                              | V <sub>IN</sub> = 3.3V    | Full           |                     |           | 28                  | mΩ   |

|                                                                                                                                                                                                                              |                                                                           |                                              | 0.51/                     | 25°C           |                     | 16        | 22                  | 0    |

|                                                                                                                                                                                                                              |                                                                           |                                              | <sub>VIN</sub> = 2.5V     | Full           |                     |           | 24                  | mΩ   |

|                                                                                                                                                                                                                              | 0                                                                         |                                              |                           | 25°C           |                     | 15        | 20                  | 0    |

| V <sub>IH, ADDx</sub><br>V <sub>IL, ADDx</sub><br>V <sub>IL, ONx</sub><br>V <sub>IL, ONx</sub><br>V <sub>IL, ONx</sub><br>I <sup>2</sup> C CHARACT<br>f <sub>SCL</sub> <sup>(1)</sup><br>t <sub>SU, SDA</sub> <sup>(1)</sup> | On-state resistance                                                       | $V_{BIAS} = 5.2V, I_{OUT} = -200mA$          | V <sub>IN</sub> = 1.8V    | Full           |                     |           | 23                  | mΩ   |

|                                                                                                                                                                                                                              |                                                                           |                                              | V 4 EV                    | 25°C           |                     | 15        | 20                  | 0    |

|                                                                                                                                                                                                                              |                                                                           |                                              | V <sub>IN</sub> = 1.5V    | Full           |                     |           | 22                  | mΩ   |

|                                                                                                                                                                                                                              |                                                                           |                                              | V/ 4.05V/                 | 25°C           |                     | 15        | 20                  | 0    |

|                                                                                                                                                                                                                              |                                                                           |                                              | V <sub>IN</sub> = 1.05V   | Full           |                     |           | 22                  | mΩ   |

|                                                                                                                                                                                                                              |                                                                           | $V_{IN} = 3.3V, V_{ON} = 0V, I_{OUT} = 1mA,$ | QOD[1:0] = 00             | 25°C           |                     | 110       |                     |      |

|                                                                                                                                                                                                                              |                                                                           | $V_{IN} = 3.3V, V_{ON} = 0V, I_{OUT} = 1mA,$ | QOD[1:0] = 01             | 25°C           |                     | 483       |                     |      |

| R <sub>PD</sub>                                                                                                                                                                                                              | Output pulldown resistance                                                | $V_{IN} = 3.3V, V_{ON} = 0V, I_{OUT} = 1mA,$ | QOD[1:0] = 10             | 25°C           |                     | 949       |                     | Ω    |

|                                                                                                                                                                                                                              | V <sub>IN</sub> = 3.3V, V <sub>ON</sub> = 0V, I <sub>OUT</sub> = 1mA, QOI |                                              | QOD[1:0] = 11             |                |                     | No<br>QOD |                     |      |

| THRESHOLD                                                                                                                                                                                                                    | CHARACTERISTICS                                                           |                                              |                           |                |                     |           |                     |      |

| V <sub>IH, ADDx</sub>                                                                                                                                                                                                        | High-level input voltage for ADDx                                         |                                              |                           | Full           | 0.7×V <sub>DD</sub> |           | $V_{\text{DD}}$     | V    |

| V <sub>IL, ADDx</sub>                                                                                                                                                                                                        | Low-level input voltage for ADDx                                          |                                              |                           | Full           | 0                   |           | $0.3 \times V_{DD}$ | V    |

| V <sub>IH, ONx</sub>                                                                                                                                                                                                         | High-level input voltage for ONx                                          |                                              |                           | Full           | 1.05                |           | 5                   | V    |

| V <sub>IL, ONx</sub>                                                                                                                                                                                                         | Low-level input voltage for ONx                                           |                                              |                           | Full           | 0                   |           | 0.4                 | V    |

|                                                                                                                                                                                                                              |                                                                           | V <sub>BIAS</sub> = 5.2V                     |                           |                |                     | 130       |                     |      |

| M                                                                                                                                                                                                                            | Livetere eie fen ONia                                                     | V <sub>BIAS</sub> = 7.2V                     |                           | <b>5</b>       |                     | 130       |                     |      |

| V <sub>HYS</sub> , ONx                                                                                                                                                                                                       | Hysteresis for ONx                                                        | V <sub>BIAS</sub> = 10.8V                    | Full                      |                | 130                 |           | mV                  |      |

|                                                                                                                                                                                                                              |                                                                           | V <sub>BIAS</sub> = 12.6V                    | / <sub>BIAS</sub> = 12.6V |                |                     | 130       |                     |      |

| I <sup>2</sup> C CHARAC                                                                                                                                                                                                      | TERISTICS                                                                 |                                              |                           |                |                     |           |                     |      |

| f <sub>SCL</sub> <sup>(1)</sup>                                                                                                                                                                                              | Clock frequency                                                           |                                              |                           | Full           |                     |           | 1                   | MHz  |

|                                                                                                                                                                                                                              | Setup time for SDA                                                        | f <sub>SCL</sub> = 1MHz (fast mode plus)     |                           | Full           | 50                  |           |                     | ns   |

| t <sub>HD, SDA</sub> <sup>(1)</sup>                                                                                                                                                                                          | Hold time for SDA                                                         |                                              |                           | Full           | 0                   |           |                     | ns   |

| IOL, SDA                                                                                                                                                                                                                     | SDA output low current                                                    | $V_{OL,SDA} = 0.4V$                          |                           | 25°C           |                     | 8         |                     | mA   |

| VIH, SDA                                                                                                                                                                                                                     | High-level input voltage for SDA                                          |                                              |                           | Full           | 0.7×V <sub>DD</sub> |           | V <sub>DD</sub>     | V    |

| V <sub>IH, SCL</sub>                                                                                                                                                                                                         | High-level input voltage for SCL                                          |                                              |                           | Full           | 0.7×V <sub>DD</sub> |           | $V_{DD}$            | V    |

| V <sub>IL, SDA</sub>                                                                                                                                                                                                         | Low-level input voltage for SDA                                           |                                              |                           | Full           | 0                   |           | $0.3 \times V_{DD}$ | V    |

|                                                                                                                                                                                                                              | Low-level input voltage for                                               |                                              |                           | Full           | 0                   |           | 0.3×V <sub>DD</sub> | V    |

(1) Parameter verified by design.

www.ti.com

## 7.6 Switching Characteristics

Values below are typical values at  $T_A = 25^{\circ}C$ .  $V_{BIAS} = 7.2V$  (unless otherwise noted).

|                  | DADAMETED           | TEST CONDITION                                                                          |                        |      | VIN V | OLTAGE |       | LINUT    |

|------------------|---------------------|-----------------------------------------------------------------------------------------|------------------------|------|-------|--------|-------|----------|

|                  | PARAMETER           | TEST CONDITION                                                                          |                        | 3.3V | 1.8V  | 1.5V   | 1.05V | UNIT     |

|                  |                     |                                                                                         | Slew rate[4:2] = 000   | 11   | 11    | 11     | 11    |          |

|                  |                     | $V_{BIAS} = 7.2V,$                                                                      | Slew rate[4:2] = 001   | 247  | 181   | 167    | 146   |          |

| t <sub>ON</sub>  | VOUTx turn-on time  | $R_L=10\Omega, C_L=0.1\mu F,$<br>QOD[1:0] = 10,                                         | Slew rate[4:2] = 010   | 416  | 302   | 279    | 243   | μs       |

|                  |                     | ON-delay[6:5] = 00                                                                      | Slew rate[4:2] = 011   | 761  | 549   | 505    | 438   |          |

|                  |                     |                                                                                         | Slew rate[4:2] = 100   | 1481 | 1066  | 980    | 848   |          |

| t <sub>OFF</sub> | VOUTx turn-off time | V <sub>BIAS</sub> = 7.2V, R <sub>L</sub> =10Ω, C <sub>L</sub> =0.1µF, QOD[1:0] =        | 10, ON-delay[6:5] = 00 | 2    | 2     | 2      | 2     | μs       |

|                  |                     |                                                                                         | Slew rate[4:2] = 000   | 2    | 1.1   | 1      | 0.8   |          |

|                  |                     |                                                                                         | Slew rate[4:2] = 001   | 307  | 203   | 180    | 147   | μs       |

| t <sub>R</sub>   | VOUTx rise time     | $V_{BIAS} = 7.2V, R_{L}=10\Omega, C_{L}=0.1\mu F,$<br>QOD[1:0] = 10, ON-delay[6:5] = 00 | Slew rate[4:2] = 010   | 527  | 346   | 307    | 248   |          |

|                  |                     | QOD[1.0] = 10, ON-delay[0.0] = 00                                                       | Slew rate[4:2] = 011   | 970  | 638   | 566    | 459   |          |

|                  |                     |                                                                                         | Slew rate[4:2] = 100   | 1898 | 1245  | 1105   | 888   |          |

| t <sub>F</sub>   | VOUTx fall time     | V <sub>BIAS</sub> = 7.2V, R <sub>L</sub> =10Ω, C <sub>L</sub> =0.1µF, QOD[1:0] =        | 10, ON-delay[6:5] = 00 | 2    | 2     | 2      | 2     | μs       |

|                  |                     |                                                                                         | ON delay[4:2] = 00     | 11   | 11    | 11     | 11    |          |

|                  |                     | $V_{BIAS} = 7.2V, R_{I} = 10\Omega, C_{I} = 0.1 \mu F,$                                 | ON delay[4:2] = 01     | 102  | 104   | 105    | 106   | µs<br>µs |

| t <sub>D</sub>   | VOUTx ON delay time | QOD[1:0] = 10, Slew rate[6:5] = 000                                                     | ON delay[4:2] = 10     | 324  | 332   | 334    | 338   |          |

|                  |                     |                                                                                         | ON delay[4:2] = 11     | 923  | 946   | 953    | 965   | 1        |

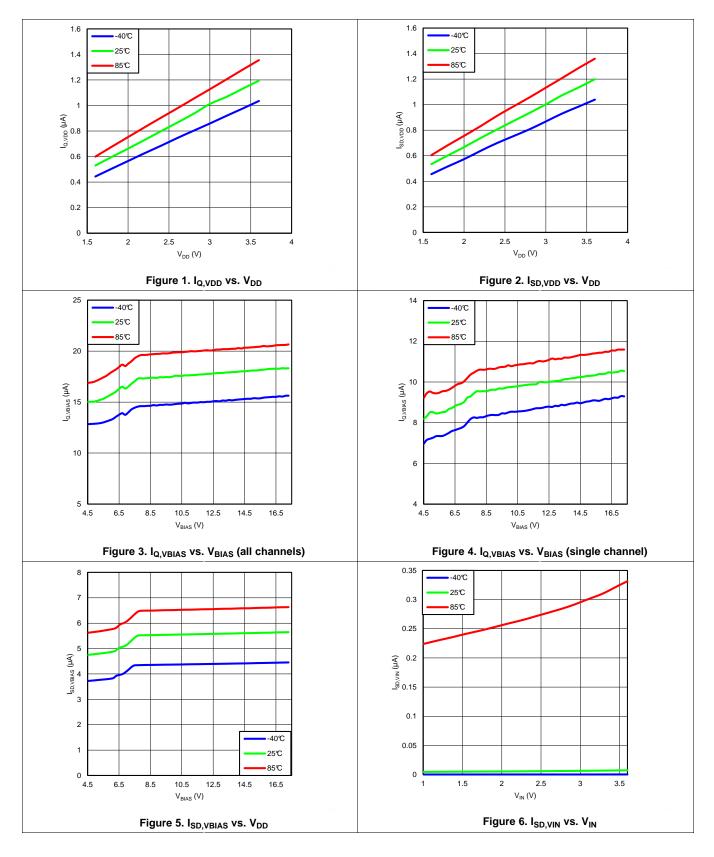

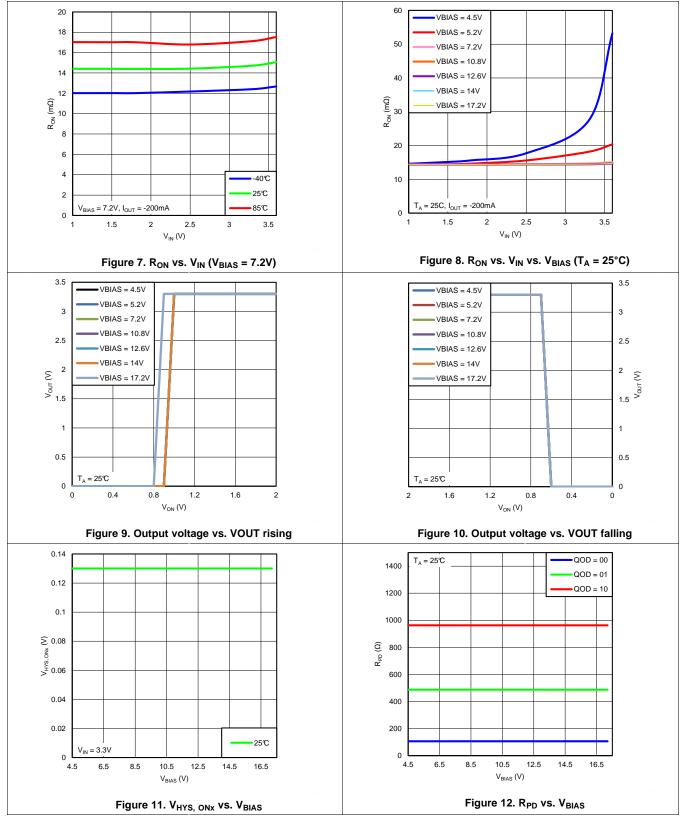

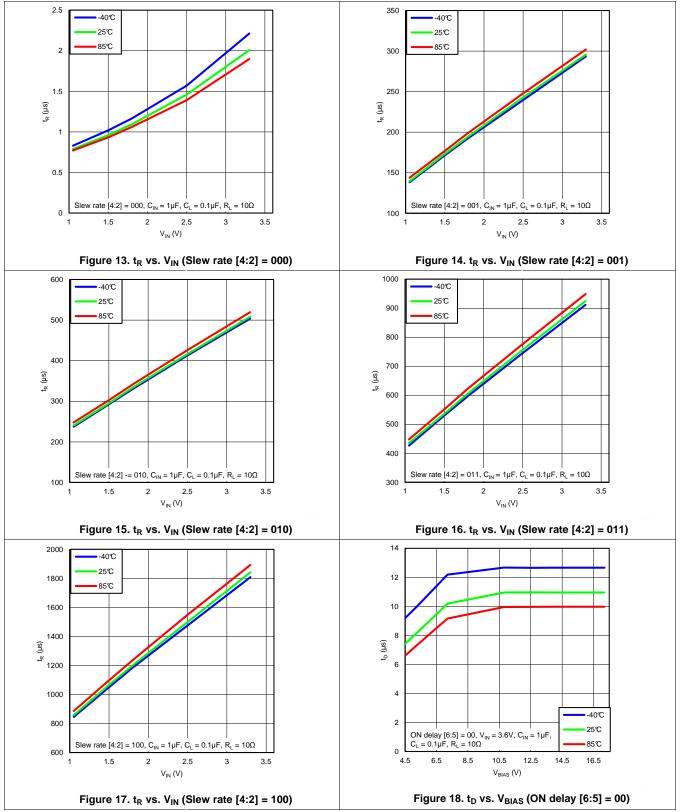

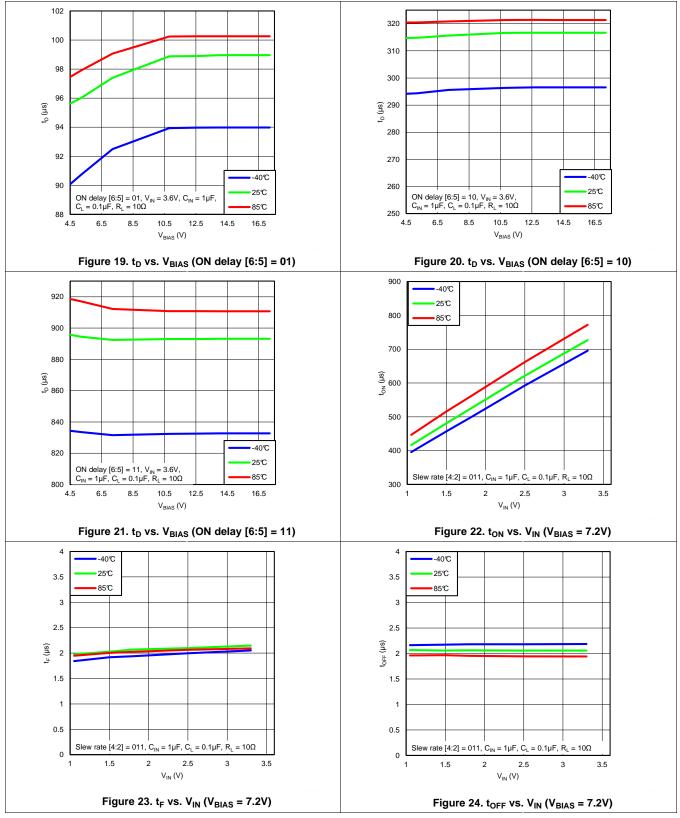

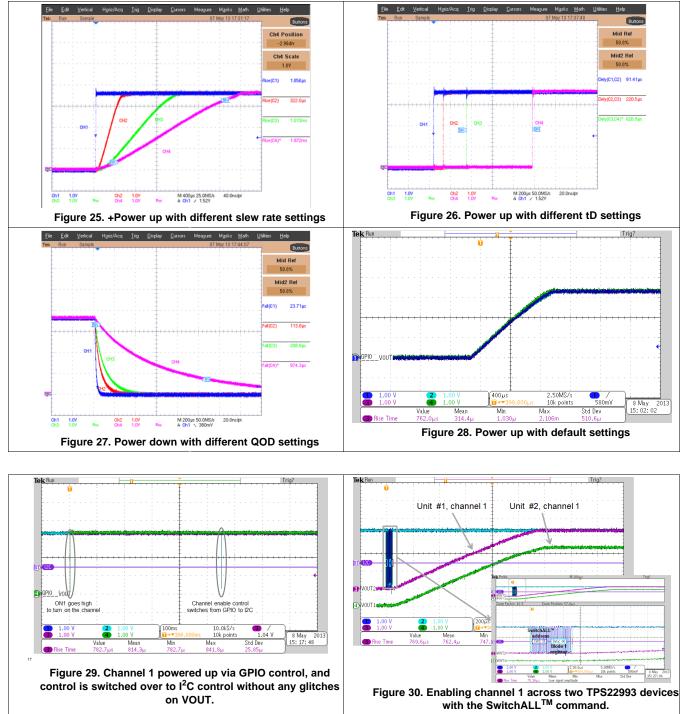

## 7.7 Typical Characteristics

www.ti.com

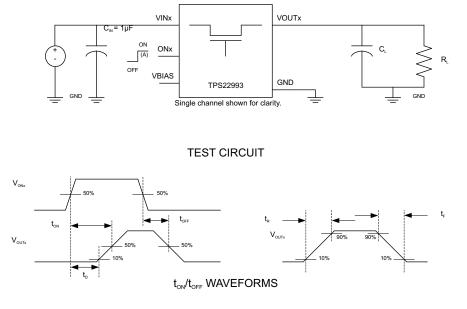

## 8 Parametric Measurement Information

(A) Rise and fall times of the control signal is 100ns.

(B) All switching measurements are done using GPIO control only.

Figure 31. Test Circuit and  $t_{ON}/t_{OFF}$  Waveforms

## 9 Detailed Description

## 9.1 Block Diagram

## 9.2 Register Map

#### Configuration registers (default register values shown below)

Channel 1 configuration register (Address: **01h**)

| BIT         | B7 | B6   | B5   | B4 | B3        | B2 | B1 | B0                        |  |

|-------------|----|------|------|----|-----------|----|----|---------------------------|--|

| DESCRIPTION | х  | ON-D | ELAY |    | SLEW RATE |    |    | QUICK OUTPUT<br>DISCHARGE |  |

| DEFAULT     | Х  | 0    | 0    | 0  | 1         | 1  | 1  | 0                         |  |

#### Channel 2 configuration register (Address: 02h)

| BIT         | B7 | B6       | B5 | B4        | B3 | B2 | B1                        | B0 |

|-------------|----|----------|----|-----------|----|----|---------------------------|----|

| DESCRIPTION | x  | ON-DELAY |    | SLEW RATE |    |    | QUICK OUTPUT<br>DISCHARGE |    |

| DEFAULT     | Х  | 0        | 0  | 0 1 1     |    |    | 1                         | 0  |

#### Channel 3 configuration register (Address: 03h)

| BIT         | B7 | B6   | B5   | B4    | B3        | B2 | B1               | B0 |

|-------------|----|------|------|-------|-----------|----|------------------|----|

| DESCRIPTION | х  | ON-D | ELAY |       | SLEW RATE |    | QUICK (<br>DISCH |    |

| DEFAULT     | Х  | 0    | 0    | 0 1 1 |           |    | 1                | 0  |

#### Channel 4 configuration register (Address: 04h)

| BIT         | B7 | B6   | B5   | B4 | B3        | B2 | B1               | В0              |

|-------------|----|------|------|----|-----------|----|------------------|-----------------|

| DESCRIPTION | х  | ON-D | ELAY |    | SLEW RATE |    | QUICK (<br>DISCH | OUTPUT<br>IARGE |

| DEFAULT     | Х  | 0    | 0    | 0  | 1         | 1  | 1                | 0               |

#### Control register (default register values shown below)

Control register (Address: 05h)

| BIT         | B7                            | B6                       | B5                       | B4                            | B3        | B2        | B1        | B0        |

|-------------|-------------------------------|--------------------------|--------------------------|-------------------------------|-----------|-----------|-----------|-----------|

| DESCRIPTION | GPIO/I <sup>2</sup> C ch<br>4 | GPIO/I <sup>2</sup> C ch | GPIO/I <sup>2</sup> C ch | GPIO/I <sup>2</sup> C ch<br>1 | ENABLE CH | ENABLE CH | ENABLE CH | ENABLE CH |

| DEFAULT     | 0                             | 0                        | 0                        | 0                             | 0         | 0         | 0         | 0         |

#### Mode registers (default register values shown below)

Mode1 (Address: 06h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | x  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

Mode2 (Address: 07h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | x  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode3 (Address: 08h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

## Texas Instruments

www.ti.com

Mode4 (Address: 09h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | B0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

Mode5 (Address: **0Ah**)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | B0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode6 (Address: **0Bh**)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | B0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode7 (Address: 0Ch)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode8 (Address: 0Dh)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | B0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode9 (Address: **0Eh**)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode10 (Address: 0Fh)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode11 (Address: 10h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

#### Mode12 (Address: 11h)

| BIT         | B7 | B6 | B5 | B4 | B3             | B2             | B1             | В0             |

|-------------|----|----|----|----|----------------|----------------|----------------|----------------|

| DESCRIPTION | х  | х  | х  | х  | ENABLE CH<br>4 | ENABLE CH<br>3 | ENABLE CH<br>2 | ENABLE CH<br>1 |

| DEFAULT     | Х  | Х  | Х  | Х  | 0              | 0              | 0              | 0              |

## **10** Application and Implementation

### **10.1** Application Information

#### 10.1.1 I<sup>2</sup>C Control

When power is applied to VBIAS, the device comes up in its default mode of GPIO operation where the channel outputs can be controlled solely via the ON terminals. At any time, if SDA and SCL are present and valid, the device can be configured to be controlled via I<sup>2</sup>C (if in GPIO control) or GPIO (if in I<sup>2</sup>C control).

The control register (address **05h**) can be configured for GPIO or I<sup>2</sup>C enable on a per channel basis.

#### 10.1.1.1 Operating Frequency

The TPS22993 is designed to be compatible with fast-mode plus and operate up to 1MHz clock frequency for bus communication. The device is also compatible with standard-mode (100kHz) and fast-mode (400kHz). This device can reside on the same bus as high-speed mode (3.4MHz) devices, but the device is not designed to respond to I<sup>2</sup>C commands for frequencies greater than 1MHz. See table below for characteristics of the fast-mode plus, fast-mode, and standard-mode bus speeds.

|                       | PARAMETER                                                                  | STANE<br>MOI<br>I <sup>2</sup> C E | DE   | FAST MC<br>I <sup>2</sup> C BU |     | FAST MC<br>PLUS (FI<br>I <sup>2</sup> C BU | M+)  | UNIT |

|-----------------------|----------------------------------------------------------------------------|------------------------------------|------|--------------------------------|-----|--------------------------------------------|------|------|

|                       |                                                                            | MIN                                | MAX  | MIN                            | MAX | MIN                                        | MAX  |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                                           | 0                                  | 100  | 0                              | 400 | 0                                          | 1000 | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time                                           | 4                                  |      | 0.6                            |     | 0.26                                       |      | μs   |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time                                            | 4.7                                |      | 1.3                            |     | 0.5                                        |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                                                |                                    | 50   |                                | 50  |                                            | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial data setup time                                    | 250                                |      | 100                            |     | 50                                         |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial data hold time                                     | 0                                  |      | 0                              |     | 0                                          |      | ns   |

| t <sub>icr</sub>      | I2C input rise time                                                        |                                    | 1000 | 20                             | 300 |                                            | 120  | ns   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between Stop and Start                      | 4.7                                |      | 1.3                            |     | 0.5                                        |      | μs   |

| t <sub>sts</sub>      | I <sup>2</sup> C Start or repeater Start condition setup time              | 4.7                                |      | 0.6                            |     | 0.26                                       |      | μs   |

| t <sub>sth</sub>      | I <sup>2</sup> C Start or repeater Start condition hold time               | 4                                  |      | 0.6                            |     | 0.26                                       |      | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C Stop condition setup time                                 | 4                                  |      | 0.6                            |     | 0.26                                       |      | μs   |

| t <sub>vd(data)</sub> | Valid data time; SCL low to SDA output valid                               |                                    | 3.45 | 0.3                            | 0.9 |                                            | 0.45 | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition; ACK signal from SCL low to SDA (out) low |                                    | 3.45 | 0.3                            | 0.9 |                                            | 0.45 | μs   |

#### Table 1. I<sup>2</sup>C Interface Timing Requirements<sup>(1)</sup>

(1) over operating free-air temperature range (unless otherwise noted)

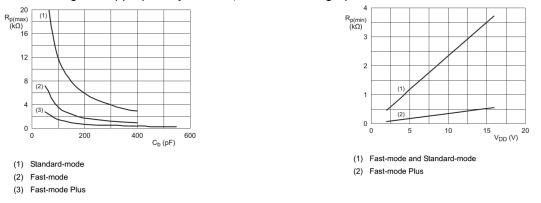

#### 10.1.1.2 SDA/SCL Terminal Configuration

The SDA and SCL terminals of the device operate use an open-drain configuration, and therefore, need pull up resistors to communicate on the  $l^2$ C bus. The graph below shows recommended values for max pullup resistors (R<sub>P</sub>) and bus capacitances (C<sub>b</sub>) to ensure proper bus communications. The SDA and SCL terminals should be pulled up to VDD through an appropriately sized R<sub>P</sub> based on the graphs below.

#### 10.1.1.3 Address (ADDx) Terminal Configuration

The TPS22993 can be configured with an unique I<sup>2</sup>C slave addresses by using the ADDx terminals. There are 3 ADDx terminals that can be tied high to VDD or low to GND (independent of each other) to get up to 7 different slave addresses. The ADDx terminals should be tied to GND if the I<sup>2</sup>C functionality of the device is not to be used. External pull-up resistors for the ADDx are optional as the ADDx inputs are high impedance. The following table shows the ADDx terminal tie-offs with their associated slave addresses (assuming an eight bit word, where the LSB is the read/write bit and the device address bits are the 7 MSB bits) :

| Hex Address | ADD3 | ADD2                                     | ADD1 |

|-------------|------|------------------------------------------|------|

| E0/E1       | GND  | GND                                      | GND  |

| E2/E3       | GND  | GND                                      | VDD  |

| E4/E5       | GND  | VDD                                      | GND  |

| E6/E7       | GND  | VDD                                      | VDD  |

| E8/E9       | VDD  | GND                                      | GND  |

| EA/EB       | VDD  | GND                                      | VDD  |

| EC/ED       | VDD  | VDD                                      | GND  |

| EE          |      | d unique device ad<br>s is the SwitchALL |      |

#### 10.1.2 GPIO Control

There are four ON terminals to enable/disable the four channels. Each ON terminal controls the state of the switch by default upon power up. Asserting ON high enables the switch. ON is active high and has a low threshold, making it capable of interfacing with low-voltage signals. The ON terminal is compatible with standard GPIO logic threshold. It can be used with any microcontroller with 1.2V or higher voltage GPIO.

#### 10.1.3 On-Delay Control

Using the I<sup>2</sup>C interface, the configuration register for each channel can be set for different ON delays for power sequencing. The options for delay are as follows:

- $00 = 11 \mu s$  delay (default register value)

- 01 = 105µs delay

- 10 = 330µs delay

- 11 = 950µs delay

#### 10.1.4 Slew Rate Control

Using the I<sup>2</sup>C interface, the configuration register for each channel can be set for different slew rates for inrush current control and power sequencing. The options for slew rate are as follows:

$000 = 1\mu s/V$   $001 = 150\mu s/V$   $010 = 250\mu s/V$   $011 = 460\mu s/V$  (default register value)  $100 = 890\mu s/V$  101 = invalid slew rate 110 = invalid slew rate111 = reserved

#### 10.1.5 Quick Output Discharge (QOD) Control

Using the I<sup>2</sup>C interface, the configuration register for each channel can be set for different output discharge resistors. The options for QOD are as follows:

00 = 110Ω 01 = 490Ω10 = 951Ω (default register value)

11 = No QOD (high impedance)

#### 10.1.6 Mode Registers

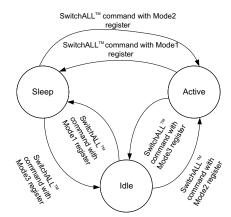

Using the I<sup>2</sup>C interface, the mode registers can be programmed to the desired on/off status for each channel. The contents of these registers are copied over to the control registers when a SwitchALL<sup>™</sup> command is issued, allowing all channels of the device to transition to their desired output states synchronously. See the I<sup>2</sup>C Protocol section and the Application Scenario section for more information on how to use the mode registers in conjunction with the SwitchALL<sup>™</sup> command.

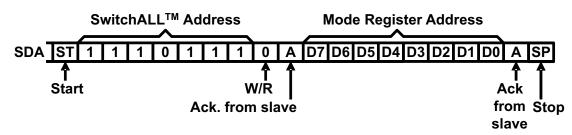

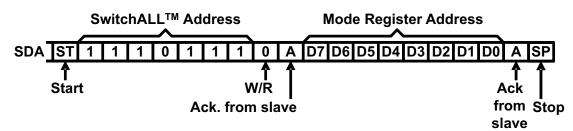

#### **10.1.7** SwitchALL<sup>™</sup> Command

I<sup>2</sup>C controlled channels can respond to a common slave address. This feature allows multiple load switches on the same I<sup>2</sup>C bus to respond simultaneously. The SwitchALL<sup>™</sup> address is **EEh**. During a SwitchALL<sup>™</sup> command, the lower four bits (bits 0 through 3) of the mode register is copied to the lower four bits (bits 0 through 3) of the control register. The mode register to be invoked is referenced in the body of the SwitchALL<sup>™</sup> command. The structure of the SwitchALL<sup>™</sup> command is as follows (as shown in Figure 32): <start><SwitchALL<sup>™</sup> addr><mode addr><stop>. See the I<sup>2</sup>C Protocol section and the Application Scenario section for more information on how to use the SwitchALL<sup>™</sup> command in conjunction with the mode registers.

#

Figure 32. Composition of SwitchALL™ Command

#### 10.1.8 V<sub>DD</sub> Supply For I<sup>2</sup>C Operation

The SDA and SCL terminals of the device must be pulled up to the VDD voltage of the device for proper I<sup>2</sup>C bus communication.

www.ti.com

#### 10.1.9 Input Capacitor (Optional)

To limit the voltage drop on the input supply caused by transient in-rush currents when the switch turns on into a discharged load capacitor or short-circuit, a capacitor needs to be placed between  $V_{IN}$  and GND. A 1- $\mu$ F ceramic capacitor,  $C_{IN}$ , placed close to the terminals, is usually sufficient. Higher values of  $C_{IN}$  can be used to further reduce the voltage drop during high-current application. When switching heavy loads, it is recommended to have an input capacitor about 10 times higher than the output capacitor to avoid excessive voltage drop. For the fastest slew rate setting of the device, a CIN to CL ratio of at least 100 to 1 is recommended to avoid excessive voltage drop.

#### 10.1.10 Output Capacitor (Optional)

Due to the integrated body diode of the NMOS switch, a  $C_{IN}$  greater than  $C_L$  is highly recommended. A  $C_L$  greater than  $C_{IN}$  can cause  $V_{OUT}$  to exceed  $V_{IN}$  when the system supply is removed. This could result in current flow through the body diode from  $V_{OUT}$  to  $V_{IN}$ . A  $C_{IN}$  to  $C_L$  ratio of at least 10 to 1 is recommended for minimizing  $V_{IN}$  dip caused by inrush currents during startup. For the fastest slew rate setting of the device, a CIN to CL ratio of at least 100 to 1 is recommended to minimize  $V_{IN}$  dip caused by inrush currents during startup.

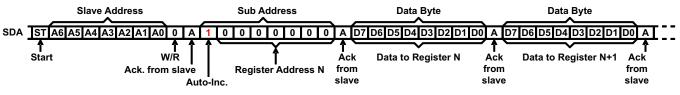

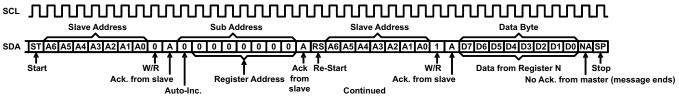

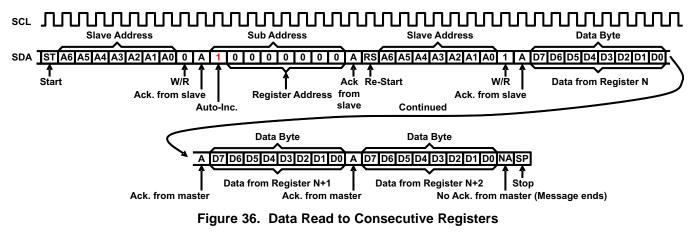

#### 10.1.11 I<sup>2</sup>C Protocol

The following section will cover the standard I<sup>2</sup>C protocol used in the TPS22993. In the I<sup>2</sup>C protocol, the following basic blocks are present in every command (except for the SwitchALL<sup>TM</sup> command):

- Start/stop bit marks the beginning and end of each command.

- Slave address the unique address of the slave device.

- Sub address this includes the register address and the auto-increment bit.

- Data byte data being written to the register. Eight bits must always be transferred even if a single bit is being written or read.

- Auto-increment bit setting this bit to '1' turns on the auto-increment functionality; setting this bit to '0' turns

off the auto-increment functionality.

- Write/read bit this bit signifies if the command being sent will result in reading from a register or writing to a register. Setting this bit to '0' signifies a write, and setting this bit to '1' signifies a read.

- Acknowledge bit this bit signifies if the master or slave has received the preceding data byte.

#### 10.1.11.1 Start and Stop Bit

In the I<sup>2</sup>C protocol, all commands contain a START bit and a STOP bit. A START bit, defined by high to low transition on the SDA line while SCL is high, marks the beginning of a command. A STOP bit, defined by low to high transition on the SDA line while SCL is high, marks the end of a command. The START and STOP bits are generated by the master device on the I<sup>2</sup>C bus. The START bit indicates to other devices that the bus is busy, and some time after the STOP bit the bus is assumed to be free.

#### 10.1.11.2 Auto-increment Bit

The auto-increment feature in the  $I^2C$  protocol allows users to read from and write to consecutive registers in fewer clock cycles. Since the register addresses are consecutive, this eliminates the need to resend the register address. The  $I^2C$  core of the device automatically increments the register address pointer by one when the auto-increment bit is set to '1'. When this bit is set to '0', the auto-increment functionality is disabled.

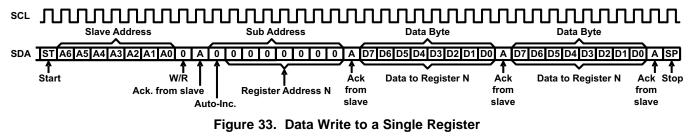

#### 10.1.11.3 Write Command

During the write command, the write/read bit is set to '0', signifying that the register in question will be written to. Figure 33 the composition of the write protocol to a *single* register:

Number of clock cycles for single register write: 29

If multiple consecutive registers must be written to, a short-hand version of the write command can be used. Using the auto-increment functionality of  $I^2C$ , the device will increment the register address after each byte. Figure 34 shows the composition of the write protocol to multiple *consecutive* registers:

#