TPS1685x 9V–80V, 3.5mΩ, 20A Stackable Integrated Hotswap (eFuse) With Accurate and Fast Current Monitor

# 1 Features

- Input operating voltage range: 9V to 80V

- 92V absolute maximum

- Withstands negative voltages up to –5V at output

- Integrated FET with low on-resistance: R<sub>ON</sub> = 3.5mΩ (typ)

- Active high enable input with adjustable undervoltage lockout (UVLO)

- Adjustable overvoltage protection

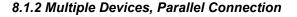

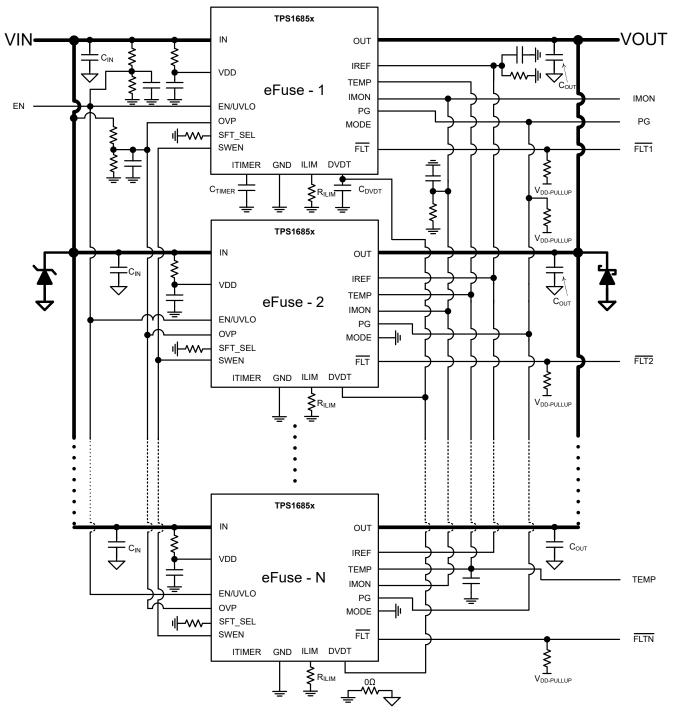

- Supports parallel connection of multiple eFuses with device state synchronization and current sharing

- Adjustable output slew rate control (dVdt) for inrush current protection

- Precise load current monitoring

- <3% error for over 50-100% of max current</p>

- 1MHz bandwidth

- Robust overcurrent protection

- Circuit-breaker response

- Adjustable threshold: 2A to 20A

- Overcurrent protection accuracy: ±3%

- Adjustable transient overcurrent timer (ITIMER) to support peak currents

- Fast-trip response to short-circuit events

- Overtemperature protection (OTP) with analog die temperature monitor output (TEMP)

- FET SOA: 0.7W√s

- FET health monitoring and reporting

- Fault indication pin (FLT)

- Power Good indication pin (PGOOD)

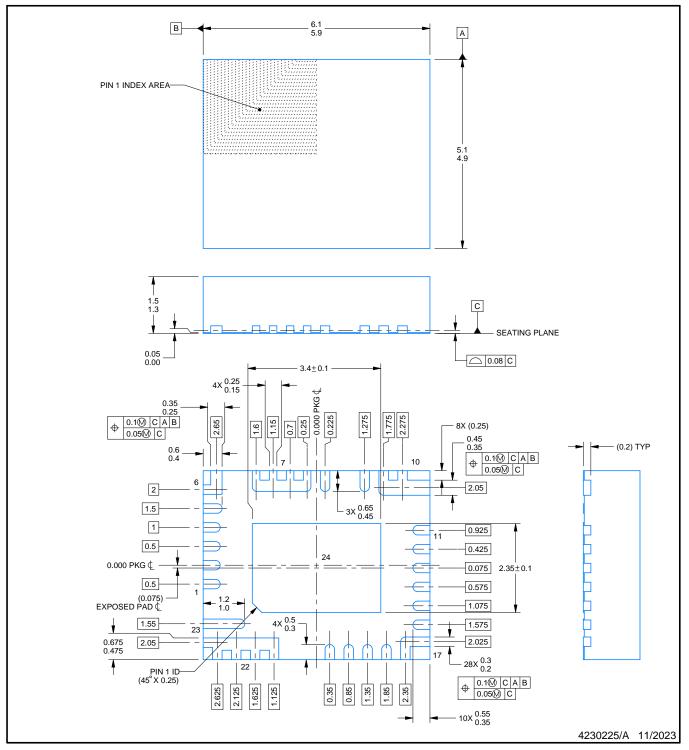

- Small footprint: QFN 6mm × 5mm

- IPC9592B clearance for 60V

# **2** Applications

- Input hotswap and hotplug

- Server and high performance computing

- Network interface cards

- Graphics and hardware accelerator cards

- Data center switches and routers

- Fire alarm control panel

# **3 Description**

The TPS1685x is an integrated high current circuit protection and power management device. The device provides multiple protection modes using very few external components and is a robust defense against overloads, short-circuits and excessive inrush current. Applications with particular inrush current requirements can set the output slew rate with a single external capacitor. Output current limit level can be set by user as per system needs. A user adjustable overcurrent blanking timer allows systems to support transient peaks in the load current without tripping the eFuse. An integrated fast and accurate sense analog load current monitor facilitates predictive maintenance and advanced dynamic platform power management such as Intel® PSYS and PROCHOT# to optimize server and datacenter performance.

Multiple TPS1685x devices can be connected in parallel to increase the total current capacity for high power systems. All devices actively synchronize the operating state and share current during start-up as well as steady state to avoid over-stressing some of the devices which can result in premature or partial shutdown of the parallel chain.

The devices are characterized for operation over a junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

| 1 9                                                            | T ackage information   |                             |  |  |  |  |  |

|----------------------------------------------------------------|------------------------|-----------------------------|--|--|--|--|--|

| PART NUMBER                                                    | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |  |  |  |  |  |

| TPS16850VMAR<br>TPS16851VMAR<br>TPS16850AVMAR<br>TPS16851AVMAR | VMA (LQFN, 23)         | 6.00mm × 5.00mm             |  |  |  |  |  |

Package Information

(1) For all available packages, see Section 11.

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

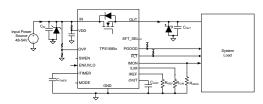

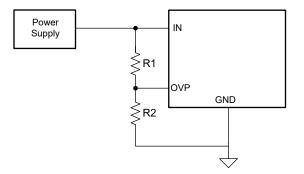

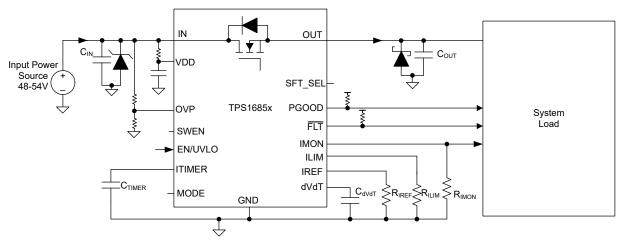

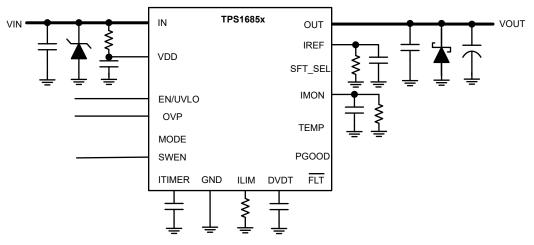

### **Simplified Schematic**

# **Table of Contents**

| 1 Features1                          |

|--------------------------------------|

| 2 Applications1                      |

| 3 Description1                       |

| 4 Device Comparison Table2           |

| 5 Pin Configuration and Functions    |

| 6 Specifications                     |

| 6.1 Absolute Maximum Ratings5        |

| 6.2 ESD Ratings5                     |

| 6.3 Recommended Operating Conditions |

| 6.4 Thermal Information6             |

| 6.5 Electrical Characteristics7      |

| 6.6 Logic Interface 10               |

| 6.7 Timing Requirements10            |

| 6.8 Switching Characteristics        |

| 6.9 Typical Characteristics12        |

| 7 Detailed Description               |

| 7.1 Overview                         |

| 7.2 Functional Block Diagram17       |

| 7.3 Feature Description                             | .18  |

|-----------------------------------------------------|------|

| 7.4 Device Functional Modes                         | .36  |

| 8 Application and Implementation                    | . 37 |

| 8.1 Application Information                         | 37   |

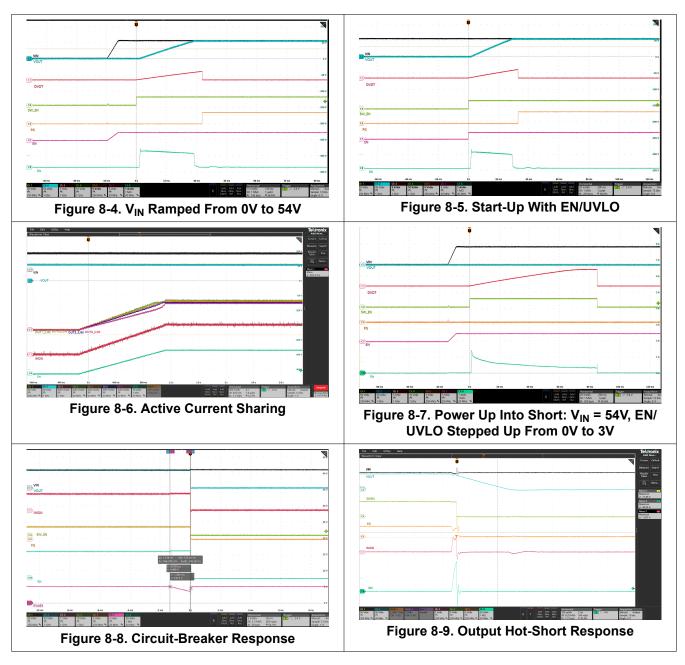

| 8.2 Typical Application: 54V Power Path Protection  |      |

| in Data Center Servers                              | .41  |

| 8.3 Power Supply Recommendations                    | .45  |

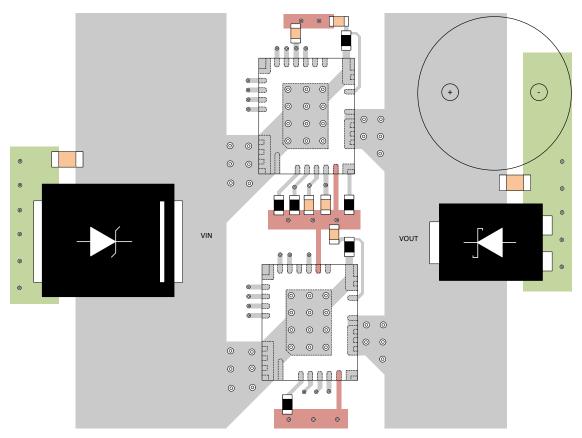

| 8.4 Layout                                          | .47  |

| 9 Device and Documentation Support                  | .49  |

| 9.1 Documentation Support                           | . 49 |

| 9.2 Receiving Notification of Documentation Updates |      |

| 9.3 Support Resources                               | . 49 |

| 9.4 Trademarks                                      | .49  |

| 9.5 Electrostatic Discharge Caution                 | .49  |

| 9.6 Glossary                                        | .49  |

| 10 Revision History                                 | . 49 |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 50 |

|                                                     |      |

# 4 Device Comparison Table

| PART NUMBER |            | Fixed Fast Trip<br>Threshold (FFT) |

|-------------|------------|------------------------------------|

| TPS16850    | Auto-retry | 73A                                |

| TPS16851    | Latch-off  | 73A                                |

| TPS16850A   | Auto-retry | 83A                                |

| TPS16851A   | Latch-off  | 83A                                |

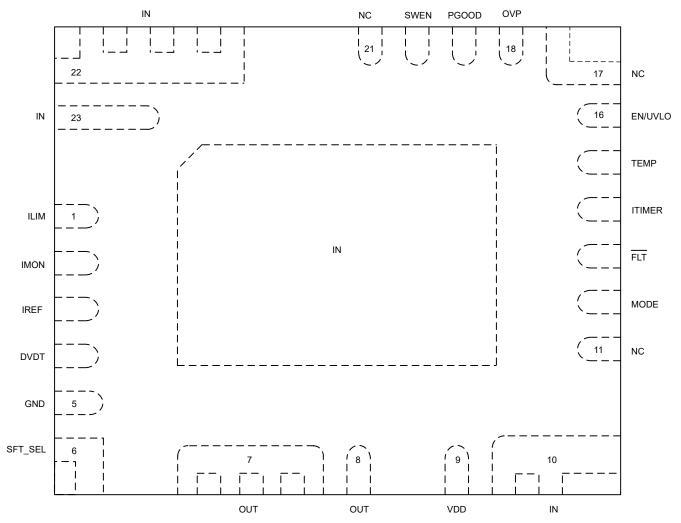

# **5** Pin Configuration and Functions

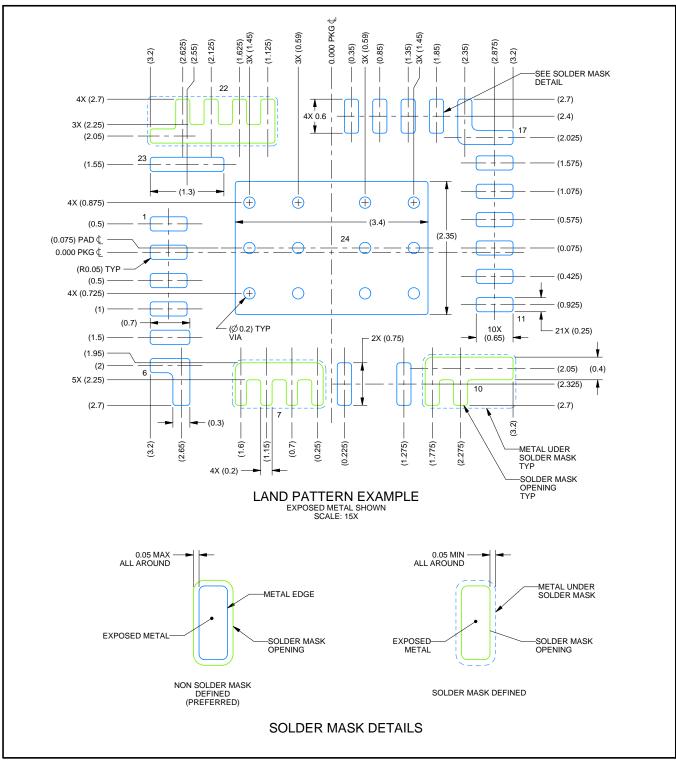

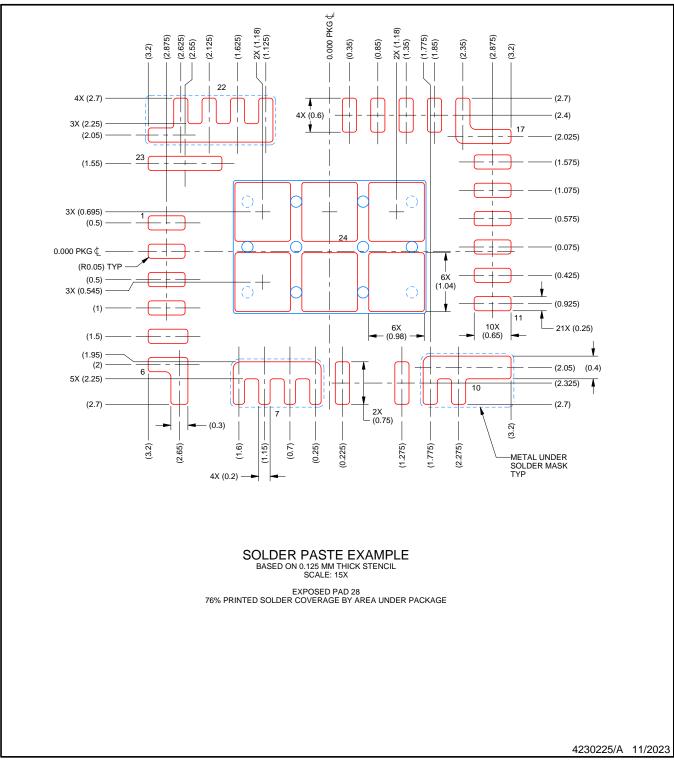

Figure 5-1. TPS1685x VMA Package, QFN 23-Pin (Top View)

Table 5-1. Pin Functions

| PI   | N   | <b>TYPE</b> <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                   |  |  |

|------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | NO. | ITPE                       | DESCRIPTION                                                                                                                                                                                                                                                                                   |  |  |

| ILIM | 1   | I/O                        | An external resistor from this pin to GND sets the active current sharing threshold during steady-state. This pin also serves as individual eFuse current monitor output during steady state. <i>Do not leave floating</i> .                                                                  |  |  |

| IMON | 2   | I/O                        | An external resistor from this pin to GND sets the overcurrent protection threshold and fast-trip threshold during steady-state. This pin also acts as a fast and accurate analog output load current monitor signal during steady-state. <i>Do not leave floating.</i>                       |  |  |

| IREF | 3   | I/O                        | This pin sets the reference voltage for overcurrent, short-circuit protection and active current sharing blocks. The reference voltage can be generated using internal current source and resistor on this pin, or can be driven from external voltage source. <i>Do not leave floating</i> . |  |  |

| dVdT | 4   | I/O                        | This pin is used to configure the output slew rate during Start-up. Leave this pin open to allow fastest start-up. Connect capacitor to ground to slow down the slew rate to manage inrush current.                                                                                           |  |  |

| GND  | 5   | G                          | Device ground reference pin. Connect to system ground.                                                                                                                                                                                                                                        |  |  |

## Table 5-1. Pin Functions (continued)

| PIN     |            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |

|---------|------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | NO.        | TTPE                | DESCRIPTION                                                                                                                                                                                                                                                                      |  |  |

| SFT_SEL | 6          | I/O                 | This pin selects the scalable fast-trip threshold multiplier during steady state.<br>Connect a resistor from this pin to GND to select the fast-trip threshold<br>multiplier.                                                                                                    |  |  |

| OUT     | 7, 8       | Р                   | Power output. Must be soldered to the output power plane uniformly for proper heat dissipation.                                                                                                                                                                                  |  |  |

| VDD     | 9          | Ρ                   | Controller power input pin. Can be used to power the internal control circuitry with a filtered and stable supply which is not affected by system transients. Connect this pin to VIN through a series resistor and add a decoupling capacitor to GND.                           |  |  |

| IN      | 10, 22, 23 | Р                   | Power input. Must be soldered to the input power plane uniformly for proper heat dissipation.                                                                                                                                                                                    |  |  |

| NC      | 11, 17, 21 | _                   | Do not connect anything to this pin.                                                                                                                                                                                                                                             |  |  |

| MODE    | 12         | I                   | This pin is used to configure the device for standalone/primary or secondary mode. Connect the pin to GND to configure device as a secondary to a primary eFuse/controller. Leave the pin floating for standalone/primary mode of operation.                                     |  |  |

| FLT     | 13         | 0                   | This is an open drain active low pin which is pulled low to indicate a fault. Pull up this pin to external supply voltage with a resistor.                                                                                                                                       |  |  |

| ITIMER  | 14         | I/O                 | A capacitor from this pin to GND sets the overcurrent blanking interval during which the output current can temporarily exceed the overcurrent threshold (but lower than fast-trip threshold) during steady-state operation before the device overcurrent response takes action. |  |  |

| ТЕМР    | 15         | I/O                 | Analog voltage output for junction temperature. Can be tied together with TEMP outputs of multiple devices in a parallel configuration to indicate the peak temperature of the parallel chain.                                                                                   |  |  |

| EN/UVLO | 16         | I                   | Active high enable input. Connect resistor divider from input supply to set the undervoltage threshold. Do not leave floating.                                                                                                                                                   |  |  |

| OVP     | 18         | I                   | This pin can be used to set the over-voltage set-point. Connect a resistor divider from VIN to this pin. Do not leave floating.                                                                                                                                                  |  |  |

| PGOOD   | 19         | 0                   | This is an open-drain active high power good pin which is asserted high when<br>the device is in steady state. This pin has a weak internal pull-up to internal<br>supply voltage.                                                                                               |  |  |

| SWEN    | 20         | I/O                 | This is an open-drain signal to indicate and control power switch ON/OFF status. This pin facilitates active synchronization between multiple devices in a parallel chain. This pin has a weak internal pull-up to internal supply voltage.                                      |  |  |

| IN      | PowerPad   | Р                   | Power input. Must be soldered to the input power plane uniformly for proper heat dissipation.                                                                                                                                                                                    |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **6** Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               | Parameter                                                                    | Pin       | MIN        | MAX                     | UNIT |

|-----------------------------------------------|------------------------------------------------------------------------------|-----------|------------|-------------------------|------|

| V <sub>INMAX</sub> , V <sub>DDMAX</sub>       | Maximum Input and Supply Voltage (–40°C $\leq$ T <sub>J</sub> $\leq$ 125°C ) | IN, VDD   | -0.3       | 90                      | V    |

| V <sub>INMAX,25</sub> , V <sub>DDMAX,25</sub> | Maximum Input and Supply Voltage (25°C $\leq$ T_J $\leq$ 125°C )             | IN, VDD   | -0.3       | 92                      | V    |

| V <sub>OUTMAX</sub>                           | Maximum Output Voltage                                                       | OUT       |            | Min(92 V,<br>VIN + 0.3) |      |

| V <sub>IN</sub> - V <sub>OUT</sub>            | Maximum difference between IN and OUT                                        | IN, OUT   | -0.3       | 90                      | V    |

| V <sub>IILIMMAX</sub>                         | Maximum ILIM Pin Voltage                                                     | ILIM      | -0.3       | 6                       | V    |

| VIMONMAX                                      | Maximum IMON Pin Voltage                                                     | IMON      | -0.3       | 6                       | V    |

| V <sub>SFT_SELMAX</sub>                       | Maximum SFT_SEL Pin Voltage                                                  | SFT_SEL   | -0.3       | 6                       | V    |

| V <sub>OVP</sub>                              | Maximum OVP Pin Voltage                                                      | OVP       | -0.3       | 6                       | V    |

| V <sub>ITIMER</sub>                           | Maximum ITIMER Pin Voltage                                                   | ITIMER    | -0.3       | 6                       | V    |

| V <sub>IREFMAX</sub>                          | Maximum IREF Pin Voltage                                                     | IREF      | -0.3       | 6                       | V    |

| V <sub>DVDTMAX</sub>                          | Maximum DVDT Pin Voltage                                                     | DVDT      | -0.3       | 6                       | V    |

| V <sub>MODEMAX</sub>                          | Maximum MODE Pin Voltage                                                     | MODE      | -0.3       | 6                       | V    |

| V <sub>SWENMAX</sub>                          | Maximum SWEN Pin Voltage                                                     | SWEN      | -0.3       | 6                       | V    |

| I <sub>SWENMAX</sub>                          | Maximum SWEN Pin Sink                                                        | SWEN      |            | 10                      | mA   |

| V <sub>ENMAX</sub>                            | Maximum EN/UVLO Pin Voltage                                                  | EN/UVLO   | -0.3       | 6                       | V    |

| V FLTMAX                                      | Maximum FLT Pin Voltage                                                      | FLT       | -0.3       | 6                       | V    |

| I FLTMAX                                      | Maximum FLT Pin Sink Current                                                 | FLT       |            | 10                      | mA   |

| V <sub>PGOODMAX</sub>                         | Maximum PGOOD Pin Voltage                                                    | PGOOD     | -0.3       | 6                       | V    |

| IPGOODMAX                                     | Maximum PGOOD Pin Sink Current                                               | PGOOD     |            | 10                      | mA   |

| V <sub>TEMP</sub>                             | Maximum TEMP Pin Voltage                                                     | TEMP      | -0.3       | 6                       | V    |

| I <sub>MAX</sub>                              | Maximum Continuous Switch Current                                            | IN to OUT | Internally | Limited                 | А    |

| T <sub>JMAX</sub>                             | Junction temperature                                                         |           | Internally | Limited                 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) During FET OFF condition for negative transients.

# 6.2 ESD Ratings

|                    |                         |                                                                                         | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>         | ±1500 | M    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                         | Parameter                                                       | Pin          | MIN | MAX             | UNIT |

|-------------------------|-----------------------------------------------------------------|--------------|-----|-----------------|------|

| V <sub>IN</sub>         | Input Voltage Range                                             | IN           | 9   | 80              | V    |

| V <sub>DD</sub>         | Supply Voltage Range                                            | VDD          | 9   | 80              | V    |

| V <sub>OUT</sub>        | Output Voltage Range                                            | OUT          |     | V <sub>IN</sub> | V    |

| V <sub>EN/UVLO</sub>    | Enable Pin Voltage Range                                        | EN/<br>UVLO  |     | 5               | V    |

| dVdT                    | dVdT Pin Cap Voltage Rating                                     | dVdT         |     | 4               | V    |

| V <sub>PGOOD</sub>      | PGOOD Pin Pull-up Voltage Range                                 | PGOOD        |     | 5               | V    |

| V <sub>FLT</sub>        | FLT Pin Pull-up Voltage Range                                   | FLT          |     | 5               | V    |

| V <sub>SWEN</sub>       | SWEN Pin Pull-up Voltage Range                                  | SWEN         |     | 5               | V    |

| V <sub>TEMP</sub>       | TEMP Pin Voltage Rating                                         | TEMP         |     | 5               | V    |

| V <sub>IREF</sub>       | IREF Pin Voltage Range                                          | IREF         | 0.3 | 1.2             | V    |

| VILIM                   | ILIM Pin Voltage Range                                          | ILIM         |     | 0.4             | V    |

| V <sub>IMON</sub>       | IMON Pin Voltage Range                                          | IMON         |     | 1.2             | V    |

| C <sub>IN</sub>         | Capacitance on IN pins                                          | IN           | 10  |                 | nF   |

| C <sub>OUT</sub>        | Capacitance on OUT pins                                         | OUT          | 10  |                 | μF   |

| dV <sub>IN</sub> /dt    | Slew rate on IN pins                                            | IN           |     | 500             | V/µs |

| I <sub>MAX</sub>        | RMS Switch Current T <sub>J</sub> ≤125°C                        | IN to<br>OUT |     | 20              | А    |

| I <sub>MAX, Pulse</sub> | Peak Output Current for ≤10 ms duration, T <sub>A</sub> ≤ 70 °C | IN to<br>OUT |     | 27              | А    |

| TJ                      | Junction temperature                                            |              | -40 | 125             | °C   |

## 6.4 Thermal Information

|                  |                                              | TPS1685x |      |

|------------------|----------------------------------------------|----------|------|

|                  | THERMAL METRIC <sup>(1)</sup> (2)            | LQFN     | UNIT |

|                  |                                              | PINS     |      |

| R <sub>0JA</sub> | Junction-to-ambient thermal resistance       | 22.1     | °C/W |

| $\Psi_{JT}$      | Junction-to-top characterization parameter   | 1.1      | °C/W |

| $\Psi_{JB}$      | Junction-to-board characterization parameter | 9.4      | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

(2) Based on simulations conducted with the device mounted on a "3 x 4.5" PCB (2s2p) as JESD51-7

## **6.5 Electrical Characteristics**

$-40^{\circ}C \le T_J \le +125^{\circ}C$ , VIN = V<sub>DD</sub> = 50V, OUT = Open, R<sub>ILIM</sub> = 931 $\Omega$ , R<sub>IMON</sub> = 2.55k $\Omega$ , V<sub>IREF</sub> = 1V, FLT = 33k $\Omega$  pull-up to 3.3V, PGOOD = 33k $\Omega$  pull-up to 3.3V, C<sub>OUT</sub> = 10µF, C<sub>IN</sub> = 10nF, dVdT = Open, ITIMER = Open, V<sub>EN/UVLO</sub> = 2V, TEMP = Open, MODE = Open. (All voltages referenced to GND, (unless otherwise noted))

|                        | PARAMETER                                                                                        | TEST CONDITIONS                                               | MIN             | TYP  | MAX  | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------|------|------|------|

| INPUT SUPPLY           | (VDD)                                                                                            |                                                               |                 |      |      |      |

| V <sub>IN</sub>        | Input voltage range                                                                              |                                                               | 9               |      | 80   | V    |

| V <sub>DD</sub>        | Input voltage range                                                                              |                                                               | V <sub>IN</sub> |      | 80   | V    |

| I <sub>QON(VDD)</sub>  | V <sub>DD</sub> ON state quiescent current                                                       | $V_{DD} > V_{UVPR}, V_{EN} \ge V_{UVLOR}, V_{OVP} < V_{OVPF}$ |                 | 0.6  | 4    | mA   |

| V <sub>UVPR</sub>      | V <sub>DD</sub> Undervoltage Protection Threshold<br>Rising                                      | V <sub>DD</sub> Rising                                        |                 | 8.5  | 8.9  | V    |

| V <sub>UVPF</sub>      | V <sub>DD</sub> Undervoltage Protection Threshold falling                                        | V <sub>DD</sub> Falling                                       | 6.7             | 7.05 |      | V    |

| V <sub>UVPHYS</sub>    | UVP Hysteresis VDD                                                                               |                                                               |                 | 1.5  |      | V    |

| INPUT SUPPLY           | (IN)                                                                                             |                                                               | 1               |      | I    |      |

| V <sub>UVPR(VIN)</sub> | VIN Undervoltage Protection Threshold                                                            | V <sub>IN</sub> Rising                                        |                 | 8.45 | 9    | V    |

| V <sub>UVPF(VIN)</sub> | VIN Undervoltage Protection Threshold                                                            | V <sub>IN</sub> Falling                                       | 6.5             | 7.05 |      | V    |

| I <sub>QON(VIN)</sub>  | V <sub>IN</sub> ON state quiescent current                                                       | V <sub>EN</sub> ≥ V <sub>UVLOR</sub>                          |                 | 1.69 |      | mA   |

| I <sub>QOFF(VIN)</sub> | V <sub>IN</sub> OFF state current                                                                | V <sub>SDR</sub> < V <sub>EN</sub> < V <sub>UVLO</sub>        |                 | 47   |      | μA   |

| I <sub>SD(VIN)</sub>   | V <sub>IN</sub> shutdown current                                                                 | V <sub>EN</sub> < V <sub>SDF</sub>                            |                 | 46   |      | μA   |

| . ,                    | ERVOLTAGE LOCKOUT (EN/UVLO)                                                                      |                                                               |                 |      |      |      |

| V <sub>UVLO(R)</sub>   | EN/UVLO pin voltage threshold for turning on, rising                                             | EN/UVLO Rising                                                | 1.18            | 1.21 | 1.23 | V    |

| V <sub>UVLO(F)</sub>   | EN/UVLO pin voltage threshold for<br>turning off and engaging QOD,<br>falling (primary device)   | EN/UVLO Falling                                               | 1               | 1.12 | 1.14 | V    |

| V <sub>UVLOF</sub>     | EN/UVLO pin voltage threshold for<br>turning off and engaging QOD,<br>falling (Secondary device) | EN/UVLO Falling                                               |                 | 1    |      | V    |

| V <sub>UVLOHYS</sub>   | UVLO Hysteresis                                                                                  |                                                               |                 | 89   |      | mV   |

| V <sub>SDF</sub>       | Shutdown threshold                                                                               | EN/UVLO Falling                                               | 0.4             | 0.42 |      | V    |

| V <sub>SDR</sub>       | Shutdown threshold                                                                               | EN/UVLO Rising                                                |                 | 0.5  | 0.55 | V    |

| I <sub>ENLKG</sub>     | EN/UVLO pin leakage current                                                                      |                                                               | -100            |      | 100  | nA   |

| OVERVOLTAGE            | E PROTECTION (IN)                                                                                |                                                               |                 |      |      |      |

| V <sub>OVP(R)</sub>    | Overvoltage protection threshold (rising)                                                        | OVP pin rising                                                | 1.11            | 1.17 | 1.20 | V    |

| V <sub>OVP(F)</sub>    | Overvoltage protection threshold (falling)                                                       | OVP pin falling                                               | 1.08            | 1.12 | 1.15 | V    |

| V <sub>OVPHYS</sub>    | Overvoltage protection threshold (Hysteresis)                                                    |                                                               |                 | 57   |      | mV   |

| I <sub>OVPLKG</sub>    | OVP pin leakage current                                                                          | V <sub>OVP</sub> = 1.2V                                       | -100            |      | 100  | nA   |

| V <sub>OVPR(IN)</sub>  | Internal Overvoltage protection threshold (rising)                                               | V <sub>IN</sub> Rising                                        | 84              | 90.8 | 95   | V    |

| V <sub>OVPF(IN)</sub>  | Internal Overvoltage protection threshold (falling)                                              | V <sub>IN</sub> falling                                       | 77              | 84.5 | 90   | V    |

| ON-RESISTAN            | CE (IN - OUT)                                                                                    |                                                               |                 |      |      |      |

| R <sub>ON</sub>        | ON state resistance                                                                              | I <sub>OUT</sub> = 12A; T <sub>J</sub> = 25°C                 |                 | 3.5  | 5.55 | mΩ   |

| R <sub>ON</sub>        | ON state resistance                                                                              | I <sub>OUT</sub> = 12A; T <sub>J</sub> = –40°C to<br>125°C    |                 |      | 6.1  | mΩ   |

| CURRENT LIMI           | T REFERENCE (IREF)                                                                               |                                                               | 1               |      |      |      |

| V <sub>IREF</sub>      | IREF pin recommended voltage range                                                               |                                                               | 0.3             |      | 1.2  | V    |

| I <sub>IREF</sub>      | IREF internal sourcing current                                                                   | V <sub>IREF</sub> = 1V                                        | 24.2            | 25   | 25.8 | μA   |

Copyright © 2025 Texas Instruments Incorporated

# 6.5 Electrical Characteristics (continued)

$-40^{\circ}C \le T_J \le +125^{\circ}C$ , VIN = V<sub>DD</sub> = 50V, OUT = Open, R<sub>ILIM</sub> = 931 $\Omega$ , R<sub>IMON</sub> = 2.55k $\Omega$ , V<sub>IREF</sub> = 1V, FLT = 33k $\Omega$  pull-up to 3.3V, PGOOD = 33k $\Omega$  pull-up to 3.3V, C<sub>OUT</sub> = 10 $\mu$ F, C<sub>IN</sub> = 10nF, dVdT = Open, ITIMER = Open, V<sub>EN/UVLO</sub> = 2V, TEMP = Open, MODE = Open. (All voltages referenced to GND, (unless otherwise noted))

|                                       | PARAMETER                                                             | TEST CONDITIONS                                                            | MIN  | TYP                        | MAX   | UNIT |

|---------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|------|----------------------------|-------|------|

| CURRENT LIMI                          | T (ILIM)                                                              |                                                                            |      |                            |       |      |

| G <sub>ILIM(LIN)</sub>                | Current Monitor Gain (ILIM:IOUT) vs.<br>IOUT.                         | Device in steady state (PG asserted), I <sub>OUT</sub> = 12 A              | 17   | 18                         | 20.6  | µA/A |

| I <sub>start-up</sub> peak            | Peak Current at Startup (Ipeak)                                       | VOUT> VFB, GHI deasserted.<br>VIN≤60V                                      |      | 0.5                        |       | А    |

| V <sub>FB</sub>                       | Foldback voltage                                                      |                                                                            |      | 2                          |       | V    |

| OUTPUT CURR                           | ENT MONITOR AND OVERCURRENT PROT                                      | ECTION (IMON)                                                              |      |                            |       |      |

| G <sub>IMON</sub>                     | Current Monitor Gain (IMON:IOUT)                                      | Device in steady state (PG asserted), for $12A \le I_{OUT} \le 20A$        | 17.7 | 18.18                      | 18.49 | μA/A |

| G <sub>IMON</sub>                     | Current Monitor Gain (IMON:IOUT)                                      | Device in steady state (PG asserted), I <sub>OUT</sub> = 4A                | 17.4 | 18.31                      | 19.1  | µA/A |

| I <sub>OCP</sub>                      | IOUT Current limit trip (Circuit-Breaker) threshold                   | $R_{IMON}$ = 2.55k $\Omega$ , $V_{IREF}$ = 1V                              | 21.2 | 21.7                       | 22.3  | А    |

| CURRENT FAU                           | LT TIMER (ITIMER)                                                     |                                                                            |      |                            |       |      |

| I <sub>ITMR</sub>                     | ITIMER pin internal discharge current                                 | $I_{OUT} > I_{OCP}$ , ITIMER $\downarrow$                                  | 1.77 | 2.2                        | 2.6   | μA   |

| R <sub>ITMR</sub>                     | ITIMER pin internal pull-up resistance                                |                                                                            | 5    | 12.3                       | 23    | kΩ   |

| V <sub>INT</sub>                      | ITIMER pin internal pull-up voltage                                   | I <sub>OUT</sub> < I <sub>OCP</sub>                                        | 4.4  | 5                          | 5.6   | V    |

| ΔV <sub>ITMR</sub>                    | ITIMER discharge voltage                                              | I <sub>OUT</sub> > I <sub>TRIP</sub> , ITIMER ↓                            | 1.28 | 1.5                        | 1.8   | V    |

| ΔV <sub>ITMR</sub> /I <sub>ITMR</sub> | ITIMER Discharge voltage to Discharge current ratio                   | I <sub>OUT</sub> > I <sub>TRIP</sub> , ITIMER ↓                            | 0.49 | 0.72                       | 0.97  | V/µA |

| SHORT-CIRCUI                          | TPROTECTION                                                           |                                                                            |      |                            |       |      |

| I <sub>FFT</sub>                      | Fixed fast-trip threshold in steady state (primary)(TPS1685xA only)   | PG asserted High (MODE = Open)                                             |      | 83                         |       | А    |

| I <sub>FFT</sub>                      | Fixed fast-trip threshold in steady state (primary)(TPS1685x)         | PG asserted High (MODE = Open)                                             |      | 73                         |       | А    |

| I <sub>FFT</sub>                      | Fixed fast-trip threshold in steady state (primary)(TPS1685xA only)   | PG asserted High (MODE =<br>Open); T <sub>J</sub> = 25°C to 125°C          | 65   |                            |       | А    |

| I <sub>FFT</sub>                      | Fixed fast-trip threshold in steady state (primary)(TPS1685x)         | PG asserted High (MODE =<br>Open); T <sub>J</sub> = 25°C to 125°C          | 55   |                            |       | А    |

| I <sub>FFT</sub>                      | Fixed fast trip threshold in steady state (secondary)(TPS1685A0 only) | PG asserted High (MODE = GND)                                              |      | 105                        |       | А    |

| I <sub>FFT</sub>                      | Fixed fast trip threshold in steady state (secondary)(TPS1685x)       | PG asserted High (MODE = GND)                                              |      | 95                         |       | А    |

| I <sub>SFT</sub>                      | Scalable fast trip current                                            | R <sub>SFT_SEL</sub> < 95kΩ, PG asserted<br>High (MODE = Open)             |      | 38.3                       |       | A    |

| I <sub>SFT</sub>                      | Scalable fast trip current                                            | 105kΩ < $R_{SFT\_SEL}$ <<br>195kΩ, PG asserted High<br>(MODE = Open)       |      | 2.5 ×<br>I <sub>OCP</sub>  |       | А    |

| I <sub>SFT</sub>                      | Scalable fast trip current                                            | 105kΩ < R <sub>SFT_SEL</sub> <<br>195kΩ, PG asserted High<br>(MODE = GND)  |      | 2.8 ×<br>I <sub>OCP</sub>  |       | A    |

| I <sub>SFT</sub>                      | Scalable fast trip current                                            | 205kΩ < R <sub>SFT_SEL</sub> <<br>295kΩ, PG asserted High<br>(MODE = Open) |      | 2 × I <sub>OCP</sub>       |       | A    |

| I <sub>SFT</sub>                      | Scalable fast trip current                                            | 205kΩ < R <sub>SFT_SEL</sub> <<br>295kΩ, PG asserted High<br>(MODE = GND)  |      | 2.26 ×<br>I <sub>OCP</sub> |       | А    |

## 6.5 Electrical Characteristics (continued)

$-40^{\circ}C \le T_{J} \le +125^{\circ}C$ , VIN = V<sub>DD</sub> = 50V, OUT = Open, R<sub>ILIM</sub> = 931 $\Omega$ , R<sub>IMON</sub> = 2.55k $\Omega$ , V<sub>IREF</sub> = 1V, FLT = 33k $\Omega$  pull-up to 3.3V, PGOOD = 33k $\Omega$  pull-up to 3.3V, C<sub>OUT</sub> = 10µF, C<sub>IN</sub> = 10nF, dVdT = Open, ITIMER = Open, V<sub>EN/UVLO</sub> = 2V, TEMP = Open, MODE = Open. (All voltages referenced to GND, (unless otherwise noted))

|                             | PARAMETER                                                                                         | TEST CONDITIONS                                                                 | MIN   | TYP                        | MAX   | UNIT  |

|-----------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|----------------------------|-------|-------|

| I <sub>SFT</sub>            | Scalable fast trip current                                                                        | 305kΩ < R <sub>SFT_SEL</sub> , PG<br>asserted High (MODE = Open)                |       | 1.5 ×<br>I <sub>OCP</sub>  |       | А     |

| I <sub>SFT</sub>            | Scalable fast trip current                                                                        | 305kΩ < R <sub>SFT_SEL</sub> ,PG<br>asserted High (MODE = GND)                  |       | 1.71 ×<br>I <sub>OCP</sub> |       | А     |

| I <sub>SFT(SAT)</sub>       | Scalable fast trip Current (inrush)                                                               | During Powerup, PGOOD Low                                                       |       | 2                          |       | А     |

| ACTIVE CURREN               | IT SHARING                                                                                        |                                                                                 |       |                            |       |       |

| R <sub>ON(ACS)</sub>        | R <sub>ON</sub> during Active current sharing                                                     | V <sub>ILIM</sub> > 1.1 x (1/3) × V <sub>IREF</sub>                             |       | 4.38                       | 6.9   | mΩ    |

| G <sub>IMON(ACS)</sub>      | IMON:IOUT ratio during active current limiting                                                    | PG asserted High, V <sub>ILIM</sub> > 1.1 × V <sub>IREF</sub>                   | 17.24 | 18.49                      | 19.84 | µA/A  |

| CL <sub>REF(ACS)</sub>      | Ratio of active current sharing trigger<br>threshold to steady state circuit-breaker<br>threshold | PG asserted High                                                                |       | 36.67                      |       | %     |

| INRUSH CURREN               | NT PROTECTION (DVDT)                                                                              |                                                                                 |       |                            |       |       |

| I <sub>DVDT</sub>           | dVdt Pin Charging Current (Primary/<br>Standalone mode)                                           | MODE = Open                                                                     | 1.5   | 2.0                        | 3     | μA    |

| G <sub>DVDT</sub>           | dVdt Gain                                                                                         | 0.4V < V <sub>dVdt</sub> < 2.4V                                                 | 22    | 25                         | 28    | V/V   |

| I <sub>DVDTLKG</sub>        | dVdt Pin Leakage Current (Secondary mode)                                                         | MODE = GND                                                                      | -100  |                            | 100   | nA    |

| R <sub>DVDT</sub>           | dVdt Pin to GND Discharge Resistance                                                              |                                                                                 |       | 500                        |       | Ω     |

| GHI                         |                                                                                                   |                                                                                 |       |                            |       |       |

| V <sub>GS(GHI)</sub> Rising | G-S Threshold when GHI/PG is asserted                                                             |                                                                                 |       | 7                          |       | V     |

| R <sub>ON(GHI)</sub>        | Ron When GHI/PG is asserted                                                                       |                                                                                 |       | 3.8                        |       | mΩ    |

| QUICK OUTPUT I              | DISCHARGE (QOD)                                                                                   |                                                                                 |       |                            |       |       |

| I <sub>QOD</sub>            | Quick Output Discharge pull-down current                                                          | V <sub>SD(R)</sub> < V <sub>EN</sub> < V <sub>UVLO</sub> , −40 < Tj<br>< 125 °C | 17    | 22                         | 25    | mA    |

| TEMPERATURE                 | SENSOR OUTPUT (TEMP)                                                                              |                                                                                 |       |                            |       |       |

| G <sub>TMP</sub>            | TEMP sensor gain                                                                                  | V <sub>IN</sub> = 51V                                                           | 2.6   | 2.73                       | 3.1   | mV/°C |

| V <sub>TMP</sub>            | TEMP pin output voltage                                                                           | T <sub>J</sub> = 25 °C, V <sub>IN</sub> = 51 V                                  | 670   | 678                        | 690   | mV    |

| ITMPSRC                     | TEMP pin sourcing current                                                                         | V <sub>IN</sub> = 51V                                                           | 110   | 119                        | 133   | μA    |

| I <sub>TMPSNK</sub>         | TEMP pin sinking current                                                                          | V <sub>IN</sub> = 51 V                                                          | 8     | 10                         | 14    | μA    |

| OVERTEMPERAT                | TURE PROTECTION (OTP)                                                                             |                                                                                 |       |                            | I     |       |

| TSD                         | Absolute Thermal Shutdown Rising<br>Threshold                                                     | $T_J$ Rising, , $V_{IN}$ = 51V                                                  |       | 150                        |       | °C    |

| TSD <sub>HYS</sub>          | Absolute Thermal shutdown hysteresis                                                              | T <sub>J</sub> Falling, V <sub>IN</sub> = 51V                                   |       | 13                         |       | °C    |

| FET HEALTH MO               | NITOR                                                                                             | ·                                                                               |       |                            | I     |       |

| V <sub>DSFLT</sub>          | FET D-S Fault Threshold                                                                           | SWEN = L, V <sub>IN</sub> = 51V                                                 |       | 0.5                        |       | V     |

| V <sub>DSOK</sub>           | FET D-S Fault Recovery Threshold                                                                  | SWEN = L, V <sub>IN</sub> = 51V                                                 |       | 0.64                       |       | V     |

| SINGLE POINT F              | AILURE (IMON, IREF, ITIMER)                                                                       | ·                                                                               |       |                            | I     |       |

| IOC BKP                     | Back-up overcurrent protection threshold                                                          | IMON short to GND                                                               |       | 38.3                       |       | Α     |

### 6.6 Logic Interface

$-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ ,  $V_{\text{IN}} = V_{\text{DD}} = 45\text{V}$  to 60V, OUT = Open,  $R_{\text{ILIM}} = 931\Omega$ ,  $R_{\text{IMON}} = 2.55k\Omega$ ,  $V_{\text{IREF}} = 1\text{V}$ ,  $\overline{\text{FLT}} = 33k\Omega$  pull-up to 3.3V, PGOOD = 33k $\Omega$  pull-up to 3.3V,  $C_{\text{OUT}} = 10\mu\text{F}$ ,  $C_{\text{IN}} = 10\text{nF}$ , dVdT = Open, ITIMER = Open,  $V_{\text{EN/UVLO}} = 2\text{V}$ , TEMP = Open, MODE = Open. (All voltages referenced to GND, (unless otherwise noted))

|                      | PARAMETER                     | TEST CONDITIONS      | MIN  | TYP | MAX | UNIT |

|----------------------|-------------------------------|----------------------|------|-----|-----|------|

| SWEN                 |                               |                      |      |     | ·   |      |

| R <sub>SWEN</sub>    | SWEN pin pull-down resistance | SWEN de-asserted Low |      | 6.8 |     | Ω    |

| FAULT IND            | FAULT INDICATION (FLT)        |                      |      |     |     |      |

| R <sub>FLTB</sub>    | FLT pin pull-down resistance  | FLT asserted Low     |      | 6.6 |     | Ω    |

| I <sub>FLTBLKG</sub> | FLT pin leakage current       | FLT de-asserted High | -0.1 |     | 0.1 | μA   |

| POWER GO             | POWER GOOD INDICATION (PG)    |                      |      |     |     |      |

| R <sub>PG</sub>      | PG pin pull-down resistance   | PG de-asserted Low   |      | 6.9 |     | Ω    |

| I <sub>PGKG</sub>    | PG pin leakage current        | PG asserted High     | -1.5 |     | 1.5 | μA   |

## 6.7 Timing Requirements

$-40^{\circ}C \le T_J \le +125^{\circ}C$ , VIN = V<sub>DD</sub> = 45V to 60V, OUT = Open, R<sub>ILIM</sub> = 931 $\Omega$  R<sub>IMON</sub> = 2.55k $\Omega$ , V<sub>IREF</sub> = 1V, FLT = 33k $\Omega$  pull-up to 3.3V, PGOOD = 33k $\Omega$  pull-up to 3.3V, C<sub>OUT</sub> = 10µF, C<sub>IN</sub> = 10nF, dVdT = Open, ITIMER = Open., V<sub>EN/UVLO</sub> = 2V, TEMP = Open, MODE = Open. (All voltages referenced to GND, (unless otherwise noted))

|                        | PARAMETER                                     | TEST CONDITIONS                                                                                                                          | MIN | TYP | MAX | UNIT |

|------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>OVP</sub>       | Overvoltage protection response time          | V <sub>OVP</sub> > V <sub>OVPR</sub> V to<br>SWEN↓                                                                                       |     | 1.5 |     | μs   |

| t <sub>Insdly</sub>    | Insertion delay                               | V <sub>EN/UVLO</sub> > V <sub>UVLO(R)</sub> to<br>SWEN↑                                                                                  |     | 16  |     | ms   |

| t <sub>FFT</sub>       | Fixed Fast-Trip response time Hard Short      | V <sub>DS</sub> > V <sub>DSCOMP</sub> to SWEN↓                                                                                           |     | 214 |     | ns   |

| t <sub>SFT</sub>       | Scalable Fast-Trip response time              | I <sub>OUT</sub> > 3 × I <sub>OCP</sub> to I <sub>OUT</sub> ↓                                                                            |     | 600 |     | ns   |

| t <sub>ITIMER</sub>    | Overcurrent blanking interval                 | I <sub>OUT</sub> = 1.5 × I <sub>OCP</sub> , C <sub>ITIMER</sub><br>= Open                                                                |     | 0   |     | ms   |

| t <sub>ITIMER</sub>    | Overcurrent blanking interval                 | $I_{OUT} = 1.5 \times I_{OCP}, C_{ITIMER} = 4.7 nF$                                                                                      |     | 3   |     | ms   |

| t <sub>RST</sub>       | Auto-Retry Interval                           | Auto-retry variant, Primary mode (MODE = Open)                                                                                           |     | 680 |     | ms   |

| t <sub>REC</sub>       | Fault Recovery Time                           | Secondary mode (MODE<br>= GND), SWEN↓ to<br>SWEN↑                                                                                        |     | 8.9 |     | μs   |

| t <sub>EN(DG)</sub>    | EN/UVLO de-glitch time                        |                                                                                                                                          |     | 12  |     | μs   |

| t <sub>SWEN(TO)</sub>  | SWEN low interval to disable fast recovery    |                                                                                                                                          |     | 35  |     | μs   |

| t <sub>SU_TMR</sub>    | Start-up timeout interval                     | SWEN↑ to FLT↓                                                                                                                            |     | 6.6 |     | S    |

| t <sub>Discharge</sub> | QOD discharge time (90% to 10% of $V_{OUT}$ ) | $\label{eq:V_SD} \begin{split} V_{SD} &< V_{EN/UVLO} < V_{UVLO}, \\ C_{OUT} &= 0.5 m \text{F},  V_{\text{IN}} = 51 \text{V} \end{split}$ |     | 872 |     | ms   |

| t <sub>QOD</sub>       | QOD enable timer                              | V <sub>SD</sub> < V <sub>EN/UVLO</sub> < V <sub>UVLO</sub>                                                                               |     | 16  |     | μs   |

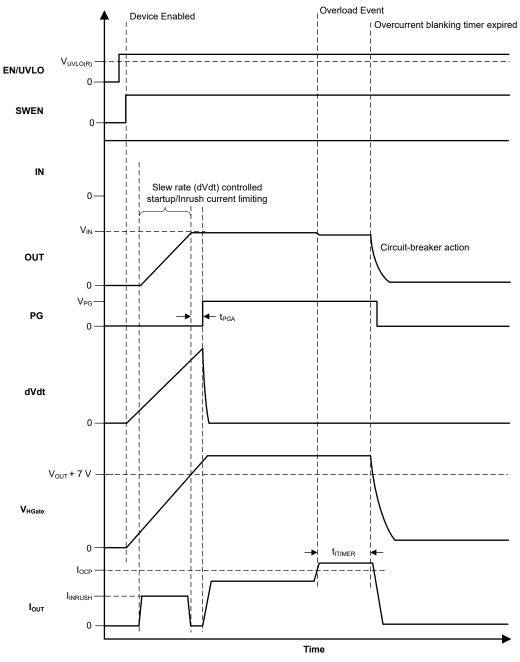

### 6.8 Switching Characteristics

The output rising slew rate is internally controlled and constant across the entire operating voltage range so that the turn on timing is not affected by the load conditions. The rising slew rate can be adjusted by adding capacitance from the dVdt pin to ground. As  $C_{dVdt}$  is increased it will reduce the slew rate (SR). See Slew Rate and Inrush Current Control (dVdt) section for more details. The Turn-Off Delay and Fall Time, however, are dependent on the RC time constant of the load capacitance ( $C_{OUT}$ ) and Load Resistance ( $R_L$ ). The Switching Characteristics are only valid for the power-up sequence where the supply is available in steady state condition and the load voltage is completely discharged before the device is enabled. Typical values are taken at  $T_J = 25^{\circ}$ C unless specifically noted otherwise.  $V_{IN} = 51V$ ,  $R_{OUT} = 2000\Omega$ ,  $C_{OUT} = 1$ mF

|                    | PARAMETER                     | C <sub>dVdt</sub> = 22 nF       | C <sub>dVdt</sub> = open | UNITS |

|--------------------|-------------------------------|---------------------------------|--------------------------|-------|

| SR <sub>ON</sub>   | Output rising slew rate       | 87                              | 80                       | V/s   |

| t <sub>D,ON</sub>  | Turn on delay                 | 16.8                            | 18                       | ms    |

| t <sub>R</sub>     | Rise time                     | 478                             | 525.6                    | ms    |

| t <sub>ON</sub>    | Turn on time                  | 494.8                           | 543.6                    | ms    |

| t <sub>D,OFF</sub> | Turn off delay (EN↓ to SWEN↓) | 1                               | 1                        | μs    |

| t <sub>F</sub>     | Fall time                     | Depends on R <sub>OUT</sub> and | C <sub>OUT</sub>         | μs    |

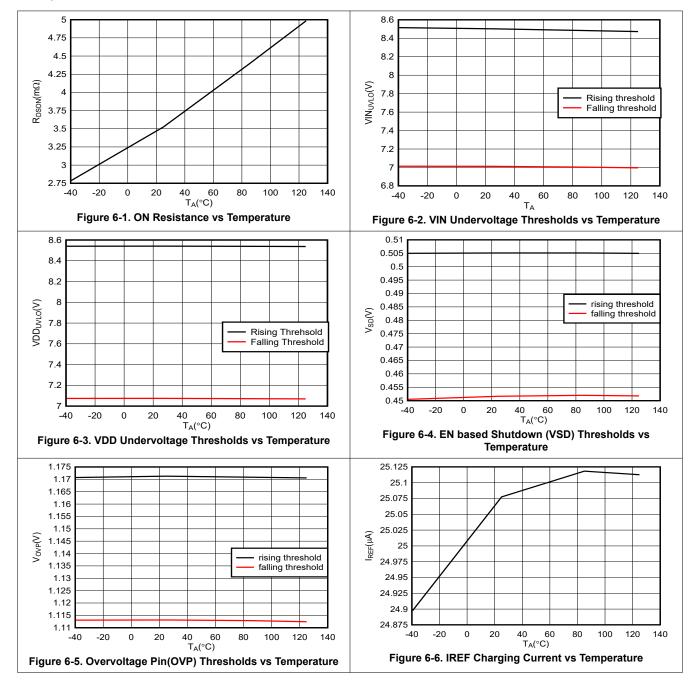

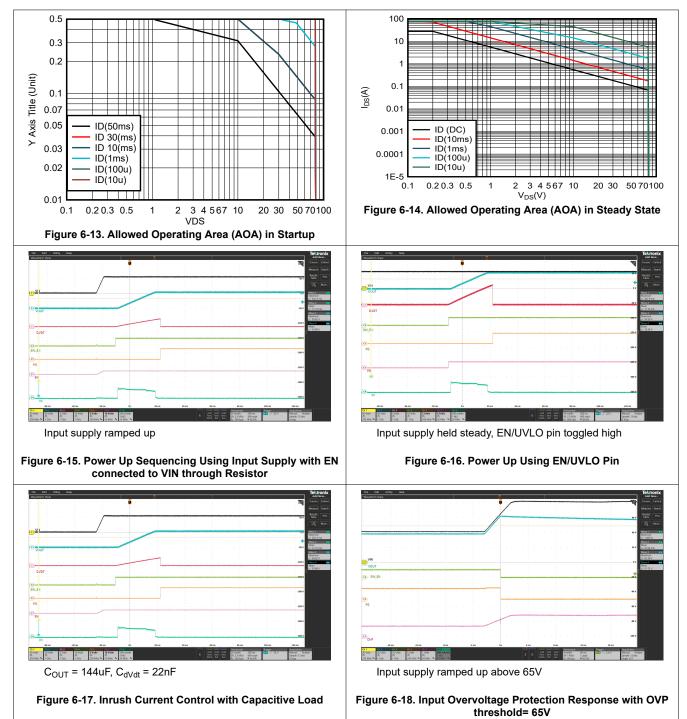

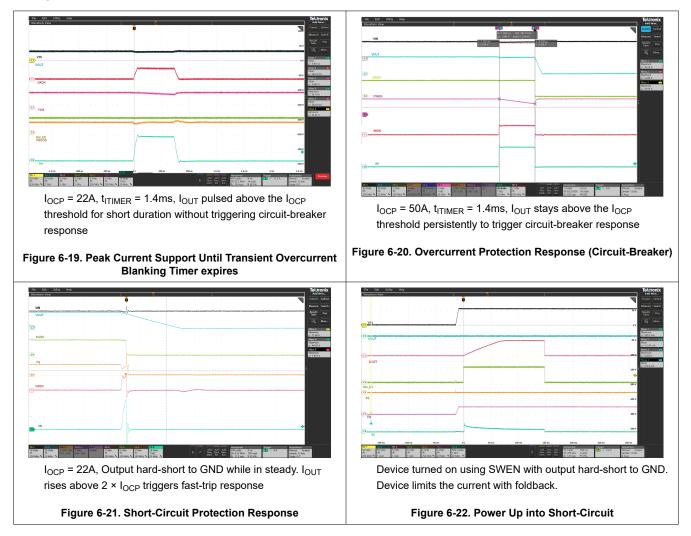

## **6.9 Typical Characteristics**

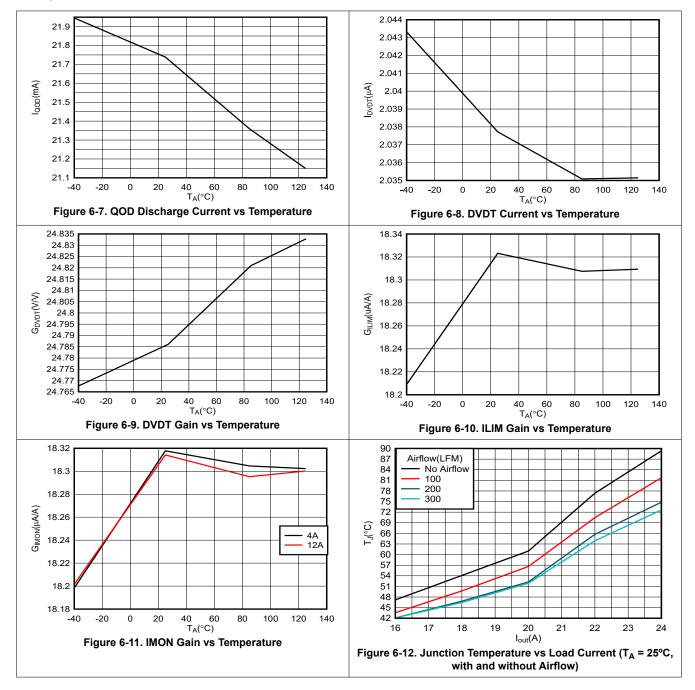

### 6.9 Typical Characteristics (continued)

## 6.9 Typical Characteristics (continued)

## 6.9 Typical Characteristics (continued)

# 7 Detailed Description

## 7.1 Overview

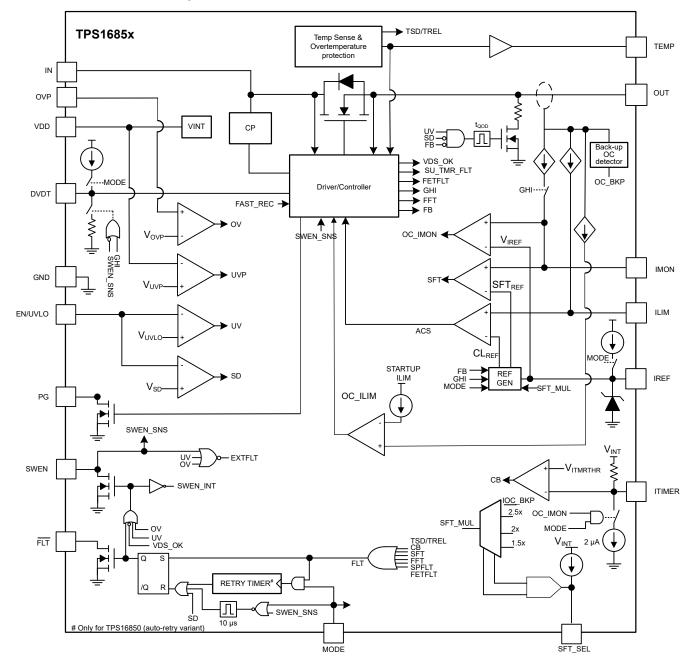

The TPS1685x is an eFuse with integrated power switch that is used to manage load voltage and load current. The device starts the operation by monitoring the VDD and IN bus. When  $V_{DD}$  and  $V_{IN}$  exceed the respective undervoltage protection (UVP) thresholds, the device waits for the insertion delay timer duration to allow the supply to stabilize before starting up. Next, the device samples the EN/UVLO pin. A high level on this pin enables the internal MOSFET to start conducting and allow current to flow from IN to OUT. When EN/UVLO is held low, the internal MOSFET is turned off.

After a successful start-up sequence, the TPS1685x device now actively monitors the load current and input voltage, and controls the internal FET to verify that the user adjustable overcurrent protection threshold limit I<sub>LIM</sub> is not exceeded and overvoltage spikes on IN pin are cut-off. This keeps the system safe from harmful levels of voltage and current. At the same time, a user adjustable overcurrent blanking timer allows the system to pass transient peaks in the load current profile without tripping the eFuse. Similarly, voltage transients on the supply line are intelligently masked to prevent nuisance trips. This provides a robust protection solution against real faults which is also immune to transients, thereby providing maximum system uptime.

The device has integrated high accuracy and high bandwidth analog load current monitor, which allows the system to precisely monitor the load current in steady state as well as during transients. This facilitates the implementation of advanced dynamic platform power management techniques to maximize system power utilization and throughput without sacrificing safety and reliability.

For systems needing higher load current support, multiple TPS1685x eFuses can be connected in parallel. All devices share current during start-up as well as steady state to avoid overstressing some of the devices more than others resulting in pre-mature or partial shutdown of the parallel chain. The devices synchronize the operating states to provide graceful startup, shutdown and response to faults.

The device has integrated protection circuits to help provide device safety and reliability under recommended operating conditions. The internal FET is protected at all time using the thermal shutdown mechanism, which turns off the FET whenever the junction temperature (Tj) becomes too hot.

# 7.2 Functional Block Diagram

(1)

## 7.3 Feature Description

The TPS1685x eFuse is a compact, feature rich power management device that provides detection, protection and indication in the event of system faults.

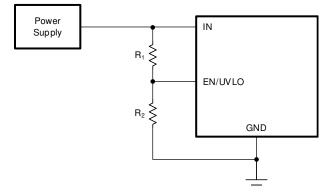

#### 7.3.1 Undervoltage Protection

The TPS1685x implements Undervoltage Lockout on VDD & VIN in case the applied voltage becomes too low for the system or device to properly operate. The Undervoltage lockout has a default lockout threshold of  $V_{UVP}$  internally on VDD and  $V_{UVPIN}$  on  $V_{IN}$ . Also, the UVLO comparator on the EN/UVLO pin allows the Undervoltage Protection threshold to be externally adjusted to a user defined value. The figure and equation below shows how a resistor divider can be used to set the UVLO set point for a given voltage supply.

Figure 7-1. Adjustable Undervoltage Protection

$$V_{IN(UV)} = V_{UVLO(R)} \frac{R_1 + R_2}{R_2}$$

The EN/UVLO pin implements a bi-level threshold.

- 1.  $V_{EN} > V_{UVLO(R)}$ : Device is fully ON.

- V<sub>SD(F)</sub> < V<sub>EN</sub> < V<sub>UVLO(F)</sub>: The FET along with most of the controller circuitry is turned OFF, except for some critical bias and digital circuitry. Holding the EN/UVLO pin in this state for > t<sub>QOD</sub> activates the Output Discharge function.

- V<sub>EN</sub> < V<sub>SD(F)</sub>: All active circuitry inside the part is turned OFF and et circuitry retains no digital state memory. The circuitry also resets any latched faults. In this condition, the device quiescent current consumption is minimal.

### 7.3.2 Insertion Delay

The TPS1685x implements insertion delay at start-up to verify the supply has stabilized before the device tries to turn on. This is to prevent any unexpected behavior in the system if the device tries to turn on while the card has not made firm contact with the backplane or if there is any supply ringing or oscillation during startup.

The device initially waits for the VDD supply to rise above the UVP threshold and all the internal bias voltages to settle. After that, the device remains off for an additional delay of  $T_{Insdly}$  irrespective of the EN/UVLO pin condition.

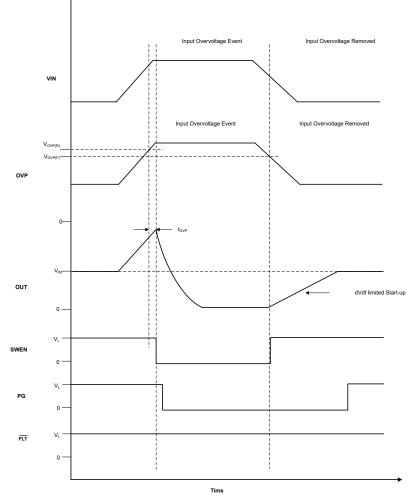

### 7.3.3 Overvoltage Protection

The TPS1685x implements overvoltage lockout to protect the load from input overvoltage conditions. A resistor divider needs to be connected on OVP pin to set the overvoltage set-point externally.

Figure 7-2. Adjustable Overvoltage Protection

$$V_{IN(OVP)} = V_{OVP(R)} \frac{R1 + R2}{R2}$$

<sup>(2)</sup>

When  $V_{IN}$  exceeds this value, the device turns off protecting the load from overvoltage. The device also has a fixed internal OV protection on IN pin at  $V_{OVPR(IN)}$ .

Figure 7-3. Input Overvoltage Protection Response

#### 7.3.4 Inrush Current, Overcurrent, and Short-Circuit Protection

TPS1685x incorporates four levels of protection against overcurrent:

- 1. Adjustable slew rate (dVdt) for inrush current control

- 2. Fixed current limit (Istart-up) for overcurrent protection during start-up

- 3. Circuit-breaker with an adjustable threshold (I<sub>OCP</sub>) and blanking timer (t<sub>ITIMER</sub>) for overcurrent protection during steady-state

#### 7.3.4.1 Slew rate (dVdt) and Inrush Current Control

During hot plug events or while trying to charge a large output capacitance, there can be a large inrush current. If the inrush current is not managed properly, the inrush current can damage the input connectors and cause the system power supply to droop. This action can lead to unexpected restarts elsewhere in the system. The inrush current during turn-on is directly proportional to the load capacitance and rising slew rate. Equation 3 can be used to find the slew rate (SR) required to limit the inrush current ( $I_{INRUSH}$ ) for a given load capacitance ( $C_{LOAD}$ ):

$$SR(V/ms) = \frac{I_{INRUSH}(A)}{C_{LOAD}(mF)}$$

(3)

A capacitor can be added to the DVDT pin to control the rising slew rate and lower the inrush current during turn-on. Slew rate control via DVDT pin holds true as long as the resulting startup current through the device is less than the  $I_{start-up peak}$ . The device limits the current at startup to not exceed  $I_{start-up peak}$ . The required CdVdt capacitance to produce a given slew rate can be calculated using Equation 4.

$$C_{DVDT}(nF) = \frac{48}{SR(V/ms)}$$

(4)

Note

The fastest output slew rate is achieved by leaving the dVdt pin open.

# 1. TI recommends using a minimum dvdt capacitor of 22nF.

- 2. High input slew rates in combination with high input power path inductance can result in oscillations during start-up. This can be mitigated using one or more of the following steps:

- a. Reduce the input inductance.

- b. Increase the capacitance on VIN pin.

- c. Increase the dVdt pin capacitance to reduce the slew rate or increase the start-up time.

#### 7.3.4.1.1 Start-Up Time Out

If the start-up is not completed, that is, the FET is not fully turned on within a certain timeout interval ( $t_{SU_TMR}$ ) after SWEN is asserted, the device registers a fault. FLT is asserted low and the device goes into latch-off or auto-retry mode depending on the device configuration.

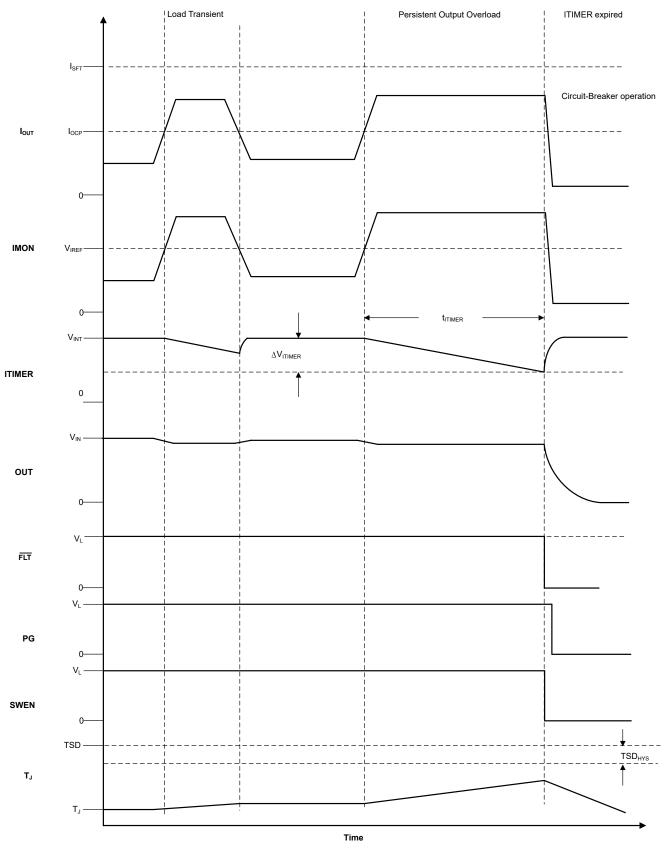

#### 7.3.4.2 Steady-State Overcurrent Protection (Circuit-Breaker)

The TPS1685x responds to output overcurrent conditions during steady-state by performing a circuit-breaker action after a user-adjustable transient fault blanking interval. This action allows the device to support a higher peak current for a short user-defined interval but also provides robust protection in case of persistent output faults.

The device constantly senses the output load current and provides an analog current output ( $I_{IMON}$ ) on the IMON pin which is proportional to the load current, which in turn produces a proportional voltage ( $V_{IMON}$ ) across the IMON pin resistor ( $R_{IMON}$ ) as per Equation 5.

$$V_{IMON} = I_{OUT} \times G_{IMON} \times R_{IMON}$$

(5)

(6)

Where  $G_{IMON}$  is the current monitor gain  $(I_{IMON} : I_{OUT})$

The overcurrent condition is detected by comparing this voltage against the voltage on the IREF pin as a reference. The reference voltage ( $V_{IREF}$ ) can be controlled in two ways, which sets the overcurrent protection threshold ( $I_{OCP}$ ) accordingly.

In the standalone or primary mode of operation, the internal current source interacts with the external IREF pin resistor (R<sub>IREF</sub>) to generate the reference voltage. Driving the IREF pin from an external low impedance reference voltage source is also possible, as shown in Equation 6.

$$V_{IREF} = I_{IREF} \times R_{IREF}$$

In a primary and secondary parallel configuration, the primary eFuse or controller drives the voltage on the IREF pin to provide an external reference (V<sub>IREF</sub>) for all the secondary devices in the chain.

The overcurrent protection threshold during steady-state (I<sub>OCP</sub>) can be calculated using Equation 7.

$$I_{OCP} = \frac{V_{IREF}}{G_{IMON} \times R_{IMON}}$$

(7)

After an overcurrent condition is detected, that is the load current exceeds the user adjustable over current limit threshold ( $I_{OCP}$ ), but stays lower than the short-circuit threshold ( $I_{SFT}$ ), the device starts discharging the ITIMER pin capacitor using an internal pulldown current. If the load current drops below the current limit threshold before the ITIMER capacitor discharges by  $\Delta V_{ITIMER}$ , the ITIMER is reset by pulling up to  $V_{INT}$  internally and the circuit-breaker action is not engaged. This action allows short overload transient pulses to pass through the device without tripping the circuit. If the overcurrent condition persists, the ITIMER capacitor continues to discharge and after the chanrge falls by  $\Delta V_{ITIMER}$ , the circuit-breaker action turns off the FET immediately. At the same time, the ITIMER cap is charged up to  $V_{INT}$  again to the default state before the next overcurrent event. This action verifies that the full blanking timer interval is provided for every overcurrent event. Equation 8 can be used to calculate the R<sub>IMON</sub> value for the desired overcurrent threshold.

$$R_{IMON} = \frac{V_{IREF}}{G_{IMON} \times I_{OCP}}$$

(8)

The duration for which transients are allowed can be adjusted using an appropriate capacitor value from ITIMER pin to ground. The transient overcurrent blanking interval can be calculated using Equation 9.

$$t_{ITIMER}(ms) = \frac{C_{ITIMER}(nF) \times \Delta V_{ITIMER}(V)}{I_{ITIMER}(\mu A)}$$

(9)

### Note

- 1. Leave the ITIMER pin open to allow the part to break the circuit with the minimum possible delay. However, this makes the circuit-breaker response extremely sensitive to noise and can cause false tripping during load transients.

- Shorting the ITIMER pin to ground results in minimum overcurrent response delay (similar to ITIMER pin open condition), but increases the quiescent current – not a recommended mode of operation.

- Increasing the ITIMER cap value extends the overcurrent blanking interval. However, the time needed is also extended for the ITIMER capacitor to recharge up to V<sub>INT</sub> before the next overcurrent event. If the next overcurrent event occurs before the ITIMER cap is recharged fully, discharging to the VITIMER threshold takes less time, thereby providing a shorter blanking interval than intended.

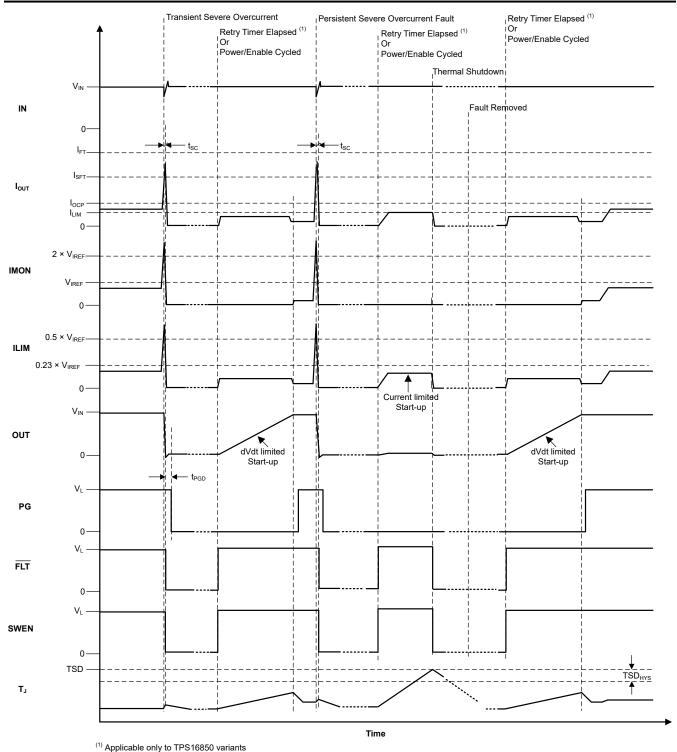

Figure 7-4 illustrates the overcurrent response for TPS1685x eFuse. After the part shuts down due to a circuitbreaker fault, the parts either stays latched off (TPS16851 variant) or restarts automatically after a fixed delay (TPS16850 variant).

TPS1685 SLVSHA1C – SEPTEMBER 2024 – REVISED AUGUST 2025

#### 7.3.4.3 Active Current Limiting During Start-Up

The TPS1685x responds to output overcurrent conditions during start-up by actively limiting the current. The startup current limit is internally fixed to I<sub>start-up</sub>.

When the load current during start-up exceeds I<sub>Start-up</sub>, the device tries to regulate and hold the load current at I<sub>Start-up</sub>.

During current regulation, the output voltage drops, resulting in increased device power dissipation across the FET. If the device internal temperature  $(T_J)$  exceeds the thermal shutdown threshold (TSD), the FET is turned off. After the part shuts down due to a TSD fault, the device either stays latched off (TPS16851 variants) or restarts automatically after a fixed delay (TPS16850 variants). See *Overtemperature protection* section for more details on device response to overtemperature.

#### Note

The active current limit block employs a foldback mechanism during start-up based on the output voltage ( $V_{OUT}$ ). When  $V_{OUT}$  is below the foldback threshold ( $V_{FB}$ ), the current limit threshold is further lowered.

#### 7.3.4.4 Short-Circuit Protection

During a output short-circuit event, the current through the device increases very rapidly. When an output short-circuit is detected, the internal fast-trip comparator triggers a fast protection sequence to prevent the current from building up further and causing any damage or excessive input supply droop. The fast-trip comparator employs a scalable threshold ( $I_{SFT}$ ) during steady-state .  $I_{SFT}$  can be selected by resistor on SFT\_SEL pin. This enables the user to adjust the fast-trip threshold as per system rating, rather than using a high fixed threshold which is not always suitable for all systems. After the current exceeds the fast-trip threshold, the TPS1685x turns off the FET within  $t_{SFT}$ . The device also employs a higher fixed fast-trip threshold ( $I_{FFT}$ ) to provide fast protection against hard short-circuits during steady-state (FET in linear region). After the current exceeds  $I_{FFT}$ , the FET is turned off completely within  $t_{FTT}$ .

| I <sub>SFT_SEL</sub>    | SFT_SEL pin                              | MODE pin |

|-------------------------|------------------------------------------|----------|

| Іос_вкр                 | $R_{SFT\_SEL} < 95k\Omega$               | Open     |

| $2.5 \times I_{OCP}$    | 105kΩ < R <sub>SFT_SEL</sub> < 195kΩ     | Open     |

| 2.8 × I <sub>OCP</sub>  | $105k\Omega < R_{SFT\_SEL} < 195k\Omega$ | Gnd      |

| 2 × I <sub>OCP</sub>    | $205k\Omega < R_{SFT\_SEL} < 295k\Omega$ | Open     |

| 2.26 × I <sub>OCP</sub> | $205k\Omega < R_{SFT\_SEL} < 295k\Omega$ | Gnd      |

| 1.5 × I <sub>OCP</sub>  | $305k\Omega < R_{SFT\_SEL}$              | Open     |

| 1.71 × I <sub>OCP</sub> | $305k\Omega < R_{SFT\_SEL}$              | Gnd      |

| Table 7-1. D | <b>Device Functiona</b> | I Modes Based | on Resistor on | SFT_SEL Pin |

|--------------|-------------------------|---------------|----------------|-------------|

|              |                         |               |                |             |

Figure 7-5 illustrates the short-circuit response for TPS1685x eFuse.

TPS1685 SLVSHA1C – SEPTEMBER 2024 – REVISED AUGUST 2025

### 7.3.5 Analog Load Current Monitor (IMON)

The TPS1685x allows the system to monitor the output load current accurately by providing an analog current on the IMON pin which is proportional to the current through the FET. The benefit of having a current output is that the signal can be routed across a board without adding significant errors due to voltage drop or noise coupling from adjacent traces. The current output also allows the IMON pins of multiple TPS1685x devices to be

Copyright © 2025 Texas Instruments Incorporated

TEXAS INSTRUMENTS www.ti.com

tied together to get the total current in a parallel configuration. The IMON signal can be converted to a voltage by dropping it across a resistor at the point of monitoring. The user can sense the voltage ( $V_{IMON}$ ) across the  $R_{IMON}$  to get a measure of the output load current using Equation 10.

$$I_{OUT} = \frac{V_{IMON}}{G_{IMON} \times R_{IMON}}$$

(10)

The TPS1685x IMON circuit is designed to provide high bandwidth and high accuracy across load and temperature conditions, irrespective of board layout and other system operating conditions. This design allows the IMON signal to be used for advanced dynamic platform power management techniques such as Intel<sup>®</sup> PSYS or PROCHOT# to maximize system power usage and platform throughput without sacrificing safety or reliability.

Figure 7-6. Analog Load Current Monitor Response

#### Note

- 1. The IMON pin provides load current monitoring information only during steady-state. During inrush, the IMON pin reports zero load current.

- 2. The ILIM pin reports the individual device load current at all times and can also be used as an analog load current monitor for each individual device.

- 3. Care must be taken to minimize parasitic capacitance on the IMON and ILIM pins to avoid any impact on the overcurrent and short-circuit protection timing.

### 7.3.6 Mode Selection (MODE)

This pin can be used to configure the TPS1685x as a primary device in a chain along with other TPS1685x eFuses, designated as secondary devices. This feature allows some of the TPS1685x pin functions to be changed to aid the primary and secondary parallel connection.

This pin is sampled at power up. Leaving the pin open configures the pin as a primary or standalone device. Connecting this pin to GND configures the pin as a secondary device.

The following functions are disabled in secondary mode and the device relies on the primary device to provide this functionality:

- 1. IREF internal current source

- 2. DVDT internal current source

- 3. Overcurrent detection in steady-state for circuit-breaker response

- 4. PG de-assertion (pulldown) after reaching steady-state

- 5. Latch-off after fault

In secondary mode, the following functions are still active:

- 1. Overtemperature protection

- 2. Start-up current limit

- 3. Active current sharing during inrush as well as steady-state

- 4. Analog current monitor (IMON) in steady state

- 5. Steady-state overcurrent detection based on IMON. This is indicated by pulling ITIMER pin low internally, but does not trigger circuit-breaker action on ITIMER expiry. Rather, the pin relies on the primary device to start a dedicated ITIMER and then trigger the circuit-breaker action for the whole chain by pulling SWEN low after the ITIMER expiry. However, the secondary devices use an internal overcurrent timer as a backup in case the primary device fails to initiate circuit-breaker action for an extended period of time. Refer to *Single Point Failure Mitigation* section for details.

- 6. Each device still has individual scalable and fixed fast-trip thresholds to protect itself. The individual shortcircuit protection threshold is set to higher values in secondary mode so that the primary device can lower it further for the whole system.

- 7. Individual OVP is set to maximum in secondary device so that the primary can lower individual OVP further for the whole system.

- 8. FLT assertion based on individual device fault detection (except circuit-breaker).

- 9. PG de-assertion control during inrush and assertion control after device reaches steady state. However, after that in steady state, the secondary device no longer controls the de-assertion of the PG in case of faults.

- 10. SWEN assertion or de-assertion based on internal events as well as FET ON and OFF control based on SWEN pin status.

In secondary mode, the device behavior during short-circuit and fast-trip is also altered. More details are available in the *Short-Circuit Protection* section.

#### 7.3.7 Parallel Device Synchronization (SWEN)