Now

**TPD5S115**

SLVSBL2D - OCTOBER 2012 - REVISED JUNE 2017

# TPD5S115 HDMI Companion Chip With Step-Up DC-DC Converter, Level-Shifter, and ESD Clamp

#### 1 Features

- Conforms to HDMI Compliance Tests Without Any **External Components**

- Supports HDMI 2.0, HDMI 1.4, and HDMI 1.3 Standards

- Matches HDMI Connector Pin Mapping

- Internal DC-DC Converter to Generate 5 V From a Battery Voltage as Low as 2.3 V

- Auto-Direction Sensing, Level Shifting, and . Buffering in the CEC, SDA, and SCL Paths

- IEC 61000-4-2 (Level 4) System Level ESD Compliance

- Reverse Current Blocking and Short-Circuit • Protection to Protect Against Fault Conditions

- Industrial Temperature Range: -40°C to 85°C •

#### 2 Applications

- Set-Top Boxes

- TVs

- Smart Phones

- **Digital Camcorders**

- Portable Game Consoles

- **Digital Still Cameras**

# 3 Description

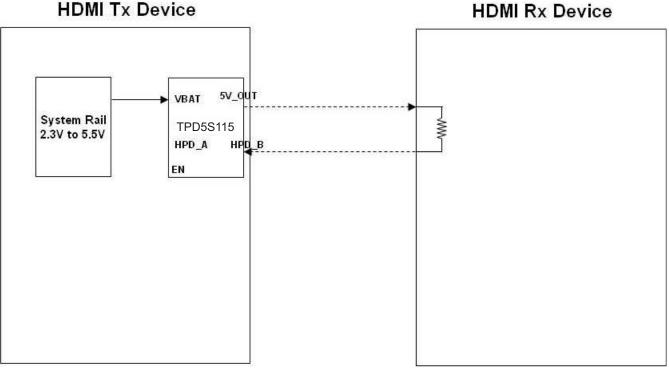

The TPD5S115 device is an integrated HDMI companion chip solution. The device provides a regulated 5-V output (5VOUT) for sourcing the HDMI power line. The regulated 5-V output supplies up to 55 mA to the HDMI receiver with a current limiting function. The TPD5S115 features two control signals: EN and LS\_OE. The control of 5VOUT and the hot plug detect (HPD) circuitry is independent of the LS\_OE control signal and is controlled by the EN pin. The EN pin allows the detection scheme (5VOUT + HPD) to be active before turning on the whole HDMI link. The LS\_OE activates the internal LDO, CEC, SCL, and SDA buffers only when EN is also activated. This dual stage enable scheme ensures optimized power saving for portable applications.

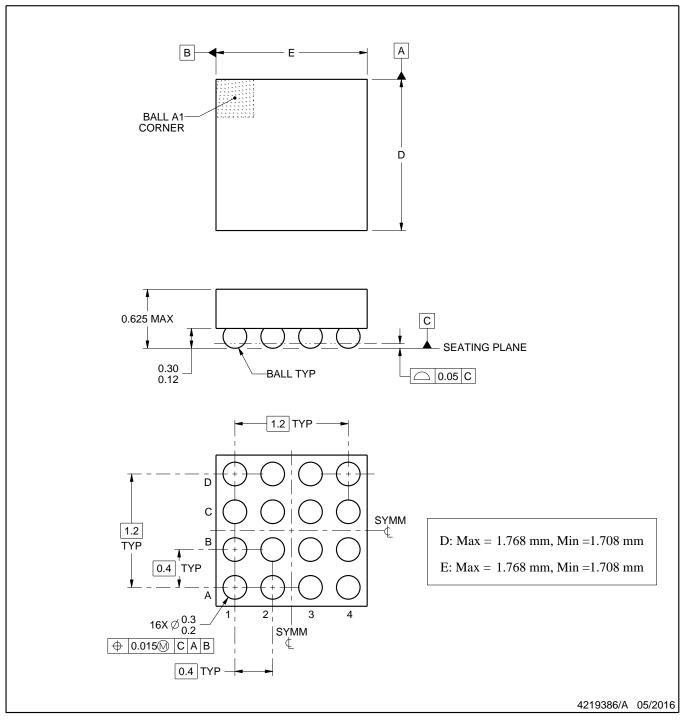

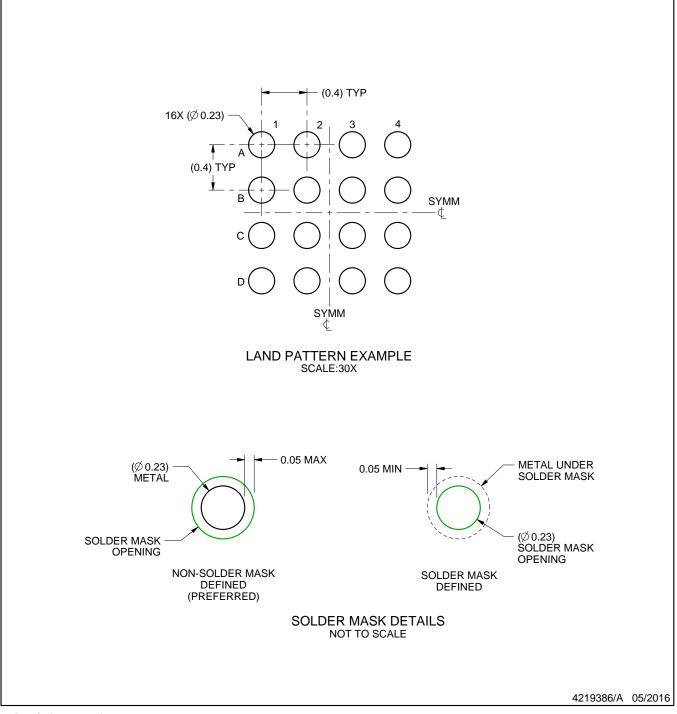

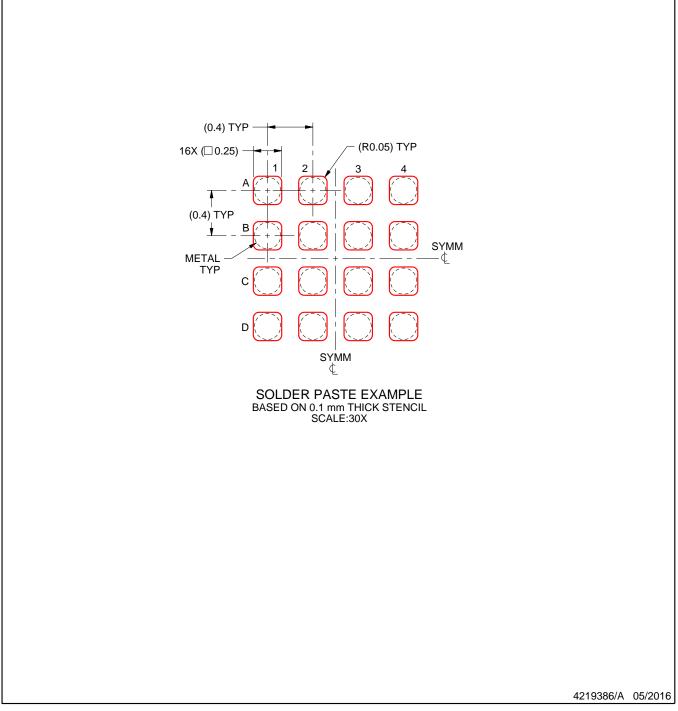

There are three noninverting, bidirectional, voltage level translation circuits for the SDA, SCL, and CEC lines. Each have a common power rail (VCCA) on the A side from 1.1 V to 3.6 V. On the B side, the SCL\_B and SDA B each have an internal 1.75-k $\Omega$  pullup connected to the regulated 5-V rail (5VOUT). The DDC (SCL\_B and SDA\_B) pins meet the I<sup>2</sup>C specification and drive up to 750-pF loads with the buffers. The CEC B pin has an internal  $27 \cdot k\Omega$  pullup to an internal 3.3-V supply. The TPD5S115 exceeds the IEC61000-4-2 (Level 4) ESD protection level. This device features a space saving, 1.72-mm x 1.72-mm, YFF package with 0.4-mm pitch.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TPD5S115    | DSBGA (16) | 1.72 mm × 1.72 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

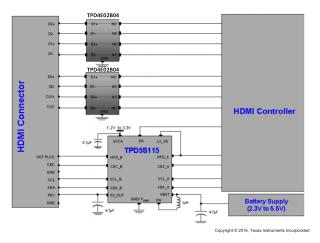

## Typical System Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

2

# Table of Contents

| 1 | Feat  | ures1                                            |

|---|-------|--------------------------------------------------|

| 2 | Appl  | ications1                                        |

| 3 |       | ription 1                                        |

| 4 |       | sion History2                                    |

| 5 | Pin ( | Configuration and Functions                      |

| 6 | Spec  | cifications 4                                    |

|   | 6.1   | Absolute Maximum Ratings 4                       |

|   | 6.2   | ESD Ratings 4                                    |

|   | 6.3   | Recommended Operating Conditions 4               |

|   | 6.4   | Thermal Information 5                            |

|   | 6.5   | Electrical Characteristics5                      |

|   | 6.6   | Electrical Characteristics – I/O Capacitances    |

|   | 6.7   | Switching Characteristics – $V_{CCA}$ = 1.2 V    |

|   | 6.8   | Switching Characteristics – $V_{CCA}$ = 1.5 V    |

|   | 6.9   | Switching Characteristics – $V_{CCA}$ = 1.8 V    |

|   | 6.10  | Switching Characteristics – $V_{CCA}$ = 2.5 V 9  |

|   | 6.11  | Switching Characteristics – $V_{CCA}$ = 3.3 V 10 |

|   | 6.12  | Typical Characteristics 11                       |

| 7 | Deta  | iled Description 13                              |

|   |       |                                                  |

|    | 7.1  | Overview                          | 13 |

|----|------|-----------------------------------|----|

|    | 7.2  | Functional Block Diagram          | 13 |

|    | 7.3  | Feature Description               | 13 |

|    | 7.4  | Device Functional Modes           | 15 |

| 8  | App  | lication and Implementation       | 16 |

|    | 8.1  | Application Information           | 16 |

|    | 8.2  | Typical Applications              | 16 |

| 9  | Pow  | er Supply Recommendations         | 20 |

| 10 | Lay  | out                               | 21 |

|    | 10.1 |                                   |    |

|    | 10.2 | Layout Example                    | 21 |

| 11 | Dev  | ice and Documentation Support     | 22 |

|    | 11.1 | Documentation Support             | 22 |

|    | 11.2 |                                   |    |

|    | 11.3 | Community Resources               | 22 |

|    | 11.4 | -                                 |    |

|    | 11.5 | Electrostatic Discharge Caution   | 22 |

|    | 11.6 | Glossary                          | 22 |

| 12 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | mation                            | 22 |

|    |      |                                   |    |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision C (December 2016) to Revision D | Page |

|---|------------------------------------------------------|------|

| • | Updated Pinout image                                 |      |

#### Changes from Revision B (March 2013) to Revision C

| Ch | nanges from Revision A (February 2013) to Revision B                                                                                                                                                                                                                                                                                                            | Page |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Moved the passive components parameters from <i>Recommended Operating Conditions</i> table to the <i>Output</i><br><i>Capacitor</i> section                                                                                                                                                                                                                     | 18   |

| •  | Added Thermal Information table                                                                                                                                                                                                                                                                                                                                 | 5    |

| •  | Deleted Ordering Information table; see POA at the end of the data sheet                                                                                                                                                                                                                                                                                        | 1    |

| •  | Added Device Information table, Pin Configuration and Functions section, Specifications section, ESD Ratings table,<br>Detailed Description section, Application and Implementation section, Power Supply Recommendations section,<br>Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information<br>section | 1    |

www.ti.com

Page

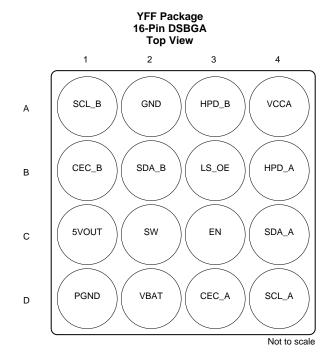

# 5 Pin Configuration and Functions

#### **Pin Functions**

| Р               | IN     | TYPE <sup>(1)</sup> | DECODIDATION                                                                                                                                                                                         |

|-----------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.    | ITPE("              | DESCRIPTION                                                                                                                                                                                          |

| 5VOUT           | C1     | ο                   | DC-DC output. The 5-V power pin can supply a 55-mA regulated current to the HDMI receiver. A separate DC-DC converter control pin (EN) disables the DC-DC converter when operating at low-power mode |

| CEC_A           | D3     | I/O                 | LS system side CEC bus I/O. This pin is bidirectional and referenced to VCCA                                                                                                                         |

| CEC_B           | B1     | I/O                 | LS HDMI connector side CEC bus I/O. This pin is bidirectional and referenced to the 3.3-V internal supply                                                                                            |

| EN              | C3     | С                   | DC-DC enable. Enables the DC-DC converter and HPD circuitry when EN is HIGH. The EN is referenced based off VCCA                                                                                     |

| GND             | A2     | G                   | Device ground                                                                                                                                                                                        |

| HPD_A           | B4     | 0                   | System side output for the hot plug detect. This pin is unidirectional and is referenced to VCCA                                                                                                     |

| HPD_B           | A3     | I                   | HDMI side input for the hot plug detect. This pin is unidirectional and is referenced to 5VOUT                                                                                                       |

| LS_OE           | B3     | С                   | Level shifter enable. This pin is referenced to VCCA. Enables level shifters and LDO when EN is HIGH and LS_OE is HIGH                                                                               |

| PGND            | D1     | G                   | DC-DC converter ground. These pins are isolated from the GND pins. This pin should be tied to system GND                                                                                             |

| SCL_A,<br>SDA_A | D4, C4 | I/O                 | LS system side input and output for I <sup>2</sup> C Bus. These pins are bidirectional and referenced to VCCA                                                                                        |

| SCL_B,<br>SDA_B | A1, B2 | I/O                 | LS HDMI side connector side input and output for I <sup>2</sup> C Bus. These pins are bidirectional and referenced to 5VOUT                                                                          |

| SW              | C2     | I                   | Switch input. This pin is the inductor input for the DC-DC converter                                                                                                                                 |

| VBAT            | D2     | Р                   | Battery supply. This voltage is typically 2.3 V to 5.5 V                                                                                                                                             |

| VCCA            | A4     | Р                   | System side supply. This voltage is typically 1.2 V to 3.3 V from the core microcontroller                                                                                                           |

(1) C = Control, G = Ground, I = Input, O = Output, P = Power

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                                           |                            | MIN  | MAX            | UNIT |

|-------------------------------------------------------------------------------------------|----------------------------|------|----------------|------|

| Current weather a                                                                         | VCCA                       |      | 4              | V    |

| Supply voltage                                                                            | VBAT                       | -0.3 | 6              | V    |

|                                                                                           | SCL_A, SDA_A, CEC_A        | -0.3 | 4              |      |

| Input voltage, V <sub>I</sub> <sup>(2)</sup>                                              | SCL_B, SDA_B, CEC_B, HPD_B | -0.3 | 6              | V    |

|                                                                                           | EN, LS_OE                  | -0.3 | 4              |      |

| Voltage applied to any output in the high-impedance or                                    | SCL_A, SDA_A, CEC_A        | -0.3 | 4              | V    |

| Voltage applied to any output in the high-impedance or power-off state, ${\rm V_O}^{(2)}$ | SCL_B, SDA_B, CEC_B        | -0.3 | 6              | v    |

|                                                                                           | SCL_A, SDA_A, CEC_A        | -0.3 | VCCA + 0.3     |      |

| Voltage applied to any output in the high or low state, $V_0^{(2)}$                       | SCL_B, SDA_B, CEC_B        | -0.3 | 5VOUT +<br>0.3 | V    |

| Input clamp current (IV < 0)                                                              |                            |      | -50            | mA   |

| Output clamp current (V <sub>O</sub> < 0)                                                 |                            |      | -50            | mA   |

| Continuous current through 5VOUT, or GND                                                  |                            |      | ±100           | mA   |

| Storage temperature, T <sub>stg</sub>                                                     |                            | -65  | 150            | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

# 6.2 ESD Ratings

|                    |                         |                                                                      |                                                 | VALUE  | UNIT |

|--------------------|-------------------------|----------------------------------------------------------------------|-------------------------------------------------|--------|------|

|                    |                         | Human-body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins except pins 4A, B3, C3, C4, D3, and D4 | 500    |      |

|                    |                         | ANSI/ESDA/JEDEC 33-001                                               | Pins 4A, B3, C3, C4, D3, and D4                 | 2000   |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JE                                   | DEC specification JESD22-C101 <sup>(2)</sup>    | 1000   | V    |

|                    |                         | IEC 61000-4-2 Contact Discharge                                      | Pins A1, A3, B1, B2, and C1                     | ±14000 |      |

|                    |                         | IEC 61000-4-2 Air-gap Discharge                                      | Pins A1, A3, B1, B2, and C1                     | ±16000 |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                          |                       |              | MIN                                      | NOM   | MAX                            | UNIT |   |

|------------------|--------------------------|-----------------------|--------------|------------------------------------------|-------|--------------------------------|------|---|

| V <sub>CCA</sub> | Supply voltage, VCCA     |                       |              | 1.2                                      |       | 3.6                            | V    |   |

| V <sub>BAT</sub> | Supply voltage, VBAT     |                       |              | 2.3                                      |       | 5.5                            | V    | ] |

|                  |                          |                       | SCL_A, SDA_A | $0.7 \times V_{CCA}$                     |       | $V_{CCA}$                      |      |   |

|                  |                          | VCCA = 1.2 V to 3.6 V | CEC_A        | $0.7 \times V_{CCA}$                     |       | $V_{CCA}$                      |      |   |

|                  |                          |                       | EN, LS_OE    | 1                                        |       | $V_{CCA}$                      |      |   |

| $V_{\text{IH}}$  | High-level input voltage |                       | SCL_B, SDA_B | 0.7 ×<br>5VOUT                           | :     | 5VOUT                          | V    |   |

|                  |                          | 5VOUT = 5 V           | CEC_B        | 0.7 × 3.3 V<br>(internal) <sup>(1)</sup> | (inte | 3.3 V<br>ernal) <sup>(1)</sup> |      |   |

|                  |                          |                       | HPD_B        | 2                                        |       |                                |      |   |

3.3 V (internal) is an internally generated voltage node for the CEC\_B output buffer supply reference. An LDO generates this 3.3 V from 5VOUT when LS\_OE and EN are HIGH.

# **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                    |                                     |                                          |              | MIN  | NOM MAX                                | UNIT |

|--------------------|-------------------------------------|------------------------------------------|--------------|------|----------------------------------------|------|

|                    |                                     |                                          | SCL_A, SDA_A | -0.5 | $0.082 \times V_{CCA}$                 |      |

|                    |                                     | VCCA = 1.2 V to 3.6 V                    | CEC_A        | -0.5 | $0.082 \times V_{CCA}$                 |      |

|                    |                                     |                                          | EN, LS_OE    | -0.5 | 0.4                                    |      |

| V <sub>IL</sub>    | Low-Level input voltage             |                                          | SCL_B, SDA_B | -0.5 | 0.3 × 5VOUT                            | V    |

|                    |                                     | 5VOUT = 5 V                              | CEC_B        | -0.5 | 0.3 × 3.3<br>(internal) <sup>(1)</sup> |      |

|                    |                                     |                                          | HPD_B        | 0    | 0.8                                    |      |

| V <sub>ILC</sub>   | Low-level input voltage             |                                          |              | -0.5 | $0.065 \times V_{CCA}$                 | V    |

| $V_{OL} - V_{ILC}$ | Delta between V <sub>OL</sub> and V | <sub>ILC</sub> (V <sub>IO</sub> = 2.5 V) |              | 0.   | 1 × V <sub>CCA</sub>                   | V    |

| T <sub>A</sub>     | Operating free-air temper           | ature                                    |              | -40  | 85                                     | °C   |

## 6.4 Thermal Information

|                       |                                              | TPD5S115    |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                       |                                              | 16 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 78.2        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.6         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 13.2        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 2.5         | °C/W |

| ΨJB                   | Junction-to-board characterization parameter | 13          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

| $T_A = -40^{\circ}C$ to 85°C (unless otherwise noted) |

|-------------------------------------------------------|

|-------------------------------------------------------|

|                                  | PARAMETER                                                      |                                | TEST CONDITIONS                                                                             | MIN                  | TYP                     | MAX | UNIT       |

|----------------------------------|----------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------|----------------------|-------------------------|-----|------------|

| V <sub>OHA</sub>                 |                                                                |                                | $I_{OH} = -10 \ \mu\text{A}, \ V_I = V_{IH}, \ V_{CCA} = 1.2 \ V \ to \ 3.6 \ V$            | $V_{CCA} \times 0.8$ |                         |     | V          |

| V <sub>OLA</sub>                 |                                                                |                                | $I_{OL}$ = 10 µA, $V_I$ = $V_{IL}$ , $V_{CCA}$ = 1.2 V to 3.6 V                             |                      | V <sub>CCA</sub> × 0.16 |     | V          |

| V <sub>OHB</sub>                 |                                                                |                                | $I_{OH} = -10 \ \mu A, \ V_I = V_{IH}$                                                      |                      |                         |     | V          |

| V <sub>OLB</sub>                 |                                                                |                                | $I_{OL} = 3 \text{ mA}, V_I = V_{IL}$                                                       |                      |                         | 0.4 | V          |

| D                                | SCL A, SDA A                                                   |                                | Pullup connected to VCCA rail                                                               |                      | 10                      |     | ko         |

| R <sub>PU</sub>                  | internal pullup                                                | SCL_B, SDA_B                   | Pullup connected to 5-V rail                                                                |                      | 1.75                    |     | kΩ         |

| I <sub>PULLUPAC</sub>            | Transient boosted<br>pullup current<br>(rise-time accelerator) | SCL_B, SDA_B                   | Pullup connected to 5-V rail                                                                |                      | 15                      |     | mA         |

|                                  |                                                                | A port                         | VCCA = 0 V, V <sub>I</sub> or V <sub>O</sub> = 0 to 3.6 V, V <sub>CCA</sub> = 0 V           |                      |                         | ±5  |            |

| I <sub>OFF</sub> Leakage current |                                                                | B port                         | 5VOUT = 0 V, V <sub>1</sub> or V <sub>0</sub> = 0 to 5.5 V, V <sub>CCA</sub> = 0 V to 3.6 V |                      |                         | ±5  | μA         |

|                                  |                                                                | A port                         | $V_{O} = V_{CCO}$ or GND, $V_{CCA} = 1.2$ V to 3.6 V                                        |                      |                         | ±5  |            |

| l <sub>oz</sub>                  |                                                                | B port                         | $V_I = V_{CCI}$ or GND, $V_{CCA} = 1.2$ V to 3.6 V                                          |                      |                         | ±5  |            |

| 0                                | Due load conseitence                                           | A port                         |                                                                                             |                      |                         | 15  | ~ <b>F</b> |

| CL                               | Bus load capacitance                                           | B port                         |                                                                                             |                      |                         | 750 | pF         |

| SUPPLY C                         | CURRENT                                                        | ·                              |                                                                                             |                      |                         |     |            |

|                                  |                                                                | Standby                        | I/Os = HIGH                                                                                 |                      |                         | 2   | μA         |

| I <sub>CCA</sub>                 | VCCA supply current                                            | Active                         | I/Os = HIGH                                                                                 |                      |                         | 15  | μA         |

|                                  |                                                                | Standby                        | EN = LOW, LS_OE = LOW                                                                       |                      | 0.5                     |     | μA         |

| I <sub>CCB</sub>                 | VBAT supply current                                            | DC-DC and<br>HPD active        | EN = HIGH, LS_OE = LOW                                                                      |                      | 30                      | 50  | μA         |

|                                  |                                                                | DC-DC, HPD,<br>DDC, CEC Active | EN = HIGH, LS_OE = LOW, I/Os = HIGH                                                         |                      | 225                     | 300 | μA         |

Copyright © 2012–2017, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

$T_A = -40^{\circ}C$  to 85°C (unless otherwise noted)

|                        | PARAMETER               | R                           | TEST CONDITIONS                                                                             | MIN                  | TYP                   | MAX  | UNIT             |

|------------------------|-------------------------|-----------------------------|---------------------------------------------------------------------------------------------|----------------------|-----------------------|------|------------------|

| DC-DC CO               | ONVERTER                |                             |                                                                                             |                      |                       |      |                  |

| V <sub>BAT</sub>       | Input voltage           |                             |                                                                                             | 2.3                  |                       | 5.5  | V                |

| V <sub>OUT</sub>       | Total DC output volta   | ige <sup>(1)</sup>          |                                                                                             | 4.9                  | 5                     | 5.13 | V                |

| T <sub>OVA</sub>       | Total output voltage a  | accuracy <sup>(2)</sup>     |                                                                                             | 4.8                  | 5                     | 5.3  | V                |

| V                      | Output voltage ripple   | loodod                      | I <sub>O</sub> = 65 mA                                                                      |                      | 50.6                  |      | m\/              |

| V <sub>IO_Ripple</sub> | Output voltage hpple    | , loaded                    | I <sub>O</sub> = 150 mA                                                                     |                      | 16                    |      | mV <sub>PP</sub> |

| f <sub>CLK</sub>       | Internal operating free | quency                      | $V_{BAT}$ = 2.3 V to 5.5 V                                                                  |                      | 3.5                   |      | MHz              |

| t <sub>START</sub>     | Start-up time           |                             | From EN input to 5-V power output 90% point                                                 |                      | 187                   |      | μs               |

|                        | Output current          |                             | $V_{BAT}$ = 2.3 V to 5.5 V                                                                  | 55                   |                       |      | mA               |

| I <sub>O</sub>         | Reverse leakage cur     | rent, V <sub>O</sub>        | $EN = LOW, V_0 = 5.5 V$                                                                     |                      |                       | 2.5  | μA               |

|                        | Leakage current from    | h battery to V <sub>O</sub> | EN = LOW                                                                                    |                      |                       | 5    | μA               |

|                        |                         | the second second           | Falling                                                                                     |                      | 2                     |      | V                |

| V <sub>BATUV</sub>     | Undervoltage lockout    | Intestioid                  | Rising                                                                                      |                      | 2.1                   |      | V                |

|                        | Line transient respon   | se                          | $V_{BAT}$ = 3.4 V, $I_{O}$ = 20 mA to 65 mA, A 217 Hz, 600 mV_{PP} square wave pulse        |                      | 17.1                  |      | $mV_{pk}$        |

|                        | Load transient respor   | nse                         | $V_{BAT}$ = 3.4 V, $I_{O}$ = 5 mA to 65 mA, 10-µs pulse, $t_{RISE}$ = $t_{FALL}$ = 0.1 µs   |                      | 63.5                  |      | $mV_{pk}$        |

| IINRUSH                | Inrush current, average | ge over t <sub>START</sub>  | V <sub>BAT</sub> = 2.3 V to 5.5 V, I <sub>OUT</sub> = 65 mA                                 |                      | 168                   |      | mA               |

| I <sub>SC</sub>        | Short-circuit current l | imit from output            |                                                                                             |                      | 90                    |      | mA               |

| VOLTAGE                | E LEVEL SHIFTER CEC     | CLINE (x_A & x_B            | PORTS)                                                                                      |                      |                       |      |                  |

| V <sub>OHA</sub>       |                         |                             | $I_{OH}$ = -10 µA, $V_I$ = $V_{IH}$ , $V_{CCA}$ = 1.2 V to 3.6 V                            | $V_{CCA} \times 0.8$ |                       |      | V                |

| V <sub>OLA</sub>       |                         |                             | $I_{OL} = 10 \ \mu A, \ V_I = V_{IL}, \ V_{CCA} = 1.2 \ V \ to \ 3.6 \ V$                   | V                    | <sub>CCA</sub> × 0.16 |      | V                |

| V <sub>OHB</sub>       |                         |                             | $I_{OH} = -20 \ \mu A, \ V_I = V_{IH}$                                                      | $V_{CCA} \times 0.8$ |                       |      | V                |

| V <sub>OLB</sub>       |                         |                             | $I_{OL} = 3 \text{ mA}, V_I = V_{IL}$                                                       |                      |                       | 0.4  | V                |

| 5                      |                         | CEC_A                       | Pullup connected to V <sub>CCA</sub> rail                                                   |                      | 10                    |      | 10               |

| R <sub>PU</sub>        | Internal pullup         | CEC_B                       | Pullup connected to 3.3 V rail                                                              | 22                   | 26                    | 30   | kΩ               |

| R <sub>PD</sub>        | Internal pulldown       | CEC_B                       | Pullup connected to GND                                                                     |                      | 14                    |      | MΩ               |

|                        |                         | A port                      | VCCA = 0 V, V <sub>I</sub> or V <sub>O</sub> = 0 to 3.6 V, V <sub>CCA</sub> = 0 V           |                      |                       | ±5   |                  |

| I <sub>OFF</sub>       |                         | B port                      | 5VOUT = 0 V, V <sub>I</sub> or V <sub>O</sub> = 0 to 5.5 V, V <sub>CCA</sub> = 0 V to 3.6 V |                      |                       | ±1.8 | μA               |

|                        |                         | A port                      | $V_{O} = V_{CCO}$ or GND, $V_{CCA} = 1.2$ V to 3.6 V                                        |                      |                       | ±5   | r                |

| I <sub>OZ</sub>        |                         | B port                      | $V_I = V_{CCI}$ or GND, $V_{CCA} = 1.2$ V to 3.6 V                                          |                      |                       | ±5   |                  |

| VOLTAGE                | E LEVEL SHIFTER - HP    | D LINE (X_A & x_            |                                                                                             | L                    |                       |      |                  |

| V <sub>OHA</sub>       |                         |                             | $I_{OH} = -3$ mA, $V_I = V_{IH}$ , $V_{CCA} = 1.2$ V to 3.6 V                               | $V_{CCA} \times 0.7$ |                       |      | V                |

| V <sub>OLA</sub>       |                         |                             | $I_{OL}$ = 3 mA, $V_I$ = $V_{IL}$ , $V_{CCA}$ = 1.2 V to 3.6 V                              |                      |                       | 0.4  | V                |

| R <sub>PD</sub>        | Internal pulldown       | HPD_B                       | Pullup connected to GND                                                                     |                      | 100                   |      | kΩ               |

| I <sub>OZ</sub>        |                         | A port                      | $V_{I} = V_{CCI}$ or GND, $V_{CCA} = 3.6$ V                                                 |                      |                       | ±5   | μA               |

| LS_OE, E               | N                       |                             |                                                                                             |                      |                       |      |                  |

| l <sub>l</sub>         |                         |                             | $V_I = V_{CCA}$ or GND, $V_{CCA} = 1.2$ V to 3.6 V                                          |                      |                       | ±12  |                  |

(1) Includes voltage references, DC load and line regulations, process and temperature.

(2) Includes voltage references, DC load and line regulations, transient load and line regulations, ripple, process, and temperature.

# 6.6 Electrical Characteristics – I/O Capacitances

over operating free-air temperature range (unless otherwise noted)

|             | PARAMETER           | TES                                                                    | T CONDITIONS                                                               | MIN | TYP | MAX | UNIT |

|-------------|---------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

|             | EN, LS_OE           |                                                                        | $V_{CCA} = 3.6 \text{ V}, \text{ V}_{BAT} = 5 \text{ V}$                   |     | 7.1 | 9.5 | pF   |

|             | SCL_A, SDA_A, CEC_A | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz,<br>30-mV <sub>PP</sub> AC signal | $V_{CCA} = 3.6 \text{ V}, \text{ V}_{BAT} = 5 \text{ V}, \text{ EN} = LOW$ |     | 7   |     | pF   |

|             | HPD_A, HPD_B        |                                                                        | $V_{CCA}$ = 3.6 V, $V_{BAT}$ = 5 V, EN = LOW                               |     | 4   |     | pF   |

| Capacitance | SCL_B, SDA_B        | $V_{BIAS}$ = 2.5 V, f = 100 kHz,<br>3.5-V <sub>PP</sub> AC signal      | $V_{\rm CCA}$ = 3.6 V, $V_{\rm BAT}$ = 5 V, EN = LOW, LS_OE = HIGH         |     | 10  |     | pF   |

|             | CEC_B               | $V_{BIAS} = 1.65 \text{ V}, \text{ f} = 100 \text{ kHz},$              | $V_{CCA}$ = 3.6 V, $V_{BAT}$ = 5 V, EN = LOW, LS_OE = HIGH                 |     | 7   |     | pF   |

|             | CEC_B               | 2.5-V <sub>PP</sub> AC signal                                          | V <sub>CCA</sub> = 0 V, 5V_IN = 0 V                                        |     | 7   |     | pF   |

# 6.7 Switching Characteristics – $V_{CCA}$ = 1.2 V

|                   | PARAMETER                      |        | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|-------------------|--------------------------------|--------|----------------------|-----|------|-----|------|

| SCL an            | d SDA LINES (x_A & x_B PORTS)  |        |                      |     |      |     |      |

|                   | Lligh to low propagation dolow | A to B | DDC channels enabled |     | 394  |     | 20   |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | DDC channels enabled |     | 347  |     | ns   |

|                   | Low to birth managedian datas  | A to B | DDC channels enabled |     | 504  |     |      |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | DDC channels enabled |     | 171  |     | ns   |

|                   |                                | A port | DDC channels enabled |     | 146  |     | 20   |

| t <sub>FALL</sub> | Fall time                      | B port | DCC channels enabled |     | 135  |     | ns   |

|                   |                                | A port | DCC channels enabled |     | 190  |     |      |

| t <sub>RISE</sub> | Rise time                      | B port | DCC channels enabled |     | 93   |     | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency    |        | DCC channels enabled | 400 |      |     | kHz  |

|                   | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

|                   |                                | A to B | CEC channels enabled |     | 550  |     |      |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 350  |     | ns   |

|                   | Low to high more action delay. | A to B | CEC channels enabled |     | 13   |     | μs   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 290  |     | ns   |

|                   |                                | A port | CEC channels enabled |     | 146  |     |      |

| t <sub>FALL</sub> | Fall time                      | B port | CEC channels enabled |     | 200  |     | ns   |

|                   |                                | A port | CEC channels enabled |     | 190  |     | ns   |

| t <sub>RISE</sub> | Rise time                      | B port | CEC channels enabled |     | 16.4 |     | μs   |

| HPD LII           | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

| t <sub>PHL</sub>  | Propagation delay              | B to A | CEC channels enabled |     | 10.4 |     | ns   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 9.9  |     | ns   |

| t <sub>FALL</sub> | Fall time                      | A port | CEC channels enabled |     | 0.7  |     | ns   |

| t <sub>RISE</sub> | Rise time                      | A port | CEC channels enabled |     | 0.8  |     | ns   |

SLVSBL2D -OCTOBER 2012-REVISED JUNE 2017

www.ti.com

# 6.8 Switching Characteristics – $V_{CCA}$ = 1.5 V

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                      |        | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|-------------------|--------------------------------|--------|----------------------|-----|------|-----|------|

| SCL, SI           | DA LINES (x_A & x_B PORTS)     |        |                      | 1   |      |     |      |

|                   | Ligh to low propagation dology | A to B | DDC channels enabled |     | 375  |     | 20   |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | DDC channels enabled |     | 272  |     | ns   |

|                   | Low to bisk supportion dates   | A to B | DDC channels enabled |     | 488  |     |      |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | DDC channels enabled |     | 166  |     | ns   |

|                   |                                | A port | DDC channels enabled |     | 114  |     |      |

| t <sub>FALL</sub> | Fall time                      | B port | DCC channels enabled |     | 135  |     | ns   |

|                   | Disc the                       | A port | DCC channels enabled |     | 186  |     |      |

| t <sub>RISE</sub> | Rise time                      | B port | DCC channels enabled |     | 93   |     | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency    |        | DCC channels enabled | 400 |      |     | kHz  |

| CEC Li            | ne (x_A & x_B Ports)           |        |                      |     |      |     |      |

|                   | High-to-low propagation delay  | A to B | CEC channels enabled |     | 536  |     | 20   |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 272  |     | ns   |

|                   | Low to bisk supportion dates   | A to B | CEC channels enabled |     | 13   |     | μs   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 285  |     | ns   |

|                   |                                | A port | CEC channels enabled |     | 113  |     |      |

| t <sub>FALL</sub> | Fall time                      | B port | CEC channels enabled |     | 201  |     | ns   |

|                   |                                | A port | CEC channels enabled |     | 187  |     | ns   |

| t <sub>RISE</sub> | Rise time                      | B port | CEC channels enabled |     | 16   |     | μs   |

| HPD LI            | NE (x_A & x_B PORTS)           |        |                      | 1   |      |     |      |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>FALL</sub> | Fall time                      | A port | CEC channels enabled |     | 0.46 |     | ns   |

| t <sub>RISE</sub> | Rise time                      | A port | CEC channels enabled |     | 0.5  |     | ns   |

# 6.9 Switching Characteristics – $V_{CCA}$ = 1.8 V

|                   | PARAMETER                                |        | TEST CONDITIONS      | MIN | ТҮР | MAX | UNIT |

|-------------------|------------------------------------------|--------|----------------------|-----|-----|-----|------|

| SCL, S            | DA LINES (x_A & x_B PORTS)               |        | •                    |     |     |     |      |

|                   | Llich to low propagation dology          | A to B | DDC channels enabled |     | 370 |     | ~~   |

| t <sub>PHL</sub>  | PHL High-to-low propagation delay        |        | DDC channels enabled |     | 230 |     | ns   |

|                   | Low to high propagation dolog            | A to B | DDC channels enabled |     | 480 |     | ~~   |

| t <sub>PLH</sub>  | Low-to-high propagation delay            | B to A | DDC channels enabled |     | 163 |     | ns   |

|                   |                                          | A port | DDC channels enabled |     | 100 |     |      |

| t <sub>FALL</sub> | Fall time                                | B port | DCC channels enabled |     | 135 |     | ns   |

| t Diss time       |                                          | A port | DCC channels enabled |     | 180 |     |      |

| t <sub>RISE</sub> | Rise time                                | B port | DCC channels enabled |     | 93  |     | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency              |        | DCC channels enabled | 400 |     |     | kHz  |

| CEC LI            | NE (x_A & x_B PORTS)                     |        | •                    | •   |     |     |      |

|                   |                                          | A to B | CEC channels enabled |     | 530 |     |      |

| t <sub>PHL</sub>  | High-to-low propagation delay            | B to A | CEC channels enabled |     | 230 |     | ns   |

|                   | Louise kick menopotion delay             | A to B | CEC channels enabled |     | 13  |     | μs   |

| t <sub>PLH</sub>  | PLH Low-to-high propagation delay B to A |        | CEC channels enabled |     | 280 |     | ns   |

|                   |                                          | A port | CEC channels enabled | 98  |     |     |      |

| t <sub>FALL</sub> | Fall time                                | B port | CEC channels enabled |     | 200 |     | ns   |

# Switching Characteristics – $V_{CCA}$ = 1.8 V (continued)

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                     |        | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|-------------------|-------------------------------|--------|----------------------|-----|------|-----|------|

|                   | Rise time                     | A port | CEC channels enabled |     | 180  |     | ns   |

| t <sub>RISE</sub> | Rise une                      | B port | CEC channels enabled |     | 16   |     | μs   |

| HPD LI            | NE (x_A & x_B PORTS)          |        |                      |     |      | ·   |      |

| t <sub>PHL</sub>  | High-to-low propagation delay | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>PLH</sub>  | Low-to-high propagation delay | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>FALL</sub> | Fall time                     | A port | CEC channels enabled |     | 0.41 |     | ns   |

| t <sub>RISE</sub> | Rise time                     | A port | CEC channels enabled |     | 0.41 |     | ns   |

# 6.10 Switching Characteristics – V<sub>CCA</sub> = 2.5 V

|                   | PARAMETER                      |        | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|-------------------|--------------------------------|--------|----------------------|-----|------|-----|------|

| SCL, SI           | DA LINES (x_A & x_B PORTS)     |        |                      |     |      | ·   |      |

|                   | Llich to low propagation dolow | A to B | DDC channels enabled |     | 370  |     | ~~~  |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | DDC channels enabled |     | 185  |     | ns   |

|                   | Low to bisk supportion delay   | A to B | DDC channels enabled |     | 467  |     |      |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | DDC channels enabled |     | 160  |     | ns   |

|                   |                                | A port | DDC channels enabled |     | 80   | _   |      |

| t <sub>FALL</sub> | Fall time                      | B port | DCC channels enabled |     | 135  |     | ns   |

|                   | Diag time                      | A port | DCC channels enabled |     | 179  |     | ~~~  |

| t <sub>RISE</sub> | Rise time                      | B port | DCC channels enabled |     | 93   |     | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency    |        | DCC channels enabled | 400 |      |     | kHz  |

| CEC LI            | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

|                   | High-to-low propagation delay  | A to B | CEC channels enabled |     | 530  |     | ~~~  |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 185  |     | ns   |

|                   | Low to high propagation dology | A to B | CEC channels enabled |     | 13   |     | μs   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 275  |     | ns   |

|                   | Fall time                      | A port | CEC channels enabled |     | 80   |     |      |

| t <sub>FALL</sub> | Fairume                        | B port | CEC channels enabled |     | 200  |     | ns   |

|                   | Rise time                      | A port | CEC channels enabled |     | 180  |     | ns   |

| t <sub>RISE</sub> | Rise une                       | B port | CEC channels enabled |     | 16   |     | μs   |

| HPD LI            | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>FALL</sub> | Fall time                      | A port | CEC channels enabled |     | 0.35 |     | ns   |

| t <sub>RISE</sub> | Rise time                      | A port | CEC channels enabled |     | 0.35 |     | ns   |

SLVSBL2D-OCTOBER 2012-REVISED JUNE 2017

www.ti.com

# 6.11 Switching Characteristics – $V_{CCA} = 3.3 V$

|                   | PARAMETER                      |        | TEST CONDITIONS      | MIN | TYP  | MAX | UNIT |

|-------------------|--------------------------------|--------|----------------------|-----|------|-----|------|

| SCL, SI           | DA LINES (x_A & x_B PORTS)     |        |                      |     |      |     |      |

|                   | Llich to low propagation dolou | A to B | DDC channels enabled |     | 370  |     | 20   |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | DDC channels enabled |     | 160  |     | ns   |

|                   | Low to bisk supportion dates   | A to B | DDC channels enabled |     | 460  |     |      |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | DDC channels enabled |     | 155  |     | ns   |

|                   |                                | A port | DDC channels enabled |     | 75   |     |      |

| t <sub>FALL</sub> | Fall time                      | B port | DCC channels enabled |     | 135  |     | ns   |

|                   |                                | A port | DCC channels enabled |     | 180  |     |      |

| t <sub>RISE</sub> | Rise time                      | B port | DCC channels enabled |     | 93   |     | ns   |

| f <sub>MAX</sub>  | Maximum switching frequency    | ÷      | DCC channels enabled | 400 |      |     | kHz  |

| CEC LI            | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

|                   | High-to-low propagation delay  | A to B | CEC channels enabled |     | 530  |     | 20   |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 160  |     | ns   |

|                   | Low to bisk supportion dates   | A to B | CEC channels enabled |     | 13   |     | μs   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 275  |     | ns   |

|                   | Fall time                      | A port | CEC channels enabled |     | 73   |     | 20   |

| t <sub>FALL</sub> | Fairume                        | B port | CEC channels enabled |     | 200  |     | ns   |

|                   |                                | A port | CEC channels enabled |     | 180  |     | ns   |

| t <sub>RISE</sub> | Rise time                      | B port | CEC channels enabled |     | 16   |     | μs   |

| HPD LI            | NE (x_A & x_B PORTS)           |        |                      |     |      |     |      |

| t <sub>PHL</sub>  | High-to-low propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>PLH</sub>  | Low-to-high propagation delay  | B to A | CEC channels enabled |     | 10   |     | ns   |

| t <sub>FALL</sub> | Fall time                      | A port | CEC channels enabled |     | 0.34 |     | ns   |

| t <sub>RISE</sub> | Rise time                      | A port | CEC channels enabled |     | 0.36 |     | ns   |

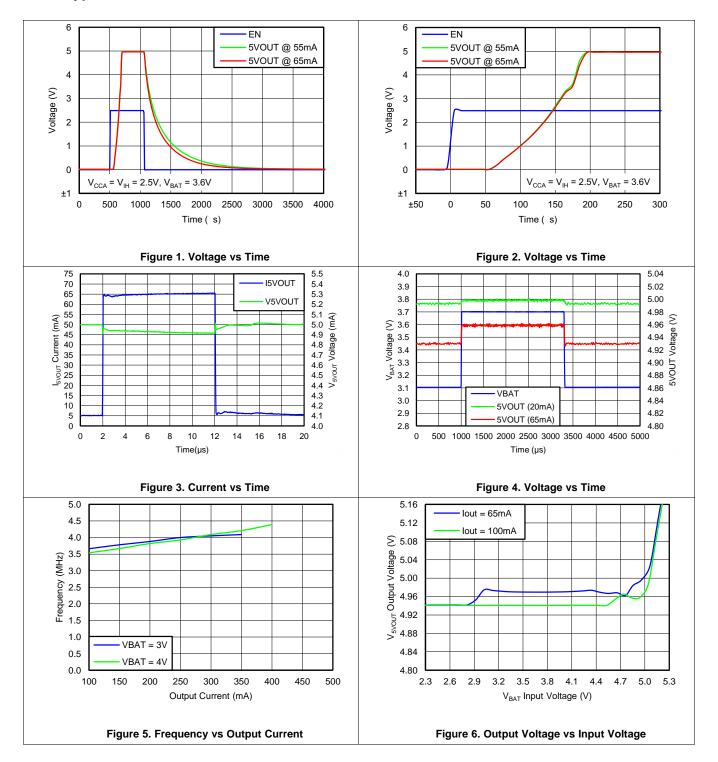

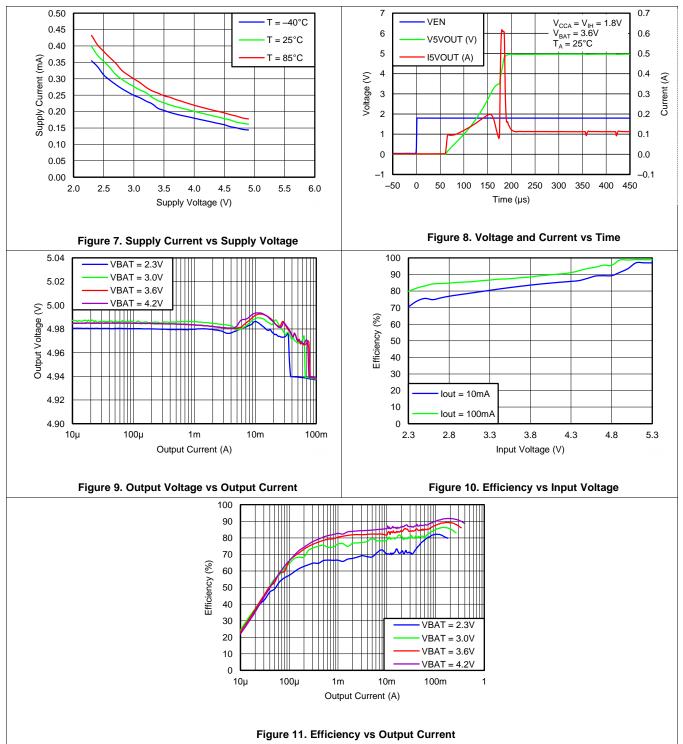

#### 6.12 Typical Characteristics

### **Typical Characteristics (continued)**

### 7 Detailed Description

#### 7.1 Overview

The TPD5S115 is an integrated interface solution that covers HDMI versions' 2.0, 1.4, and 1.3 need for power supply voltage management and control line level translation. On the power supply line, it has a DC-DC converter that takes the internal power supply from 2.3 V to 5.5 V, and outputs a regulated and current-limited, 5-V voltage to the connector. The drivers support level translation on HPD, ECE, SCL, and SDA lines in both transmission directions. Moreover, the rise-time acceleration feature helps drive the high capacitive load on the cable side. Every channel comes with robust ESD protection with ±14-kV contact and ±16-kV air-gap IEC61000-4-2 capability.

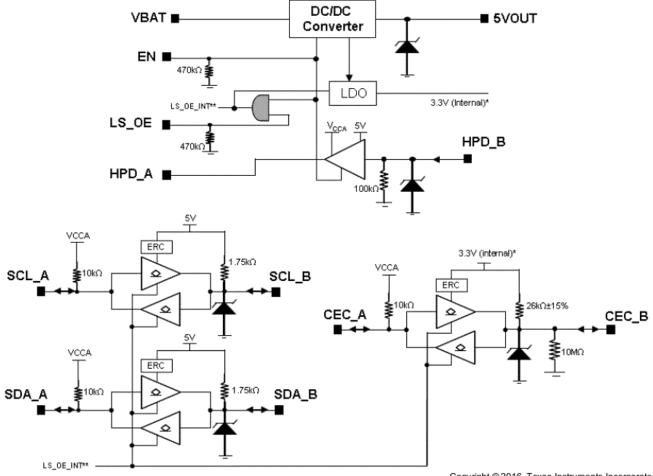

#### 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

- (1) 3.3 V (internal) is an internal 3.3-V supply rail which is generated from 5VOUT when EN and LS\_OE are HIGH.

- (2) LS\_OE\_INT is an internal control signal generated from EN and LS\_OE signals. LS\_OE\_INT is active when both EN and LS\_OE are HIGH.

### 7.3 Feature Description

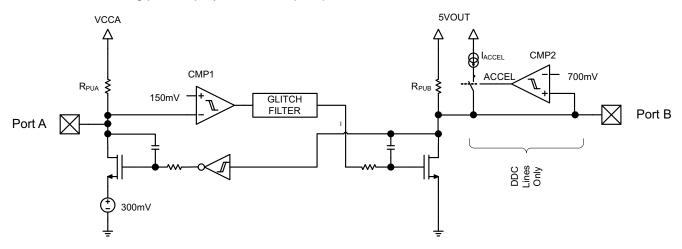

#### 7.3.1 Rise-Time Accelerators

The HDMI cable side of the DDC lines incorporates rise-time accelerators to support the high capacitive load on the HDMI cable side. The rise-time accelerator boosts the cable-side DDC signal, independent of which side of the bus is releasing the signal.

Copyright © 2012–2017, Texas Instruments Incorporated

### Feature Description (continued)

Copyright © 2016, Texas Instruments Incorporated

Figure 12. Receiving and Transmitting Interaction

#### 7.3.2 Hot Plug Detect

After the TPD5S115's DC-DC converter and HPD block are enabled through the EN pin, the TPD5S115 is ready for continual HDMI receiver detection. After a HDMI cable connects a receiving and transmitting device together, the 5-V signal from the DC-DC output flows through the receiving device's internal resistor and into HPD's input. The HPD buffer's output then goes high, indicating to the transmitter that a receiving device is connected. To save power, periodic detection can be done by turning on and off the DC-DC converter before a receiving device is connected.

#### NOTE

Ground offset between the TPD5S115 ground and the ground of devices on port A of the TPD5S115 must be avoided. A CMOS or NMOS open-drain capable of sinking 3 mA of current at 0.4 V has an output resistance of 133  $\Omega$  or less (R = E / I). Such a driver shares enough current with the port A output pulldown of the TPD5S115 to be detected as a LOW while the ground offset is zero. If the ground offset is greater than 0 V, then the driver resistance must be less. Because V<sub>ILC</sub> can be as low as 90 mV at cold temperatures and the low end of the current distribution, the maximum ground offset should not exceed 50 mV. Bus repeaters that use an output offset are not interoperable with the port A of the TPD5S115 as their output LOW levels are not recognized by the TPD5S115 as a LOW. If the TPD5S115 is placed in an application where the V<sub>IL</sub> of port A of the TPD5S115 does not go below its V<sub>ILC</sub> it will pull port B LOW initially when port A input transitions LOW but the port B will return HIGH, so it does not reproduce the port A input on port B. Such applications must be avoided. Port B is interoperable with all I<sup>2</sup>C-bus slaves, masters, and repeaters.

#### 7.3.3 CEC Level Shift Operation

The CEC level shift function operates in the same manner as the DDC lines except that the CEC line does not need the rise time accelerator function.

#### 7.3.4 Pullup Resistor

The system is designed to work properly with no external pullup resistors on the DDC, CEC, and HPD lines.

#### 7.3.5 Undervoltage Lockout

The undervoltage-lockout circuit prevents the DC-DC converter from malfunctioning at low input voltages and from excessive discharge of the battery. It disables the output stage of the converter once the falling  $V_{IN}$  trips the undervoltage-lockout threshold ( $V_{BATUV}$ ). The undervoltage-lockout threshold for falling  $V_{IN}$  is typically 2 V. The device starts operation once the rising  $V_{IN}$  trips the under-voltage-lockout threshold again at 2.1 V (typical).

#### 7.3.6 Soft Start

The DC-DC converter has an internal soft-start circuit that controls the ramp-up of the output voltage. The output voltage reaches its nominal value within 250  $\mu$ s (typical) after EN has been pulled high. The output voltage ramps up from 5% to its nominal value within 300  $\mu$ s (typical). This limits the in-rush current in the converter during start-up and prevents possible input voltage drops when a battery or high impedance power source is used. During soft start, the switch current limit is reduced to 300 mA until the output voltage reaches V<sub>IN</sub>. Once the output voltage trips this threshold, the device operates with its nominal current limit.

#### 7.4 Device Functional Modes

#### 7.4.1 Power-Save Mode

The TPD5S115 integrates a power-save mode to improve efficiency at light loads. In power-save mode, the converter only operates when the output voltage trips below a set threshold voltage. It ramps up the output voltage with several pulses and goes into power-save mode once the output voltage exceeds the set threshold voltage. The PFM mode is ended and PWM mode begins in case the output current can no longer be supported in PFM mode.

#### 7.4.2 Enable

The DC-DC converter is enabled when the EN is set to high. At first, the internal reference is activated and the internal analog circuits are settled. Afterwards, the soft start is activated and the output voltage is ramped up. The output voltage reaches its nominal value in 250  $\mu$ s (typical) after the device has been enabled. The EN input can be used to control power sequencing in a system with various DC-DC converters. The EN pin can be connected to the output of another converter to drive the EN pin high and create a sequencing of supply rails. When EN = GND, the converter enters shutdown mode.

**TPD5S115**

SLVSBL2D - OCTOBER 2012 - REVISED JUNE 2017

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The TPD5S115 is an integrated solution for HDMI 2.0, 1.3, and 1.4 interfaces. The device has a boost converter on the power supply, signal conditioning circuits on CEC, SCL, SDA, and HPD lines, and ESD protection on all the connector-facing lines.

#### 8.2 Typical Applications

#### 8.2.1 DDC or CEC Level Shifter

The TPD5S115 enables DDC translation from VCCA (system side) voltage levels to 5-V (HDMI cable side) voltage levels without degradation of system performance. The TPD5S115 contains 2 bidirectional, open-drain buffers specifically designed to support up and down-translation between the low voltage, VCCA side DDC-bus and the 5-V DDC-bus. The port B I/Os are overvoltage tolerant to 5.5 V, even when the device is shutdown. After power up and with the LS\_OE and EN pins HIGH, a LOW level on port A (below V<sub>ILC</sub> = 0.08 × V<sub>CCA</sub>) turns the corresponding port B driver (either SDA or SCL) on and drives port B down to V<sub>OLB</sub>. When port A rises above approximately 0.10 × V<sub>CCA</sub>, the port B pulldown driver is turned off and the internal pullup resistor pulls the pin HIGH. When port B falls first and goes below 0.3 × V<sub>OUT</sub>, a CMOS hysteresis input buffer detects the falling edge, turns on the port A driver, and pulls port A down to approximately V<sub>OLA</sub> = 0.16 × V<sub>CCA</sub>. The port B pulldown is not enabled unless the port A voltage goes below V<sub>ILC</sub>. If the port A low voltage goes below V<sub>ILC</sub>, the port B pulldown driver is enabled until port A rises above (V<sub>ILC</sub> +  $\Delta$ V<sub>T-HYSTA</sub>), then port B, if not externally driven LOW, continues to rise being pulled up by the internal pullup resistor.

Copyright © 2016, Texas Instruments Incorporated

Figure 13. DDC or CEC Level Shifter Block Diagram

#### **Typical Applications (continued)**

#### 8.2.1.1 Design Requirements

For this design example, use the parameters listed in Table 1 as the input parameters.

| PARAMETER                                | VALUE            |

|------------------------------------------|------------------|

| 5VOUT DC current                         | 55 mA            |

| CEC_A, HPD_A, SCL_A, SDA_A voltage level | V <sub>CCA</sub> |

| HDMI 2.0 data rate per TMDS signal pair  | 6 Gbps           |

| Required IEC 61000-4-2 ESD Protection    | ±8-kV contact    |

#### **Table 1. Design Parameters**

#### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 DDC or CEC Level Shifter Operational Notes for V<sub>CCA</sub> = 1.8 V

- The threshold of CMP1 is approximately 150 mV ± the 40 mV of total hysteresis

- The comparator trips for a falling waveform at approximately 130 mV

- The comparator trips for a rising waveform at approximately 170 mV

- To be recognized as a zero, the level at port A must first go below 130 mV (V<sub>ILC</sub> in spec) and then stay below 170 mV ( $V_{IIA}$  in spec)

- To be recognized as a one, the level at A must first go above 170 mV and then stay above 130 mV

- V<sub>II C</sub> is specified as 110 mV in *Electrical Characteristics* to give some margin to the 130 mV

- VILA is specified as 140 mV in *Electrical Characteristics* to give some margin to the 170 mV

- VIHA is specified as 70% of V<sub>CCA</sub> to be consistent with standard CMOS levels

#### 8.2.1.2.2 Input Capacitor

Due to the nature of the boost converter having a pulsating input current, a low-ESR input capacitor is required to prevent large voltage transients that can cause poor performance of the device or interference with other circuits in the system. TI recommends a 1.2-µF (minimum) input capacitor to improve transient behavior of the regulator and EMI behavior of the total power-supply circuit. TI recommends placing a ceramic capacitor (4.7 µF) as close as possible to the V<sub>IN</sub> and GND pins to improve the input noise filtering.

#### 8.2.1.2.3 Output Capacitor

TI recommends using a small ceramic capacitors placed as close as possible to the V<sub>OUT</sub> and GND pins of the IC. If the application requires the use of large capacitors which can not be placed close to the IC, TI recommends using a smaller ceramic capacitor in parallel to the large capacitor. This small capacitor must be placed as close as possible to the V<sub>OUT</sub> and GND pins of the IC. Use Equation 1 to estimate the recommended minimum output capacitance.

$$\mathbf{C}_{\min} = \frac{\mathbf{I}_{\mathsf{OUT}} \times \left(\mathbf{V}_{\mathsf{OUT}} - \mathbf{V}_{\mathsf{IN}}\right)}{\mathbf{f} \times \Delta \mathbf{V} \times \mathbf{V}_{\mathsf{OUT}}}$$

where

- f is the switching frequency

- $\Delta V$  is the maximum allowed ripple ٠

If a ripple voltage of 10 mV is chosen, a minimum effective capacitance of 2.7 µF is needed. The total ripple is larger due to the ESR of the output capacitor. This additional component of the ripple can be calculated using Equation 2.

$$\Delta V_{\rm ESR} = I_{\rm OUT} \times R_{\rm ESR}$$

To maintain control loop stability, a capacitor with a value in the range of the calculated minimum must be used. There are no additional requirements regarding minimum ESR. There is no upper limit for the output capacitance value. Larger capacitors cause lower output voltage ripple as well as lower output voltage drop during load transients.

Copyright © 2012-2017, Texas Instruments Incorporated

(1)

(2)

Ceramic capacitors have a DC-bias effect, which has a strong influence on the final effective capacitance needed. Therefore the appropriate capacitor value must be chosen very carefully. Package size, voltage rating, and material are responsible for differences between the rated capacitor value and the effective capacitance. The minimum effective capacitance value is  $1.2 \ \mu\text{F}$ , but the recommended value is  $4.7 \ \mu\text{F}$ .

| Table 2. Passive Components: Recommended |

|------------------------------------------|

| Effective Values                         |

| COMPONENT         | MIN | TYP | MAX | UNIT |

|-------------------|-----|-----|-----|------|

| C <sub>IN</sub>   | 1.2 | 4.7 | 6.5 | μF   |

| C <sub>OUT</sub>  | 1.2 | 4.7 | 10  | μF   |

| L <sub>IN</sub>   | 0.7 | 1   | 1.3 | μH   |

| C <sub>VCCA</sub> |     | 0.1 |     | μF   |

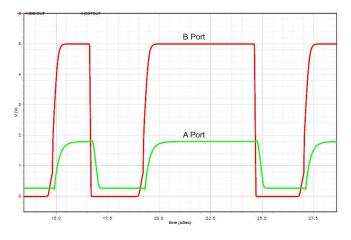

#### 8.2.1.3 Application Curve

Figure 14. DDC Level Shifter Operation (B to A Direction)

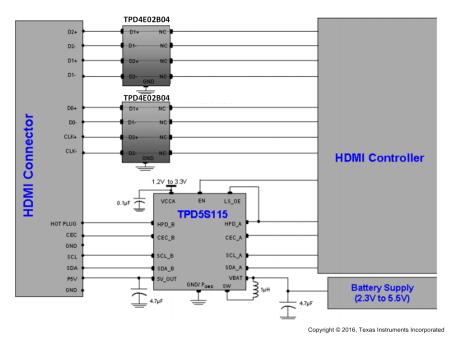

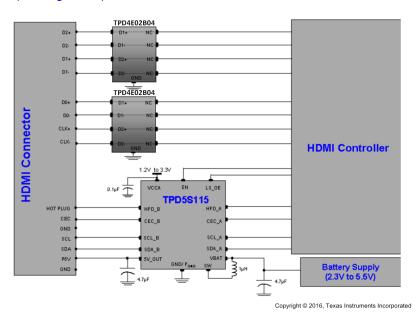

#### 8.2.2 Other Application Circuits

Figure 15 and Figure 16 show application examples using the TPD5S115 devices. Customers must fully validate and test any circuit before implementing a design based on an example in this section. Unless otherwise noted, the design procedures in *DDC or CEC Level Shifter* are applicable.

Figure 15. Application Schematic for HDMI Controllers With One GPIO for HDMI Interface Control

Some HDMI controllers may have only one GPIO to control the HDMI interface, thus, the HDMI driver chip controls the TPD5S115 through only one control line (EN). In this mode the HPD\_A to LS\_OE pins are connected to each other (see Figure 15).

Figure 16. Application Schematic for HDMI Controllers With Two GPIOs for HDMI Interface Control

Some HDMI driver chips may have two GPIOs to control the HDMI interface chip. In this case a flexible power saving mode can be implemented. The LS\_OE and EN are active-high enable pins. They control the TPD5S115 power-saving options according to Table 3 and Table 4.

| LS_OE | EN | V <sub>CCA</sub> | V <sub>BAT</sub> | 5VOUT  | A-SIDE PULLUPS | DCC, B-SIDE PULLUPS | CEC, B-SIDE PULLUPS |

|-------|----|------------------|------------------|--------|----------------|---------------------|---------------------|

| L     | L  | 1.8 V            | 5 V              | Off    | Off            | Off                 | Off                 |

| L     | Н  | 1.8 V            | 5 V              | On     | On             | On                  | Off                 |

| Н     | L  | 1.8 V            | 5 V              | Off    | Off            | Off                 | Off                 |

| Н     | Н  | 1.8 V            | 5 V              | On     | On             | On                  | On                  |

| Х     | Х  | 0 V              | 0 V              | High-Z | High-Z         | High-Z              | High-Z              |

| Х     | Х  | 1.8 V            | 0 V              | Low    | Low            | High-Z              | High-Z              |

| Х     | Х  | 0 V              | 5 V              | High-Z | High-Z         | High-Z              | High-Z              |

#### Table 3. Device Status – Part 1

#### Table 4. Device Status – Part 2

| LS_OE | EN | CEC LDO | DC-DC AND HPD | DDC OR CEC VLTS | I <sub>CCA</sub> TYP | I <sub>CC</sub> V <sub>BAT</sub> TYP | COMMENT          |

|-------|----|---------|---------------|-----------------|----------------------|--------------------------------------|------------------|

| L     | L  | Off     | Off           | OFF and High-Z  | 1 µA                 | 1 µA                                 | Fully disabled   |

| L     | Н  | Off     | On            | OFF and High-Z  | 1 µA                 | 30 µA                                | DC-DC (30 µA) ON |

| Н     | L  | Off     | Off           | OFF and High-Z  | 1 µA                 | 1 µA                                 | Not valid state  |

| Н     | Н  | On      | On            | ON              | 13 µA                | 225 µA                               | Fully ON         |

| Х     | Х  | Off     | Off           | High-Z          | 0 µA                 | 0 µA                                 | Power down       |

| Х     | Х  | Off     | Off           | High-Z          | 0 µA                 | 0 µA                                 | Power down       |

| Х     | Х  | Off     | Off           | High-Z          | 0 µA                 | 0 µA                                 | Power down       |

# 9 Power Supply Recommendations

To keep the normal function of TPD5S115, the designer needs to make sure that both VBAT and VCCA are within the recommended operating range. See *Detailed Design Procedure* for power supply recommendations.

# 10 Layout

### 10.1 Layout Guidelines

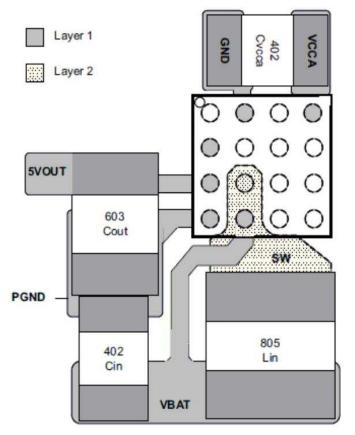

For proper operation, follow these layout and design guidelines:

- Place the TPD5S115 as close to the connector as possible. This allows it to remove the energy associated with ESD strike before it reaches the internal circuitry of the system board.

- Place power line capacitors and inductors close to the pins with wide traces to allow enough current to flow through with less trace parasitics. Ensure that there is enough metallization for the GND pad. A sufficient current path enables safe discharge of all the energy associated with the ESD strike.

### 10.2 Layout Example

Figure 17. Board Layout With DC-DC Components (Top View)

TEXAS INSTRUMENTS

www.ti.com

## **11** Device and Documentation Support

### **11.1 Documentation Support**

#### 11.1.1 Related Documentation

For related documentation see the following:

• Reading and Understanding an ESD Protection Datasheet

• ESD Layout Guide

#### 11.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### **11.3 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

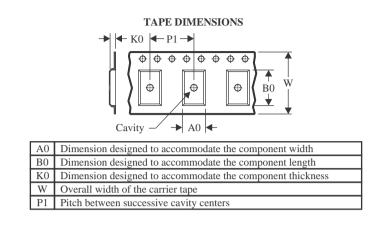

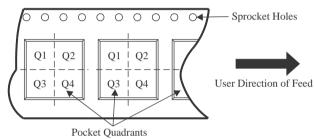

### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type (2) | Package   Pins   | Package qty   Carrier | <b>RoHS</b><br>(3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|-------------------|------------------|-----------------------|--------------------|-------------------------------|----------------------------|--------------|---------------------|

|                       |               |                   |                  |                       |                    | (4)                           | (5)                        |              |                     |

| TPD5S115YFFR          | Active        | Production        | DSBGA (YFF)   16 | 3000   LARGE T&R      | Yes                | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | RE115               |

| TPD5S115YFFR.A        | Active        | Production        | DSBGA (YFF)   16 | 3000   LARGE T&R      | Yes                | SNAGCU                        | Level-1-260C-UNLIM         | -40 to 85    | RE115               |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.