**TMP126-Q1** SNIS227C - MAY 2021 - REVISED JUNE 2022

# TMP126-Q1 Low-Power, 0.25°C SPI Temperature Sensor With 175°C Operation, CRC and Slew Rate Alert

### 1 Features

- AEC-Q100 qualified for automotive applications

- Device temperature grade-0: –55°C to 175°C ambient operating temperature

- Device HBM classification level 2

- Device CDM classification level C2b

- Function Safety Capable

- Documentation available to aid functional safety system design

- High accuracy

- ±0.25°C (maximum) from 20°C to 30°C

- ±0.3°C (maximum) from –20°C to 85°C

- ±0.4°C (maximum) from –40°C to 125°C

- ±0.5°C (maximum) from –55°C to 150°C

- ±0.75°C (maximum) from 150°C to 175°C

- Fast measurement intervals with no self-heating

- Supply range: 1.62 V to 5.5 V

- Factory-calibrated

- NIST traceability

- Low power consumption

- Programmable temperature alert limits

- Temperature slew rate warning

- Optional Cyclic Redundancy Check (CRC)

- 3-wire SPI interface

## 2 Applications

- Transmission Control Units

- On-board Chargers (OBC)

- **Brake Systems**

- **Traction Inverters**

- Vehicle Control Units (VCU)

- DC/DC Converters

- Power Distribution Units (PDU)

- Powertrain Exhaust Sensors

## 3 Description

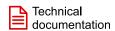

The TMP126-Q1 is a 0.25°C accuracy digital temperature that supports an ambient temperature range of -55°C to 175°C. The TMP126-Q1 features a 14-bit signed temperature resolution (0.03125°C per LSB) while operating over a supply range of 1.62 V to 5.5 V. With a fast conversion rate, low supply current, and a simple 3-wire SPI compatible interface, the TMP126-Q1 is designed for a wide range of applications.

The TMP126-Q1 includes additional advanced features for increased reliability in harsh environments such as optional CRC checksum for data integrity, programmable alert limits, a temperature slew rate warning, and an enhanced operational temperature range. The device utilizes a NIST traceable factory calibration for guaranteed accuracy and comes in a small SOT package for close placement to heat sources along with fast response times.

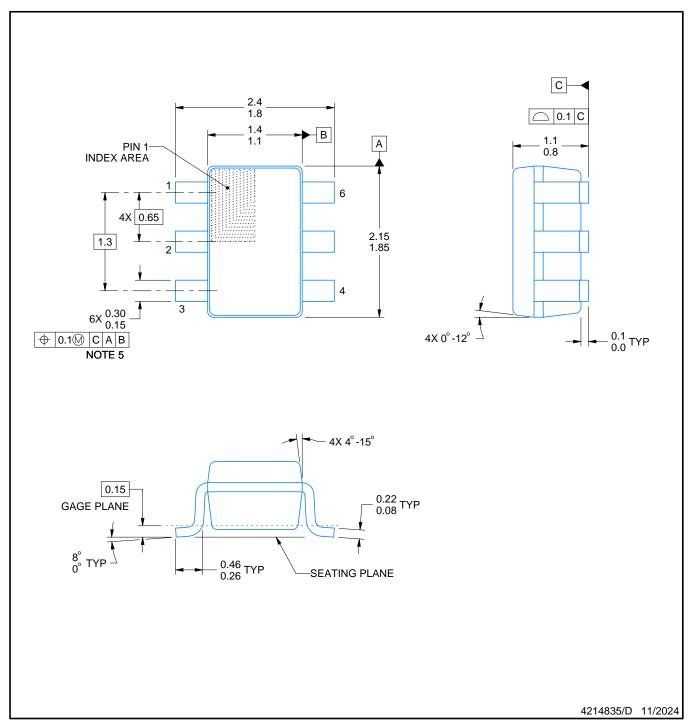

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |

|-------------|------------------------|-------------------|--|

| TMP126-Q1   | SOT-SC70 (6)           | 2.00 mm × 1.25 mm |  |

|             | SOT-23 (6)             | 2.90 mm × 1.60 mm |  |

For all available packages, see the orderable addendum at the end of the data sheet.

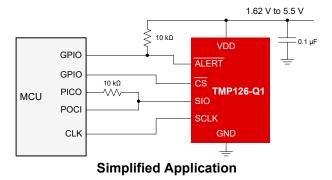

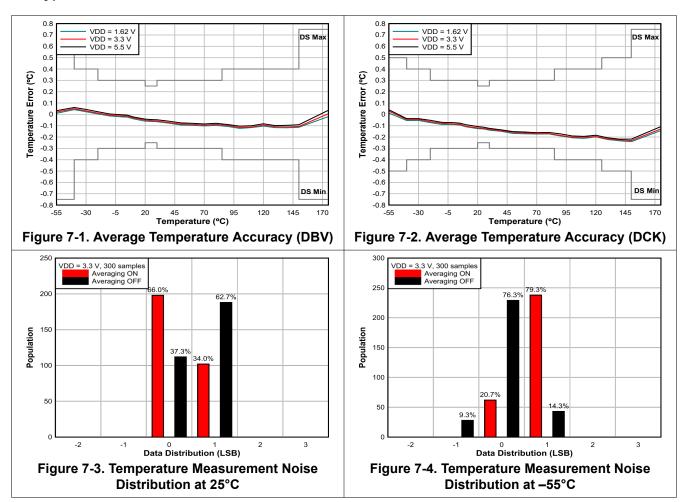

Average Temperature Accuracy (DBV)

## **Table of Contents**

| 1 Features                           | 1  | 8.5 Programming                                      | 18 |

|--------------------------------------|----|------------------------------------------------------|----|

| 2 Applications                       |    | 8.6 Register Map                                     |    |

| 3 Description                        |    | 9 Application and Implementation                     |    |

| 4 Revision History                   |    | 9.1 Application Information                          |    |

| 5 Device Comparison                  |    | 9.2 Typical Application                              |    |

| 6 Pin Configuration and Functions    | 3  | 10 Power Supply Recommendations                      |    |

| 7 Specifications                     | 4  | 11 Layout                                            | 37 |

| 7.1 Absolute Maximum Ratings         |    | 11.1 Layout Guidelines                               |    |

| 7.2 ESD Ratings                      |    | 11.2 Layout Example                                  |    |

| 7.3 Recommended Operating Conditions |    | 12 Device and Documentation Support                  |    |

| 7.4 Thermal Information              | 4  | 12.1 Documentation Support                           | 39 |

| 7.5 Electrical Characteristics       | 5  | 12.2 Receiving Notification of Documentation Updates | 39 |

| 7.6 SPI Interface Timing             | 7  | 12.3 Support Resources                               |    |

| 7.7 Typical Characteristics          |    | 12.4 Trademarks                                      |    |

| 8 Detailed Description               |    | 12.5 Electrostatic Discharge Caution                 | 39 |

| 8.1 Overview                         |    | 12.6 Glossary                                        |    |

| 8.2 Functional Block Diagram         |    | 13 Mechanical, Packaging, and Orderable              |    |

| 8.3 Feature Descriptions             | 11 | Information                                          | 39 |

| 8.4 Device Functional Modes          | 14 |                                                      |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision B (March 2022) to Revision C (June 2022)                               | Page                |

|---|---------------------------------------------------------------------------------------------|---------------------|

| • | Changed the resistance between the VDD and ALERT pins in the Simplified Application key     | graphic on the      |

|   | first page from: 5 k $\Omega$ to: 10 k $\Omega$                                             | 1                   |

| • | Added the Average Temperature Accuracy (DBV) key graphic to the first page                  | 1                   |

| • | Changed Device Comparison table                                                             |                     |

| • | Added Response Time specification to the Electrical Characteristics table                   | 5                   |

| • | Added new graphs to the Typical Characteristics section                                     |                     |

| • | Added note to the Slew Rate Warning section                                                 |                     |

| • | Added the response time (stirred liquid) parameter for the DBV package to the Electrical Ch | aracteristics table |

|   |                                                                                             | <mark>23</mark>     |

| • | Corrected bit range for the Reserved section of configuration register                      | 25                  |

| С | hanges from Revision A (March 2022) to Revision B (March 2022)                              | Page                |

| • | Changed data sheet status from: Advanced Information to: Production Data                    | 1                   |

| C | hanges from Revision * (May 2021) to Revision A (March 2022)                                | Page                |

| • | Changed the Layout Example                                                                  | 37                  |

|   | •                                                                                           |                     |

# **5 Device Comparison**

Table 5-1. Device Comparison

| Feature                      | TMP126  | TMP126N | TMP126-Q1 | TMP127-Q1 |

|------------------------------|---------|---------|-----------|-----------|

| Best accuracy (maximum)      | 0.25 °C | 0.8 °C  | 0.25 °C   | 0.8 °C    |

| Packages                     | DCK     | DCK     | DBV, DCK  | DBV       |

| Continuous and shutdown mode | •       | •       | •         | •         |

| 175°C operation              | •       |         | •         | •         |

| Automotive Grade-0           |         |         | •         | •         |

| NIST Traceable               | •       | •       | •         |           |

| Alert pin functionality      | •       | •       | •         |           |

| Slew rate warning            | •       | •       | •         |           |

| CRC option                   | •       | •       | •         |           |

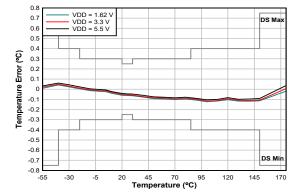

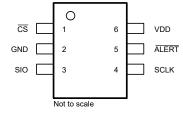

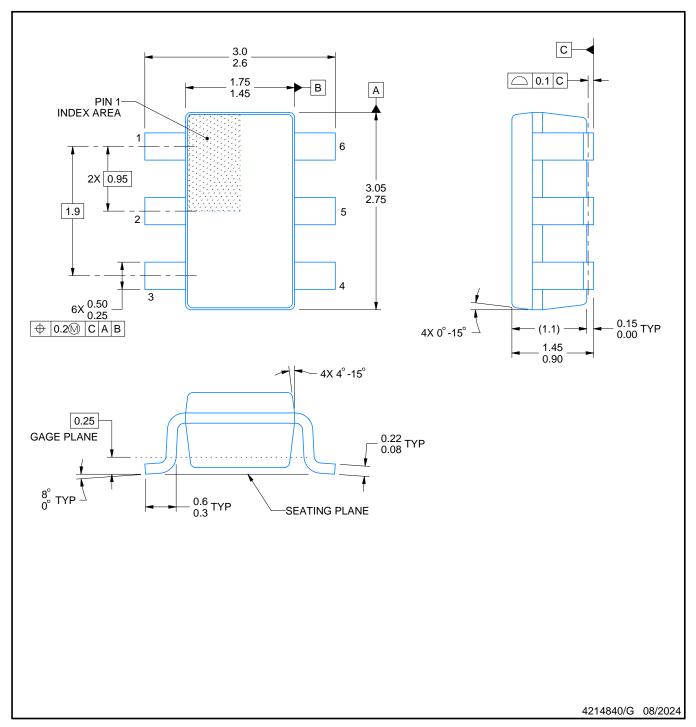

# **6 Pin Configuration and Functions**

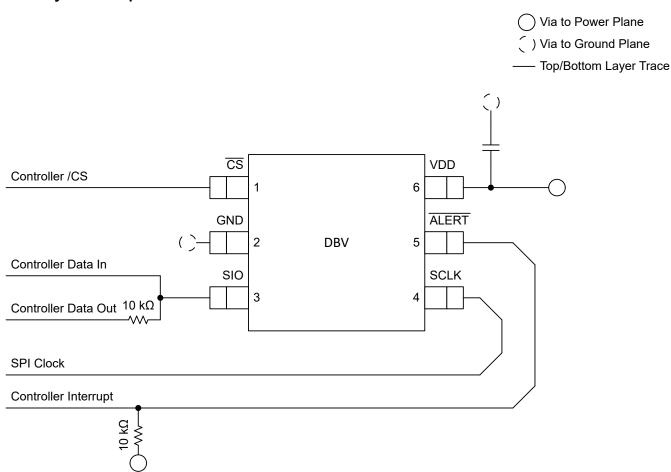

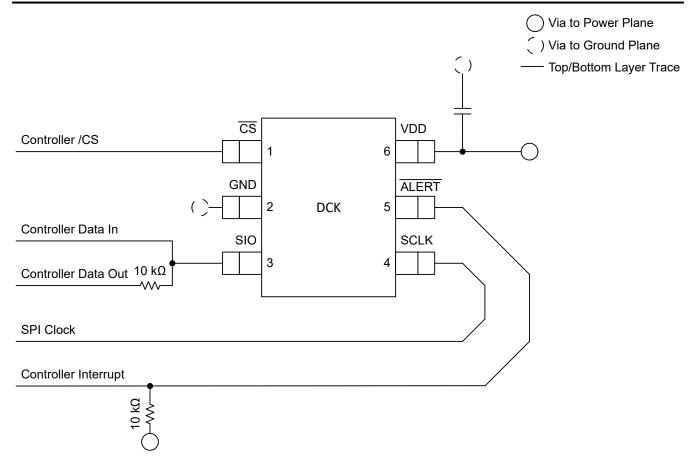

Figure 6-2. DCK 6-pin SC70 Top View

Figure 6-1. DBV 6-pin SOT-23 Top View

**Table 6-1. Pin Functions**

| P        | PIN I/O |     | DESCRIPTION                                                              |  |

|----------|---------|-----|--------------------------------------------------------------------------|--|

| NAME NO. |         | 1/0 | DESCRIPTION                                                              |  |

| CS       | 1       | I   | Chip select signal to activate SPI interface                             |  |

| GND      | 2       | -   | Ground                                                                   |  |

| SIO      | 3       | I/O | System input/output                                                      |  |

| SCLK     | 4       | I   | System clock input                                                       |  |

| ALERT    | 5       | 0   | Alert open-drain output. Can be left floating or grounded when not used. |  |

| VDD      | 6       | -   | Supply voltage                                                           |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over free-air temperature range unless otherwise noted<sup>(1)</sup>

| •                      |                          | 24121 | BB A 3/                 |      |

|------------------------|--------------------------|-------|-------------------------|------|

|                        |                          | MIN   | MAX                     | UNIT |

| Supply voltage         | VDD                      | -0.3  | 6                       | V    |

| I/O voltage            | SIO                      | -0.3  | V <sub>DD</sub> + 0.2 V | V    |

| I/O voltage            | CS,ALERT, SCLK           | -0.3  | 6                       | V    |

| Operating junction tem | perature, T <sub>J</sub> | -65   | 180                     | °C   |

| Storage temperature, T | stg                      | -65   | 180                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------------------|-------|------|

| V                  | Floatrootatio discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM classification level 2 | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per AEC Q100-011<br>CDM classification level C2b          | ±750  | V    |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### 7.3 Recommended Operating Conditions

|                  |                                              | MIN  | NOM MAX  | UNIT |

|------------------|----------------------------------------------|------|----------|------|

| $V_{DD}$         | Supply voltage                               | 1.62 | 3.3 5.5  | V    |

| V <sub>I/O</sub> | SIO                                          | 0    | $V_{DD}$ | V    |

| V <sub>I/O</sub> | CS,ALERT, SCLK                               | 0    | 5.5      | V    |

| T <sub>A</sub>   | Operating ambient temperature <sup>(1)</sup> | -55  | 175      | °C   |

<sup>(1)</sup> HTOL was performed at 175 °C for 1410 hours

### 7.4 Thermal Information

|                       |                                              | TMP1   | 26-Q1  |      |

|-----------------------|----------------------------------------------|--------|--------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DBV    | DCK    | UNIT |

|                       |                                              | 6-pins | 6-pins |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 168.2  | 183.4  | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 85.5   | 136.4  | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | -      | _      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 48.1   | 74.2   | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 27.5   | 57.9   | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 47.9   | 74.0   | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Product Folder Links: TMP126-Q1

### 7.5 Electrical Characteristics

Over free-air temperature range and  $V_{DD}$  = 1.62 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25 °C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                      | PARAMETER                                         | TEST CO                                                  | NDITIONS       | MIN                   | TYP   | MAX                   | UNIT  |

|----------------------|---------------------------------------------------|----------------------------------------------------------|----------------|-----------------------|-------|-----------------------|-------|

| TEMPERA              | TURE SENSOR                                       |                                                          |                | <u>'</u>              |       |                       |       |

|                      |                                                   | 20 °C to 30 °C                                           |                | -0.25                 |       | 0.25                  | °C    |

|                      |                                                   | -20 °C to 85 °C                                          |                | -0.3                  |       | 0.3                   | °C    |

| T <sub>ERR</sub> (1) | Temperature accuracy                              | -40 °C to 125 °C                                         |                | -0.4                  |       | 0.4                   | °C    |

|                      |                                                   | -55 °C to 150 °C                                         |                | -0.5                  |       | 0.5                   | °C    |

|                      |                                                   | -55 °C to 175 °C                                         |                | -0.75                 |       | 0.75                  | °C    |

| PSR                  | DC power supply rejection                         | One-shot mode                                            |                |                       | 12.7  |                       | m°C/V |

| Ŧ                    | T                                                 | Including sign bit                                       |                |                       | 14    |                       | Bits  |

| T <sub>RES</sub>     | Temperature resolution                            | LSB                                                      |                |                       | 31.25 |                       | m°C   |

| T <sub>REPEAT</sub>  | Repeatability <sup>(2)</sup>                      | V <sub>DD</sub> = 3.3 V<br>1-Hz conversion cycle         |                |                       | ±1    |                       | LSB   |

| T <sub>LTD</sub>     | Long-term stability and drift <sup>(3)</sup>      | 1000 hours at 175 °C                                     |                |                       | 0.07  |                       | °C    |

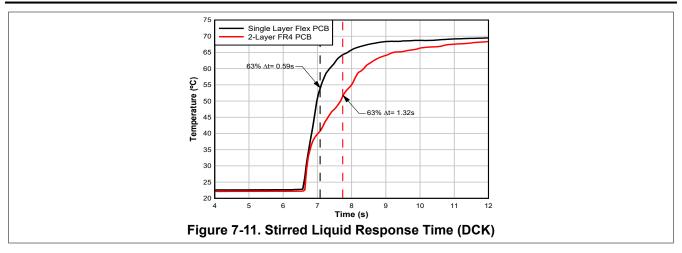

|                      | Response time (Stirred Liquid)                    | Single layer Flex PCB 0.2032 mm thickness                | т = 63 %       |                       | 0.8   |                       | s     |

| t <sub>LIQUID</sub>  | DBV Package                                       | 2-layer FR4 PCB<br>1.5748 mm thickness                   | 25 °C to 75 °C |                       | 1.8   |                       | s     |

| 4                    | Response time (Stirred Liquid)                    | Single layer Flex PCB 0.2032 mm thickness                | т = 63 %       |                       | 0.6   |                       | s     |

| t <sub>LIQUID</sub>  | DCK Package                                       | 2-layer FR4 PCB<br>1.5748 mm thickness                   | 25 °C to 75 °C |                       | 1.3   |                       | s     |

|                      | Temperature cycling and hysteresis <sup>(4)</sup> |                                                          |                |                       | ±0.5  |                       | LSB   |

| t <sub>CONV</sub>    | Active conversion time                            |                                                          |                | 4.5                   | 6     | 7.5                   | ms    |

| t <sub>VAR</sub>     | Timing variation                                  | Conversion Period<br>Slew Rate Result<br>Slew Rate Limit |                | -15                   |       | 15                    | %     |

| DIGITAL IN           | NPUT/OUTPUT                                       |                                                          |                |                       |       |                       |       |

| C <sub>IN</sub>      | Input capacitance                                 | f = 1 MHz                                                |                |                       |       | 20                    | pF    |

| V <sub>IH</sub>      | Input logic high level                            | SCLK, SIO, CS                                            |                | 0.7 * V <sub>DD</sub> |       | $V_{DD}$              | V     |

| V <sub>IL</sub>      | Input logic low level                             | SCLK, SIO, CS                                            |                | 0                     |       | 0.3 * V <sub>DD</sub> | V     |

| I <sub>IN</sub>      | Input leakage current                             | SCLK, SIO, CS                                            |                | -0.5                  |       | 0.5                   | μΑ    |

| V <sub>OH</sub>      | SIO output high level                             | I <sub>OH</sub> = 3 mA                                   |                | V <sub>DD</sub> - 0.4 |       | $V_{DD}$              | V     |

| V <sub>OL</sub>      | SIO output low level                              | I <sub>OL</sub> = -3 mA                                  |                | 0                     |       | 0.4                   | V     |

| V <sub>OL</sub>      | ALERT output logic low level                      | I <sub>OL</sub> = -3 mA                                  |                | 0                     |       | 0.4                   | V     |

Over free-air temperature range and  $V_{DD}$  = 1.62 V to 5.5 V (unless otherwise noted); Typical specifications are at  $T_A$  = 25 °C and  $V_{DD}$  = 3.3 V (unless otherwise noted)

|                        | PARAMETER                               | TEST                                   | CONDITIONS                                                          | MIN | TYP  | MAX  | UNIT |

|------------------------|-----------------------------------------|----------------------------------------|---------------------------------------------------------------------|-----|------|------|------|

| POWER SU               | PPLY                                    |                                        |                                                                     |     |      |      |      |

|                        |                                         |                                        | T <sub>A</sub> = 25 °C                                              |     | 77   | 87   |      |

| I <sub>DD_ACTIVE</sub> | Supply current during active conversion | CS = V <sub>DD</sub>                   | T <sub>A</sub> = -55 °C to 150 °C                                   |     |      | 135  | μΑ   |

|                        | sentenen.                               |                                        | T <sub>A</sub> = 175 °C                                             |     |      | 160  |      |

|                        |                                         |                                        | T <sub>A</sub> = 25 °C<br>Conversion cycle<br>time: 1 Hz            |     | 1    | 1.2  |      |

| I <sub>DD</sub>        | Average current consumption             | $\overline{\text{CS}} = V_{\text{DD}}$ | T <sub>A</sub> = -55 °C to 150 °C<br>Conversion cycle<br>time: 1 Hz |     |      | 16   | μΑ   |

|                        |                                         |                                        | T <sub>A</sub> = 175 °C<br>Conversion cycle<br>time: 1 Hz           |     |      | 35   |      |

|                        |                                         |                                        | T <sub>A</sub> = 25 °C                                              |     | 0.5  | 0.75 |      |

| I <sub>SB</sub>        | Standby current <sup>(5)</sup>          | CS = V <sub>DD</sub>                   | T <sub>A</sub> = -55 °C to 150 °C                                   |     |      | 15   | μΑ   |

|                        |                                         |                                        | T <sub>A</sub> = -55 °C to 175 °C                                   |     |      | 34   |      |

|                        |                                         |                                        | T <sub>A</sub> = 25 °C                                              |     | 0.35 | 0.5  |      |

| $I_{SD}$               | Shutdown current                        | CS = V <sub>DD</sub>                   | T <sub>A</sub> = -55 °C to 150 °C                                   |     |      | 15   | μΑ   |

|                        |                                         |                                        | T <sub>A</sub> = -55 °C to 175 °C                                   |     |      | 34   |      |

| V <sub>POR</sub>       | Power-on reset threshold voltage        | Supply rising                          |                                                                     |     | 1.3  |      | V    |

|                        | Brownout detect                         | Supply falling                         |                                                                     |     | 1.1  |      | V    |

| t <sub>RESET</sub>     | Reset Time                              | Time required by o                     | levice to reset                                                     |     | 0.5  |      | ms   |

<sup>(1)</sup> Temperature Accuracy (averaging on or averaging off) guaranteed in both continuous conversion mode and one-shot mode with a conversion period greater than or equal to 31.25 ms.

(5) Quiescent current between conversions

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

<sup>(2)</sup> Repeatability is the ability to reproduce a reading when the measured temperature is applied consecutively, under the same conditions.

<sup>(3)</sup> Long term stability is determined using accelerated operational life testing at a junction temperature of 150 °C.

<sup>(4)</sup> Hysteresis is defined as the ability to reproduce a temperature reading as the temperature varies from room → hot →room→cold→room. The temperatures used for this test are -40 °C, 25 °C, and 150 °C.

### 7.6 SPI Interface Timing

Over free-air temperature range and  $V_{DD}$  = 1.62 V to 5.5 V (unless otherwise noted)

|                         |                                                                           | SPI BUS | SPI BUS |      |  |

|-------------------------|---------------------------------------------------------------------------|---------|---------|------|--|

|                         |                                                                           | MIN     | MAX     | UNIT |  |

| f <sub>CLK</sub>        | SCLK frequency                                                            |         | 10      | MHz  |  |

| t <sub>CLK</sub>        | SCLK Period                                                               | 100     |         | ns   |  |

| t <sub>LEAD</sub>       | Falling edge of $\overline{\text{CS}}$ to rising edge of SCLK setup time  | 100     |         | ns   |  |

| t <sub>LAG</sub>        | Rising edge of SCLK to rising edge of $\overline{\text{CS}}$ setup time   | 20      |         | ns   |  |

| t <sub>SU</sub>         | SIO to SCLK rising edge setup time                                        | 10      |         | ns   |  |

| t <sub>HOLD</sub>       | SIO hold time after rising edge of SCLK                                   | 20      |         | ns   |  |

| t <sub>VALID</sub>      | Time from falling edge of SLCK to valid SIO data                          |         | 35      | ns   |  |

| t <sub>SIO(DIS)</sub>   | Time from rising edge of $\overline{\text{CS}}$ to SIO high-impedance     |         | 200     | ns   |  |

| t <sub>RISE</sub>       | SIO, SCLK, $\overline{\text{CS}}$ rise time                               |         | 100     | ns   |  |

| t <sub>FALL</sub>       | SIO, SCLK, $\overline{\text{CS}}$ fall time                               |         | 100     | ns   |  |

| t <sub>INTERFRAME</sub> | Delay between two SPI communication sequences (CS high)                   | 100     |         | ns   |  |

| t <sub>INITIATION</sub> | Delay between valid V <sub>DD</sub> voltage and initial SPI communication | 0.5     |         | ms   |  |

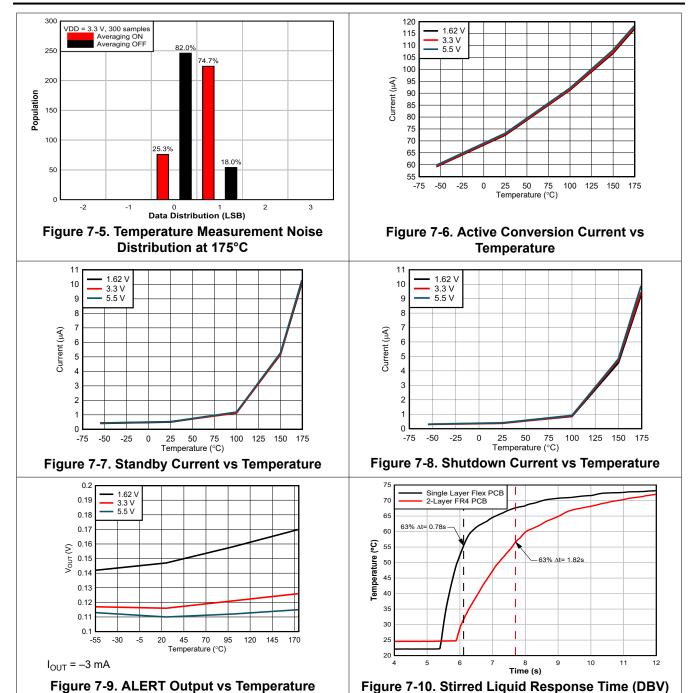

## 7.7 Typical Characteristics

## **8 Detailed Description**

### 8.1 Overview

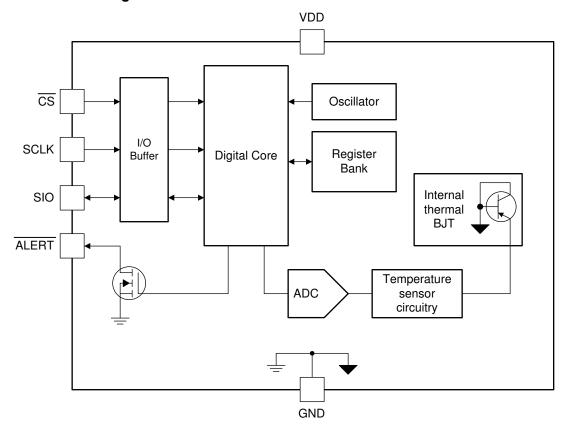

The TMP126-Q1 is a factory calibrated digital output temperature sensor designed for thermal management and thermal protection applications. The device has a 3-wire SPI compatible interface with multiple operating modes including continuous, one-shot, and shutdown mode. The TMP126-Q1 features an ALERT output with temperature threshold settings for autonomous monitoring and system alerts. In addition the TMP126-Q1 also includes a temperature slew rate warning feature that alerts the system to temperature spikes, allowing for corrective action before reaching thermal limits.

For data integrity an optional Cyclic Redundancy Check (CRC) is available that will validate communication with the device.

## 8.2 Functional Block Diagram

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

### 8.3 Feature Descriptions

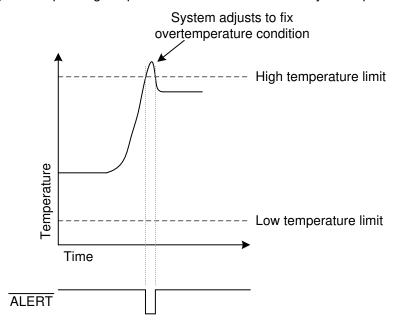

### 8.3.1 Temperature Limits

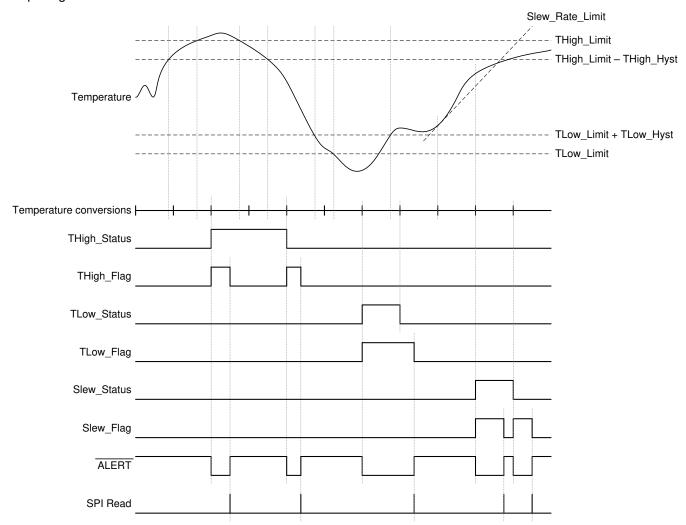

The TMP126-Q1 includes a temperature limit warning that can be enabled or disabled in the configuration register. If enabled, at the end of every completed conversion the TMP126-Q1 will compare the result against the limits stored in the low limit register and the high limit register. When exceeding these limits the ALERT pin will be set. The ALERT pin behavior will change depending on which mode the device is configured to as described in the *Interrupt and Comparator Mode* section.

The Alert functionality can allow the system to set the desired operating thermal limits of the system with the TMP126-Q1 and allow autonomous monitoring of temperature without the need for the system to read the temperature. When a thermal limit is exceeded the system will receive a warning through the ALERT pin and can react accordingly to adjust the operating temperature back to within normal system operation.

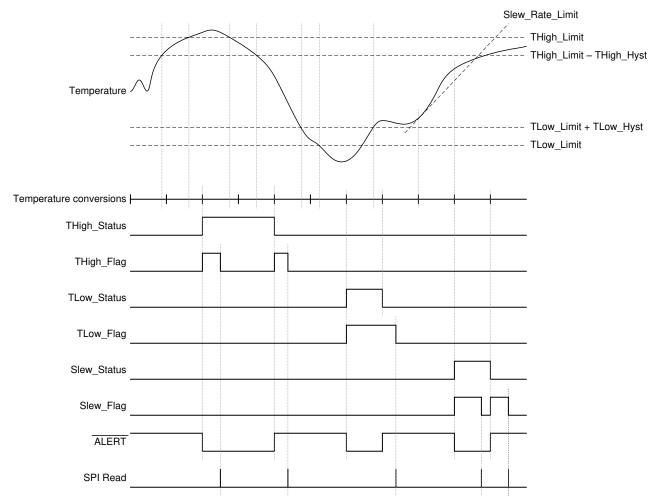

Figure 8-1. Temperature Limit Alert

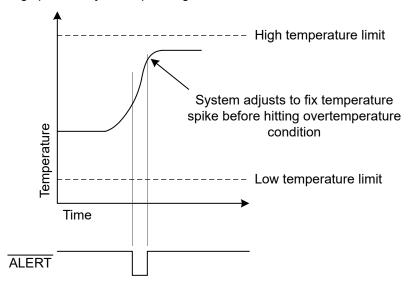

### 8.3.2 Slew Rate Warning

The slew rate warning is an adjustable alert option that can be adjusted with the Slew Limit register.

The slew rate warning will notify the system of temperature spikes as they occur, allowing the system to react and correct for the increase in temperature before reaching thermal operating limits. Compared to throttling a system after crossing a thermal limit, the slew rate warning will allow a more safe system operation and greater reliability by not exceeding specified system operating conditions.

Figure 8-2. Slew Rate Warning

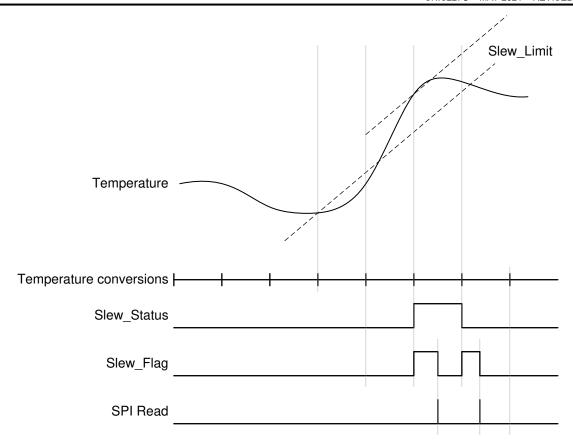

The Slew\_Limit register is used to set the unsigned limit. The TMP126-Q1 will monitor the temperature slew rate and compare the positive change of temperature from the current conversion to the previous against the Slew\_Limit. If the slew rate exceeds the Slew\_Limit, the respective bits in the Alert\_Status register will be set to indicate the warning. Figure 8-3 depicts the timing of the Slew Rate Warning relative to the temperature conversions. The slew rate check is always applied to the current temperature conversion and the previous temperature conversion.

Note the following considerations when using the Slew Rate Warning feature:

- Calculating the slew rate requires a fixed time period and is only available in continuous mode.

- Similar to other timing parameters of the device, consider that the slew rate calculation interval is impacted by the timing variation (t<sub>VAR</sub>) of the device.

- Slew rate calculation is supported for positive temperature changes (temperature increase) only.

- Take the sensor response time into account when using the Slew Rate Warning feature as the response time impacts how quickly the sensor responses to temperature changes.

Figure 8-3. Slew Rate Warning Timing Diagram

### 8.3.3 Cyclic Redundancy Check (CRC)

The TMP126-Q1 has integrated optional CRC that can be used to determine the integrity of the SPI communication to the TMP126-Q1. The CRC is enabled by setting the CRC\_Enable bit in the command word to 1 with an appropriate data block length. During a read, the TMP126-Q1 will append a 16 bit CRC checksum to the data block for the host to compare with its own checksum. In this manner the host can validate the data sent by TMP126-Q1 and read from the device again if necessary. During write operations, the host will send the CRC word that the TMP126-Q1 will compare against its own checksum. If the TMP126-Q1 determines that the data sent during the write transaction was corrupted, the TMP126-Q1 will discard the write and set the CRC\_Flag in the Alert\_Status register to alert the host that the register settings must be sent again.

This allows the system to ensure the data integrity of the SPI communication in both write and read operations.

Writing to the configuration register with a CRC enabled transaction is currently not supported.

### 8.3.4 NIST Traceability

The accuracy of temperature testing is verified with equipment that is calibrated by an accredited lab that complies with ISO/IEC 17025 policies and procedures. Each device is tested and trimmed to conform to its respective data sheet specification limits.

### 8.3.5 Fast Measurement Intervals With No Self-Heating Concerns

The TMP126-Q1 is optimized to minimize the effects of self-heating and maintain the temperature accuracy if the conversion period is greater than 31.25 ms in continuous conversion or one-shot mode. This eliminates measurement waiting time normally needed for self-heating avoidance.

### 8.4 Device Functional Modes

The TMP126-Q1 can be configured to operate in various conversion modes by using the Mode bit in the configuration register. These modes provide flexibility to operate the device in the most power efficient way necessary for the intended application.

### 8.4.1 Continuous Conversion Mode

When the Mode bit is set to 0 in the Configuration register, the device operates in continuous conversion mode. Figure 8-4 shows that the device continuously performs temperature conversions in this mode. The TMP126-Q1 does not wait until the end of the conversion period to update the temperature, instead the temperature result register is updated at the end of the temperature conversion. After a completed active conversion, the Data\_Ready flag bit is set to 1. The user can read the interrupt/status register or the temperature result register to clear the Data\_Ready flag. Therefore, the Data\_Ready\_Flag can be used to determine when the conversion completes so that an external controller can synchronize reading the result register with conversion result updates. The user can set the Data\_Ready\_Flag\_En bit in the configuration register to monitor the state of the Data\_Ready\_Flag on the ALERT pin.

Every conversion period consists of an active temperature conversion followed by a standby period. During standby the TMP126-Q1 will de-activate all measurement circuitry to conserve power but will remain available for any SPI communication. The device typically consumes 75  $\mu$ A during the temperature conversion and only 1  $\mu$ A during the low-power standby period. The duration of the temperature conversion will remain fixed, but the conversion period can be configured using the Conv\_Period[2:0] bit field in the Configuration register, allowing the average current consumption of the device to be optimized based on the application requirements. Changing the conversion period also affects the temperature result update rate due to the temperature result register being updated at the end of every temperature conversion.

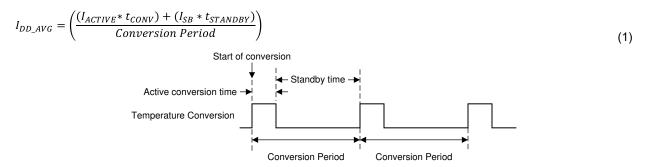

Use Equation 1 to calculate the average current consumption of the device in continuous conversion mode.

Figure 8-4. Conversion Period Timing Diagram

### 8.4.2 Shutdown Mode

When the Mode bit is set to 1 in the Configuration register, the device immediately enters the low-power shutdown mode. If the TMP126-Q1 is making a temperature conversion, the device will stop the conversion and discard the partial result. In this mode, the device powers down all active circuitry and can be used in conjunction with the One\_Shot bit to perform temperature conversions. Engineers can use the TMP126-Q1 for battery-operated systems and other low-power consumption applications because the device typically only consumes 350 nA in Shutdown Mode.

Changing between continuous and shutdown will not clear any active alerts in the Alert\_Status register and the ALERT pin will continue to be asserted until cleared by the host. The slew rate alert will not be triggered again in shutdown mode but will not clear until read if it is already set.

#### 8.4.3 One-Shot Mode

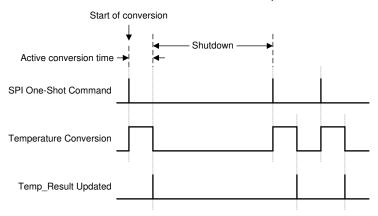

When One\_Shot bit is set to 1 in the Configuration register the TMP126-Q1 will immediately start a new temperature conversion, referred to as a one-shot conversion, and discard any partial conversion results. After the device completes a one-shot conversion, the device will enter the low power shutdown mode. The Mode bit will be set to 1 and the One\_Shot bit will be set to 0 automatically. Figure 8-5 shows a current consumption timing diagram for this mode. At the end of a one-shot conversion, the Data\_Ready\_Flag in the Alert\_Status register is set and can be used to determine when the conversion completes.

Figure 8-5. One-Shot Timing Diagram

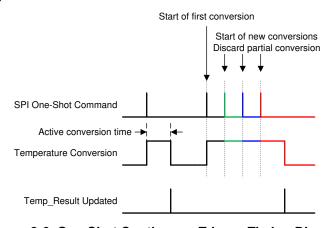

If the One\_Shot bit is continuously written to faster than the active conversion time of the TMP126, the device will continue to restart the temperature conversion with each new write. It is recommended to avoid this behavior as the temperature result does not update until a conversion finishes. If continuous one-shots are being triggered by the system Figure 8-6 depicts how the device would continually partially finish new conversions and not update the Temp Result register.

Figure 8-6. One-Shot Continuous Trigger Timing Diagram

### 8.4.4 Interrupt and Comparator Mode

The ALERT pin of the TMP126-Q1 can be programmed to operate in two different modes. In the interrupt mode the TMP126-Q1 will assert the ALERT pin if the temperature exceeds the limits set by temperature limit registers and the flags are enabled. After the Alert\_Status is read and the interrupt bits cleared, the ALERT pin will be de-asserted. In the Comparator mode, the ALERT pin will assert if any enabled status bits of the Alert\_Status are set. Changes to the Alert\_Enable register will be reflected on the ALERT pin after the completed conversion or device read.

### 8.4.4.1 Interrupt Mode

When the INT\_COMP bit in the Configuration register is set to 0, the device is in interrupt mode. Changing the device to Interrupt mode from Comparator mode will immediately clear the Alert\_Status register and reset the ALERT pin. The TMP126-Q1 will then behave as described in this section at the next temperature conversion. In this mode, the device compares the temperature result at the end of every conversion with the values in the TLow\_Limit register and THigh\_Limit register. If the temperature result is higher the value in the THigh\_Limit register, the THigh\_Status and THigh\_Flag bits in the Alert\_Status register will be set and the ALERT pin will assert. After a read of the Alert\_Status register the flag bit will clear and the ALERT pin will de-assert. Subsequent temperature results above the hysteresis value (THigh\_Limit - THigh\_Hysteresis), where THigh\_Hysteresis is the Most Significant Byte (MSB) in the Hysteresis register, will not set the THigh\_Flag bit. The status bit will not clear until a temperature result is below (THigh\_Limit - THigh\_Hysteresis).

After a temperature result below (THigh\_Limit - THigh\_Hysteresis), the THigh\_Status bit will clear, the THigh\_Flag bit will be set, and the ALERT pin will be asserted to indicate the change.

If the THigh\_Flag bit is not enabled in the Alert\_Enable register, the flag bit will be set when the measured temperature crosses the THigh\_Limit or hysteresis but the ALERT pin will not assert. The behavior for the TLow\_Limit and Slew rate will be the same as the previously described high limit. Figure 8-7 shows a diagram depicting the behavior.

Figure 8-7. Interrupt Mode Diagram

### 8.4.4.2 Comparator Mode

When the INT\_COMP bit in the Configuration register is set to 0, the device is in comparator mode. Changing the device to Comparator mode from Interrupt mode will immediately clear the Alert\_Status register and reset the ALERT pin. The TMP126-Q1 will then behave as described in this section at the next temperature conversion. In this mode, the device compares the temperature result at the end of every conversion with the limit registers. If the flag is enabled to assert the ALERT, the ALERT will reflect the status bit of the limits. For example, if the THigh\_Flag alert is enabled and the THigh\_Limit is exceeded, the ALERT will assert while the THigh\_Status bit is 1. If the THigh\_Flag alert is not enabled in the Alert\_Enable register, the ALERT will not assert when THigh Status bit is 1.

After a conversion below the Hysteresis the Status bit will be set to '0' and the ALERT will de-assert. Unlike the interrupt mode, the ALERT behavior is not affected when reading the Alert\_Status register. If the Alert flag is disabled in the Alert\_Enable register, the ALERT pin will de-assert immediately if the respective bit is causing an alert. If there are two statuses that are affecting the ALERT such as a THigh\_Limit and Slew\_Rate\_Limit and one of the alerts is disabled, the ALERT will remain asserted until the other limit is not exceeded. For example, if the ALERT has asserted due to a high slew rate and a high temperature and the slew rate alert is then disabled, the ALERT will only de-assert when the temperature drops below the hysteresis value. If both alerts were disabled the ALERT would then de-assert.

Thus, this mode effectively makes the device behave like a high-limit threshold detector. This mode can be used in applications where detecting if the temperature has exceeded a desired threshold is necessary. Figure 8-8 shows a timing diagram of this mode.

Figure 8-8. Comparator Mode Timing Diagram

### 8.5 Programming

## 8.5.1 Temperature Data Format

Temperature data is represented by a 14-bit, two's complement word with an LSB (Least Significant Bit) equal to 0.03125 °C. The last two bits of the register are always 00.

| Table 8-1. 14-Bit Temperature Data Format |                     |      |  |  |  |  |  |

|-------------------------------------------|---------------------|------|--|--|--|--|--|

| Tomporatura                               | Digital Output      |      |  |  |  |  |  |

| Temperature                               | Binary              | Hex  |  |  |  |  |  |

| 175°C                                     | 0101 0111 1000 0000 | 5780 |  |  |  |  |  |

| 150°C                                     | 0100 1011 0000 0000 | 4B00 |  |  |  |  |  |

| 125°C                                     | 0011 1110 1000 0000 | 3E80 |  |  |  |  |  |

| 25°C                                      | 0000 1100 1000 0000 | 0C80 |  |  |  |  |  |

| 0.03125°C                                 | 0000 0000 0000 0100 | 0004 |  |  |  |  |  |

| 0°C                                       | 0000 0000 0000 0000 | 0000 |  |  |  |  |  |

| -0.03125°C                                | 1111 1111 1111 1100 | FFFC |  |  |  |  |  |

| -25°C                                     | 1111 0011 1000 0000 | F380 |  |  |  |  |  |

| -40°C                                     | 1110 1100 0000 0000 | EC00 |  |  |  |  |  |

| −55°C                                     | 1110 0100 1000 0000 | E480 |  |  |  |  |  |

Table 8-1. 14-Bit Temperature Data Format

The first data byte is the most significant byte with most significant bit first, permitting only as much data as necessary to be read to determine temperature condition. For example, if the first four bits of the temperature data indicate an over temperature condition, the host controller could immediately abort communication and take action to remedy the excessive temperature condition.

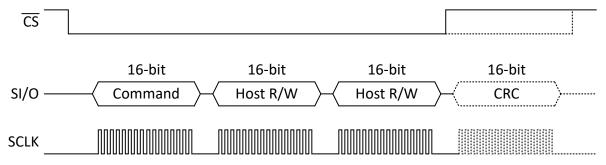

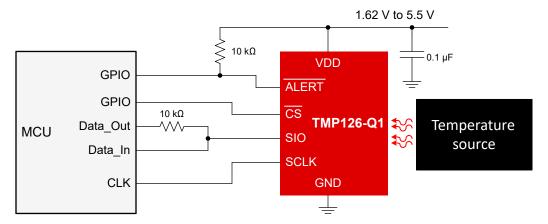

#### 8.5.2 Serial Bus Interface

Figure 8-9 shows an overview of the TMP126-Q1 protocol. The  $\overline{\text{CS}}$  pin must be taken low between communication transactions. Data is clocked out on the falling edge of the serial clock (SCLK), while data is clocked in on the rising edge of SCLK. The 16-bit write words are latched to the respective registers after the 16th rising clock edge including during burst write mode. If a software reset is enabled, the device will immediately reset after the 16th rising clock edge and will not respond to SPI communication until a new falling edge of the  $\overline{\text{CS}}$  is observed. If a software reset is triggered during burst write, any data after the configuration register write will be ignored. The SIO buffer is high impedance during reset.

Each transaction with the TMP126-Q1 will consist of a command word, followed by the data block, and the optional CRC that is enabled in the command word.

Figure 8-9. TMP126-Q1 Communication Overview

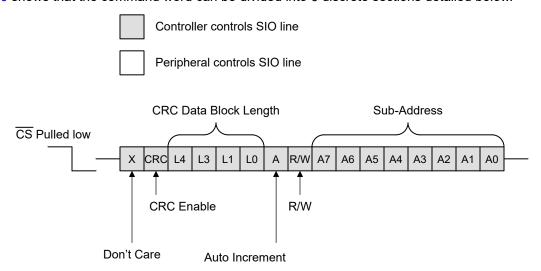

#### 8.5.2.1 Command Word Structure

Figure 8-10 shows that the command word can be divided into 6 discrete sections detailed below.

Figure 8-10. TMP126 Command Word

#### 8.5.2.1.1 Don't Care

Bit 15 of the command word is a don't care and the TMP126-Q1 will ignore this bit.

#### 8.5.2.1.2 CRC Enable

Bit 14 of the command word is the CRC enable bit. Setting this bit to 1 will enable the CRC checksum at the end of the communication as described in the CRC section.

#### 8.5.2.1.3 CRC Data Block Length

Bits [13:10] of the command word is the CRC data block length. These bits are used to indicate how long the transaction will be when the CRC checksum is used. If these bits are all set to 0 or the combination of the bits set to 1 exceeds 1010 (i. e. 1011, 1100, 1101, 1110 or 1111), the CRC enable will be ignored.

#### 8.5.2.1.4 Auto Increment

Bit 9 of the command word is the auto-increment bit.

Setting this bit to 1 will cause the address pointer of the TMP126-Q1 to increment by after every word of data on a read or write transaction. If the bit is set to 0, the address pointer is not incremented and reads/writes will continue to only apply the Sub-Address specified in the command word.

### 8.5.2.1.5 Read/Write

Bit 8 of the command word is the read/write bit.

Setting this bit to 1 will issue a read command. During a read command the TMP126-Q1 will control the SIO pin after the command word. Setting this bit to 0 will issue a write command. During a write command the controller will control the SIO pin and the TMP126-Q1 will internally set the SIO pin to high impedance.

### 8.5.2.1.6 Sub-Address

Bits [7:0] of the command word make up the register Sub-Address.

This is the register map address that will be used for reading or writing data depending on the read/write bit. Writes to Sub-Addresses outside the register map will be ignored. Reads from Sub-Addresses outside the register map will return all '0's.

#### 8.5.2.2 Communication

Communication is initiated by taking the  $\overline{\text{CS}}$  pin low and clocking the SCLK pin. The first 16 bits of the communication are the command word for the TMP126-Q1. The following data will depend on the command byte. If a write command is issued, the TMP126-Q1 will store the data input during the next 16 bits into the appropriate Sub-Address set in the command byte. If the auto-increment bit is set to 1, the address pointer is incremented after every 16-bit word. This allows the system to program all the registers of the TMP126-Q1 in a single burst write command. If the auto-increment is set to 1 for a read command, after each 16-bit word the address pointer is incremented and the next word of data will be from the next Sub-Address.

The following sections denote example write and read operations with the TMP126-Q1.

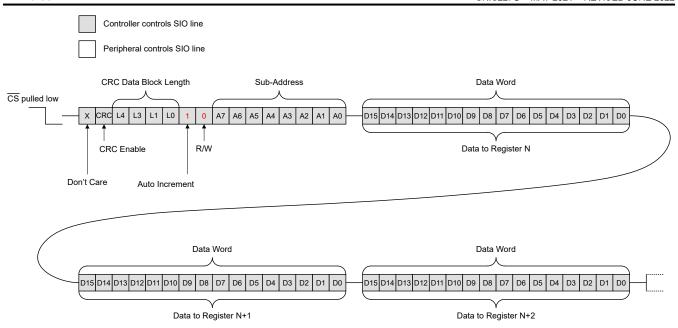

### 8.5.2.3 Write Operations

Data is transmitted to the TMP126-Q1 by setting the R/W bit of the command word to 0. Data can be continuously written to a single register by setting the auto-increment bit to 0 in the command register. Figure 8-11 shows an example of a repeated data write to a single register.

Figure 8-11. Repeated Data Write to a Single Register

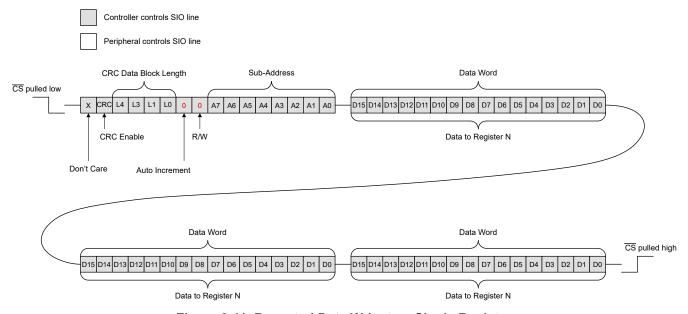

Figure 8-12 shows how setting the auto increment to logic 1 to can enable a write from multiple registers in a single transaction.

Product Folder Links: TMP126-Q1

Figure 8-12. Burst Data Write to Multiple Registers

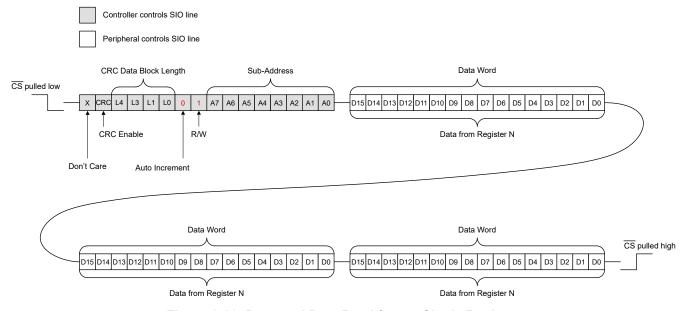

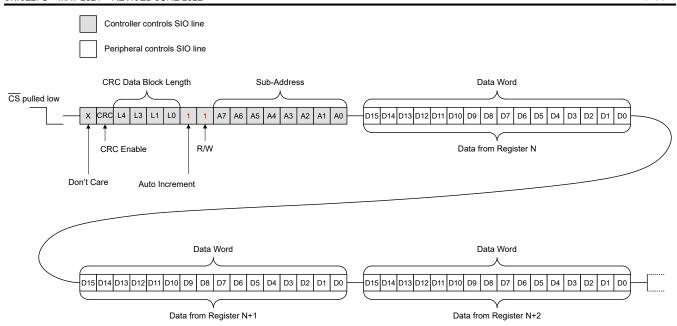

### 8.5.2.4 Read Operations

Data is read from the TMP126-Q1 by setting the R/W bit of the command word to 1. Data can be continuously read from a single register by setting the auto-increment bit to 0 in the command register. Figure 8-13 shows an example of a repeated data read from a single register. Repeated temperature reads are not supported.

Figure 8-13. Repeated Data Read from a Single Register

Figure 8-14 shows how setting the auto increment to 1 to can enable a read from multiple registers in a single transaction.

Figure 8-14. Burst Data Read from Multiple Registers

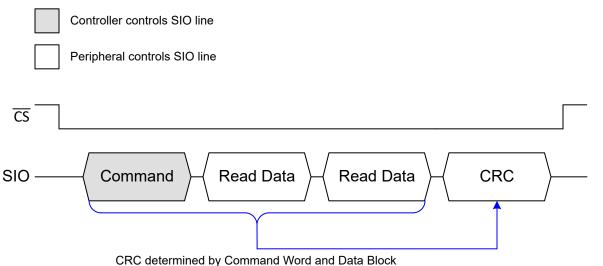

### 8.5.2.5 Cyclic Redundancy Check (CRC)

The TMP126-Q1 has an optional CRC feature to determine the integrity of the data that has been transmitted across the SPI communication interface. The CRC for the TMP126-Q1 is enabled by setting the CRC bit in the command word to 1. When enabled, the TMP126-Q1 will append a 16-bit CRC checksum to the end the data block for read transactions. The controller can then compare this checksum to their own calculation and determine if the transaction was valid. During a write transaction, the host will append the 16-bit CRC checksum. The TMP126-Q1 will compare this to its own checksum. If there is a mismatch, the TMP126 will discard the write transaction and set a CRC fault ALERT to indicate to the host that the transaction failed. The host will need to send the register settings again to correctly program the TMP126-Q1. Reading the Alert\_Status register will clear the CRC Fault bit and de-assert the ALERT pin.

An overview of a CRC enabled write transaction is shown below with a data block length of 2.

Controller controls SIO line

Peripheral controls SIO line

CS

SIO

Command

Write Data

Write Data

CRC

CRC determined by Command word and Data Block

Figure 8-15. CRC Enabled Write

An overview of a CRC enabled read transaction is shown below with a data block length of 2.

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

termined by Command Word and Data Block

### 8.5.2.5.1 Cyclic Redundancy Check Implementation

Table 8-2 defines the CRC calculation rule.

Table 8-2. CRC Rule Table

Figure 8-16. CRC Enabled Read

| Temperature           | Digital Output                                                 |

|-----------------------|----------------------------------------------------------------|

| CRC Width             | 16 bits                                                        |

| Polynomial            | X <sup>16</sup> + X <sup>12</sup> + X <sup>5</sup> + 1 (1021h) |

| Initial seed value    | FFFFh                                                          |

| Input data reflected  | No                                                             |

| Result data reflected | No                                                             |

| XOR value             | 0000h                                                          |

| Example               | CRC of 0xABCD = 0xD46A                                         |

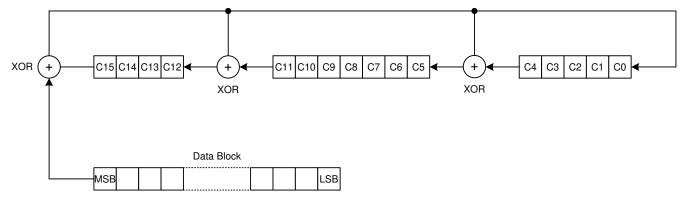

Figure 8-17 shows the CRC Module block diagram. The CRC calculation is done on the command word and the data block. The module consists of a 16-bit shift register and 3 exclusive-OR gates. The register starts with the seed value FFFFh and the module performs an XOR function and shifts its content until the last bit of the register string is used. The final value of the shift register checksum is output onto the SIO line by the TMP126-Q1 at the end of the data block for the host to validate the transaction.

Figure 8-17. CRC Module

The following is an example of C code programming example to calculative the communication CRC:

```

#include <stdio.h>

void main(int argc, char *argv[]){

unsigned short crc = 0xFFFF;

unsigned int msg[20];

int msglen = (argc > 1)? (argc - 1) : 1;

msg[0] = 0x0CE8;

for (int i = 1; i < argc; i++){

sscanf(argv[i], "%X", &msg[i-1]);

for (int byte = 0; byte < msglen; byte++){

crc ^= msg[byte];

printf("msgbyte: 0x%X\n", msg[byte]);

for (int bit = 0; bit < 16; bit++){

// printf("crc: 0x%X byte: %d bit: %d\n", crc, byte, bit);

if (crc & 0x8000)

crc = (crc << 1) ^ 0x1021;

else

crc = (crc << 1);</pre>

printf("crc: 0x%X\n",crc);

```

Figure 8-18. CRC Calculation C Code Example

# 8.6 Register Map

Table 8-3. TMP126-Q1 Registers

| ADDRESS | TYPE | RESET | ACRONYM       | REGISTER NAME                        | SECTION |

|---------|------|-------|---------------|--------------------------------------|---------|

| 00h     | R    | 0000h | Temp_Result   | Temperature result register          | Go      |

| 01h     | R    | 0000h | Slew_Result   | Slew rate result register            | Go      |

| 02h     | R/RC | 0000h | Alert_Status  | Alert status register                | Go      |

| 03h     | R/W  | 0006h | Configuration | Configuration register               | Go      |

| 04h     | R/W  | 0016h | Alert_Enable  | Alert enable register                | Go      |

| 05h     | R/W  | F380h | TLow_Limit    | Temperature low limit register       | Go      |

| 06h     | R/W  | 2A80h | THigh_Limit   | Temperature high limit register      | Go      |

| 07h     | R/W  | 0A0Ah | Hysteresis    | Hysteresis register                  | Go      |

| 08h     | R/W  | 0500h | Slew_Limit    | Temperature slew rate limit register | Go      |

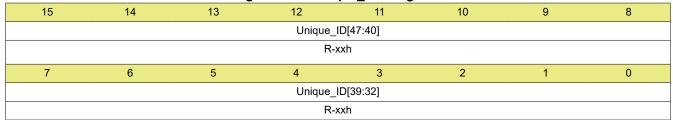

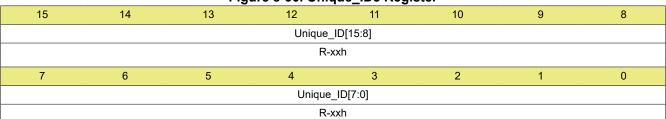

| 09h     | R    | xxxxh | Unique_ID1    | Unique ID1 register                  | Go      |

| 0Ah     | R    | xxxxh | Unique_ID2    | Unique ID2 register                  | Go      |

| 0Bh     | R    | xxxxh | Unique_ID3    | Unique ID3 register                  | Go      |

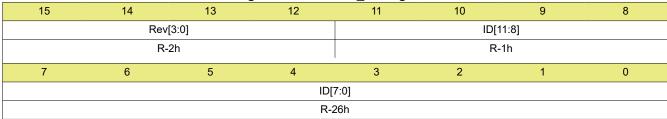

| 0Ch     | R    | 2126h | Device_ID     | Device ID register                   | Go      |

| 10h-2Ah | R    | xxxxh | Reserved      | Reserved                             |         |

Table 8-4. TMP126-Q1 Access Type Codes

| Tuble 0 4: Tim 120 Q1 Access Type Godes |         |                                        |  |  |  |  |

|-----------------------------------------|---------|----------------------------------------|--|--|--|--|

| Access Type                             | Code    | Description                            |  |  |  |  |

| Read Type                               |         |                                        |  |  |  |  |

| R                                       | R       | Read                                   |  |  |  |  |

| RC                                      | R<br>C  | Read<br>to Clear                       |  |  |  |  |

| R-0                                     | R<br>-0 | Read<br>Returns 0s                     |  |  |  |  |

| Write Type                              |         |                                        |  |  |  |  |

| W                                       | W       | Write                                  |  |  |  |  |

| Reset or Default Value                  |         |                                        |  |  |  |  |

| -n                                      |         | Value after reset or the default value |  |  |  |  |

## 8.6.1 Temp\_Result Register (Address = 00h) [reset = 0000h]

This register stores the latest temperature conversion result in a 14-bit two's complement format with a LSB (Least Significant Bit) equal to 0.03125°C.

Return to Register Map.

Figure 8-19. Temp\_Result Register

|                  |                   |     |     | <u></u> |    |      |       |

|------------------|-------------------|-----|-----|---------|----|------|-------|

| 15               | 14                | 13  | 12  | 11      | 10 | 9    | 8     |

|                  | Temp_Result[13:6] |     |     |         |    |      |       |

|                  | R-00h             |     |     |         |    |      |       |

| 7                | 7 6 5 4 3 2 1 0   |     |     |         |    |      | 0     |

| Temp_Result[5:0] |                   |     |     |         |    | Rese | erved |

|                  |                   | R-0 | 00h |         |    | R-0  | )0b   |

Table 8-5. Temp\_Result Register Field Descriptions

| Bit  | Field             | Туре | Reset | Description                                                                                                                                                      |

|------|-------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:2 | Temp_Result[13:0] | R    | 0000h | 14-bit temperature conversion result. Temperature data is represented by a 14-bit, two's complement word with an LSB (Least Significant Bit) equal to 0.03125°C. |

| 1:0  | Reserved          | R    | 00b   | These two bits will always read 00b                                                                                                                              |

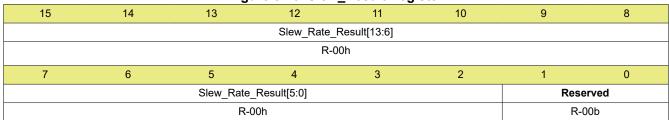

### 8.6.2 Slew\_Result Register (Address = 01h) [reset = 0000h]

This register shows the latest slew rate calculation. Two consecutive measurements in continuous conversion mode are required before a result is shown. When not in continuous conversion mode the register will return to the default value.

The slew rate result is depicted in 14-bit twos-complement format with the LSB equal to 0.03125°C/s. The TMP126 does not accurately report negative slew rate values and bit 13 of the output result can be used to indicate a negative slew rate but the output value cannot be guaranteed.

Return to Register Map.

Figure 8-20. Slew Result Register

Table 8-6. Slew\_Result Register Field Descriptions

| Bit  | Field                  | Туре | Reset | Description                                                                                                                                                                  |

|------|------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:2 | Slew_Rate_Result[13:0] | R    | 0000h | Temperature slew rate result. Temperature slew rate is represented by a 14-bit, twoscomplement word with an LSB (Least Significant Bit) equal to 0.03125°C/s. Format is°C/s. |

| 1:0  | Reserved               | R    | 00b   | Reserved                                                                                                                                                                     |

Product Folder Links: TMP126-Q1

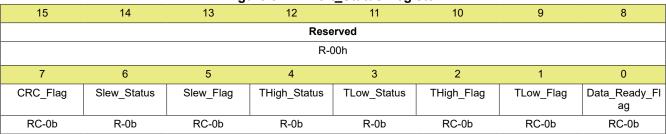

## 8.6.3 Alert\_Status Register(Address = 02h) [reset = 0000h]

This register show the current alert status of the TMP126-Q1. This register will currently only clear with a single register read without auto increment.

Return to Register Map.

Figure 8-21. Alert\_Status Register

Table 8-7. Alert Status Register Field Descriptions

|      | Table 8-7. Alert_Status Register Field Descriptions |      |       |                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------|-----------------------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit  | Field                                               | Type | Reset | Description                                                                                                                                                                                                                                                                                                                                                |  |  |

| 15:8 | Reserved                                            | R    | 00h   | Reserved                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 7    | CRC_Flag                                            | RC   | Ob    | CRC checksum error flag indicator. This indicates that the write transaction CRC checksum failed and the register settings were discarded.  0b = The most recent CRC enabled write transaction was successful.  1b = The most recent CRC enabled write transaction failed.                                                                                 |  |  |

| 6    | Slew_Pos_Status                                     | R    | Ob    | Positive slew rate status indicator. This bit is set if there is a positive slew rate exceeding the Slew_Rate_Limit.  Ob: The most recent temperature conversion result is below the Slew_Rate_Limit.  1b: The most recent temperature conversion result is above the Slew_Rate_Limit.                                                                     |  |  |

| 5    | Slew_Flag                                           | RC   | Ob    | Slew rate flag indicator. This indicates that the current there was a temperature slew rate beyond the slew rate limit threshold. Reading Alert_Status register will clear this bit.  0b = The most recent temperature conversion has not crossed the Slew_Rate_Limit threshold.  1b = A temperature conversion has crossed the Slew_Rate_Limit threshold. |  |  |

| 4    | THigh_Status                                        | R    | Ob    | High temperature status indicator.  0b: The most recent temperature conversion result is below the Thigh_Limit  1b: The most recent temperature conversion is above the THigh_Limit. Once set, this bit will not clear until a temperature conversion is below THigh_Limit - THigh_Hyst                                                                    |  |  |

| 3    | TLow_Status                                         | R    | Ob    | Low temperature status indicator.  0b: The most recent temperature conversion result is above the TLow_Limit  1b: The most recent temperature conversion is below the THigh_Limit. Once set, this bit will not clear until a temperature conversion is above TLow_Limit + TLow_Hyst                                                                        |  |  |

## Table 8-7. Alert\_Status Register Field Descriptions (continued)

| Bit | Field           | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | THigh_Flag      | RC   | Ob    | High temperature flag indicator. This indicates that the latest temperature conversion has cross above the THigh_Limit register threshold or crossed below the THigh_Limit - THigh_Hyst threshold. Reading Alert_Status register will clear this bit.  0b = The most recent temperature conversion has not crossed the THigh_Limit or the hysteresis threshold.  1b: A temperature conversion crossed the THigh_Limit or crossed below the THigh_Limit - THigh_Hyst threshold. Once the THigh_Flag is set, THigh_Flag will not be set again until a temperature conversion is below THigh_Limit - THigh_Hyst |

| 1   | TLow_Flag       | RC   | Ob    | Low temperature flag indicator. This indicates that the latest temperature conversion has cross below the TLow_Limit register threshold or crossed above the Tlow_Limit + TLow_Hyst threshold. Reading Alert_Status register will clear this bit.  0b = The most recent temperature conversion has not crossed the TLow_Limit or the hysteresis threshold.  1b: A temperature conversion crossed below the TLow_Limit.  Once the TLow_Flag is set, TLow_Flag will not be set again until temperature conversion is above TLow_Limit + TLow_Hyst                                                              |

| 0   | Data_Ready_Flag | RC   | 0b    | Data Ready flag indicator. This indicates that there is an unread temperature conversion. Reading Alert_Status register or the Temperature Results register will clear this bit.  0b = Data in Temp_Result has been read already  1b = Data in Temp_Result is unread                                                                                                                                                                                                                                                                                                                                         |

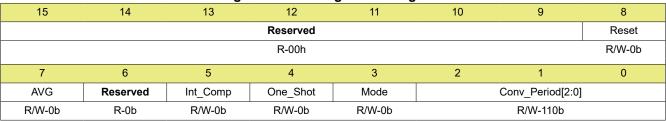

# 8.6.4 Configuration Register (Address = 03h) [reset = 0006h]

This register is used to configuration the operation of the TMP126-Q1.

Return to Register Map.

Figure 8-22. Configuration Register

**Table 8-8. Configuration Register Field Descriptions**

|      |                  |      |       | egister Field Descriptions                                                                                                                                                                                                                                        |

|------|------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit  | Field            | Туре | Reset | Description                                                                                                                                                                                                                                                       |

| 15:9 | Reserved         | R    | 00h   | Reserved                                                                                                                                                                                                                                                          |

| 8    | Resets           | R/W  | 0b    | Software reset bit.  When set to 1b it triggers software reset with a duration of 0.5 ms.  This bit will always read back 0b                                                                                                                                      |

| 7    | AVG              | R/W  | 0b    | Averaging enable bit. Averaging will force every measurement including one-shot measurements to be averaged with eight conversions.  Ob: Averaging is disabled  1b: Averaging is enabled                                                                          |

| 6    | Reserved         | R    | 0b    | Reserved                                                                                                                                                                                                                                                          |

| 5    | Int_Comp         | R/W  | 0b    | Interrupt or comparator mode select  0b = Interrupt mode  1b = Comparator mode                                                                                                                                                                                    |

| 4    | One_Shot         | R/W  | 0b    | One-shot conversion trigger. Triggering a one-shot conversion will place the TMP126-Q1 into shutdown mode after the conversion completes. This bit will always read 0h.  0b = Default  1b = Trigger a one-shot conversion                                         |

| 3    | Mode             | R/W  | 0b    | Conversion mode selection bit.  0b = Continuous conversion mode  1b = Shutdown mode                                                                                                                                                                               |

| 2:0  | Conv_Period[2:0] | R/W  | 110b  | Conversion period setting. This bit field changes the conversion period of the TMP126-Q1.  000b = 6 ms  001b = 31.25 ms / 32 Hz  010b = 62.5 ms / 16 Hz  011b = 125 ms / 8 Hz  100b = 250 ms / 4 Hz  101b = 500 ms / 2 Hz  110b = 1 s / 1 Hz  111b = 2 s / 0.5 Hz |

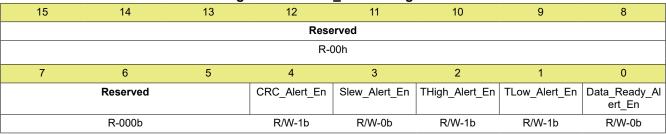

## 8.6.5 Alert\_Enable Register(Address = 04h) [reset = 0016h]

This register configures which flags of the Alert\_Status register are enabled or disabled. Disabling an Alert flag will cause the ALERT pin to not assert when that flag bit is set. If the flag is enabled the ALERT pin will assert when that flag is set. The flag bit will still be set in the register when the Alert functionality is disabled for that bit.

Currently if there is an active alert on the ALERT pin and the enable for that alert is set to 0b, the TMP126-Q1 will not the de-assert the pin until the status register is read or a new conversion occurs.

Return to Register Map.

Figure 8-23. Alert\_Enable Register

Table 8-9. Alert\_Enable Register Field Descriptions

|      | Table 8-9. Alert_Enable Register Field Descriptions |      |       |                                                                                                                                                                                                            |  |  |  |

|------|-----------------------------------------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Field                                               | Туре | Reset | Description                                                                                                                                                                                                |  |  |  |

| 15:5 | Reserved                                            | R    | 000h  | Reserved                                                                                                                                                                                                   |  |  |  |

| 4    | CRC_Alert_En                                        | R/W  | 1b    | Enables the CRC_Flag alert to assert the ALERT pin.  0b = CRC_Flag ALERT disabled  1b = CRC_Flag ALERT enabled                                                                                             |  |  |  |

| 3    | Slew_Alert_En                                       | R/W  | Ob    | Enables the Slew_Flag assert the ALERT pin while in interrupt mode. When in comparator mode, enables the Slew_Status to assert the ALERT.  Ob = Slew_Flag ALERT disabled  1b = Slew_Flag ALERT enabled     |  |  |  |

| 2    | THigh_Alert_En                                      | R/W  | 1b    | Enables the THigh_Flag assert the ALERT pin while in interrupt mode. When in comparator mode, enables the THigh_Status to assert the ALERT.  Ob = THigh_Flag Alert disabled  1b = THigh_Flag Alert enabled |  |  |  |

| 1    | TLow_Alert_En                                       | R/W  | 1b    | Enables the TLow_Flag assert the ALERT pin while in interrupt mode. When in comparator mode, enables the TLow_Status to assert the ALERT.  Ob = TLow_Flag Alert disabled  1b = TLow_Flag Alert enabled     |  |  |  |

| 0    | Data_Ready_Alert_En                                 | R/W  | Ob    | Enables the Data_Ready_Flag to assert the ALERT pin.  0b = Data_Ready Alert disabled  1b = Data_Ready Alert enabled                                                                                        |  |  |  |

Product Folder Links: TMP126-Q1

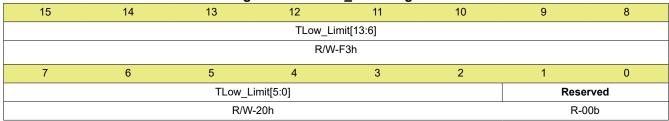

# 8.6.6 TLow\_Limit Register(Address = 05h) [reset = F380h]

This register is used to configuration the low temperature limit of the TMP126-Q1. The limit is formatted in a 14-bit two's complement format with a LSB (Least Significant Bit) equal to 0.03125°C. This is the same format as the TEMP\_RESULT register. The range of the register is ±256°C. The default value on start-up is F380h or -25°C. If the THigh\_Limit register is equal to or less than the TLow\_Limit register the temperature limits will be ignored until configured such that THigh\_Limit is greater than TLow\_Limit.

Return to Register Map.

Figure 8-24. TLow\_Limit Register

Table 8-10. TLow\_Limit Register Field Descriptions

| Bit  | Field            | Туре | Reset | Description                                                  |

|------|------------------|------|-------|--------------------------------------------------------------|

| 15:2 | TLow_Limit[13:0] | R/W  | 3CE0h | 14-bit temperature low limit setting.                        |

|      |                  |      |       | Temperature low limit is represented by a 14-bit, two's      |

|      |                  |      |       | complement word with an LSB (Least Significant Bit) equal to |

|      |                  |      |       | 0.03125°C. The default setting for this is -25°C.            |

| 1:0  | Reserved         | R    | 00b   | These two bits will always read 00b                          |

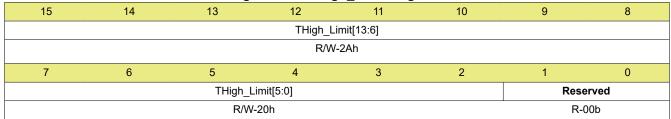

### 8.6.7 THigh\_Limit Register(Address = 06h) [reset = 2A80h]

This register is used to configuration the high temperature limit of the TMP126-Q1. The limit is formatted in a 14-bit two's complement format with a LSB (Least Significant Bit) equal to 0.03125°C. This is the same format as the Temp\_Result register. The range of the register is ±256°C. The default value on start-up is 2A80h or 85°C. If the THigh\_Limit register is equal to or less than the TLow\_Limit register the temperature limits will be ignored until configured such that THigh\_Limit is greater than TLow\_Limit.

Return to Register Map.

Figure 8-25. THigh\_Limit Register

Table 8-11. Thigh Limit Register Field Descriptions

|      | rabio o fili filigiimint flogicioi filora zocompanono |      |       |                                                                                                                                                                         |  |  |  |

|------|-------------------------------------------------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit  | Field                                                 | Туре | Reset | Description                                                                                                                                                             |  |  |  |

| 15:2 | THigh_Limit[13:0]                                     | R/W  |       | 14-bit temperature high limit setting. Temperature high limit is represented by a 14-bit, two's complement word with an LSB (Least Significant Bit) equal to 0.03125°C. |  |  |  |

| 1:0  | Reserved                                              | R    | 00b   | These two bits will always read 00b                                                                                                                                     |  |  |  |

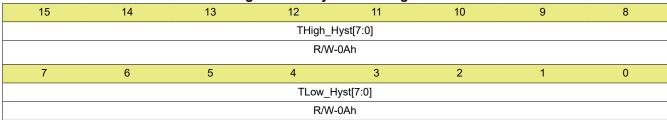

### 8.6.8 Hysteresis Register (Address = 07h) [reset = 0A0Ah]

This register sets the hysteresis for the THigh\_Limit threshold and the TLow\_Limit threshold. The default hysteresis value for both the high and low limits is equal to 5 °C.

The Hysteresis is in a 8-bit unsigned format with the LSB equal to 0.5°C. This gives a maximum value of 127.5°C of hysteresis.

Return to Register Map.

Figure 8-26. Hysteresis Register

Table 8-12. Hysteresis Register Field Descriptions

| Bit  | Field           | Туре | Reset | Description                                                                                                                                                                                                                                   |

|------|-----------------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | THigh_Hyst[7:0] | R/W  | 0Ah   | THigh_Limit Hysteresis setting. Hysteresis value is represented by a unsigned Byte with the LSB equal to 0.5°C. The High temperature limit hysteresis threshold is equal to (THigh_Limit - THigh_Hyst). The default hysteresis value is 5 °C. |

| 7:0  | TLow_Hyst[7:0]  | R/W  | 0Ah   | TLow_Limit Hysteresis setting. Hysteresis value is represented by a unsigned Byte with the LSB equal to 0.5°C. The Low temperature limit hysteresis threshold is equal to (TLow_Limit + TLow_Hyst). The default hysteresis value is 5 °C.     |

Product Folder Links: TMP126-Q1

## 8.6.9 Slew\_Limit Register (Address = 08h) [reset = 0500h]

This register is used to configure the temperature slew rate limit of the TMP126-Q1. The limit is formatted in a 13-bit unsigned format with the LSB (Least Significant Bit) equal to 0.03125°C/s. The range of the register is 0°C to +256°C. The default value on start-up is 0140h or 10°C/s. The slew rate limit will trigger a slew rate alert on positive slew rates that are greater than the unsigned limit as enabled by the Alert\_Enable register.

Return to Register Map.

Figure 8-27. Slew\_Limit Register

| 15       | 14                    | 13        | 12   | 11   | 10  | 9 | 8 |

|----------|-----------------------|-----------|------|------|-----|---|---|

| Reserved | Slew_Rate_Limit[12:6] |           |      |      |     |   |   |

| R-0b     | R/W-05h               |           |      |      |     |   |   |