www.ti.com

# Industrial Temp, Single Port 10/100 Mb/s Ethernet Physical Layer Transceiver

Check for Samples: TLK100

#### 1 Introduction

#### 1.1 Features

- Temperature From -40°C to 85°C

- Low Power Consumption, < 200mW Typical</li>

- Cable Diagnostics

- Error-Free Operation up to 200 Meters Under Typical Conditions

- 3.3V MAC Interface

- Auto-MDIX for 10/100 Mb/s

- Energy Detection Mode

- 25 MHz Clock Out

- MII Serial Management Interface (MDC and MDIO)

- IEEE 802.3u MII

- IEEE 802.3u Auto-Negotiation and Parallel Detection

- IEEE 802.3u ENDEC, 10BASE-T Transceivers and Filters

- Bus I/O Protection ±16kV JEDEC HBM

- IEEE 802.3u PCS, 100BASE-TX Transceivers

- Enables IEEE1588 Time-Stamping

- IEEE 1149.1 JTAG

- Integrated ANSI X3.263 Compliant TP-PMD Physical Sublayer with Adaptive Equalization and Baseline Wander Compensation

- Programmable LED Support Link, 10/100 Mb/s Mode, Activity, and Collision Detect

- 10/100 Mb/s Packet BIST (Built in Self Test)

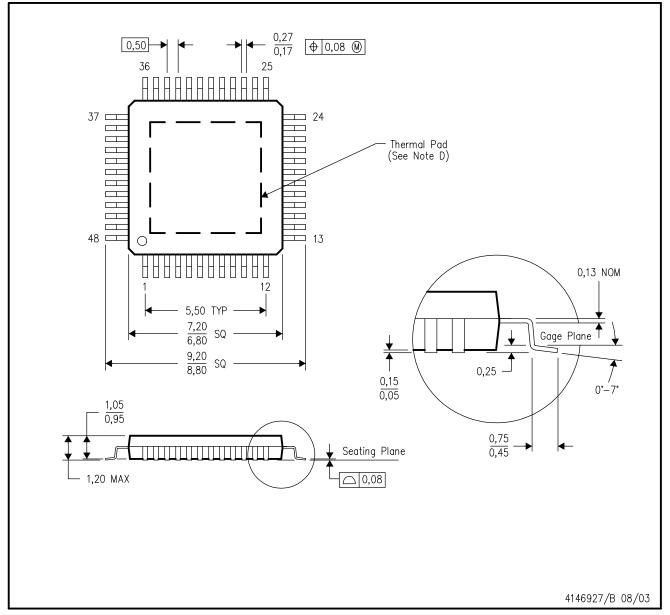

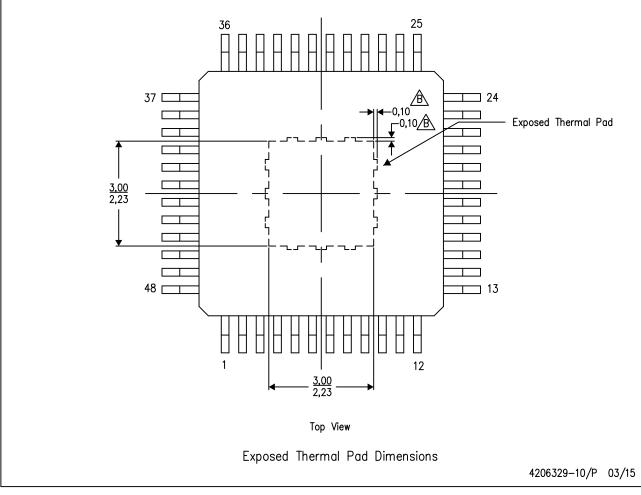

- 48-pin TQFP Package (7mm) x (7mm)

## 1.2 Applications

- Industrial Controls and Factory Automation

- General Embedded Applications

# 1.3 General Description

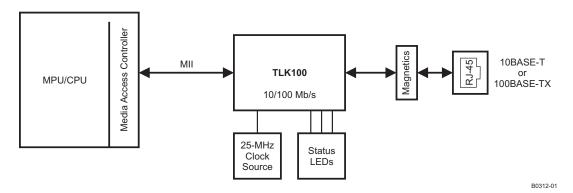

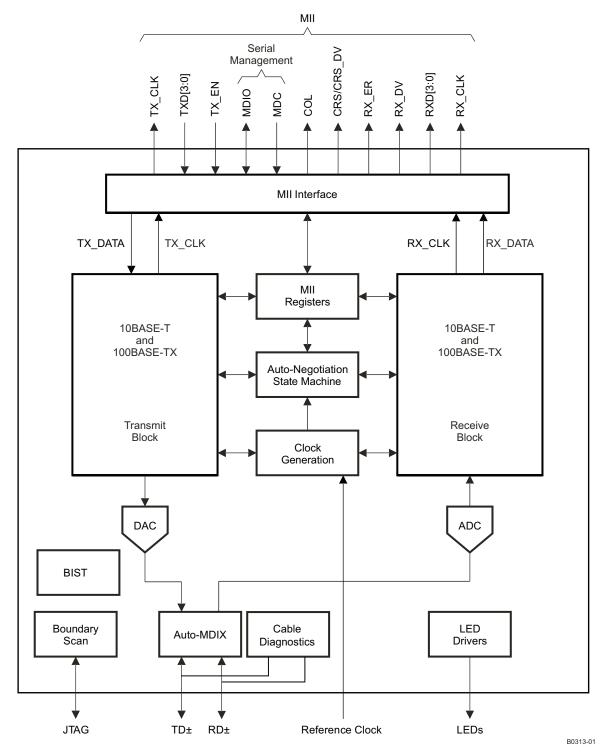

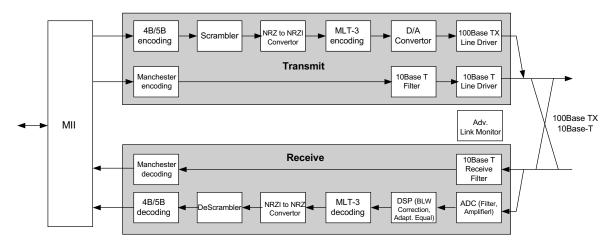

The TLK100 is a single-port Ethernet PHY for 10BaseT and 100Base TX signaling. It integrates all the physical-layer functions needed to transmit and receive data on standard twisted-pair cables. This device supports the standard Media Independent Interface (MII) for direct connection to a Media Access Controller (MAC).

The TLK100 is designed for power-supply flexibility, and can operate with a single 3.3V power supply or with combinations of 3.3V, 1.8V, and 1.1V power supplies for reduced power operation.

The TLK100 uses mixed-signal processing to perform equalization, data recovery, and error correction to achieve robust operation over CAT 5 twisted-pair wiring. It not only meets the requirements of IEEE 802.3, but maintains high margins in terms of cross-talk and alien noise.

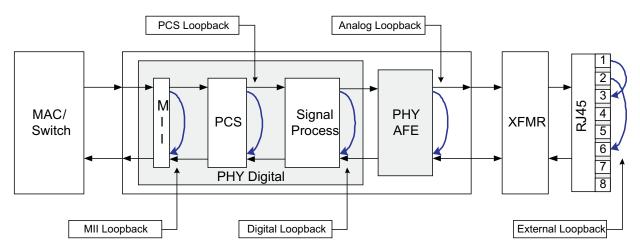

# 1.4 System Diagram

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

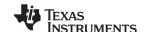

Figure 1-1. TLK100 Functional Block Diagram

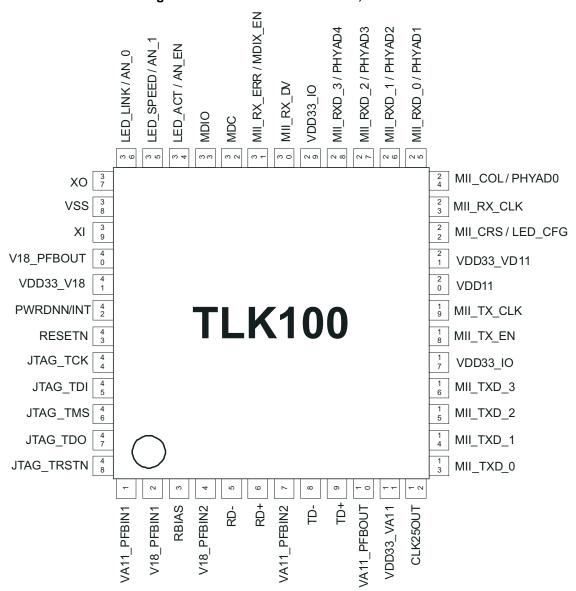

# 1.5 Pin Layout

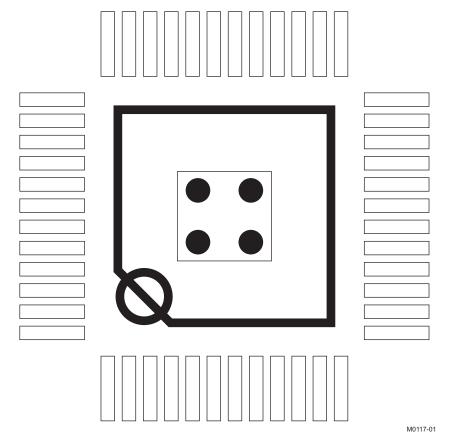

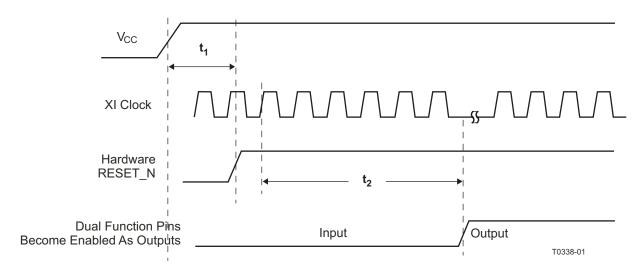

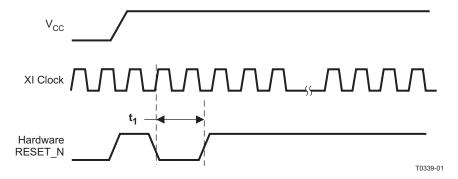

Figure 1-2. TLK100 PIN DIAGRAM, TOP VIEW

# SLLS931B-AUGUST 2009-REVISED DECEMBER 2009

| 1 | Intro | duction                            | <u>1</u>  |     | 5.1   | Transmit Path Encoder                    | <u>26</u> |

|---|-------|------------------------------------|-----------|-----|-------|------------------------------------------|-----------|

|   | 1.1   | Features                           | <u>1</u>  |     | 5.2   | Receive Path Decoder                     | <u>28</u> |

|   | 1.2   | Applications                       | 1         |     | 5.3   | 10M Squelch                              | <u>30</u> |

|   | 1.3   | General Description                | 1         |     | 5.4   | Auto MDI/MDI-X Crossover                 | _         |

|   | 1.4   | System Diagram                     | 1         |     | 5.5   | Auto Negotiation                         |           |

|   | 1.5   | Pin Layout                         | _         | 6   | Rese  | et and Power Down Operation              |           |

| 2 | -     | Descriptions                       | _         |     | 6.1   | Hardware Reset                           | <u>34</u> |

|   | 2.1   | Serial Management Interface        | 5         |     | 6.2   | Software Reset                           | _         |

|   | 2.2   | MAC Data Interface                 | _         |     | 6.3   | Power Down/Interrupt                     |           |

|   | 2.3   | Clock Interface                    | _         | _   | 6.4   | Power Down Modes                         |           |

|   | 2.4   | LED Interface                      | _         | 7   |       | gn Guidelines                            |           |

|   |       | JTAG Interface                     | _         |     | 7.1   | TPI Network Circuit                      | _         |

|   | 2.5   |                                    | _         |     | 7.2   | Clock In (XI) Requirements               |           |

|   | 2.6   | Reset and Power Down               | _         |     | 7.3   | Thermal Vias Recommendation              | _         |

|   | 2.7   | Jumper Options                     | <u>8</u>  | 8   | _     | ster Block                               | _         |

|   | 2.8   | 10 Mb/s and 100 Mb/s PMD Interface | 9         |     | 8.1   | Register Definition                      | <u>43</u> |

|   | 2.9   | Power and Bias Connections         | 9         |     | 8.2   | Register Control Register (REGCR)        | <u>52</u> |

|   | 2.10  | Power Supply Configuration         | <u>10</u> |     | 8.3   | Address or Data Register (ADDAR)         |           |

| 3 | Conf  | iguration 1                        | 13        |     | 8.4   | Extended Registers                       |           |

|   | 3.1   | Auto-Negotiation                   | 13        |     | 8.5   | Cable Diagnostic Registers               |           |

|   | 3.2   | Auto-MDIX                          | 14        | 9   | Elect | rical Specifications                     | <u>69</u> |

|   | 3.3   | PHY Address                        | —<br>15   |     | 9.1   | ABSOLUTE MAXIMUM RATINGS                 | <u>69</u> |

|   | 3.4   | LED Interface                      | —<br>16   |     | 9.2   | THERMAL CHARACTERISTICS                  | <u>69</u> |

|   | 3.5   | Loopback Functionality             |           |     | 9.3   | RECOMMENDED OPERATING CONDITIONS $\dots$ | <u>69</u> |

|   | 3.6   | BIST                               |           |     | 9.4   | DC CHARACTERISTICS                       | <u>70</u> |

|   | 3.7   | Cable Diagnostics                  |           |     | 9.5   | POWER SUPPLY CHARACTERISTICS             | <u>70</u> |

| 4 | Inter | faces                              |           |     | 9.6   | AC Specifications                        | <u>71</u> |

|   | 4.1   | Media Independent Interface (MII)  | <u> </u>  | 10  |       | endix A: Digital Spectrum Analyzer (DSA) |           |

|   | 4.2   | Serial Management Interface        |           |     |       | ut                                       |           |

| 5 | Arch  | itecture                           | 26        | Rev | ision | History                                  | <u>84</u> |

|   |       |                                    |           |     |       |                                          |           |

www.ti.com

## 2 Pin Descriptions

The TLK100 pins are classified into the following interface categories (each interface is described in the sections that follow):

- Serial Management Interface

- MAC Data Interface

- Clock Interface

- LED Interface

- JTAG Interface

- · Reset and Power Down

- Configuration (Jumper) Options

- 10/100 Mb/s PMD Interface

- Special Connect Pins

- · Power and Ground pins

Note: Configuration pin option. See Section 2.7 for *Jumper Definitions*.

The definitions below define the functionality of each pin.

Type: I Input

Type: O Output

Type: I/O Input/Output

Type: OD Open Drain

Type: PD, PU Internal Pulldown/Pullup

Type: S Configuration Pin (All configuration pins have weak internal pullups or pulldowns. If

a different default value is needed, then use an external  $2.2k\Omega$  resistor. See

Section 2.7 for details.)

# 2.1 Serial Management Interface

| Р    | PIN |      | DESCRIPTION                                                                                                                                                                                                                                |  |  |  |  |

|------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME | NO. | TYPE | DESCRIPTION                                                                                                                                                                                                                                |  |  |  |  |

| MDC  | 32  | I    | MANAGEMENT DATA CLOCK: Clock signal for the management data input/output (MDIO) interface. The maximum MDC rate is 25 MHz; there is no minimum MDC rate. MDC is <b>not</b> required to be synchronous to the MII_TX_CLK or the MII_RX_CLK. |  |  |  |  |

| MDIO | 33  | I/O  | <b>MANAGEMENT DATA I/O:</b> Bidirectional command / data signal synchronized to MDC. Either the local controller or the TLK100 may drive the MDIO signal. This pin requires a pull-up resistor with value 1.5 k $\Omega$ .                 |  |  |  |  |

# 2.2 MAC Data Interface

| PIN NAME NO.                                                                 |                      | TYPE                                                                              | DECCRIPTION                                                                                                                                                                                       |  |  |

|------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                              |                      | TTPE                                                                              | DESCRIPTION                                                                                                                                                                                       |  |  |

| MII_TX_CLK                                                                   | 19                   | O, PD                                                                             | MII TRANSMIT CLOCK: : MII Transmit Clock provides 25MHz or 2.5MHz reference clock depending on the speed.                                                                                         |  |  |

| MII_TX_EN                                                                    | 18                   | I, PD                                                                             | MII TRANSMIT ENABLE: MII_TX_EN is presented on the rising edge of the MII_TX_CLK . It indicates the presence of valid data inputs on MII_TXD[3:0]. It is an active high signal.                   |  |  |

| MII_TXD_0<br>MII_TXD_1<br>MII_TXD_2<br>MII_TXD_3                             | 13<br>14<br>15<br>16 | IS, I, PD                                                                         | MII TRANSMIT DATA: The transmit data nibble received from the MAC that is synchronous to the rising edge of the MII_TX_CLK.                                                                       |  |  |

| MII_RX_CLK                                                                   | 23                   | 0                                                                                 | MII RECEIVE CLOCK: MII receive clock provides a 25MHz or 2.5MHz reference condepending on the speed, that is derived from the received data stream.                                               |  |  |

| MII_RX_DV                                                                    | 30                   | S, O, PD                                                                          | MII RECEIVE DATA VALID: This pin indicates valid data is present on the corresponding MII_RXD[3:0].                                                                                               |  |  |

| MII_RX_ERR/MDIX_EN                                                           | 31                   | S, O, PU                                                                          | MII RECEIVE ERROR: This pin indicates that an error symbol has been detected within a received packet.                                                                                            |  |  |

| MII_RXD_0/PHYAD1<br>MII_RXD_1/PHYAD2<br>MII_RXD_2/PHYAD3<br>MII_RXD_3/PHYAD4 | 25<br>26<br>27<br>28 | S, O, PD                                                                          | MII RECEIVE DATA: Symbols received on the cable are decoded and presented on these pins synchronous to MII_RX_CLK. They contain valid data when MII_RX_DV is asserted.                            |  |  |

| MII_CRS/LED_CFG 22 S, O, PU MII CARRIER SENSE: This pin is asserted high who |                      | MII CARRIER SENSE: This pin is asserted high when the receive medium is non-idle. |                                                                                                                                                                                                   |  |  |

| MII_COL/PHYAD0                                                               | 24                   | S, O, PU                                                                          | MII COLLISION DETECT: In Full Duplex Mode this pin is always low. In 10BASE-T/100BASE-TX half-duplex modes, this pin is asserted HIGH only when both the transmit and receive media are non-idle. |  |  |

# 2.3 Clock Interface

| PIN      | PIN NAME NO. |   | DESCRIPTION                                                                                                                                                                                                                                                               |  |  |  |

|----------|--------------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     |              |   |                                                                                                                                                                                                                                                                           |  |  |  |

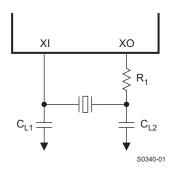

| XI       | 39           | I | CRYSTAL/OSCILLATOR INPUT: Reference clock. 25MHz ±50 ppm tolerance crystal reference or oscillator input. The TLK100 supports either an external crystal resonator connected across pins XI and XO, or an external CMOS-level oscillator source connected to pin XI only. |  |  |  |

| хо       | 37           | 0 | CRYSTAL OUTPUT: Reference Clock output. XO pin is used for crystal only. This pin should be left floating when an oscillator input is connected to XI.                                                                                                                    |  |  |  |

| CLK25OUT | 12           | 0 | 25 MHz CLOCK OUTPUT: In MII mode, this pin provides a 25 MHz clock output to the system. This allows other devices to use the reference clock from the TLK100 without requiring additional clock sources.                                                                 |  |  |  |

# 2.4 LED Interface

(See Table 3-3 for LED Mode Selection)

| PIN                       |    | TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                             |  |  |

|---------------------------|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                      |    |          |                                                                                                                                                                                                                                                                                                         |  |  |

| LED_LINK/AN_0             | 36 | S, O, PU | This pin indicates the status of the link in Mode 1. When the link is good the LED will be ON. In Mode 2 and Mode 3, this pin indicates transmit and receive activity in addition to the status of the Link. The LED is ON when Link is good. It will blink when the transmitter or receiver is active. |  |  |

| LED_SPEED/AN_1            | 35 | S, O, PU | This pin indicates the speed of the link. It is ON when the link speed is 100 Mb/s and OFF when it is 10 Mb/s.                                                                                                                                                                                          |  |  |

| LED_ACT/AN_EN 34 S, O, PU |    | S, O, PU | In mode 1 this pin indicates if there is any activity on the link. It is ON (pulse) when activity is present on either Transmit or Receive channel. In Mode 3, this LED output may be programmed to indicate Full-duplex status.                                                                        |  |  |

www.ti.com

# 2.5 JTAG Interface

| PIN            |     | TYPE  | DESCRIPTION                                                                             |  |  |  |  |

|----------------|-----|-------|-----------------------------------------------------------------------------------------|--|--|--|--|

| NAME           | NO. | ITPE  | DESCRIPTION                                                                             |  |  |  |  |

| JTAG_TCK       | 44  | I, PU | This pin is the test clock. This pin has a weak internal pullup.                        |  |  |  |  |

| JTAG_TDI       | 45  | I, PU | This pin is the test data input. This pin has a weak internal pullup.                   |  |  |  |  |

| JTAG_TDO       | 47  | 0     | This pin is the test data output.                                                       |  |  |  |  |

| JTAG_TMS       | 46  | I, PU | This pin selects the test mode. This pin has a weak internal pullup.                    |  |  |  |  |

| JTAG_TRST<br>N | 48  | I, PU | This pin is an active low asynchronous test reset. This pin has a weak internal pullup. |  |  |  |  |

# 2.6 Reset and Power Down

| PIN NAME NO. |                                                                                      | TYPE      | DESCRIPTION                                                                                                                                                                                                                                  |  |  |  |

|--------------|--------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|              |                                                                                      | ITPE      |                                                                                                                                                                                                                                              |  |  |  |

| RESETN       | 43                                                                                   | I, PU     | This pin is an active Low reset input that initializes or re-initializes all the internal registers of tTLK100. Asserting this pin low for at least 1 µs will force a reset process to occur. All jumper options are reinitialized as well.  |  |  |  |

|              |                                                                                      |           | Register access is required for this pin to be configured either as power down or as an interrupt. The default function of this pin is power down.                                                                                           |  |  |  |

| PWRDNN/INT   | 42                                                                                   | I, OD, PU | When this pin is configured for a power down function, an active low signal on this pin will put the device is power down mode.                                                                                                              |  |  |  |

|              | When this pin is configured as an condition occurs. The pin has an condition occurs. |           | When this pin is configured as an interrupt pin then this pin is asserted low when an interrupt condition occurs. The pin has an open-drain output with a weak internal pull-up. Some applications may require an external pull-up resistor. |  |  |  |

# 2.7 Jumper Options

Jumper option is an elegant way to configure the TLK100 into specific modes of operation. Some of the functional pins are used as jumper options. The logic states of these pins are sampled during reset and are used to configure the device into specific modes of operation. Below table shows the pins used for the jumper option and its description. The functional pin name is indicated in parentheses.

A 2.2 k $\Omega$  resistor should be used for pull-down or pull-up to change the default jumper option. If the default option is required, then there is no need for external pull-up or pull down resistors. Since these pins may have alternate functions after reset is deasserted, they should not be connected directly to VCC or GND.

| PIN -                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | TYPE     |                                                                                                                                                                                                                                                                               |             |      |      |                                                                                                                      |                                                        |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NAME NO.                   |          |                                                                                                                                                                                                                                                                               | DESCRIPTION |      |      |                                                                                                                      |                                                        |  |

| PHYAD0 (MII_COL) PHYAD1 (MII_RXD_0) PHYAD2 (MII_RXD_1) PHYAD3 (MII_RXD_2) PHYAD4 (MII_RXD_3)                                                                                                                                                                                                                                                                                                                                                             | 24<br>25<br>26<br>27<br>28 | S, O, PD | The TLK100 provides five PHY address pins, the states of which are latched into an internal register at system hardware reset. The TLK100 supports PHY Address jumpering values 0 (<00000>) through 31 (<11111>). All PHYAD[4:0] pins have weak internal pull-down resistors. |             |      |      |                                                                                                                      |                                                        |  |

| <ul> <li>AN_EN: When high, this puts the part into advertised Auto-Negotiatic capability set by AN_0 and AN_1 pins. When low, this puts the part the capability set by AN_0 and AN_1 pins.</li> <li>AN_0 / AN_1: These input pins control the forced or advertised of TLK100 according to the following table. The value on these pins is input pins to GND (0) or VCC (1) through 2.2 kΩ resistors. These pronnected directly to GND or VCC.</li> </ul> |                            |          |                                                                                                                                                                                                                                                                               |             |      |      | . When low, this puts the part into Foins.  rol the forced or advertised operatile. The value on these pins is set b | orced Mode with<br>ing mode of the<br>y connecting the |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               |             |      |      | d into the Basic Mode Control R<br>ster during Hardware-Reset.                                                       | Register and the                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          | The default is 111 since these pins have internal pull-ups.                                                                                                                                                                                                                   |             |      |      |                                                                                                                      |                                                        |  |

| AN EN (LED ACT)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 34                         |          |                                                                                                                                                                                                                                                                               | AN_EN       | AN_1 | AN_0 | Forced Mode                                                                                                          |                                                        |  |

| AN_1 (LÈD_SPEED)                                                                                                                                                                                                                                                                                                                                                                                                                                         | 35                         | S, O, PU |                                                                                                                                                                                                                                                                               | 0           | 0    | 0    | 10BASE-T, Half-Duplex                                                                                                |                                                        |  |

| AN_0 (LED_LINK)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                         |          |                                                                                                                                                                                                                                                                               | 0           | 0    | 1    | 10BASE-T, Full-Duplex                                                                                                |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | 0           | 1    | 0    | 100BASE-TX, Half-Duplex                                                                                              |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | 0           | 1    | 1    | 100BASE-TX, Full-Duplex                                                                                              |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | AN_EN       | AN_1 | AN_0 | Advertised Mode                                                                                                      |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | 1           | 0    | 0    | 10BASE-T, Half/Full-Duplex                                                                                           |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | 1           | 0    | 1    | 10BASE-TX, Half/Full-Duplex                                                                                          |                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               |             | 1    | 1    | 0                                                                                                                    | 10BASE-T, Half-Duplex<br>100BASE-TX, Half-Duplex       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |          |                                                                                                                                                                                                                                                                               | 1           | 1    | 1    | 10BASE-T, Half/Full-Duplex<br>100BASE-TX, Half/Full-Duplex                                                           |                                                        |  |

| LED_CFG (MII_CRS)                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22                         | S, O, PU | This jumpering option along with LEDCR register bit determines the mode of operation of the LED pins. Default is Mode 1. All modes are also configurable via register access. See the table in the LED Interface Section.                                                     |             |      |      |                                                                                                                      |                                                        |  |

| MDIX_EN (MII_RX_ERR)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                         | S, O, PU | This jumpering option sets the Auto-MDIX mode. By default it enables MDIX. An external pull-down will disable Auto-MDIX mode.                                                                                                                                                 |             |      |      |                                                                                                                      |                                                        |  |

www.ti.com

# 2.8 10 Mb/s and 100 Mb/s PMD Interface

| PIN      | PIN               |      | DESCRIPTION                                                                                                                                                       |  |  |  |  |

|----------|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME     | NO.               | TYPE | DESCRIPTION                                                                                                                                                       |  |  |  |  |

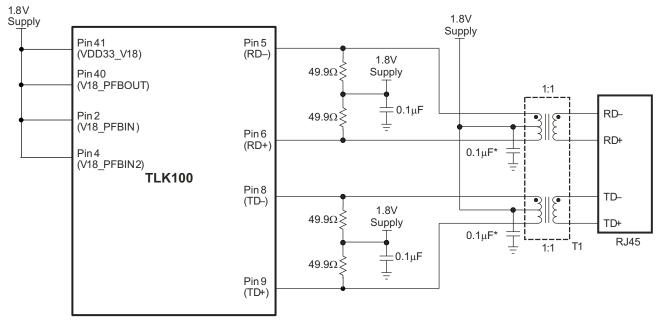

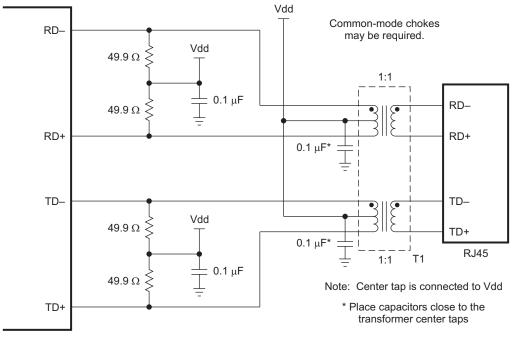

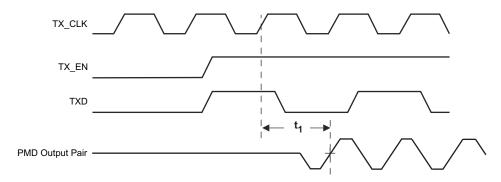

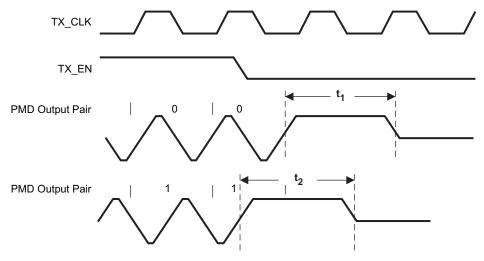

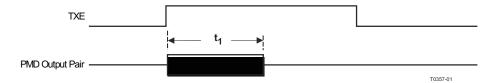

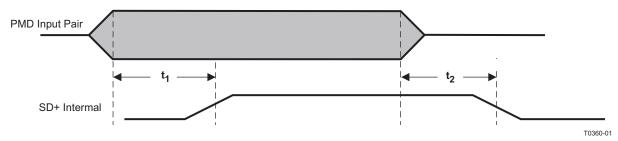

| TD TD+   | TD-, TD+ 8, 9 I/O |      | Differential common driver transmit output (PMD Output Pair). These differential outputs are automatically configured to either 10BASE-T or 100BASE-TX signaling. |  |  |  |  |

| 10-, 10+ | 0, 9              | 1/0  | In Auto-MDIX mode of operation, this pair can be used as the Receive Input pair. These pins require 1.8V or 3.3V bias for operation.                              |  |  |  |  |

| RD RD+   | 5, 6              | I/O  | Differential receive input (PMD Input Pair). These differential inputs are automatically configured to accept either 100BASE-TX or 10BASE-T signaling.            |  |  |  |  |

| KD-, KD+ | ა, ხ              |      | In Auto-MDIX mode of operation, this pair can be used as the Transmit Output pair. These pins require 1.8V or 3.3V bias for operation.                            |  |  |  |  |

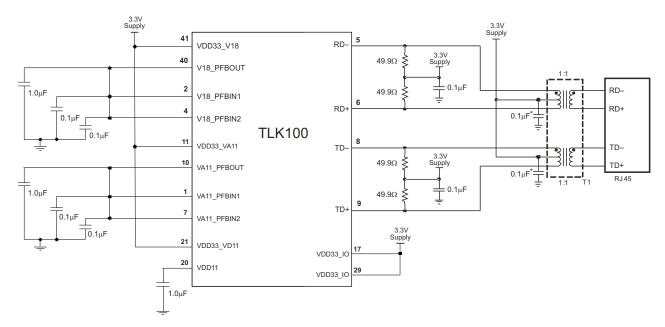

# 2.9 Power and Bias Connections

| PIN         |          | T)/DE | DESCRIPTION                                                                                                                                                                                                                                                     |  |  |  |

|-------------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME NO.    |          | TYPE  |                                                                                                                                                                                                                                                                 |  |  |  |

| RBIAS       | 3        | I     | Bias Resistor Connection. Use a 4.99kΩ 1% resistor connected from RBIAS to GND.                                                                                                                                                                                 |  |  |  |

| V18_PFBOUT  | 40       | 0     | 1.8V Power Feedback Output. A 1µF capacitor (ceramic preferred), should be placed close to the V18_PFBOUT.                                                                                                                                                      |  |  |  |

|             |          |       | In single supply operation, connect this pin should be connected to V18_PFBIN1 and V18_PFBIN2 (pin 2 and pin 4). See Figure 2-1 for proper placement pin.                                                                                                       |  |  |  |

|             |          |       | In multiple supply operation, when supplying 1.8V from external supply, this pin should be connected together with VDD33_V18 (pin 41), V18_PFBIN1 and V18_PFBIN2 (pin 2 and pin 4) to the 1.8V external supply source. See Figure 2-2 for proper placement pin. |  |  |  |

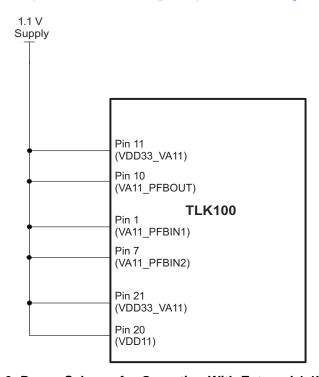

| VA11_PFBOUT | 10       | 0     | 1.1V Analog Power Feedback Output. A 1 $\mu F$ capacitor (Ceramic preferred), should be placed close to the VA11_PFBOUT.                                                                                                                                        |  |  |  |

|             |          |       | In single supply operation this pin should be connected to VA11_PFBIN1 and V11_PFBIN2 (pin 1 and pin 7). See Figure 2-1 for proper placement pin.                                                                                                               |  |  |  |

|             |          |       | In multiple supply operation, when supplying 1.1V from external supply, this pin should be connected together with VDD33_VA11 (pin 11), V11_PFBIN1 and V11_PFBIN2 (pin 1 and pin 7) to 1.1V external supply source. See Figure 2-3 for proper placement pin.    |  |  |  |

| V18_PFBIN1  | 2        |       | 1.8V Power Feedback Input. These pins are fed with power from V18_PFBOUT (pin 40) in single supply operation.                                                                                                                                                   |  |  |  |

| V18_PFBIN2  | 4        | I     | 1.8V from external source in multiple supply operation. A small $1\mu F$ capacitor should be connected close to each pin.                                                                                                                                       |  |  |  |

| VA11_PFBIN1 | 1        | _     | 1.1V Analog Power Feedback Input. These pins are fed with power from: VA11_PFBOUT (pin 10) in single supply operation.                                                                                                                                          |  |  |  |

| VA11_PFBIN2 | 7        | '     | 1.1V from external source in multiple supply operation. A small capacitor of 0.1 $\mu F$ should be connected close to each pin.                                                                                                                                 |  |  |  |

| VDD11       | 20       | 0     | 1.1V Core Power Output. A capacitor of 1µF (Ceramic preferred) , should be placed close to the VDD11                                                                                                                                                            |  |  |  |

| VDD33_IO    | 17<br>29 | Р     | I/O 3.3V Supply                                                                                                                                                                                                                                                 |  |  |  |

| VDD33_VA11  | 11       | Р     | External supply input to 1.1V analog regulator This pin should be connected to 3.3V or 2.5V external supply, in single supply operation. In multiple supply operation this pin should be connected to external 1.1V supply source.                              |  |  |  |

| VDD33_V18   | 41       | Р     | External supply input to 1.8V regulator In single supply operation, this pin should be connected to a 3.3V or 2.5V external supply. In multiple supply operation this pin should be connected to an external 1.8V supply source.                                |  |  |  |

| VDD33_VD11  | 21       | Р     | External supply input to 1.1V Core regulator This pin should be connected to 3.3V or 2.5V external supply, in single supply operation. In multiple supply operation this pin should be connected to external 1.1V supply source.                                |  |  |  |

| VSS         | 38       | Р     | Ground pin for Oscillator                                                                                                                                                                                                                                       |  |  |  |

| GNDPAD      | 49       | Р     | Ground Pad                                                                                                                                                                                                                                                      |  |  |  |

# 2.10 Power Supply Configuration

The TLK100 provides best-in-class flexibility of power supplies.

• Single supply operation – If a single 3.3V power supply is desired, the TLK100 will sense the presence of the supply and configure the internal voltage regulators to provide all necessary supply voltages. To operate in this mode, connect the TLK100 supply pins according to the following scheme:

Figure 2-1. Power Scheme for Single Supply Operation

- Multiple Supply operation When additional 1.8V and/or 1.1V external power rails are available, the TLK100 can be configured in various ways as given in Table 2-1. This gives the highest flexibility for the user and enables significant reduction in power consumption. When using multiple external supplies, the internal regulators must be disabled by appropriate device connections.

- When an external 1.8V rail is available Connect the external 1.8V to all following TLK100 pins to enable proper operation: V18\_PFBOUT (pin 40), V18\_PFBIN1 (pin 2), V18\_PFBIN2 (pin 4) and VDD33\_V18 (pin 41). In addition, connect the 1.8V rail to the transformer center tap to further reduce the transmission power, as shown in Figure 2-2:

Figure 2-2. Power Scheme for Operation With External 1.8V Supply

External 1.1V rail – When external 1.1V rail is available – Connect the external 1.1V to the following pins: VA11\_PFBOUT (pin 10), VDD11 (pin 20), VA11\_PFBIN1 (pin 1), VA11\_PFBIN2 (pin 7), VDD33\_VA11 (pin 11) and VDD33\_VD11 (pin 21) as shown in Figure 2-3:

Figure 2-3. Power Scheme for Operation With External 1.1V Supply

• Lowest-power operation – When 1.1V and 1.8V supplies are already available in addition to 3.3V, designers can take advantage of the lowest-power configuration of the TLK100. By supplying external 1.8 and 1.1V as explained above, all the internal regulators are powered down and the device is fully driven by the external supplies giving the lowest power operation.

Other power supply options – Because the TLK100 incorporates independent voltage regulators, designers may take advantage of several optional configurations, depending on available power supplies. See Table 2-1 for these options.

**Table 2-1. Power Supply Options**

| Mada                        | MAC I/F<br>(3.3V)         | Transformer CT (3.3V or 1.8V) | (                     | 1.8V)                     | (1.1V)                 |                           |  |

|-----------------------------|---------------------------|-------------------------------|-----------------------|---------------------------|------------------------|---------------------------|--|

| Mode                        | Voltage Source            | Voltage Source                | Regulator<br>(ON/OFF) | Voltage Source            | Regulators<br>(ON/OFF) | Voltage Source            |  |

| Single Supply<br>Operation  | 3.3V from external supply | 3.3V from external supply     | ON                    | 3.3V from external supply | ON                     | 3.3V from external supply |  |

|                             | 3.3V from external supply | 3.3V from external supply     | ON                    | 3.3V from external supply | ON                     | 2.5V from external supply |  |

|                             | 3.3V from external supply | 3.3V from external supply     | ON                    | 3.3V from external supply | OFF                    | 1.1V from external supply |  |

|                             | 3.3V from external supply | 3.3V from external supply     | ON                    | 2.5V from external supply | ON                     | 3.3V from external supply |  |

|                             | 3.3V from external supply | 3.3V from external supply     | ON                    | 2.5V from external supply | ON                     | 2.5V from external supply |  |

|                             | 3.3V from external supply | 3.3V from external supply     | ON                    | 2.5V from external supply | OFF                    | 1.1V from external supply |  |

|                             | 3.3V from external supply | 1.8V from external supply     | OFF                   | 1.8V from external supply | ON                     | 3.3V from external supply |  |

|                             | 3.3V from external supply | 1.8V from external supply     | OFF                   | 1.8V from external supply | ON                     | 2.5V from external supply |  |

| Lowest Power<br>Consumption | 3.3V from external supply | 1.8V from external supply     | OFF                   | 1.8V from external supply | OFF                    | 1.1V from external supply |  |

When operating with multiple supplies, it is recommended that the 3.3V supply ramps up at least 200ms before the 1.8V and 1.1V supplies ramp up.

www.ti.com

## 3 Configuration

This section includes information on the various configuration options available with the TLK100. The configuration options described below include:

- Auto-Negotiation

- Auto-MDIX

- PHY Address

- LED Interface

- Loopback Functionality

- BIST

- · Cable Diagnostics

# 3.1 Auto-Negotiation

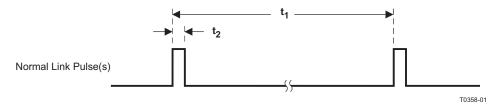

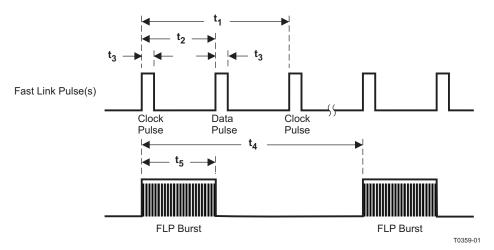

The TLK100 device can auto-negotiate to operate in 10BASE-T or 100BASE-TX. If Auto-Negotiation is enabled, then the TLK100 device negotiates with the link partner to determine the speed and duplex with which to operate. If the link partner is unable to Auto-Negotiate, the TLK100 device would go into the parallel detect mode to determine the speed of the link partner. Under parallel detect mode, the duplex mode is fixed at half-duplex.

The TLK100 supports four different Ethernet protocols (10 Mb/s Half Duplex, 10 Mb/s Full Duplex, 100 Mb/s Half Duplex, and 100 Mb/s Full Duplex), so the inclusion of Auto-Negotiation ensures that the highest performance protocol will be selected based on the advertised ability of the Link Partner. The Auto-Negotiation function within the TLK100 can be controlled either by internal register access or by the use of the AN\_EN, AN\_1 and AN\_0 pins.

The state of AN\_EN, AN\_0 and AN\_1 pins determines whether the TLK100 is forced into a specific mode or Auto-Negotiation will advertise a specific ability (or set of abilities) as given in Table 2-1. These pins allow configuration options to be selected without requiring internal register access. The state of AN\_EN, AN\_0 and AN\_1, upon power-up/reset, determines the state of bits [8:5] of the ANAR register (0x04h).

AN\_EN AN\_0  $AN_1$ **Forced Mode** 0 0 0 10BASE-T, Half-Duplex 0 0 10BASE-T, Full-Duplex 1 0 1 0 100BASE-TX, Half-Duplex 0 1 1 100BASE-TX, Full-Duplex AN\_EN AN\_1 AN\_0 **Advertised Mode** 0 1 0 10BASE-T, Half/Full-Duplex 1 1 10BASE-TX, Half/Full-Duplex 0 0 1 10BASE-T, Half Duplex 1 100BASE-TX, Half Duplex 10BASE-T, Half/Full-Duplex 1 1 1

100BASE-TX, Half/Full-Duplex

**Table 3-1. Auto-Negotiation Modes**

The Auto-Negotiation function can also be controlled by internal register access using registers as defined by the IEEE 802.3u specification. For further detail regarding Auto-Negotiation, see Clause 28 of the IEEE 802.3u specification.

#### 3.2 **Auto-MDIX**

The TLK100 device automatically determines whether or not it needs to cross over between pairs so that an external crossover cable is not required. If the TLK100 device interoperates with a device that implements MDI/MDIX crossover, a random algorithm as described in IEEE 802.3 determines which device performs the crossover.

Auto-MDIX is enabled by default and can be configured via jumper or via PHYCR (0x10h) register, bits [6:5].

The crossover can be manually forced through bit 5 of PHYCR (0x10h) register. Neither Auto-Negotiation nor Auto-MDIX is required to be enabled in forcing crossover of the MDI pairs.

Auto-MDIX can be used in the forced 100BT mode but not in the forced MDIX mode. As in modern networks all the nodes are 100BT, having the Auto-MDIX working in the forced 100BT mode will resolve the link faster without the need for the long Auto-Negotiation.

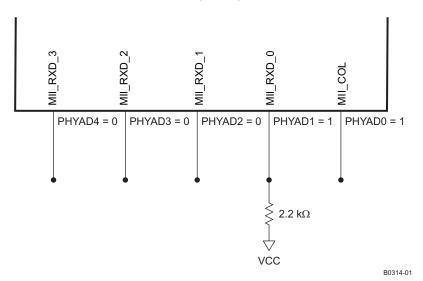

#### 3.3 PHY Address

The 5 PHY address inputs pins are shared with the MII\_RXD[3:0] pins and COL pin as shown in Table 3-2.

**Table 3-2. PHY Address Mapping**

| PIN# | PHYAD FUNCTION | RXD FUNCTION |

|------|----------------|--------------|

| 24   | PHYAD0         | MII_COL      |

| 25   | PHYAD1         | MII_RXD_0    |

| 26   | PHYAD2         | MII_RXD_1    |

| 27   | PHYAD3         | MII_RXD_2    |

| 28   | PHYAD4         | MII_RXD_3    |

Each TLK100 or port sharing an MDIO bus in a system must have a unique physical address. With 5 address input pins, the TLK100 can support PHY Address values 0 (<00000>) through 31 (<11111>). The address-pin states are latched into an internal register at device power-up and hardware reset. Because all the PHYAD[4:0] pins have weak internal pull-down resistors, the default setting for the PHY address is 00000 (0x00h).

See Figure 3-1 for an example of a PHYAD connection to external components. In this example, the PHYAD configuration results in address 00010 (0x02h).

Figure 3-1. PHYAD Configuration Example

#### 3.4 **LED Interface**

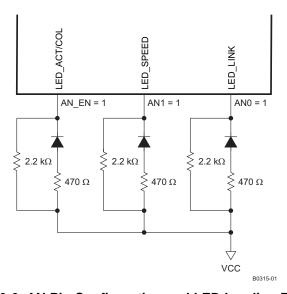

The TLK100 supports three configurable Light Emitting Diode (LED) pins. The device supports three LED configurations: Link, Speed, and Activity. Functions are multiplexed among the LEDs into three modes. The LEDs can be controlled by configuration pin and/or internal register bits. Bits 6:5 of the LED Direct Control register (LEDCR) selects the LED mode as described in Table 3-3.

| Mode | LED_CFG[1]<br>(bit 6) | LED_CFG[0]<br>(bit 5) or (pin 22) | LED_LINK                               | LED_SPEED                        | LED_ACT                                      |

|------|-----------------------|-----------------------------------|----------------------------------------|----------------------------------|----------------------------------------------|

| 1    | don't care            | 1                                 | ON for Good Link<br>OFF for No Link    | ON in 100 Mb/s<br>OFF in 10 Mb/s | ON Pulse for Activity<br>OFF for No Activity |

| 2    | 0                     | 0                                 | ON for Good Link<br>BLINK for Activity | ON in 100 Mb/s<br>OFF in 10 Mb/s | None                                         |

| 3    | 1                     | 0                                 | ON for Good Link<br>BLINK for Activity | ON in 100 Mb/s<br>OFF in 10 Mb/s | ON for Full Duplex<br>OFF for Half Duplex    |

Table 3-3. LED Mode Select

The LED LINK pin in Mode 1 indicates the link status of the port. It is OFF when no LINK is present. In Mode 2 and Mode 3 it is ON to indicate Link is good and BLINK to indicate activity is present on either transmit or receive channel. The blink rate is decided by the bits 9:8 of the LEDCR register (0x18). The default blink rate is 5Hz.

The LED SPEED pin indicates 10 or 100 Mb/s data rate of the port. This LED is ON when the device is operating in 100 Mb/s operation. The functionality of this LED is independent of mode selected.

The LED ACT pin in Mode 1 indicates the presence of either transmit or receive activity. The LED is ON (Pulse) for Activity and OFF for No Activity. The width of the pulse is determined by the bits 14:13 of the LEDCR register (0x18). The default pulse width is 200ms. In mode 3 this pin indicates the Duplex status of operation. The LED is ON for Full Duplex and OFF for Half Duplex.

Bits 2:0 of the LEDCR register defines the polarity of the signals on the LED pins.

Since the Auto-Negotiation (AN) configuration options share the LED output pins, the external components required for configuration-pin programming and those for LED usage must be considered in order to avoid contention.

See Figure 3-2 for an example of AN connections to external components. In this example, the AN programming results in Auto-Negotiation with 10/100 Half/Full-Duplex advertised.

Figure 3-2. AN Pin Configuration and LED Loading Example

# 3.5 Loopback Functionality

The TLK100 provides several options for Loopback that test and verify various functional blocks within the PHY. Enabling loopback mode allows in-circuit testing of the TLK100 digital and analog data path. Generally, the TLK100 may be configured to one of the Near-end loopback modes or to the Far-end (reverse) loopback.

### 3.5.1 Near-End Loopback

Near-end loopback provides the ability to loop the transmitted data back to the receiver via the digital or analog circuitry. The point at which the signal is looped back is selected using loopback control bits with several options being provided. Figure 3-3 shows the PHY near-end loopback functionality.

Figure 3-3. Block Diagram, Near-End Loopback Mode

The Near-end Loopback mode is selected by setting the respective bit in the BIST Control Register (BISCR), MII register address 0x16. Bits 3:0 of the BISCR register are used to set the loopback mode according to the following:

- Bit [0]: MII Loopback

- Bit [1]: PCS Loopback (in 100BaseTX only)

- Bit [2]: Digital Loopback

- Bit [3]: Analog Loopback

While in Loopback mode the data is looped back and also transmitted onto the media. To ensure proper operation in Analog Loopback mode  $100\Omega$  terminations should be attached to the RJ45 connector.

**External Loopback** can be performed while working in normal mode (Bits 3:0 of the BISCR register are assert to 0 and on RJ45 connector pin 1 is shorted to pin 3 and pin 2 is shorted to pin 6).

To maintain the desired operating mode, Auto-Negotiation should be disabled before selecting Loopback mode. This is not relevant for external-loopback mode.

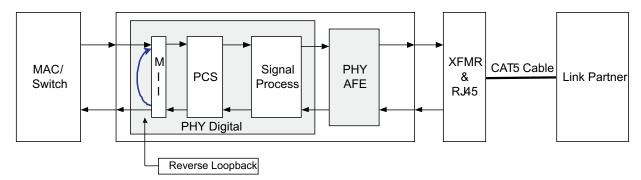

### 3.5.2 Far-End Loopback

Far-end (Reverse) loopback is a special test mode to allow testing the PHY from link partner side. In this mode data that is received from the link partner pass through the PHY's receiver, looped back on the MII and transmitted back to the link partner. Figure 3-4 shows Far-end loopback functionality.

Figure 3-4. Block Diagram, Far-End Loopback Mode

The Reverse Loopback mode is selected by setting bit 4 in the BIST Control Register (BISCR), MII register address 0x16.

While in Reverse Loopback mode the data is looped back and also transmitted onto the MAC Interface and all data signals that come from the MAC are ignored.

### 3.6 BIST

The TLK100 incorporates an internal PRBS Built-in Self Test (BIST) circuit to accommodate in-circuit testing or diagnostics. The BIST circuit can be utilized to test the integrity of the transmit and receive data paths. The BIST testing can be performed using both internal loopback (digital or analog) or external loop back using a cable fixture. The BIST simulates a real data transfer scenarios using real packets on the lines. The BIST allows full control of the packets lengths and of the Inter Packet Gap (IPG)

The BIST is implemented with independent transmit and receive paths, with the transmit block generating a continuous stream of a pseudo random sequence. The TLK100 generates a 23-bit pseudo random sequence for doing the BIST test. The received data is compared to the generated pseudo-random data by the BIST Linear Feedback Shift Register (LFSR) to determine the BIST pass/fail status. The number of error bytes that the PRBS checker received is stored in the BISECR register (0x72h). The number of transmitted bytes that the PRBS checker received is stored in the BISBCR register (0x71h). The status of whether the PRBS checker is locked to the incoming receive bit stream, whether the PRBS is in sync or not and whether the packet generator is busy or not can be found by reading the BISSR register (0x17h).

The PRBS test can be put in a continuous mode or single mode by using the bit 15 of the BISCR register (0x16h). In the continuous mode, when one of the PRBS counter reaches the maximum value the counter starts counting from zero again. In the single mode when the PRBS counter reaches its maximum value the PRBS checker stops counting.

TLK100 allows the user to control the length of the PRBS packet. By programming the BISPLR register (0x7Bh) register one can set the length of the PRBS packet. There is also an option to generate a single packet transmission of two types 64 and 1518 bytes through register bit – bit13 of the BISCR register (0x16h). The single generated packet is composed of a constant data.

## 3.7 Cable Diagnostics

With the vast deployment of Ethernet devices, the need for reliable, comprehensive and user-friendly cable diagnostic tool is more important than ever. The wide variety of cables, topologies, and connectors deployed results with the need to non-intrusively identify and report cable faults. TI cable diagnostic unit provides extensive information about cable integrity.

The TLK100 offers the following capabilities in its Cable Diagnostic tools kit:

- 1. Time Domain Reflectometry (TDR).

- 2. Active Link Cable Diagnostic (ALCD).

- 3. Digital Spectrum Analyzer (DSA)

#### 3.7.1 TDR

The TLK100 uses Time Domain Reflectometry (TDR) to determine the quality of the cables, connectors, and terminations in addition to estimation of the cable length. Some of the possible problems that can be diagnosed include opens, shorts, cable impedance mismatch, bad connectors, termination mismatches, and any other discontinuities on the cable.

The TLK100 device transmits a test pulse of known amplitude (1V) down each of the two pairs of an attached cable. The transmitted signal continues down the cable and reflects from each cable imperfection, fault, bad connector and the end of the cable itself. After the pulse transmission the TLK100 measures the return time and amplitude of all these reflected pulses. This technique enables measuring the distance and magnitude (impedance) of non-terminated cables (open or short), discontinuities (bad connectors), and improperly-terminated cables with an accuracy of ±1m.

To do this, the TLK100 uses a RAM with up to 256 samples to record all the input sampled data (Equals to max possible measured cable length of over 200m). The TLK100 also uses soft data averaging to reduce noise and improve accuracy. The TLK100 is capable of recording up to five reflections within the tester pair. In case more than 5 reflections were recorded the TLK100 will save the last 5 of them.

For all TDR measurements, the transformation between time of arrival and physical distance is done by the external host using minor computations (such as multiplication/addition and lookup tables). The host must know the expected propagation delay of the cable, which depends, among other things, on the cable category (e.g. CAT5/CAT5e/CAT6).

#### 3.7.2 ALCD

The TLK100 also supports Active Link Cable Diagnostic (ALCD). The ALCD offers a passive method to estimate the cable length during active link. It uses passive digital signal processing based on adapted data thus enabling measurement of cable length with an active link partner.

The ALCD also uses pre-defined parameters according to the cable properties (e.g. CAT5/CAT5e/CAT6) in order to achieve higher accuracy in the estimated cable length. The ALCD Cable length measurement accuracy is +/-5m for the pair used in the Rx path (due to the passive nature of the test we measure only the pair on the Rx path).

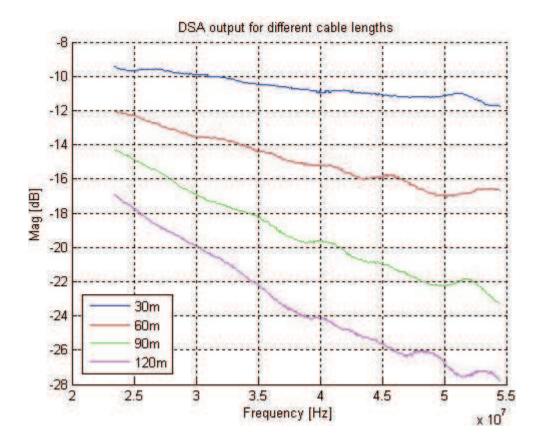

#### 3.7.3 DSA

The TLK100 also offers a unique capability of Digital Spectrum Analyzer (DSA). The DSA enables a detailed analysis of the channel frequency response (Magnitude only). The DSA has the following capabilities:

- Produce channel frequency response in resolution of 119.2Hz.

- Save up to 512 bins per DSA run.

- Full control in the analyzed frequency bins location and resolution.

- Programmable options for input data for the DSA:

- Use raw data taken directly from the channel

- Use adapted data that passed digital signal processing

- Use additional filtering for smoothing the total channel frequency response.

- Build in averaging for more accurate results

NOTE: For an example of the DSA output please see appendix A

To reset the cable diagnostic registers, set bit 14 of RAMCR2 register (0x0D01) to '1'. Writing software global reset 0x001F bit 15 does not reset the cable diagnostic registers.

#### 4 Interfaces

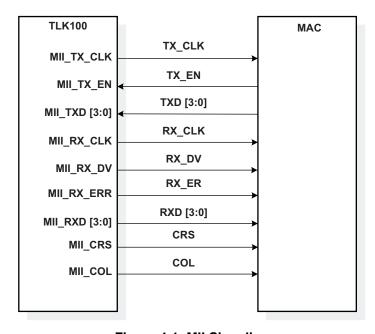

#### 4.1 Media Independent Interface (MII)

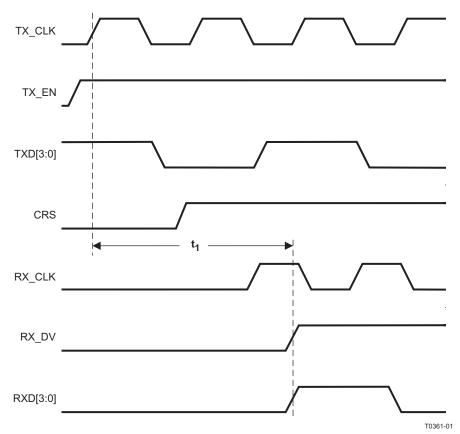

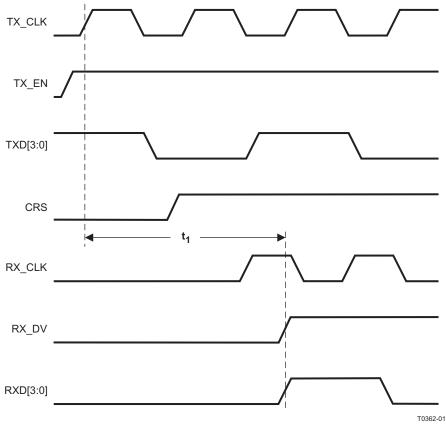

The Media Independent Interface (MII) is a synchronous 4-bit wide nibble data interface that connects the PHY to the MAC in 100B-TX and 10B-T modes. The MII is fully compliant with IEEE802.3-2002 clause 22.

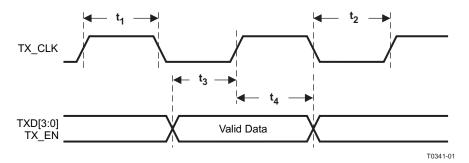

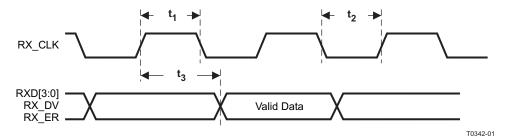

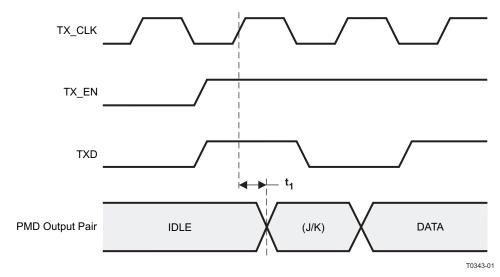

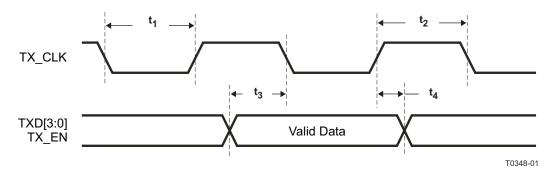

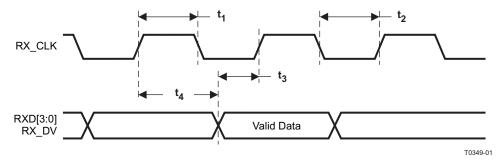

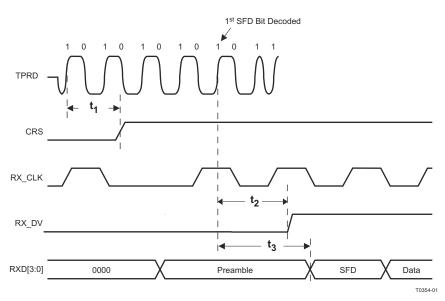

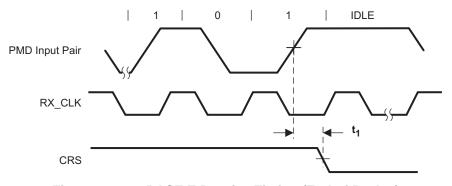

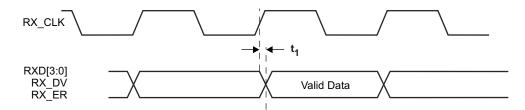

The MII consists of the data signals MII\_TXD[3:0] and MII\_RXD[3:0], transmit and receive valid signals MII\_TX\_EN and MII\_RX\_DV, error signal MII\_RX\_ERR and transmit/receive clocks MII\_TX\_CLK and MII\_RX\_CLK. In addition, the interface consists of asynchronous line status signals MII\_CRS and MII\_COL, indicating carrier sense and collision. Data on MII\_TXD[3:0] and MII\_RXD[3:0] are latched with reference to the edges of MII\_RX\_CLK and MII\_TX\_CLK clocks respectively as defined in the MII timing diagrams 22-14 and 22-15 of IEEE802.3-2002 clause 22. Both clocks are sourced by the PHY. In 100B-TX mode, the MII\_RX\_CLK and MII\_TX\_CLK source 25MHz clocks and in 10B-T, they source 2.5MHz clocks.

Figure 4-1 describes the MII signals connectivity.

Figure 4-1. MII Signaling

The isolate register 0.10 defined in IEEE802.3-2002 used to electrically isolate the PHY from the MII (if set, all transactions on the MII interface are ignored by the PHY).

Additionally, the MII interface includes the carrier sense signal MII\_CRS, as well as a collision detect signal MII\_COL. The MII\_CRS signal asserts to indicate the reception of data from the network or as a function of transmit data in Half Duplex mode. The MII\_COL signal asserts as an indication of a collision which can occur during half-duplex operation when both transmit and receive operation occur simultaneously.

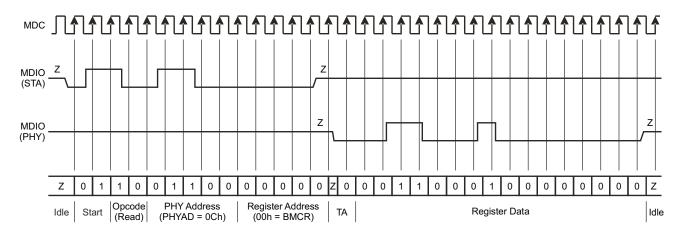

#### 4.2 Serial Management Interface

The Serial Management Interface (SMI), provides access to the TLK100's internal registers space for status information and configuration. The SMI is compatible with IEEE802.3-2002 clause 22. The implemented register set consists of all the registers required by the IEEE802.3-2002 in addition to several others, providing additional visibility and controllability of the TLK100 device.

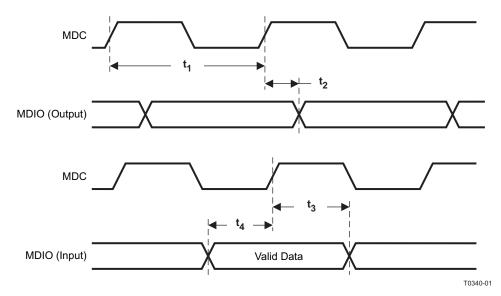

The SMI includes the MDC management clock input and the management MDIO data pin. The MDC clock is sourced by the external management entity (also referred to as STA), and can run at maximum clock rate of 25MHz. MDC is not expected to be continuous, and can be turned off by the external management entity when the bus is idle.

The MDIO is sourced by the external management entity and by the PHY. The data on the MDIO pin is latched on the rising edge of the MDC clock. The MDIO pin requires a pull-up resistor (1.5k $\Omega$ ) which, during IDLE and turnaround, pulls MDIO high.

Up to 32 PHYs can share a common SMI bus. To distinguish between the PHYs, a 5-bit address is used. During power-up reset, the TLK100 latches the PHYAD[4:0] configuration pins (Pin 25 to Pin 28) to determine its address.

The management entity must not start an SMI transaction in the first cycle after power-up reset.

To maintain legal operation, SMI bus should remain inactive at least one MDC cycle after hard reset is de-asserted.

In normal MDIO transactions, the register address is taken directly from the management frame's reg addr field, thus allowing direct access to 32 16-bit registers (including those defined in IEEE802.3 and vendor specific). The data field is used for both reading and writing.

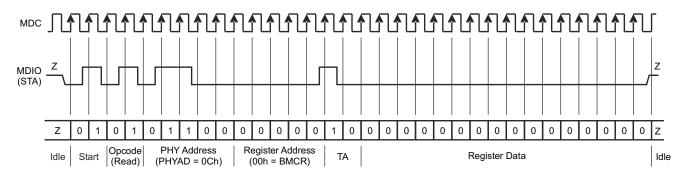

The Start code is indicated by a <01> pattern. This makes sure that the MDIO line transitions from the default idle line state. Turnaround is defined as an idle bit time inserted between the Register Address field and the Data field. To avoid contention during a read transaction, no device may actively drive the MDIO signal during the first bit of Turnaround. The addressed TLK100 drives the MDIO with a zero for the second bit of turnaround and follows this with the required data. Figure 4-2 shows the timing relationship between MDC and the MDIO as driven/received by the Station (STA) and the TLK100 (PHY) for a typical register read access.

For write transactions, the station-management entity writes data to the addressed TLK100, thus eliminating the requirement for MDIO Turnaround. The Turnaround time is filled by the management entity by inserting <10>. Figure 4-3 shows the timing relationship for a typical MII register write access. The frame structure and general read/write transactions are shown in Table 4-1, Figure 4-2, and Figure 4-3.

**Table 4-1. Typical MDIO Frame Format**

| MII Management Serial Protocol | <idle><start><op code=""><device addr=""><reg addr=""><turnaround><data><idle></idle></data></turnaround></reg></device></op></start></idle> |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Read Operation                 | <idle>&lt;01&gt;&lt;10&gt;<aaaaa><rrrrr><z0><xxxx td="" xx<="" xxxx=""></xxxx></z0></rrrrr></aaaaa></idle>                                   |  |

| Write Operation                | <idle>&lt;01&gt;&lt;04AAAA&gt;<rrrrr>&lt;10&gt;<xxxx td="" xx<="" xxxx=""></xxxx></rrrrr></idle>                                             |  |

Figure 4-2. Typical MDC/MDIO Read Operation

Figure 4-3. Typical MDC/MDIO Write Operation

#### 4.2.1 Extended Address Space Access

The TLK100 SMI function supports read/write access to the extended register set using registers REGCR(0x000Dh) and ADDAR(0x000Eh) and the MDIO Manageable Device (MMD) indirect method defined in IEEE802.3ah Draft for clause 22 for accessing the clause 45 extended register set.

Accessing the standard register set, i.e. MDIO registers 0 to 31, can be performed using the normal direct MDIO access or the indirect method, except for register REGCR(0x000Dh) and ADDAR(0x000Eh) which can be accessed only using the normal MDIO transaction. The SMI function will ignore indirect accesses to these registers.

REGCR(0x000Dh) is the MDIO Manageable MMD access control. In general, register REGCR(4:0) is the device address DEVAD that directs any accesses of ADDAR(0x000Eh) register to the appropriate MMD. Specifically, the TLK100 uses the vendor specific **DEVAD[4:0] = "11111"** for accesses. All accesses through registers REGCR and ADDAR should use this DEVAD. Transactions with other DEVAD are ignored. REGCR[15:14] holds the access function: address (00), data with no post increment (01), data with post increment on read and writes (10) and data with post increment on writes only (11).

- ADDAR is the address/data MMD register. It is used in conjunction with REGCR to provide the access

to the extended register set. If register REGCR[15:14] is 00, then ADDAR holds the address of the

extended address space register. Otherwise, ADDAR holds the data as indicated by the contents of its

address register. When REGCR[15:14] is set to 00, accesses to register ADDAR modify the extended

register set address register. This address register should always be initialized in order to access any

of the register within the extended register set.

- When REGCR[15:14] is set to 01, accesses to register ADDAR access the register within the extended register set selected by the value in the address register.

- When REGCR[15:14] is set to 10, access to register ADDAR access the register within the extended register set selected by the value in the address register. After that access is complete, for both reads and writes, the value in the address register is incremented.

- When REGCR[15:14] is set to 11, access to register ADDAR access the register within the extended register set selected by the value in the address register. After that access is complete, for write accesses only, the value in the address register is incremented. For read accesses, the value of the address register remains unchanged.

The following sections describe how to perform operations on the extended register set using register REGCR and ADDAR.

#### 4.2.1.1 Write Address Operation

To set the address register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

Subsequent writes to register ADDAR (step 2) continue to write the address register.

#### 4.2.1.2 Read Address Operation

To read the address register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Read the register address from register ADDAR.

Subsequent reads to register ADDAR (step 2) continue to read the address register.

www ti com

#### 4.2.1.3 Write (no post increment) Operation

To write an extended register set register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

- 3. Write the value 0x401F (data, no post increment function field = 01, DEVAD = 31) to register REGCR.

- 4. Write the content of the desired extended register set register to register ADDAR.

Subsequent writes to register ADDAR (step 4) continue to rewrite the register selected by the value in the address register.

Note: steps (1) and (2) can be skipped if the address register was previously configured.

# 4.2.1.4 Read (no post increment) Operation

To read an extended register set register:

- 1. Write the value 0x001F (address function field = 00, DEVAD = 31) to register REGCR.

- 2. Write the desired register address to register ADDAR.

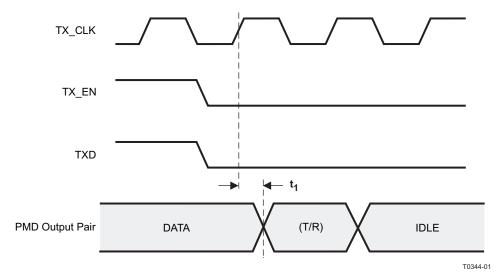

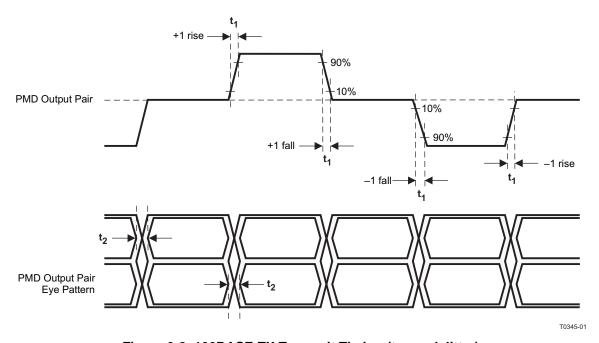

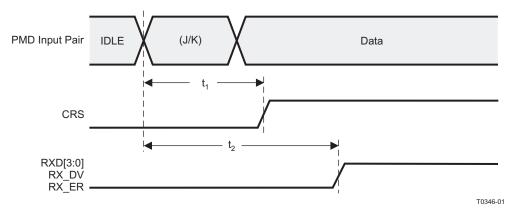

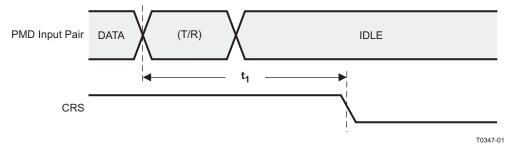

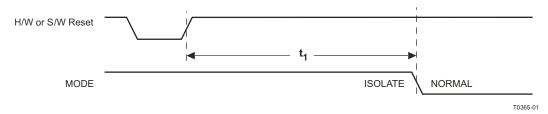

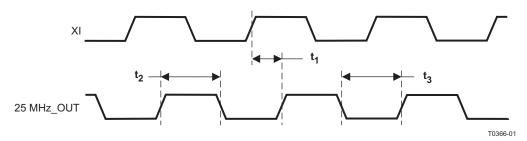

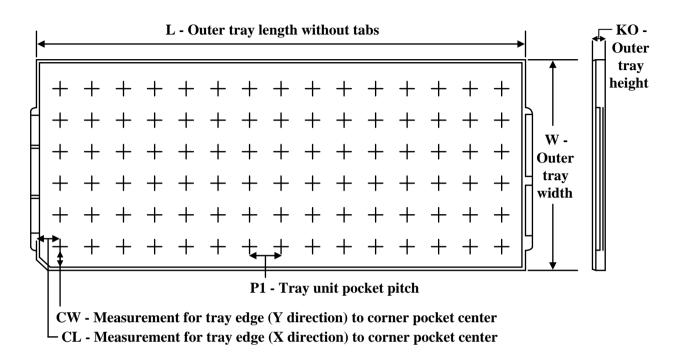

- 3. Write the value 0x401F (data, no post increment function field = 01, DEVAD = 31) to register REGCR.