**TL16C750E**

SLLSF10-DECEMBER 2019

## TL16C750E UART with 128-Byte FIFO

#### **Features**

- Supports wide supply voltage range of 1.62 V to

- 6 Mbps (48-MHz oscillator input clock) at 5 V and 3.3 V

- 3 Mbps (48-MHz oscillator input clock) at 5 V and 3.3 V

- 2 Mbps (32-MHz oscillator input clock) at 3.3 V

- 1.5 Mbps (24-MHz oscillator input clock) at 2.5 V

- 1 Mbps (16-MHz oscillator Input clock) at 1.8 V

- Characterized for operation from -40°C to 105°C

- 128-byte transmit or receive FIFO

- 6-bit fractional baud rate divider

- Software-selectable baud-rate generator

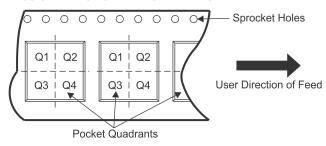

- Programmable and selectable transmit and Receive FIFO Trigger Levels for DMA, interrupt generation, and software or hardware flow control

- Software/Hardware flow control

- Programmable Xon and Xoff characters with optional Xon any character

- Programmable Auto-RTS and Auto-CTSmodem control functions (CTS, RTS, DSR, DTR, RI, and CD)

- DMA signaling capability for both received and transmitted data

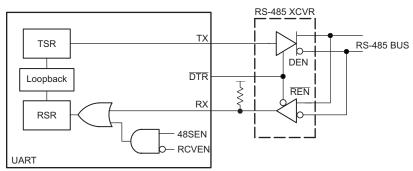

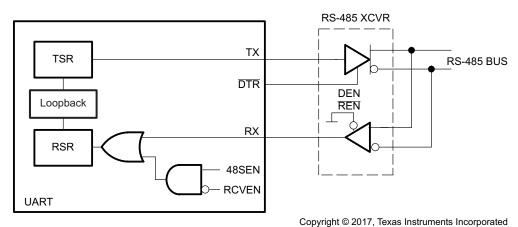

- RS-485 mode support

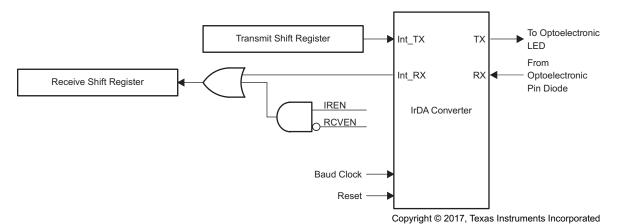

- Infrared data association (IrDA) capability

- Programmable sleep mode

- Programmable serial interface characteristics

- 5, 6, 7, or 8-bit characters with 1, 1.5, or 2 stop bit generation

- Even, odd, or no parity bit generation and detection

- False start bit and line break detection

- Internal test and loopback capabilities

## Applications

- Industrial computing

- Communications equipment

- White goods

### Description

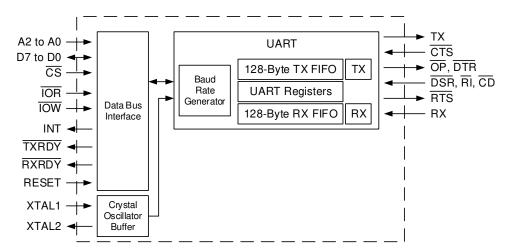

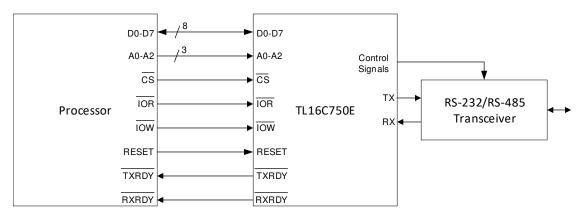

The TL16C750E is a single universal asynchronous receiver transmitter (UART) with 128-byte FIFOs, fractional baud rate support, automatic hardware, software flow control and data rates up to 6 Mbps. The device offers enhanced features such as fractional baud rate and a transmission character control register (TCR) that stores received FIFO threshold level to start or stop transmission during hardware and software flow control automatically without intervention from the CPU.

With the FIFO RDY register, the software gets the status of TXRDY or RXRDY, saving extra GPIO usage. On-chip status registers provide the user with error indications, operational status, and modem interface control. System interrupts may be tailored to meet user requirements. An internal loop-back capability allows onboard diagnostics. TL16C750E incorporates the functionality of UART, the UART having its own register set and FIFO.

This version includes the Alternate Function Register (AFR) and this is used to enable some extra functionality beyond the capabilities of the TL16C750 version. One addition is the IrDA mode, which supports Standard IrDA (SIR) mode with baud rates from 2400 to 115.2 kbps. The third addition is support for RS-485 bus drivers or transceivers by providing an output pin (DTRx) per channel, which is timed to keep the RS-485 driver enabled as long as transmit data is pending.

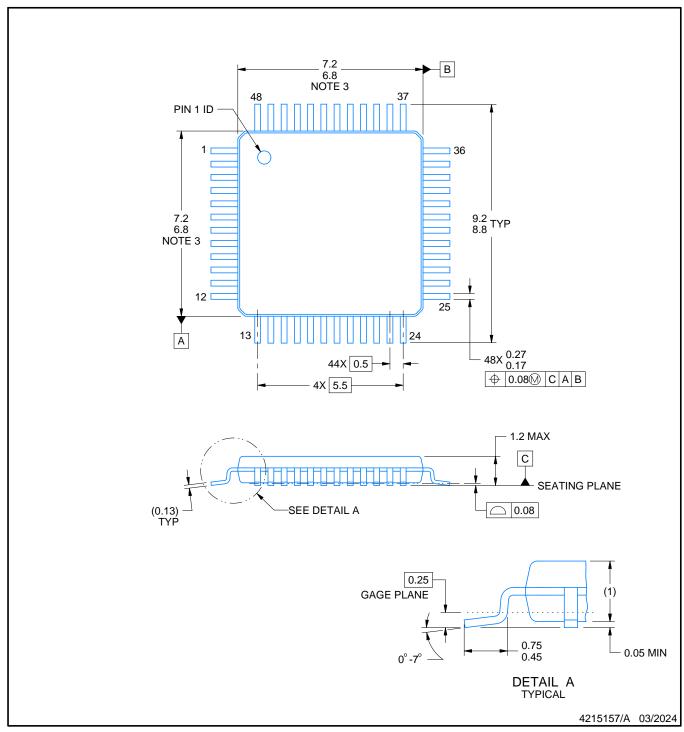

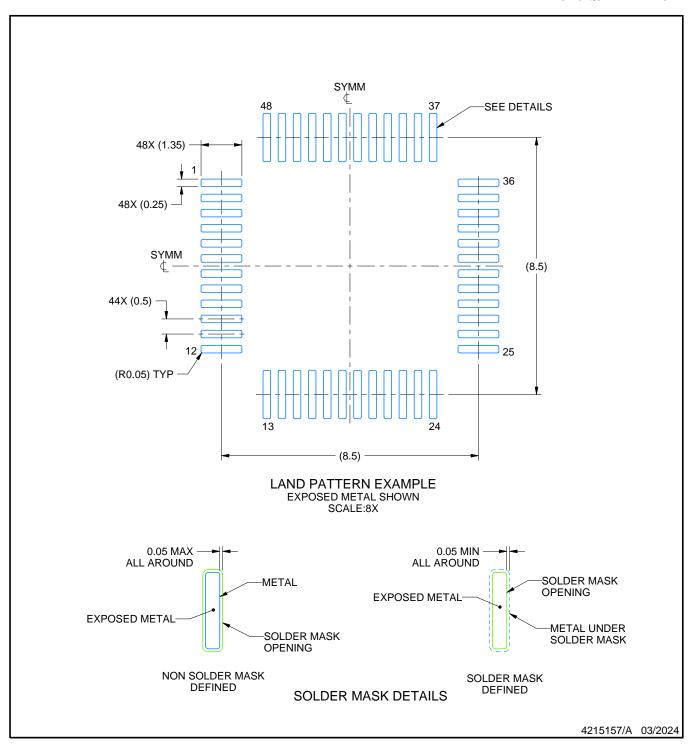

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TL16C750E   | TQFP (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

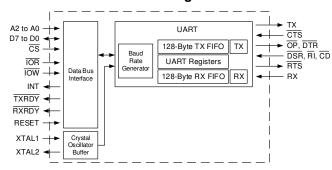

#### **Block Diagram**

SLLSF10 – DECEMBER 2019 www.ti.com

## **Table of Contents**

| 1 | Features 1                           |    | 9.3 Feature Description                             | 20                 |

|---|--------------------------------------|----|-----------------------------------------------------|--------------------|

| 2 | Applications 1                       |    | 9.4 Device Functional Modes                         | 32                 |

| 3 | Description 1                        |    | 9.5 Register Maps                                   | 34                 |

| 4 | Revision History2                    | 10 | Application and Implementation                      | 50                 |

| 5 | Description (continued)3             |    | 10.1 Application Information                        | 50                 |

| 6 | Pin Configuration and Functions      |    | 10.2 Typical Application                            | 50                 |

| 7 | Specifications5                      | 11 | Power Supply Recommendations                        | 53                 |

| • | 7.1 Absolute Maximum Ratings         | 12 | Layout                                              | 53                 |

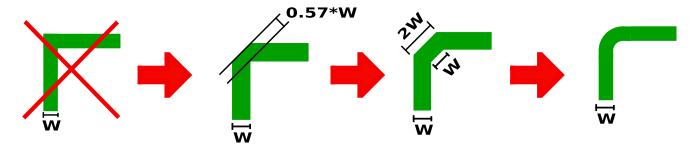

|   | 7.2 ESD Ratings                      |    | 12.1 Layout Guidelines                              | 53                 |

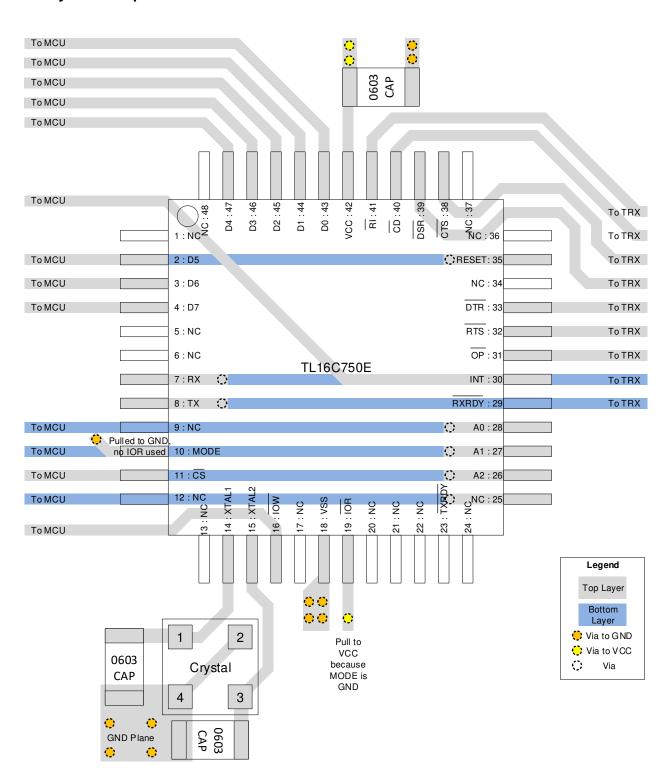

|   | 7.3 Recommended Operating Conditions |    | 12.2 Layout Examples                                | 54                 |

|   | 7.4 Thermal Information              | 13 | Device and Documentation Support                    | 55                 |

|   | 7.5 Electrical Characteristics       |    | 13.1 Documentation Support                          | 55                 |

|   | 7.6 Timing Requirements              |    | 13.2 Receiving Notification of Documentation Update | es <mark>55</mark> |

|   | 7.7 Typical Characteristics          |    | 13.3 Support Resources                              | 55                 |

| 8 | Parameter Measurement Information 10 |    | 13.4 Trademarks                                     | 55                 |

| 9 | Detailed Description 19              |    | 13.5 Electrostatic Discharge Caution                | 55                 |

| • | 9.1 Overview                         |    | 13.6 Glossary                                       | 55                 |

|   | 9.2 Functional Block Diagrams        | 14 | Mechanical, Packaging, and Orderable Information    | 55                 |

## 4 Revision History

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2019 | *        | Initial Release |

## 5 Description (continued)

Another name for the UART function is asynchronous communications element (ACE), and these terms are used interchangeably. The bulk of this document describes the behavior of each ACE, with the understanding that two such devices are incorporated into the TL16C750E device.

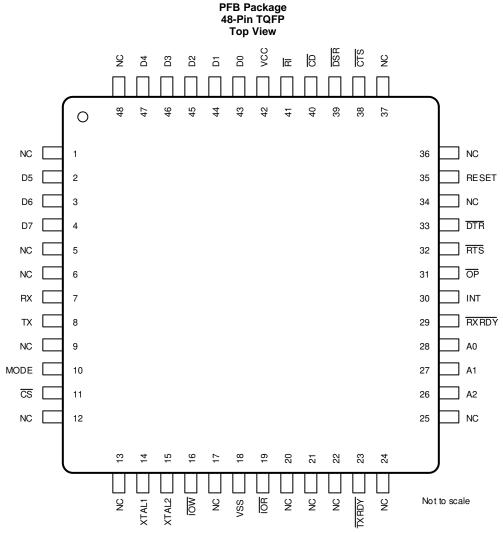

## 6 Pin Configuration and Functions

N.C. - No internal connection

## **Pin Functions**

| PIN FUNCTIONS PIN                   |                                                                        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|-------------------------------------|------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                | NO.                                                                    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

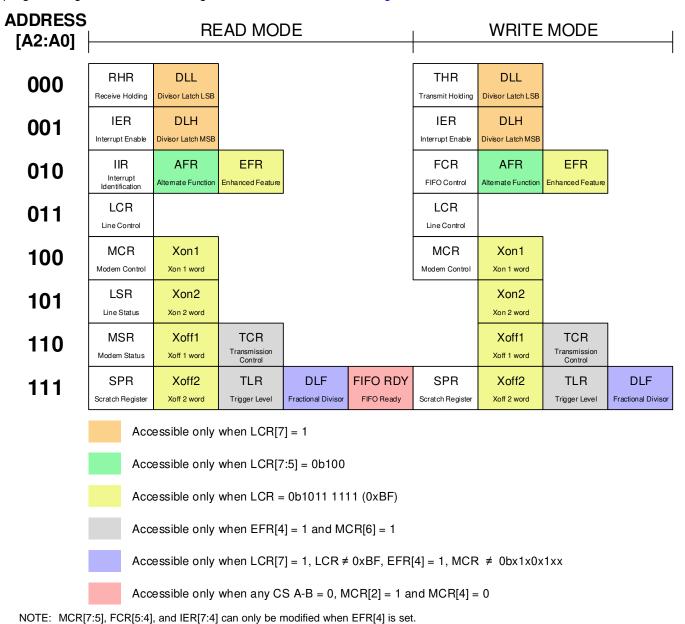

| A0                                  | 28                                                                     | ı   | Address bit 0 select. Internal registers address selection. Refer to Figure 30 for register address map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| A1                                  | 27                                                                     | ı   | Address bit 1 select. Internal registers address selection. Refer to Figure 30 for register address map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| A2                                  | 26                                                                     | 1   | Address bit 2 select. Internal registers address selection. Refer to Figure 30 for register address map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| CD                                  | 40                                                                     | ı   | Carrier detect (active low). A low on these pins indicates that a carrier has been detected by the modem.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| <del>CS</del>                       | 11                                                                     | I   | Chip select. When $\overline{\text{CS}}$ is low, this input enables the ACE. When this input is high, the ACE remains inactive. When MODE is pulled low for " $\overline{\text{IOR}}$ Unused" mode, this will be pulled low and the state of $\overline{\text{IOW}}$ is read to determine if the transaction is a read or a write                                                                                                                                                                                                                                                                          |  |  |

| стѕ                                 | 38                                                                     | ı   | Clear to send. $\overline{\text{CTS}}$ is a modem status signal. Its condition can be checked by reading bit 4 ( $\overline{\text{CTS}}$ ) of the modem status register. Bit 0 ( $\Delta$ CTS) of the modem status register indicates that $\overline{\text{CTS}}$ has changed states since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{\text{CTS}}$ changes levels and the auto-CTS mode is not enabled, an interrupt is generated. $\overline{\text{CTS}}$ is also used in the auto- $\overline{\text{CTS}}$ mode to control the transmitter. |  |  |

| D0, D1, D2<br>D3, D4, D5, D6,<br>D7 | 43, 44, 45<br>46, 47, 2,<br>3, 4                                       | I/O | Data bus (bidirectional). These pins are the 8-bit, 3-state data bus for transferring information to or from the controlling CPU. D0 is the least significant bit and the first data bit in a transmit or receive serial data stream.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| DSR                                 | 39                                                                     | I   | Data set ready. $\overline{DSR}$ is a modem status signal. Its condition can be checked by reading bit 5 ( $\overline{DSR}$ ) of the modem status register. Bit 1 ( $\Delta DSR$ ) of the modem status register indicates $\overline{DSR}$ has changed levels since the last read from the modem status register. If the modem status interrupt is enabled when $\overline{DSR}$ changes levels, an interrupt is generated.                                                                                                                                                                                |  |  |

| DTR                                 | 33                                                                     | 0   | Data terminal ready. When active (low), DTR informs a modem or data set that the ACE is ready to establish communication. DTR is placed in the active level by setting the DTR bit of the modem control register. DTR is placed in the inactive level either as a result of a master reset, during loop mode operation, or clearing the DTR bit. These pins can also be used in the RS-485 mode to control an external RS-485 driver or transceiver.                                                                                                                                                       |  |  |

| MODE                                | 10                                                                     | I   | Interface mode select pin. This pin must be tied to VCC or to GND. If MODE is pulled to VCC, $\overline{\text{IOR}}$ is used in communication. If MODE is pulled to GND, $\overline{\text{IOR}}$ is NOT used for communication. Only the state of $\overline{\text{IOW}}$ is sampled when $\overline{\text{CS}}$ is toggled low to determine if the transaction is a read or a write. In this mode, $\overline{\text{IOR}}$ must be connected to VCC                                                                                                                                                       |  |  |

| $V_{SS}$                            | 18                                                                     | GND | Power Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

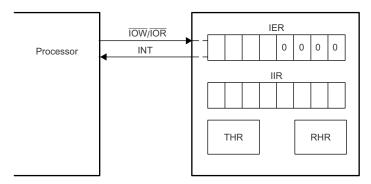

| INT                                 | 30                                                                     | 0   | Interrupt. When active, INT informs the CPU that the ACE has an interrupt to be serviced. Four conditions that cause an interrupt to be issued are: a receiver error, received data that is available or timed out (FIFO mode only), an empty transmitter holding register, or an enabled modem status interrupt. INT is reset (deactivated) either when the interrupt is serviced or as a result of a master reset.                                                                                                                                                                                       |  |  |

| ĪŌR                                 | 19                                                                     | I   | Read inputs. When IOR is active (low) while the ACE is selected, the CPU is allowed to read status information or data from ACE register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| ĪŌW                                 | 16                                                                     | I   | Write input (active low strobe). A valid low level on $\overline{\text{IOW}}$ transfers the contents of the data bus (D0 through D7) from the external CPU to an internal register that is defined by address bits A0 through A2.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| NC                                  | 1, 5, 6, 9,<br>12, 13, 17,<br>20, 21, 22,<br>24, 25, 34,<br>36, 37, 48 |     | No internal connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| <del>OP</del>                       | 31                                                                     | 0   | The state of this pin is defined by the user through the software settings of the MCR register, bit 3. INT is set to active mode and OP to logic 0 when the MCR-3 is set to logic 1. INT is set to the 3-state mode and OP to a logic 1 when MCR-3 is set to a logic 0                                                                                                                                                                                                                                                                                                                                     |  |  |

| RESET                               | 35                                                                     | I   | Reset. RESET resets the internal registers and all the outputs. The UART transmitter output and the receiver input are disabled during reset time.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RI                                  | 41                                                                     | I   | Ring indicator. $\overline{RI}$ is a modem status signal. Its condition can be checked by reading bit 6 ( $\overline{RI}$ ) of the modem status register. Bit 2 (TERI) of the modem status register indicates that $\overline{RI}$ has transitioned from a low to a high level since the last read from the modem status register. If the modem status interrupt is enabled when this transition occurs, an interrupt is generated.                                                                                                                                                                        |  |  |

| RTS                                 | 32                                                                     | 0   | Request to send. When active, $\overline{\text{RTS}}$ informs the modem or data set that the ACE is ready to receive data. $\overline{\text{RTS}}$ is set to the active level by setting the $\overline{\text{RTS}}$ modem control register bit and is set to the inactive (high) level either as a result of a master reset or during loop mode operations or by clearing bit 1 ( $\overline{\text{RTS}}$ ) of the MCR. In the auto- $\overline{\text{RTS}}$ mode, $\overline{\text{RTS}}$ is set to the inactive level by the receiver threshold control logic                                           |  |  |

| RX                                  | 7                                                                      | I   | Receive data input. During the local loopback mode, this RX input pin is disabled and TX data is internally connected to the UART RX input internally. During normal mode, RX should be held high when no data is being received. This input also can be used in IrDA mode. For more information, see IrDA Overview.                                                                                                                                                                                                                                                                                       |  |  |

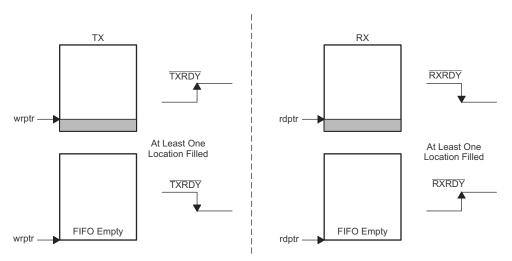

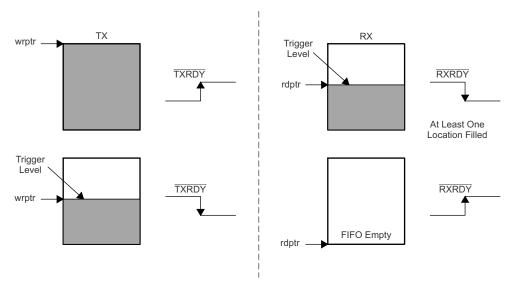

| RXRDY                               | 29                                                                     | 0   | Receive ready (active low). RXRDY goes low when the trigger level has been reached or a timeout interrupt occurs. It go high when the RX FIFO is empty or there is an error in RX FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| тх                                  | 8                                                                      | 0   | Transmit data. This output is associated with serial transmit data from the TL16C750E device. During the local loopback mode, the TX input pin is disabled and TX data is internally connected to the UART RX input.                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TXRDY                               | 23                                                                     | 0   | Transmit ready (active low). TXRDY goes low when there are a trigger level number of spaces available. They go high when the TX buffer is full.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| V <sub>cc</sub>                     | 42                                                                     | PWR | Power supply inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

#### Pin Functions (continued)

| PIN      |     |     | PIN I/O                                                                                                                                                                                                                                                                                                |  | DESCRIPTION |

|----------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                            |  |             |

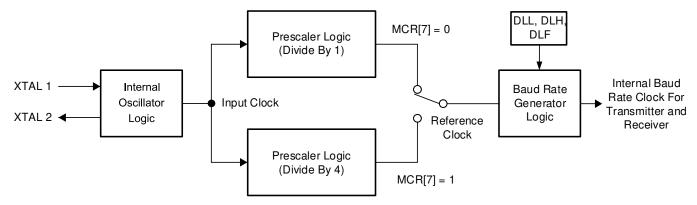

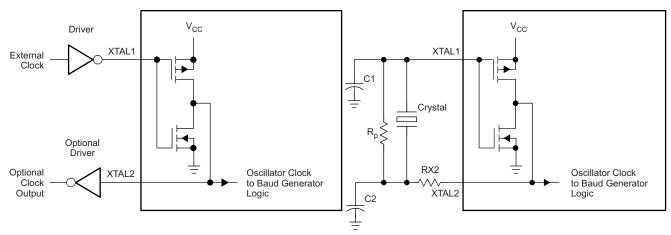

| XTAL1 14 |     | I   | Crystal or external clock input. XTAL1 functions as a crystal input or as an external clock input. A crystal can be connected between XTAL1 and XTAL2 to form an internal oscillator circuit (see Figure 27). Alternatively, an external clock can be connected to XTAL1 to provide custom data rates. |  |             |

| XTAL2 15 |     | 0   | Output of the crystal oscillator or buffered clock. See also XTAL1. XTAL2 is used as a crystal oscillator output or buffered clock output.                                                                                                                                                             |  |             |

## **Specifications**

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                | MIN  | MAX                   | UNIT |

|------------------|--------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Supply voltage                 | -0.5 | 6                     | ٧    |

| VI               | Input voltage                  | -0.5 | V <sub>CC</sub> + 0.5 | ٧    |

| Vo               | Output voltage                 | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| T <sub>A</sub>   | Operating free-air temperature | -40  | 105                   | °C   |

| T <sub>stg</sub> | Storage temperature            | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>   | ±2000 | \/   |

|                    | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | ٧    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Copyright © 2019, Texas Instruments Incorporated

over operating free-air temperature range (unless otherwise noted)

|                      |                                |             |  | MIN  | NOM | MAX                   | UNIT |

|----------------------|--------------------------------|-------------|--|------|-----|-----------------------|------|

| V <sub>CC</sub> = 1. | .8 V ±10%                      |             |  |      |     |                       |      |

| V <sub>CC</sub>      | Supply voltage                 |             |  | 1.62 | 1.8 | 1.98                  | V    |

| VI                   | Input voltage                  |             |  | -0.3 |     | 0.9 × V <sub>CC</sub> | V    |

| V <sub>IH</sub>      | High-level input voltage       |             |  | 1.4  |     |                       | V    |

| V <sub>IL</sub>      | Low-level input voltage        |             |  |      |     | 0.4                   | V    |

| Vo                   | Output voltage                 |             |  | 0    |     | V <sub>CC</sub>       | V    |

| l <sub>он</sub>      | High-level output current      | All outputs |  |      |     | -0.5                  | mA   |

| OL                   | Low-level output current       | All outputs |  |      |     | 1                     | mA   |

|                      | Oscillator/clock speed         |             |  |      | 16  | MHz                   |      |

| T <sub>A</sub>       | Operating free-air temperature |             |  | -40  |     | 105                   | °C   |

| V <sub>CC</sub> = 2. | .5 V ±10%                      |             |  |      |     |                       |      |

| V <sub>CC</sub>      | Supply voltage                 |             |  | 2.25 | 2.5 | 2.75                  | V    |

| V <sub>I</sub>       | Input voltage                  |             |  | -0.3 |     | 0.9 × V <sub>CC</sub> | V    |

| V <sub>IH</sub>      | High-level input voltage       |             |  | 1.8  |     |                       | V    |

| V <sub>IL</sub>      | Low-level input voltage        |             |  |      |     | 0.6                   | V    |

| Vo                   | Output voltage                 |             |  | 0    |     | V <sub>CC</sub>       | V    |

| l <sub>он</sub>      | High-level output current      | All outputs |  |      |     | -1                    | mA   |

| l <sub>OL</sub>      | Low-level output current       | All outputs |  |      |     | 2                     | mA   |

|                      | Oscillator/clock speed         |             |  |      |     | 24                    | MHz  |

| T <sub>A</sub>       | Operating free-air temperature |             |  | -40  |     | 105                   | °C   |

| / <sub>CC</sub> = 3. | .3 V ±10%                      |             |  |      |     |                       |      |

# TEXAS INSTRUMENTS

## **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

| V <sub>cc</sub>       |                                |              | MIN                   | NOM | MAX                                                | UNIT |

|-----------------------|--------------------------------|--------------|-----------------------|-----|----------------------------------------------------|------|

|                       | Supply voltage                 |              | 3                     | 3.3 | 3.6                                                | V    |

| V <sub>I</sub>        | Input voltage                  |              | -0.3                  |     | V <sub>CC</sub>                                    | V    |

| V <sub>IH</sub>       | High-level input voltage       |              | 0.7 × V <sub>CC</sub> |     |                                                    | V    |

| V <sub>IL</sub>       | Low-level input voltage        |              |                       |     | 0.8                                                | V    |

| Vo                    | Output voltage                 |              | 0                     |     | $V_{CC}$                                           | V    |

| он                    | High-level output current      | All outputs  |                       |     | -1.8                                               | mA   |

| OL                    | Low-level output current       | All outputs  |                       |     | 3.2                                                | mA   |

|                       | Oscillator or clock speed      |              |                       |     | 48                                                 | MHz  |

| T <sub>A</sub>        | Operating free-air temperature |              | -40                   |     | 105                                                | °C   |

| V <sub>CC</sub> = 5 \ | / ±10%                         |              |                       |     |                                                    |      |

| V <sub>CC</sub>       | Supply voltage                 |              | 4.5                   | 5   | 5.5                                                | V    |

| V <sub>I</sub>        | Input voltage                  |              | -0.3                  |     | $V_{CC}$                                           | V    |

| .,                    | High-level input voltage       | Except XTAL1 | 2                     |     |                                                    | V    |

| V <sub>IH</sub>       | High-level input voltage       | XTAL1        | 0.7 × V <sub>CC</sub> |     | 0.8<br>V <sub>CC</sub><br>-1.8<br>3.2<br>48<br>105 | V    |

| .,                    | Low-level input voltage        | Except XTAL1 |                       |     | 8.0                                                | V    |

| V <sub>IL</sub>       | Low-level input voltage        | XTAL1        |                       | 0.3 | × V <sub>CC</sub>                                  | V    |

| Vo                    | Output voltage                 |              | 0                     |     | V <sub>CC</sub>                                    | V    |

| он                    | High-level output current      | All outputs  |                       |     | -4                                                 | mA   |

| OL                    | Low-level output current       | All outputs  |                       |     | 4                                                  | mA   |

|                       | Oscillator or clock speed      |              |                       |     | 48                                                 | MHz  |

| T <sub>A</sub>        | Operating free-air temperature |              | -40                   |     | 105                                                | °C   |

#### 7.4 Thermal Information

|                        | THERMAL METRIC <sup>(1)</sup>                | PFB (TQFP) | UNIT |

|------------------------|----------------------------------------------|------------|------|

|                        | I HERMAL METRIC                              | 48 PINS    | UNII |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 61         | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 17.3       | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                           | TEST CON                                                                                      | IDITIONS                                                                                    | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> = 1.8 | 3 V                                 |                                                                                               |                                                                                             |     |     |     |      |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -0.5 mA                                                                     |                                                                                             | 1.3 |     |     | V    |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 1 mA                                                                        |                                                                                             |     |     | 0.5 | V    |

| l <sub>l</sub>        | Input current                       | V <sub>CC</sub> = 1.98 V,<br>V <sub>I</sub> = 0 to 1.98 V                                     | V <sub>SS</sub> = 0,<br>All other terminals floating                                        |     |     | 10  | μА   |

| l <sub>OZ</sub>       | High-impedance state output current | V <sub>CC</sub> = 1.98 V,<br>V <sub>O</sub> = 0 to 1.98 V                                     | Chip selected in write mode or chip deselect                                                |     |     | ±20 | μА   |

| I <sub>CC</sub>       | Supply current                      | $V_{CC}$ = 1.98 V, $\overline{\rm DSR}$ , $\overline{\rm CTS}$ , and $\overline{\rm RI}$ at 2 | All other inputs at 0.4 V,<br>No load on outputs, XTAL1 at 16<br>MHz,<br>Baud rate = 1 Mb/s |     |     | 6   | mA   |

| C <sub>I(CLK)</sub>   | Clock input capacitance             |                                                                                               |                                                                                             |     | 5   | 7   |      |

| C <sub>O(CLK)</sub>   | Clock output capacitance            | $V_{CC} = 0$ ,                                                                                | V <sub>SS</sub> = 0,                                                                        |     | 5   | 7   | _    |

| Cı                    | Input capacitance                   | f = 1 MHz, All other terminals grounded                                                       | T <sub>A</sub> = 25°C,                                                                      |     | 6   | 10  | pF   |

| Co                    | Output capacitance                  |                                                                                               |                                                                                             |     | 10  | 15  |      |

| V <sub>CC</sub> = 2.5 | 5 V                                 | '                                                                                             |                                                                                             |     |     |     |      |

Submit Documentation Feedback

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                           | TEST CON                                                                                                                 | IDITIONS                                                                                    | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -1 mA                                                                                                  |                                                                                             | 1.8 |     |     |      |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 2 mA                                                                                                   |                                                                                             |     |     | 0.5 | V    |

| I                     | Input current                       | V <sub>CC</sub> = 2.75 V,<br>V <sub>I</sub> = 0 to 2.75 V                                                                | V <sub>SS</sub> = 0,<br>All other terminals floating                                        |     |     | 10  | μА   |

| I <sub>OZ</sub>       | High-impedance state output current | V <sub>CC</sub> = 2.75 V,<br>V <sub>O</sub> = 0 to 2.75 V                                                                | Chip selected in write mode or chip deselect                                                |     |     | ±20 | μА   |

| Icc                   | Supply current                      | V <sub>CC</sub> = 2.75 V, <del>DCD</del> , <del>CTS</del> , and <del>RI</del> at 2                                       | All other inputs at 0.6 V, No load on outputs, XTAL1 at 24 MHz, Baud rate = 1.5 Mb/s        |     |     | 13  | mA   |

| C <sub>I(CLK)</sub>   | Clock input capacitance             |                                                                                                                          |                                                                                             |     | 5   | 7   |      |

| C <sub>O(CLK)</sub>   | Clock output capacitance            | $V_{CC} = 0$ ,                                                                                                           | V <sub>SS</sub> = 0,                                                                        |     | 5   | 7   | _    |

| Cı                    | Input capacitance                   | f = 1 MHz, All other terminals grounded                                                                                  | T <sub>A</sub> = 25°C,                                                                      |     | 6   | 10  | pF   |

| Co                    | Output capacitance                  | All other terminals grounded                                                                                             |                                                                                             |     | 10  | 15  |      |

| V <sub>CC</sub> = 3.3 |                                     |                                                                                                                          | 1                                                                                           |     |     | -   |      |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -1.8 mA                                                                                                |                                                                                             | 2.4 |     |     |      |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 3.2 mA                                                                                                 |                                                                                             |     |     | 0.5 | V    |

| I                     | Input current                       | V <sub>CC</sub> = 3.6 V,<br>V <sub>I</sub> = 0 to 3.6 V                                                                  | V <sub>SS</sub> = 0,<br>All other terminals floating                                        |     |     | 10  | μА   |

| l <sub>OZ</sub>       | High-impedance state output current | V <sub>CC</sub> = 3.6 V,<br>V <sub>O</sub> = 0 to 3.6 V                                                                  | Chip selected in write mode or chip deselect                                                |     |     | ±20 | μА   |

| I <sub>CC</sub>       | Supply current                      | $V_{CC} = 3.6 \text{ V}, \overline{\text{DSR}}, \overline{\text{CTS}}, \text{ and } \overline{\text{RI}} \text{ at 2 V}$ | All other inputs at 0.8 V, No load on outputs, XTAL1 at 32 MHz, Baud rate = 2 Mb/s          |     |     | 25  | mA   |

| C <sub>I(CLK)</sub>   | Clock input capacitance             |                                                                                                                          |                                                                                             |     | 5   | 7   |      |

| C <sub>O(CLK)</sub>   | Clock output capacitance            | V <sub>CC</sub> = 0,                                                                                                     | $V_{SS} = 0,$ $T_A = 25^{\circ}C,$                                                          |     | 5   | 7   |      |

| C <sub>I</sub>        | Input capacitance                   | f = 1 MHz,                                                                                                               |                                                                                             |     | 6   | 10  | pF   |

| Co                    | Output capacitance                  | All other terminals grounded                                                                                             |                                                                                             |     | 10  | 15  |      |

| V <sub>CC</sub> = 5 \ |                                     |                                                                                                                          |                                                                                             |     |     |     |      |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -4 mA                                                                                                  |                                                                                             | 4   |     |     |      |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 4 mA                                                                                                   |                                                                                             |     |     | 0.5 | V    |

| I <sub>I</sub>        | Input current                       | $V_{CC} = 5.5 \text{ V},$ $V_{I} = 0 \text{ to } 5.5 \text{ V}$                                                          | V <sub>SS</sub> = 0,<br>All other terminals floating                                        |     |     | 10  | μА   |

| I <sub>OZ</sub>       | High-impedance state output current | V <sub>CC</sub> = 5.5 V,<br>V <sub>O</sub> = 0 to 5.5 V                                                                  | Chip selected in write mode or chip deselect                                                |     |     | ±20 | μА   |

| I <sub>cc</sub>       | Supply current                      | $V_{CC} = 5.5 \text{ V}, \overline{DSR}, \overline{CTS}, \text{ and } \overline{RI} \text{ at 2 V}$                      | All other inputs at 0.8 V,<br>No load on outputs, XTAL1 at 48<br>MHz,<br>Baud rate = 3 Mb/s |     |     | 60  | mA   |

| C <sub>I(CLK)</sub>   | Clock input capacitance             |                                                                                                                          |                                                                                             |     | 5   | 7   | pF   |

| C <sub>O(CLK)</sub>   | Clock output capacitance            | $V_{CC} = 0,$                                                                                                            | V <sub>SS</sub> = 0,                                                                        |     | 5   | 7   |      |

| Cı                    | Input capacitance                   | f = 1 MHz,  All other terminals grounded                                                                                 | $T_A = 25^{\circ}C$ ,                                                                       |     | 6   | 10  |      |

| Co                    | Output capacitance                  | 7 iii Julier terriiiriais grounded                                                                                       |                                                                                             |     | 10  | 15  |      |

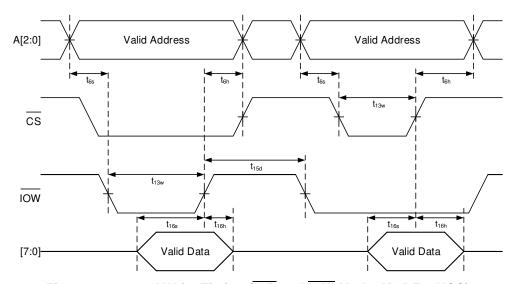

## 7.6 Timing Requirements

$T_A = -40$ °C to 105°C,  $V_{CC} = 1.8$  V to 5 V ±10% (unless otherwise noted)

|                    |                           | 1.8 V   | 2.5 V   | 3.3 V   | 5 V     | UNIT |

|--------------------|---------------------------|---------|---------|---------|---------|------|

|                    |                           | MIN MAX | MIN MAX | MIN MAX | MIN MAX |      |

| IOR Use            | ed (MODE = VCC)           |         |         |         |         |      |

| t <sub>RESET</sub> | Reset pulse width         | 200     | 200     | 200     | 200     | ns   |

| C <sub>P</sub>     | CP clock period           | 63      | 42      | 20      | 20      | ns   |

| t <sub>3w</sub>    | Oscillator or clock speed | 16      | 24      | 48      | 48      | MHz  |

# TEXAS INSTRUMENTS

## **Timing Requirements (continued)**

$T_A$  = -40°C to 105°C,  $V_{CC}$  = 1.8 V to 5 V ±10% (unless otherwise noted)

| · A ·              | $0^{\circ}$ C to 105°C, $V_{CC} = 1.8 \text{ V to 5}$ | 2.070 (0000 00              |     | <u>,                                      </u> |     | LIM | ITS |     |     |     |          |

|--------------------|-------------------------------------------------------|-----------------------------|-----|------------------------------------------------|-----|-----|-----|-----|-----|-----|----------|

|                    |                                                       |                             | 1.8 | ٧                                              | 2.5 | V   | 3.3 | ٧   | 5 ' | ٧   | UNIT     |

|                    |                                                       |                             | MIN | MAX                                            | MIN | MAX | MIN | MAX | MIN | MAX |          |

| t <sub>6s</sub>    | Address setup time                                    |                             | 65  |                                                | 45  |     | 30  |     | 20  |     | ns       |

| t <sub>6h</sub>    | Address hold time                                     | See Figure 2 and Figure 4   | 15  |                                                | 10  |     | 7   |     | 5   |     | ns       |

| t <sub>7w</sub>    | IOR strobe width                                      | See Figure 2 and Figure 4   | 85  |                                                | 70  |     | 50  |     | 40  |     | ns       |

| t <sub>9w</sub>    | Read cycle delay                                      | See Figure 4                | 85  |                                                | 70  |     | 60  |     | 50  |     | ns       |

| t <sub>12d</sub>   | Delay from IOR to data                                | See Figure 4                |     | 90                                             |     | 55  |     | 35  |     | 25  | ns       |

| t <sub>12h</sub>   | Data disable time                                     | 1                           |     | 45                                             |     | 30  |     | 20  |     | 15  | ns       |

| t <sub>13w</sub>   | IOW strobe width                                      | See Figure 2                | 85  |                                                | 70  |     | 50  |     | 40  |     | ns       |

| t <sub>15w</sub>   | Write cycle delay                                     | See Figure 2                | 85  |                                                | 70  |     | 60  |     | 50  |     | ns       |

| t <sub>16s</sub>   | Data setup time                                       | See Figure 2                | 70  |                                                | 50  |     | 30  |     | 20  |     | ns       |

| t <sub>16h</sub>   | Data hold time                                        | See Figure 2                | 35  |                                                | 25  |     | 15  |     | 10  |     | ns       |

| t <sub>17d</sub>   | Delay from IOW to output                              | 50-pF load, see Figure 6    |     | 80                                             |     | 50  |     | 35  |     | 25  | ns       |

| t <sub>18d</sub>   | Delay to set interrupt from MODEM input               | 50-pF load, see Figure 6    |     | 120                                            |     | 80  |     | 50  |     | 35  | ns       |

| t <sub>19d</sub>   | Delay to reset interrupt from IOR                     | 50-pF load                  |     | 100                                            |     | 65  |     | 40  |     | 30  | ns       |

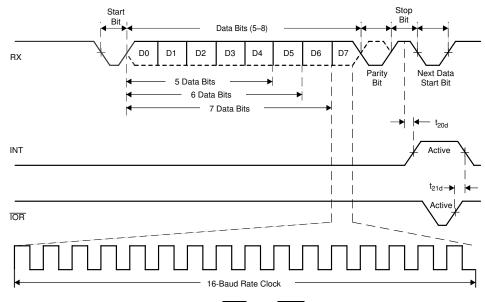

| t <sub>20d</sub>   | Delay from stop to set interrupt                      | See Figure 8                |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

| t <sub>21d</sub>   | Delay from IOR to reset interrupt                     | 50-pF load, see Figure 8    |     | 100                                            |     | 65  |     | 40  |     | 30  | ns       |

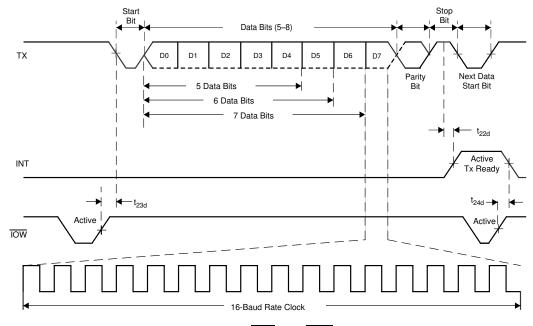

| t <sub>22d</sub>   | Delay from stop to interrupt                          | See Figure 14               |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

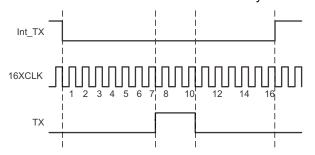

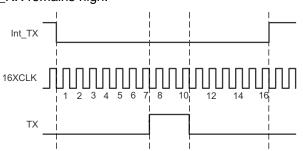

| t <sub>23d</sub>   | Delay from initial IOW reset to transmit start        | See Figure 14               | 8   | 24                                             | 8   | 24  | 8   | 24  | 8   | 24  | baudrate |

| t <sub>24d</sub>   | Delay from IOW to reset interrupt                     | See Figure 14               |     | 90                                             |     | 60  |     | 35  |     | 25  | ns       |

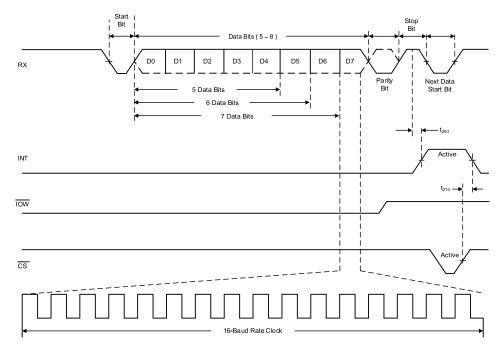

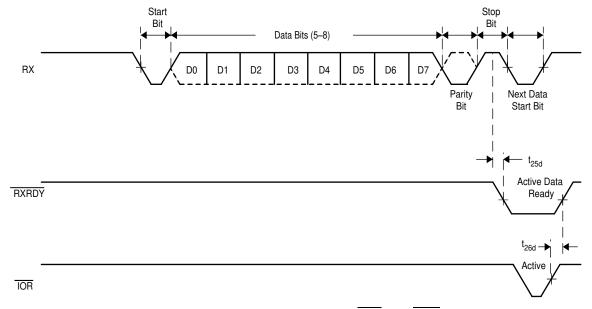

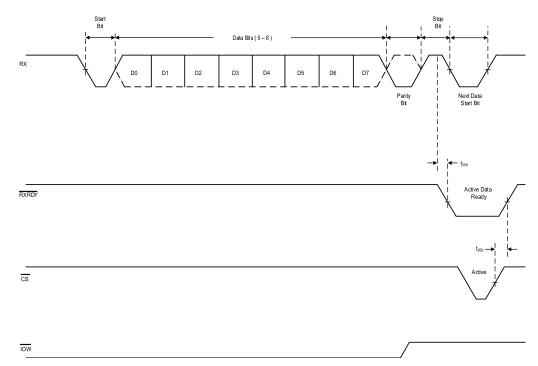

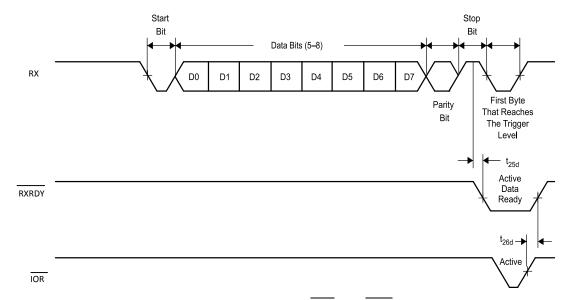

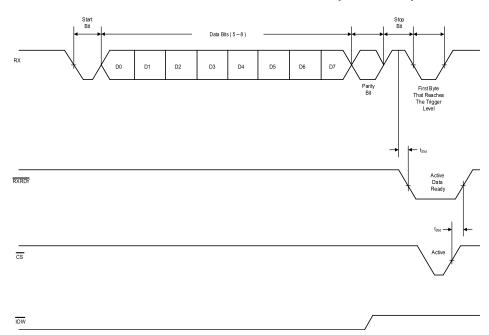

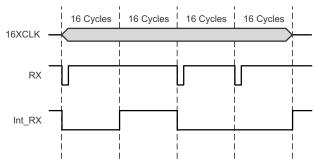

| t <sub>25d</sub>   | Delay from stop to set RXRDY                          | See Figure 10 and Figure 12 |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

| t <sub>26d</sub>   | Delay from IOR to reset RXRDY                         | See Figure 10 and Figure 12 |     | 100                                            |     | 65  |     | 40  |     | 30  | ns       |

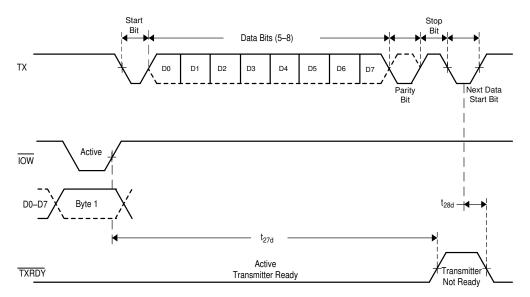

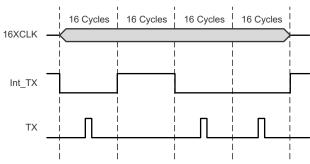

| t <sub>27d</sub>   | Delay from IOW to set TXRDY                           | See Figure 16 and           |     | 80                                             |     | 50  |     | 35  |     | 25  | ns       |

| t <sub>28d</sub>   | Delay from start to reset TXRDY                       | See Figure 16 and           |     | 16                                             |     | 16  |     | 16  |     | 16  | baudrate |

|                    | (MODE = GND)                                          | 1                           |     |                                                |     |     |     |     |     |     |          |

| t <sub>RESET</sub> | Reset pulse width                                     |                             | 200 |                                                | 200 |     | 200 |     | 200 |     | ns       |

| C <sub>P</sub>     | CP clock period                                       |                             | 63  |                                                | 42  |     | 20  |     | 20  |     | ns       |

| t <sub>3w</sub>    | Oscillator or clock speed                             |                             |     | 16                                             |     | 24  |     | 48  |     | 48  | MHz      |

| t <sub>6s</sub>    | Address setup time                                    |                             | 70  |                                                | 45  |     | 30  |     | 20  |     | ns       |

| t <sub>6h</sub>    | Address hold time                                     | See Figure 3 and Figure 5   | 15  |                                                | 10  |     | 7   |     | 5   |     | ns       |

| t <sub>9w</sub>    | Read cycle delay                                      | See Figure 5                | 85  |                                                | 70  |     | 60  |     | 50  |     | ns       |

| t <sub>12d</sub>   | Delay from CS to data                                 | See Figure 5                |     | 95                                             |     | 65  |     | 40  |     | 25  | ns       |

| t <sub>12h</sub>   | Data disable time                                     |                             |     | 45                                             |     | 30  |     | 20  |     | 15  | ns       |

| t <sub>13w</sub>   | IOW strobe width                                      | See Figure 3                | 85  |                                                | 70  |     | 50  |     | 40  |     | ns       |

| t <sub>15w</sub>   | Write cycle delay                                     | See Figure 3                | 85  |                                                | 70  |     | 60  |     | 50  |     | ns       |

| t <sub>16s</sub>   | Data setup time                                       | See Figure 3                | 75  |                                                | 50  |     | 30  |     | 25  |     | ns       |

| t <sub>16h</sub>   | Data hold time                                        | See Figure 3                | 80  |                                                | 50  |     | 35  |     | 25  |     | ns       |

| t <sub>17d</sub>   | Delay from CS to output                               | 50-pF load, see Figure 6    |     | 80                                             |     | 50  |     | 35  |     | 25  | ns       |

| t <sub>18d</sub>   | Delay to set interrupt from MODEM input               | 50-pF load, see Figure 6    |     | 120                                            |     | 75  |     | 45  |     | 35  | ns       |

| t <sub>19d</sub>   | Delay to reset interrupt from CS                      | 50-pF load                  | 1   | 95                                             |     | 65  |     | 40  |     | 30  | ns       |

| t <sub>20d</sub>   | Delay from stop to set interrupt                      | See Figure 8                |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

| t <sub>21d</sub>   | Delay from IOR to reset interrupt                     | 50-pF load, see Figure 8    | 1   | 85                                             |     | 55  |     | 40  |     | 30  | ns       |

| t <sub>22d</sub>   | Delay from stop to interrupt                          | See Figure 14               |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

| t <sub>23d</sub>   | Delay from initial CS reset to transmit start         | See Figure 14               | 8   | 24                                             | 8   | 24  | 8   | 24  | 8   | 24  | baudrate |

| t <sub>24d</sub>   | Delay from IOW to reset interrupt                     | See Figure 14               | 1   | 90                                             |     | 60  |     | 40  |     | 25  | ns       |

| t <sub>25d</sub>   | Delay from stop to set RXRDY                          | See Figure 10 and Figure 12 |     | 1                                              |     | 1   |     | 1   |     | 1   | baudrate |

| t <sub>26d</sub>   | Delay from CS to reset RXRDY                          | See Figure 10 and Figure 12 | 1   | 95                                             |     | 60  |     | 35  |     | 25  | ns       |

|                    |                                                       |                             |     |                                                |     |     |     |     |     |     |          |

Submit Documentation Feedback

Copyright © 2019, Texas Instruments Incorporated

## **Timing Requirements (continued)**

$T_A = -40$ °C to 105°C,  $V_{CC} = 1.8 \text{ V}$  to 5 V ±10% (unless otherwise noted)

|                  |                                 |                           |     | LIMITS |     |     |     |     |     |     |          |

|------------------|---------------------------------|---------------------------|-----|--------|-----|-----|-----|-----|-----|-----|----------|

|                  |                                 |                           | 1.8 | ٧      | 2.5 | ٧   | 3.3 | V   | 5 ' | ٧   | UNIT     |

|                  |                                 |                           | MIN | MAX    | MIN | MAX | MIN | MAX | MIN | MAX |          |

| t <sub>27d</sub> | Delay from CS to set TXRDY      | See Figure 16 and         |     | 80     |     | 50  |     | 35  |     | 25  | ns       |

| t <sub>28d</sub> | Delay from start to reset TXRDY | See Figure 16 and         |     | 16     |     | 16  |     | 16  |     | 16  | baudrate |

| t <sub>29h</sub> | IOW hold time to CS             | See Figure 3 and Figure 5 | 15  |        | 10  |     | 7   |     | 5   |     | ns       |

| t <sub>29s</sub> | IOW setup time to CS            | See Figure 3 and Figure 5 | 70  |        | 50  |     | 30  |     | 20  |     | ns       |

Product Folder Links: TL16C750E

SLLSF10 – DECEMBER 2019 www.ti.com

## TEXAS INSTRUMENTS

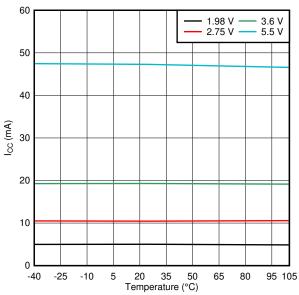

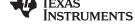

## 7.7 Typical Characteristics

Tested as per electrical characteristics table

Figure 1. I<sub>CC</sub> vs Temperature

## 8 Parameter Measurement Information

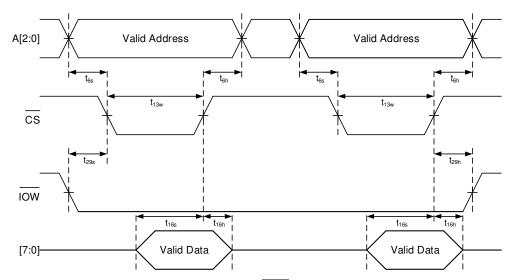

Figure 2. General Write Timing (IOR and IOW Mode, MODE = VCC)

10

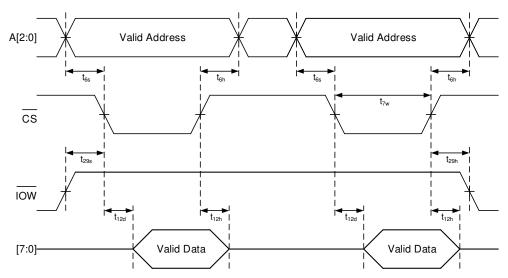

Figure 3. General Write Timing (IOW Only Mode, MODE = GND)

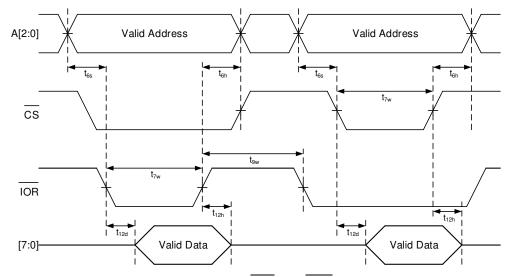

Figure 4. General Read Timing (IOR and IOW Mode, MODE = VCC)

Figure 5. General Read Timing (IOW Only Mode, MODE = GND)

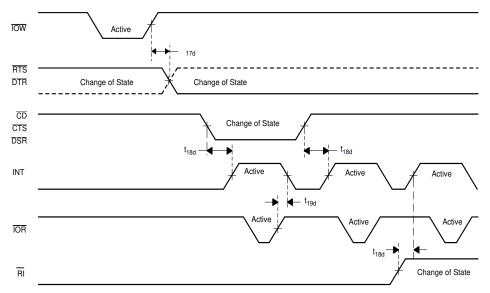

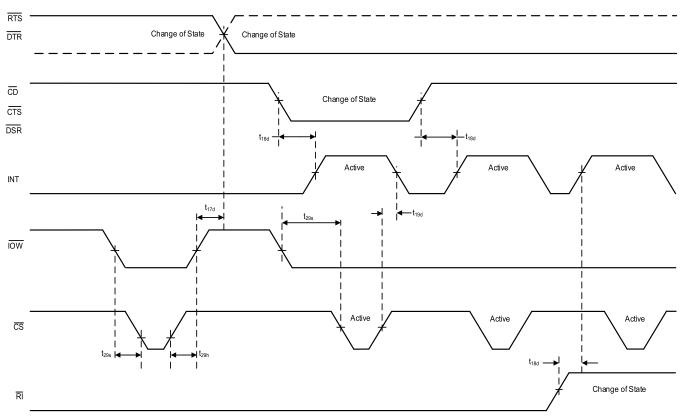

Figure 6. Modem or Output Timing ( $\overline{IOR}$  and  $\overline{IOW}$  Mode, MODE = VCC)

Figure 7. Modem or Output Timing (IOW Only Mode, MODE = GND)

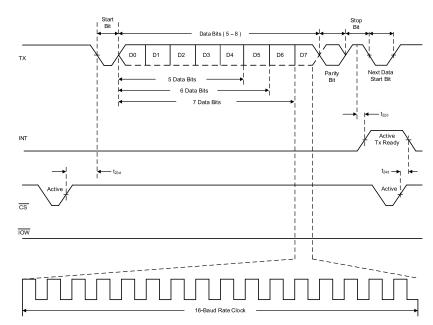

Figure 8. Receive Timing (IOR and IOW Mode, MODE = VCC)

## **Parameter Measurement Information (continued)**

Figure 9. Receive Timing (IOW Only Mode, MODE = GND)

Figure 10. Receive Ready Timing in Non-FIFO Mode (IOR and IOW Mode, MODE = VCC)

Submit Documentation Feedback

Figure 11. Receive Ready Timing in Non-FIFO Mode (IOW Only Mode, MODE = GND)

Figure 12. Receive Timing in FIFO Mode (IOR and IOW Mode, MODE = VCC)

## **Parameter Measurement Information (continued)**

Figure 13. Receive Timing in FIFO Mode (IOW Only Mode, MODE = GND)

Figure 14. Transmit Timing (IOR and IOW Mode, MODE = VCC)

Submit Documentation Feedback

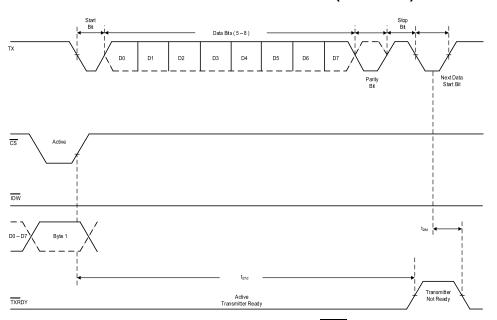

Figure 15. Transmit Timing (IOW Only Mode, MODE = GND)

Figure 16. Transmit Ready Timing in Non-FIFO Mode (IOR and IOW Mode, MODE = VCC)

Figure 17. Transmit Ready Timing in Non-FIFO Mode (IOW Only Mode, MODE = GND)

#### 9 Detailed Description

#### 9.1 Overview

www.ti.com

The TL16C750E UART is pin-compatible with the TL16C550D UART in the PFB package. It provides more enhanced features. All additional features are provided through a special enhanced features register.

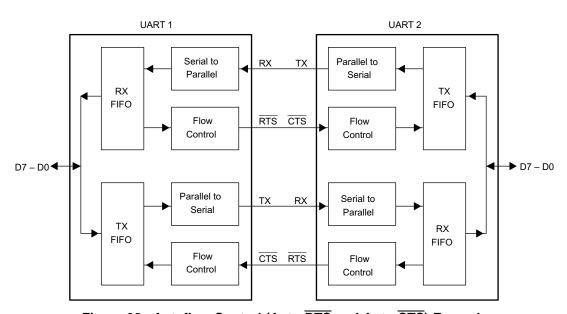

The TL16C750E UART performs serial-to-parallel conversion on data characters received from peripheral devices or modems and parallel-to-parallel conversion on data characters transmitted by the processor. The complete status of the TL16C750E UART can be read at any time during functional operation by the processor.

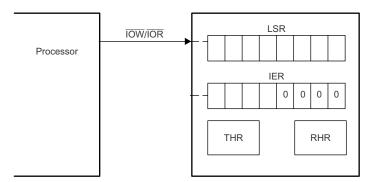

The UART transmits data sent to it from the peripheral 8-bit bus on the TX signal and receives characters on the RX signal. Characters can be programmed to be 5, 6, 7, or 8 bits. The UART has a 128-byte receive FIFO and transmit FIFO and can be programmed to interrupt at different trigger levels. The UART generates its own desired baud rate based upon a programmable divisor and its input clock. It can transmit even, odd, or no parity and 1-, 1.5-, or 2-stop bits. The receiver can detect break, idle or framing errors, FIFO overflow, and parity errors. The transmitter can detect FIFO underflow. The UART also contains a software interface for modem control operations, software flow control and hardware flow control capabilities.

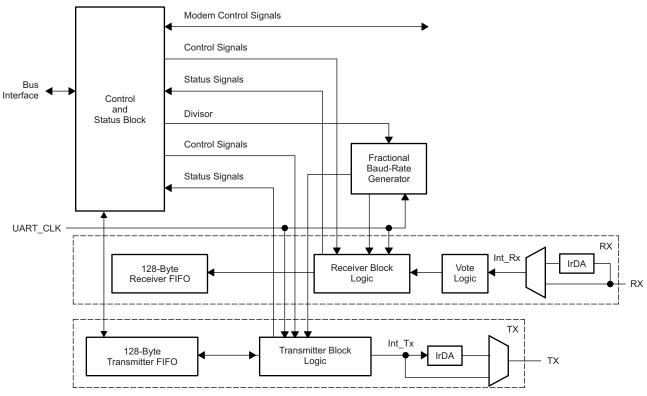

#### 9.2 Functional Block Diagrams

Figure 18. TL16C750E Functional Block Diagram

Copyright © 2019, Texas Instruments Incorporated

## **NSTRUMENTS**

#### Functional Block Diagrams (continued)

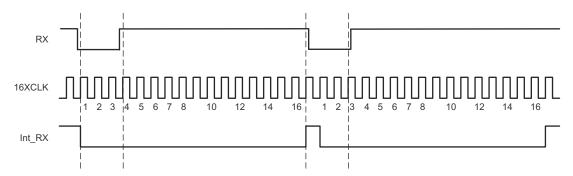

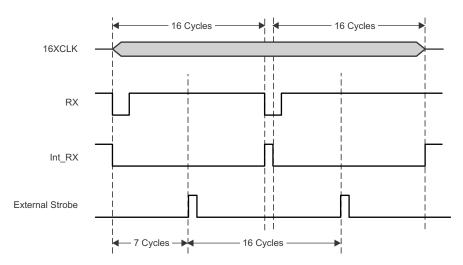

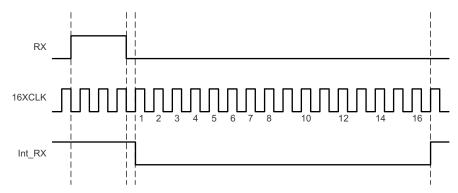

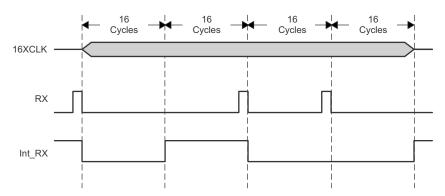

NOTE: The vote logic determines whether the RX data is a logic 1 or 0. It takes three samples of the RX line and uses a majority vote to determine the logic level received. The vote logic operates on all bits received.

Figure 19. TL16C750E Functional Block Diagram – Control Blocks

#### 9.3 Feature Description

#### 9.3.1 UART Modes

The TL16C750E UART can be placed in an alternate mode (FIFO mode) relieving the processor of excessive software overhead by buffering received and transmitted characters.

The TL16C750E UART has selectable hardware flow control and software flow control. Both schemes significantly reduce software overhead and increase system efficiency by automatically controlling serial data flow. Hardware flow control uses the RTS output and CTS input signals. Software flow control uses programmable Xon and Xoff characters.

## 9.3.2 Trigger Levels

The TL16C750E UART provides independent selectable and programmable trigger levels for both receiver and transmitter DMA and interrupt generation. After reset, both transmitter and receiver FIFOs are disabled and so, in effect, the trigger level is the default value of one byte. The selectable trigger levels are available through the FCR. The programmable trigger levels are available through the TLR.

Both the receiver and transmitter FIFOs can store up to 128 bytes (including three additional bits of error status per byte for the receiver FIFO) and have selectable or programmable trigger levels. Primary outputs RXRDY and TXRDY allow signaling of DMA transfers.

20

#### Feature Description (continued)

#### NOTE

When writing data into the transmit FIFO, the transmission starts immediately, which shifts the first element out of the FIFO. Depending on the speed of the processor, it may be possible to get a pulse on the TXRDY pin, since the level falls below the trigger threshold.

#### 9.3.3 Hardware Flow Control

Hardware flow control is composed of auto-CTS and auto-RTS. Auto-CTS and auto-RTS can be enabled or disabled independently by programming EFR[7:6].

With auto-CTS, CTS must be active before the UART can transmit data. Auto-RTS only activates the RTS output when there is enough room in the FIFO to receive data and deactivates the RTS output when the RX FIFO is sufficiently full. The HALT and RESTORE trigger levels in the TCR determine the levels at which RTS is activated or deactivated. If both auto-CTS and auto-RTS are enabled, when RTS is connected to CTS, data transmission does not occur unless the receiver FIFO has empty space. Thus, overrun errors are eliminated during hardware flow control. If not enabled, overrun errors occur if the transmit data rate exceeds the receive FIFO servicing latency.

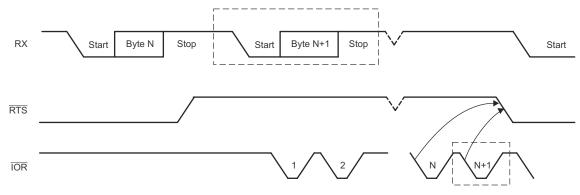

#### 9.3.4 Auto-RTS

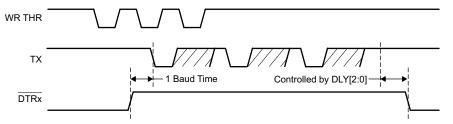

Auto-RTS data flow control originates in the receiver block (see Figure 18). Figure 20 shows RTS functional timing. The receiver FIFO trigger levels used in Auto-RTS are stored in the TCR. RTS is active if the RX FIFO level is below the HALT trigger level in TCR[3:0]. When the receiver FIFO HALT trigger level is reached, RTS is deasserted. The sending device (for example, another UART) may send an additional byte after the trigger level is reached (assuming the sending UART has another byte to send) because it may not recognize the deassertion of RTS until it has begun sending the additional byte. RTS is automatically reasserted once the receiver FIFO reaches the RESUME trigger level programmed via TCR[7:4]. This reassertion allows the sending device to resume transmission.

N = receiver FIFO trigger level B.

Copyright © 2019, Texas Instruments Incorporated

The two blocks in dashed lines cover the case where an additional byte is sent as described in Auto-RTS.

Figure 20. RTS Functional Timing

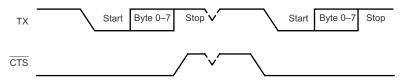

## 9.3.5 Auto-CTS

The transmitter circuitry checks CTS before sending the next data byte. When CTS is active, the transmitter sends the next byte. To stop the transmitter from sending the following byte, CTS must be deasserted before the middle of the last stop bit that is currently being sent. The auto-CTS function reduces interrupts to the host system. When flow control is enabled, the CTS state changes and need not trigger host interrupts because the device automatically controls its own transmitter. Without auto-CTS, the transmitter sends any data present in the transmit FIFO and a receiver overrun error can result. Figure 21 shows CTS functional timing, and Figure 22 shows an example of autoflow control.

Product Folder Links: TL16C750E

#### **Feature Description (continued)**

- A. When CTS is low, the transmitter keeps sending serial data out.

- B. When CTS goes high before the middle of the last stop bit of the current byte, the transmitter finishes sending the current byte, but it does not send the next byte.

- C. When CTS goes from high to low, the transmitter begins sending data again.

Figure 21. CTS Functional Timing

Figure 22. Autoflow Control (Auto-RTS and Auto-CTS) Example

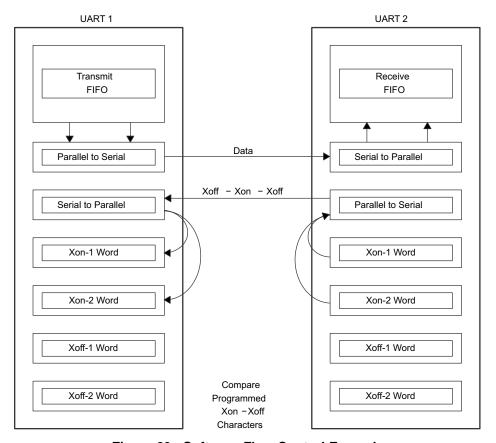

#### 9.3.6 Software Flow Control

Software flow control is enabled through the enhanced feature register and the modem control register. Different combinations of software flow control can be enabled by setting different combinations of EFR[3-0]. Table 1 shows software flow control options.

Two other enhanced features relate to software flow control:

- Xon Any Function [MCR(5): Operation resumes after receiving any character after recognizing the Xoff character.

- **Special Character [EFR(5)]**: Incoming data is compared to Xoff2. Detection of the special character sets the Xoff interrupt [IIR(4)] but does not halt transmission. The Xoff interrupt is cleared by a read of the IIR. The special character is transferred to the RX FIFO.

#### **NOTE**

It is possible for an Xon1 character to be recognized as an Xon Any character, which could cause an Xon2 character to be written to the RX FIFO.

2 Submit Documentation Feedback

| BIT 3 | BIT 2 | BIT 1 | BIT 0 | TX, RX SOFTWARE FLOW CONTROLS                                                      |

|-------|-------|-------|-------|------------------------------------------------------------------------------------|

| 0     | 0     | Х     | Х     | No transmit flow control                                                           |

| 1     | 0     | Х     | Х     | Transmit Xon1, Xoff1                                                               |

| 0     | 1     | Х     | Х     | Transmit Xon2, Xoff2                                                               |

| 1     | 1     | Х     | Х     | Transmit Xon1, Xon2: Xoff1, Xoff2                                                  |

| Х     | Х     | 0     | 0     | No receive flow control                                                            |

| Х     | Х     | 1     | 0     | Receiver compares Xon1, Xoff1                                                      |

| Х     | Х     | 0     | 1     | Receiver compares Xon2, Xoff2                                                      |

| 1     | 0     | 1     | 1     | Transmit Xon1, Xoff1 Receiver compares Xon1 or Xon2, Xoff1 or Xoff2                |

| 0     | 1     | 1     | 1     | Transmit Xon2, Xoff2 Receiver compares Xon1 or Xon2, Xoff1 or Xoff2                |

| 1     | 1     | 1     | 1     | Transmit Xon1, Xon2: Xoff1, Xoff2 Receiver compares Xon1 and Xon2: Xoff1 and Xoff2 |

| 0     | 0     | 1     | 1     | No transmit flow control<br>Receiver compares Xon1 and Xon2: Xoff1 and Xoff2       |

When software flow control operation is enabled, the TL16C750E device compares incoming data with Xoff1 and Xoff2 programmed characters (in certain cases Xoff1 and Xoff2 must be received sequentially). (1) When an Xoff character is received, transmission is halted after completing transmission of the current character. Xoff character detection also sets IIR[4] and causes INT to go high (if enabled via IER[5]).

To resume transmission an Xon1 and Xon2 character must be received (in certain cases Xon1 and Xon2 must be received sequentially). When the correct Xon characters are received IIR[4] is cleared and the Xoff interrupt disappears.

#### NOTE

If a parity, framing, or break error occurs while receiving a software flow control character, this character is treated as normal data and is written to the RCV FIFO.

Xoff1 and Xoff2 characters are transmitted when the RX FIFO has passed the programmed trigger level TCR[3:0].

Xon1 and Xon2 characters are transmitted when the RX FIFO reaches the trigger level programmed via TCR[7:4].

#### **NOTE**

If, after an Xoff character has been sent, software flow control is disabled, the UART transmits Xon characters automatically to enable normal transmission to proceed. A feature of the TL16C750E UART design is that if the software flow combination (EFR[3:0]) changes after an Xoff has been sent, the originally programmed Xon is automatically sent. If the RX FIFO is still above the trigger level, the newly programmed Xoff1 or Xoff2 is transmitted.

The transmission of Xoff and Xon follows the exact same protocol as transmission of an ordinary byte from the FIFO. This means that even if the word length is set to be 5, 6, or 7 characters, then the 5, 6, or 7 least significant bits of Xoff1, Xoff2 and Xon1, Xon2 are transmitted. The transmission of 5, 6, or 7 bits of a character is seldom done, but this functionality is included to maintain compatibility with earlier designs.

It is assumed that software flow control and hardware flow control are never enabled simultaneously. Figure 23 shows a software flow control example.

(1) When pairs of Xon and Xoff characters are programmed to occur sequentially, received Xon1 and Xoff1 characters is written to the RX FIFO if the subsequent character is not Xon2 and Xoff2.

Copyright © 2019, Texas Instruments Incorporated

Figure 23. Software Flow Control Example

#### 9.3.7 Software Flow Control Example

Assumptions: UART1 is transmitting a large text file to UART2. Both UARTs are using software flow control with single character Xoff (0F) and Xon (0D) tokens. Both have Xoff threshold (TCR [3:0] = 7) set to 56 and Xon threshold (TCR[7:4] = 4) set to 32. Both have the interrupt receive threshold (TLR[7:4] = 6) set to 48.

UART1 begins transmission and sends 48 characters, at which point UART2 generates an interrupt to its processor to service the RCV FIFO, but assumes the interrupt latency is fairly long. UART1 continues sending characters until a total of 56 characters have been sent. At this time UART2 transmits a 0F to UART1, informing UART1 to halt transmission. UART1 likely sends the 57<sup>th</sup> character while UART2 is sending the Xoff character. Now, UART2 is serviced and the processor reads enough data out of the RCV FIFO that the level drops to 32. UART2 now sends a 0D to UART1, informing UART1 to resume transmission.

#### NOTE

It is possible that there could be a glitch on the  $\overline{\mathsf{RXRDY}}$  pin when the Xoff2 character is received with a parity error. A read to the LSR register shows that bit 7 is set, due to an error in the RX FIFO.

4 Submit Documentation Feedback

#### 9.3.8 Reset

Table 2 summarizes the state of outputs after reset.

Table 2. Register Reset Functions<sup>(1)</sup>

| REGISTER | NAME                              | RESET<br>CONTROL | RESET STATE                                     |

|----------|-----------------------------------|------------------|-------------------------------------------------|

| IER      | Interrupt enable register         | RESET            | 0x00                                            |

| IIR      | Interrupt identification register | RESET            | 0x01                                            |

| FCR      | FIFO control register             | RESET            | 0x00                                            |