# TIOL221 Dual Channel IO-Link Device PHY with Integrated LDO and SPI Interface

#### 1 Features

- 7V to 36V supply voltage

- IO-link configurable CQ output with auxiliary digital output (DO) and digital input (DI) channels

- Configurable via pin-control or SPI interface

- Both CQ and DO channels configurable for use in IO-link master modules

- · PNP, NPN or IO-Link configurable CQ output

- IEC 61131-9 COM1, COM2 and COM3 Data Rate Support

- Output drivers with low power dissipation and high configurability

- Low R<sub>DSON</sub> 2.5Ω (typical)

- Active driver current limiting capability

- Configurable driver overcurrent limit: 50mA to 500mA

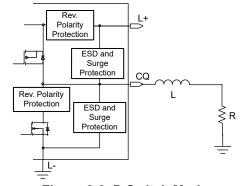

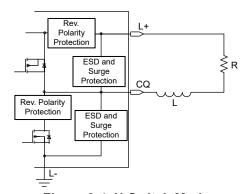

- Active reverse polarity protection of up to 65V on LP, CQ, DO and DI

- Safe and fast demagnetization of inductive loads

- Integrated protection features for robust systems

- Fault indicator for overcurrent, overtemperature and UVLO faults

- Extended ambient temperature operation:

-40°C to 125°C

- ±8kV IEC 61000-4-2 ESD contact discharge

- ±4kV IEC 61000-4-4 electrical fast transient

- ±1.2kV, 500Ω IEC 61000-4-5 surge

- Large capacitive and inductive load driving capability

- · Integrated LDO provides up to 20mA current

- Optional external regulator input (5V) to reduce internal power dissipation in the LDO

- Small space-saving package options

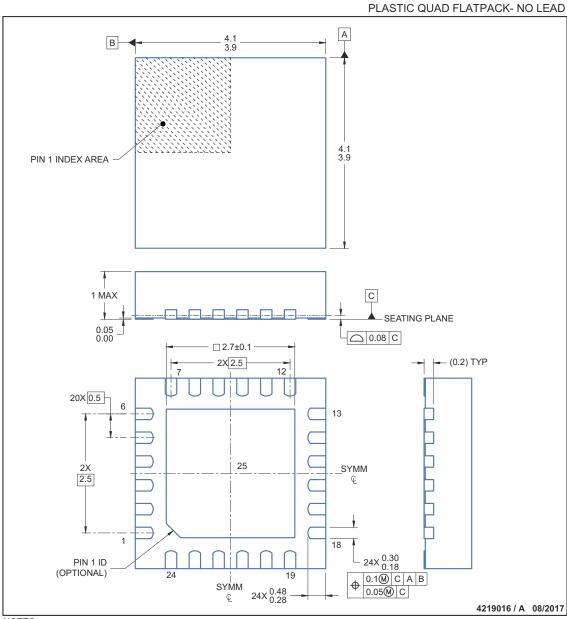

- 4mm x 4mm VQFN package

- 2.7mm x 2.7mm DSBGA package

# 2 Applications

- · Field Transmitters and actuators

- Factory automation

- · Process automation

- · IO-link PHY in remote IO

## 3 Description

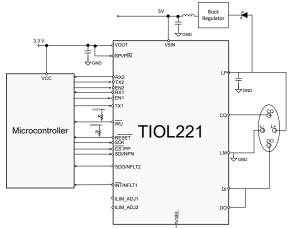

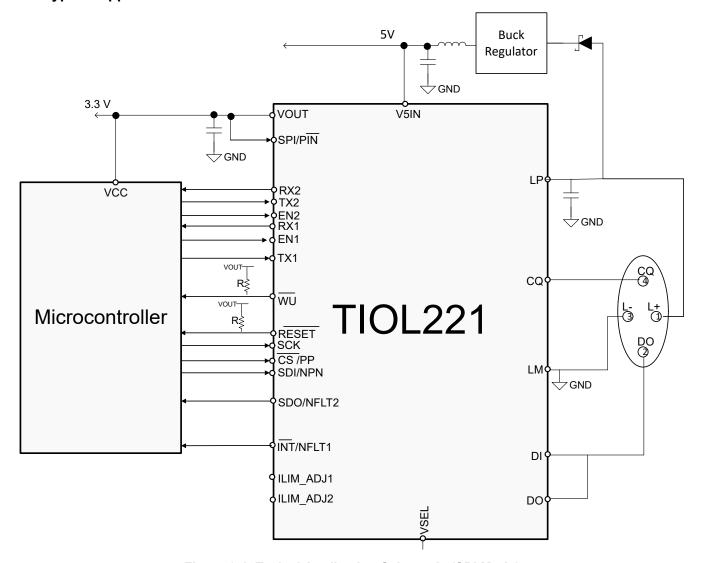

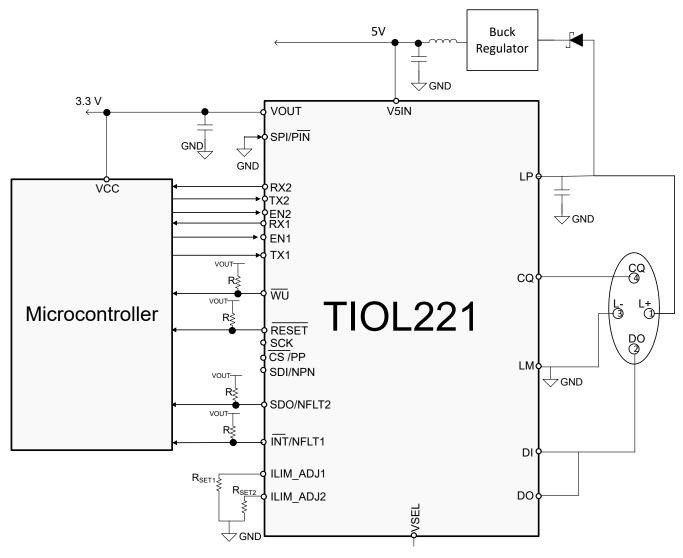

The TIOL221 transceiver integrates dual low-power output drivers with active reverse polarity protection. When the device is connected to an IO-Link controller through a three-wire interface, the controller can initiate communication, and exchange data with the remote node while the TIOL221 acts as a complete physical layer for the communication. The device also integrates an auxiliary DI channel.

The device is capable of withstanding up to  $1.2\text{kV}~(500\Omega)$  of IEC 61000-4-5 surge and features integrated reverse polarity protection. In addition to the SPI interface for configurability and expanded diagnostic capability, a simple pin-programmable interface allows easy interfacing with the controller circuits. The output current limit can be configured using either an external resistor or per-configured limits via SPI interface. TIOL221 can be configured to generate wake-up pulse, and be used in IO-link controller applications. Fault reporting and internal protection functions are provided for undervoltage, overcurrent and overtemperature conditions.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TIOL221     | VQFN (24)              | 4mm x 4mm                   |

|             | DSBGA (25) (3)         | 2.7mm x 2.7mm               |

- (1) For more information, see Section 12.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

- (3) Product Preview

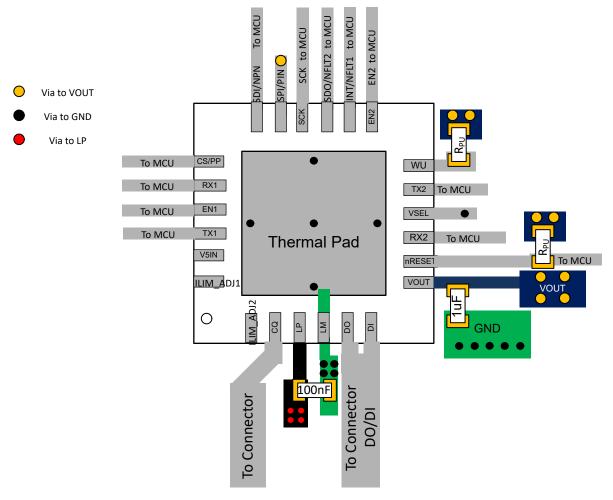

**Typical Application Diagram**

# **Table of Contents**

| 1 Features                           | 1              | 7.4 Device Functional Modes                      | 26      |

|--------------------------------------|----------------|--------------------------------------------------|---------|

| 2 Applications                       |                | 7.5 SPI Programming                              |         |

| 3 Description                        |                | 8 Application and Implementation                 |         |

| 4 Pin Configuration and Functions    |                | 8.1 Application Information                      |         |

| 5 Specifications                     | <mark>5</mark> | 8.2 Typical Application                          |         |

| 5.1 Absolute Maximum Ratings         |                | 8.3 Power Supply Recommendations                 |         |

| 5.2 ESD Ratings                      | <u>5</u>       | 8.4 Layout                                       |         |

| 5.3 ESD Ratings - IEC Specifications |                | 9 TIOL221 Registers                              |         |

| 5.4 Recommended Operating Conditions | 5              | 10 Device and Documentation Support              | 47      |

| 5.5 Thermal Information              | 6              | 10.1 Receiving Notification of Documentation Upo | lates47 |

| 5.6 Electrical Characteristics       | 6              | 10.2 Support Resources                           | 47      |

| 5.7 Switching Characteristics        | 9              | 10.3 Trademarks                                  | 47      |

| 5.8 Typical Characteristics          | 12             | 10.4 Electrostatic Discharge Caution             | 47      |

| 6 Parameter Measurement Information  |                | 10.5 Glossary                                    |         |

| 7 Detailed Description               | 17             | 11 Revision History                              |         |

| 7.1 Overview                         |                | 12 Mechanical, Packaging, and Orderable          |         |

| 7.2 Functional Block Diagrams        | 18             | Information                                      | 47      |

| 7.3 Feature Description              | 18             | 12.1 Mechanical Data                             |         |

| •                                    |                |                                                  |         |

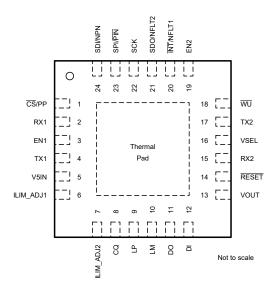

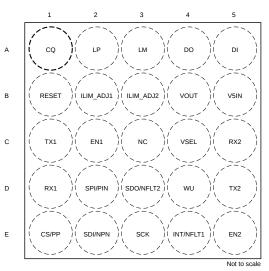

# **4 Pin Configuration and Functions**

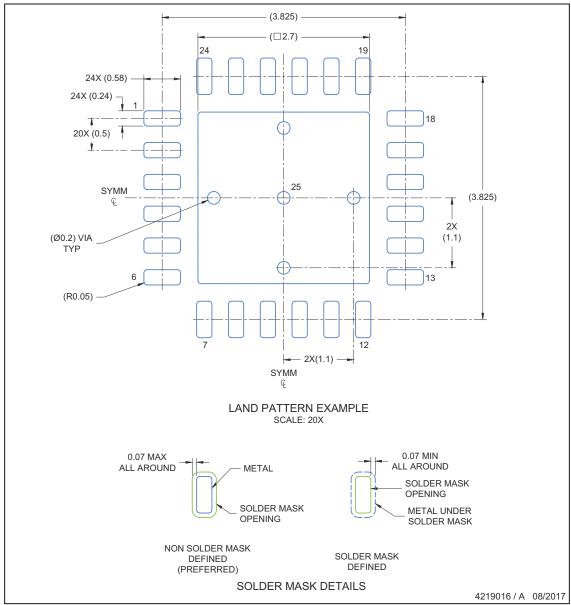

Figure 4-1. RGE (VQFN), 24-Pin (Top View)

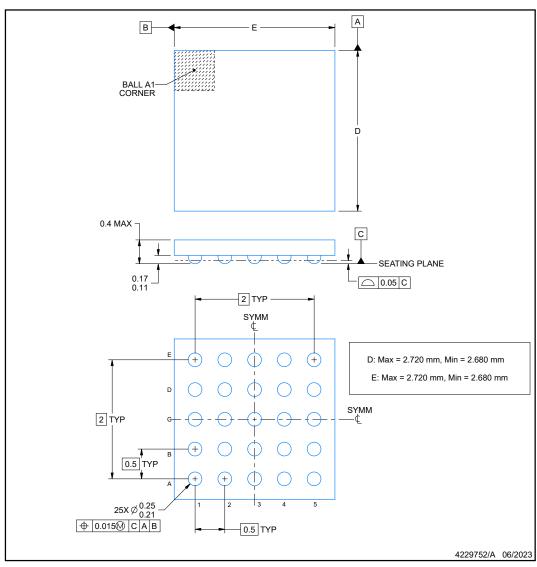

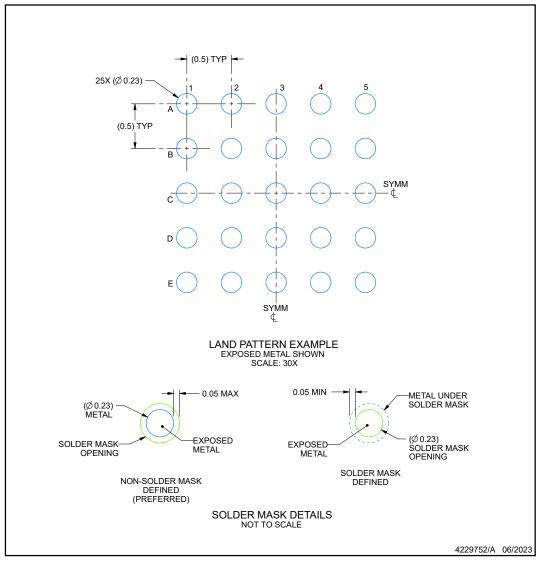

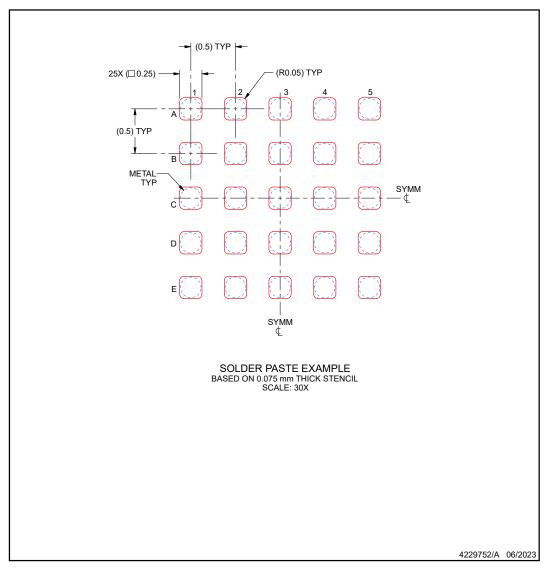

Figure 4-2. YAH (DSBGA), 25-Pin (Top View, Bumps Down)

**Table 4-1. Pin Functions**

| PIN NAME PIN NUMBER |      | UMBER | 1/0 | TVDE                   | DESCRIPTION                                                                                                                   |

|---------------------|------|-------|-----|------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME            | VQFN | DSBGA | 1/0 | TYPE                   | DESCRIPTION                                                                                                                   |

| CQ                  | 8    | A1    | I/O | High Voltage           | IO-link signal data pin.                                                                                                      |

| CS/PP               | 1    | E1    | I   | Digital                | Chip select input pin in the SPI-mode. Push-pull mode selection input in pin-mode                                             |

| DI                  | 12   | A5    | 1   | High Voltage           | DI receiver Input. DI receiver output can be monitored at the RX2 pin.                                                        |

| DO                  | 11   | A4    | 0   | High Voltage           | DO driver output. DO is the inverse logic level of the input at the TX2 pin.                                                  |

| EN1                 | 3    | C2    | I   | Low voltage<br>Digital | CQ driver enable input signal from the local controller. Logic low sets the CQ output at Hi-Z. Weak internal pull-down.       |

| EN2                 | 19   | E5    | I   | Low voltage<br>Digital | DO driver enable input signal from the local controller. Logic low sets the DO output at Hi-Z. Weak internal pull-down.       |

| ILIM_ADJ1           | 6    | B2    | I   | Low voltage<br>Analog  | Input for the current limit adjustment for the CQ driver. Connect resistor RSET1 between ILIM_ADJ1 and LM.                    |

| ILIM_ADJ2           | 7    | B3    | I   | Low voltage<br>Analog  | Input for the current limit adjustment for the DO driver. Connect resistor RSET2 between ILIM_ADJ2 and LM.                    |

| ĪNT/NFLT1           | 20   | E4    | 0   | Low voltage<br>Digital | Interrupt output, push-pull (SPI-mode) or fault indicator for CQ channel, opendrain (pin-mode)                                |

| LM                  | 10   | A3    | G   | Ground                 | Ground.                                                                                                                       |

| LP                  | 9    | A2    | PI  | High Voltage           | Power supply input (24V typical) to the device. Connect $1\mu F$ capacitor to LM (ground) as close to the device as possible. |

| NC                  |      | C3    | NC  | No Connect             | Not connected internally.                                                                                                     |

| RX1                 | 2    | D1    | 0   | Low voltage<br>Digital | C/Q Receiver Logic Output. RX2 is the inverse logic level of the signal on the CQ input.                                      |

| RX2                 | 15   | C5    | 0   | Low voltage<br>Digital | DI Receiver Logic Output. RX2 is the inverse logic level of the signal on the DI input.                                       |

| SCK                 | 22   | E3    | I   | Low voltage<br>Digital | SPI clock input                                                                                                               |

| SDI/NPN             | 24   | E2    | ı   | Low voltage<br>Digital | SPI serial data input (SPI-mode) Or NPN mode selector (pin-mode)                                                              |

| SDO/NFLT2           | 21   | D3    | 0   | Low voltage<br>Digital | SPI serial data output, push-pull (SPI-mode) or fault inductor for DO channel, open-drain (pin-mode)                          |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

# **Table 4-1. Pin Functions (continued)**

| PIN NAME    | PIN NU      | JMBER | I/O   | TYPE                   | DESCRIPTION                                                                                                                                                                                                       |  |  |  |

|-------------|-------------|-------|-------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NAME    | VQFN        | DSBGA | 1 1/0 | ITPE                   | DESCRIPTION                                                                                                                                                                                                       |  |  |  |

| SPI/PIN     | 23          | D2    | I     | Low voltage<br>Digital | SPI or pin-mode selection input. Drive this pin low for pin-mode operation. Drive this pin high for SPI-mode control.                                                                                             |  |  |  |

| TX1         | 4           | C1    | I     | Low voltage<br>Digital | CQ driver input data from local microcontroller. Weak internal pull-up.                                                                                                                                           |  |  |  |

| TX2         | 17          | D5    | ı     | Low voltage<br>Digital | DO driver input data from local microcontroller. Weak internal pull-up.                                                                                                                                           |  |  |  |

| VOUT        | 13          | B4    | PO    | Low voltage            | LDO regulator output. Output level determined by VSEL pin                                                                                                                                                         |  |  |  |

| VSEL        | 16          | C4    | I     | Low voltage            | Connect to GND for 3.3V LDO output with LP as the LDO input supply Connect to VOUT for 5V LDO output with LP as the LDO input supply Leave the pin floating for 3.3V LDO output with V5IN as the LDO input supply |  |  |  |

| RESET       | 14          | B1    | О     | Low voltage            | Reset output pin, open-drain, active low. The pin behaves as a reset pin to indicate UV on LP or VOUT.                                                                                                            |  |  |  |

| V5IN        | 5           | B5    | PI    | Low voltage            | (Optional) Connect this pin 5V supply input from external regulator to reduce the power dissipation from the internal regulator. Leave the pin floating if unused.                                                |  |  |  |

| WU          | 18          | D4    | 0     | Low voltage<br>Digital | Wake-up indicator to the local microcontroller. Open-drain output, connect this pin via pull-up resistor to VOUT.                                                                                                 |  |  |  |

| Thermal Pad | Thermal Pad | N/A   | G     | Ground                 | Connect the exposed thermal pad to ground (LM) for optimal thermal and electrical performance                                                                                                                     |  |  |  |

# 5 Specifications

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                                                                             |                                                                                                       | MIN  | MAX                               | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|-----------------------------------|------|

| LP, CQ, DO, DI                                                                                                                                              | Steady state voltage for LP, CQ, DO and DI                                                            | -65  | 65                                | V    |

| [LF, CQ, DO, DI                                                                                                                                             | Steady state voltage for LP, CQ, DO and DI  Transient pulse width < 100 $\mu$ s for LP, CQ, DO and DI | V    |                                   |      |

| $ \begin{vmatrix}  V_{(LP)} - V_{(CQ)} , \  V_{(LP)} - V_{(DO)} , \  V_{(LP)} - V_{(DI)} , \  V_{(LP)} - V_{(DI)} , \  V_{(DO)} - V_{(DI)}  \end{vmatrix} $ | Voltage drop between bus pins                                                                         |      | 65                                | V    |

| V <sub>OUT</sub>                                                                                                                                            | Regulator output voltage                                                                              | -0.3 | 6                                 | V    |

| TX1, TX2, EN1, EN2, VSEL, RX1, RX2, CS/PP, SDI/NPN, SDO/NFLT2, SCK, ĪNT/NFLT1, WŪ, ILIM_ADJ1, ILIM_ADJ2, SPI/PĪN                                            | Logic pin voltage                                                                                     | -0.3 | min(V <sub>OUT</sub> +0.3<br>, 6) | V    |

| Output current                                                                                                                                              | RX1, RX2, WU, INT/NFLT1, SDO/NFLT2,                                                                   | -5   | 5                                 | mA   |

| Storage temperature, T <sub>stg</sub>                                                                                                                       |                                                                                                       | -55  | 170                               | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute maximum ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If briefly operating outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not sustain damage, but it may not be fully functional. Operating the device in this manner may affect device reliability, functionality, performance, and shorten the device lifetime. All voltages are with reference to the L- pin, unless otherwise specified.

## 5.2 ESD Ratings

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | All pins | ±4000 | ٧ |

|--------------------|-------------------------|-------------------------------------------------------------------|----------|-------|---|

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged Device Model (CDM), per ANSI/ESDA/JEDEC JS-002 (2)        | All pins | ±750  | V |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

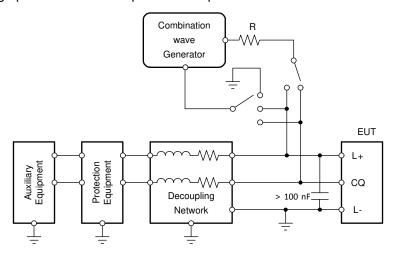

## 5.3 ESD Ratings - IEC Specifications

|                    |                         |                                                                                               | VALUE  | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------|--------|------|

|                    | Electrostatic discharge | IEC 61000-4-2 ESD (Contact Discharge), LP, CQ, DO, DI and LM (1) (2)                          | ±8,000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | IEC 61000-4-5, 1.2 µs/50 µs Surge with 500 $\Omega$ in series, LP, CQ, DO, DI and LM $^{(1)}$ | ±1,200 | V    |

|                    | Electrostatic discharge | IEC 61000-4-4 EFT (Fast transient or burst), LP, CQ, DO, DI and LM (1)                        | ±4,000 |      |

- (1) Minimum 100-nF capacitor is required between LP and LM. Minimum 1-µF capacitor is required between VOUT and LM.

- (2) Device requires a minimum 1nF capacitor between the CQ/DO driver output and LM to pass ±8000 V. Passing level is ±4000 V without the minimum 1nF capacitor

## 5.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                                             |                         | MIN | NOM | MAX | UNIT |

|---------------------|---------------------------------------------|-------------------------|-----|-----|-----|------|

| V <sub>(LP)</sub>   | 24V Input Supply Voltage                    |                         | 7   | 24  | 36  | V    |

| V <sub>(V5IN)</sub> | 5V Input Supply Voltage                     | 5V Input Supply Voltage | 4.5 | 5   | 5.5 | V    |

| V <sub>(I)</sub>    | Logic level input voltage at TX1, TX2, EN1, | 3.3 V configuration     | 3   | 3.3 | 3.6 |      |

|                     | EN2, CS/PP, SDI/NPN, SCK, SPI/PIN           | 5 V configuration       | 4.5 | 5   | 5.5 | V    |

| 1/t <sub>BIT</sub>  | Data rate (Communication mode)              |                         |     |     | 250 | kbps |

| I <sub>(VOUT)</sub> | LDO output current                          |                         |     |     | 20  | mA   |

| T <sub>A</sub>      | Operating ambient temperature               |                         | -40 |     | 125 | °C   |

| TJ                  | Junction temperature                        |                         | -40 |     | 150 | °C   |

### 5.5 Thermal Information

|                       | THERMAL METRIC(1)                            |               | UNIT          |      |

|-----------------------|----------------------------------------------|---------------|---------------|------|

|                       | THERMAL METRIC                               | RGE (24 Pins) | YAH (25 Pins) | ONI  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 32.2          | 58.5          | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 27.2          | 0.2           | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 11.4          | 14.5          | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3           | 0.1           | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 11.4          | 14.3          | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | 2.7           | N/A           | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 5.6 Electrical Characteristics

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V,  $V_{VOUT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                                | PARAMETER                                                   | TEST CONDITIO                                                                                                                                                                                             | NS                                                                            | MIN  | TYP  | MAX  | UNIT |

|--------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|------|

| POWER SUF                      | PPLIES (LP)                                                 |                                                                                                                                                                                                           |                                                                               |      |      |      |      |

| I <sub>(LP-SHDN)</sub>         | Supply quiescent current in shutdown mode                   | CQ TX and RX, DO and DI are dis<br>VOUT. SPI mode only                                                                                                                                                    | abled. No load on                                                             |      | 1.2  | 2.1  | mA   |

| I <sub>(LP-RX-ONLY)</sub>      | Supply current when only inputs are enabled                 | CQ and DO are disabled. CQ RX and DI are enabled. No load on VOUT. $R_{SETx} >= 10k\Omega \; \text{(current limit} < 500\text{mA)} \; , \; \text{EN1=EN2=L}$                                              | CQ and DO<br>are disabled. CQ<br>RX and DI are<br>enabled. No load<br>on VOUT |      | 1.4  | 2.5  | mA   |

| I <sub>(LP-CQ-DO)</sub>        | Quiescent supply current when both CQ and DO are enabled.   | $R_{SETx} >= 10k\Omega$ . TX1=TX2=H, No I Push-pull or NPN mode only                                                                                                                                      | oad on CQ or DO,                                                              |      | 4.5  | 5.5  | mA   |

| I <sub>(LP-CQ-DO)</sub>        | V5IN supplied externally                                    | $R_{SETx} >= 10k\Omega$ . TX1=TX2=L, No k                                                                                                                                                                 | oad on CQ or DO                                                               |      | 3.6  | 4.5  | mA   |

| $V_{(LP-UVLO)}$                | LP under voltage lockout                                    | LP falling; UVLO indicated by RES                                                                                                                                                                         | ET pin going low                                                              | 6    | 6.3  |      | V    |

| V <sub>(LP-UVLO)</sub>         | LP under voltage lockout                                    | Pricing: LIVI O recovery indicated on PESET pin                                                                                                                                                           |                                                                               | 6.8  | V    |      |      |

| V <sub>(LP-</sub><br>UVLO,HYS) | LP under voltage hysteresis                                 | Rising to falling threshold                                                                                                                                                                               |                                                                               | 150  | 250  |      | mV   |

| V <sub>(LPW)</sub>             | LP undervoltage warning                                     | LP falling                                                                                                                                                                                                |                                                                               | 14   | 16   | 18   | V    |

| V <sub>(LPW-HYS)</sub>         | LP undervoltage warning hysteresis                          |                                                                                                                                                                                                           |                                                                               |      | 530  |      | mV   |

| V5IN                           |                                                             |                                                                                                                                                                                                           |                                                                               |      |      |      |      |

| V5IN(UVLO,<br>F)               | Falling UVLO level for V5IN                                 | V5IN Falling                                                                                                                                                                                              |                                                                               | 3.4  | 3.5  | 3.6  | V    |

| V5IN(UVLO,<br>R)               | Rising UVLO level for V5IN                                  | V5IN Rising                                                                                                                                                                                               |                                                                               | 3.7  | 3.8  | 4.0  | V    |

| V5IN(UVLO,<br>HYS)             | V5IN UVLO hysteresis                                        |                                                                                                                                                                                                           |                                                                               |      | 0.3  |      | V    |

| 15_IN                          | Input supply current at 5VIN                                | CQ and DO disabled, No load on                                                                                                                                                                            | /OUT                                                                          |      | 0.15 | 1    | mA   |

| LINEAR REG                     | GULATOR (VOUT)                                              |                                                                                                                                                                                                           |                                                                               |      |      |      |      |

| V                              | Voltage regulator output                                    | VOUT set to 5 V                                                                                                                                                                                           |                                                                               | 4.75 | 5    | 5.25 | V    |

| V <sub>(VOUT)</sub>            | Voltage regulator output                                    | VOUT set to 3.3 V                                                                                                                                                                                         |                                                                               | 3.13 | 3.3  | 3.46 | V    |

| LINEREG <sub>VO</sub><br>UT    | Line regulation (dV <sub>(VOUT)</sub> /dV(LP))              | $ \begin{array}{l} I_{(VCC\_OUT)} = 1 \text{ mA} \\ V_{(LP)} = 7 \text{ V to } 36 \text{ V (VOUT} = 5 \text{ V)} \\ V_{(LP)} = 7 \text{ V to } 36 \text{ V OR V5IN} = 4.5 \\ 3.3 \text{ V)} \end{array} $ | to 5.5 V (VOUT =                                                              |      |      | 1.7  | mV/V |

| LOADREG <sub>V</sub>           | Load regulation (dV <sub>(VOUT)</sub> /V <sub>(OUT)</sub> ) | $V_{(LP)}$ = 24 V for VOUT=5V<br>$V_{(LP)}$ = 24 V or V5IN= 5V for VOUT<br>$I_{(VCC\_OUT)}$ = 100 $\mu$ A to 20 mA                                                                                        | Γ=3.3 V                                                                       |      |      | 1    | %    |

| UV <sub>VOUT5F</sub>           | Falling UV threshold on VOUT (5V setting)                   | VSEL connected to VOUT, VOUT                                                                                                                                                                              | falling                                                                       | 3.4  | 3.6  | 3.8  | V    |

| UV <sub>VOUT5R</sub>           | Rising UV threshold on VOUT (5V setting)                    | VSEL connected to VOUT, VOUT                                                                                                                                                                              | rising                                                                        | 3.6  | 3.8  | 4.0  | V    |

# **5.6 Electrical Characteristics (continued)**

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V  $V_{VOLT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                      | PARAMETER                                                      | TEST CONDITIO                                                                                                                             | NS                            | MIN          | TYP  | MAX                                                                         | UNIT |

|----------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------|------|-----------------------------------------------------------------------------|------|

| UV <sub>VOUT3F</sub> | Falling UV threshold on VOUT (3.3V setting)                    | VSEL connected to GND or Floatin<br>VOUT falling                                                                                          | ng(V5IN supplied),            | 2.5          | 2.7  | 2.9                                                                         | V    |

| JV <sub>VOUT3R</sub> | Rising UV threshold on VOUT (3.3V setting)                     | VSEL connected to GND or Floatin VOUT rising                                                                                              | ng(V5IN supplied),            | 2.6          | 2.8  | 3.0                                                                         | V    |

| PSSR                 | Power Supply Rejection Ratio                                   | 100 kHz, I <sub>(VCC_OUT)</sub> = 20 mA                                                                                                   |                               |              | 40   |                                                                             | dB   |

| DRIVER OU            | TPUT (CQ, DO)                                                  |                                                                                                                                           |                               |              |      |                                                                             |      |

| R <sub>DSON-HS</sub> | High-side driver on-resistance                                 | I <sub>LOAD</sub> = 200 mA, Current Limit = 300 mA                                                                                        |                               |              | 2.5  | 4.5                                                                         | Ω    |

| R <sub>DSON-LS</sub> | Low-side driver on-resistance                                  | I <sub>LOAD</sub> = 200 mA, Current Limit = 300 mA                                                                                        |                               |              | 2.5  | 4.5                                                                         | Ω    |

|                      |                                                                |                                                                                                                                           | R <sub>SETx</sub> = 110 kΩ    | 35           | 55   | 70                                                                          | mA   |

|                      |                                                                |                                                                                                                                           | R <sub>SETx</sub> = 10 kΩ     | 300          | 350  | 400                                                                         | mA   |

| I <sub>O(LIM)</sub>  | Driver output current limit                                    | $SPI/\overline{PIN} = LOW$<br>$V_{(DRIVER)} = (V_{LP} - 3) V \text{ or } 3V,$                                                             | $R_{SETx} = 0$ to $5 k\Omega$ | 500          |      |                                                                             | mA   |

|                      |                                                                |                                                                                                                                           | R <sub>SETx</sub> = OPEN      | 260          | 330  | 3 4.5 4.5 5 4.5 5 70 400 415 75 6 95 75 75 75 75 75 75 75 75 75 75 75 75 75 | mA   |

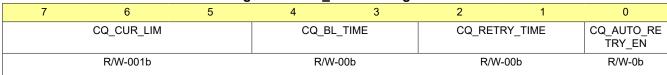

|                      |                                                                |                                                                                                                                           | 3h[7:6]= 0h                   | 35           | 60   | 75                                                                          | mA   |

|                      |                                                                |                                                                                                                                           | 3h[7:6]= 1h                   | 50           | 75   | 95                                                                          | mA   |

|                      |                                                                |                                                                                                                                           | 3h[7:6]= 2h                   | 100          | 140  | 175                                                                         | mA   |

|                      | Driver output ourt liit                                        | SPI/PIN = HIGH,                                                                                                                           | 3h[7:6]= 3h                   | 150          | 190  | 260                                                                         | mA   |

| O(LIM)               | Driver output current limit                                    | $V_{(DRIVER)} = (V_{LP} - 3) V \text{ or } 3V,$                                                                                           | 3h[7:6]= 4h                   | 200          | 230  | 330                                                                         | mA   |

|                      |                                                                |                                                                                                                                           | 3h[7:6] = 5h                  | 250          | 290  | 485                                                                         | mA   |

|                      |                                                                |                                                                                                                                           | 3h[7:6] = 6h                  | 300          | 350  |                                                                             | mA   |

|                      |                                                                |                                                                                                                                           | 3h[7:6]= 7h                   | 500          | 700  |                                                                             | mA   |

| OZ(CQ)               | CQ leakage                                                     | EN1 = LOW, 0 ≤ V <sub>(CQ)</sub> ≤ (V <sub>(LP)</sub> - 0.                                                                                | 1 V)                          | -2           |      | 2                                                                           | μA   |

| LLM(CQ)              | CQ load discharge current                                      | EN1 = LOW, $R_{SET1}$ = 0 to 5 kΩ <sup>(1)</sup> ,                                                                                        | V <sub>(CQ)</sub> >= 5 V      | 5            | 8.5  | 15                                                                          | mA   |

| LLM(DO)              | DO load discharge current                                      | EN2 = LOW, $R_{SET2}$ = 0 to 5 k $\Omega$ ; $V_0$                                                                                         | <sub>(DO)</sub> >= 5 V        | 5            | 8.5  | 15                                                                          | mA   |

| PU-DO                | DO driver weak pull-up current                                 | SPI/ $\overline{PIN}$ =HIGH,<br>EN2=LOW, TX2=HIGH, RSET2:<br>10 k $\Omega$ to 110 k $\Omega$ AND Weak pull-<br>up enabled (SPI mode only) | 0 ≤ V(DO) ≤<br>(V(LP) - 2 V)  | 40           | 50   | 80                                                                          | μA   |

| PD-DO                | DO driver weak pull-down current                               | (SPI/PIN=HIGH, EN2=LOW,<br>TX2=LOW, RSET2: 10 kΩ to<br>110 kΩ<br>AND Weak pull-up enabled (SPI<br>mode only)                              | 2 ≤ V(DO) ≤ V(LP)             | 40           | 50   | 80                                                                          | μΑ   |

| I <sub>PU-CQ</sub>   | CQ driver weak pull-up current                                 | Driver disabled, Weak pull-up enabled (SPI mode)                                                                                          | 0 ≤ V(CQ) ≤<br>(V(LP) - 2 V)  | 40           | 50   | 80                                                                          | μΑ   |

| PD-CQ                | CQ driver weak pull-down current                               | Driver disabled, Weak pull-down enabled (SPI mode)                                                                                        | 2 ≤ V(CQ) ≤ V(LP)             | 40           | 50   | 80                                                                          | μΑ   |

| RECEIVER             | INPUT (CQ, DI)                                                 |                                                                                                                                           |                               |              |      |                                                                             |      |

| V <sub>(THH)</sub>   | Input threshold "H"                                            |                                                                                                                                           |                               | 10.5         |      | 13                                                                          | V    |

| V <sub>(THL)</sub>   | Input threshold "L"                                            | V <sub>(LP)</sub> > 18 V, EN= LOW                                                                                                         |                               | 8            |      | 11.5                                                                        | V    |

| V <sub>(HYS)</sub>   | Receiver Hysteresis (V <sub>(THH)</sub> - V <sub>(THL)</sub> ) | (=-)                                                                                                                                      |                               |              | 0.75 |                                                                             | V    |

| V <sub>(THH)</sub>   | Input threshold "H"                                            | V <sub>(LP)</sub> < 18 V, EN= LOW                                                                                                         |                               | See Note (2) |      | See Note (3)                                                                | V    |

| V <sub>(THL)</sub>   | Input threshold "L"                                            |                                                                                                                                           |                               | See Note (4) |      | See Note (5)                                                                | V    |

| V <sub>(HYS)</sub>   | Receiver Hysteresis (V <sub>(THH)</sub> - V <sub>(THL)</sub> ) | V <sub>(LP)</sub> < 18 V, EN= LOW                                                                                                         |                               |              | 0.75 |                                                                             | V    |

| C <sub>IN-CQ</sub>   | CQ input capacitance                                           | CQ driver disabled, weak pull-up/<br>pull-down disabled, f =100kHz                                                                        |                               |              | 150  |                                                                             | pF   |

| C <sub>IN-DI</sub>   | DI input capacitance                                           | f=100kHz                                                                                                                                  |                               |              | 100  |                                                                             | pF   |

## **5.6 Electrical Characteristics (continued)**

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V,  $V_{VOUT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                               | PARAMETER                                                | TEST CONDITIO                                                                                                        | NS                                             | MIN      | TYP | MAX      | UNIT |

|-------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------|-----|----------|------|

| I <sub>PU-DI</sub>            | DI weak pull-up current                                  | SPI Mode, Weak pull-up enabled on DI pin                                                                             | 0 ≤ V(DI) ≤ (V(LP)<br>- 2 V)                   | 40       | 50  | 80       | μA   |

| I <sub>PD-DI</sub>            | DI weak pull-down current                                | SPI Mode, Weak pull-down enabled on DI pin                                                                           | 2 ≤ V(DI) ≤ V(LP)                              | 40       | 50  | 80       | μΑ   |

| LOGIC-LE                      | EVEL INPUTS (CS/PP, SCK, SDI/NPN                         | SPI/PIN, EN1, EN2, TX1, TX2, VS                                                                                      | EL)                                            |          |     |          |      |

| V <sub>IL</sub>               | Input logic low voltage                                  |                                                                                                                      |                                                |          |     | 0.3*VOUT | V    |

| V <sub>IH</sub>               | Input logic high voltage                                 |                                                                                                                      |                                                | 0.7*VOUT |     |          | V    |

| R <sub>PD</sub>               | Pull-down resistance at EN1,<br>EN2, SDI/NPN, SCK        |                                                                                                                      |                                                |          | 100 |          | kΩ   |

| R <sub>PU</sub>               | Pull-up resistance at TX1, TX2, , CS/PP, SPI/PIN         |                                                                                                                      |                                                |          | 100 |          | kΩ   |

| R <sub>PU</sub>               | Pull-up resistance at VSEL                               |                                                                                                                      |                                                |          | 500 |          | kΩ   |

| LOGIC-LE                      | EVEL OUTPUTS (WU, SDO/NFLT2, IN                          | T/NFLT1, RX1, RX2, RESET)                                                                                            |                                                |          |     | •        |      |

| V <sub>OH</sub>               | Output logic high voltage RX1, RX2, SDO, INT             | I <sub>O</sub> = 4 mA                                                                                                | I <sub>O</sub> = 4 mA                          | VOUT-0.5 |     |          | V    |

| V <sub>OL</sub>               | Output logic low voltage                                 | I <sub>O</sub> = 4 mA                                                                                                |                                                |          |     | 0.4      | V    |

| l <sub>OZ</sub>               | Output high impedance leakage at NFLT1, NFLT2, WU, RESET | Output in Hi-Z, V <sub>O</sub> = 0 V or VCC_I                                                                        | N/OUT                                          | -1       |     | 1        | μА   |

| PROTECT                       | TION CIRCUITS                                            |                                                                                                                      | -                                              |          |     |          |      |

| T <sub>(WRN)</sub>            | Thermal warning                                          |                                                                                                                      |                                                | 125      |     |          | °C   |

| T <sub>(SDN)</sub>            | Thermal shutdown                                         | Die temperature T <sub>J</sub>                                                                                       |                                                | 150      | 160 |          | °C   |

| T <sub>(HYS)</sub>            | Thermal hysteresis for shutdown                          |                                                                                                                      |                                                |          | 14  |          | °C   |

| T <sub>(WRN)</sub>            | Thermal hysteresis for warning                           | Die temperature T <sub>J</sub>                                                                                       | Die temperature T <sub>J</sub>                 |          | 14  |          | °C   |

|                               | CQ, DO, DI Leakage current                               | EN1/2=LOW, TX1/2=x; LP= 24 V<br>-36V) OR V <sub>(CQ/DO/DI)</sub> = (V <sub>(LP)</sub> +3                             | V <sub>(CQ/ DO/ DI)</sub> = (V <sub>(LP)</sub> |          |     | 60       | μA   |

| PROTECTION T <sub>(WRN)</sub> | in reverse polarity (Drivers disabled)                   | EN1/2=LOW, TX1/2=x; LP= 24 V V <sub>(CQ/ DO/DI )</sub> = (V <sub>(LP)</sub> -65V) OR V <sub>(CQ/ DO/ DI)</sub> = 65V |                                                |          |     | 110      | μΑ   |

|                               | CQ, DO (Drivers enabled)                                 | EN1/2 = HIGH, TX1/2 = LOW; $V_{(C)}$<br>R <sub>SET</sub> >= 10 k $\Omega$                                            | <sub>Q/DO to LP)</sub> = 3 V,                  |          |     | 650      | μΑ   |

|                               |                                                          | EN1/2 = HIGH, TX1/2 = HIGH; V <sub>(C</sub>                                                                          | CQ/DO to LM) = -3 V                            |          |     | 10       | μA   |

- Current fault indication and current fault auto recovery will be de-activated.

- (2)  $V_{THH}$  (min) = 5 V + (11/18) [ $V_{(LP)}$  8 V] (3)  $V_{THH}$  (max) = 6.5 V + (13/18) [ $V_{(LP)}$  8 V] (4)  $V_{THL}$  (min) = 4 V + (8/18) [ $V_{(LP)}$  8 V] (5)  $V_{THL}$  (max) = 6 V + (11/18) [ $V_{(LP)}$  8 V]

# **5.7 Switching Characteristics**

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V,  $V_{VOUT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                      | PARAMETER                                                           | = 3.3 V and T <sub>A</sub> = 25 °C unles                                                                                                                                                                                                                                                                         | TEST<br>CONDITI<br>ONS | TEST CONDITIONS | MIN | ТҮР | MAX  | UNIT |

|----------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----|-----|------|------|

| CQ, DO               | DRIVER                                                              |                                                                                                                                                                                                                                                                                                                  |                        |                 |     |     | -    |      |

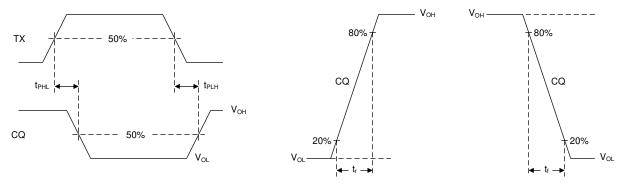

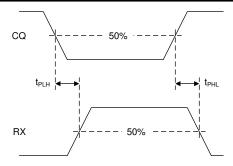

| t <sub>PLH</sub>     | Driver propagation delay,<br>low-to-high transition                 | See Test Circuit for Driver Output Nand Driver Output Switching Wave $R_L = 2 \ k\Omega$ $C_L = 5 \ nF$ Push-pull and PNP configuration $R_{SET} = 10 \ k\Omega$                                                                                                                                                 |                        | ts              |     | 600 | 1200 | ns   |

| t <sub>PHL</sub>     | Driver propagation delay,<br>high-to-low transition                 | See Test Circuit for Driver Output Nand Driver Output Switching Wave $R_L = 2 \ k\Omega$ $C_L = 5 \ nF$ Push-pull and NPN configuration $R_{SET} = 10 \ k\Omega$                                                                                                                                                 |                        | ts              |     | 600 | 1200 | ns   |

| t <sub>P(skew)</sub> | Driver propagation delay skew.  t <sub>PLH</sub> - t <sub>PHL</sub> | See Test Circuit for Driver Output Notes Driver Output Switching Wave $R_L=2~k\Omega$ $C_L=5~nF$ Push-pull configuration $R_{SET}=10~k\Omega$                                                                                                                                                                    |                        | ts              |     | 120 |      | ns   |

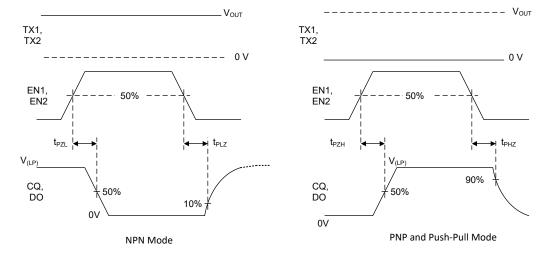

| t <sub>PZH</sub>     | Driver enable delay high                                            | See Test Circuit for Driver Output Mand Driver Enable/Disable Timing Diag R <sub>L</sub> = 2 kΩ C <sub>L</sub> = 5 nF Push-pull and PNP configuration o                                                                                                                                                          | grams                  | ts              |     |     | 4    | μs   |

| t <sub>PZL</sub>     | Driver enable delay low                                             | $\begin{aligned} R_{SET} &= 10 \text{ k}\Omega \\ \text{See Test Circuit for Driver Output N} \\ \text{and} \\ \text{Driver Enable/Disable Timing Diag} \\ R_L &= 2 \text{ k}\Omega \\ \text{C}_L &= 5 \text{ nF} \\ \text{Push-pull and NPN configuration or R} \\ R_{SET} &= 10 \text{ k}\Omega \end{aligned}$ | grams                  | ts              |     |     | 4    | μs   |

| t <sub>PHZ</sub>     | Driver disable delay high                                           | See Test Circuit for Driver Output N and Driver Enable/Disable Timing Diag $R_L=2~k\Omega$ $C_L=5~nF$ Push-pull and PNP configuration o $R_{SET}=10~k\Omega$                                                                                                                                                     | grams                  | ts              |     |     | 4    | μs   |

| t <sub>PLZ</sub>     | Driver disable delay low                                            | See Test Circuit for Driver Output Mand Driver Enable/Disable Timing Diag $R_L=2~k\Omega$ $C_L=5~nF$ Push-pull and NPN configuration of $R_{SET}=10~k\Omega$                                                                                                                                                     | grams                  | ts              |     |     | 4    | μs   |

| t <sub>r</sub>       | Driver output rise time                                             | See Test Circuit for Driver Output I and Driver Output Switching Wave $R_L = 2 \ k\Omega$ $C_L = 5 \ nF$ Push-pull and PNP configuration $R_{SET} = 10 \ k\Omega$                                                                                                                                                |                        | ts              | 200 | 530 | 900  | ns   |

| t <sub>f</sub>       | Driver output fall time                                             | See Test Circuit for Driver Output I and Driver Output Switching Wave $R_L = 2 \ k\Omega$ $C_L = 5 \ nF$ Push-pull and NPN configuration $R_{SET} = 10 \ k\Omega$                                                                                                                                                |                        | ts              | 200 | 480 | 900  | ns   |

# **5.7 Switching Characteristics (continued)**

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V,  $V_{VOUT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                                             | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                  | TEST<br>CONDITI<br>ONS                            | TEST CONDITIONS                                   | MIN   | TYP  | MAX  | UNIT |

|---------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------|-------|------|------|------|

| $ t_r-t_f $                                 | Difference in rise and fall time             | See Test Circuit for Driver Output N and Driver Output Switching Wave $R_L = 2 \text{ k}\Omega$ $C_L = 5 \text{ n}F$ Push-pull configuration only $R_{SET} = 10 \text{ k}\Omega$ |                                                   | ts                                                |       | 60   |      | ns   |

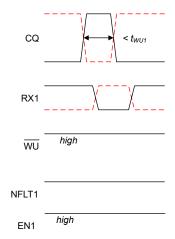

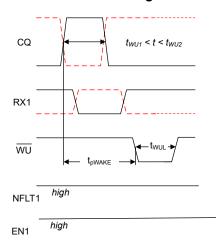

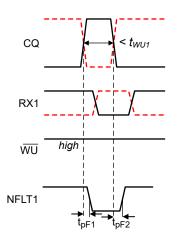

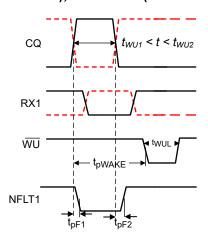

| WU1                                         | Wake-up recognition begin                    |                                                                                                                                                                                  |                                                   |                                                   | 45    | 60   | 75   | μs   |

| WU2                                         | Wake-up recognition end                      |                                                                                                                                                                                  |                                                   |                                                   | 85    | 100  | 145  | μs   |

| pWAKE                                       | Wake-up output delay                         | See Wake-up recognition timing dia                                                                                                                                               | agram                                             |                                                   |       |      | 150  | μs   |

| WUL                                         | Wake output pulse duration on wake detection |                                                                                                                                                                                  |                                                   |                                                   | 175   | 225  | 285  | μs   |

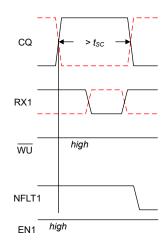

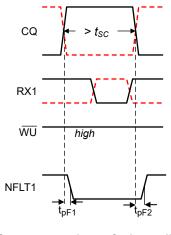

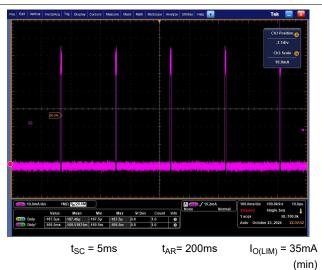

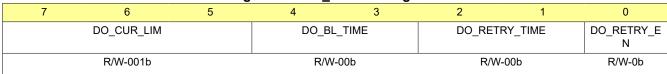

|                                             |                                              |                                                                                                                                                                                  | RSETx <= SPI/PIN=hi CQ_BL_TII DO_BL_TII           | ME[1:0]=00b (CQ) OR<br>ME[1:0]=00b (DO)           | 0.175 | 0.2  |      | ms   |

| t <sub>SC</sub> Current fault blanking time | See Wake-up recognition timing               |                                                                                                                                                                                  | gh and<br>ME[1:0]=01b (CQ) OR<br>ME[1:0]=01b (DO) | 0.25                                              | 0.5   |      | ms   |      |

|                                             | Current lault blanking time                  | diagram                                                                                                                                                                          |                                                   | gh and<br>ME[1:0]=10b (CQ) OR<br>ME[1:0]=10b (DO) |       | 5    |      | ms   |

|                                             |                                              | floating) OF<br>SPI/PIN=hi<br>CQ_BL_TII                                                                                                                                          |                                                   | 0.5                                               | 2     | 4    | μs   |      |

|                                             |                                              |                                                                                                                                                                                  |                                                   | OR SPI/ <del>PIN</del> =H and<br>/_TIME=00b       |       | 50   |      | ms   |

| AR                                          | Auto retry time after current                | Auto retry time after current fault                                                                                                                                              | SPI/PIN=H<br>CQ_RETR                              | and<br>/_TIME=01b                                 |       | 100  |      | ms   |

| AK                                          | fault                                        | Autoreary anne aner carrent laut                                                                                                                                                 | SPI/PIN=H<br>CQ_RETR                              | and<br>/_TIME=10b                                 |       | 200  |      | ms   |

|                                             |                                              |                                                                                                                                                                                  | SPI/PIN=H<br>CQ_RETR                              | and<br>/_TIME=11b                                 |       | 500  |      | ms   |

| (UVLO)                                      | CQ and DO re-enable delay after LP UVLO (1)  | CQ and DO re-enable delay after UVLO (1)                                                                                                                                         | T_UVLO=1                                          |                                                   | 0.05  | 0.25 | 0.5  | ms   |

| (UVLO)                                      | CQ and DO re-enable delay after LP UVLO (1)  | CQ and DO re-enable delay after UVLO (1)                                                                                                                                         | SPI/PIN = I<br>T_UVLO=1                           | OR SPI/PIN=H and<br>b1                            | 10    | 30   | 50   | ms   |

| CQ, DI RI                                   | ECEIVER                                      | I                                                                                                                                                                                | T                                                 |                                                   |       |      | Т    |      |

| PLH_CQ,                                     | CQ Receiver propagation                      |                                                                                                                                                                                  | CQ_RX_FI                                          |                                                   |       | 0.2  | 0.36 | μs   |

| PHL_CQ                                      | <sub>CQ</sub> delay                          | See Receiver Test Circuit - Diagram and Receiver Timing                                                                                                                          | SPI/PIN=H<br>CQ_RX_FI                             | LTER=1b1                                          |       | 1.15 | 1.6  | μs   |

| PLH_DI,                                     | DI Receiver propagation                      | Diagram C <sub>L</sub> =15 pF                                                                                                                                                    | DI_RX_FIL                                         |                                                   |       | 1    | 1.5  | μs   |

| PHL_DI                                      |                                              | delay                                                                                                                                                                            |                                                   | and<br>TER=1b1                                    |       | 1.8  | 2.7  | μs   |

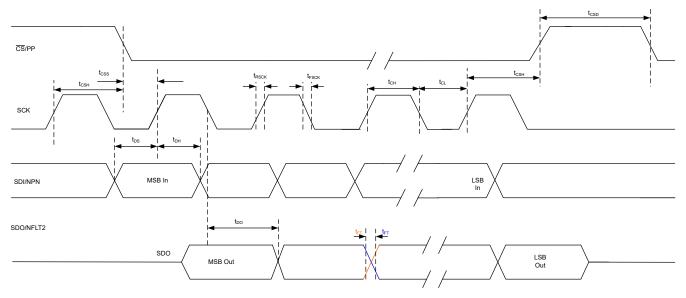

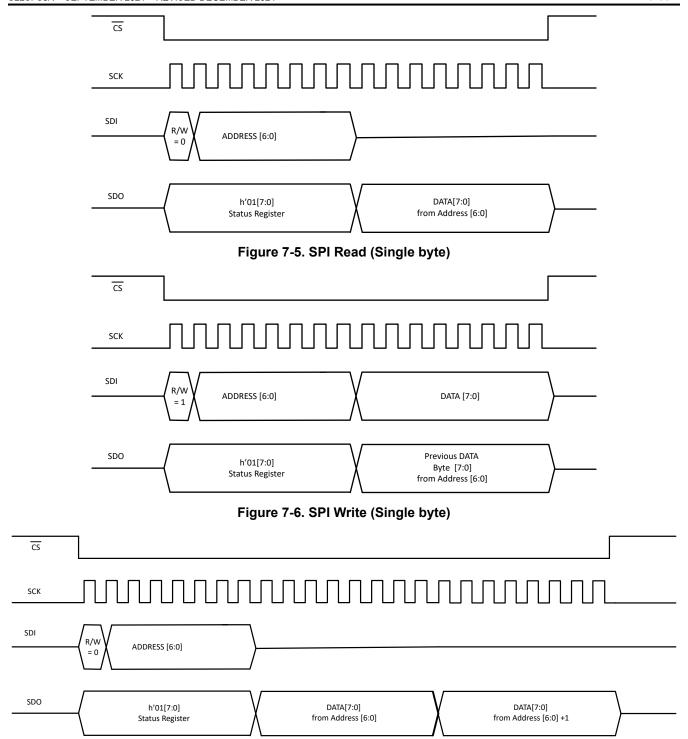

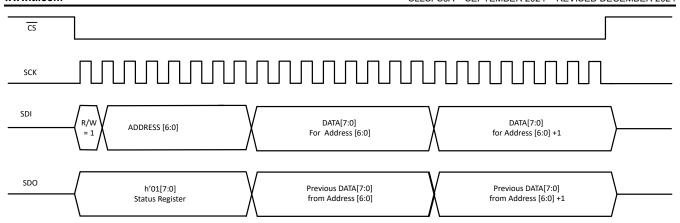

| 3PI Timir                                   | ng (CS, SCK, SDI, SDO/CUR_C                  | OK2)                                                                                                                                                                             |                                                   |                                                   |       |      |      |      |

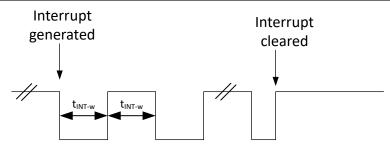

| INT_TOG                                     | INT pin High/low time (when toggling)        | C <sub>OUT</sub> = 10 pF                                                                                                                                                         |                                                   |                                                   |       | 100  |      | μs   |

$\label{eq:copyright} \mbox{Copyright @ 2024 Texas Instruments Incorporated} \\ \mbox{Product Folder Links: } \emph{T/OL221}$

# **5.7 Switching Characteristics (continued)**

Over recommended operating conditions and recommended free-air temperature range (unless otherwise noted). Typical values are at LP = 24 V,  $V_{VOUT}$  = 3.3 V and  $T_A$  = 25 °C unless otherwise specified.

|                       | PARAMETER                                                   | TEST CONDITIONS          | TEST<br>CONDITI<br>ONS | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------|--------------------------|------------------------|-----------------|-----|-----|------|------|

| f <sub>SCK_BURS</sub> | Maximum SPI clock frequency                                 |                          |                        |                 |     |     | 10   | MHz  |

| tSCK                  | SCK period                                                  | Burst mode               |                        |                 | 100 |     |      | ns   |

| t <sub>SCKH</sub>     | SCK pulse-width high                                        |                          |                        |                 | 50  |     |      | ns   |

| t <sub>SCKL</sub>     | SCK pulse-width low                                         |                          |                        |                 | 50  |     |      | ns   |

| f <sub>SCK</sub>      | Maximum SPI clock frequency                                 |                          |                        |                 |     |     | 12.5 | MHz  |

| tSCK                  | SCK period                                                  | Non-burst mode           | Non-burst mode         |                 |     |     |      | ns   |

| t <sub>SCKH</sub>     | SCK pulse-width high                                        |                          |                        |                 |     |     |      | ns   |

| t <sub>SCKL</sub>     | SCK pulse-width low                                         |                          |                        |                 | 40  | -   |      | ns   |

| t <sub>CSS</sub>      | CS falling edge to SCK rise time                            |                          |                        |                 | 20  |     |      | ns   |

| t <sub>CSH</sub>      | SCK rise to CS rise hold time                               |                          |                        |                 | 40  |     |      | ns   |

| t <sub>DH</sub>       | SDI hold time                                               |                          |                        |                 | 10  | -   |      | ns   |

| t <sub>DS</sub>       | SDI setup time                                              |                          |                        |                 |     | -   | 25   | ns   |

| t <sub>DO</sub>       | SDO data propagation delay                                  | C <sub>OUT</sub> = 10 pF |                        |                 |     |     | 20   | ns   |

| t <sub>DORF</sub>     | SDO rise and fall time                                      | C <sub>OUT</sub> = 10 pF |                        |                 |     |     | 20   | ns   |

| t <sub>CSPW</sub>     | Minimum CS pulse width (idle time between SPI transactions) |                          |                        |                 | 10  |     |      | ns   |

<sup>(1)</sup> CQ/DO output remains Hi-Z for this time

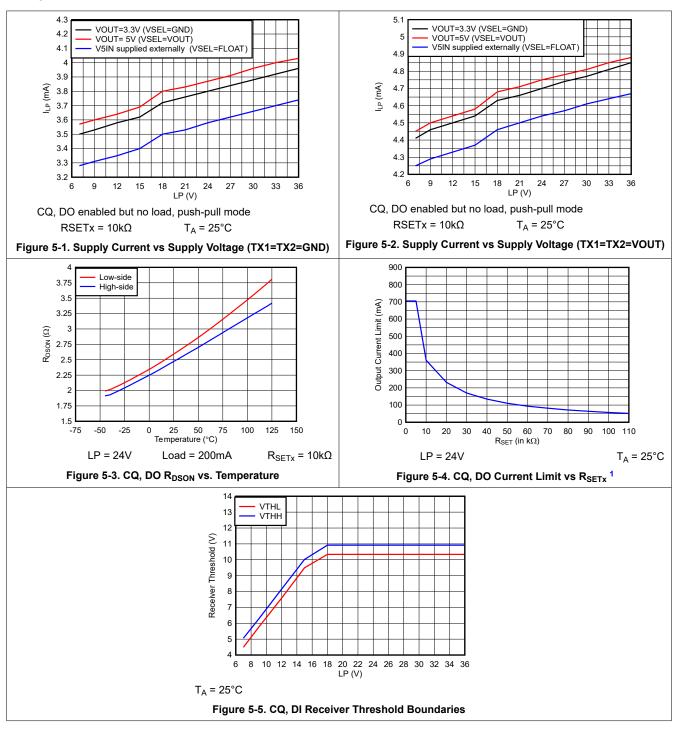

# 5.8 Typical Characteristics

For R<sub>SET</sub> in the 0-5kΩ range, TIOL221 can source/sink 500mA required for wake-up pulse generation in IO-link applications. For R<sub>SET</sub> in the 0-5kΩ range, TIOL221 also activates a pull-down current source (I<sub>LLM</sub>) when the driver is disabled.

## **6 Parameter Measurement Information**

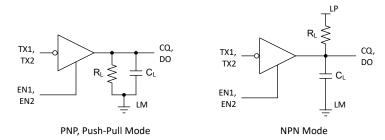

Figure 6-1. Test Circuit for Driver Switching

Figure 6-2. Waveforms for Driver Output Switching Measurements

Figure 6-3. Waveforms for Driver Enable or Disable Time Measurements

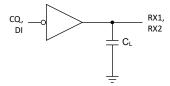

Figure 6-4. Test Circuit for Receiver Switching

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

Figure 6-5. Receiver Switching Measurements

- a) Over-current due to transient

- b) Valid Wake-up pulse

- c) Over-current due to fault condition

Figure 6-6. Overcurrent and Wake Conditions for EN = H and ILIM\_ADJ =  $10k\Omega$  to  $110k\Omega$ , TX = H (Full Lines); and TX = L (Red Dotted Lines)

- a) Over-current due to transient

- b) Valid Wake-up pulse

- c) Over-current due to fault condition

Figure 6-7. Overcurrent and Wake Conditions for EN = H and ILIM\_ADJ is floating, TX = H (Full Lines); and TX = L (Red Dotted Lines)

Submit Document Feedback

Figure 6-8. SPI Read/Write Timing Characteristics

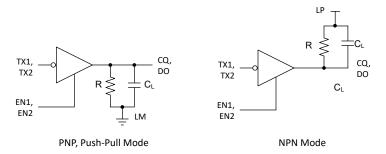

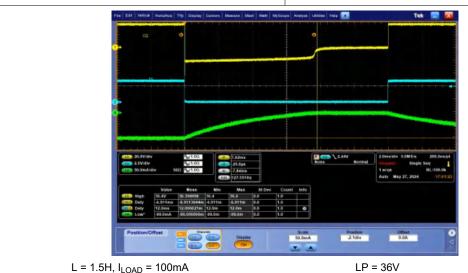

Figure 6-9. Driving the Inductive Load

Figure 6-10. Driving the Capacitive Load

Figure 6-11. Interrupt Pin Toggling Behavior (SPI Mode; INT\_TOG = 1b)

# 7 Detailed Description

### 7.1 Overview

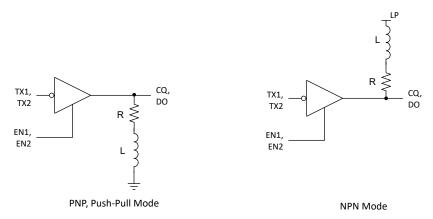

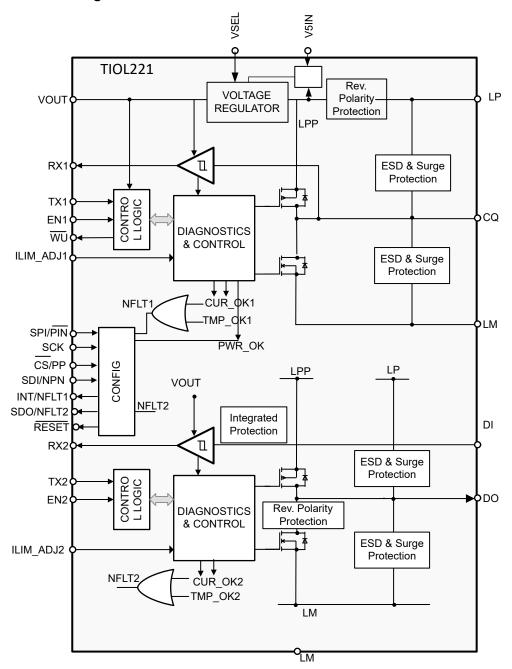

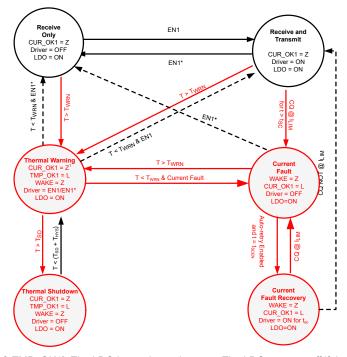

Figure 7-1 shows the functional block diagram of TIOL221. The device has an IO-link compatible channel (CQ), a digital output driver (DO) and a digital input (DI) interface. The drivers at CQ and DO can be used in either push-pull, high-side driver (PNP), or low-side driver (NPN) configuration using the  $\overline{CS}$ /PP and SDI/NPN pins in the pin-mode or via the serial peripheral interface (SPI). The internal receiver on the CQ line converts the 24V signal to standard logic levels on the receiver data output pin, RX1. Similarly, internal receiver on the DI line converts the 24V signal to standard logic levels on the receiver data output pin, RX2. A simple parallel interface is used to receive/transmit data and status information between the device and the local controller.

The device can be configured by using the pins via pin mode (when SPI/PIN is tied low) or using the SPI interface (when SPI/PIN is tied high). By using the SPI interface, the micro controller can read additional diagnostics and status information as well as configure the device.

The device has integrated IEC 61000-4-4/5 EFT and surge protection. In addition, tolerance to  $\pm 70V$  transients enables flexibility to choose from a wider range of TVS diodes if an application requires higher levels of protection. These integrated robustness features simplify the system level design by reducing external protection circuitry.

TIOL221 transceiver implements protection features for overcurrent, overvoltage and over-temperature conditions. The devices also provide a current-limit setting of the driver output current using an external resistor.

The devices derive the low-voltage supply from the IO-Link LP voltage (24V nominal) via an internal linear regulator to provide power to the local controller and sensor circuitry.

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

### 7.2 Functional Block Diagrams

Figure 7-1. Block Diagram

### 7.3 Feature Description

# 7.3.1 Wake-Up Detection

The CQ channel of TIOL221 may be operated in IO-Link mode or Standard Input / Output (SIO) mode. If the CQ channel is in SIO mode, and the IO-link controller node wants to initiate communication with the device node, the controller drives the CQ line to the opposite of the present state. The device either sinks or sources the current (≥ 500mA) for the wake-up duration (typically 80µs) depending on the CQ logic level as per the IO-Link specification. The TIOL221 detects a wake-up condition and communicates to the local microcontroller

Submit Document Feedback

by asserting the  $\overline{WU}$  pin low for the duration of  $t_{WUL}$ . The IO-Link communication specification requires the device node to switch to receive mode within 500 $\mu$ s after receiving the wake-up signal.

Table 7-1. Wake-Up Function ( $t_{WU1} < t < t_{WU2}$ )

| 1 (1101 1102) |          |                                |                                  |                                                                                                                  |  |  |  |

|---------------|----------|--------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

| EN1           | TX1      | CQ CURRENT                     | WAKE                             | COMMENT                                                                                                          |  |  |  |

| L / Open      | Х        | X                              | Asserts low for t <sub>WUL</sub> | Device asserts low for $t_{WUL}$ if RX output changes high-to-low or low-to-high for $t_{WU1}$ < $t$ < $t_{WU2}$ |  |  |  |

| Н             | H / Open | $ I_{(CQ)}  \ge I_{O(LIM)} mA$ | Asserts low for t <sub>WUL</sub> | Device receives high-level wake-up request over the IO-Link bus                                                  |  |  |  |

| Н             | L        | $ I_{(CQ)}  \ge I_{O(LIM)} mA$ | Asserts low for t <sub>WUL</sub> | Device receives low-level wake-up request over the IO-<br>Link bus                                               |  |  |  |

For overcurrent conditions shorter or longer than a valid wake-up pulse, the WAKE pin remains in a high-impedance (inactive) state. This is illustrated in Figure 6-6.

In the SPI-mode, in addition to the WU asserted low, WU\_INT bit is set. Wake-up signaling can be disabled in the SPI-mode by setting the WU\_DIS bit to 1b in the DEVICE\_CONFIG register. Wake-up detection cannot be disabled in the pin-mode.

The DO channel of TIOL221 does not recognize wake-up pulses. The DO pin does provide overcurrent limiting and detection.

### 7.3.2 Current Limit Configuration

The output current of CQ and DO pins can be configured independently in the pin-mode as well as SPI-mode.

#### 7.3.2.1 Current Limit Configuration in Pin-Mode