**THS4509**

SLOS454I - JANUARY 2005-REVISED JULY 2016

# THS4509 Wideband, Low-Noise, Low-Distortion, Fully-Differential Amplifier

#### **Features**

- Fully-Differential Architecture

- Centered Input Common-Mode Range

- Output Common-Mode Control

- Minimum Gain of 2 V/V (6 dB)

- Bandwidth: 1900 MHz Slew Rate: 6600 V/µs

- 1% Settling Time: 2 ns

- HD<sub>2</sub>: -75 dBc at 100 MHz

- HD<sub>3</sub>: -80 dBc at 100 MHz

- OIP<sub>3</sub>: 37 dBm at 70 MHz

- Input Voltage Noise: 1.9 nV/ $\sqrt{Hz}$  (f > 10 MHz)

- Power-Supply Voltage: 3 V to 5 V Power-Supply Current: 37.7 mA Power-Down Current: 0.65 mA

# **Applications**

- 5-V Data Acquisition Systems High Linearity ADC Amplifiers

- Wireless Communication

- Medical Imaging

- **Test and Measurement**

### 3 Description

The THS4509 device is a wideband, fully-differential op amp designed for 5-V data acquisition systems. It has a low noise at 1.9 nV/\(\sqrt{Hz}\), and low harmonic distortion of -75 dBc HD2 and -80 dBc HD3 at 100 MHz with 2  $V_{PP}$ , G = 10 dB, and 1-k $\Omega$  load. Slew rate is high at 6600 V/ $\mu$ s, and with settling time of 2 ns to 1% (2-V step), it is ideal for pulsed applications. It is designed for a minimum gain of 6 dB, but is optimized for gains of 10 dB.

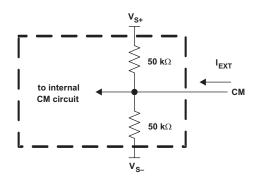

To allow for DC coupling to analog-to-digital converters (ADCs), its unique output common-mode control circuit maintains the output common-mode voltage within 3-mV offset (typical) from the set voltage, when set within 0.5-V of midsupply, with less than 4-mV differential offset voltage. The commonmode set point is set to midsupply by internal circuitry, which may be overdriven from an external source.

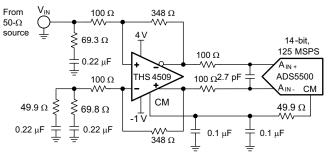

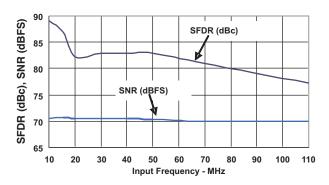

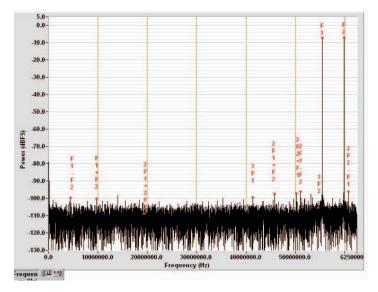

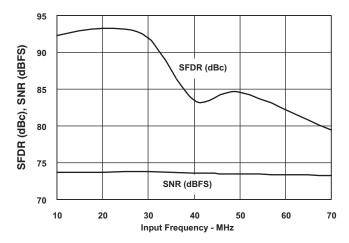

The input and output are optimized for best performance with the common-mode voltages set to midsupply. Along with high performance at low power-supply voltage, this design makes it ideal for high-performance, single-supply 5-V data acquisition systems. The combined performance of the THS4509 in a gain of 10 dB driving the ADS5500 ADC, sampling at 125 MSPS, is 81-dBc SFDR and 69.1-dBc SNR with a -1 dBFS signal at 70 MHz.

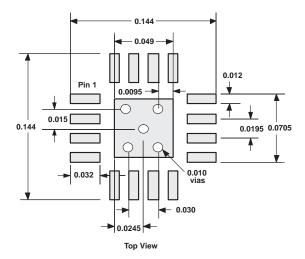

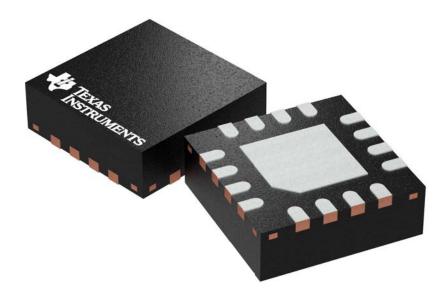

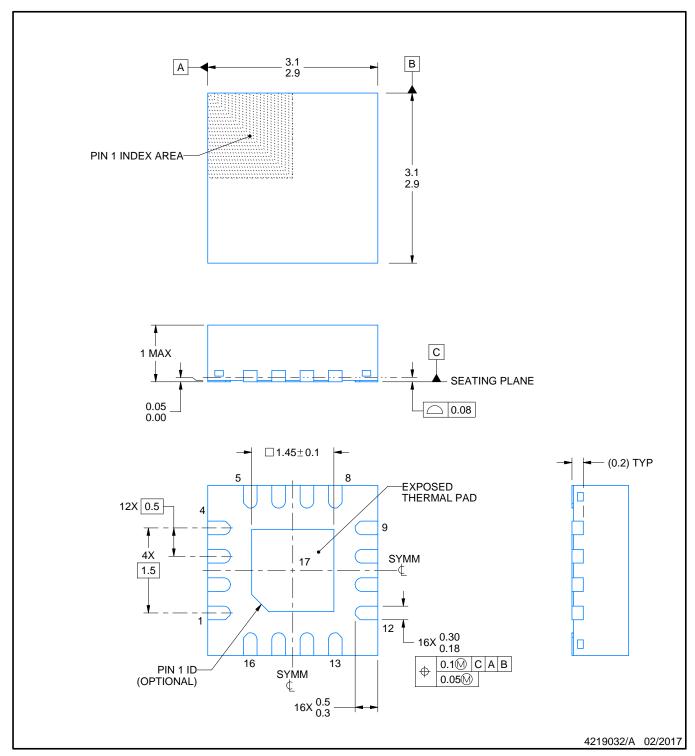

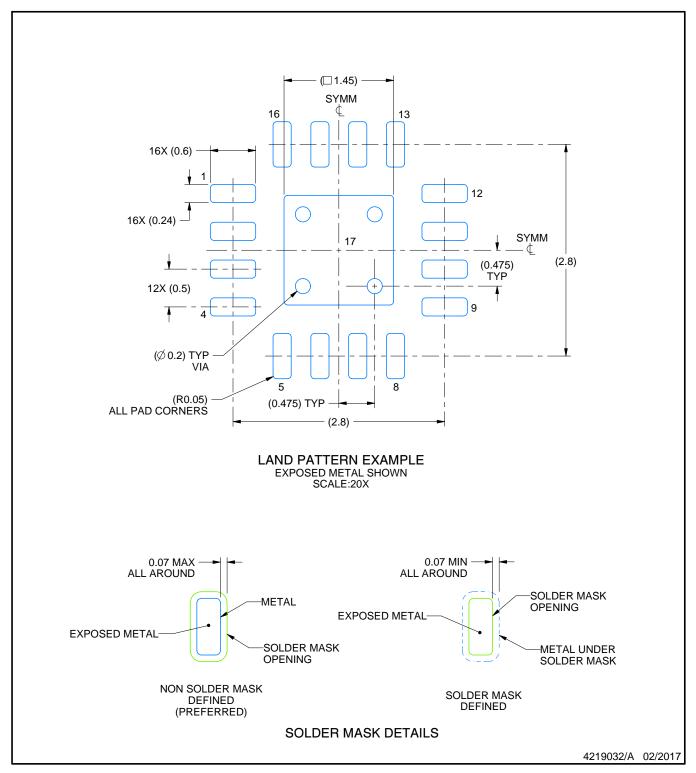

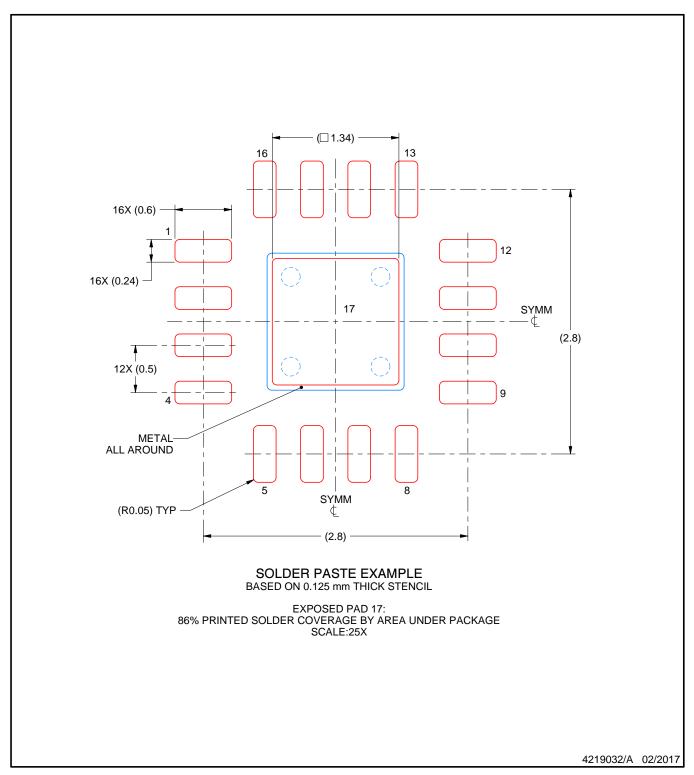

The THS4509 is offered in a quad, leadless VQFN-16 package (RGT), and is characterized for operation over the full industrial temperature range from -40°C to +85°C.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| THS4509     | VQFN (16) | 3.00 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

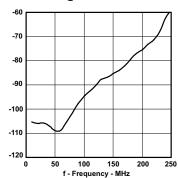

#### **Measured 3rd Order Intermodulation Spurious** Signal Level

### **Test Configuration**

# **Table of Contents**

| 1 | Features 1                                                              |    | 8.4 Device Functional Modes                          | . 28 |

|---|-------------------------------------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                                          | 9  | Application and Implementation                       | 29   |

| 3 | Description 1                                                           |    | 9.1 Application Information                          |      |

| 4 | Revision History2                                                       |    | 9.2 Typical Applications                             | . 29 |

| 5 | Device Comparison Table 4                                               | 10 | Power Supply Recommendations                         | 35   |

| 6 | Pin Configuration and Functions 4                                       | 11 | Layout                                               | 36   |

| 7 | Specifications5                                                         |    | 11.1 Layout Guidelines                               | . 36 |

| • | 7.1 Absolute Maximum Ratings 5                                          |    | 11.2 Layout Example                                  | . 37 |

|   | 7.2 ESD Ratings                                                         |    | 11.3 PowerPAD™ Design Considerations                 | . 38 |

|   | 7.3 Recommended Operating Conditions                                    | 12 | Device and Documentation Support                     | 40   |

|   | 7.4 Thermal Information                                                 |    | 12.1 Device Support                                  | . 40 |

|   | 7.5 Electrical Characteristics: V <sub>S+</sub> – V <sub>S</sub> = 5 V  |    | 12.2 Documentation Support                           | . 40 |

|   | 7.6 Electrical Characteristics: V <sub>S+</sub> – V <sub>S-</sub> = 3 V |    | 12.3 Receiving Notification of Documentation Updates | 40   |

|   | 7.7 Dissipation Ratings                                                 |    | 12.4 Community Resources                             | . 40 |

|   | 7.8 Typical Characteristics                                             |    | 12.5 Trademarks                                      | . 40 |

| 8 | Detailed Description                                                    |    | 12.6 Electrostatic Discharge Caution                 | . 40 |

| U | 8.1 Overview                                                            |    | 12.7 Glossary                                        | . 40 |

|   | 8.2 Functional Block Diagram                                            | 13 | Mechanical, Packaging, and Orderable                 |      |

|   | 8.3 Feature Description                                                 |    | Information                                          | 40   |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | Changes from Revision H (November 2009) to Revision I                                                                                                                                                                                                                                                          | Page |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added ESD Ratings table, Thermal Information table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| • | Deleted the Packaging/Ordering Information table, see POA at the end of the data sheet                                                                                                                                                                                                                         | 1    |

| • | Deleted the THS4509 EVM section to the Layout Example section                                                                                                                                                                                                                                                  | 37   |

| С | Changes from Revision G (May 2008) to Revision H                                                                                                                                                                                                                                                               | Page |

| • | Changed title of <i>Typical Characteristics</i> : V <sub>S+</sub> – V <sub>S</sub> = 5 V                                                                                                                                                                                                                       | 10   |

| • | Deleted conditions from <i>Typical Characteristics</i> : $V_{S+} - V_{S-} = 5$ V table of graphs                                                                                                                                                                                                               | 10   |

| • | Changed title of <i>Typical Characteristics</i> : V <sub>S+</sub> – V <sub>S</sub> = 3 V                                                                                                                                                                                                                       | 18   |

| • | Deleted conditions from <i>Typical Characteristics</i> : $V_{S+} - V_{S-} = 3$ V table of graphs                                                                                                                                                                                                               | 18   |

| • | Added y-axis to Figure 87                                                                                                                                                                                                                                                                                      | 33   |

| • | Added y-axis to Figure 90                                                                                                                                                                                                                                                                                      | 35   |

| • | Changed item 10 in Layout Recommendations section                                                                                                                                                                                                                                                              | 36   |

| • | Added the PowerPAD PCB Layout Considerations section                                                                                                                                                                                                                                                           | 36   |

| • | Moved Figure 92 and associated paragraph to PowerPAD PCB Layout Considerations section                                                                                                                                                                                                                         | 36   |

| • | Added the PowerPAD Design Considerations section                                                                                                                                                                                                                                                               | 38   |

| nges from Revision F (October 2007) to Revision G                                           | Page                   |

|---------------------------------------------------------------------------------------------|------------------------|

| lpdated document format                                                                     | 1                      |

| Changed common-mode range column for THS4509 and THS4513 rows in the Related Products table | 4                      |

| dded footnote 1 to Absolute Maximum Ratings table                                           | 5                      |

| dded V (volts) to unit column of ESD ratings rows in Absolute Maximum Ratings table         | 5                      |

| )                                                                                           | pdated document format |

| • | Changed $V_{S+} - V_{S-} = 5$ V Input specifications from 1.75 V typ (common-mode input range high) to 1.4 V typ; $-1.75$ V (common-mode input range low) to $-1.4$ V; 1.35 M $\Omega$    1.77 pF (differential input impedance) to 1.3 M $\Omega$    1.8 pF; 1.02 M $\Omega$    2.26 pF (common-mode input impedance) to 1.0 M $\Omega$    2.3 pF                        | 6 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Changed $V_{S+} - V_{S-} = 5 \text{ V}$ Input specifications from 1.75 V typ (common-mode input range high) to 1.4 V typ; -1.75 V (common-mode input range low) to -1.4 V; 1.35 M $\Omega$    1.77 pF (differential input impedance) to 1.3 M $\Omega$    1.8 pF; 1.02 M $\Omega$    2.26 pF (common-mode input impedance) to 1.0 M $\Omega$    2.3 pF                    | 7 |

| • | Changed V <sub>S+</sub> – V <sub>S-</sub> = 3 V <i>Input</i> specifications from 0.75 V typ (common-mode input range high) to 0.4 V typ; $-0.75$ V (common-mode input range low) to $-0.4$ V; 1.35 M $\Omega$    1.77 pF (differential input impedance) to 1.3 M $\Omega$    1.8 pF; 1.02 M $\Omega$    2.26 pF (common-mode input impedance) to 1.0 M $\Omega$    2.3 pF | 8 |

# 5 Device Comparison Table

| DEVICE  | MIN. GAIN | COMMON-MODE RANGE OF INPUT <sup>(1)</sup> |

|---------|-----------|-------------------------------------------|

| THS4508 | 6 dB      | -0.3 V to 2.3 V                           |

| THS4509 | 6 dB      | 1.1 V to 3.9 V                            |

| THS4511 | 0 dB      | -0.3 V to 2.3 V                           |

| THS4513 | 0 dB      | 1.1 V to 3.9 V                            |

(1) Assumes a 5-V single-ended power supply

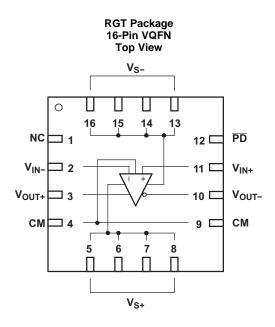

# 6 Pin Configuration and Functions

### **Pin Functions**

|                    | PIN TYPE       |      | DESCRIPTION                                                                                                                      |  |  |

|--------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.           |                | ITPE |                                                                                                                                  |  |  |

| NC                 | 1              | N/A  | No internal connection                                                                                                           |  |  |

| V <sub>IN</sub> _  | 2              | I    | Inverting amplifier input                                                                                                        |  |  |

| $V_{OUT+}$         | 3              | 0    | Noninverting amplifier output                                                                                                    |  |  |

| CM                 | 4, 9           | I    | ommon-mode voltage input                                                                                                         |  |  |

| V <sub>S+</sub>    | 5-8            | Р    | sitive amplifier power-supply input                                                                                              |  |  |

| V <sub>OUT</sub> - | 10             | 0    | verted amplifier output                                                                                                          |  |  |

| $V_{IN+}$          | 11             | I    | Noninverting amplifier input                                                                                                     |  |  |

| PD                 | 12             | I    | Power-down; $\overline{PD}$ = logic low puts part into low power mode, $\overline{PD}$ = logic high or open for normal operation |  |  |

| V <sub>S-</sub>    | 13, 14, 15, 16 | Р    | Negative amplifier power-supply input                                                                                            |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range, unless otherwise noted. (1)

|                                    |                                | MIN         | MAX             | UNIT |

|------------------------------------|--------------------------------|-------------|-----------------|------|

| V <sub>S-</sub> to V <sub>S+</sub> | Supply voltage                 |             | 6               | V    |

| VI                                 | Input voltage                  |             | ±V <sub>S</sub> |      |

| V <sub>ID</sub>                    | Differential input voltage     |             | 4               | V    |

| Io                                 | Output current <sup>(2)</sup>  |             | 200             | mA   |

|                                    | Continuous power dissipation   | See Dissipa | ation Ratings   |      |

| T <sub>J</sub>                     | Maximum junction temperature   |             | 150             | °C   |

| T <sub>A</sub>                     | Operating free-air temperature | -40         | 85              | °C   |

| T <sub>stg</sub>                   | Storage temperature            | -65         | 150             | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

### 7.2 ESD Ratings

|        |                         |                                                                     | VALUE | UNIT |

|--------|-------------------------|---------------------------------------------------------------------|-------|------|

|        |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V(EOD) | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

|        | distriarge              | Machine model                                                       | ±100  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     | MIN | NOM | MAX  | UNIT |

|---------------------|-----|-----|------|------|

| Supply voltage      | 3   | 5   | 5.25 | ٧    |

| Ambient temperature | -40 | 25  | 85   | °C   |

#### 7.4 Thermal Information

|                      |                                              | THS4509 |      |

|----------------------|----------------------------------------------|---------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                |         | UNIT |

|                      |                                              | 16 PINS |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 49.8    | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 66.9    | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 23.7    | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.7     | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 23.7    | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 7.1     | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> The THS4509 incorporates a (QFN) exposed thermal pad on the underside of the chip. This pad acts as a heatsink and must be connected to a thermally dissipative plane for proper power dissipation. Failure to do so may result in exceeding the maximum junction temperature which could permanently damage the device. See TI technical briefs SLMA002 and SLMA004 for more information about using the QFN thermally-enhanced package.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$

Test conditions are at  $V_{S+}$  = +2.5 V,  $V_{S-}$  = -2.5 V, G = 10 dB, CM = open,  $V_O$  = 2  $V_{PP}$ ,  $R_F$  = 349  $\Omega$ ,  $R_L$  = 200- $\Omega$  differential,  $T_A$  = +25°C, single-ended input, differential output, and input and output referenced to midsupply, unless otherwise noted.

| PARAMETER                                 | TEST COM                                            | NDITIONS                                      | TEST<br>LEVEL <sup>(1)</sup> | MIN | TYP  | MAX  | UNIT               |  |

|-------------------------------------------|-----------------------------------------------------|-----------------------------------------------|------------------------------|-----|------|------|--------------------|--|

| AC PERFORMANCE                            |                                                     |                                               |                              |     |      |      |                    |  |

|                                           | G = 6 dB, V <sub>O</sub> = 100 mV <sub>PP</sub>     |                                               |                              | 2   |      |      | GHz                |  |

| Ownell size of boardwidth                 | $G = 10 \text{ dB}, V_O = 100 \text{ mV}_{PP}$      |                                               |                              | 1.9 |      | GHz  |                    |  |

| Small-signal bandwidth                    | $G = 14 \text{ dB}, V_O = 100 \text{ mV}_{PP}$      |                                               |                              | 600 |      | MHz  |                    |  |

|                                           | $G = 20 \text{ dB}, V_0 = 100 \text{ mV}_1$         | PP .                                          |                              |     | 275  |      | MHz                |  |

| Gain-bandwidth product                    | G = 20 dB                                           |                                               |                              |     | 3    |      | GHz                |  |

| Bandwidth for 0.1-dB flatness             | $G = 10 \text{ dB}, V_O = 2 V_{PP}$                 | G = 10 dB, V <sub>O</sub> = 2 V <sub>PP</sub> |                              |     | 300  |      | MHz                |  |

| Large-signal bandwidth                    | $G = 10 \text{ dB}, V_O = 2 V_{PP}$                 | $G = 10 \text{ dB}, V_O = 2 V_{PP}$           |                              | 1.5 |      |      | GHz                |  |

| Slew rate (differential)                  |                                                     |                                               |                              |     | 6600 |      | V/μs               |  |

| Rise time                                 |                                                     |                                               |                              |     | 0.5  |      |                    |  |

| Fall time                                 | 2-V step                                            |                                               |                              |     | 0.5  |      |                    |  |

| Settling time to 1%                       |                                                     |                                               |                              |     | 2    |      | ns                 |  |

| Settling time to 0.1%                     |                                                     |                                               |                              |     | 10   |      |                    |  |

|                                           | f = 10 MHz -104                                     |                                               |                              |     |      |      |                    |  |

| 2nd-order harmonic distortion             | f = 50 MHz                                          | f = 50 MHz                                    |                              |     | -80  |      | dBc                |  |

|                                           | f = 100 MHz                                         |                                               |                              |     | -68  |      |                    |  |

|                                           | f = 10 MHz                                          |                                               | С                            |     | -108 |      |                    |  |

| 3rd-order harmonic distortion             | f = 50 MHz                                          |                                               |                              |     | -92  |      | dBc                |  |

|                                           | f = 100 MHz                                         |                                               |                              |     | -81  |      |                    |  |

|                                           |                                                     | f <sub>C</sub> = 70 MHz                       |                              |     | -78  |      |                    |  |

| 2nd-order intermodulation distortion      | 200-kHz tone spacing, $R_L = 499 \Omega$            | f <sub>C</sub> = 140 MHz                      |                              |     | -64  |      | -10 -              |  |

|                                           |                                                     | f <sub>C</sub> = 70 MHz                       |                              |     | -95  |      | dBc                |  |

| 3rd-order intermodulation distortion      |                                                     | f <sub>C</sub> = 140 MHz                      |                              |     | -78  |      | 1                  |  |

|                                           | f <sub>C</sub> = 70 MHz                             |                                               |                              | 78  |      |      |                    |  |

| 2nd-order output intercept point          | 200-kHz tone spacing                                | f <sub>C</sub> = 140 MHz                      |                              | 58  |      |      |                    |  |

|                                           | $R_L$ = 100 Ω, referenced to 50-Ω output            | f <sub>C</sub> = 70 MHz                       |                              |     | 43   |      | dBm                |  |

| 3rd-order output intercept point          | •                                                   | f <sub>C</sub> = 140 MHz                      |                              |     | 38   |      |                    |  |

|                                           | f <sub>C</sub> = 70 MHz                             | 1                                             |                              |     | 12.2 |      |                    |  |

| 1-dB compression point                    | f <sub>C</sub> = 140 MHz                            |                                               |                              |     | 10.8 |      | dBm                |  |

| Noise figure                              | 50-Ω system, 10 MHz                                 |                                               |                              |     | 17.1 |      | dB                 |  |

| Input voltage noise                       | f > 10 MHz                                          |                                               |                              |     | 1.9  |      | nV/√ <del>Hz</del> |  |

| Input current noise                       | f > 10 MHz                                          |                                               |                              |     | 2.2  |      | pA/√ <del>Hz</del> |  |

| DC PERFORMANCE                            | -                                                   |                                               |                              |     |      | '    |                    |  |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                     |                                               | С                            |     | 68   |      | dB                 |  |

|                                           | T <sub>A</sub> = +25°C                              |                                               |                              |     | 1    | 4    | mV                 |  |

| Input offset voltage                      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | A                            |     | 1    | 5    | mV                 |  |

| Average offset voltage drift              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | В                            |     | 2.6  |      | μV/°C              |  |

|                                           | T <sub>A</sub> = +25°C                              |                                               |                              |     | 8    | 15.5 | •                  |  |

| Input bias current                        | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | Α                            |     | 8    | 18.5 | μА                 |  |

| Average bias current drift                | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | В                            |     | 20   |      | nA/°C              |  |

|                                           | T <sub>A</sub> = +25°C                              |                                               | 1                            |     | 1.6  | 3.6  | цΑ                 |  |

| Input offset current                      | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | A                            |     | 1.6  | 7    |                    |  |

| Average offset current drift              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               | В                            |     | 4    |      | nA/°C              |  |

<sup>(1)</sup> Test levels: (A) 100% tested at +25°C. Over-temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

# Electrical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V (continued)}$

Test conditions are at  $V_{S+}$  = +2.5 V,  $V_{S-}$  = -2.5 V, G = 10 dB, CM = open,  $V_O$  = 2  $V_{PP}$ ,  $R_F$  = 349  $\Omega$ ,  $R_L$  = 200- $\Omega$  differential,  $T_A$  = +25°C, single-ended input, differential output, and input and output referenced to midsupply, unless otherwise noted.

| PARAMETER                                   | TEST CONDITIONS                                     |                         | TEST<br>LEVEL <sup>(1)</sup> | MIN  | TYP                        | MAX      | UNIT                   |  |

|---------------------------------------------|-----------------------------------------------------|-------------------------|------------------------------|------|----------------------------|----------|------------------------|--|

| INPUT                                       |                                                     |                         |                              |      |                            |          |                        |  |

| Common-mode input range high                |                                                     |                         |                              |      | 1.4                        |          | V                      |  |

| Common-mode input range low                 |                                                     |                         | В                            |      | -1.4                       |          | V                      |  |

| Common-mode rejection ratio                 |                                                     |                         |                              |      | 90                         |          | dB                     |  |

| Differential input impedance                |                                                     |                         | С                            |      | 1.3    1.8                 |          | $M\Omega \parallel pF$ |  |

| Common-mode input impedance                 |                                                     |                         | С                            |      | 1.0    2.3                 |          | MΩ    pF               |  |

| OUTPUT                                      |                                                     |                         |                              |      |                            |          |                        |  |

| Maximum autout valtage bigh                 | $T_A = +25$ °C                                      |                         |                              | 1.2  | 1.4                        |          | V                      |  |

| Maximum output voltage high                 | Each output with 100 Ω                              | $T_A = -40$ °C to +85°C |                              | 1.1  | 1.4                        |          | V                      |  |

| Minimum output voltage love                 | to midsupply                                        | $T_A = +25^{\circ}C$    | Α —                          |      | -1.4                       | -1.2     | V                      |  |

| Minimum output voltage low                  |                                                     | $T_A = -40$ °C to +85°C |                              |      | -1.4                       | -1.1     | V                      |  |

| Differential output valtege aving           |                                                     |                         |                              | 4.8  | 5.6                        |          | V                      |  |

| Differential output voltage swing           | $T_A = -40$ °C to +85°C                             |                         |                              | 4.4  |                            |          |                        |  |

| Differential output current drive           | R <sub>L</sub> = 10 Ω                               |                         |                              |      | 96                         |          | mA                     |  |

| Output balance error                        | V <sub>O</sub> = 100 mV, f = 1 MHz                  |                         | С                            |      | -49                        |          | dB                     |  |

| Closed-loop output impedance                | f = 1 MHz                                           |                         |                              |      | 0.3                        |          | Ω                      |  |

| OUTPUT COMMON-MODE VOLTAGE CO               | NTROL                                               |                         |                              |      |                            | *        |                        |  |

| Small-signal bandwidth                      |                                                     |                         |                              |      | 700                        |          | MHz                    |  |

| Slew rate                                   |                                                     |                         |                              |      | 110                        |          | V/μs                   |  |

| Gain                                        |                                                     |                         |                              |      | 1                          |          | V/V                    |  |

| Output common-mode offset from CM input     | 1.25 V < CM < 3.5 V                                 |                         |                              |      | 5                          |          | mV                     |  |

| CM input bias current                       | 1.25 V < CM < 3.5 V                                 |                         | С                            |      | ±40                        |          | μА                     |  |

| CM input voltage high                       |                                                     |                         |                              |      | 1.5                        |          | V                      |  |

| CM input voltage low                        |                                                     |                         |                              |      | -1.5                       | -1.5     |                        |  |

| CM input impedance                          |                                                     |                         |                              |      | 23    1                    |          | kΩ    pF               |  |

| CM default voltage                          |                                                     |                         |                              |      | 0                          |          | V                      |  |

| POWER SUPPLY                                |                                                     |                         |                              |      |                            |          |                        |  |

| Specified operating voltage                 |                                                     |                         | С                            | 3    | 5                          | 5.25     | V                      |  |

|                                             | T <sub>A</sub> = +25°C                              |                         |                              |      | 37.7                       | 40.9     |                        |  |

| Maximum quiescent current                   | $T_A = -40$ °C to +85°C                             |                         | 1                            |      | 37.7                       | 41.9     | mA                     |  |

|                                             | T <sub>A</sub> = +25°C                              |                         | Α -                          | 34.5 | 37.7                       |          |                        |  |

| Minimum quiescent current                   | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                         |                              | 33.5 | 37.7                       |          | mA                     |  |

| Power-supply rejection (±PSRR)              |                                                     |                         | С                            |      | 90                         |          | dB                     |  |

| POWER-DOWN - Referenced to V <sub>S</sub> _ |                                                     |                         | 1                            |      |                            |          |                        |  |

| Enable voltage threshold                    | Assured <i>on</i> above 2.1 V                       | + V <sub>S-</sub>       |                              |      | > 2.1 +<br>V <sub>S-</sub> |          | V                      |  |

| Disable voltage threshold                   | Assured off below 0.7 V + V <sub>S</sub> _          |                         | С                            |      | < 0.7 +<br>V <sub>S-</sub> |          | V                      |  |

| Power-down quiescent current                | $T_A = +25^{\circ}C$                                |                         | А                            |      | 0.65                       | 0.9      | mA                     |  |

| 1                                           | $T_A = -40$ °C to +85°C                             |                         | ^                            |      | 0.65                       | 1        | 1 ""                   |  |

| Input bias current                          | $\overline{PD} = V_{S-}$                            |                         |                              |      | 100                        |          | μΑ                     |  |

| Input impedance                             |                                                     |                         | C 50    2                    |      |                            | kΩ    pF |                        |  |

| Turnon time delay                           | Measured to output on                               |                         |                              |      | 55                         |          | ns                     |  |

| Turnoff time delay                          | Measured to output off                              |                         |                              |      | 10                         |          | μS                     |  |

# 7.6 Electrical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V}$

Test conditions at  $V_{S+}$  = +1.5 V,  $V_{S-}$  = -1.5 V, G = 10 dB, CM = open,  $V_{O}$  = 1  $V_{PP}$ ,  $R_{F}$  = 349  $\Omega$ ,  $R_{L}$  = 200- $\Omega$  differential,  $T_{A}$  = +25°C, single-ended input, differential output, and input and output referenced to midsupply, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                                     |                                               | TEST<br>LEVEL <sup>(1)</sup> | MIN | TYP        | MAX  | UNIT               |  |

|-------------------------------------------|-----------------------------------------------------|-----------------------------------------------|------------------------------|-----|------------|------|--------------------|--|

| AC PERFORMANCE                            |                                                     |                                               |                              |     |            |      |                    |  |

|                                           | $G = 6 \text{ dB}, V_O = 100 \text{ mV}_P$          | $G = 6 \text{ dB}, V_O = 100 \text{ mV}_{PP}$ |                              | 1.9 |            |      | GHz                |  |

| 0 11 1 11 11                              | $G = 10 \text{ dB}, V_0 = 100 \text{ mV}$           | PP                                            |                              |     | 1.6        |      | GHz                |  |

| Small-signal bandwidth                    | G = 14 dB, V <sub>O</sub> = 100 mV                  | PP                                            |                              |     | 625        |      | MHz                |  |

|                                           | $G = 20 \text{ dB}, V_0 = 100 \text{ mV}$           | PP                                            |                              |     | 260        |      | MHz                |  |

| Gain-bandwidth product                    | G = 20 dB                                           |                                               |                              | 3   |            | GHz  |                    |  |

| Bandwidth for 0.1-dB flatness             | $G = 10 \text{ dB}, V_O = 1 V_{PP}$                 |                                               |                              |     | 400        |      | MHz                |  |

| Large-signal bandwidth                    | G = 10 dB, V <sub>O</sub> = 1 V <sub>PP</sub>       |                                               |                              |     | 1.5        |      | GHz                |  |

| Slew rate (differential)                  |                                                     |                                               |                              |     | 3500       |      | V/μs               |  |

| Rise time                                 |                                                     |                                               |                              |     | 0.25       |      |                    |  |

| Fall time                                 | 2-V step                                            |                                               |                              |     | 0.25       |      |                    |  |

| Settling time to 1%                       |                                                     |                                               |                              |     | 1          |      | ns                 |  |

| Settling time to 0.1%                     |                                                     |                                               |                              |     | 10         |      |                    |  |

|                                           | f = 10 MHz                                          | f = 10 MHz                                    |                              |     | -107       |      |                    |  |

| 2nd-order harmonic distortion             | f = 50 MHz                                          |                                               |                              |     | -83        |      | dBc                |  |

|                                           | f = 100 MHz                                         |                                               |                              |     | -60        |      |                    |  |

|                                           | f = 10 MHz                                          |                                               | С                            |     | -87        |      | 1                  |  |

| 3rd-order harmonic distortion             | f = 50 MHz                                          |                                               |                              |     | -65        |      | dBc                |  |

|                                           | f = 100 MHz                                         |                                               |                              |     | -54        |      | 1                  |  |

| 2nd-order intermodulation distortion      | f <sub>C</sub> = 70 MHz                             |                                               |                              |     | -77        |      |                    |  |

|                                           | 200-kHz tone spacing, $R_L = 499 \ \Omega$          | f <sub>C</sub> = 140 MHz                      |                              | -54 |            |      |                    |  |

|                                           |                                                     | f <sub>C</sub> = 70 MHz                       |                              |     | <b>–77</b> |      | dBc                |  |

| 3rd-order intermodulation distortion      |                                                     | f <sub>C</sub> = 140 MHz                      |                              |     | -62        |      |                    |  |

|                                           |                                                     | f <sub>C</sub> = 70 MHz                       |                              |     | 72         |      |                    |  |

| 2nd-order output intercept point          | 200-kHz tone spacing                                | f <sub>C</sub> = 140 MHz                      |                              | 52  |            |      |                    |  |

|                                           | $R_L = 100 \Omega$                                  | f <sub>C</sub> = 70 MHz                       |                              |     | 38.5       |      | dBm                |  |

| 3rd-order output intercept point          |                                                     | f <sub>C</sub> = 140 MHz                      |                              |     | 30         |      |                    |  |

|                                           | f <sub>C</sub> = 70 MHz                             |                                               |                              |     | 2.2        |      | dBm                |  |

| 1-dB compression point                    | f <sub>C</sub> = 140 MHz                            |                                               |                              |     | 0.25       | 0.25 |                    |  |

| Noise figure                              | 50 Ω system, 10 MHz                                 |                                               |                              |     | 17.1       |      | dB                 |  |

| Input voltage noise                       | f > 10 MHz                                          |                                               |                              |     | 1.9        |      | nV/√ <del>Hz</del> |  |

| Input current noise                       | f > 10 MHz                                          |                                               |                              |     | 2.2        |      | pA/√ <del>Hz</del> |  |

| DC PERFORMANCE                            |                                                     |                                               |                              |     |            |      |                    |  |

| Open-loop voltage gain (A <sub>OL</sub> ) |                                                     |                                               |                              |     | 68         |      | dB                 |  |

| Input offset voltage                      | T <sub>A</sub> = +25°C                              |                                               |                              |     | 1          |      | mV                 |  |

| Average offset voltage drift              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               |                              |     | 2.6        |      | μV/°C              |  |

| Input bias current                        | T <sub>A</sub> = +25°C                              |                                               | С                            |     | 6          |      | <u>.</u><br>μΑ     |  |

| Average bias current drift                | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               |                              |     | 20         |      | nA/°C              |  |

| Input offset current                      | T <sub>A</sub> = +25°C                              |                                               |                              |     | 1.6        |      | μА                 |  |

| Average offset current drift              | $T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ |                                               |                              |     | 4          |      | nA/°C              |  |

<sup>(1)</sup> Test levels: (A) 100% tested at +25°C. Over-temperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

# Electrical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V (continued)}$

Test conditions at  $V_{S+}$  = +1.5 V,  $V_{S-}$  = -1.5 V, G = 10 dB, CM = open,  $V_{O}$  = 1  $V_{PP}$ ,  $R_{F}$  = 349  $\Omega$ ,  $R_{L}$  = 200- $\Omega$  differential,  $T_{A}$  = +25°C, single-ended input, differential output, and input and output referenced to midsupply, unless otherwise noted.

| PARAMETER                                 | TEST COM                                   | NDITIONS                                         | TEST<br>LEVEL <sup>(1)</sup> | MIN     | TYP MAX                  | UNIT     |  |

|-------------------------------------------|--------------------------------------------|--------------------------------------------------|------------------------------|---------|--------------------------|----------|--|

| INPUT                                     |                                            |                                                  |                              |         |                          |          |  |

| Common-mode input range high              |                                            |                                                  |                              |         | 0.4                      |          |  |

| Common-mode input range low               |                                            |                                                  | В                            | -       | -0.4                     | V        |  |

| Common-mode rejection ratio               |                                            |                                                  |                              |         | 80                       | dB       |  |

| Differential input impedance              |                                            |                                                  | С                            | 1.3     | 1.8                      | MΩ    pF |  |

| Common-mode input impedance               |                                            |                                                  | С                            | 1.0     | 2.3                      | MΩ    pF |  |

| OUTPUT                                    | 1                                          |                                                  |                              |         | -                        |          |  |

| Maximum output voltage high               | Each output with 100 Ω                     | T <sub>A</sub> = +25°C                           |                              | (       | 0.45                     | V        |  |

| Minimum output voltage low                | to midsupply                               | T <sub>A</sub> = +25°C                           |                              | -       | 0.45                     | V        |  |

| Differential output voltage swing         |                                            |                                                  | _                            |         | 1.8                      | V        |  |

| Differential output current drive         | R <sub>L</sub> = 10 Ω                      |                                                  | С                            |         | 50                       | mA       |  |

| Output balance error                      | V <sub>O</sub> = 100 mV, f = 1 MHz         |                                                  |                              |         | -49                      | dB       |  |

| Closed-loop output impedance              | f = 1 MHz                                  |                                                  |                              |         | 0.3                      | Ω        |  |

| OUTPUT COMMON-MODE VOLTAGE C              | ONTROL                                     |                                                  |                              |         |                          |          |  |

| Small-signal bandwidth                    | 1.25 V < CM < 3.5 V                        |                                                  |                              |         | 570                      | MHz      |  |

| Slew rate                                 |                                            |                                                  |                              |         | 60                       | V/μs     |  |

| Gain                                      |                                            |                                                  |                              |         | 1                        | V/V      |  |

| Output common-mode offset from CM input   |                                            |                                                  | c                            |         | 4                        | mV       |  |

| CM input bias current                     | 1.25 V < CM < 3.5 V                        | 1.25 V < CM < 3.5 V                              |                              |         | ±40                      | μА       |  |

| CM input voltage high                     |                                            |                                                  |                              |         | 1.5                      |          |  |

| CM input voltage low                      |                                            |                                                  |                              |         | -1.5                     | V        |  |

| CM input impedance                        |                                            |                                                  |                              | 20      | )    1                   | kΩ    pF |  |

| CM default voltage                        |                                            |                                                  |                              |         | 0                        | V        |  |

| POWER SUPPLY                              |                                            |                                                  |                              |         |                          | +        |  |

| Specified operating voltage               |                                            |                                                  | С                            |         | 3                        | V        |  |

| Quiescent current                         | T <sub>A</sub> = +25°C                     |                                                  | A                            | ;       | 34.8                     | mA       |  |

| Power-supply rejection (±PSRR)            |                                            |                                                  | С                            |         | 70                       | dB       |  |

| POWER-DOWN Referenced to V <sub>S</sub> _ |                                            |                                                  |                              |         |                          | •        |  |

| Enable voltage threshold                  | Assured on above 2.1 V                     | Assured <i>on</i> above 2.1 V + V <sub>S</sub> _ |                              | > 2     | 2.1 +<br>V <sub>S-</sub> | ٧        |  |

| Disable voltage threshold                 | Assured off below 0.7 V + V <sub>S</sub> _ |                                                  |                              | < 0.7 + | - V <sub>S-</sub>        | V        |  |

| Power-down quiescent current              |                                            |                                                  | С                            | 1       | 0.46                     | mA       |  |

| Input bias current                        | PD = V <sub>S-</sub>                       | $\overline{PD} = V_{S-}$                         |                              |         | 65                       | μА       |  |

| Input impedance                           |                                            |                                                  |                              | 50      | )    2                   | kΩ    pF |  |

| Turnon time delay                         | Measured to output on                      |                                                  |                              |         | 100                      | ns       |  |

| Turnoff time delay                        | Measured to output off                     |                                                  |                              |         | 10                       | μS       |  |

# 7.7 Dissipation Ratings

|          |         |               | POWER RATING           |                        |  |

|----------|---------|---------------|------------------------|------------------------|--|

| PACKAGE  | θυς     | $\theta_{JA}$ | T <sub>A</sub> ≤ +25°C | T <sub>A</sub> = +85°C |  |

| RGT (16) | 2.4°C/W | 39.5°C/W      | 2.3 W                  | 225 mW                 |  |

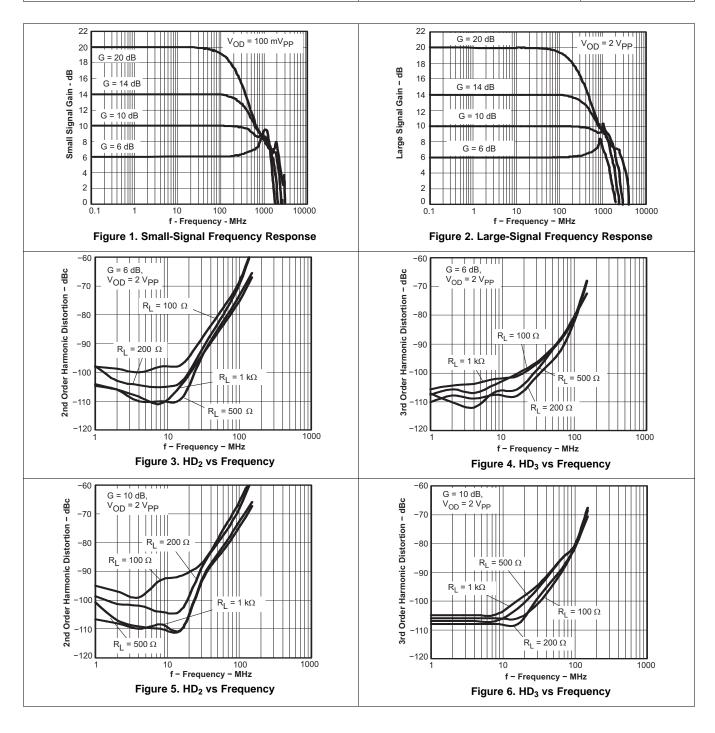

# 7.8 Typical Characteristics

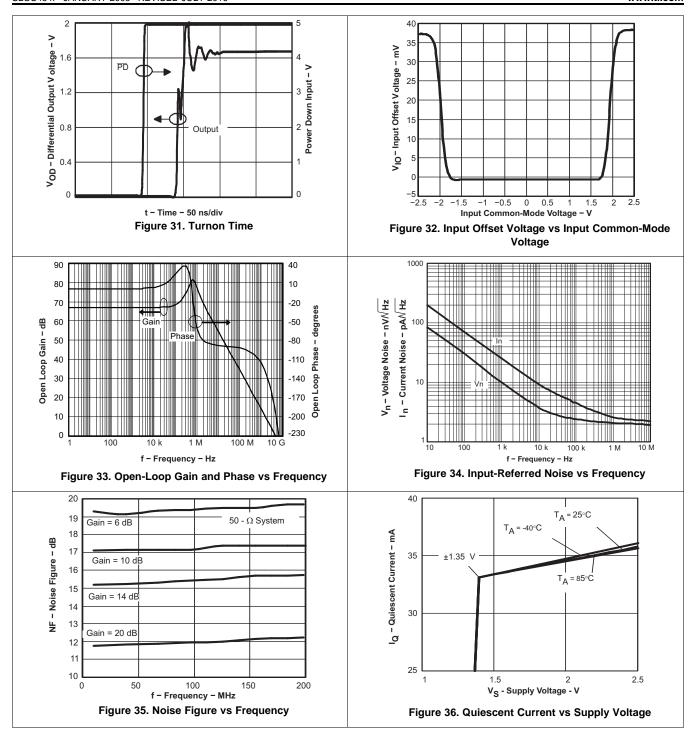

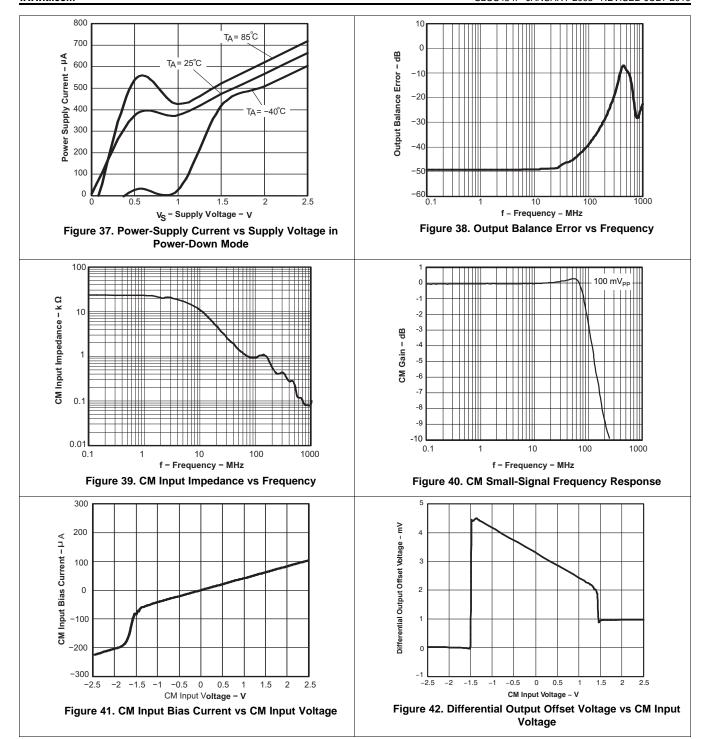

# 7.8.1 Typical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V}$

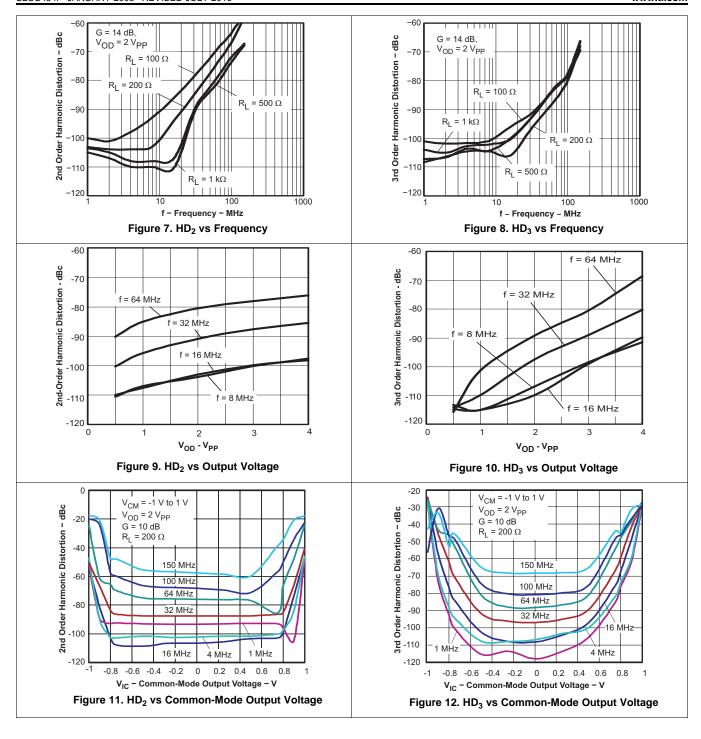

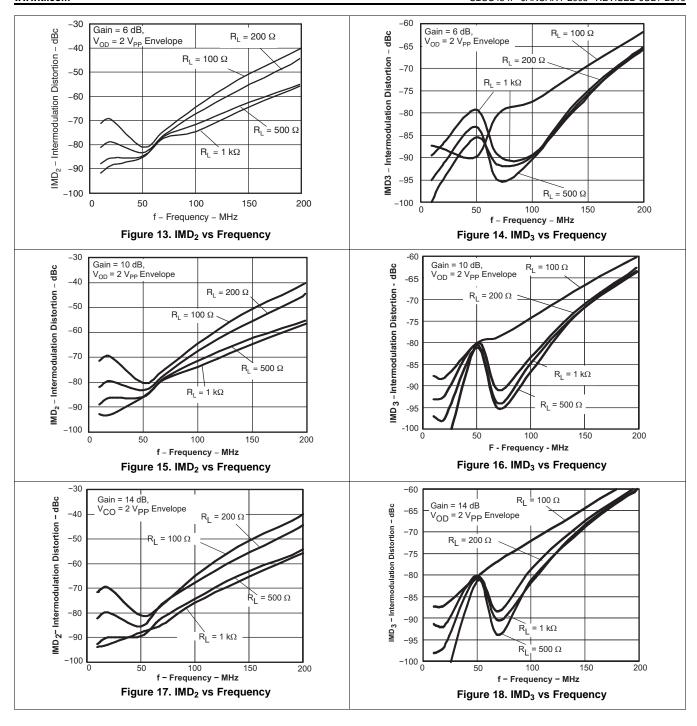

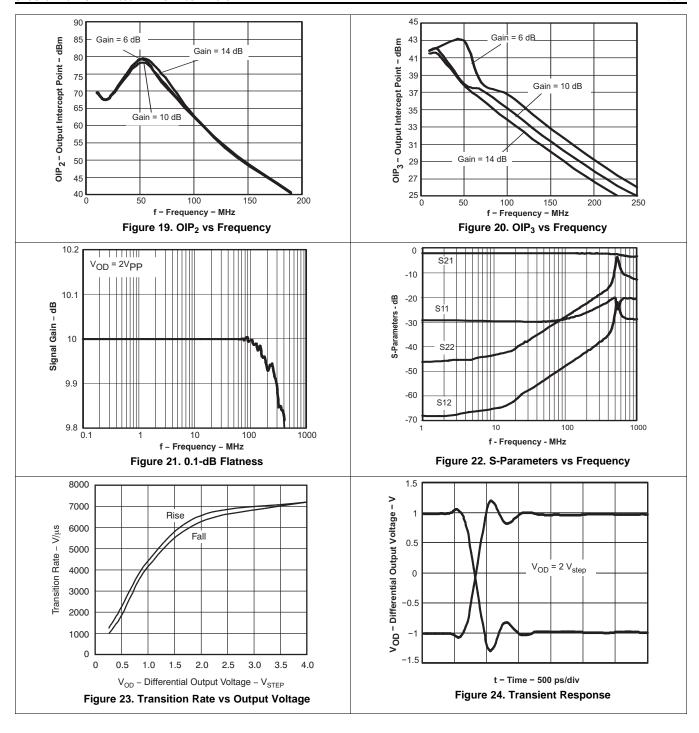

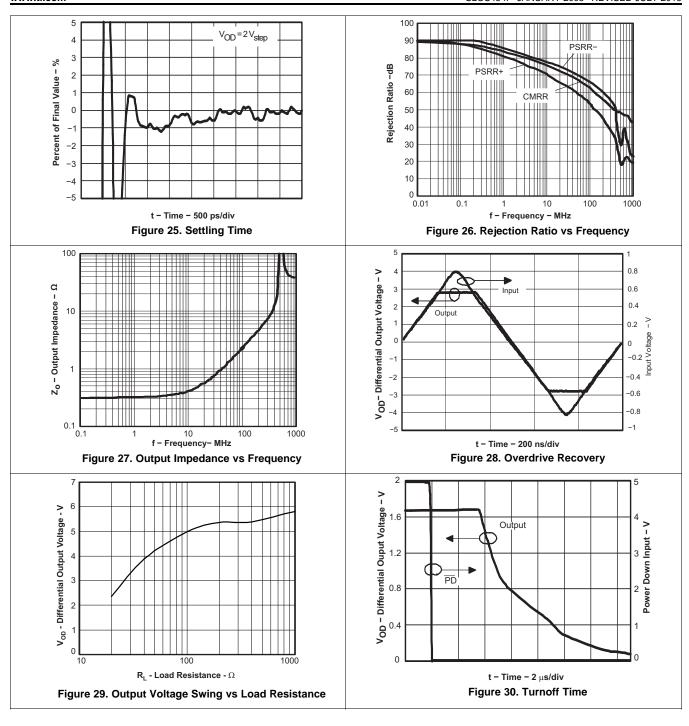

Test conditions at  $V_{S+}$  = +2.5 V,  $V_{S-}$  = -2.5 V, CM = open,  $V_{O}$  = 2  $V_{PP}$ ,  $R_{F}$  = 349  $\Omega$ ,  $R_{L}$  = 200- $\Omega$  differential, G = 10 dB, single-ended input, and input and output referenced to midrail, unless otherwise noted.

Table 1. Table of Graphs

|                                |                                                                  |                                      | FIGURE    |

|--------------------------------|------------------------------------------------------------------|--------------------------------------|-----------|

| Small-Signal Frequency Res     | ponse                                                            |                                      | Figure 1  |

| Large-Signal Frequency Res     | sponse                                                           |                                      | Figure 2  |

|                                | $HD_2$ , G = 6 dB, $V_{OD}$ = 2 $V_{PP}$                         | vs Frequency                         | Figure 3  |

|                                | $HD_3$ , $G = 6$ dB, $V_{OD} = 2$ $V_{PP}$                       | vs Frequency                         | Figure 4  |

|                                | $HD_2$ , $G = 10$ dB, $V_{OD} = 2$ $V_{PP}$                      | vs Frequency                         | Figure 5  |

|                                | $HD_3$ , $G = 10$ dB, $V_{OD} = 2$ $V_{PP}$                      | vs Frequency                         | Figure 6  |

| Harmonic                       | HD <sub>2</sub> , G = 14 dB, V <sub>OD</sub> = 2 V <sub>PP</sub> | vs Frequency                         | Figure 7  |

| Distortion                     | HD <sub>3</sub> , G = 14 dB, V <sub>OD</sub> = 2 V <sub>PP</sub> | vs Frequency                         | Figure 8  |

|                                | HD <sub>2</sub> , G = 10 dB                                      | vs Output Voltage                    | Figure 9  |

|                                | HD <sub>3</sub> , G = 10 dB                                      | vs Output Voltage                    | Figure 10 |

|                                | HD <sub>2</sub> , G = 10 dB                                      | vs Common-Mode Input Voltage         | Figure 11 |

|                                | HD <sub>3</sub> , G = 10 dB                                      | vs Common-Mode Input Voltage         | Figure 12 |

|                                | $IMD_2$ , G = 6 dB, $V_{OD}$ = 2 $V_{PP}$                        | vs Frequency                         | Figure 13 |

|                                | $IMD_3$ , G = 6 dB, $V_{OD}$ = 2 $V_{PP}$                        | vs Frequency                         | Figure 14 |

| Intermodulation                | $IMD_2$ , G = 10 dB, $V_{OD}$ = 2 $V_{PP}$                       | vs Frequency                         | Figure 15 |

| Distortion                     | $IMD_3$ , G = 10 dB, $V_{OD}$ = 2 $V_{PP}$                       | vs Frequency                         | Figure 16 |

|                                | $IMD_2$ , G = 14 dB, $V_{OD}$ = 2 $V_{PP}$                       | vs Frequency                         | Figure 17 |

|                                | $IMD_3$ , G = 14 dB, $V_{OD}$ = 2 $V_{PP}$                       | vs Frequency                         | Figure 18 |

| Output latere and Balat        | OIP <sub>2</sub>                                                 | vs Frequency                         | Figure 19 |

| Output Intercept Point         | OIP <sub>3</sub>                                                 | vs Frequency                         | Figure 20 |

| 0.1-dB Flatness                |                                                                  |                                      | Figure 21 |

| S-Parameters                   |                                                                  | vs Frequency                         | Figure 22 |

| Transition Rate                |                                                                  | vs Output Voltage                    | Figure 23 |

| Transient Response             |                                                                  |                                      | Figure 24 |

| Settling Time                  |                                                                  |                                      | Figure 25 |

| Rejection Ratio                |                                                                  | vs Frequency                         | Figure 26 |

| Output Impedance               |                                                                  | vs Frequency                         | Figure 27 |

| Overdrive Recovery             |                                                                  |                                      | Figure 28 |

| Output Voltage Swing           |                                                                  | vs Load Resistance                   | Figure 29 |

| Turnoff Time                   |                                                                  |                                      | Figure 30 |

| Turnon Time                    |                                                                  |                                      | Figure 31 |

| Input Offset Voltage           |                                                                  | vs Input Common-Mode Voltage         | Figure 32 |

| Open-Loop Gain                 |                                                                  | vs Frequency                         | Figure 33 |

| Input-Referred Noise           |                                                                  | vs Frequency                         | Figure 34 |

| Noise Figure                   |                                                                  | vs Frequency                         | Figure 35 |

| Quiescent Current              |                                                                  | vs Supply Voltage                    | Figure 36 |

| Power-Supply Current           |                                                                  | vs Supply Voltage in Power-Down Mode | Figure 37 |

| Output Balance Error           |                                                                  | vs Frequency                         | Figure 38 |

| CM Input Impedance             |                                                                  | vs Frequency                         | Figure 39 |

| CM Small-Signal Frequency      | Response                                                         |                                      | Figure 40 |

| CM Input Bias Current          | -                                                                | vs CM Input Voltage                  | Figure 41 |

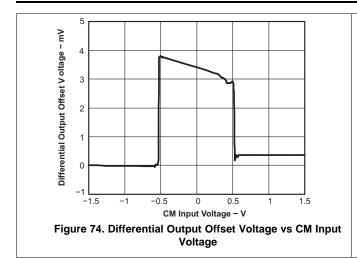

| Differential Output Offset Vol | Itage                                                            | vs CM Input Voltage                  | Figure 42 |

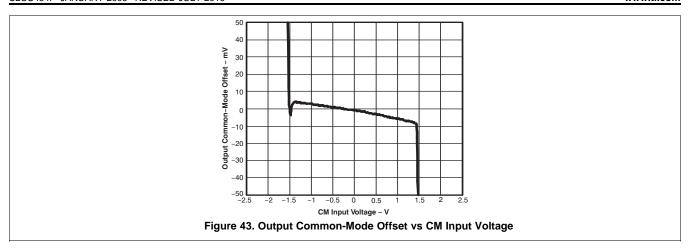

# Typical Characteristics: $V_{S+} - V_{S-} = 5 \text{ V (continued)}$

### Table 1. Table of Graphs (continued)

|                           |                     | FIGURE    |

|---------------------------|---------------------|-----------|

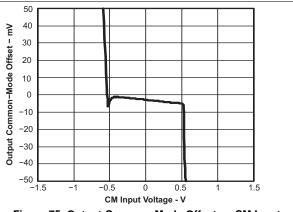

| Output Common-Mode Offset | vs CM Input Voltage | Figure 43 |

Copyright © 2005–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Submit Documentation Feedback

Copyright © 2005–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Copyright © 2005–2016, Texas Instruments Incorporated

Copyright © 2005–2016, Texas Instruments Incorporated

Submit Documentation Feedback

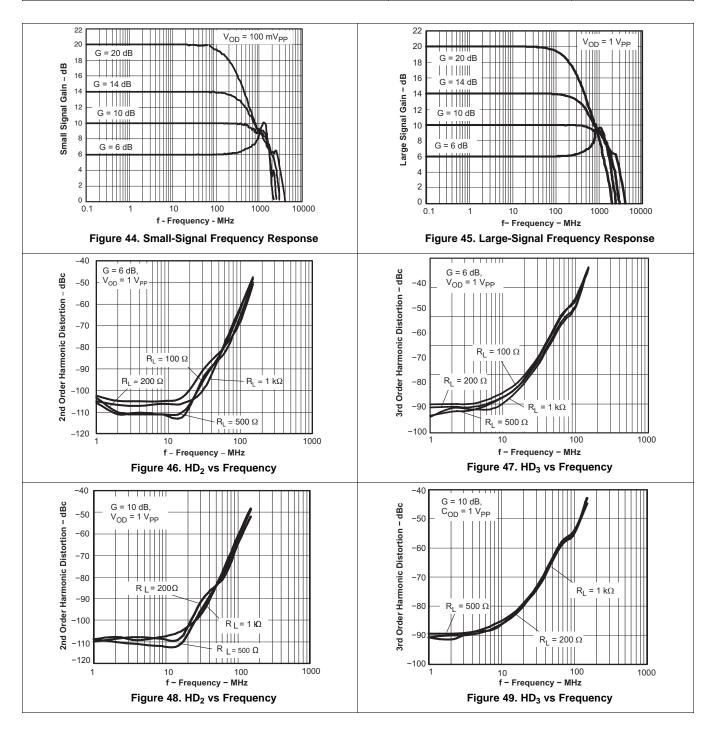

# 7.8.2 Typical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V}$

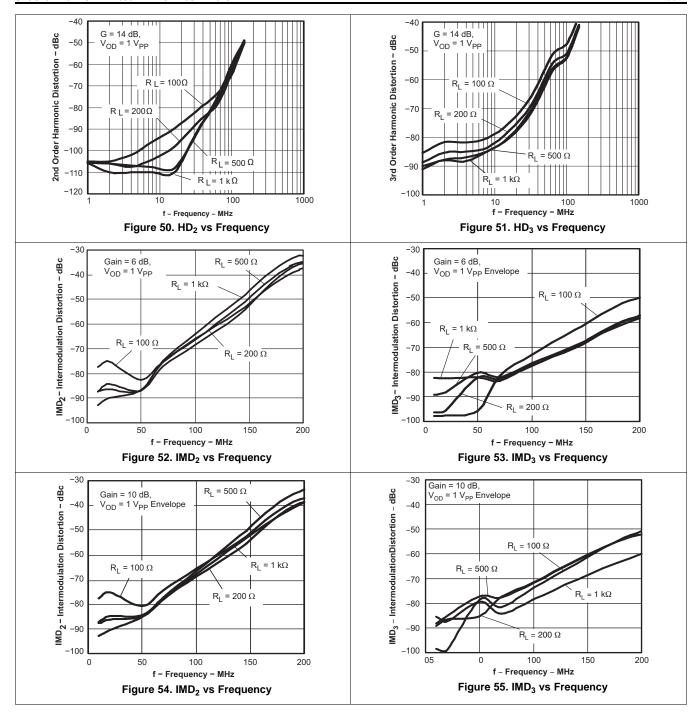

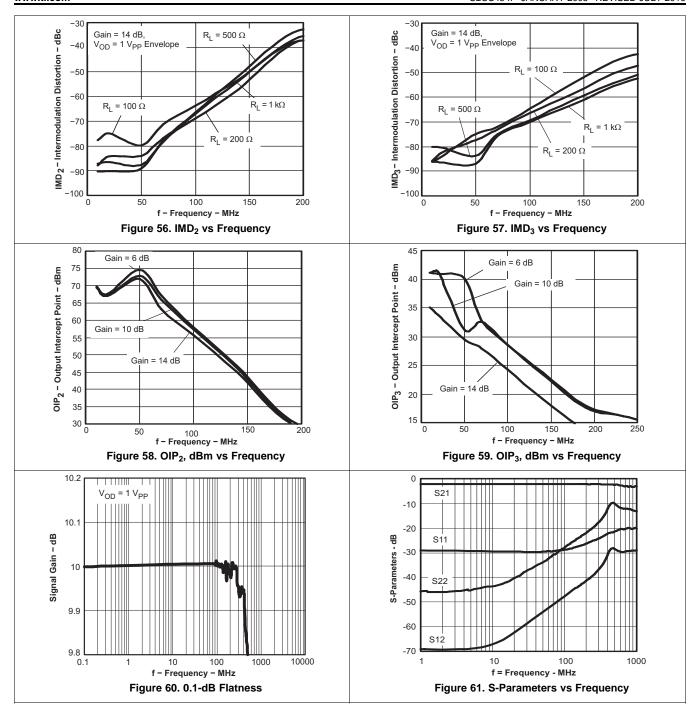

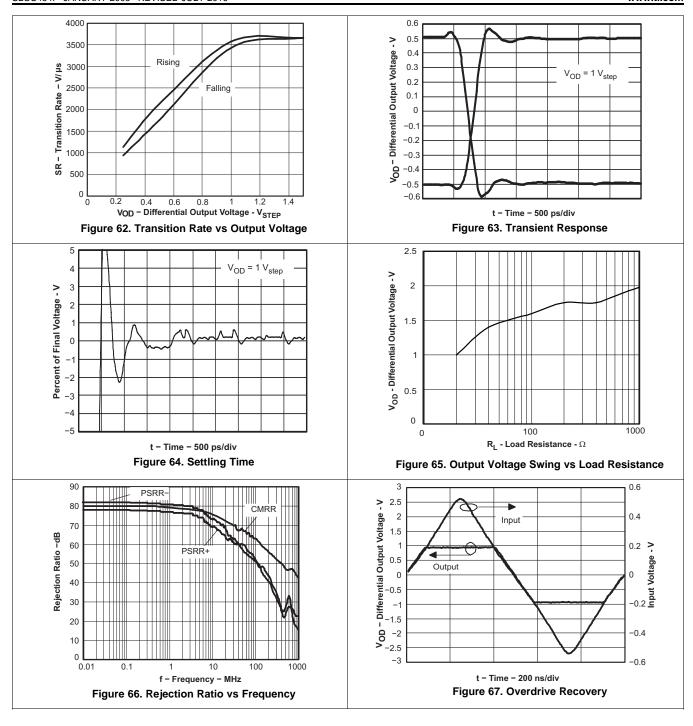

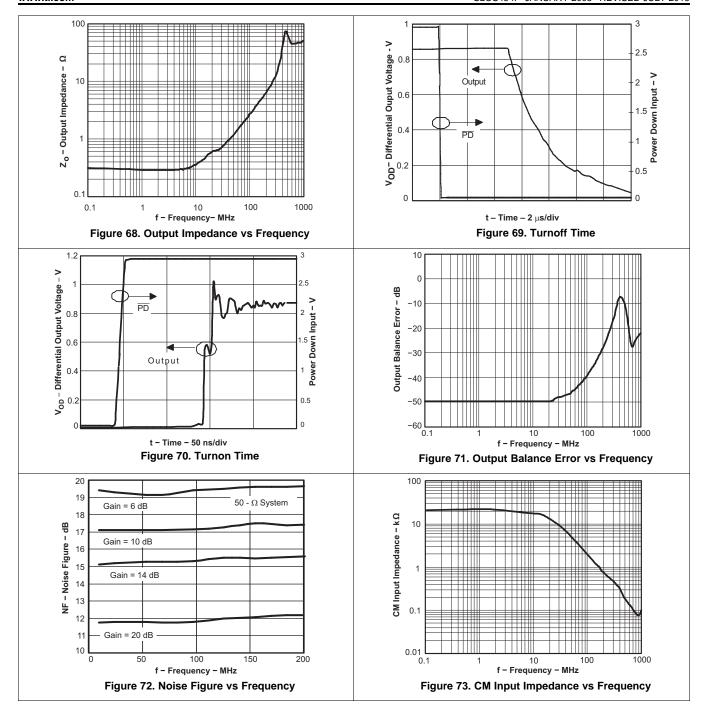

Test conditions at  $V_{S+}$  = +1.5 V,  $V_{S-}$  = -1.5 V, CM = open,  $V_{OD}$  = 1  $V_{PP}$ ,  $R_F$  = 349  $\Omega$ ,  $R_L$  = 200- $\Omega$  differential, G = 10 dB, single-ended input, and input and output referenced to midrail, unless otherwise noted.

**Table 2. Table of Graphs**

|                             |                                            |                    | FIGURE    |

|-----------------------------|--------------------------------------------|--------------------|-----------|

| Small-Signal Frequency Resp | onse                                       |                    | Figure 44 |

| Large-Signal Frequency Resp | onse                                       |                    | Figure 45 |

|                             | $HD_2$ , $G = 6$ dB, $V_{OD} = 1$ $V_{PP}$ | vs Frequency       | Figure 46 |

| Harmonic                    | $HD_3$ , $G = 6$ dB, $V_{OD} = 1$ $V_{PP}$ | vs Frequency       | Figure 47 |

|                             | $HD_2$ , $G = 10 dB$ , $V_{OD} = 1 V_{PP}$ | vs Frequency       | Figure 48 |

| Distortion                  | $HD_3$ , $G = 10 dB$ , $V_{OD} = 1 V_{PP}$ | vs Frequency       | Figure 49 |

|                             | $HD_2$ , $G = 14 dB$ , $V_{OD} = 1 V_{PP}$ | vs Frequency       | Figure 50 |

|                             | $HD_3$ , $G = 14 dB$ , $V_{OD} = 1 V_{PP}$ | vs Frequency       | Figure 51 |

|                             | $IMD_2$ , G = 6 dB, $V_{OD}$ = 1 $V_{PP}$  | vs Frequency       | Figure 52 |

|                             | $IMD_3$ , $G = 6 dB$ , $V_{OD} = 1 V_{PP}$ | vs Frequency       | Figure 53 |

| Intermodulation             | $IMD_2$ , G = 10 dB, $V_{OD}$ = 1 $V_{PP}$ | vs Frequency       | Figure 54 |

| Distortion                  | $IMD_3$ , G = 10 dB, $V_{OD}$ = 1 $V_{PP}$ | vs Frequency       | Figure 55 |

|                             | $IMD_2$ , G = 14 dB, $V_{OD}$ = 1 $V_{PP}$ | vs Frequency       | Figure 56 |

|                             | $IMD_3$ , G = 14 dB, $V_{OD}$ = 1 $V_{PP}$ | vs Frequency       | Figure 57 |

| 0                           | OIP <sub>2</sub>                           | vs Frequency       | Figure 58 |

| Output Intercept Point      | OIP <sub>3</sub>                           | vs Frequency       | Figure 59 |

| 0.1 dB Flatness             | ,                                          | ,                  | Figure 60 |

| S-Parameters                |                                            | vs Frequency       | Figure 61 |

| Transition Rate             |                                            | vs Output Voltage  | Figure 62 |

| Transient Response          |                                            |                    | Figure 63 |

| Settling Time               |                                            |                    | Figure 64 |

| Output Voltage Swing        |                                            | vs Load Resistance | Figure 65 |

| Rejection Ratio             |                                            | vs Frequency       | Figure 66 |

| Overdrive Recovery          |                                            |                    | Figure 67 |

| Output Impedance            |                                            | vs Frequency       | Figure 68 |

| Turnoff Time                |                                            |                    | Figure 69 |

| Turnon Time                 |                                            |                    | Figure 70 |

| Output Balance Error        |                                            | vs Frequency       | Figure 71 |

| Noise Figure                |                                            | vs Frequency       | Figure 72 |

| CM Input Impedance          |                                            | vs Frequency       | Figure 73 |

Product Folder Links: THS4509

Submit Documentation Feedback

# Typical Characteristics: $V_{S+} - V_{S-} = 3 \text{ V (continued)}$

# Table 2. Table of Graphs (continued)

|                                    |                     | FIGURE    |

|------------------------------------|---------------------|-----------|

| Differential Output Offset Voltage | vs CM Input Voltage | Figure 74 |

| Output Common-Mode Offset          | vs CM Input Voltage | Figure 75 |

Copyright © 2005–2016, Texas Instruments Incorporated

Submit Documentation Feedback

Copyright © 2005–2016, Texas Instruments Incorporated Submit Documentation Feedback

Figure 75. Output Common-Mode Offset vs CM Input Voltage

Submit Documentation Feedback

Copyright © 2005–2016, Texas Instruments Incorporated

# 8 Detailed Description

#### 8.1 Overview

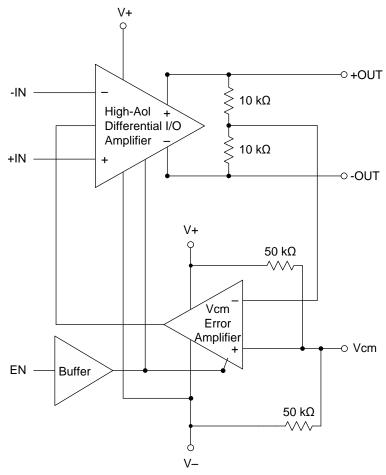

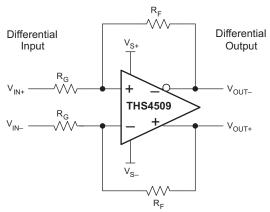

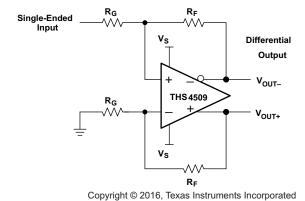

The THS4509 is a fully differential amplifier with integrated common-mode control designed to provide low distortion amplification to wide bandwidth differential signals. The common-mode feedback circuit sets the output common-mode voltage independent of the input common mode, as well as forcing the V+ and V – outputs to be equal in magnitude and opposite in phase, even when only one of the inputs is driven as in single to differential conversion.

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

# 8.3 Feature Description

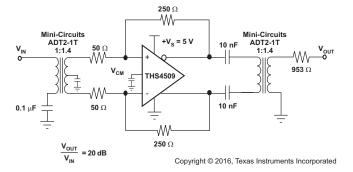

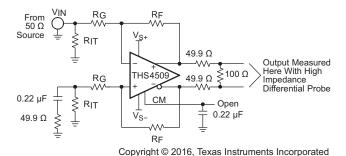

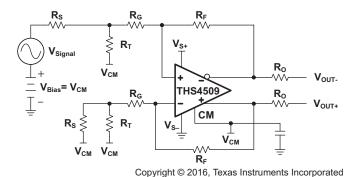

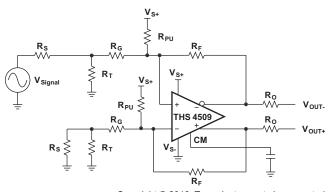

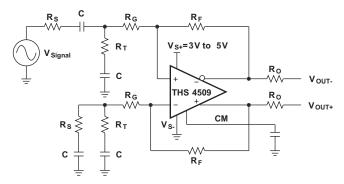

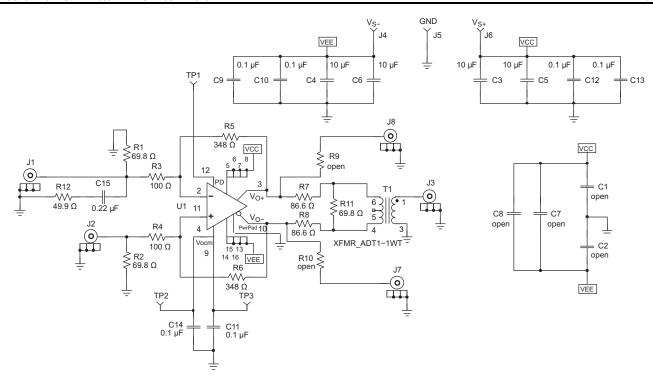

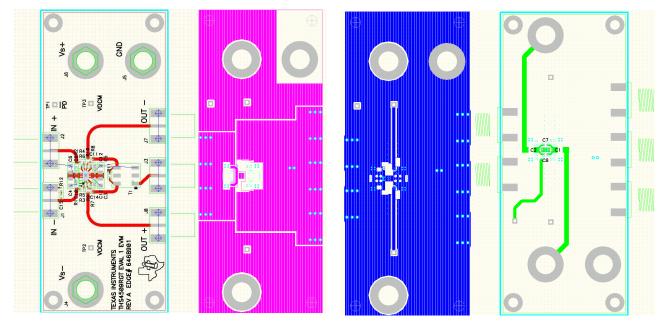

#### 8.3.1 Test Circuits

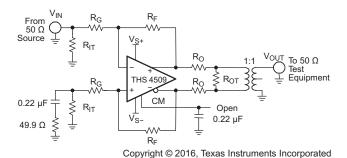

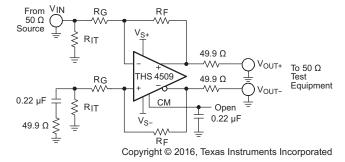

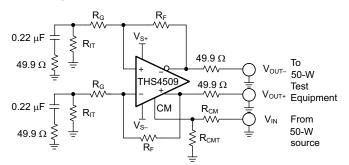

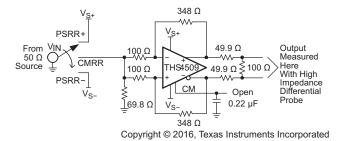

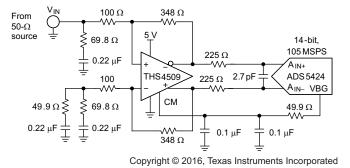

The THS4509 is tested with the following test circuits built on the evaluation module (EVM). For simplicity, power-supply decoupling is not shown—see *Layout* for recommendations. Depending on the test conditions, component values are changed per Table 3 and Table 4, or as otherwise noted. The signal generators used are AC-coupled,  $50-\Omega$  sources, and a  $0.22-\mu$ F capacitor and  $49.9-\Omega$  resistor to ground are inserted across  $R_{IT}$  on the alternate input to balance the circuit. A split power supply is used to ease the interface to common test equipment, but the amplifier can be operated single-supply as described in *Typical Applications* with no impact on performance.

### **Feature Description (continued)**

**Table 3. Gain Component Values**

| GAIN  | R <sub>F</sub> | R <sub>G</sub> | R <sub>IT</sub> |

|-------|----------------|----------------|-----------------|

| 6 dB  | 348 Ω          | 165 Ω          | 61.9 Ω          |

| 10 dB | 348 Ω          | 100 Ω          | 69.8 Ω          |

| 14 dB | 348 Ω          | 56.2 Ω         | 88.7 Ω          |

| 20 dB | 348 Ω          | 16.5 Ω         | 287 Ω           |

Note the gain setting includes 50- $\Omega$  source impedance. Components are chosen to achieve gain and 50- $\Omega$  input termination.

**Table 4. Load Component Values**

| $R_L$ | R <sub>O</sub> | R <sub>OT</sub> | ATTEN.  |

|-------|----------------|-----------------|---------|

| 100 Ω | 25 Ω           | Open            | 6 dB    |

| 200 Ω | 86.6 Ω         | 69.8 Ω          | 16.8 dB |

| 499 Ω | 237 Ω          | 56.2 Ω          | 25.5 dB |

| 1k Ω  | 487 Ω          | 52.3 Ω          | 31.8 dB |

Note the total load includes 50- $\Omega$  termination by the test equipment. Components are chosen to achieve load and 50- $\Omega$  line termination through a 1:1 transformer.

Due to the voltage divider on the output formed by the load component values, the amplifier output is attenuated. The column *Atten* in Table 4 shows the attenuation expected from the resistor divider. When using a transformer at the output as shown in Figure 77, the signal sees slightly more loss, and these numbers are approximate.

#### 8.3.1.1 Frequency Response

The circuit shown in Figure 76 is used to measure the frequency response of the circuit.

Figure 76. Frequency Response Test Circuit

A network analyzer is used as the signal source and as the measurement device. The output impedance of the network analyzer is 50  $\Omega$ .  $R_{IT}$  and  $R_{G}$  are chosen to impedance match to 50  $\Omega$ , and to maintain the proper gain. To balance the amplifier, a 0.22- $\mu$ F capacitor and 49.9- $\Omega$  resistor to ground are inserted across  $R_{IT}$  on the alternate input.

The output is probed using a high-impedance differential probe across the  $100-\Omega$  resistor. The gain is referred to the amplifier output by adding back the 6-dB loss due to the voltage divider on the output.

#### 8.3.1.2 Distortion and 1-dB Compression

The circuit shown in Figure 77 is used to measure harmonic distortion, intermodulation distortion, and 1-db compression point of the amplifier.

### Feature Description (continued)

Figure 77. Distortion Test Circuit