**TDES4940**

SNLS747 - NOVEMBER 2023

# TDES4940 4K V<sup>3</sup>Link Enhanced Video to Embedded DisplayPort Bridge Deserializer

#### 1 Features

- DisplayPort (DP) / Embedded DisplayPort (eDP) Transmitter

- VESA DP v1.4a/eDP v1.4b transmitter

- HBR3/HBR2/HBR/RBR Link Bit Rates

- Main link: 1, 2, or 4 lanes

- Each lane up to 8.1Gbps

- AUX CH 1Mbps

- Hot Plug Detect (HPD)

- Extracts aggregated video streams to local eDP

- Designed for 4 K @ 60 Hz video resolution

- Stream synchronization and splitting

- V<sup>3</sup>Link enhanced video interface

- 13.5/12.528/10.8/6.75/3.375 Gbps per Channel; Up to 27 Gbps over dual channels

- Coax/STP interconnect support

- Selectable 1, 2 channels

- Daisy-chain and splitting

- Adaptive equalization

- Ultra-low latency control channel

- Two fast-mode plus I2C up to 1 MHz (up to 3.4 MHz local bus access)

- High-speed GPIOs

- Supports SPI and UART pass through GPIOs

- Compatibility

- Integrated HDCP v1.4 with on-chip keys

- V<sup>3</sup>Link video and V<sup>3</sup>Link enhanced video product families

- Image enhancement (white balance and dithering)

- Security and diagnostics

- Voltage and temperature monitoring

- BIST and pattern generation

- CRC and error diagnostics

- ECC on control bits

- Unique ID for counterfeit protection

- Advanced link robustness and EMC control

- Spread spectrum clocking generation (SSCG)

- Adaptive Receiver Equalization (AEQ)

- Low power operation

- 1.8V and 1.15V dual power supply

- Qualifications

- ISO 10605 and IEC 61000-4-2 ESD compliant

- Temperature: -20°C to +85°C

## 2 Applications

- High resolution display:

- Operating room displays

- Seat back entertainment displays

- High resolution HMI

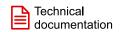

## 3 Description

The TDES4940 is a V<sup>3</sup>Link Enhanced Video to DisplayPort (DP) / Embedded DisplayPort (eDP) bridge device. In conjunction with a V3Link Enhanced Video serializer, the chipset receives a high-speed serialized interface over low-cost 50  $\Omega$  coax or STP/STQ cables. The TDES4940 is a VESA DP v1.4a/eDP v1.4b compatible device that supports advanced features such as HBR3, and SuperFrame formats. The device supports video resolutions of 4K 30-bit color and higher. The V<sup>3</sup>Link Enhanced Video supports video and audio data transmission and full duplex control, including I2C, and GPIO data over the same link. Consolidation of video data and control over V<sup>3</sup>Link Enhanced Video lanes reduces the interconnect size and weight and simplifies system design. EMI is minimized by the use of low voltage differential signaling, data scrambling, and randomization. In compatible V<sup>3</sup>Link mode, the device supports up to 2K resolutions with 24-bit color depth over a single/dual link as well as HDCP v1.4 support when paired with an HDCP capable serializer.

#### **Device Information**

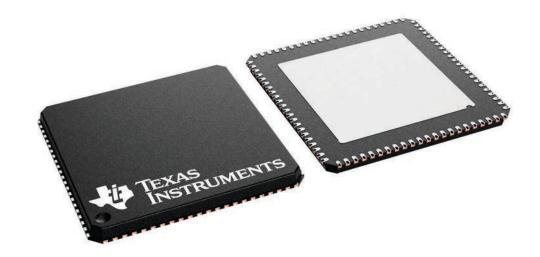

| PART NUMBER | PACKAGE (1) | BODY SIZE (NOM) |

|-------------|-------------|-----------------|

| TDES4940    | VQFNP (88)  | 12 mm × 12 mm   |

For all available packages, see the orderable addendum at the end of the data sheet.

## 4 Device and Documentation Support

## **4.1 Documentation Support**

#### 4.1.1 Related Documentation

For related documentation see the following:

- Soldering Specifications Application Report, SNOA549

- IC Package Thermal Metrics Application Report, SPRA953

- Leadless Leadframe Package (LLP) Application Report, SNOA401

#### 4.2 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 4.3 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

## 4.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 4.5 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

Product Folder Links: TDES4940

## 5 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Copyright © 2023 Texas Instruments Incorporated

## 5.1 Package Option Addendum

**Packaging Information**

| Orderable Device | Status | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan        | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking |

|------------------|--------|-----------------|--------------------|------|----------------|-----------------|------------------|---------------------|--------------|----------------|

| TDES4940RURTQ1   | ACTIVE | VQFN            | RUR0088D           | 88   | 250            | RoHS &<br>Green | NiPdAuAg         | Level-3-260C-168 HR | -20 to 85    | TDES4940       |

| TDES4940RURRQ1   | ACTIVE | VQFN            | RUR0088D           | 88   | 2500           | RoHS &<br>Green | NiPdAuAg         | Level-3-260C-168 HR | -20 to 85    | TDES4940       |

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: *TDES4940*

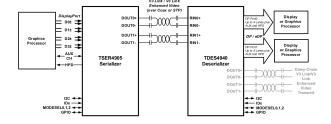

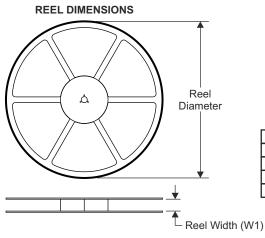

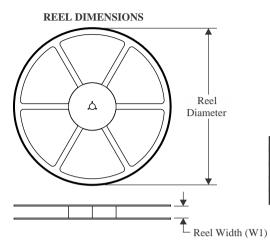

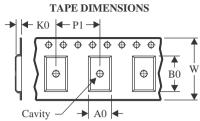

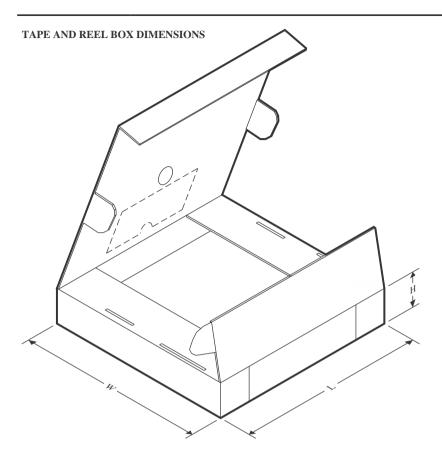

## 5.2 Tape and Reel Information

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

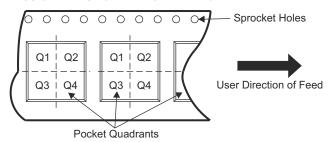

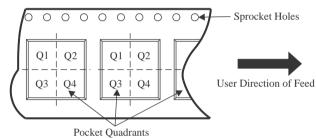

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Reel Width W1 Reel Package Drawing Pin1 Package A0 В0 K0 Р1 w Pins Device SPQ Diamete Туре (mm) (mm) Quadrant (mm) (mm) (mm) (mm) (mm) RUR0088 TDES4940RURTQ1 VQFN 12.30 12.30 24.00 Q2 88 250 180 24.4 1.10 16.00 TDES4940RURRQ1 VQFN RUR0088 2500 330 24.4 12.30 12.30 1.10 16.00 24.00 Q2

Copyright © 2023 Texas Instruments Incorporated

Product Folder Links: *TDES4940*

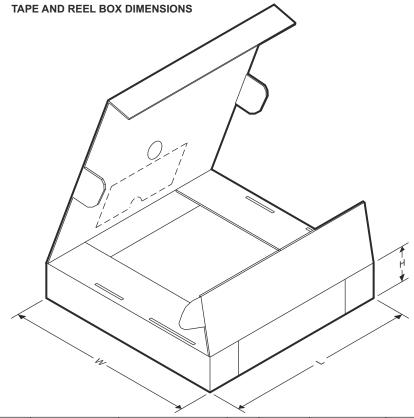

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TDES4940RURTQ1 | VQFN         | RUR0088D        | 88   | 250  | 210         | 185        | 35          |

| TDES4940RURRQ1 | VQFN         | RUR0088D        | 88   | 2500 | 360         | 360        | 36          |

| TDES4940RURRQ1 | VQFN         | RUR0088D        | 88   | 2500 | 367         | 367        | 35          |

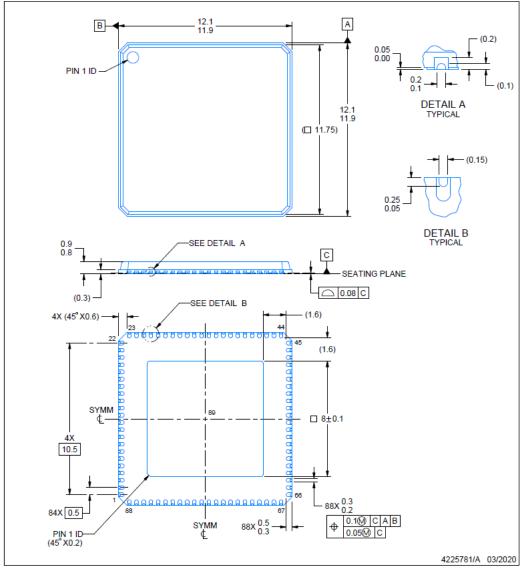

# RUR0088D

## PACKAGE OUTLINE

## VQFNP - 0.9 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

This drawing is subject to change without notice.

The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

Product Folder Links: TDES4940

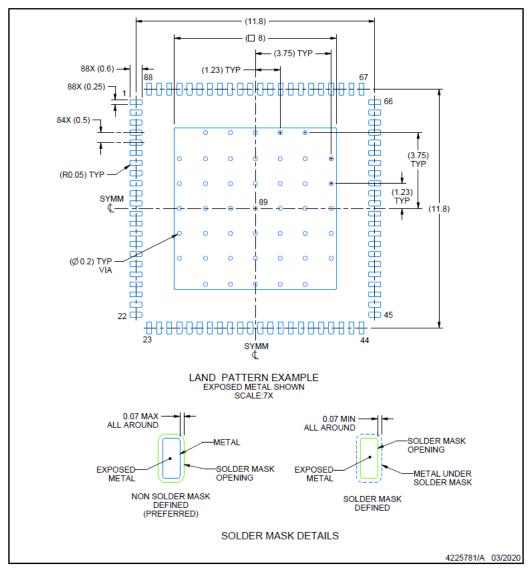

## **EXAMPLE BOARD LAYOUT**

## RUR0088D

## VQFNP - 0.9 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown

- on this view. It is recommended that vias under paste be filled, plugged or tented.

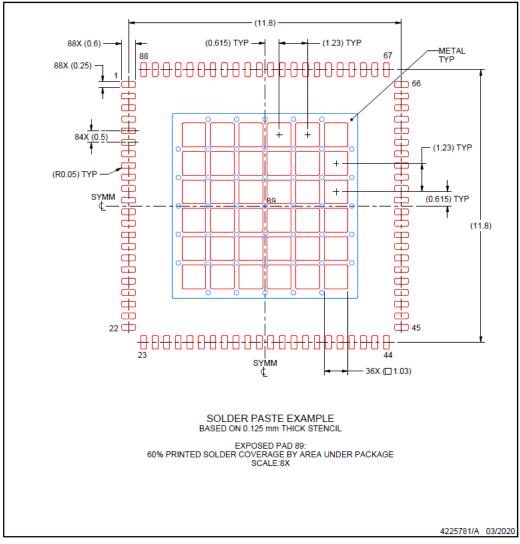

## **EXAMPLE STENCIL DESIGN**

## RUR0088D

## VQFNP - 0.9 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

Product Folder Links: TDES4940

Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                 |              |              |

| TDES4940RURR          | Active | Production    | VQFNP (RUR)   88 | 2500   LARGE T&R      | Yes  | NIPDAUAG      | Level-3-260C-168 HR | -20 to 85    | TDES4940     |

| TDES4940RURR.A        | Active | Production    | VQFNP (RUR)   88 | 2500   LARGE T&R      | Yes  | NIPDAUAG      | Level-3-260C-168 HR | -20 to 85    | TDES4940     |

| TDES4940RURT          | Active | Production    | VQFNP (RUR)   88 | 250   SMALL T&R       | Yes  | NIPDAUAG      | Level-3-260C-168 HR | -20 to 85    | TDES4940     |

| TDES4940RURT.A        | Active | Production    | VQFNP (RUR)   88 | 250   SMALL T&R       | Yes  | NIPDAUAG      | Level-3-260C-168 HR | -20 to 85    | TDES4940     |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 30-Nov-2023

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TDES4940RURR | VQFNP           | RUR                | 88 | 2500 | 330.0                    | 24.4                     | 12.3       | 12.3       | 1.1        | 16.0       | 24.0      | Q2               |

| TDES4940RURT | VQFNP           | RUR                | 88 | 250  | 180.0                    | 24.4                     | 12.3       | 12.3       | 1.1        | 16.0       | 24.0      | Q2               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 30-Nov-2023

## \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TDES4940RURR | VQFNP        | RUR             | 88   | 2500 | 367.0       | 367.0      | 35.0        |

| TDES4940RURT | VQFNP        | RUR             | 88   | 250  | 210.0       | 185.0      | 35.0        |

12 x 12, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated