# TCAN5102-Q1 Automotive Self-supplied CAN FD Light Responder to SPI, UART, or I<sup>2</sup>C Controller

## 1 Features

- AEC-Q100: Qualified for automotive applications

- CAN FD Light Responder meets ISO 11898-1:202x

- Supports CAN FD Light data rates up to 5Mbps when using TCAN4562-Q1 CAN FD Light Commander

- Ability to control external CAN transceiver such as: TCAN1162x-Q1, TCAN1043A, TCAN1463A

- Programmable via CAN bus

- 3.3V to 5V Supply voltage

- SPI controller support for up to 20MHz with up to 8 chip selects

- UART controller support for up to 2.5 Mbaud

- I<sup>2</sup>C controller supports fast mode plus (1MHz)

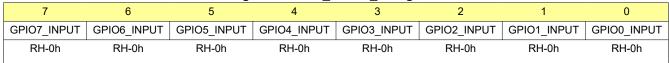

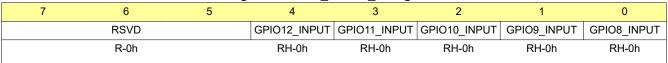

- 13 GPIOs which can be muxed with other functionality

- Programmable PWM output with trapezoidal ramp profile support for motor control

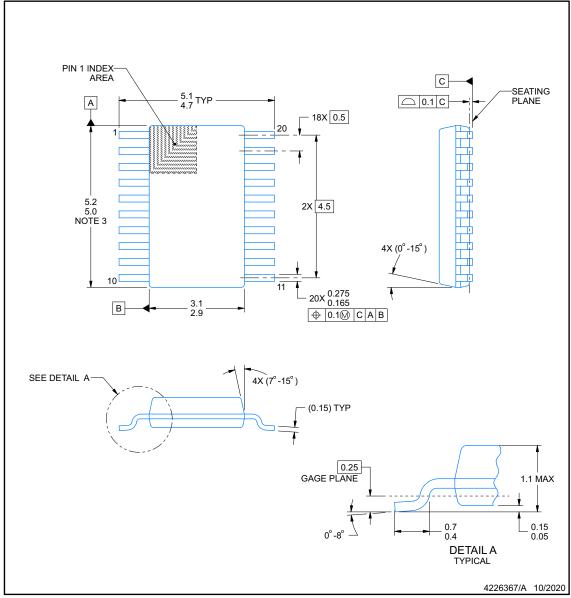

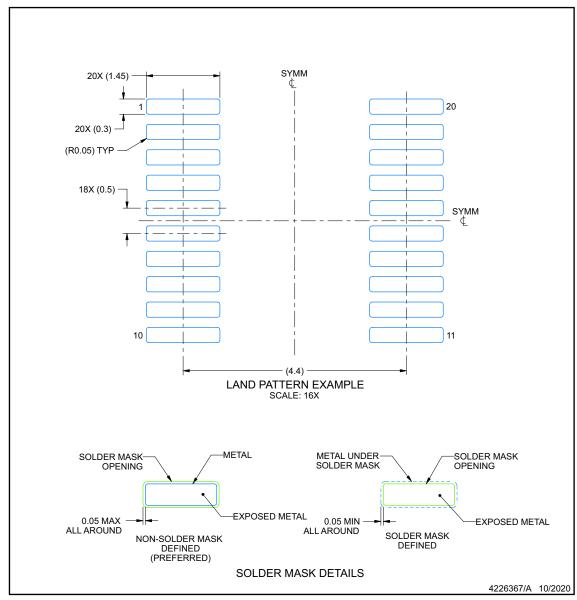

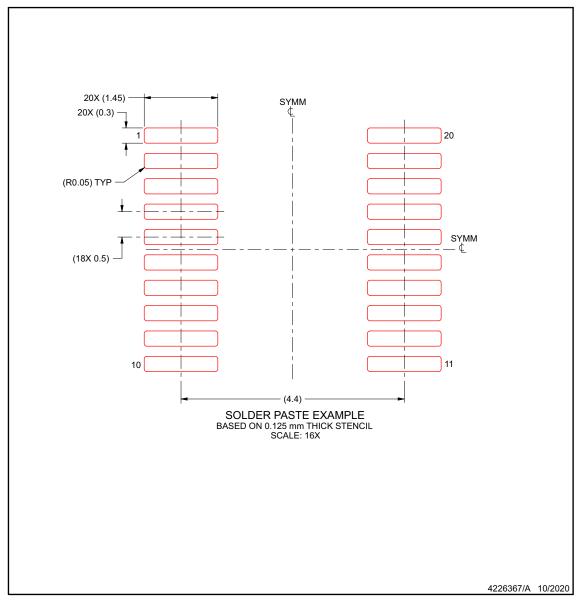

- 20-pin VSSOP (DGQ) package

# 2 Applications

- · Body electronics and lighting

- · Hybrid, electric and powertrain systems

- Infotainment and cluster

- Appliances

# 3 Description

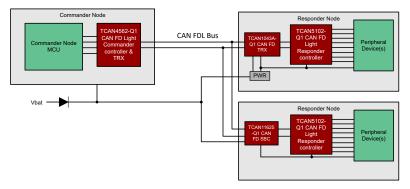

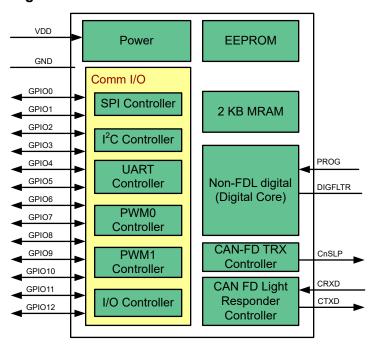

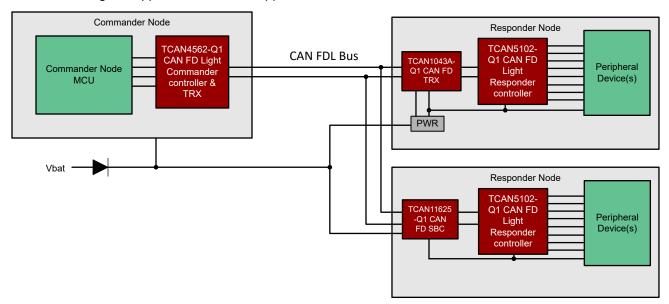

The TCAN5102-Q1 is a Control Area Network (CAN) Flexible Data (FD) Light responder device compatible with CiA 604-1 and ISO 11898-1:2024, capable of supporting up to 5Mbps data rate when a dedicated CAN FD light commander is used. The device is designed to support CAN FD light responder node applications in a commander - responder architecture which does not require a responder node processor. All control to the responder node is through the CAN bus from the commander node processor which eliminates the need for responder node processor and software.

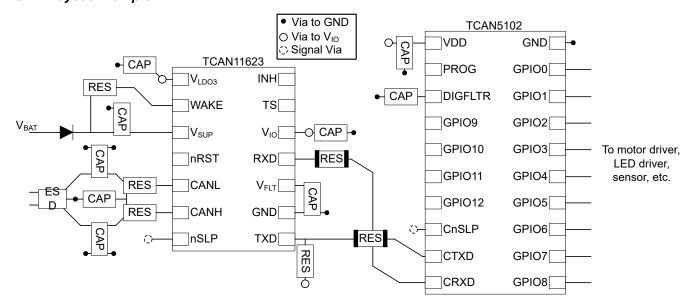

The device receives data and/or commands from a CAN FD light commander node which translates these to either Serial Peripheral Interface (SPI) controller, UART controller, I2C controller, and/or GPIO pins communication to the device and/or peripheral devices the TCAN5102-Q1 is controlling. PWM output channels also support trapezoidal ramp profiles in hardware for controlling stepper motors. Ramping of duty cycle or frequency is possible. No external crystal or clock is required. The device controls the external TCAN1162x-Q1, TCAN1043A-Q1 or TCAN1463A-Q1 CAN FD (SIC) transceivers for system level flexibility. The device relys upon the CAN FD transceiver/SBC to control the node power and communicate a wake up signal to the TCAN5102-Q1 by latching the CAN RXD (CRXD) pin low.

#### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| TCAN5102-Q1 | 20-Pin (VSSOP,<br>DGQ) | 5.1mm × 4.9mm               |

- (1) For more information, see Section 11.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

**CAN FD Light Commander-Responder Application**

# **Table of Contents**

| 1 Features                                   | 1              | 7.4 Device Functional Modes                     | 18               |

|----------------------------------------------|----------------|-------------------------------------------------|------------------|

| 2 Applications                               |                | 7.5 Programming                                 |                  |

| 3 Description                                |                | 7.6 Register Maps                               | 54               |

| 4 Pin Configuration and Functions            | 3              | 8 Application and Implementation                |                  |

| 5 Specifications                             |                | 8.1 Application Information                     | 224              |

| 5.1 Absolute Maximum Ratings                 |                | 8.2 Typical Application                         |                  |

| 5.2 ESD Ratings                              |                | 8.3 Power Supply Recommendations                |                  |

| 5.3 Recommended Operating Conditions         | 4              | 8.4 Layout                                      | 225              |

| 5.4 Thermal Information                      | 4              | 9 Device and Documentation Support              | 227              |

| 5.5 Supply Characteristics                   | <mark>5</mark> | 9.1 Documentation Support                       | 227              |

| 5.6 Electrical Characteristics               | <mark>5</mark> | 9.2 Receiving Notification of Documentation Upd | ates227          |

| 5.7 Timing Requirements                      | 6              | 9.3 Support Resources                           | 227              |

| 5.8 Switching Characteristics                | <mark>7</mark> | 9.4 Trademarks                                  | 227              |

| 5.9 I <sup>2</sup> C Bus Timing Requirements | 8              | 9.5 Electrostatic Discharge Caution             | 227              |

| 6 Parameter Measurement Information          | 10             | 9.6 Glossary                                    | 227              |

| 7 Detailed Description                       | 13             | 10 Revision History                             | <mark>227</mark> |

| 7.1 Overview                                 | 13             | 11 Mechanical, Packaging, and Orderable         |                  |

| 7.2 Functional Block Diagram                 | 13             | Information                                     | <mark>227</mark> |

| 7.3 Feature Description                      | 15             | 11.1 Mechanical Data                            | 228              |

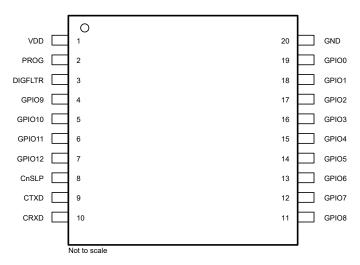

# 4 Pin Configuration and Functions

Figure 4-1. DGQ 20-PIN (Top View)

**Table 4-1. Pin Functions**

| PIN                 |     | TYPE(1) | DESCRIPTION                                                                                          |  |

|---------------------|-----|---------|------------------------------------------------------------------------------------------------------|--|

| NAME                | NO. | ITPE    | DESCRIPTION                                                                                          |  |

| VDD                 | 1   | Р       | Device power input, 3.3V or 5V                                                                       |  |

| PROG                | 2   | ı       | Input for device configuration and debug                                                             |  |

| DIGFLTR             | 3   | Р       | Digital power supply filter pin                                                                      |  |

| GPIO9/CS4/SCL       | 4   | I/O     | General purpose input/output pin, SPI chip select channel 4 output, or I <sup>2</sup> C clock output |  |

| GPIO10/CS5/SDA      | 5   | I/O     | General purpose input/output pin, SPI chip select channel 5 output, or I <sup>2</sup> C data pin     |  |

| GPIO11/CS6/PWM0     | 6   | I/O     | General purpose input/output pin, SPI chip select channel 6 output, or PWM0 output                   |  |

| GPIO12/CS7/<br>PWM1 | 7   | I/O     | General purpose input/output pin, SPI chip select channel 6 output, or PWM1 output                   |  |

| CnSLP               | 8   | 0       | CAN transceiver control output pin (nSLP)                                                            |  |

| CTXD                | 9   | 0       | CAN transceiver TXD output pin (connects to transceiver's TXD input pin)                             |  |

| CRXD                | 10  | ı       | CAN transceiver RXD input pin (connects to transceiver's RXD output pin)                             |  |

| GPIO8/URXD          | 11  | I/O     | General purpose input/output pin or UART RXD input                                                   |  |

| GPIO7/UTXD          | 12  | I/O     | General purpose input/output pin or UART TXD output                                                  |  |

| GPIO6/PICO          | 13  | I/O     | General purpose input/output pin or SPI peripheral in, controller out output                         |  |

| GPIO5/POCI          | 14  | I/O     | General purpose input/output pin or SPI peripheral out, controller in input                          |  |

| GPIO4/SCK           | 15  | I/O     | General purpose input/output pin or SPI clock output                                                 |  |

| GPIO3/CS0           | 16  | I/O     | General purpose input/output pin or SPI chip select channel 0 output                                 |  |

| GPIO2/CS1           | 17  | I/O     | General purpose input/output pin or SPI chip select channel 1 output                                 |  |

| GPIO1/CS2           | 18  | I/O     | General purpose input/output pin or SPI chip select channel 2 output                                 |  |

| GPIO0/CS3           | 19  | I/O     | eneral purpose input/output pin or SPI chip select channel 3 output                                  |  |

| GND                 | 20  | Р       | Ground pin                                                                                           |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# Note

For pins that have multiple functions see the IO\_CFG registers to configure the pins and see Section 7.3.4 for more information about the pin muxing.

# **5 Specifications**

# 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                | MIN  | MAX | UNIT |

|------------------------|--------------------------------|------|-----|------|

| VDD                    | Supply input                   | -0.3 | 6   | V    |

| DIGFLTR                | Digital core filter pin        | -0.3 | 1.8 | V    |

| V <sub>LOGIC_IN</sub>  | Logic pin input voltage range  | -0.3 | 6   | V    |

| V <sub>LOGIC_OUT</sub> | Logic pin output voltage range | -0.5 | 6   | V    |

| I <sub>O(LOGIC)</sub>  | Logic pin output current       |      | 12  | mA   |

| TJ                     | Junction temperature           | -40  | 150 | °C   |

| T <sub>stg</sub>       | Storage temperature            | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute MaximumRatings do not imply functional operation of the device at these or any other conditions beyond those listed underRecommended Operating Conditions. If used outside the Recommended Operating Conditions but within theAbsolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability,functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|             |                                                                |                                                                                                 |             | VALUE | UNIT |

|-------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------|-------|------|

|             | Human body model (HBM) Classifi<br>AEC Q100-002 <sup>(1)</sup> | Human body model (HBM) Classification Level 3A, all other pins, per AEC Q100-002 <sup>(1)</sup> |             |       |      |

| $V_{(ESD)}$ | Electrostatic discharge                                        | Charged device model (CDM)                                                                      | Corner pins | ±750  | V    |

|             |                                                                | Classifcation Level C5, per AEC Q100-011                                                        | Other pins  | ±750  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                        |                                                    | MIN   | NOM | MAX | UNIT |

|------------------------|----------------------------------------------------|-------|-----|-----|------|

| VDD                    | Supply voltage                                     | 3.0   |     | 5.5 | V    |

| I <sub>OH(DO)</sub>    | Digital output high level current                  | -12   |     |     | mA   |

| I <sub>OL(DO)</sub>    | Digital output low level current                   |       |     | 12  | mA   |

| C <sub>(VDD)</sub>     | VDD supply capacitance                             | 1     |     |     | μF   |

| C <sub>(DIGFLTR)</sub> | Digitial core filter pin capacitance               | 0.33  | 1   |     | μF   |

| ESR <sub>CO</sub>      | Supply and filter pin ESR capacitance requirements | 0.001 |     | 1   | Ω    |

| T <sub>J</sub>         | Operating junction temperature range               | -40   |     | 125 | °C   |

# 5.4 Thermal Information

|                        | THERMAL METRIC(1)                            | RGY (QFN) | UNIT |

|------------------------|----------------------------------------------|-----------|------|

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 31.8      | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 11.8      | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 21.4      | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.8       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.3       | °C/W |

# 5.4 Thermal Information (continued)

| THERMAL METRIC(1)                                            | RGY (QFN)<br>24-PINS | UNIT |

|--------------------------------------------------------------|----------------------|------|

| Ψ <sub>JB</sub> Junction-to-board characterization parameter | 11.8                 | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 5.5 Supply Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                | TEST CONDITIONS                                                                                                            | MIN      | TYP | MAX  | UNIT |

|---------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------|-----|------|------|

| VDD                 |                                          |                                                                                                                            | <u> </u> |     |      |      |

| IDD                 | VDD supply current device in normal mode | Normal mode; VDD = 5 V<br>I <sub>I</sub> = 0, 0 V or VDD<br>SPI, UART, I2C disabled                                        |          | 1.4 | 1.8  | mA   |

|                     |                                          | Normal mode; VDD = 3.3 V<br>I <sub>I</sub> = 0, 0 V or VDD<br>SPI, UART, I2C disabled                                      |          | 1.4 | 1.8  | mA   |

|                     | VDD supply current device in sleep mode  | Sleep mode; VDD = 5 V<br>$I_1$ = 0, 0 V or VDD<br>-40 °C $\leq$ T <sub>J</sub> $\leq$ 85 °C                                |          | 10  | 20   | μΑ   |

| IDD                 |                                          | Sleep mode; VDD = 5 V<br>I <sub>I</sub> = 0, 0 V or VDD<br>T <sub>J</sub> > 85 °C                                          |          | 20  | 60   | μA   |

| טטו                 |                                          | Sleep mode; VDD = $3.3 \text{ V}$<br>$I_1 = 0, 0 \text{ V or VDD}$<br>$-40 \text{ °C} \leq T_J \leq 85 \text{ °C}$         |          | 10  | 20   | μΑ   |

|                     |                                          | Sleep mode; VDD = $3.3 \text{ V}$<br>I <sub>I</sub> = $0$ , $0 \text{ V or VDD}$<br>T <sub>J</sub> > $85 ^{\circ}\text{C}$ |          | 20  | 60   | μΑ   |

| UV <sub>DDR</sub>   | Supply undervoltage rising threshold     | VDD rising                                                                                                                 | 2.35     |     | 2.95 | V    |

| UV <sub>DDF</sub>   | Supply undervoltage falling threshold    | VDD falling                                                                                                                | 2.1      |     | 2.7  | V    |

| UV <sub>DDHYS</sub> | Supply undervoltage detection hysteresis |                                                                                                                            |          | 350 | 430  | mV   |

# 5.6 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                        | TEST CONDITIONS                                        | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------|--------------------------------------------------------|-----|-----|-----|------|

| GPIOs (Ir       | nputs)                           | 1                                                      |     |     |     |      |

|                 |                                  | GPIOx pins                                             | 0.7 |     |     |      |

| $V_{IH}$        | High-level input voltage         | CRXD pin                                               | 0.7 |     |     | VDD  |

|                 |                                  | PROG pin                                               | 0.7 |     |     |      |

|                 |                                  | GPIOx pins                                             |     |     | 0.3 |      |

| $V_{IL}$        | Low-level input voltage          | CRXD pin                                               |     |     | 0.3 | VDD  |

|                 |                                  | PROG pin                                               |     |     | 0.3 |      |

|                 |                                  | GPIOx pins Input = VDD Pull-up/down resistors disabled | -1  |     | 1   |      |

| I <sub>IH</sub> | High-level input leakage current | CRXD pin<br>Input = VDD                                | -1  |     | 1   | μΑ   |

|                 |                                  | PROG pin<br>Input = VDD                                |     | 90  | 140 |      |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

# **5.6 Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                       | TEST CONDITIONS                                        | MIN        | TYP  | MAX | UNIT |

|-----------------------|---------------------------------|--------------------------------------------------------|------------|------|-----|------|

|                       |                                 | GPIOx pins Input = 0 V Pull-up/down resistors disabled | -1         |      | 1   |      |

| I <sub>IL</sub>       | Low-level input leakage current | PROG pins<br>Input = 0 V                               | -1         |      | 1   | μΑ   |

|                       |                                 | CRXD<br>Input = 0 V                                    | -140       | -90  |     |      |

|                       |                                 | 20 MHz, GPIOx pins                                     |            | 4    | 10  |      |

| $C_{IN}$              | Input Capacitance               | 1 MHz, CRXD pin                                        |            | 4    | 10  | pF   |

|                       |                                 | 1 MHz, PROG pin                                        |            | 4    | 10  |      |

| I <sub>LKG(OFF)</sub> | Unpowered leakage current       | GPIOx pins<br>Inputs = 5.5 V, VDD = 0 V                | <b>–1</b>  | 0    | 1   | μΑ   |

| В                     | Dull down Decistores            | GPIOx (if enabled)                                     | 40         | 60   | 80  | kΩ   |

| $R_{PD}$              | Pull-down Resistance            | PROG                                                   | 40         | 60   | 80  | K12  |

| D                     | Dull up Bosistanos              | GPIOx (if enabled)                                     | 40         | 60   | 80  | kΩ   |

| R <sub>PU</sub>       | Pull-up Resistance              | CRXD                                                   | 40         | 60   | 80  | K12  |

| GPIOs (Out            | puts)                           |                                                        |            |      |     |      |

| V <sub>OH</sub>       | High level output voltage       | GPIOx, CTXD, CnSLP pins I <sub>OH</sub> = 10 mA        | 0.7        | 0.85 |     | VDD  |

|                       |                                 | GPIOx, CTXD, CnSLP pins I <sub>OH</sub> = 2 mA         | 0.8        | 0.9  |     |      |

| V <sub>OL</sub>       | Low level output voltage        | GPIOx, CTXD, CnSLP pins I <sub>OL</sub> = -10 mA       |            | 0.15 | 0.3 | VDD  |

|                       |                                 | GPIOx, CTXD, CnSLP pins I <sub>OL</sub> = -2 mA        |            | 0.1  | 0.2 |      |

| I <sub>OH</sub>       | High level output current       | GPIOx, CTXD, CnSLP pins<br>V <sub>O</sub> = 0.7 VDD    | 10         | 12   |     | mA   |

| I <sub>OL</sub>       | Low Level output current        | GPIOx, CTXD, CnSLP pins<br>V <sub>O</sub> = 0.3 VDD    |            | -12  | -10 | mA   |

| I <sub>LKG(OFF)</sub> | Unpowered leakage current       | CTXD, CnSLP pins<br>VPIN = 5.5 V                       | <b>–</b> 5 |      | 5   | μΑ   |

| Thermal Sh            | utdown                          |                                                        |            |      | '   |      |

| TSD <sub>F</sub>      | Thermal shut down falling       |                                                        | 155        | 171  | 180 | °C   |

| TSD <sub>R</sub>      | Thermal shut down rising        |                                                        | 160        | 176  | 190 | °C   |

| TSD <sub>HYS</sub>    | Thermal shut down hysteresis    |                                                        | 2          | 5    | 10  | °C   |

|                       |                                 | 1                                                      |            |      |     |      |

# 5.7 Timing Requirements

|                           |                                                                                       | MIN | TYP | MAX | UNIT |

|---------------------------|---------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply                    |                                                                                       |     |     |     |      |

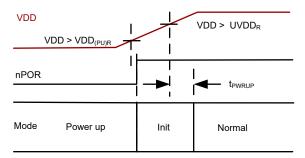

| t <sub>PWRUP</sub>        | Time after VDD exceeds POR for device to power up                                     |     |     | 2   | ms   |

| Mode Change               |                                                                                       |     |     |     |      |

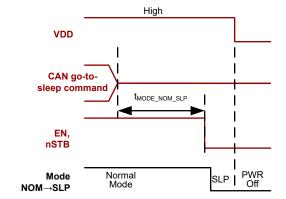

| t <sub>MODE_NOM_SLP</sub> | Time from Go-to-sleep command where device turns off CAN transceiver                  |     | 100 | 600 | μs   |

| Device Timing             |                                                                                       |     |     |     |      |

| t <sub>MODE_POR_NOM</sub> | Time from POR to normal mode, ready to receive CAN messages                           |     | 150 | 400 | μs   |

| SPI Timing Requirements   |                                                                                       |     |     |     |      |

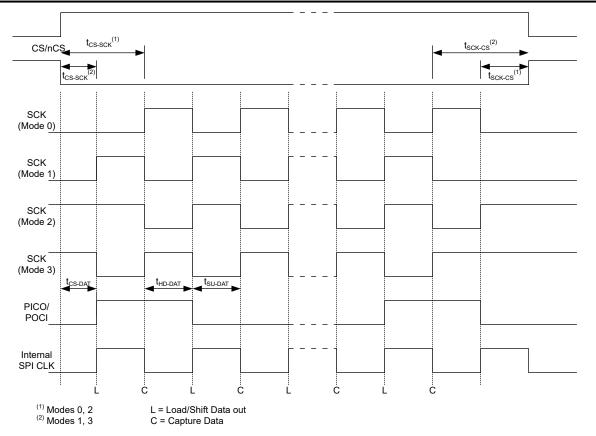

| t <sub>HD-DAT</sub>       | POCI input hold time requirement after active SCK edge See SPI Timing Characteristics | 20  |     |     | ns   |

# 5.7 Timing Requirements (continued)

|                     |                                                                                          | MIN  | TYP | MAX  | UNIT |

|---------------------|------------------------------------------------------------------------------------------|------|-----|------|------|

| t <sub>SU-DAT</sub> | POCI input set up time requirement before active SCK edge See SPI Timing Characteristics | 5    |     |      | ns   |

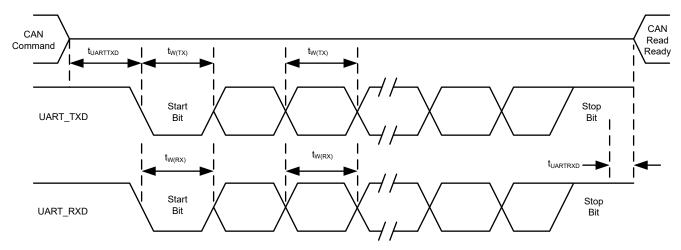

| UART                | ·                                                                                        |      |     |      |      |

| t <sub>W(RX)</sub>  | Pulse width, receive start, stop, data bit <sup>(1)</sup>                                | 0.97 | 1   | 1.04 | U    |

<sup>(1)</sup> U = UART baud time = 1/programmed baud rate

# **5.8 Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                                    | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT             |

|----------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------------------|

| SPI Switching        | Characteristics                                                                              |                                                                        |      |      |      |                  |

| f <sub>SCK-MAX</sub> | SCK, Maximum SPI clock frequency (1)                                                         | Normal mode; C <sub>L</sub> = 20 pF                                    |      | 20   |      | MHz              |

| t <sub>SCK-MIN</sub> | SCK, Minimum SPI clock period (1)                                                            | Normal mode; C <sub>L</sub> = 20 pF                                    |      | 50   |      | ns               |

| t <sub>SCKR</sub>    | SCK rise time <sup>(1)</sup>                                                                 | Normal mode; C <sub>L</sub> = 20 pF                                    |      | 4    | 10   | ns               |

| t <sub>SCKF</sub>    | SCK fall time (1)                                                                            | Normal mode; C <sub>L</sub> = 20 pF                                    |      | 4    | 8    | ns               |

| t <sub>SCKH</sub>    | SCK, SPI clock high (1)                                                                      | Normal mode                                                            | 0.47 | 0.49 | 0.5  | S <sup>(3)</sup> |

| t <sub>SCKL</sub>    | SCK, SPI clock low (1)                                                                       | Normal mode                                                            | 0.5  | 0.51 | 0.53 | S <sup>(3)</sup> |

| t <sub>sck-cs</sub>  | Delay time from last SCK edge to CS inactive (1)                                             | Normal mode<br>See SPI Timing Characteristics                          | 0.44 | 0.5  | 0.52 | S <sup>(3)</sup> |

| t <sub>CS-SCK</sub>  | Delay time from CS active to first SCK edge <sup>(1)</sup>                                   | Normal mode<br>See SPI Timing Characteristics                          | 0.49 | 0.5  | 0.57 | S <sup>(3)</sup> |

| t <sub>HD-DAT</sub>  | Data hold time from capture SCK edge to PICO data changing <sup>(1)</sup>                    | Normal mode<br>See SPI Timing Characteristics                          | 0.47 | 0.5  | 0.51 | S <sup>(3)</sup> |

|                      |                                                                                              | Normal mode<br>SPI Modes 0, 2<br>See SPI Timing Characteristics        |      | 0    | 5    | ns               |

| t <sub>CS-DV</sub>   | PICO data valid <sup>(1)</sup>                                                               | Normal mode<br>SPI Modes 1, 3<br>See SPI Timing Characteristics        |      | 0.5  | 0.57 | S <sup>(3)</sup> |

| I2C Switching        | Characteristics                                                                              |                                                                        |      |      |      |                  |

| tstuckbus_i2c        | The time for a bus line to be "stuck" low until the device considers the bus stuck.          |                                                                        | 25   | 40   | 65   | ms               |

| fsb_sclout_i2c       | I2C stuck bus recovery pattern clock frequency generated while attempting to unstick the bus |                                                                        | 5.5  | 8.5  | 14   | kHz              |

| UART                 |                                                                                              |                                                                        |      |      |      |                  |

| t <sub>baud</sub>    | Maximum UART baud rate                                                                       |                                                                        |      |      | 2.5  | MHz              |

| t <sub>UARTTXD</sub> | Time from Complete of CAN command to start of UART transmit                                  |                                                                        |      | 1    | 2    | U                |

| t <sub>UARTRXD</sub> | Time from UART reception to CAN read ready <sup>(1)</sup>                                    | End of last data/parity bit to UART.RXN bit set C <sub>L</sub> = 20 pF |      | 0.5  | 2    | U                |

| t <sub>W(TX)</sub>   | Pulse width, transmit start, stop, data bit <sup>(1)</sup> (2)                               | C <sub>L</sub> = 20 pF                                                 | 0.98 |      | 1.02 | U                |

- (1) Specified by design

- (2) U = UART baud time = 1/programmed baud rate

- (3) S = SPI clock period = 1/SPI clock frequency

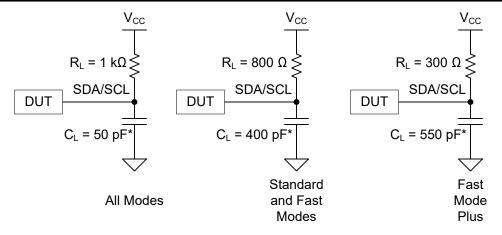

# 5.9 I<sup>2</sup>C Bus Timing Requirements

over operating free-air temperature range (unless otherwise noted)

|                       |                                                          |                                          | MIN                            | MAX  | UNIT |

|-----------------------|----------------------------------------------------------|------------------------------------------|--------------------------------|------|------|

| <sup>2</sup> C Bus -  | - Standard Mode                                          |                                          |                                |      |      |

| scl                   | I <sup>2</sup> C clock frequency                         |                                          | 0                              | 100  | kHz  |

| sch                   | I <sup>2</sup> C clock high time <sup>(1)</sup>          |                                          | 4                              |      | μs   |

| scl                   | I <sup>2</sup> C clock low time <sup>(1)</sup>           |                                          | 4.7                            |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                              |                                          |                                | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial-data setup time                  |                                          | 250                            |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial-data hold time                   |                                          | 0                              |      | ns   |

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time <sup>(1)</sup>          |                                          |                                | 1000 | ns   |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                         |                                          |                                | 300  | ns   |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time                        | 10-pF to 400-pF bus                      |                                | 300  | ns   |

| buf                   | I <sup>2</sup> C bus free time between stop and start    |                                          | 4.7                            |      | μs   |

| sts                   | I <sup>2</sup> C start or repeated start condition setup |                                          | 4.7                            |      | μs   |

| t <sub>sth</sub>      | I <sup>2</sup> C start or repeated start condition hold  |                                          | 4                              |      | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C stop condition setup                    |                                          | 4                              |      | μs   |

| t <sub>vd(data)</sub> | Valid data time                                          | SCL low to SDA output valid              |                                | 3.45 | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition                         | ACK signal from SCL low to SDA (out) low |                                | 3.45 | μs   |

| C <sub>b</sub>        | I <sup>2</sup> C bus capacitive load                     |                                          | 400                            | pF   |      |

| <sup>2</sup> C Bus -  | - Fast Mode                                              | -                                        |                                | -    |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                         |                                          | 0                              | 400  | kHz  |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time <sup>(1)</sup>          |                                          | 0.6                            |      | μs   |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time <sup>(1)</sup>           |                                          | 1.3                            |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                              |                                          |                                | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial-data setup time                  |                                          | 100                            |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial-data hold time                   |                                          | 0                              |      | ns   |

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time <sup>(1)</sup>          |                                          | 20                             | 300  | ns   |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                         |                                          | 20 × (V <sub>CC</sub> / 5.5 V) | 300  | ns   |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time                        | 10-pF to 400-pF bus                      | 20 × (V <sub>CC</sub> / 5.5 V) | 300  | ns   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between stop and start    |                                          | 1.3                            |      | μs   |

| t <sub>sts</sub>      | I <sup>2</sup> C start or repeated start condition setup |                                          | 0.6                            |      | μs   |

| t <sub>sth</sub>      | I <sup>2</sup> C start or repeated start condition hold  |                                          | 0.6                            |      | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C stop condition setup                    |                                          | 0.6                            |      | μs   |

| t <sub>vd(data)</sub> | Valid data time                                          | SCL low to SDA output valid              |                                | 0.9  | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition                         | ACK signal from SCL low to SDA (out) low |                                | 0.9  | μs   |

| C <sub>b</sub>        | I <sup>2</sup> C bus capacitive load                     |                                          |                                | 400  | pF   |

| <sup>2</sup> C Bus -  | - Fast Mode Plus                                         |                                          |                                |      |      |

| f <sub>scl</sub>      | I <sup>2</sup> C clock frequency                         | 0                                        | 1000                           | kHz  |      |

| t <sub>sch</sub>      | I <sup>2</sup> C clock high time <sup>(1)</sup>          | 0.26                                     |                                | μs   |      |

| t <sub>scl</sub>      | I <sup>2</sup> C clock low time <sup>(1)</sup>           |                                          | 0.5                            |      | μs   |

| t <sub>sp</sub>       | I <sup>2</sup> C spike time                              |                                          |                                | 50   | ns   |

| t <sub>sds</sub>      | I <sup>2</sup> C serial-data setup time                  |                                          | 50                             |      | ns   |

| t <sub>sdh</sub>      | I <sup>2</sup> C serial-data hold time                   |                                          | 0                              |      | ns   |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# 5.9 I<sup>2</sup>C Bus Timing Requirements (continued)

over operating free-air temperature range (unless otherwise noted)

|                       |                                                          |                                          | MIN                            | MAX  | UNIT |

|-----------------------|----------------------------------------------------------|------------------------------------------|--------------------------------|------|------|

| t <sub>icr</sub>      | I <sup>2</sup> C input rise time <sup>(1)</sup>          |                                          |                                | 120  | ns   |

| t <sub>icf</sub>      | I <sup>2</sup> C input fall time                         |                                          | 20 × (V <sub>CC</sub> / 5.5 V) | 120  | ns   |

| t <sub>ocf</sub>      | I <sup>2</sup> C output fall time                        | 10-pF to 550-pF bus                      | 20 × (V <sub>CC</sub> / 5.5 V) | 120  | ns   |

| t <sub>buf</sub>      | I <sup>2</sup> C bus free time between stop and start    |                                          | 0.5                            |      | μs   |

| t <sub>sts</sub>      | I <sup>2</sup> C start or repeated start condition setup | 0.26                                     |                                | μs   |      |

| t <sub>sth</sub>      | I <sup>2</sup> C start or repeated start condition hold  |                                          | 0.26                           |      | μs   |

| t <sub>sps</sub>      | I <sup>2</sup> C stop condition setup                    |                                          | 0.26                           |      | μs   |

| t <sub>vd(data)</sub> | Valid data time                                          | SCL low to SDA output valid              |                                | 0.45 | μs   |

| t <sub>vd(ack)</sub>  | Valid data time of ACK condition                         | ACK signal from SCL low to SDA (out) low |                                | 0.45 | μs   |

| C <sub>b</sub>        | I <sup>2</sup> C bus capacitive load                     |                                          | 550                            | pF   |      |

<sup>(1)</sup> This parameter is up to the system designer to ensure is met. It will vary depending on bus load and pull up resistance.

Copyright © 2025 Texas Instruments Incorporated

# **6 Parameter Measurement Information**

Figure 6-1. Power Up Timing

Figure 6-2. Normal Mode to Sleep Mode Timing

Figure 6-3. SPI Timing Characteristics

Figure 6-4. UART Timing Characteristics

\*C<sub>L</sub> includes probe and jig capacitance

Figure 6-5. I2C Bus Loading

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

# 7 Detailed Description

# 7.1 Overview

The TCAN5102-Q1 is a Control Area Network (CAN) Flexible Data (FD) Light responder device compatible with CiA 604-1 and ISO 11898-1:2024, capable of supporting up to 5Mbps data rate when a dedicated CAN FD light commander is used. The device is designed to support CAN FD light responder node applications in a commander - responder architecture which does not require a responder node processor. All control to the responder node is through the CAN bus from the commander node processor which eliminates the need for responder node processor and software.

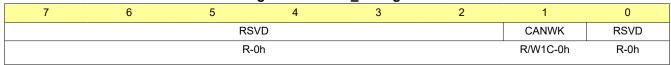

The device receives data and/or commands from a CAN FD light commander node which translates these to either Serial Peripheral Interface (SPI) controller, UART controller, I<sup>2</sup>C controller, and/or GPIO pins communication to the device and/or peripheral devices the TCAN5102-Q1 is controlling. PWM output channels also support trapezoidal ramp profiles in hardware for controlling stepper motors. Ramping of duty cycle or frequency is possible. No external crystal or clock is required. The device controls the external TCAN1162x-Q1, TCAN1043A-Q1 or TCAN1463A-Q1 CAN FD (SIC) transceivers for system level flexibility. The device relies upon the CAN FD transceiver/SBC to control the node power and communicate a wake up signal to the TCAN5102-Q1 by latching the CAN RXD (CRXD) pin low.

# 7.2 Functional Block Diagram

Figure 7-1. High-level block diagram

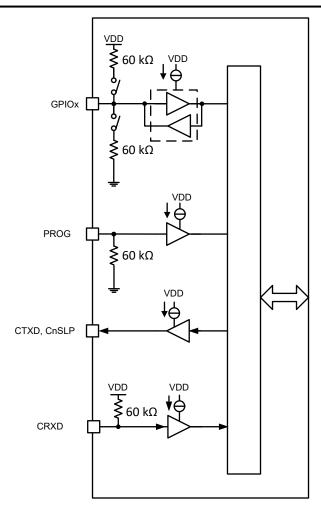

Figure 7-2. Input and Output Block Diagram

# 7.3 Feature Description

#### 7.3.1 VDD

VDD is a power input for the device and sets the digital input/output voltage levels 3.3V, and 5V.

#### 7.3.2 PROG Pin

The PROG pin is used during the ECU development phase. When setting this pin to GND at power up, the TCAN5102-Q1 can be programmed via end of line programming using the CAN bus. The CAN bus programming data rate is set at 1 Mbps for this process.

#### 7.3.3 DIGFLTR Pin

This pin is used to provide filtering for the internal digital core regulator. Please refer to the Recommended Operating Conditions table to see the suggested filter capacitor value.

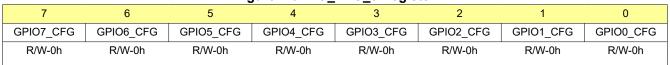

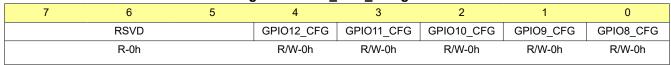

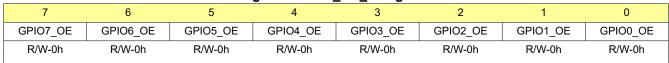

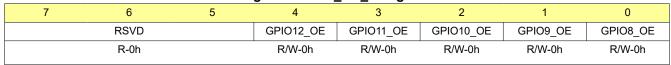

## 7.3.4 GPIOx and Pin Muxing Special Functions

The TCAN5102-Q1 has 12 GPIO pins which can be configured for multiple uses. As a general purpose I/O, the pin can be configured to be an input, a push-pull output, or an open-drain output. The pins also offer integrated user-enabled pull-up and pull-down resistors.

To support the different serial interfaces and IP blocks within the device, several pins have the option to be muxed with GPIOs. The extra functionality is referred to as "special function" in the register configuration, meaning that the pin no longer functions as a GPIO, but instead connects to a special IP block. When configured for special function, only the pull-up and pull down resistor configuration is used for the pin. When special function is selected, the output/input, push pull/open drain, etc mode is automatically configured for you. For example, if the GPIO corresponding to SPI POCI is selected to be a special function, then the settings for that GPIO are overwritten by the SPI IP to configure that GPIO to become an input. If desired, an internal pull up or pull down resistor can be enabled on that pin to provide a known pin state.

#### Note

Some pins have 2 special-functions assigned to them. In the event of an enable contention, the higher priority IP gets priority. For example, if the SPI IP block has enabled SPI chip select channel 4 (CS4) and the I<sup>2</sup>C IP has also been enabled, then GPIO9 is muxed to the I<sup>2</sup>C SCL pin. The default unprogrammed behavior of all pins is to be an input and high impedance.

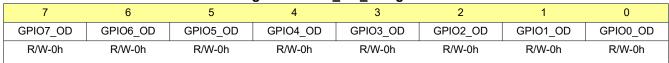

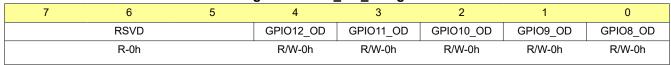

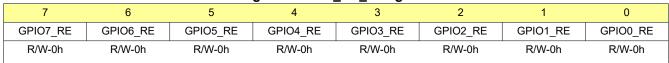

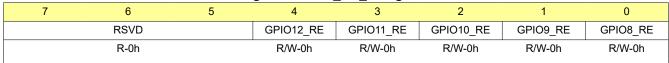

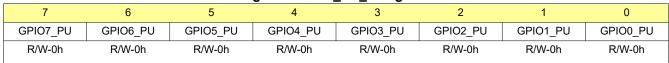

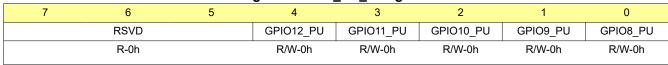

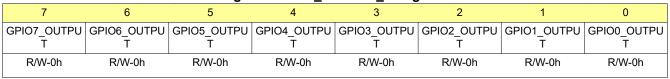

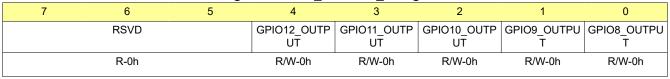

The default power-on state for the GPIOs can be stored in EEPROM to have a power on response. The pins are in a high-impedance state while unpowered or below the POR threshold. Once the device powers up, the configuration is copied from EEPROM to the GPIO registers. Only the configuration registers which can affect the output behavior are are stored in EEPROM. The stored registers are

- 1. IO\_OE\_0 and IO\_OE\_1

- 2. IO\_RE\_0 and IO\_RE\_1

- 3. IO PU 0 and IO PU 1

- 4. IO OUTPUT 0 and IO OUTPUT 1

Table 7-1. Pin Muxing for Special Functions

| PIN | NAME   | LOW-PRIORITY | HIGH-PRIORITY        |

|-----|--------|--------------|----------------------|

| 4   | GPIO9  | SPI CS4      | I <sup>2</sup> C SCL |

| 5   | GPIO10 | SPI CS5      | I <sup>2</sup> C SDA |

| 6   | GPIO11 | SPI CS6      | PWM0                 |

| 7   | GPIO12 | SPI CS7      | PWM1                 |

| 11  | GPIO8  | UART RXD     | -                    |

| 12  | GPIO7  | UART TXD     | -                    |

| 13  | GPIO6  | SPI PICO     | -                    |

| 14  | GPIO5  | SPI POCI     | -                    |

**Table 7-1. Pin Muxing for Special Functions (continued)**

| PIN |       | LOW-PRIORITY | HIGH-PRIORITY |

|-----|-------|--------------|---------------|

| 15  | GPIO4 | SPI SCK      | -             |

| 16  | GPIO3 | SPI CS0      | -             |

| 17  | GPIO2 | SPI CS1      | -             |

| 18  | GPIO1 | SPI CS2      | -             |

| 19  | GPIO0 | SPI CS3      | -             |

#### 7.3.4.1 GPIO Synchronization

The GPIOs configured as outputs support updates being done at the same time. There are 2 modes for this GPIO output updates to take place

- 1. Default: GPIOs are updated immediately when the IO\_OUTPUT\_x registers are updated (each byte)

- Synchronized: Updates only occur after a write to IO\_OUTPUT\_1. To synchronize all, write to IO\_OUTPUT\_0 first, then once the write to IO\_OUTPUT\_1 is complete, all bits are updated at the same time

The feature is enabled in the MRAM IP CFG register by setting the GPIO\_OUT\_SYNC bit to 1.

## **7.3.5 EEPROM**

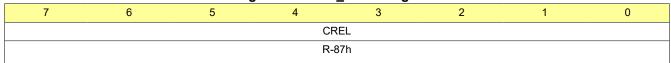

The TCAN5102-Q1 has an integrated EEPROM which is used to store pieces of information for power up configuration:

- 1. CAN bus data rate

- CAN ID

- 3. Broadcast CAN ID and mask

- 4. Configuration locks (data rate and CAN IDs)

- 5. GPIO configuration required to set the power on reset pin state

- a. IO OE 0 and IO OE 1

- b. IO\_RE\_0 and IO\_RE\_1

- c. IO\_PU\_0 and IO\_PU\_1

- d. IO\_OUTPUT\_0 and IO\_OUTPUT\_1

#### Note

The EEPROM has a CRC field, and when a fault is detected with the CRC, the device disables the CAN interface and will hold the GPIOs in high impedance

## 7.3.6 SPI Controller

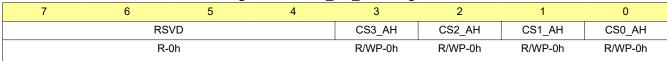

The TCAN5102-Q1 features a SPI controller featuring 8 chip selects and different SPI settings for SPI channels 0 to 3. The last 4 channels share configuration with SPI channel 3. Each of the 4 first channels can have independent SPI speed, and SPI modes. Using the different chip selects allows communication to occur with a shared SPI POCI, PICO, and SCK lines. The chip selects can be configured for active high or active low. Messages are stored in the message RAM (MRAM), and the IP must be allocated space in the MRAM to function. See Section 7.5.3 for more information.

See Section 7.5.4 for more information about the configuration and usage of the SPI controller.

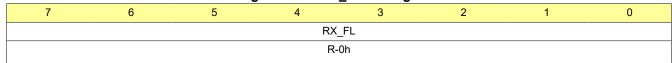

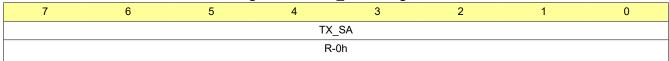

# 7.3.7 UART Controller

The TCAN5102-Q1 features a UART controller. UART is a standard byte-oriented protocol that is used for many different interfaces (LIN, RS232, RS485, Flexwire, and so on). This controller has a fractional baud rate divider to support a wide range of baud rates for use with many interfaces.

Messages are stored in the message RAM (MRAM), and the IP must be allocated space in the MRAM to function. See Section 7.5.3 for more information. It is possible to run the UART IP in single-byte mode, without using the MRAM. There is an enable bit for this mode in the UART configuration register.

See Section 7.5.5 for more information about the configuration and usage of the UART controller.

#### 7.3.8 I2C Controller

The TCAN5102-Q1 features an  $I^2$ C controller supporting standard, fast, and fast mode plus. In addition to the standard controller, there is also a built-in stuck-bus recovery feature, which can detect when the SDA line is stuck low, and toggles the SCL line attempting to unstick the bus. In addition, clock stretching is also supported, as long as the clock stretch time is less than the  $t_{STUCKBUS}$   $t_{ISC}$  time.

Messages are stored in the message RAM (MRAM), and the IP must be allocated space in the MRAM to function. See Section 7.5.3 for more information.

See Section 7.5.6 for more information about the configuration and usage of the I<sup>2</sup>C controller.

## 7.3.8.1 I2C Stuck Bus Recovery

The I2C controller has an optional feature called stuck bus recovery (SBR). Stuck bus recovery attempts to fix the bus when the SDA or SCL line is "stuck" low. This can occur if there is noise on the bus that causes an I2C peripheral to see the incorrect number of clocks. The stuck bus recovery toggles the SCL line up to 16 times to attempt to get offending device to release the bus. See Section 7.5.6.2 for more information.

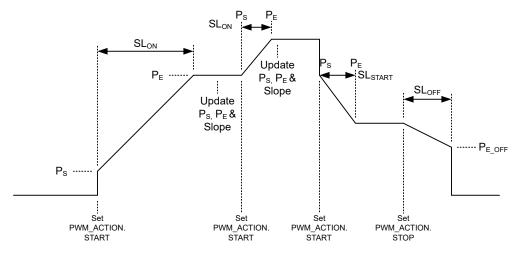

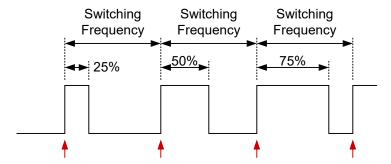

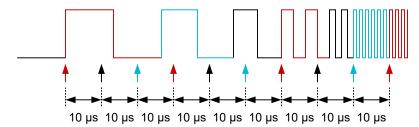

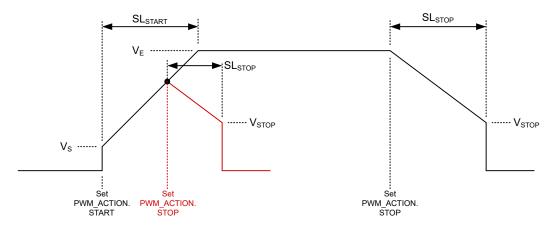

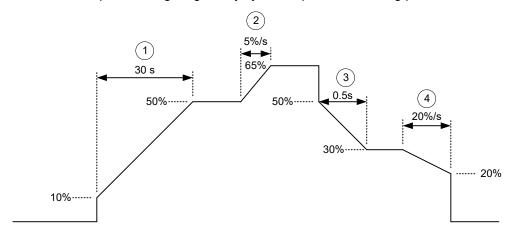

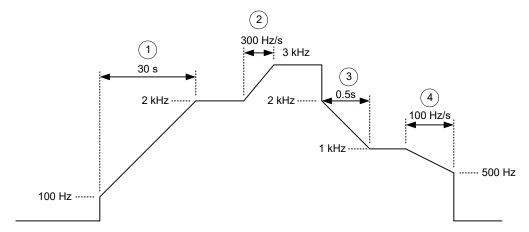

#### 7.3.9 PWM Controller

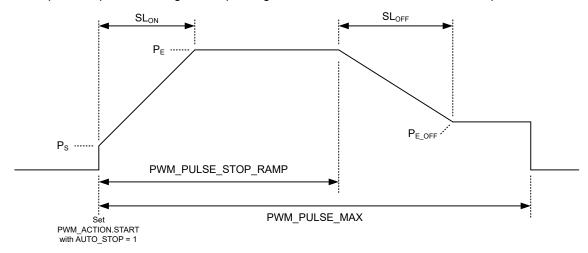

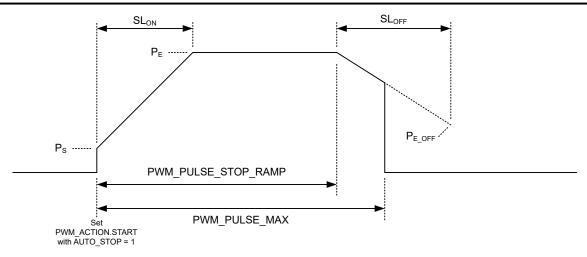

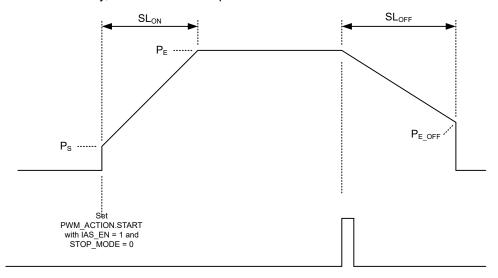

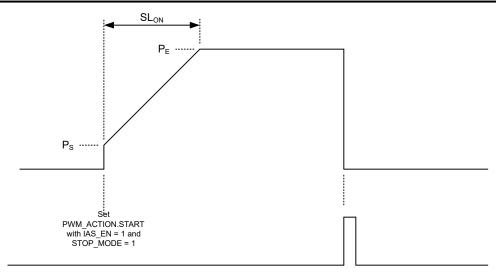

The TCAN5102-Q1 features a PWM controller with integrated ramping features. The PWM controller supports static/typical PWM output (fixed duty cycle and frequency), but also supports advanced PWM features such as the ability to ramp either the duty cycle or the frequency in order to support basic motor control. The controller was developed with stepper motor control in mind, allowing the user to program an acceleration and deceleration profile. Once the controller is told to start the ramp, it does the math and performs the specified ramp profile on the PWM output.

The PWM controller even supports additional features such as PWM pulse counting, allowing the user to configure the PWM output to generate an acceleration and deceleration profile, and then stop after a certain amount of pulses/steps automatically. The sequence is programmed into the registers, and requires no intervention from the upstream controller other than being told to start the ramp.

For additional features, a GPIO input can be used to either start a deceleration ramp or to immediately turn off the PWM output. This is useful for a limit switch or some motor fault detection.

See Section 7.5.7 for more information about the configuration and usage of the PWM controller.

## 7.3.10 CAN Transceiver Control Pins

The TCAN5102-Q1 does not have an integrated CAN transceiver, and requires an external one. This allows the user to select whichever CAN transceiver they want to support. This device has a CAN TXD, RXD and nSLP pin. The nSLP pin is used to control the sleep or standby mode of an external transceiver when going into sleep mode.

#### 7.3.11 Under-Voltage Lockout and Unpowered Device

The TCAN5102-Q1 monitors the supply rail of the device (VDD). VDD is monitored for under-voltage. When a UVDD fault is detected, the device has a corresponding state change.

| Table 7-2. \ | <b>VDD</b> | Faults and | d Device | Mode |

|--------------|------------|------------|----------|------|

|--------------|------------|------------|----------|------|

| VDD    | Device Mode    |

|--------|----------------|

| > UVDD | Normal         |

| < UVDD | Power on reset |

# 7.4 Device Functional Modes

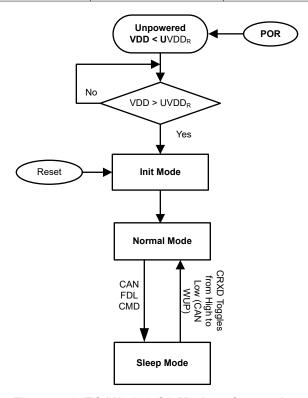

The TCAN5102-Q1 has four modes of operation, unpowered, Init, Sleep, and Normal. See Table 7-3 for how the different device blocks behave in each mode. See Figure 7-3 for how the overall modes of operation interact.

Table 7-3. Mode Overview

| Block                   | Init       | Normal           | Sleep         |

|-------------------------|------------|------------------|---------------|

| CAN Transceiver Control | Off (Hi-Z) | On               | Off           |

| CAN nSLP                | Off (Hi-Z) | High (VDD)       | Low (GND)     |

| SPI                     | Off (Hi-Z) | On if programmed | Off           |

| I <sup>2</sup> C        | Off (Hi-Z) | On if programmed | Off           |

| UART                    | Off (Hi-Z) | On if programmed | Off           |

| GPIOx                   | Off (Hi-Z) | As programmed    | As programmed |

Figure 7-3. TCAN5102-Q1 Modes of operation

#### 7.4.1 Init Mode

This is the initial mode of operation upon powering up. This is a transitional mode that is entered once VDD is greater than  $UV_{DD}$  and the saved device configuration is loaded. Once the configuration is loaded, the device transitions to normal mode.

In init mode, the EEPROM is read, and once EEPROM is read, the configuration is copied to the registers and the device transitions to normal mode. See Section 7.3.5 for more information about which configurations are saved.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

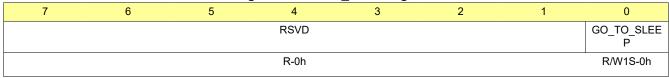

## 7.4.2 Sleep Mode

Sleep mode is the lowest power state of the device. The TCAN5102-Q1 receives the go-to-sleep command from the CAN bus, and perform the following:

- Perform any internal house keeping actions

- Place the external CAN transceiver into sleep mode

Once the CAN transceiver is placed into sleep mode, no power is expected on VDD. The device is in the unpowered state. Keeping VDD powered while in sleep mode is possible. The device remains in a low power state until a WUP signal is received from the CAN transceiver to wake up the device.

#### 7.4.3 Normal Mode

After leaving INIT mode, the device enters normal mode. Normal mode activates the transceiver and the device is ready to receive or transmit data.

## 7.5 Programming

The device uses a CAN FD Light interface for configuration. Configuration is done by writing to registers on the device. There is a specific CAN FD message structure used to access the device registers. There are multiple frame formats that this device supports for accessing device registers.

## 7.5.1 Device Programming via SPI Peripheral Mode

There are 2 options for configuration programming:

- 1. Program via CAN FD Light (using PROG pin to force baud rate to 1Mbps)

- 2. Using SPI (using a toggle sequence with the PROG and RXD pins to enable a local SPI peripheral to allow a programmer to write to the EEPROM)

The SPI peripheral mode method can be used if the CAN interface is not available to program EEPROM. This method requires a specific sequence of events in order to enable the local SPI peripheral. When the device is in SPI peripheral mode, the CAN interface is disabled and stays disabled until a power cycle.

#### 7.5.2 CAN FD Light Protocol

The TCAN5102-Q1 supports the CiA 604-1 and CiA 604-3 communication standard through use of logical link control (LLC) and the FD Base Frame Format (FBFF),, see Table 7-4.

**Table 7-4. Protocol CiA Format**

| Field                                                 | Size                                                              | Function                                          |  |

|-------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------|--|

| Identifier                                            | 11 bit                                                            | Base identifier (either a target or broadcast ID) |  |

| DLC                                                   | 4 bit Data length code, as specified in ISO 11898-1:2015, Table 5 |                                                   |  |

| LLC Data 0 to 64 byte Data content of the data frames |                                                                   |                                                   |  |

| Data content of the data frames                       |                                                                   |                                                   |  |

Since all transmitted and received frames are in FBFF and the bits ESI=0 and BRS=0, all bits in the format field are fixed. Therefore, the format field is omitted.

The device protocol is split into a request and a response. A device request is a request to this device to perform a read or a write to a specific register. A request always has at least 3 fields, which are required to decode any operation. These fields are always at the start of the CAN frame data section.

- 1. Operation Code (Op Code): This tells the device if a read or write to a register or FIFO is occurring

- Length: Indicates the total size (in bytes) of data being transferred (after the device header)

- 3. Register Address: A 16-bit address of the register or FIFO being written to or read from

A device response is sent after a request to let the requesting device know that the request was received and is in progress or invalid. The response contains at least 3 fields

Product Folder Links: TCAN5102-Q1

1. Operation Code (Op Code): Repeats back the received Op code

- Length: Indicates the total size (in bytes) of data being returned after the header (if the request was a write, then this mirrors the number of bytes written, but no data is sent. The length field is used to confirm the number of bytes that were written)

- 3. Status Byte: Signals the status of the request. This can be OK/successful, or an error of some sort such as an invalid address or length.

There are 2 types of identifiers used by the device. A target identifier is the specific address that is unique to an individual responder. This allows a commander to address/configure an individual node. A broadcast identifier is also supported, which uses the broadcast ID and mask fields to match 1 or several IDs. Any requests from a broadcast ID has the request performed, but there is no response from the responder, since arbitration is not supported in CAN FD Light. Broadcast is useful if the commander wants to configure many nodes at once, or put multiple nodes to sleep. However, this drops the response frame, so it is not confirmed by the responder.

#### 7.5.2.1 CAN Frame Format

The standard CAN frame format uses 3 bytes of the CAN payload as a header, containing 3 fields: operation code (op code), data length and address.

| CAN ID          |      | Byte 0               | Byte 1     | Byte 2    | Byte 3 |     |

|-----------------|------|----------------------|------------|-----------|--------|-----|

| Device ID[10:0] | CTRL | OP[7:6]/<br>LEN[5:0] | ADDR[15:8] | ADDR[7:0] | Data   | ••• |

Figure 7-4. Example Standard CAN Frame Format Request

Table 7-5. Standard CAN Frame Format Request Header Fields

| Byte | Bits | Field      | Description                                                                                                               |

|------|------|------------|---------------------------------------------------------------------------------------------------------------------------|

| 0    | 7:6  | OPCODE     | Operation code of the device<br>2'b00 = Write<br>2'b01 = Read<br>2'b10 = Reserved<br>2'b11 = Reserved                     |

|      | 5:0  | LEN        | Number of data bytes being transferred after this header<br>Valid values (write): 0 to 61<br>Valid values (read): 0 to 62 |

| 1    | 7:0  | ADDR[15:8] | Upper byte of the address                                                                                                 |

| 2    | 7:0  | ADDR[7:0]  | Lower byte of the address                                                                                                 |

#### Note

For multi-byte reads, if the starting address is before the RX FIFO of one of the serial communication blocks (I2C, SPI, UART), the FIFO is NOT actually read. Instead, the byte corresponding to the RX FIFO returns 0 and then read continues on. This is to prevent a burst read from getting "stuck" in an RX FIFO. If the starting address of the read starts at the RX FIFO, then all bytes read are from the RX FIFO only.

| CAN ID          |      | Byte 0               | Byte 1      | Byte 2 |       |

|-----------------|------|----------------------|-------------|--------|-------|

| Device ID[10:0] | CTRL | OP[7:6]/<br>LEN[5:0] | STATUS_BYTE | Data   | • • • |

Figure 7-5. Example Standard CAN Frame Format Response

Table 7-6. Standard CAN Frame Format Response Header Fields

| Byte | Bits | Field  | Description                                                                                                                                                                                                                      |

|------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 7:6  | OPCODE | Operation code of the device 2'b00 = Write 2'b01 = Read 2'b10 = Reserved 2'b11 = Reserved                                                                                                                                        |

| 0    |      |        | Echos the number of bytes of data that were requested being sent after the header if the requested amount of valid.  Note                                                                                                        |

|      | 5:0  | LEN    | If the response is to a write request, then the length field is the length of bytes that were requested, but no data is sent after the header. This is to allow for confirmation that the response frame is to the write request |

| 1    | 7:5  | RSVD   | Reserved                                                                                                                                                                                                                         |

| 1    | 4    | FE     | Framing error on the previous request. Request ignored. Typically caused when the DLC is < 3 bytes since there is a minimum requirement for headers                                                                              |

| 1    | 3    | Ю      | Invalid operation. Request ignored                                                                                                                                                                                               |

| 1    | 2    | IL     | Invalid length. Request ignored                                                                                                                                                                                                  |

| 1    | 1    | IA     | Invalid address. Request ignored                                                                                                                                                                                                 |

| 1    | 0    | OK     | Ok request, request complete or in progress                                                                                                                                                                                      |

## 7.5.3 Message RAM (MRAM) and IP Enable

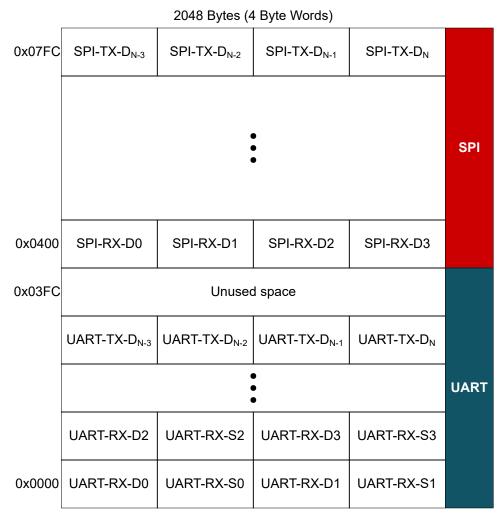

The TCAN5102-Q1 has a 2kB message RAM (MRAM) that is used for storing the mailboxes for SPI, I2C, and UART communication. This RAM can split the memory allocated to any combination of the 2 IP blocks based upon the end-application's needs in 25% increments. The split between RX and TX is not adjustable and is always 50/50%. Handling of the RX and TX FIFOs is done by the TCAN5102-Q1, and requires no user setup outside of choosing how much of the MRAM to allocate to each IP block.

SPI and I2C have a straight forward split for memory use, where 50% of the allocated memory is used to store the TX data and the other 50% is used to store the RX data if specified.

For UART, there are additional bytes needed to store the status of each received byte. This means that for each byte of data received on UART, 1 additional byte is needed for storing the status of the byte. The result is that only 2/3 of the allocated memory for UART is used for storing actual data bytes.

Table 7-7 shows how many bytes of data are allocated to the TX or RX buffers for each IP block. The size shown is the same value for both the TX and RX buffers, and is NOT the value shared between both. For example, if 100% of the MRAM space is allocated to the SPI, then the SPI TX size is 1024 bytes, and the SPI RX buffer is 1024 bytes. Together, the TX and RX buffer sum up to 2048 bytes, which is all of the memory.

In the example where 50% of the MRAM is allocated to SPI and UART, the SPI RX and TX sizes are 512 each (1kB total). The UART IP is only 340 bytes for each buffer. Due to UART RX requiring an additional byte to store the status for each byte received, only 2/3 of the available 1024 bytes is used to store data. Internally, the number of bytes that can be stored by the TX and RX buffers are identical. For this reason, 4 bytes of data end up unused, because the 4 bytes remaining cannot be divided evenly across 3 functions (TX, RX, and RX status).

#### Note

The MRAM allocation setting is used to enable the IP module for SPI and I2C. If any memory is allocated to the module, then the module is enabled, but the GPIOs in use for the module must still be manually set to special-function in the GPIO configuration registers.

# Table 7-7. MRAM Allocation

| % Allocated to SPI | SPI TX or RX Size<br>(Bytes) | UART TX or RX Size<br>(Bytes) | Total Bytes Used<br>(% of Total) |

|--------------------|------------------------------|-------------------------------|----------------------------------|

| 100%               | 1024                         | 0                             | 2048 (100%)                      |

| 75%                | 768                          | 168                           | 2040 (99.6%)                     |

| 50%                | 512                          | 340                           | 2044 (99.8%)                     |

| 25%                | 256                          | 512                           | 2048 (100%)                      |

| 0%                 | 0                            | 680                           | 2040 (99.6%)                     |

# **Table 7-8. MRAM Allocation**

| MRAM_IP_EN<br>(Hex) | % Allocated to SPI | % Allocated to UART | % Allocated to I2C | SPI TX and RX<br>Size<br>(Bytes) | UART TX and<br>RX Size<br>(Bytes) | I2C TX and RX<br>Size<br>(Bytes) | Total Bytes<br>Used<br>(% of Total) |

|---------------------|--------------------|---------------------|--------------------|----------------------------------|-----------------------------------|----------------------------------|-------------------------------------|

| 0h                  | 0%                 | 0%                  | 0%                 | 0                                | 0                                 | 0                                | 0 (0%)                              |

| 1h                  | 0%                 | 100%                | 0%                 | 0                                | 680                               | 0                                | 2040 (99.61%)                       |

| 2h                  | 25%                | 75%                 | 0%                 | 256                              | 512                               | 0                                | 2048 (100%)                         |

| 3h                  | 50%                | 50%                 | 0%                 | 512                              | 340                               | 0                                | 2044 (99.8%)                        |

| 4h                  | 75%                | 25%                 | 0%                 | 768                              | 168                               | 0                                | 2040 (99.61%)                       |

| 5h                  | 100%               | 0%                  | 0%                 | 1024                             | 0                                 | 0                                | 2048 (100%)                         |

| 6h                  | 0%                 | 0%                  | 100%               | 0                                | 0                                 | 1024                             | 2048 (100%)                         |

| 7h                  | 0%                 | 25%                 | 75%                | 0                                | 168                               | 768                              | 2040 (99.61%)                       |

| 8h                  | 0%                 | 50%                 | 50%                | 0                                | 340                               | 512                              | 2044 (99.8%)                        |

| 9h                  | 0%                 | 75%                 | 25%                | 0                                | 512                               | 256                              | 2048 (100%)                         |

| Ah                  | 25%                | 0%                  | 75%                | 256                              | 0                                 | 768                              | 2048 (100%)                         |

| Bh                  | 50%                | 0%                  | 50%                | 512                              | 0                                 | 512                              | 2048 (100%)                         |

| Ch                  | 75%                | 0%                  | 25%                | 768                              | 0                                 | 256                              | 2048 (100%)                         |

Product Folder Links: TCAN5102-Q1

Submit Document Feedback

Figure 7-6. Example MRAM Layout (SPI and UART enabled with a 50% split)

# 2048 Bytes (4 Byte Words)

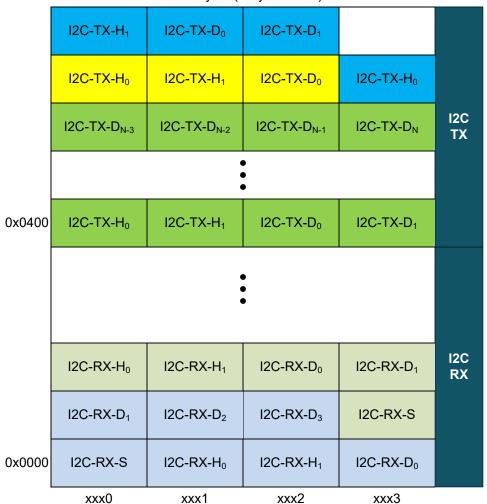

Figure 7-7. Example MRAM Layout with Example Data (100% of MRAM to I2C)

In the above graphic, an example of how the MRAM holds data for I2C is shown. Each individual I2C frame/ message is shown in a different color to show how the messages are grouped tightly in each RX or TX FIFO. The user does not need to be aware of how the data is stored in the FIFO, only the total size of the FIFO and the fact that any header/status bytes are also stored in memory.

## 7.5.4 SPI Controller

#### Note

Before the module can be used, the appropriate GPIOs must be set to special function (see Section 7.3.4 and Section 7.6.1.18) and the MRAM must enable the module by allocation memory (see Section 7.5.3 and Section 7.6.1.17). Only once the GPIOs have been set to special function, and the module has been enabled by selecting a MRAM configuration that allocates memory, can the module be used. The appropriate SPI configuration registers can be seen in Section 7.6.2.

## 7.5.4.1 SPI Pins

SPI communication typically uses 4 pins for communication to another SPI device: clock (SCLK), data in (PICO), data out (POCI) and chip select (CS or nCS).

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

#### 7.5.4.1.1 SPI Clock (SCLK)

The SPI clock output pin is used to generate a clock that synchronizes data shifted in or out of the target peripheral. The pin can be configured for any of the 4 SPI modes (2 clock polarities) to give maximum configurability and compatibility with downstream peripherals.

## 7.5.4.1.2 Peripheral In Controller Out (PICO)

This output pin is used to shift data into the peripheral device (downstream device). When the chip select signal is asserted (can be high or low depending on configuration, the PICO shifts data into the target/peripheral device). This pin would be connected to a serial data input (SDI) pin on a peripheral/target device.

#### 7.5.4.1.3 Peripheral Out Controller In (POCI)

This input pin is used to shift data out of a peripheral/downstream device and into this device/controller. The POCI pin is typically connected to the serial data output (SDO) pin on the peripheral/target device.

## 7.5.4.1.4 Chip Select (CS or nCS)

The chip select output pin is used to tell a target peripheral when it is being communicated with. This device supports up to 4 separate chip select channels with individual polarity selects.

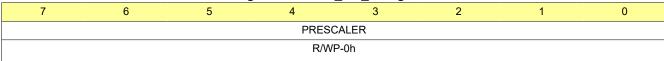

#### 7.5.4.2 SPI Clock Generator

The TCAN5102-Q1 SPI module contains a programmable clock generator that uses an 8-bit divisor. The SPI\_DR register is interpreted as 1 more than the value in the SPI\_DR register, and is used for the half-period. The formula for the divisor is:

Where clock frequency is 40MHz. This formula shows that the maximum SPI frequency supported is 20MHz and the minimum frequency is 78,125Hz.

Table 7-9. Common SPI Clocks

| DESIRED SPI CLOCK | DIVISOR USED TO GENERATE CLOCK | SPI_DR VALUE<br>(HEX) |

|-------------------|--------------------------------|-----------------------|

| 80kHz             | 249                            | 0xF9                  |

| 100kHz            | 199                            | 0xC7                  |

| 200kHz            | 99                             | 0x63                  |

| 250kHz            | 79                             | 0x4F                  |

| 500kHz            | 39                             | 0x27                  |

| 1MHz              | 19                             | 0x13                  |

| 2MHz              | 9                              | 0x09                  |

| 4MHz              | 4                              | 0x04                  |

| 5MHz              | 3                              | 0x03                  |

| 6.67MHz           | 2                              | 0x02                  |

| 10MHz             | 1                              | 0x01                  |

| 20MHz             | 0                              | 0x00                  |

#### 7.5.4.3 SPI Control Protocol

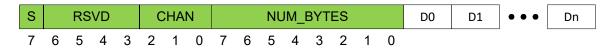

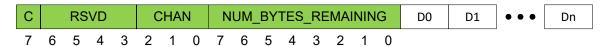

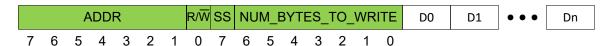

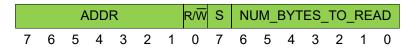

When reading or writing to the SPI TX or RX FIFOs, there is an additional 2 byte header which provides additional robustness when reading or writing to a target peripheral. There are 2 formats, which are similar but differ depending on if the action is a read or a write to the SPI TX or RX FIFO.

When reading the RX FIFO, there is always the 2-byte header at the beginning of the data field which contains information on how many bytes are remaining and if the read is a continuation of a previous read (needed for SPI messages that are larger than can fit in a single CAN frame).

When writing to the TX FIFO, only the first write of a message contains the 2-byte header.

See SPI Receive FIFO (address = h1010) and SPI Transmit FIFO (address = h1010) for more information about the header formats.

# 7.5.4.3.1 SPI Write Example 1

This is a basic example of sending a stream of bytes via SPI that fits into a single CAN frame. Once the device receives all bytes for the SPI frame (determined by the number of bytes given in the SPI header), the device begins transmitting the SPI frame.

#### Note

Before the module can be used, the appropriate GPIOs must be set to special function (see Section 7.3.4 and Section 7.6.1.18) and the MRAM must enable the module by allocation memory (see Section 7.5.3 and Section 7.6.1.17). Only once the GPIOs have been set to special function, and the module has been enabled by selecting a MRAM configuration that allocates memory, can the module be used. The appropriate SPI configuration registers can be seen in Section 7.6.2.

Table 7-10. Design Parameters and Assumptions

| PARAMETER                     | VALUE                                                      |

|-------------------------------|------------------------------------------------------------|

| CAN Frame format              | Standard Frame Format                                      |

| Bytes to transfer             | 10'B                                                       |

| SPI channel                   | Channel 1                                                  |

| Save received data to RX FIFO | No                                                         |

| SPI byte stream               | 0x11, 0x22, 0x33, 0x44, 0x55, 0x66, 0x77, 0x88, 0x99, 0xAA |

The following table shows the steps and what data is transmitted on the CAN bus. The central gateway/controller of the bus is referred to as the ECU, and the TCAN device is referred to as "responder".

- Hexadecimal values marked as **BOLD** signify the bytes for CAN Frame header (standard frame format for this example)

- Hexadecimal values marked as ITALIC signify the SPI header bytes