Sample &

Buy

SLLS545G-NOVEMBER 2002-REVISED OCTOBER 2015

## SNx5HVD251 Industrial CAN Bus Transceiver

Technical

Documents

#### 1 Features

- Drop-In Improved Replacement for the PCA82C250 and PCA82C251

- Bus-Fault Protection of ±36 V

- Meets or Exceeds ISO 11898

- Signaling Rates<sup>(1)</sup> up to 1 Mbps

- High Input Impedance Allows up to 120 Nodes on a Bus

- Bus Pin ESD Protection Exceeds 14 kV HBM

- Unpowered Node Does Not Disturb the Bus

- Low-Current Standby Mode: 200-µA Typical

- Thermal Shutdown Protection

- Glitch-Free Power-Up and Power-Down CAN Bus Protection for Hot-Plugging

- DeviceNet Vendor ID #806

- <sup>(1)</sup> The signaling rate of a line is the number of voltage transitions that are made per second expressed in bps (bits per second).

#### 2 Applications

- CAN Data Buses

- Industrial Automation

- SAE J1939 Standard Data Bus Interface

- NMEA 2000 Standard Data Bus Interface

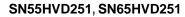

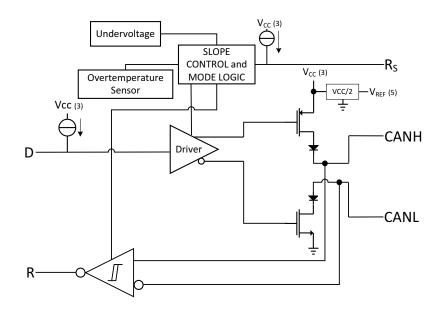

#### Block Diagram

#### 3 Description

Tools &

Software

The HVD251 is intended for use in applications employing the Controller Area Network (CAN) serial communication physical layer in accordance with the ISO 11898 Standard. The HVD251 provides differential transmit capability to the bus and differential receive capability to a CAN controller at speeds up to 1 megabits per second (Mbps).

Support &

Community

2.2

Designed for operation in harsh environments, the device features cross-wire, overvoltage and loss of ground protection to  $\pm 36$  V. Also featured are overtemperature protection as well as -7-V to 12-V common-mode range, and tolerance to transients of  $\pm 200$  V. The transceiver interfaces the single-ended CAN controller with the differential CAN bus found in industrial, building automation, and automotive applications.

Rs, pin 8, selects one of three different modes of operation: high-speed, slope control, or low-power mode. The high-speed mode of operation is selected by connecting pin 8 to ground, allowing the transmitter output transistors to switch as fast as possible with no limitation on the rise and fall slope. The rise and fall slope can be adjusted by connecting a resistor to ground at pin 8; the slope is proportional to the pin's output current. Slope control with an external resistor value of 10 k $\Omega$  gives about 15-V / µs slew rate; 100 k $\Omega$  gives about 2-V/µs slew rate.

If a high logic level is applied to the Rs pin 8, the device enters a low-current standby mode where the driver is switched off and the receiver remains active. The local protocol controller returns the device to the normal mode when it transmits to the bus.

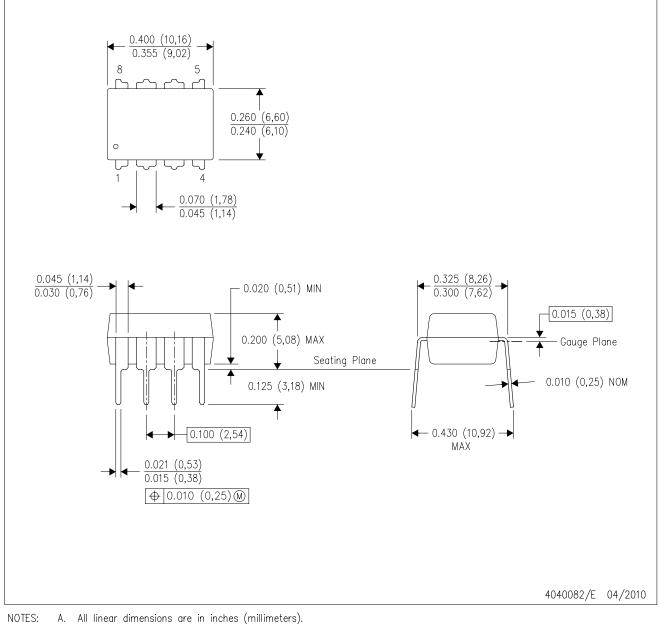

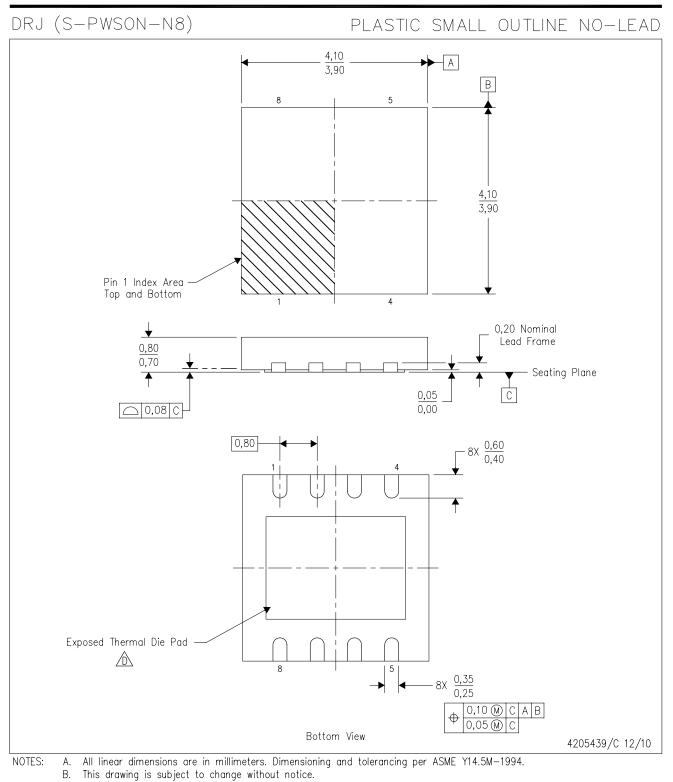

| Device I | ormation <sup>(</sup> | 1) |

|----------|-----------------------|----|

|----------|-----------------------|----|

| PART NUMBER | PACKAGE  | BODY SIZE (NOM)   |  |

|-------------|----------|-------------------|--|

| SN55HVD251  | WSON (8) | 4.00 mm × 4.00 mm |  |

|             | SOIC (8) | 4.90 mm × 3.91 mm |  |

| SN65HVD251  | PDIP (8) | 9.81 mm × 6.35 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Table of Contents**

| 1 | Feat  | ures                                 | 1 |

|---|-------|--------------------------------------|---|

| 2 | App   | lications                            | 1 |

| 3 | Desc  | cription                             | 1 |

| 4 | Revi  | sion History                         | 2 |

| 5 | Pin ( | Configuration and Functions          | 4 |

| 6 |       | cifications                          |   |

|   | 6.1   | Absolute Maximum Ratings             | 4 |

|   | 6.2   | ESD Ratings                          | 4 |

|   | 6.3   | Recommended Operating Conditions     | 5 |

|   | 6.4   | Thermal Information                  | 5 |

|   | 6.5   | Supply Current                       | 5 |

|   | 6.6   | Electrical Characteristics: Driver   | 5 |

|   | 6.7   | Electrical Characteristics: Receiver | 6 |

|   | 6.8   | VREF-Pin Characteristics             |   |

|   | 6.9   | Power Dissipation Characteristics    | 7 |

|   | 6.10  | Switching Characteristics: Driver    | 7 |

|   | 6.11  | Switching Characteristics: Device    | 7 |

|   | 6.12  | Switching Characteristics: Receiver  | 8 |

|   | 6.13  |                                      |   |

|   | 6.14  | Typical Characteristics              | 9 |

| 7 | Para  | meter Measurement Information        | 1 |

### **4** Revision History

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

#### Changes from Revision F (June 2015) to Revision G

| ٠ | Changed the value of HBM "All pins" From: ±14000 V To: ±6000 V. Changed the value of "CANH, CANL and GND" |

|---|-----------------------------------------------------------------------------------------------------------|

|   | From: ±6000 V To: ±14000 V in the ESD Ratings                                                             |

#### Changes from Revision E (March 2010) to Revision F

Submit Documentation Feedback

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | and Documentation Support section, and Mechanical, Packaging, and Orderable Information section                                                                                                                              |

| • | Changed the location of section "6.12 VREF-Pin Characteristics" to section 6.8                                                                                                                                               |

| С | hanges from Revision C (September 2005) to Revision D                                                                                                        | Page |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added device SN55HVD251                                                                                                                                      | 1    |

| • | Added the DRJ Package.                                                                                                                                       | 1    |

| • | Changed the data sheet title From: CAN TRANSCEIVER To: INDUSTRIAL CAN TRANSCEIVER                                                                            | 1    |

| • | Deleted APPLICATIONS bullets: DeviceNet <sup>™</sup> Data Buses, Smart Distributed Systems (SDS <sup>™</sup> ), and ISO 11783<br>Standard Data Bus Interface | 1    |

| • | Deleted last paragraph from the DESCRIPTION - "The HVD251 may be used"                                                                                       | 1    |

| • | Added Electrical fast transient/burst to the Abs Max Ratings table                                                                                           | 4    |

| • | Deleted the condition - over recommended operating conditions (unless otherwise noted). From the<br>RECOMMENDED OPERATING CONDITIONS table                   | 5    |

| • | Added SN55HVD251 to the Operating free-air temperature, T <sub>A</sub> in the ROC table                                                                      | 5    |

| • | Added DRJ to the Junction-to-case thermal resistance                                                                                                         | 5    |

| • | Added DRJ to the Junction-to-board thermal resistance                                                                                                        | 5    |

| 8  | Deta | iled Description                  | 17 |

|----|------|-----------------------------------|----|

|    | 8.1  | Overview                          | 17 |

|    | 8.2  | Functional Block Diagram          | 17 |

|    | 8.3  | Feature Description               | 17 |

|    | 8.4  | Device Functional Modes           | 19 |

| 9  | Арр  | lication and Implementation       | 21 |

|    | 9.1  | Application Information           | 21 |

|    | 9.2  | Typical Application               | 24 |

|    | 9.3  | System Example                    | 26 |

| 10 | Pow  | ver Supply Recommendations        | 28 |

| 11 | Lay  | out                               | 28 |

|    | 11.1 | Layout Guidelines                 | 28 |

|    | 11.2 | Layout Example                    |    |

| 12 | Dev  | ice and Documentation Support     | 30 |

|    | 12.1 | Related Links                     |    |

|    | 12.2 | Community Resources               | 30 |

|    | 12.3 | Trademarks                        | 30 |

|    | 12.4 | Electrostatic Discharge Caution   | 30 |

|    | 12.5 | Glossary                          | 30 |

| 13 | Mec  | hanical, Packaging, and Orderable |    |

|    |      | rmation                           | 30 |

www.ti.com

#### Page

4

Page

INSTRUMENTS

XAS

www.ti.com

| • | Added the SUPPLY CURRENT table                                                                                                                   | 5  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Deleted ICC - Supply current from the DRIVER ELECTRICAL CHARACTERISTICS                                                                          | 5  |

| • | Added T ≥ -40°C to V <sub>O(D)</sub> Test Conditions in the DRIVER ELECTRICAL CHARACTERISTICS                                                    | 5  |

| • | Added $R_{NODE}$ = 330 $\Omega$ to Differential output voltage (Dominant) (second line of Test Conditions) in the DRIVER ELECTRICAL table.       | 5  |

| • | Added a third line of Test Conditions to Differential output voltage (Dominant) in the DRIVER ELECTRICAL table                                   | 5  |

| • | Added T ≤ 85°C to V <sub>OD®)</sub> Test Conditions in the DRIVER ELECTRICAL CHARACTERISTICS                                                     | 5  |

| • | Deleted ICC - Supply current from the RECEIVER ELECTRICAL CHARACTERISTICS                                                                        | 6  |

| • | Added Receiver noise rejection row to the RECEIVER ELECTRICAL CHARACTERISTIC table                                                               | 6  |

| • | Added TYP values to the Differential output signal rise and fall times in the DRIVER SWITCHING CHARACTERISTIC table                              |    |

| • | Changed table title From: ABSOLUTE MAXIMUM POWER DISSIPATION RATINGS To: PACKAGE DISSIPATION RATINGS                                             | 8  |

| • | Added the SON (DRJ) option to the PACKAGE DISSIPATION RATINGS table                                                                              | 8  |

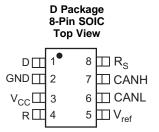

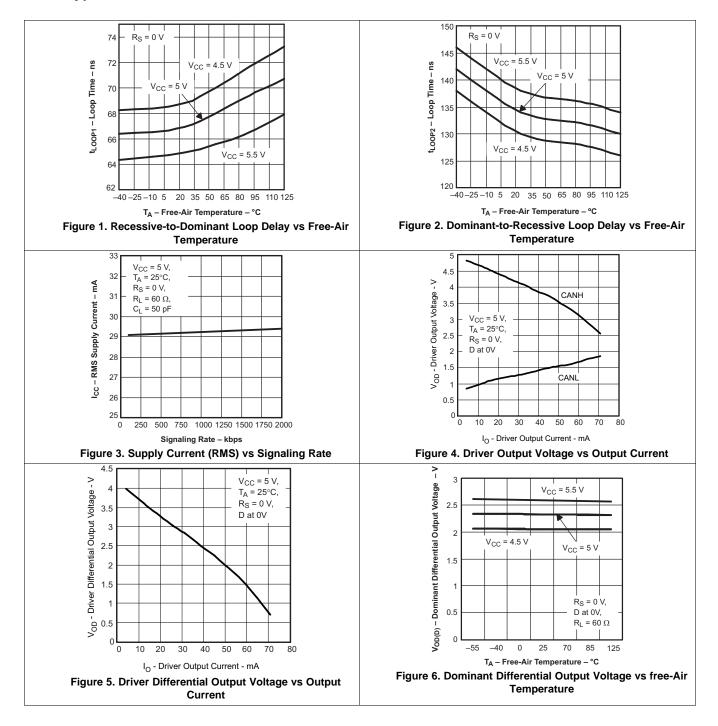

| • | Changed Figure 1 title From: t <sub>LOOP1-LOOP</sub> TIME To: RECESSIVE-TO-DOMINANT LOOP DELAY                                                   | 9  |

| • | Changed Figure 2 title From: t <sub>LOOP2-LOOP</sub> TIME To: DOMINANT-TO-RECESSIVE LOOP DELAY                                                   | 9  |

| • | Changed Figure 4 From: DRIVER LOW-LEVEL OUTPUT CURRENT vs LOW-LEVEL OUTPUT VOLTAGE To:<br>DRIVER OUTPUT VOLTAGE vs OUTPUT CURRENT                | 9  |

| • | Changed Figure 5 From: DRIVER HIGH-LEVEL OUTPUT CURRENT vs HIGH-LEVEL OUTPUT VOLTAGE To:<br>DRIVER DIFFERENTIAL OUTPUT VOLTAGE vs OUTPUT CURRENT | 9  |

| • | Changed Figure 8 title From: DIFFERENTIAL OUTPUT FALL TIME To: DIFFERENTIAL OUTPUT TRANSITION TIME                                               | 9  |

| • | Changed Figure 12 - Driver V <sub>OD</sub> , label R <sub>NODE</sub> was 330Ω±1%                                                                 |    |

| • | Changed Table 1 header From: MEASURED To: DIFFERENTIAL INPUT                                                                                     |    |

| • | Added Note B to Figure 22                                                                                                                        |    |

| • | Added a row ( X Open) to Table 2 - Driver                                                                                                        | 19 |

#### Changes from Revision B (September 2003) to Revision C

| • | Changed the front page format                                                              | 1 |

|---|--------------------------------------------------------------------------------------------|---|

| • | Changed Junction temperature, T <sub>J</sub> - SOIC Package MAX value From 150°C To: 145°C | 5 |

| • | Changed the THERMAL CHARACTERISTICS table values                                           | 7 |

| • | Changed the ABSOLUTE MAXIMUM POWER DISSIPATION RATINGS table values                        | 8 |

|   |                                                                                            |   |

| C | Changes from Revision A (September 2003) to Revision B Page Page Page Page Page Page Page Page                  |  |  |  |

|---|-----------------------------------------------------------------------------------------------------------------|--|--|--|

| • | Changed the front page format 1                                                                                 |  |  |  |

| • | Changed DESCRIPTION text From: and tolerance to transients of ±50 V To: and tolerance to transients of ±200 V 1 |  |  |  |

| _ |                                                                                                                 |  |  |  |

####

Page

ISTRUMENTS

www.ti.com

EXAS

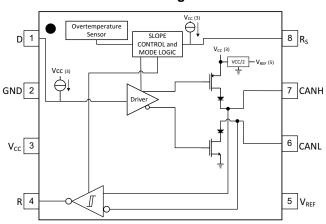

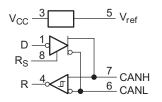

#### 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN I/O              |   | 1/0    | DECODIDITION                                                                                                                                                                 |  |  |

|----------------------|---|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                      |   | 1/0    | DESCRIPTION                                                                                                                                                                  |  |  |

| CANH                 | 7 | I/O    | High-level CAN bus line                                                                                                                                                      |  |  |

| CANL                 | 6 | I/O    | Low-level CAN bus line                                                                                                                                                       |  |  |

| D                    | 1 | I      | CAN transmit data input (LOW for dominant and HIGH for recessive bus states), also called TXD, driver input                                                                  |  |  |

| GND                  | 2 | GND    | round connection                                                                                                                                                             |  |  |

| R                    | 4 | 0      | CAN receive data output (LOW for dominant and HIGH for recessive bus states), also called RXD, receiver output                                                               |  |  |

| R <sub>S</sub>       | 8 | I      | Mode select pin: strong pulldown to GND = high-speed mode, strong pull up to $V_{CC}$ = low-power mode, 10-k $\Omega$ to 100-k $\Omega$ pulldown to GND = slope control mode |  |  |

| V <sub>CC</sub>      | 3 | Supply | Transceiver 5-V supply voltage                                                                                                                                               |  |  |

| V <sub>REF</sub> 5 O |   | 0      | Reference output voltage                                                                                                                                                     |  |  |

#### 6 Specifications

#### 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                                                         |                                 |            | MIN          | MAX                   | UNIT |

|-------------------------------------------------------------------------|---------------------------------|------------|--------------|-----------------------|------|

| Supply voltage, V <sub>CC</sub>                                         | Supply voltage, V <sub>CC</sub> |            |              | 7                     | V    |

| Voltage at any bus pin(CANH or CANL                                     | .)                              |            | -36          | 36                    | V    |

| Transient voltage per ISO 7637, pulse                                   | 1, 2, 3a, 3b                    | CANH, CANL | -200         | 200                   | V    |

| Input voltage, V <sub>I</sub> (D, Rs, or R)                             |                                 |            | -0.3         | V <sub>CC</sub> + 0.5 | V    |

| Receiver output current, I <sub>O</sub>                                 |                                 |            | -10          | 10 mA                 | mA   |

| Electrical fast IEC 61000-4-4, Classification CANH<br>transient/burst B |                                 | CANH, CANL | -3           | 3                     | kV   |

| Continuous total power dissipation                                      |                                 |            | (see Dissipa | tion Ratings)         |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground pin.

#### 6.2 ESD Ratings

|                    |                         |                                                           |                       |        | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------|-----------------------|--------|------|

| V <sub>(ESD)</sub> |                         |                                                           | All pins              | ±6000  |      |

|                    | Electrostatic discharge | ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                     | CANH, CANL and GND    | ±14000 | V    |

|                    |                         | Charged-device model (CDM), per JEDEC C101 <sup>(2)</sup> | specification JESD22- | ±1000  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

|                                                  |                                           | MIN                  | NOM MAX                                                              | UNIT |

|--------------------------------------------------|-------------------------------------------|----------------------|----------------------------------------------------------------------|------|

| Supply voltage, V <sub>CC</sub>                  |                                           | 4.5                  | 5.5                                                                  | V    |

| Voltage at any bus terminal (separately or commo | n mode) V <sub>I</sub> or V <sub>IC</sub> | -7 <sup>(1)</sup>    | 12                                                                   | V    |

| High-level input voltage, V <sub>IH</sub>        | D input                                   | 0.7 V <sub>CC</sub>  |                                                                      | V    |

| Low-level input voltage, VIL                     | D input                                   |                      | 0.3 V <sub>CC</sub>                                                  | V    |

| Differential input voltage, V <sub>ID</sub>      |                                           | 6                    | 6                                                                    | V    |

| Input voltage to Rs, V <sub>I(Rs)</sub>          |                                           | 0                    | V <sub>CC</sub>                                                      | V    |

| Input voltage at Rs for standby, $V_{I(Rs)}$     |                                           | 0.75 V <sub>CC</sub> | V <sub>CC</sub>                                                      | V    |

| Rs wave-shaping resistance                       |                                           | 0                    | 100                                                                  | kΩ   |

| High lovel output ourrest                        | Driver                                    | -50                  |                                                                      | mA   |

| High-level output current, I <sub>OH</sub>       | Receiver                                  | -4                   | 12<br>0.3 V <sub>CC</sub><br>6<br>V <sub>CC</sub><br>V <sub>CC</sub> | ША   |

|                                                  | Driver                                    |                      | 50                                                                   |      |

| Low-level output current, I <sub>OL</sub>        | Receiver                                  |                      | 4                                                                    | mA   |

| Operating free-air temperature, T <sub>A</sub>   | SN65HVD251                                | -40                  | 125                                                                  | °C   |

|                                                  | SN55HVD251                                | -55                  | 125                                                                  | C    |

| Junction temperature, T <sub>J</sub>             |                                           |                      | 145                                                                  | °C   |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

#### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                           | SN55HVD251 | SN65H    |          |      |

|-------------------------------|-------------------------------------------|------------|----------|----------|------|

|                               |                                           | DRJ (SON)  | D (SOIC) | P (PDIP) | UNIT |

|                               |                                           | 8 PINS     | 8 PINS   | 8 PINS   |      |

| $R_{\theta JC(top)}$          | Junction-to-case (top) thermal resistance | 52         | 44.6     | 66.6     | °C/W |

| $R_{	extsf{	heta}JB}$         | Junction-to-board thermal resistance      | 73         | 78.7     | 48.9     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 6.5 Supply Current

over operating free-air temperature range (unless otherwise noted)

| PARAMETER       |                | TEST CONDITIONS | MIN                                          | TYP <sup>(1)</sup> | MAX | UNIT |     |

|-----------------|----------------|-----------------|----------------------------------------------|--------------------|-----|------|-----|

| I <sub>CC</sub> | Supply current | Standby         | Rs at V <sub>CC</sub> , D at V <sub>CC</sub> |                    |     | 275  | μA  |

|                 |                | Dominant        | D at 0 V, 60- $\Omega$ load, Rs at 0 V       |                    |     | 65   | ~ ^ |

|                 |                | Recessive       | D at $V_{CC}$ , no load, Rs at 0 V           |                    |     | 14   | mA  |

(1) All typical values are at 25°C and with a 5-V supply.

#### 6.6 Electrical Characteristics: Driver

over recommended operating conditions (unless otherwise noted).

|                    | PARAMETER                               |                              | TEST CONDITIONS                                                            | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|--------------------|-----------------------------------------|------------------------------|----------------------------------------------------------------------------|------|--------------------|------|------|

| V                  | Bus output voltage                      | Bus output voltage CANH Figu | Figure 10 and Figure 11,                                                   | 2.75 | 3.5                | 4.5  |      |

| V <sub>O(D)</sub>  | (Dominant)                              | CANL                         | D at 0 V Rs at 0 V, T ≥ –40°C                                              | 0.5  |                    | 2    | V    |

| V                  | Bus output voltage                      | CANH                         | Figure 10 and Figure 11 , D at 0.7 $V_{CC}$ ,                              | 2    | 2.5                | 3    | v    |

| V <sub>O(R)</sub>  | (Recessive)                             | essive) CANL Rs at 0 V       | 2                                                                          | 2.5  | 3                  |      |      |

|                    |                                         |                              | Figure 10 , D at 0 V, Rs at 0 V                                            | 1.5  | 2                  | 3    | V    |

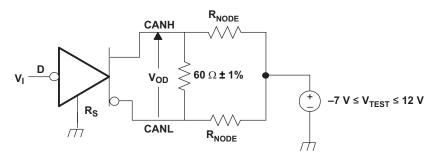

| V <sub>OD(D)</sub> | Differential output voltage (           | Dominant)                    | Figure 12 , D at 0 V, Rs at 0 V, R_{NODE} = 330 $\Omega$                   | 1.2  | 2                  | 3.1  | V    |

| V OD(D)            |                                         |                              | Figure 12 , D at 0 V, Rs at 0 V, R_{NODE} = 165 $\Omega,V_{CC} \ge 4.75$ V | 1.2  | 2                  | 3.1  | V    |

| V                  | Differential output valteres (          |                              | Figure 10 and Figure 11 , D at 0.7 $V_{CC}$                                | -120 |                    | 12   | mV   |

| V <sub>OD(R)</sub> | Differential output voltage (Recessive) |                              | D at 0.7 V <sub>CC</sub> , no load, T $\leq$ 85°C                          | -0.5 |                    | 0.05 | V    |

(1) All typical values are at 25°C and with a 5-V supply.

Copyright © 2002–2015, Texas Instruments Incorporated

#### **Electrical Characteristics: Driver (continued)**

over recommended operating conditions (unless otherwise noted).

|                     | PARAMETER                                 | TEST CONDITIONS                                 | MIN  | TYP <sup>(1)</sup> | MAX | UNIT |

|---------------------|-------------------------------------------|-------------------------------------------------|------|--------------------|-----|------|

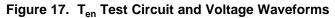

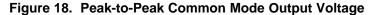

| V <sub>OC(pp)</sub> | Peak-to-peak common-mode output voltage   | Figure 18, Rs at 0 V                            |      | 600                |     | mV   |

| I <sub>IH</sub>     | High-level input current, D Input         | D at 0.7 V <sub>CC</sub>                        | -40  |                    | 0   | μA   |

| Ι <sub>ΙL</sub>     | Low-level input current, D Input          | D at 0.3 V <sub>CC</sub>                        | -60  |                    | 0   | μA   |

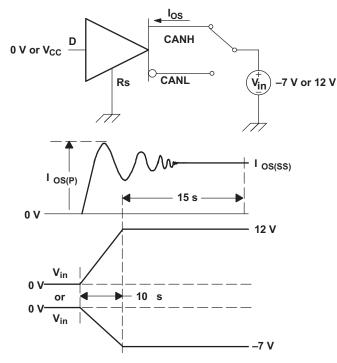

|                     | Short-circuit steady-state output current | Figure 20, V <sub>CANH</sub> at –7 V, CANL Open | -200 |                    |     |      |

|                     |                                           | Figure 20, V <sub>CANH</sub> at 12 V, CANL Open |      |                    | 2.5 | ~ ^  |

| I <sub>OS(SS)</sub> |                                           | Figure 20, V <sub>CANL</sub> at -7 V, CANH Open | -2   |                    |     | mA   |

|                     |                                           | Figure 20, V <sub>CANL</sub> at 12 V, CANH Open |      |                    | 200 |      |

| Co                  | Output capacitance                        | See receiver input capacitance                  |      |                    |     |      |

| I <sub>OZ</sub>     | High-impedance output current             | See receiver input current                      |      |                    |     |      |

| I <sub>IRs(s)</sub> | Rs input current for standby              | Rs at 0.75 V <sub>CC</sub>                      | -10  |                    |     | μA   |

| I <sub>IRs(f)</sub> | Rs input current for full speed operation | Rs at 0 V                                       | -550 |                    | 0   | μA   |

#### 6.7 Electrical Characteristics: Receiver

over recommended operating conditions (unless otherwise noted).

|                  | PARAMETER                                                 | TEST CONDITIC                                                                        | NS                                                                 | MIN                 | TYP | MAX                 | UNIT |

|------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------|-----|---------------------|------|

| V <sub>IT+</sub> | Positive-going input threshold voltage                    |                                                                                      |                                                                    |                     | 750 | 900                 |      |

| V <sub>IT-</sub> | Negative-going input threshold voltage                    | Rs at 0 V, (See Table 1)                                                             |                                                                    | 500                 | 650 |                     | mV   |

| $V_{\text{hys}}$ | Hysteresis voltage (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                                      |                                                                    |                     | 100 |                     |      |

| V <sub>OH</sub>  | High-level output voltage                                 | Figure 15, $I_0 = -4 \text{ mA}$                                                     |                                                                    | 0.8 V <sub>CC</sub> |     |                     | V    |

| V <sub>OL</sub>  | Low-level output voltage                                  | Figure 15, $I_0 = 4 \text{ mA}$                                                      |                                                                    |                     |     | 0.2 V <sub>CC</sub> | V    |

|                  | Bus input current                                         | CANH or CANL at 12 V                                                                 |                                                                    |                     |     | 600                 |      |

|                  |                                                           | CANH or CANL at 12 V,<br>V <sub>CC</sub> at 0 V                                      | Other bus<br>pin at 0 V,<br>Rs at 0 V, D<br>at 0.7 V <sub>CC</sub> |                     |     | 715                 |      |

| II.              |                                                           | CANH or CANL at -7 V                                                                 |                                                                    | -460                |     |                     | μA   |

|                  |                                                           | CANH or CANL at -7 V, $V_{CC}$ at 0 V                                                |                                                                    | -340                |     |                     |      |

| CI               | Input capacitance, (CANH or CANL)                         | Pin-to-ground, $V_I = 0.4 \sin(0.05)$                                                | 4E6πt) + 0.5                                                       |                     | 20  |                     | pF   |

| C <sub>ID</sub>  | Differential input capacitance                            | Pin-to-pin, V <sub>I</sub> = 0.4 sin (4E6 $\pi$ t) + 0.5 V, D at 0.7 V <sub>CC</sub> |                                                                    |                     | 10  |                     | pF   |

| R <sub>ID</sub>  | Differential input resistance                             | D at 0.7 V <sub>CC</sub> , Rs at 0 V                                                 |                                                                    | 40                  |     | 100                 | kΩ   |

| R <sub>IN</sub>  | Input resistance, (CANH or CANL)                          | D at 0.7 V <sub>CC</sub> , Rs at 0 V                                                 |                                                                    | 20                  |     | 50                  | kΩ   |

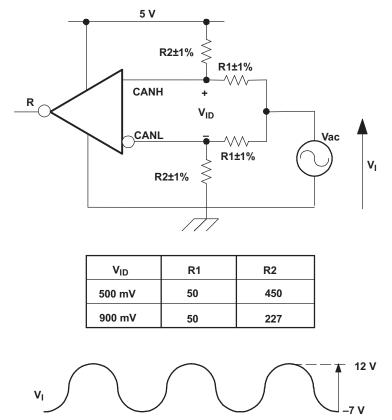

|                  | Receiver noise rejection                                  | See Figure 22                                                                        |                                                                    |                     |     |                     |      |

#### 6.8 VREF-Pin Characteristics

over recommended operating conditions (unless otherwise noted).

|                             | PARAMETER                       | TEST CONDITIONS     | MIN                 | TYP MAX | UNIT |

|-----------------------------|---------------------------------|---------------------|---------------------|---------|------|

| Vo Reference output voltage | –5 μA < I <sub>O</sub> < 5 μA   | $0.45 V_{CC}$       | $0.55 V_{CC}$       |         |      |

|                             | –50 μA < I <sub>O</sub> < 50 μA | 0.4 V <sub>CC</sub> | 0.6 V <sub>CC</sub> | v       |      |

#### 6.9 Power Dissipation Characteristics

|                 | PARAMETER                             | TEST CONDITIONS                                                                                                                                               | MIN  | TYP | MAX | UNIT |

|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| P <sub>D</sub>  | Device power dissipation              | $V_{CC} = 5 \text{ V}, \text{ Tj} = 27^{\circ}\text{C}, \text{ RL} = 60 \Omega,$<br>R <sub>S</sub> at 0 V, Input to D a 500-kHz<br>50% duty cycle square wave | 97.7 |     | mW  |      |

|                 |                                       | $V_{CC}$ = 5.5 V, Tj = 130°C, RL = 60 $\Omega$ ,<br>R <sub>S</sub> at 0 V, Input to D a 500-kHz<br>50% duty cycle square wave                                 |      | 142 |     | mW   |

| T <sub>SD</sub> | Thermal shutdown junction temperature |                                                                                                                                                               |      | 165 |     | °C   |

#### 6.10 Switching Characteristics: Driver

over recommended operating conditions (unless otherwise noted).

|                    | PARAMETER                                           | TEST CONDITIONS                             | MIN | TYP  | MAX  | UNIT |

|--------------------|-----------------------------------------------------|---------------------------------------------|-----|------|------|------|

|                    |                                                     | Figure 13, Rs at 0 V                        |     | 40   | 70   |      |

| t <sub>pLH</sub>   | Propagation delay time, low-to-high-level output    | Figure 13, Rs with 10 k $\Omega$ to ground  |     | 90   | 125  |      |

|                    |                                                     | Figure 13, Rs with 100 k $\Omega$ to ground |     | 500  | 800  |      |

|                    |                                                     | Figure 13, Rs at 0 V                        |     | 85   | 125  |      |

| t <sub>pHL</sub>   | Propagation delay time, high-to-low-level output    | Figure 13, Rs with 10 k $\Omega$ to ground  |     | 200  | 260  |      |

|                    |                                                     | Figure 13, Rs with 100 k $\Omega$ to ground |     | 1150 | 1450 |      |

|                    |                                                     | Figure 13, Rs at 0 V                        |     | 45   | 85   |      |

| t <sub>sk(p)</sub> | Pulse skew ( t <sub>pHL</sub> - t <sub>pLH</sub>  ) | Figure 13, Rs with 10 k $\Omega$ to ground  |     | 110  | 180  | ns   |

|                    |                                                     | Figure 13, Rs with 100 k $\Omega$ to ground |     | 650  | 900  |      |

| t <sub>r</sub>     | Differential output signal rise time                |                                             | 35  | 80   | 100  |      |

| t <sub>f</sub>     | Differential output signal fall time                | Figure 13, Rs at 0 V                        | 35  | 80   | 100  |      |

| t <sub>r</sub>     | Differential output signal rise time                |                                             | 100 | 150  | 250  |      |

| t <sub>f</sub>     | Differential output signal fall time                | Figure 13, Rs with 10 kΩ to ground          | 100 | 150  | 250  |      |

| t <sub>r</sub>     | Differential output signal rise time                |                                             | 600 | 950  | 1550 |      |

| t <sub>f</sub>     | Differential output signal fall time                | Figure 13, Rs with 100 kΩ to ground         | 600 | 950  | 1550 |      |

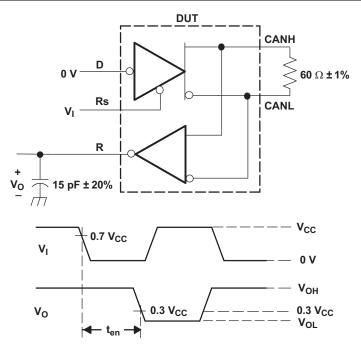

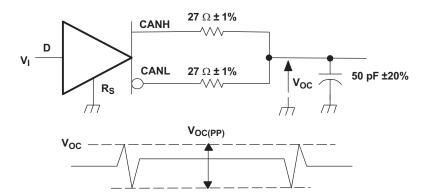

| t <sub>en</sub>    | Enable time from standby to dominant                | Figure 17                                   |     |      | 0.5  | μs   |

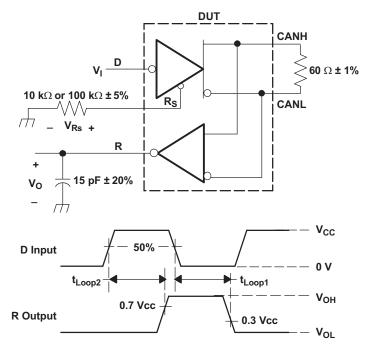

#### 6.11 Switching Characteristics: Device

over recommended operating conditions (unless otherwise noted).

|                    | PARAMETER                                                                   | TEST CONDITIONS                                    | MIN | TYP  | MAX  | UNIT |

|--------------------|-----------------------------------------------------------------------------|----------------------------------------------------|-----|------|------|------|

|                    | Total loop delay, driver input to receiver<br>output, recessive to dominant | Figure 19, Rs at 0 V                               |     | 60   | 100  |      |

| t <sub>loop1</sub> |                                                                             | Figure 19, Rs with 10 k $\Omega$ to ground         |     | 100  | 150  | ns   |

|                    |                                                                             | Figure 19, Rs with 100 k $\Omega$ to ground        |     | 440  | 800  |      |

|                    |                                                                             | Figure 19, Rs at 0 V                               |     | 115  | 150  | ns   |

| t <sub>loop2</sub> | Total loop delay, driver input to receiver<br>output, dominant to recessive | Figure 19, Rs with 10 k $\Omega$ to ground         |     | 235  | 290  |      |

|                    | output, dominant to recessive                                               | Figure 19, Rs with 100 k $\Omega$ to ground        |     | 1070 | 1450 |      |

| t <sub>loop2</sub> | Total loop delay, driver input to receiver output, dominant to recessive    | Figure 19, Rs at 0 V, $V_{CC}$ from 4.5 V to 5.1 V |     | 105  | 145  | ns   |

SLLS545G-NOVEMBER 2002-REVISED OCTOBER 2015

www.ti.com

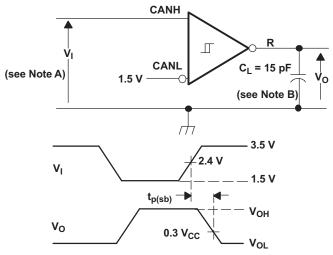

#### 6.12 Switching Characteristics: Receiver

over recommended operating conditions (unless otherwise noted).

|                    | PARAMETER                                           | TEST CONDITIONS                  | MIN | TYP | MAX | UNIT |

|--------------------|-----------------------------------------------------|----------------------------------|-----|-----|-----|------|

| t <sub>pLH</sub>   | Propagation delay time, low-to-high-level output    |                                  |     | 35  | 50  |      |

| t <sub>pHL</sub>   | Propagation delay time, high-to-low-level output    | Figure 15                        |     | 35  | 50  |      |

| t <sub>sk(p)</sub> | Pulse skew ( t <sub>pHL</sub> - t <sub>pLH</sub>  ) |                                  |     |     | 20  |      |

| t <sub>r</sub>     | Output signal rise time                             |                                  |     | 2   | 4   | ns   |

| t <sub>f</sub>     | Output signal fall time                             |                                  |     | 2   | 4   |      |

| t <sub>p(sb)</sub> | Propagation delay time in standby                   | Figure 21, Rs at V <sub>CC</sub> |     |     | 500 |      |

#### 6.13 Dissipation Ratings

| PACKAGE              | CIRCUIT BOARD<br>MODEL             | T <sub>A</sub> = 25°C<br>POWER RATING | DERATING FACTOR <sup>(1)</sup><br>ABOVE $T_A = 25^{\circ}C$ | T <sub>A</sub> = 85°C POWER<br>RATING | T <sub>A</sub> = 125°C POWER<br>RATING |  |

|----------------------|------------------------------------|---------------------------------------|-------------------------------------------------------------|---------------------------------------|----------------------------------------|--|

| Low-K <sup>(2)</sup> |                                    | 576 mW                                | 4.8 mW/°C                                                   | 288 mW                                | 96 mW                                  |  |

| SOIC (D)             | High-K <sup>(3)</sup>              | 924 mW                                | 7.7 mW/°C                                                   | 462 mW                                | 154 mW                                 |  |

| Low-K <sup>(2)</sup> |                                    | 888 mW                                | 7.4 mW/°C                                                   | 444 mW                                | 148 mW                                 |  |

| PDIP (P)             | High-K <sup>(3)</sup>              | 1212 mW                               | 10.1 mW/°C                                                  | 606 mW                                | 202 mW                                 |  |

|                      | Low-K <sup>(2)</sup>               | 403 mW                                | 4.03 mW/°C                                                  | 262 mW                                | 100 mW                                 |  |

| WSON (DRJ)           | High-K<br>(no Vias) <sup>(3)</sup> | 1081 mW                               | 10.8 mW/°C                                                  | 703 mW                                | 270 mW                                 |  |

|                      | High-K<br>(with Vias)              | 2793 mW                               | 27.9 mW/°C                                                  | 1815 mW                               | 698 mW                                 |  |

This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow. (1)

(2) (3) In accordance with the Low-K thermal metric definitions of EIA/JESD51-3.

In accordance with the High-K thermal metric definitions of EIA/JESD51-7.

8

Copyright © 2002–2015, Texas Instruments Incorporated

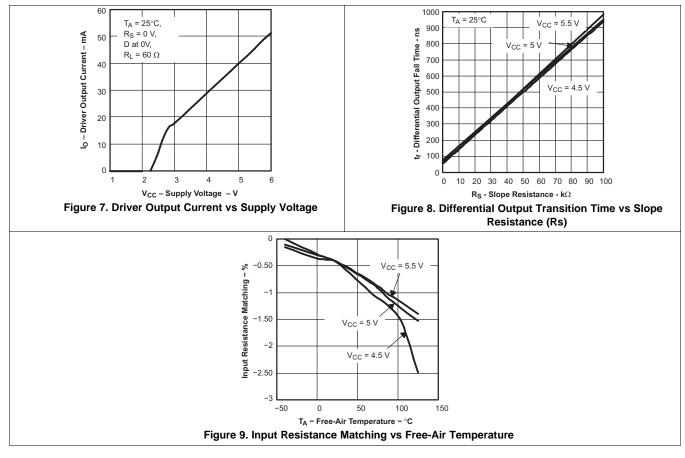

#### 6.14 Typical Characteristics

#### **Typical Characteristics (continued)**

Copyright © 2002–2015, Texas Instruments Incorporated

#### 7 Parameter Measurement Information

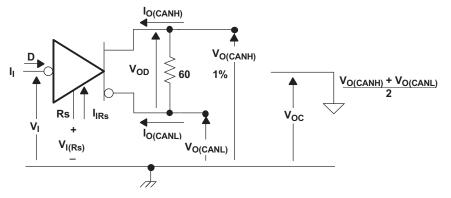

Figure 12. Driver V<sub>OD</sub>

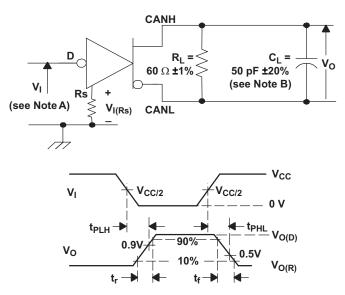

Figure 13. Driver Test Circuit and Voltage Waveforms

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle, t<sub>r</sub>  $\leq$  6ns, t<sub>f</sub>  $\leq$  6ns, Z<sub>O</sub> = 50  $\Omega$ .

- B. C<sub>L</sub> includes instrumentation and fixture capacitance within ±20%.

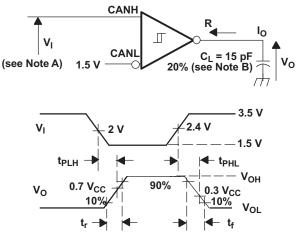

#### Figure 15. Receiver Test Circuit and Voltage Waveforms

This test is conducted to test survivability only. Data stability at the R output is not specified.

Figure 16. Test Circuit, Transient Overvoltage Test

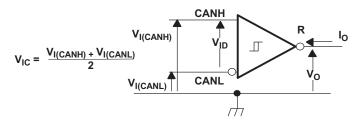

| Table 1. Receiver Characteristics Over Common Mode Voltage |

|------------------------------------------------------------|

|------------------------------------------------------------|

|                   |                   |                    | •      |                 |  |

|-------------------|-------------------|--------------------|--------|-----------------|--|

| INF               | TUT               | DIFFERENTIAL INPUT | OUTPUT |                 |  |

| V <sub>CANH</sub> | V <sub>CANL</sub> | V <sub>ID</sub>    | I      | א               |  |

| 12 V              | 11.1 V            | 900 mV             | L      |                 |  |

| –6.1 V            | -7 V              | 900 mV             |        | V               |  |

| -1 V              | -7 V              | 6 V                | L      | V <sub>OL</sub> |  |

| 12 V              | 6 V               | 6 V                | L      |                 |  |

| –6.5 V            | -7 V              | 500 mV             | Н      |                 |  |

| 12 V              | 11.5 V            | 500 mV             | Н      |                 |  |

| -7 V              | -1 V              | 6 V                | Н      | V <sub>OH</sub> |  |

| 6 V               | 12 V              | 6 V                | Н      |                 |  |

| open              | open              | Х                  | Н      |                 |  |

The input pulse is supplied by a generator having the following characteristics: PRR ≤ 125 kHz, 50% duty cycle,  $t_r \le 6ns$ ,  $t_f \le 6ns$ ,  $Z_O = 50 \Omega$ .

Figure 19. TLOOP Test Circuit and Voltage Waveforms

Figure 20. Driver Short-Circuit Test

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle, t<sub>r</sub>  $\leq$  6ns, t<sub>f</sub>  $\leq$  6ns, Z<sub>O</sub> = 50  $\Omega$ .

- B. CL includes instrumentation and fixture capacitance within ±20%.

#### Figure 21. Receiver Propagation Delay in Standby Test Circuit and Waveform

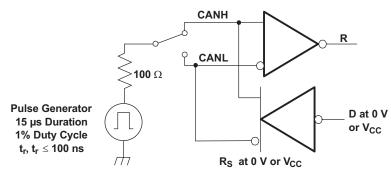

- A. All input pulses are supplied by a generator having the following characteristics:  $f_{IN} < 1.5$  MHz,  $T_A = 25^{\circ}$ C,  $V_{CC} = 5$  V.

- B. The receiver output should not change state during application of the common-mode input waveform.

Figure 22. Common-Mode Input Voltage Rejection Test

#### 8 Detailed Description

#### 8.1 Overview

The SNx5HVD251CAN bus transceiver is compatible with the ISO 11898-2 High Speed CAN (Controller Area Network) physical layer standard. It is design to interface between the differential bus lines in controller area network and the CAN protocol controller at data rates up to 1 Mbps.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

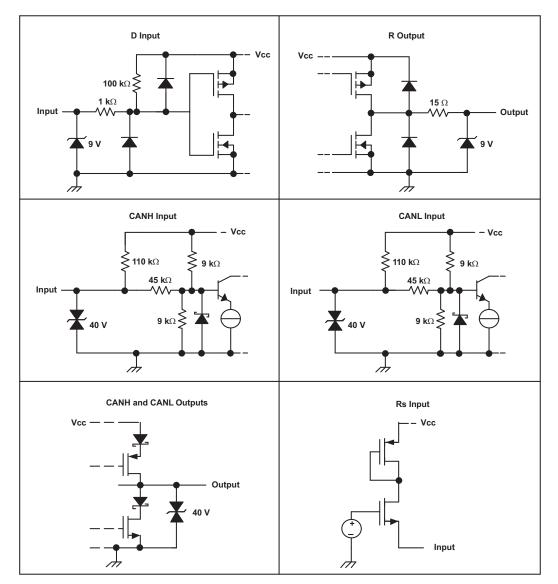

Figure 23. Function Diagram (Positive Logic)

#### 8.3.1 Mode Control

R<sub>S</sub>, Pin 8, selects one of three possible modes of operation: high-speed, slope control, or low-power mode.

#### 8.3.2 High-Speed Mode

The high-speed mode of operation can be selected by setting  $R_S$  (Pin 8) low. High-speed allows the output to switch as fast as possible with no internal limitations on the output rise and fall slopes. The CAN bus driver and receiver are fully operational and the CAN communication is bi-directional. The driver is translating a digital input on D to a differential output on CANH and CANL. The receiver is translating the differential signal from CANH and CANL to a digital output on R.

#### 8.3.3 Slope Control Mode

The rise and fall slope of the SNx5HVD251 driver output can be adjusted by connecting a resistor from Rs (Pin 8) to ground (GND), or to a low-level input voltage as shown in Figure 24. The slope of the driver output signal is proportional to the pin's output current. This slope control is implemented with an external resistor value of 10 k $\Omega$  to achieve a ~15-V/µs slew rate, and up to 100 k $\Omega$  to achieve a ~2.0-V/µs slew rate. Figure 8 shows a plot of differential output transition time vs slope resistance from which the slew rate can be calculated.

Copyright © 2002–2015, Texas Instruments Incorporated

18

#### 8.3.4 Low-Power Mode

If a high-level input (>0.75 V<sub>CC</sub>) is applied to R<sub>S</sub> (Pin 8), the circuit enters a low-current, listen only standby mode during which the driver is switched off and the receiver remains active. If using this mode to save system power while waiting for bus traffic, the local controller can monitor the R output pin for a falling edge which indicates that a dominant signal was driven onto the CAN bus. The local controller can then drive the R<sub>S</sub> pin low to return to slope control mode or high-speed mode.

# NOTE

Silent mode may be used to implement babbling idiot protection, to ensure that the driver does not disrupt the network during a local fault. Silent mode may also be used in redundant systems to select or de-select the redundant transceiver (driver) when needed.

Figure 24. Slope Control

#### 8.3.5 Thermal Shutdown

The SNx5HVD251 has a thermal shutdown feature that turns off the driver outputs when the junction temperature nears 165°C. This shutdown prevents catastrophic failure from bus shorts, but does not protect the circuit from possible damage. The user should strive to maintain recommended operating conditions and not exceed absolute-maximum ratings at all times. If an SNx5HVD251 is subjected to many, or long-duration faults that can put the device into thermal shutdown, it should be replaced.

#### 8.4 Device Functional Modes

| INPUTS | Veltere et P V                              | OUT  | OUTPUTS |           |  |  |  |  |  |

|--------|---------------------------------------------|------|---------|-----------|--|--|--|--|--|

| D      | Voltage at R <sub>s</sub> , V <sub>Rs</sub> | CANH | CANL    | BUS STATE |  |  |  |  |  |

| L      | V <sub>Rs</sub> < 1.2 V                     | Н    | L       | Dominant  |  |  |  |  |  |

| Н      | V <sub>Rs</sub> < 1.2 V                     | Z    | Z       | Recessive |  |  |  |  |  |

| Open   | X                                           | Z    | Z       | Recessive |  |  |  |  |  |

| Х      | V <sub>Rs</sub> > 0.75 V <sub>CC</sub>      | Z    | Z       | Recessive |  |  |  |  |  |

| Х      | Open                                        | Z    | Z       | Recessive |  |  |  |  |  |

#### Table 2. Driver

#### Table 3. Receiver

| DIFFERENTIAL INPUTS [V <sub>ID</sub> = V(CANH) - V(CANL)] | OUTPUT R <sup>(1)</sup> |

|-----------------------------------------------------------|-------------------------|

| $V_{ID} \ge 0.9 V$                                        | L                       |

| 0.5 V < V <sub>ID</sub> < 0.9 V                           | ?                       |

| $V_{ID} \le 0.5 V$                                        | н                       |

| Open                                                      | Н                       |

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate; Z = high impedance

Figure 25. Equivalent Input and Output Schematic Diagrams

Copyright © 2002–2015, Texas Instruments Incorporated

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

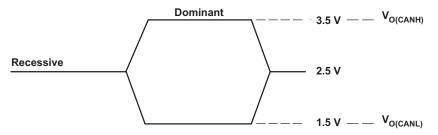

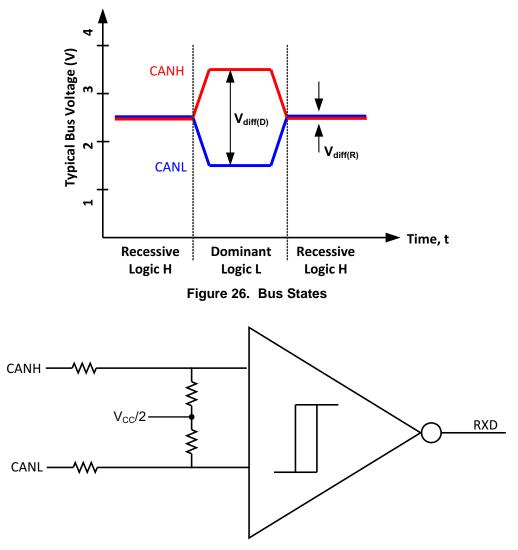

The CAN bus has two states during powered operation of the device; dominant and recessive. A dominant bus state is when the bus is driven differentially, corresponding to a logic low on the D and R pin. A recessive bus state is when the bus is biased to  $V_{CC}/2$  via the high-resistance internal resistors  $R_{IN}$  and  $R_{ID}$  of the receiver, corresponding to a logic high on the D and R pins. See Figure 26 and Figure 27.

Figure 27. Simplified Recessive Common Mode Bias and Receiver

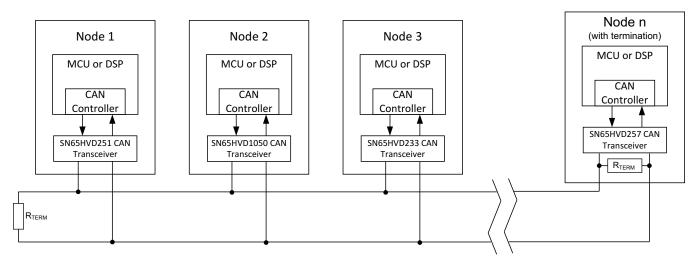

The HVD251 CAN transceiver is typically used in applications with a host microprocessor or FPGA that includes the link layer portion of the CAN protocol. The different nodes on the network are typically connected through the use of a 120- $\Omega$  characteristic impedance twisted pair cable with termination on both ends of the bus.

Copyright © 2002–2015, Texas Instruments Incorporated

#### **Application Information (continued)**

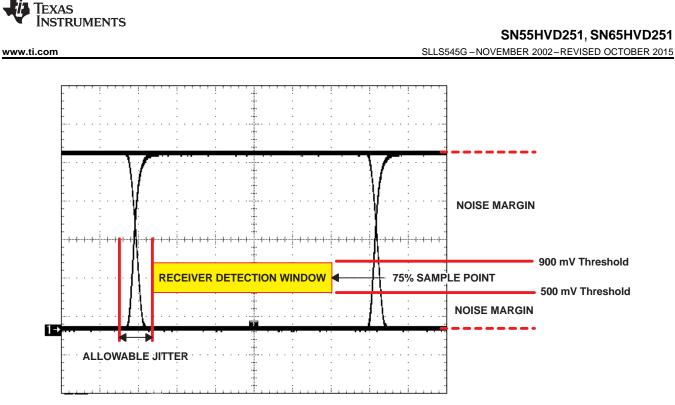

The basics of bus arbitration require that the receiver at the sending node designate the first bit as dominant or recessive after the initial wave of the first bit of a message travels to the most remote node on a network and back again. Typically, this *sample* is made at 75% of the bit width, and within this limitation, the maximum allowable signal distortion in a CAN network is determined by network electrical parameters.

Factors to be considered in network design include the 5 ns/m propagation delay of typical twisted-pair bus cable; signal amplitude loss due to the loss mechanisms of the cable; and the number, length, and spacing of drop-lines (stubs) on a network. Under strict analysis, variations among the different oscillators in a system must also be accounted for with adjustments in signaling rate and stub and bus length. Table 4 lists the maximum signaling rates achieved with the HVD251 in high-speed mode with several bus lengths of category-5, shielded twisted-pair (CAT 5 STP) cable.

| C C            |                       |  |  |  |  |  |  |  |

|----------------|-----------------------|--|--|--|--|--|--|--|

| BUS LENGTH (m) | SIGNALING RATE (kbps) |  |  |  |  |  |  |  |

| 30             | 1000                  |  |  |  |  |  |  |  |

| 100            | 500                   |  |  |  |  |  |  |  |

| 250            | 250                   |  |  |  |  |  |  |  |

| 500            | 125                   |  |  |  |  |  |  |  |

| 1000           | 62.5                  |  |  |  |  |  |  |  |

# Table 4. Maximum Signaling Rates for Various Cable Lengths

The ISO 11898 standard specifies a maximum bus length of 40 meters and maximum stub length of 0.3 meters with a maximum of 30 nodes. However, with careful design, users can have longer cables, longer stub lengths, and many more nodes on a bus. (Note: Non-standard application may come with a trade-off in signaling rate.) A bus with a large number of nodes requires a transceiver with high input impedance such as the HVD251.

The Standard specifies the interconnect to be a single twisted-pair cable (shielded or unshielded) with  $120-\Omega$  characteristic impedance (Zo). Resistors equal to the characteristic impedance of the line terminate both ends of the cable to prevent signal reflections. Unterminated drop-lines connect nodes to the bus and should be kept as short as possible to minimize signal reflections.

Connectors, while not specified by the ISO 11898 standard, should have as little effect as possible on standard operating parameters such as capacitive loading. Although unshielded cable is used in many applications, data transmission circuits employing CAN transceivers are usually used in applications requiring a rugged interconnection with a wide common-mode voltage range. Therefore, shielded cable is recommended in these electronically harsh environments, and when coupled with the -2-V to 7-V common-mode range of tolerable ground noise specified in the standard, helps to ensure data integrity. The HVD251 extends data integrity beyond that of the standard with an extended -7-V to 12-V range of common-mode operation.

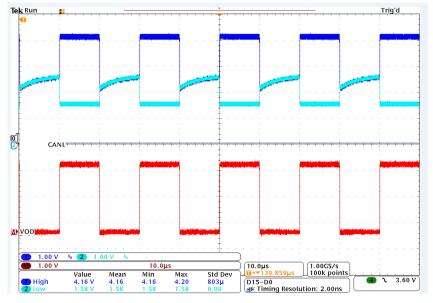

Figure 28. Typical CAN Differential Signal Eye-Pattern

An eye pattern is a useful tool for measuring overall signal quality. As displayed in Figure 28, the differential signal changes logic states in two places on the display, producing an *eye*. Instead of viewing only one logic crossing on the scope, an entire *bit* of data is brought into view. The resulting eye pattern includes all effects of systemic and random distortion, and displays the time during which a signal may be considered valid.

The height of the eye above or below the receiver threshold voltage level at the sampling point is the noise margin of the system. Jitter is typically measured at the differential voltage zero-crossing during the logic state transition of a signal. Note that jitter present at the receiver threshold voltage level is considered by some to be a more effective representation of the jitter at the input of a receiver.

As the sum of skew and noise increases, the eye closes and data is corrupted. Closing the width decreases the time available for accurate sampling, and lowering the height enters the 900-mV or 500-mV threshold of a receiver.

Different sources induce noise onto a signal. The more obvious noise sources are the components of a transmission circuit themselves; the signal transmitter, traces & cables, connectors, and the receiver. Beyond that, there is a termination dependency, cross-talk from clock traces and other proximity effects, V<sub>CC</sub> and ground bounce, and electromagnetic interference from near-by electrical equipment.

The balanced receiver inputs of the HVD251 mitigate most sources of signal corruption, and when used with a quality shielded twisted-pair cable, help meet data integrity.

#### SN55HVD251, SN65HVD251 SLLS545G – NOVEMBER 2002 – REVISED OCTOBER 2015

www.ti.com

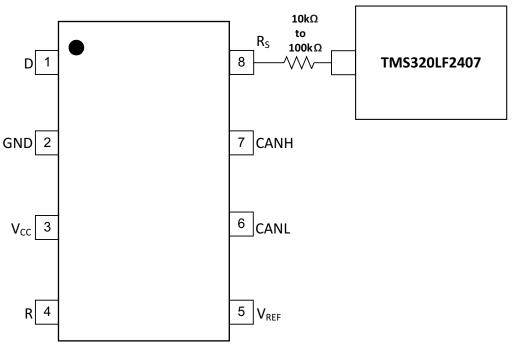

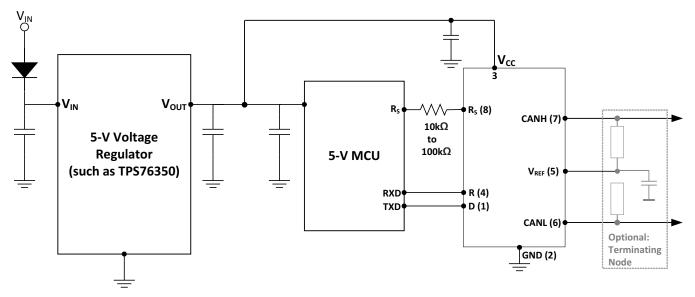

#### 9.2 Typical Application

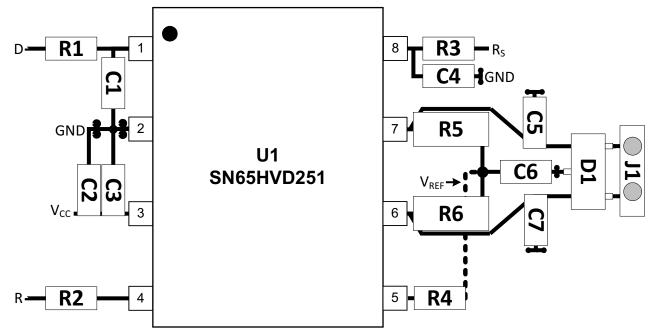

Figure 29. Typical Application Schematic

#### 9.2.1 Design Requirements

#### 9.2.1.1 Bus Loading, Length, and Number of Nodes

The ISO11898 Standard specifies up to 1-Mbps data rate, maximum bus length of 40 meters, maximum drop line (stub) length of 0.3 meters and a maximum of 30 nodes. However, with careful network design, the system may have longer cables, longer stub lengths, and many more nodes to a bus. Many CAN organizations and standards have scaled the use of CAN for applications outside the original ISO11898 standard. They have made system level trade-offs for data rate, cable length, and parasitic loading of the bus. Examples of some of these specifications are ARINC825, CANopen, CAN Kingdom, DeviceNet and NMEA200.

Figure 30. Typical CAN Bus

#### **Typical Application (continued)**

A high number of nodes requires a transceiver with high input impedance and wide common mode range such as the SNx5HVD251 CAN transceiver. ISO11898-2 specifies the driver differential output with a 60- $\Omega$  load (two 120- $\Omega$  termination resistors in parallel) and the differential output must be greater than 1.5 V. The SNx5HVD251 devices are specified to meet the 1.5-V requirement with a 60- $\Omega$  load, and additionally specified with a differential output voltage minimum of 1.2 V across a common mode range of -2 V to 7 V via a 330- $\Omega$  coupling network. This network represents the bus loading of 120 SNx5HVD251 transceivers based on their minimum differential input resistance of 40 k $\Omega$ . Therefore, the SNx5HVD251 supports up to 120 transceivers on a single bus segment with margin to the 1.2-V minimum differential input voltage requirement at each node.

For CAN network design, margin must be given for signal loss across the system and cabling, parasitic loadings, network imbalances, ground offsets and signal integrity thus a practical maximum number of nodes may be lower. Bus length may also be extended beyond the original ISO 11898 standard of 40 meters by careful system design and data rate tradeoffs. For example, CANopen network design guidelines allow the network to be up to 1 km with changes in the termination resistance, cabling, less than 64 nodes and significantly lowered data rate.

This flexibility in CAN network design is one of the key strengths of the various extensions and additional standards that have been built on the original ISO 11898 CAN standard.

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 CAN Termination

The ISO 11898 standard specifies the interconnect to be a twisted pair cable (shielded or unshielded) with 120- $\Omega$  characteristic impedance (Z<sub>O</sub>). Resistors equal to the characteristic impedance of the line should be used to terminate both ends of the cable to prevent signal reflections. Unterminated drop lines (stubs) connecting nodes to the bus should be kept as short as possible to minimize signal reflections. The termination may be on the cable or in a node, but if nodes may be removed from the bus the termination must be carefully placed so that it is not removed from the bus.

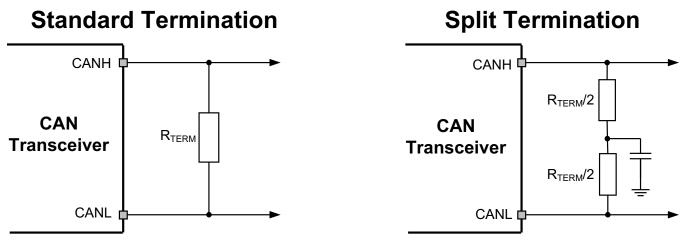

Termination is typically a  $120-\Omega$  resistor at each end of the bus. If filtering and stabilization of the common mode voltage of the bus is desired, then split termination may be used (see Figure 30). Split termination utilizes two 60- $\Omega$  resistors with a capacitor in the middle of these resistors to ground. Split termination improves the electromagnetic emissions behavior of the network by eliminating fluctuations in the bus common mode voltages at the start and end of message transmissions.

Care should be taken when determining the power ratings of the termination resistors. A typical worst case fault condition is if the system power supply and ground were shorted across the termination resistance which would result in much higher current through the termination resistance than the CAN transceiver's current limit.

#### **Typical Application (continued)**

#### 9.2.2.2 Loop Propagation Delay

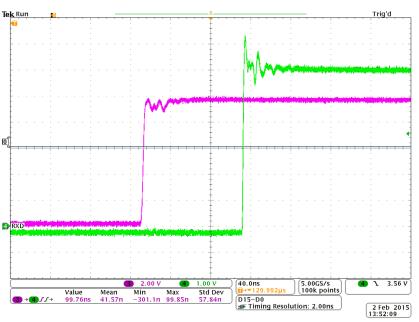

Transceiver loop delay is a measure of the overall device propagation delay, consisting of the delay from the driver input (D pin) to the differential outputs (CANH and CANL pins), plus the delay from the receiver inputs (CANH and CANL) to its output pin.

A typical loop delay for the SNx5HVD251 transceiver is displayed in Figure 32. This loop delay will increase as the slope of the driver output is slowed during slope control mode. This increased loop delay means that there is a tradeoff between the total bus length able to be used and the driver's output slope used via the slope control pin of the device. For example, the loop delay for a  $10 \cdot k\Omega$  resistor from the R<sub>S</sub> pin to ground is ~100 ns, and the loop delay for a  $100 \cdot k\Omega$  resistor is ~500 ns. Therefore, if we use the following rule-of-thumb that the propagation delay of typical twisted pair bus cable is 5 ns/m, we can calculate an approximate cable length trade-off between normal high-speed mode and slope control mode with a  $100 \cdot k\Omega$  resistor. Using typical values, the loop delay for a recessive to dominant bit with R<sub>S</sub> tied directly to ground is 60ns, and with a  $100 \cdot k\Omega$  resistor is 440 ns. At 5-ns/m of propagation delay, which you have to count in both directions the difference is 38 meters (440 - 60)/(2 x 5).

Another option to improving the electromagnetic emissions of the device besides slowing down the edge rates of the driver in slope control mode is using quality shielded bus cabling.

#### 9.2.3 Application Curve

Figure 32. t<sub>LOOP</sub> Delay

#### 9.3 System Example

#### 9.3.1 ISO 11898 Compliance of HVD251 5-V CAN Bus Transceiver

#### 9.3.1.1 Introduction

The SNx5HVD251 CAN transceiver is a 5-V CAN transceiver that meets or exceeds the specification of the ISO 11898 standard for applications employing a controller area network.

#### 9.3.1.2 Differential Signal

CAN is a differential bus where complementary signals are sent over two wires and the voltage difference between the two wires defines the logical state of the bus. The differential CAN receiver monitors this voltage difference and outputs the bus state with a single ended logic level output signal.

#### System Example (continued)

Figure 33. Differential Output Waveform

The CAN driver creates the differential voltage between CANH and CANL in the dominant state. The dominant differential output of the HVD251 is greater than 1.5 V and less than 3 V across a  $60-\Omega$  load as defined by the ISO 11898 standard. Figure 33 shows CANH, CANL, and the differential dominant state level for the SNx5HVD251.

A CAN receiver is required to output a recessive state when less than 500 mV of differential voltage exists on the bus, and a dominant state when more than 900 mV of differential voltage exists on the bus. The CAN receiver must do this with common-mode input voltages from -2 V to 7 V.

#### 9.3.1.3 Common-Mode Signal

A common-mode signal is an average voltage of the two signal wires that the differential receiver rejects. The common-mode signal comes from the CAN driver, ground noise, and coupled bus noise. Since the bias voltage of the recessive state of the device is dependent on  $V_{CC}$ , any noise present or variation of  $V_{CC}$  will have an effect on this bias voltage seen by the bus. The HVD251 CAN transceiver has the recessive bias voltage set to 0.5 x  $V_{CC}$  to comply with the ISO 11898-2 CAN standard.

#### **10** Power Supply Recommendations

To ensure reliable operation at all data rates and supply voltages, each supply should be decoupled with a 100nF ceramic capacitor located as close as possible to the  $V_{CC}$  supply pins as possible. The TPS76350 is a linear voltage regulator suitable for the 5-V supply rail.

#### 11 Layout

#### 11.1 Layout Guidelines

In order for the PCB design to be successful, start with design of the protection and filtering circuitry. Because ESD and EFT transients have a wide frequency bandwidth from approximately 3-MHz to 3-GHz, high frequency layout techniques must be applied during PCB design. On chip IEC ESD protection is good for laboratory and portable equipment but is usually not sufficient for EFT and surge transients occurring in industrial environments. Therefore robust and reliable bus node design requires the use of external transient protection devices at the bus connectors. Placement at the connector also prevents these harsh transient events from propagating further into the PCB and system.

Use V<sub>CC</sub> and ground planes to provide low inductance.

NOTE

High frequency current follows the path of least inductance and not the path of least resistance.

Design the bus protection components in the direction of the signal path. Do not force the transient current to divert from the signal path to reach the protection device.

An example placement of the Transient Voltage Suppression (TVS) device indicated as D1 (either bi-directional diode or varistor solution) and bus filter capacitors C5 and C7 are shown in Figure 34.

The bus transient protection and filtering components should be placed as close to the bus connector, J1, as possible. This prevents transients, ESD and noise from penetrating onto the board and disturbing other devices.

Bus termination: Figure 31 shows split termination. This is where the termination is split into two resistors, R5 and R6, with the center or split tap of the termination connected to ground via capacitor C6. Split termination provides common mode filtering for the bus. When termination is placed on the board instead of directly on the bus, care must be taken to ensure the terminating node is not removed from the bus as this will cause signal integrity issues if the bus is not properly terminated on both ends.

Bypass and bulk capacitors should be placed as close as possible to the supply pins of transceiver, examples C2, C3 ( $V_{CC}$ ).

Use at least two vias for  $V_{CC}$  and ground connections of bypass capacitors and protection devices to minimize trace and via inductance.

To limit current of digital lines, serial resistors may be used. Examples are R1, R2, R3 and R4.

To filter noise on the digital IO lines, a capacitor may be used close to the input side of the IO as shown by C1 and C4.

Since the internal pull up and pull down biasing of the device is weak for floating pins, an external  $1-k\Omega$  to  $10-k\Omega$  pullup or pulldown resistor should be used to bias the state of the pin more strongly against noise during transient events.

Pin 1: If an open-drain host processor is used to drive the D pin of the device an external pullup resistor between 1 k $\Omega$  and 10 k $\Omega$  should be used to drive the recessive input state of the device.

Pin 5: is  $V_{REF}$  output voltage reference, if used, this pin should be tied to the common mode point of the split termination. If  $V_{REF}$  is not used, the pin can be left floating.

Pin 8: is shown assuming the mode pin, R<sub>S</sub>, will be used. If the device will only be used in high-speed mode or slope control mode, R3 is not needed and the pads of C4 could be used for the pulldown resistor to GND.

#### 11.2 Layout Example

Figure 34. Layout Example Recommendation

#### **12 Device and Documentation Support**

#### 12.1 Related Links

The table below lists quick access links. Categories include technical documents, support and community resources, tools and software, and quick access to sample or buy.

| PARTS      | PRODUCT FOLDER | SAMPLE & BUY | TECHNICAL<br>DOCUMENTS | TOOLS &<br>SOFTWARE | SUPPORT &<br>COMMUNITY |  |

|------------|----------------|--------------|------------------------|---------------------|------------------------|--|

| SN55HVD251 | Click here     | Click here   | Click here             | Click here          | Click here             |  |

| SN65HVD251 | Click here     | Click here   | Click here             | Click here          | Click here             |  |

#### Table 5. Related Links

#### 12.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 12.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

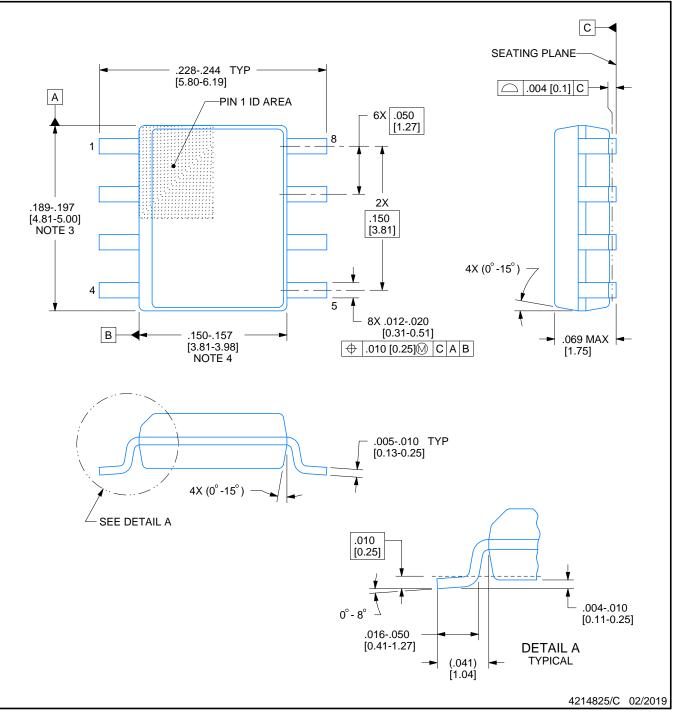

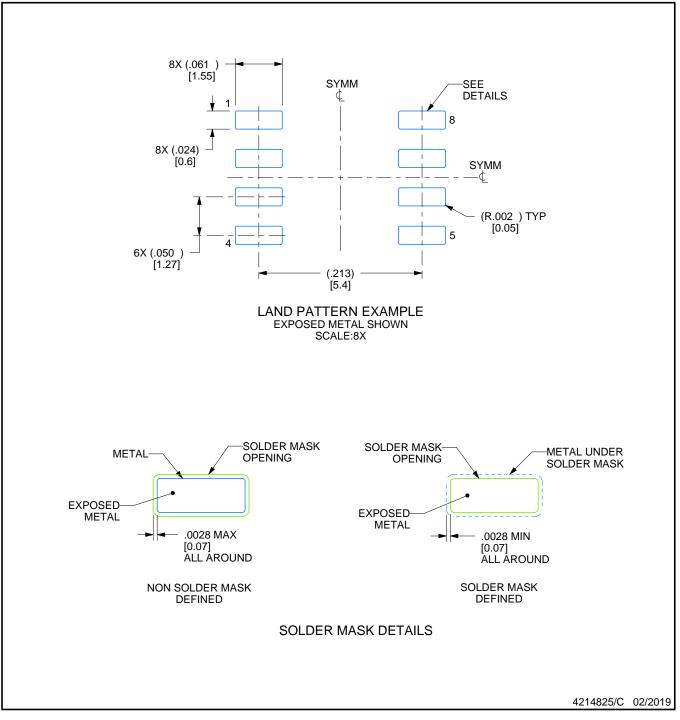

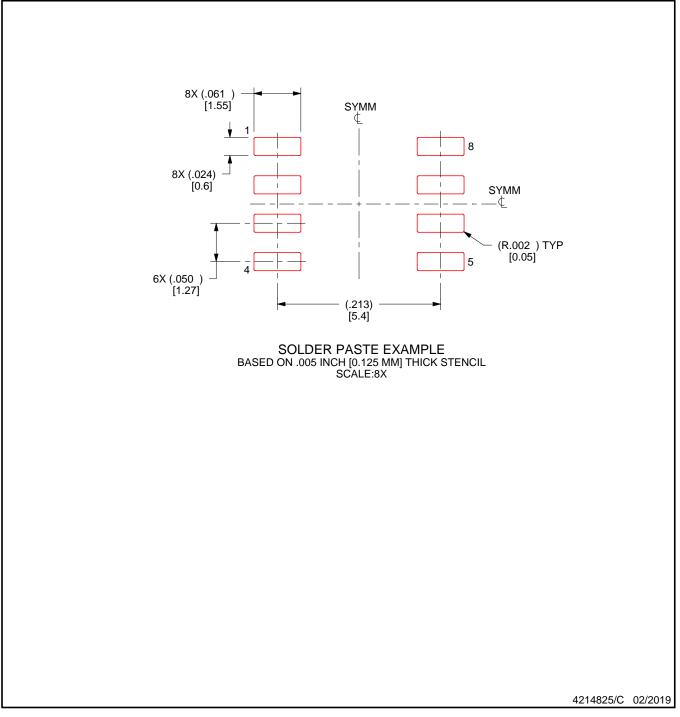

#### 13 Mechanical, Packaging, and Orderable Information

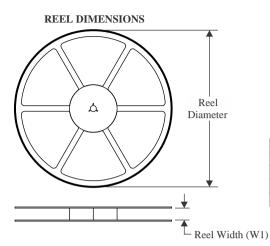

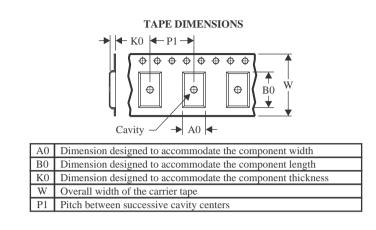

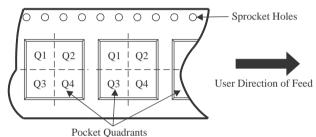

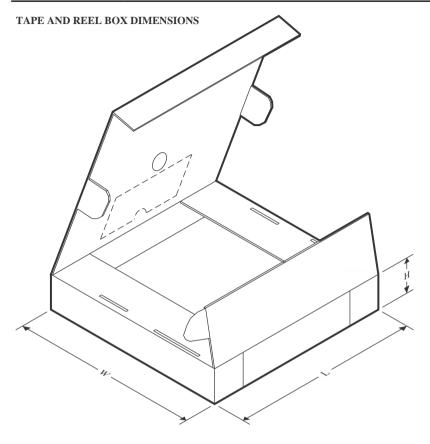

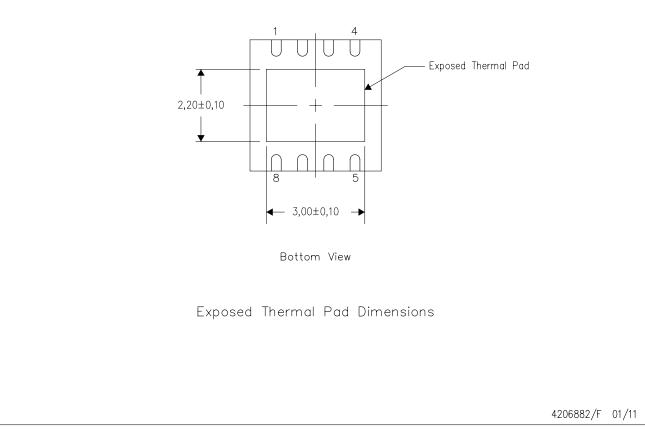

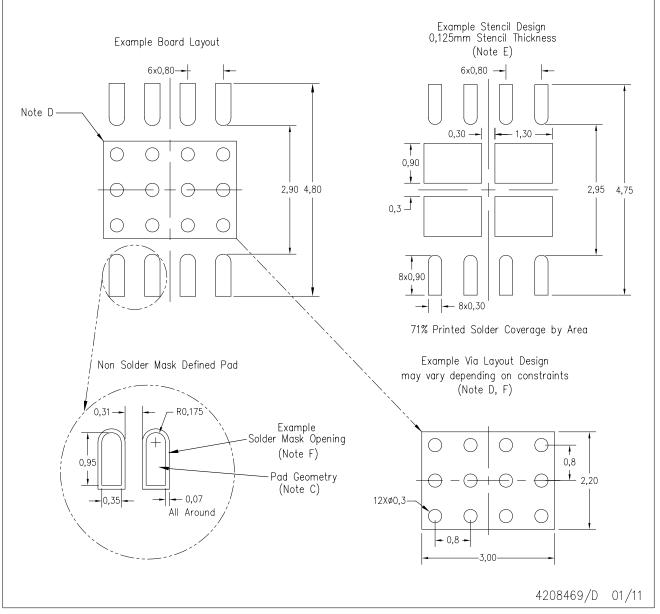

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

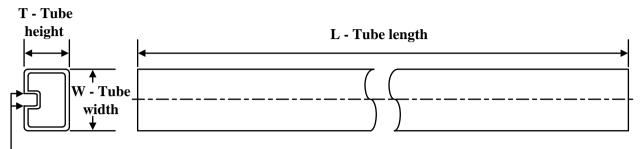

#### **PACKAGING INFORMATION**

| Orderable part number | Status   | Material type | Package   Pins | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|----------|---------------|----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       | (1)      | (2)           |                |                       | (3)             | (4)                           | (5)                        |              | (0)              |

| SN55HVD251DRJR        | Active   | Production    | SON (DRJ)   8  | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -55 to 125   | SN55<br>HVD251   |

| SN55HVD251DRJR.A      | Active   | Production    | SON (DRJ)   8  | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -55 to 125   | SN55<br>HVD251   |

| SN55HVD251DRJRG4      | Active   | Production    | SON (DRJ)   8  | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -55 to 125   | SN55<br>HVD251   |

| SN55HVD251DRJRG4.A    | Active   | Production    | SON (DRJ)   8  | 1000   LARGE T&R      | Yes             | NIPDAU                        | Level-2-260C-1 YEAR        | -55 to 125   | SN55<br>HVD251   |

| SN65HVD251D           | Obsolete | Production    | SOIC (D)   8   | -                     | -               | Call TI                       | Call TI                    | -40 to 125   | VP251            |

| SN65HVD251DR          | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VP251            |

| SN65HVD251DR.A        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VP251            |

| SN65HVD251DRG4        | Active   | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 125   | VP251            |

| SN65HVD251P           | Active   | Production    | PDIP (P)   8   | 50   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 125   | 65HVD251         |

| SN65HVD251P.A         | Active   | Production    | PDIP (P)   8   | 50   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 125   | 65HVD251         |

| SN65HVD251PE4         | Active   | Production    | PDIP (P)   8   | 50   TUBE             | Yes             | NIPDAU                        | N/A for Pkg Type           | -40 to 125   | 65HVD251         |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

(3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.