SNVS696C - JANUARY 2011 - REVISED APRIL 2013

# **Dual 5A Compound Gate Driver**

Check for Samples: SM72482

## **FEATURES**

- **Renewable Energy Grade**

- **Independently Drives Two N-Channel MOSFETs**

- **Compound CMOS and Bipolar Outputs Reduce** • **Output Current Variation**

- 5A Sink, 3A Source Current Capability

- Two Channels Can be Connected in Parallel to • **Double the Drive Current**

- Independent Inputs (TTL Compatible)

- Fast Propagation Times (25 ns Typical) •

- Fast Rise and Fall Times (14 ns Rise, 12 ns • Fall With 2 nF Load)

- Available in Dual Noninverting, Dual Inverting, • and Combination Configurations

- Supply Rail Under-Voltage Lockout Protection • (UVLO)

- SM72482 UVLO Configured to Drive PFET Through OUT\_A and NFET Through OUT\_B

- **Pin Compatible With Industry Standard Gate** Drivers

- Packages

- SOIC

- Thermally Enhanced VSSOP

## **APPLICATIONS**

- Synchronous Rectifier Gate Drivers

- Switch-mode Power Supply Gate Driver

- Solenoid and Motor Drivers

## DESCRIPTION

The SM72482 Dual Gate Driver replaces industry standard gate drivers with improved peak output current and efficiency. Each "compound" output driver stage includes MOS and bipolar transistors operating in parallel that together sink more than 5A peak from capacitive loads. Combining the unique characteristics of MOS and bipolar devices reduces drive current variation with voltage and temperature. Under-voltage lockout protection is also provided. The drivers can be operated in parallel with inputs and outputs connected to double the drive current capability. This device is available in the SOIC package.

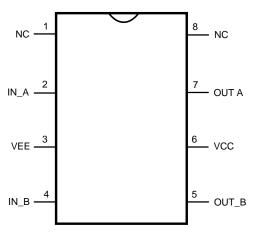

### **Connection Diagram**

Figure 1. 8-Lead SOIC or VSSOP See D or DGN Package

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNVS696C-JANUARY 2011-REVISED APRIL 2013

| Pin | Name   | Description                                  | Application Information                                                                                     |

|-----|--------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| 1   | NC     | No Connect                                   |                                                                                                             |

| 2   | IN_A   | 'A' side control input                       | TTL compatible thresholds.                                                                                  |

| 3   | VEE    | Ground reference for both inputs and outputs | Connect to power ground.                                                                                    |

| 4   | IN_B   | 'B' side control input                       | TTL compatible thresholds.                                                                                  |

| 5   | OUT_B  | Output for the 'B' side driver.              | Voltage swing of this output is from VCC to VEE. The output stage is capable of sourcing 3A and sinking 5A. |

| 6   | VCC    | Positive output supply                       | Locally decouple to VEE                                                                                     |

| 7   | OUT_A. | Output for the 'A' side driver.              | Voltage swing of this output is from VCC to VEE. The output stage is capable of sourcing 3A and sinking 5A. |

| 8   | NC     | No Connect                                   |                                                                                                             |

### Table 1. Configuration Table

| Part Number | "A" Output Configuration    | "B" Output Configuration    | Package |

|-------------|-----------------------------|-----------------------------|---------|

| SM72482MY-1 | Non-Inverting (Low in UVLO) | Non-Inverting (Low in UVLO) | VSSOP   |

| SM72482MA-4 | Inverting (High in UVLO)    | Non-Inverting (Low in UVLO) | SOIC    |

2

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## Absolute Maximum Ratings<sup>(1)</sup>

| V <sub>CC</sub> to V <sub>EE</sub>                   | -0.3V to 15V    |

|------------------------------------------------------|-----------------|

| IN to V <sub>EE</sub>                                | -0.3V to 15V    |

| Storage Temperature Range, (T <sub>STG</sub> )       | −55°C to +150°C |

| Maximum Junction Temperature, (T <sub>J</sub> (max)) | +150°C          |

| Operating Junction Temperature                       | +125°C          |

| ESD Rating                                           | 2kV             |

(1) Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For ensured specifications and test conditions, see the Electrical Characteristics.

## **Electrical Characteristics**

Submit Documentation Feedback

$T_J = -40^{\circ}C$  to +125°C,  $V_{CC} = 12V$ ,  $V_{EE} = 0V$ , No Load on OUT\_A or OUT\_B, unless otherwise specified.

| Symbol           | Parameter                                           | Conditions                               | Min | Тур  | Max | Units |

|------------------|-----------------------------------------------------|------------------------------------------|-----|------|-----|-------|

|                  | V <sub>CC</sub> Operating Range                     | V <sub>CC</sub> -V <sub>EE</sub>         | 3.5 |      | 14  | V     |

| V <sub>CCR</sub> | V <sub>CC</sub> Under Voltage Lockout (rising)      | V <sub>CC</sub> -V <sub>EE</sub>         | 2.3 | 2.9  | 3.5 | V     |

| V <sub>CCH</sub> | V <sub>CC</sub> Under Voltage Lockout<br>Hysteresis |                                          |     | 230  |     | mV    |

| I <sub>CC</sub>  | V <sub>CC</sub> Supply Current (I <sub>CC</sub> )   | IN_A = IN_B = 0V (SM72482MY-1)           |     | 1    | 2   |       |

|                  |                                                     | $IN_A = V_{CC}, IN_B = 0V$ (SM72482MA-4) |     | 1    | 2   | mA    |

| CONTROL IN       | IPUTS                                               |                                          |     |      |     |       |

| V <sub>IH</sub>  | Logic High                                          |                                          | 2.2 |      |     | V     |

| V <sub>IL</sub>  | Logic Low                                           |                                          |     |      | 0.8 | V     |

| V <sub>thH</sub> | High Threshold                                      |                                          | 1.3 | 1.75 | 2.2 | V     |

| V <sub>thL</sub> | Low Threshold                                       |                                          | 0.8 | 1.35 | 2.0 | V     |

| HYS              | Input Hysteresis                                    |                                          |     | 400  |     | mV    |

www.ti.com

#### SNVS696C - JANUARY 2011 - REVISED APRIL 2013

## **Electrical Characteristics (continued)**

$T_J = -40^{\circ}C$  to +125°C,  $V_{CC} = 12V$ ,  $V_{EE} = 0V$ , No Load on OUT\_A or OUT\_B, unless otherwise specified.

| Symbol              | Parameter                                                    | Conditions                                            | Min | Тур | Max | Units |

|---------------------|--------------------------------------------------------------|-------------------------------------------------------|-----|-----|-----|-------|

| IIL                 | Input Current Low                                            | IN_A=IN_B=V <sub>CC</sub>                             | -1  | 0.1 | 1   |       |

| I <sub>IH</sub>     | Input Current High                                           | IN_A=IN_B=V <sub>CC</sub> (SM72482MY-1)               | 10  | 18  | 25  | 1.    |

|                     |                                                              | IN_B=V <sub>CC</sub> (SM72482MA-4)                    | 10  | 18  | 25  | μA    |

|                     |                                                              | IN_A=V <sub>CC</sub> (SM72482MA-4)                    | -1  | 0.1 | 1   | 1     |

| OUTPUT DR           | IVERS                                                        |                                                       |     |     |     |       |

| R <sub>OH</sub>     | Output Resistance High                                       | $I_{OUT} = -10 \text{ mA}^{(1)}$                      |     | 30  | 50  | Ω     |

| R <sub>OL</sub>     | Output Resistance Low                                        | $I_{OUT} = + 10 \text{ mA}^{(1)}$                     |     | 1.4 | 2.5 | Ω     |

| I <sub>Source</sub> | Peak Source Current                                          | OUTA/OUTB = $V_{CC}/2$ ,<br>200 ns Pulsed Current     |     | 3   |     | А     |

| I <sub>Sink</sub>   | Peak Sink Current                                            | OUTA/OUTB = $V_{CC}/2$ ,<br>200 ns Pulsed Current     |     | 5   |     | А     |

| SWITCHING           | CHARACTERISTICS                                              | -                                                     |     |     |     |       |

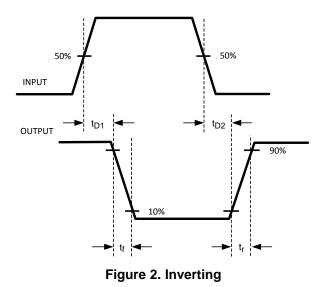

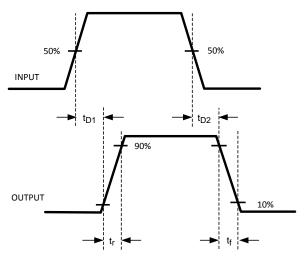

| td1                 | Propagation Delay Time Low to<br>High, IN rising (IN to OUT) | $C_{LOAD} = 2 \text{ nF}$ , see Figure 2 and Figure 3 |     | 25  | 40  | ns    |

| td2                 | Propagation Delay Time High to Low, IN falling (IN to OUT)   | $C_{LOAD} = 2 \text{ nF}$ , see Figure 2 and Figure 3 |     | 25  | 40  | ns    |

| t <sub>r</sub>      | Rise Time                                                    | $C_{LOAD} = 2 \text{ nF}$ , see Figure 2 and Figure 3 |     | 14  | 25  | ns    |

| t <sub>f</sub>      | Fall Time                                                    | $C_{LOAD} = 2 \text{ nF}$ , see Figure 2 and Figure 3 |     | 12  | 25  | ns    |

| LATCHUP P           | ROTECTION                                                    | -                                                     |     |     |     |       |

|                     | AEC - Q100, Method 004                                       | $T_J = 150^{\circ}C$                                  |     | 500 |     | mA    |

| THERMAL R           | ESISTANCE                                                    |                                                       |     |     |     |       |

| θ <sub>JA</sub>     | Junction to Ambient,                                         | SOIC Package                                          |     | 170 |     | 80 AA |

| (                   | 0 LFPM Air Flow                                              | VSSOP Package                                         |     | 60  |     | °C/W  |

| θ <sub>JC</sub>     | Junction to Case                                             | SOIC Package                                          |     | 70  |     | °C/W  |

|                     |                                                              | VSSOP Package                                         |     | 4.7 |     | - C/W |

(1) The output resistance specification applies to the MOS device only. The total output current capability is the sum of the MOS and Bipolar devices.

## TIMING WAVEFORMS

Figure 3. Non-Inverting

### SNVS696C-JANUARY 2011-REVISED APRIL 2013

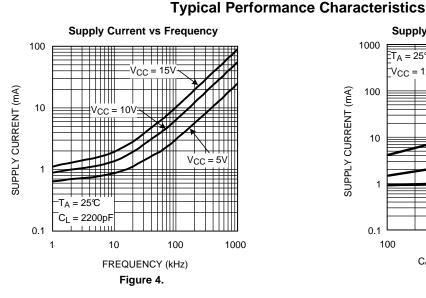

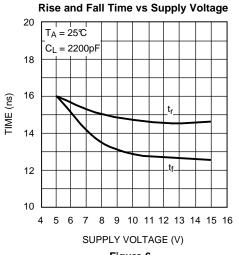

Figure 6.

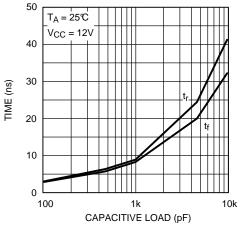

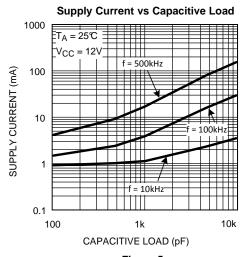

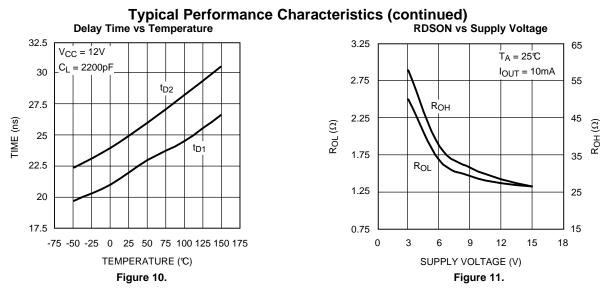

Rise and Fall Time vs Capacitive Load

Figure 5.

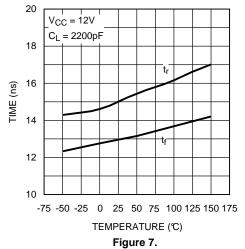

**Rise and Fall Time vs Temperature**

**Delay Time vs Supply Voltage**

4

#### SNVS696C - JANUARY 2011 - REVISED APRIL 2013

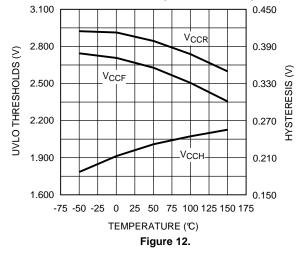

UVLO Thresholds and Hysteresis vs Temperature

TEXAS INSTRUMENTS

SNVS696C – JANUARY 2011 – REVISED APRIL 2013

www.ti.com

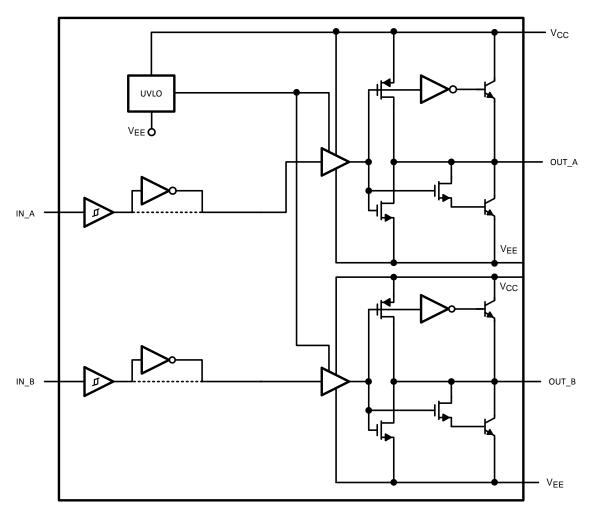

Figure 13. Block Diagram of SM72482

### DETAILED OPERATING DESCRIPTION

The SM72482 dual gate driver consists of two independent and identical driver channels with TTL compatible logic inputs and high current totem-pole outputs that source or sink current to drive MOSFET gates. The driver output consist of a compound structure with MOS and bipolar transistor operating in parallel to optimize current capability over a wide output voltage and operating temperature range. The bipolar device provides high peak current at the critical threshold region of the MOSFET VGS while the MOS devices provide rail-to-rail output swing. The totem pole output drives the MOSFET gate between the gate drive supply voltage V<sub>CC</sub> and the power ground potential at the V<sub>EE</sub> pin.

The control inputs of the drivers are high impedance CMOS buffers with TTL compatible threshold voltages. The SM72482 pinout was designed for compatibility with industry standard gate drivers in single supply gate driver applications.

The input stage of each driver should be driven by a signal with a short rise and fall time. Slow rising and falling input signals, although not harmful to the driver, may result in the output switching repeatedly at a high frequency.

The two driver channels of the SM72482 are designed as identical cells. Transistor matching inherent to integrated circuit manufacturing ensures that the AC and DC peformance of the channels are nearly identical. Closely matched propagation delays allow the dual driver to be operated as a single with inputs and output pins connected. The drive current capability in parallel operation is precisely 2X the drive of an individual channel. Small differences in switching speed between the driver channels will produce a transient current (shoot-through) in the output stage when two output pins are connected to drive a single load. Differences in input thresholds between the driver channels will also produce a transient current (shoot-through) in the output stage. Fast transition input signals are especially important while operating in a parallel configuration. The efficiency loss for parallel operation has been characterized at various loads, supply voltages and operating frequencies. The power dissipation in the SM72482 increases less than 1% relative to the dual driver configuration when operated as a single driver with inputs/ outputs connected.

An Under Voltage Lock Out (UVLO) circuit is included in the SM72482, which senses the voltage difference between  $V_{CC}$  and the chip ground pin,  $V_{EE}$ . When the  $V_{CC}$  to  $V_{EE}$  voltage difference falls below 2.8V both driver channels are disabled. The UVLO hysteresis prevents chattering during brown-out conditions and the driver will resume normal operation when the  $V_{CC}$  to  $V_{EE}$  differential voltage exceeds approximately 3.0V.

The SM72482MY –1 device hold both outputs in the low state in the under-voltage lockout (UVLO) condition. The SM72482MA–4 has an active high output state of OUT\_A during UVLO. When VCC is less than the UVLO threshold voltage, OUT\_A will be locked in the high state while OUT\_B will be disabled in the low state. This configuration allows the SM72482MY –4 to drive a PFET through OUT\_A and an NFET through OUT\_B with both FETs safely turned off during UVLO.

### Layout Considerations

Attention must be given to board layout when using SM72482. Some important considerations include:

- 1. A Low ESR/ESL capacitor must be connected close to the IC and between the  $V_{CC}$  and  $V_{EE}$  pins to support high peak currents being drawn from  $V_{CC}$  during turn-on of the MOSFET.

- 2. Proper grounding is crucial. The drivers need a very low impedance path for current return to ground avoiding inductive loops. The two paths for returning current to ground are a) between SM72482  $V_{EE}$  pin and the ground of the circuit that controls the driver inputs, b) between SM72482  $V_{EE}$  pin and the source of the power MOSFET being driven. All these paths should be as short as possible to reduce inductance and be as wide as possible to reduce resistance. All these ground paths should be kept distinctly separate to avoid coupling between the high current output paths and the logic signals that drive the SM72482. A good method is to dedicate one copper plane in a multi-layered PCB to provide a common ground surface.

- 3. With the rise and fall times in the range of 10 ns to 30 ns, care is required to minimize the lengths of current carrying conductors to reduce their inductance and EMI from the high di/dt transients generated by the SM72482.

- 4. The SM72482 footprint is compatible with other industry standard drivers including the TC4426/27/28 and UCC27323/4/5.

- 5. If either channel is not being used, the respective input pin (IN\_A or IN\_B) should be connected to either  $V_{EE}$  or  $V_{CC}$  to avoid spurious output signals.

SNVS696C - JANUARY 2011 - REVISED APRIL 2013

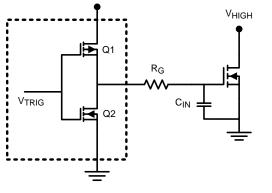

The schematic above shows a conceptual diagram of the SM72482 output and MOSFET load. Q1 and Q2 are the switches within the gate driver. R<sub>G</sub> is the gate resistance of the external MOSFET, and C<sub>IN</sub> is the equivalent gate capacitance of the MOSFET. The gate resistance Rg is usually very small and losses in it can be neglected. The equivalent gate capacitance is a difficult parameter to measure since it is the combination of C<sub>GS</sub> (gate to source capacitance) and C<sub>GD</sub> (gate to drain capacitance). Both of these MOSFET capacitances are not constants and vary with the gate and drain voltage. The better way of quantifying gate capacitance is the total gate charge Q<sub>G</sub> in coloumbs. Q<sub>G</sub> combines the charge required by C<sub>GS</sub> and C<sub>GD</sub> for a given gate drive voltage V<sub>GATE</sub>.

Assuming negligible gate resistance, the total power dissipated in the MOSFET driver due to gate charge is approximated by

$$P_{DRIVER} = V_{GATE} \times Q_G \times F_{SW}$$

where

F<sub>SW</sub> = switching frequency of the MOSFET

For example, consider the MOSFET MTD6N15 whose gate charge specified as 30 nC for V<sub>GATE</sub> = 12V.

The power dissipation in the driver due to charging and discharging of MOSFET gate capacitances at switching frequency of 300 kHz and  $V_{GATE}$  of 12V is equal to

P<sub>DRIVER</sub> = 12V x 30 nC x 300 kHz = 0.108W.

If both channels of the SM72482 are operating at equal frequency with equivalent loads, the total losses will be twice as this value which is 0.216W.

In addition to the above gate charge power dissipation, - transient power is dissipated in the driver during output transitions. When either output of the SM72482 changes state, current will flow from V<sub>CC</sub> to V<sub>EE</sub> for a very brief interval of time through the output totem-pole N and P channel MOSFETs. The final component of power dissipation in the driver is the power associated with the quiescent bias current consumed by the driver input stage and Under-voltage lockout sections.

VGATE VHIGH Q1 R<sub>G</sub> CIN VTRIG Q2 ♣

INTRODUCTION The primary goal of thermal management is to maintain the integrated circuit (IC) junction temperature  $(T_1)$  below

## **DRIVE POWER REQUIREMENT CALCULATIONS IN SM72482**

The SM72482 dual low side MOSFET driver is capable of sourcing/sinking 3A/5A peak currents for short intervals to drive a MOSFET without exceeding package power dissipation limits. High peak currents are required to switch the MOSFET gate very guickly for operation at high frequencies.

a specified maximum operating temperature to ensure reliability. It is essential to estimate the maximum  $T_1$  of IC components in worst case operating conditions. The junction temperature is estimated based on the power dissipated in the IC and the junction to ambient thermal resistance  $\theta_{JA}$  for the IC package in the application board and environment. The  $\theta_{IA}$  is not a given constant for the package and depends on the printed circuit board design and the operating environment.

Thermal Performance

FXAS **NSTRUMENTS**

(1)

(2)

Characterization of the SM72482 provides accurate estimates of the transient and quiescent power dissipation components. At 300 kHz switching frequency and 30 nC load used in the example, the transient power will be 8 mW. The 1 mA nominal quiescent current and 12V  $V_{GATE}$  supply produce a 12 mW typical quiescent power.

Therefore the total power dissipation

$$P_D = 0.216 + 0.008 + 0.012 = 0.236W.$$

We know that the junction temperature is given by

$$T_{J} = P_{D} \times \theta_{JA} + T_{A}$$

Or the rise in temperature is given by

$T_{RISE} = T_J - T_A = P_D \times \theta_{JA}$

(5)

(3)

(4)

For SOIC package,  $\theta_{JA}$  is estimated as 170°C/W for the conditions of natural convection. For VSSOP,  $\theta_{JA}$  is typically 60°C/W.

Therefore for SOIC T<sub>RISE</sub> is equal to

$T_{RISE} = 0.236 \text{ x } 170 = 40.1^{\circ}\text{C}$

(6)

(7)

### CONTINUOUS CURRENT RATING OF SM72482

The SM72482 can deliver pulsed source/sink currents of 3A and 5A to capacitive loads. In applications requiring continuous load current (resistive or inductive loads), package power dissipation, limits the SM72482 current capability far below the 5A sink/3A source capability. Rated continuous current can be estimated both when sourcing current to or sinking current from the load. For example when sinking, the maximum sink current can be calculated as:

$$I_{SINK} (MAX) := \sqrt{\frac{T_{J}(MAX) - T_{A}}{\theta_{JA} \cdot R_{DS} (ON)}}$$

where

R<sub>DS</sub>(on) is the on resistance of lower MOSFET in the output stage of SM72482

Consider  $T_J(max)$  of 125°C and  $\theta_{JA}$  of 170°C/W for an SOIC package under the condition of natural convection and no air flow. If the ambient temperature ( $T_A$ ) is 60°C, and the  $R_{DS}(on)$  of the SM72482 output at  $T_J(max)$  is 2.5 $\Omega$ , this equation yields  $I_{SINK}(max)$  of 391mA which is much smaller than 5A peak pulsed currents.

Similarly, the maximum continuous source current can be calculated as

$$I_{\text{SOURCE}}(\text{MAX}) := \frac{\mathsf{T}_{J}(\text{MAX}) - \mathsf{T}_{A}}{\theta_{JA} \cdot \mathsf{V}_{\text{DIODE}}}$$

where

V<sub>DIODE</sub> is the voltage drop across hybrid output stage which varies over temperature and can be assumed to be about 1.1V at T<sub>J</sub>(max) of 125°C

(8)

Assuming the same parameters as above, this equation yields I<sub>SOURCE</sub>(max) of 347mA.

Changes

SNVS696C - JANUARY 2011 - REVISED APRIL 2013

#### 10 Submit Documentation Feedback

**REVISION HISTORY**

| s from Revision B (April 2013) to Revision C   | Page |

|------------------------------------------------|------|

| ged layout of National Data Sheet to TI format | 9    |

### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | <b>- -</b>         |            | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|--------------------|------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow        |            | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                |            |              |

| SM72482MA-4/NOPB      | Active | Production    | SOIC (D)   8   | 95   TUBE             | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MA-4/NOPB.A    | Active | Production    | SOIC (D)   8   | 95   TUBE             | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MA-4/NOPB.B    | Active | Production    | SOIC (D)   8   | 95   TUBE             | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAE-4/NOPB     | Active | Production    | SOIC (D)   8   | 250   SMALL T&R       | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAE-4/NOPB.A   | Active | Production    | SOIC (D)   8   | 250   SMALL T&R       | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAE-4/NOPB.B   | Active | Production    | SOIC (D)   8   | 250   SMALL T&R       | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAX-4/NOPB     | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAX-4/NOPB.A   | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

| SM72482MAX-4/NOPB.B   | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | SN            | Level-1-260C-UNLIM | -40 to 125 | S482         |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

## PACKAGE OPTION ADDENDUM

23-May-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

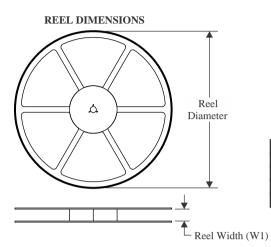

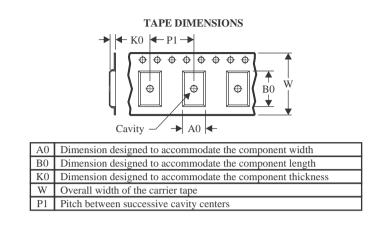

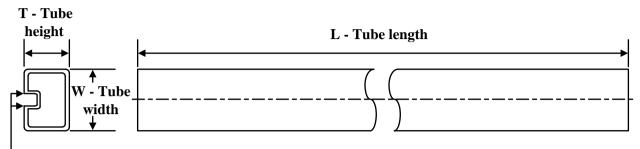

## TAPE AND REEL INFORMATION

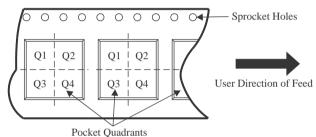

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |      |                    |   |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | -    | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| SM72482MAE-4/NOPB           | SOIC | D                  | 8 | 250  | 177.8                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

| SM72482MAX-4/NOPB           | SOIC | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.5        | 5.4        | 2.0        | 8.0        | 12.0      | Q1               |

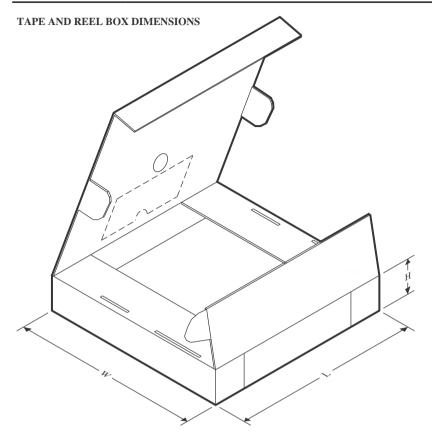

## PACKAGE MATERIALS INFORMATION

31-Jul-2025

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SM72482MAE-4/NOPB | SOIC         | D               | 8    | 250  | 208.0       | 191.0      | 35.0        |

| SM72482MAX-4/NOPB | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

31-Jul-2025

## TUBE

## - B - Alignment groove width

#### \*All dimensions are nominal

| Device             | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|--------------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SM72482MA-4/NOPB   | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| SM72482MA-4/NOPB.A | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| SM72482MA-4/NOPB.B | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

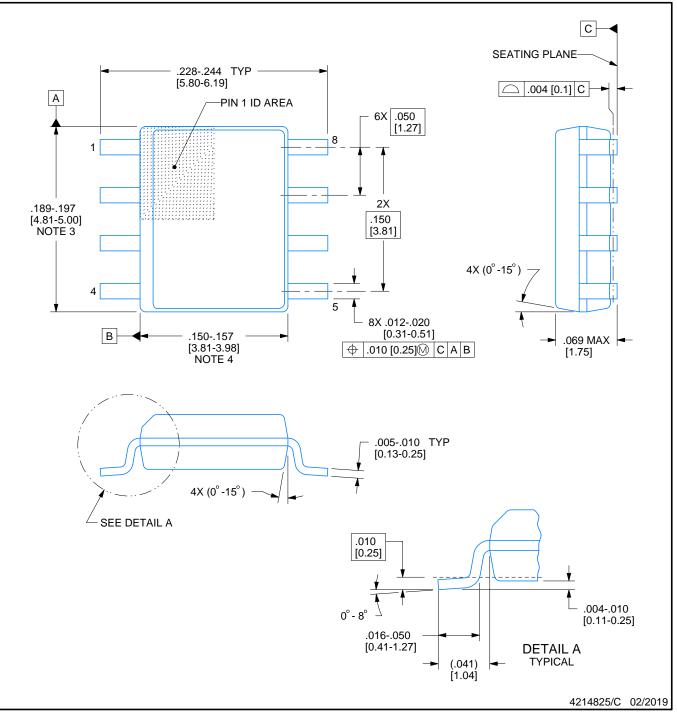

## D0008A

## **PACKAGE OUTLINE**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

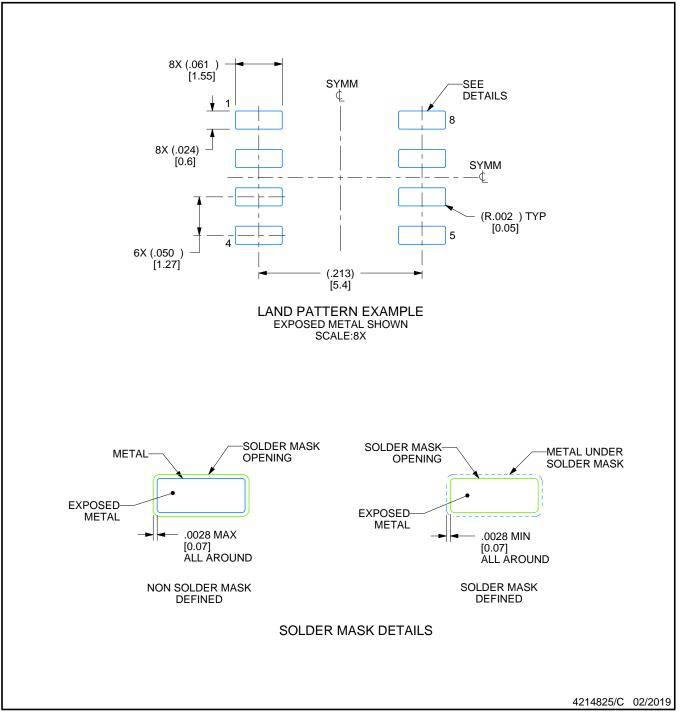

## D0008A

## **EXAMPLE BOARD LAYOUT**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

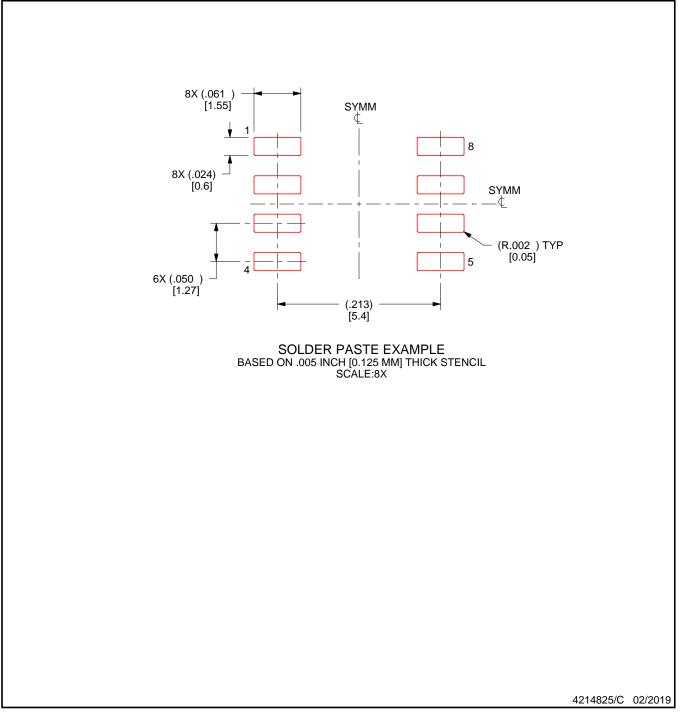

## D0008A

## **EXAMPLE STENCIL DESIGN**

## SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated