SBOS334A - SEPTEMBER 2005 - REVISED JANUARY 2006

# **3V VIDEO AMPLIFIER** with Internal Gain and Filter in SC70

### FEATURES

- EXCELLENT VIDEO PERFORMANCE

- INTERNAL GAIN: 5.2V/V

- SUPPORTS TV-DETECTION

- COMPATIBLE WITH OMAP242x and DAVINCI<sup>™</sup> PROCESSORS

- 2-POLE RECONSTRUCTION FILTER

- INPUT RANGE INCLUDES GROUND

DC-Coupled Input

- INTEGRATED LEVEL SHIFTER – DC-Coupled Output<sup>(1)</sup>

- No Output Capacitors Needed

- RAIL-TO-RAIL OUTPUT

- LOW QUIESCENT CURRENT: 5.3mA

- SHUTDOWN CURRENT: 1.5μA

- SINGLE-SUPPLY: 2.5V to 3.3V

- SC70-6 PACKAGE: 2.0mm x 2.1mm

- RoHS COMPLIANT

Internal circuitry avoids output saturation, even with 0V sync tip level at the input video signal.

# APPLICATIONS

#### (1) Closed when enabled during normal operation; open when shut down.

# 53

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

DAVINCI is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

# DESCRIPTION

The OPA361 high-speed amplifier is optimized for 3V portable video applications. It is specifically designed to be compatible with the video encoders embedded in Texas Instruments' OMAP2420 and DaVinci processors or other application processors with 0.5V<sub>PP</sub> video output. The input common-mode range includes GND, which allows a video-DAC (digital-to-analog converter) to be DC-coupled to the OPA361. The TV-detection feature simplifies the end-user interface significantly by facilitating the automatic start/stop of video transmission.

The output swings within 5mV of GND and 250mV to V+ with a standard back-terminated video load (150 $\Omega$ ). An internal level shift circuit prevents the output from saturating with 0V input, thus preventing sync-pulse clipping in common video circuits. Therefore, the OPA361 is ideally suited for DC-coupling to the video load.

The OPA361 has been optimized for space-sensitive applications by integrating internal gain setting resistors (G = 5.2V/V) and a 2-pole video-DAC reconstruction filter.

In shutdown mode, the quiescent current is reduced to  $< 1.5\mu$ A, dramatically reducing power consumption and prolonging battery life.

The OPA361 is available in the tiny 2mm x 2.1mm SC70-6 package.

### RELATED LOW VOLTAGE VIDEO AMPS

| FEATURES                                                                   | PRODUCT |

|----------------------------------------------------------------------------|---------|

| 2.7V to 3.3V, 70MHz, 6mA $I_{\mbox{\scriptsize Q}},$ 5 $\mu A$ Sleep, SC70 | OPA358  |

| 2.7V to 3.3V, Filter, SAG, G = 2, 5µA Sleep, SC70                          | OPA360  |

| 2.7V to 5.5V, 200MHz, 300V/µs, 6µA Sleep, SOT23                            | OPA355  |

| 2.7V to 5.5V, 100MHz, 150V/µs, 6µA Sleep, SOT23                            | OPA357  |

K (%)

#### **ORDERING INFORMATION(1)**

| PRODUCT | PACKAGE | PACKAGE DESIGNATOR | PACKAGE MARKING |  |  |

|---------|---------|--------------------|-----------------|--|--|

| OPA361  | SC70-6  | DCK                | AUY             |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see the TI website at www.ti.com.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ABSOLUTE MAXIMUM RATINGS(1)

| Supply Voltage, V+ to V +3.6V                                        |

|----------------------------------------------------------------------|

| Signal Input Terminals, Voltage <sup>(2)</sup> 0.5V to $(V+) + 0.5V$ |

| Current <sup>(2)</sup> ±10mA                                         |

| Output Short-Circuit through $75\Omega$ to $GND^{(3)}$ Continuous    |

| Operating Temperature40°C to +125°C                                  |

| Storage Temperature65°C to +150°C                                    |

| Junction Temperature+160°C                                           |

| ESD Rating:                                                          |

| Human Body Model 5000V                                               |

| Machine Model                                                        |

| Charged Device Model 2000V                                           |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

- (2) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.5V beyond the supply rails should be current-limited to 10mA or less.

- (3) Short-circuit to ground.

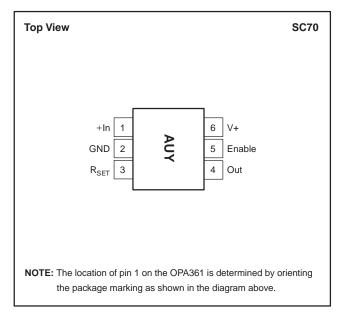

#### **PIN CONFIGURATION**

### ELECTRICAL CHARACTERISTICS: $V_S = +2.5V$ to +3.3V

Boldface limits apply over the temperature range,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ . At  $T_A = +25^{\circ}C$ ,  $R_L = 150\Omega$  connected to GND, unless otherwise noted.

| PARAMETER                                       |                  | CONDITIONS                                                                              | MIN  | TYP              | MAX  | UNITS             |

|-------------------------------------------------|------------------|-----------------------------------------------------------------------------------------|------|------------------|------|-------------------|

| OFFSET LEVEL-SHIFT VOLTAGE                      | N/               |                                                                                         | 0    | 44               |      |                   |

| Output Level-Shift Voltage <sup>(1)</sup>       | VOLS             | $V_{S} = +2.8V, V_{IN} = GND$                                                           | -3   | 11               | 55   | mV                |

| Over Temperature                                | PSRR             | $V_{S} = +2.5V \text{ to } +3.3V$                                                       |      | <b>20</b><br>±80 |      | <b>mV</b><br>μV/V |

| vs Power Supply                                 | FORK             | VS = +2.5V 10 +5.5V                                                                     |      | ±00              |      | μν/ν              |

| INPUT VOLTAGE RANGE                             |                  |                                                                                         |      |                  |      |                   |

| Input Voltage Range <sup>(2)</sup>              | V <sub>CM</sub>  | $V_{\rm S} = 2.5 V$                                                                     | GND  |                  | 0.42 | V                 |

|                                                 |                  | $V_{\rm S} = 2.8 V$                                                                     | GND  |                  | 0.48 | V                 |

|                                                 |                  | V <sub>S</sub> = 3.3V                                                                   | GND  |                  | 0.55 | V                 |

| Input Resistance (+In)                          | R <sub>IN</sub>  |                                                                                         | 450  | 510              | 550  | Ω                 |

| R <sub>SET</sub> Resistance                     | R <sub>SET</sub> |                                                                                         | 3600 | 4070             | 4400 | Ω                 |

| Matching of RIN and RSET                        |                  |                                                                                         | 2    | 0.5              |      | %                 |

| VOLTAGE GAIN                                    |                  |                                                                                         |      |                  |      |                   |

|                                                 |                  | $\Delta V_{OUT} / \Delta V_{IN}$ , $V_S$ = +2.5V, $V_{INMIN}$ = 0V, $V_{INMAX}$ = 0.42V | 5.06 | 5.17             | 5.28 | V/V               |

|                                                 |                  | $\Delta V_{OUT}/\Delta V_{IN}$ , $V_{S}$ = +2.8V, $V_{INMIN}$ = 0V, $V_{INMAX}$ = 0.48V | 5.06 | 5.17             | 5.28 | V/V               |

|                                                 |                  | $\Delta V_{OUT}/\Delta V_{IN}$ , $V_{S}$ = +3.3V, $V_{INMIN}$ = 0V, $V_{INMAX}$ = 0.55V | 5.06 | 5.17             | 5.28 | V/V               |

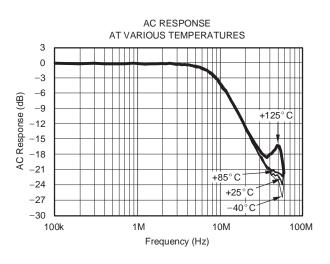

| FREQUENCY RESPONSE                              |                  |                                                                                         |      |                  |      |                   |

| Filter Response                                 |                  |                                                                                         |      |                  |      |                   |

| Cutoff Frequency                                | f_3dB            |                                                                                         |      | 9                |      | MHz               |

| Normalized Gain: $f_{IN} = 4.5MHz$              | -Sub             | $V_{O} = 2V_{PP}$                                                                       |      | -0.1             |      | dB                |

| $f_{\rm IN} = 27 \rm MHz$                       |                  | $V_{O} = 2V_{PP}$                                                                       |      | -18              |      | dB                |

| $f_{IN} = 54MHz$                                |                  | $V_0 = 2V_{PP}$                                                                         |      | -23              |      | dB                |

| Differential Gain Error                         |                  | $R_{\rm L} = 150\Omega$                                                                 |      | 1.2              |      | %                 |

| Differential Phase Error                        |                  | $R_{L} = 150\Omega$                                                                     |      | 1.6              |      | degrees           |

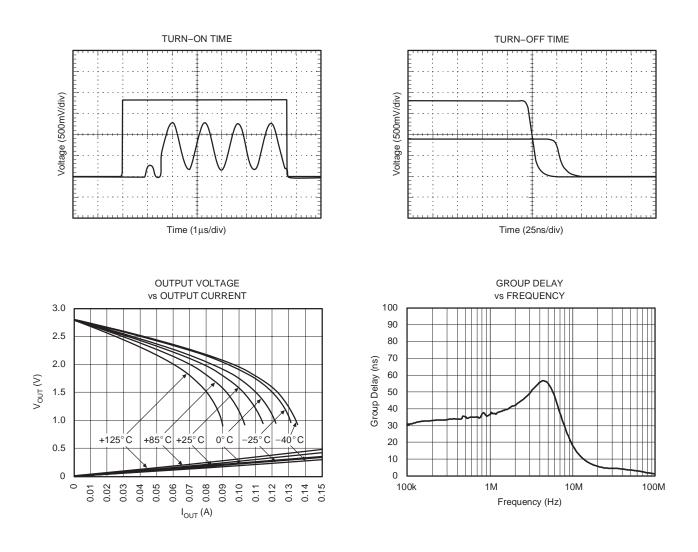

| Group Delay Variation                           |                  | 100kHz, 4.5MHz                                                                          |      | 26               |      | ns                |

| Signal-to-Noise Ratio                           | SNR              | 100% White Signal                                                                       |      | 65               |      | dB                |

|                                                 | •••••            |                                                                                         |      |                  |      |                   |

|                                                 |                  |                                                                                         |      | 400              | 050  |                   |

| Positive Voltage Output Swing from Rail         |                  | $V_{\rm S} = +2.8V, V_{\rm IN} = 0.7V, R_{\rm L} = 150\Omega$ to GND                    |      | 130              | 250  | mV                |

| Negative Voltage Output Swing from Rail         |                  | $V_{S} = +2.8V, V_{IN} = -0.05V, R_{L} = 150\Omega$ to GND                              |      | 0.15             | 5    | mV                |

| Positive Voltage Output Swing from Rail         |                  | $V_{\rm S} = +2.8V, V_{\rm IN} = 0.7V, R_{\rm L} = 75\Omega$ to GND                     |      | 260              |      | mV                |

| Negative Voltage Output Swing from Rail         |                  | $V_{S} = +2.8V, V_{IN} = -0.05V, R_{L} = 75\Omega$ to GND                               |      | 2                | 100  | mV                |

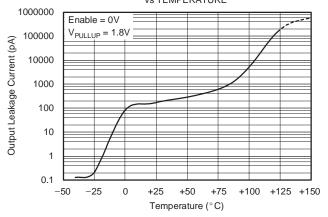

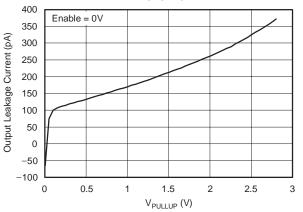

| Output Leakage<br>Output Current <sup>(3)</sup> |                  | $V_{S} = +2.8V$ , Disabled, $V_{O} = 2V$                                                |      | 0.3              | 100  | nA                |

|                                                 | Ι <sub>Ο</sub>   | V <sub>S</sub> = +2.8V                                                                  |      | ±80              |      | mA                |

| POWER SUPPLY                                    |                  |                                                                                         |      |                  |      |                   |

| Specified Voltage Range                         | VS               |                                                                                         | 2.5  |                  | 3.3  | V                 |

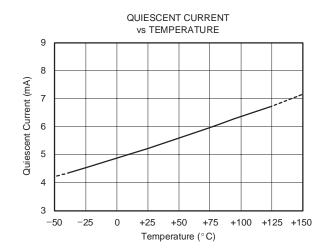

| Quiescent Current                               | IQ               | $V_{S} = +2.8V$ , Enabled, $I_{O} = 0$ , $V_{OUT} = 1.4V$                               |      | 5.3              | 7.5  | mA                |

| Over Temperature                                |                  | Specified Temperature Range                                                             |      |                  | 9    | mA                |

| ENABLE/SHUTDOWN FUNCTION                        |                  |                                                                                         |      |                  |      |                   |

| Disabled (logic-LOW threshold)                  |                  |                                                                                         | 0    |                  | 0.35 | V                 |

| Enabled (logic-HIGH threshold)                  |                  |                                                                                         | 1.3  |                  | VS   | V                 |

| Enable Time                                     |                  |                                                                                         |      | 1.5              |      | μs                |

| Disable Time                                    |                  |                                                                                         |      | 50               |      | ns                |

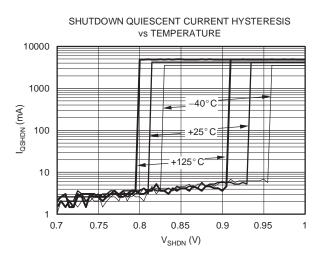

| Shutdown Current                                |                  | $V_{S}$ = +2.8V, Disabled                                                               |      | 1.5              | 3    | μΑ                |

| TEMPERATURE RANGE                               |                  |                                                                                         |      |                  |      |                   |

| Specified/Operating Range                       |                  |                                                                                         | -40  |                  | +125 | °C                |

| Storage Range                                   |                  |                                                                                         | -65  |                  | +150 | °C                |

| Thermal Resistance                              | $\theta_{JA}$    |                                                                                         |      |                  |      |                   |

| SC70                                            | 0/1              |                                                                                         |      | 250              |      | °C/W              |

(1) Output referred.

(2) Limited by output swing and internal G = 5.2V/V.

(3) See typical characteristics *Output Voltage Swing vs Output Current*.

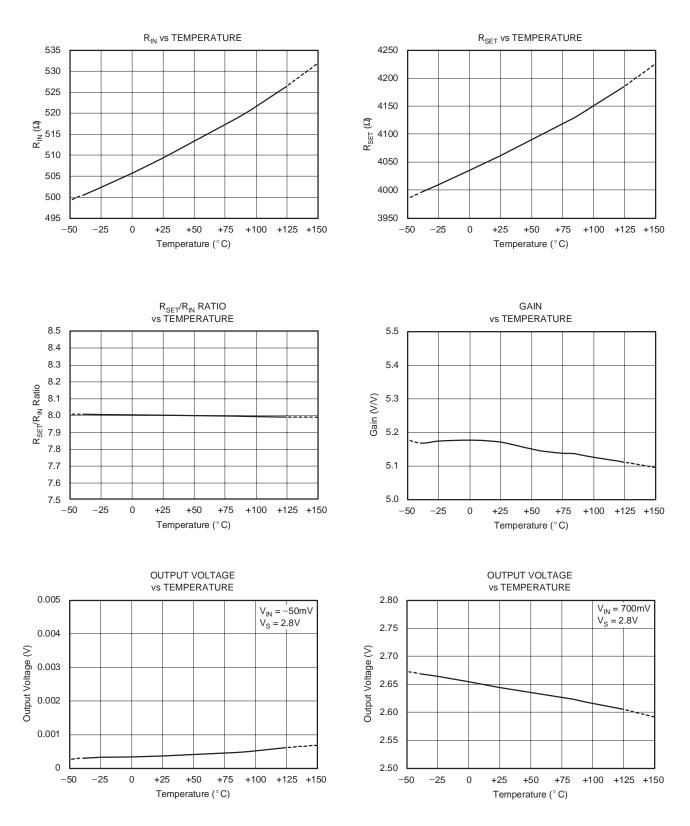

#### TYPICAL CHARACTERISTICS: V<sub>S</sub> = 2.8V

At  $T_A = +25^{\circ}C$  and  $R_L = 150\Omega$ , unless otherwise noted.

### TYPICAL CHARACTERISTICS: V<sub>S</sub> = 2.8V (continued)

At  $T_A = +25^{\circ}C$  and  $R_L = 150\Omega$ , unless otherwise noted.

TEXAS STRUMENTS www.ti.com

OUTPUT LEAKAGE CURRENT vs TEMPERATURE

OUTPUT LEAKAGE

### TYPICAL CHARACTERISTICS: V<sub>S</sub> = 2.8V (continued)

At  $T_A = +25^{\circ}C$  and  $R_L = 150\Omega$ , unless otherwise noted.

#### DIFFERENTIAL GAIN

| INP = 2 | A – C | SYNC = | INT | MTIME   | = 10s        | LINE = 330 |

|---------|-------|--------|-----|---------|--------------|------------|

|         |       | -5     |     |         | . <u>0</u> . | +5         |

| DG1     | -0.   | 6 %1 ' |     | L i L i | ' 💼 ' ' ' '  |            |

| DG2     | -1.   | 0%.    |     |         |              |            |

| DG3     | -1.   | 1 %.   |     |         |              |            |

| DG4     | -1.   | 2%.    |     | i i     |              |            |

| DG5     | -0.   | 8 %5   |     |         |              |            |

|         |       | STEPS  |     |         | ZOOM         | MODE       |

|         |       | 4 5    |     |         | 0 1          | 2 1        |

#### DIFFERENTIAL PHASE

|     |   |   |    |   |       |    |     |       |   |      |            | _ |

|-----|---|---|----|---|-------|----|-----|-------|---|------|------------|---|

| INP | = | А | -  | C | SYNC  | =  | INT | MTIME | = | 10s  | LINE = 330 | 1 |

|     |   |   |    |   |       | -5 |     | 1     |   | 0    | +5         |   |

| DP1 |   |   | 1. | 1 | dg1   | •  |     |       |   |      |            |   |

| DP2 |   |   | 1. | 6 | dg.   |    |     |       |   |      |            |   |

| DP3 |   |   | 1. | 6 | dg.   |    |     |       |   |      |            |   |

| DP4 |   |   | 1. | 5 | dg.   |    |     |       |   |      |            |   |

| DP5 |   |   | 1. | 1 | dg5   |    |     |       |   |      |            |   |

|     |   |   |    |   | STEPS |    |     |       |   | ZOOM | MODE       |   |

|     |   |   |    |   | 4     | 5  |     |       | 0 | 1    | 2 1        |   |

6

# **APPLICATIONS INFORMATION**

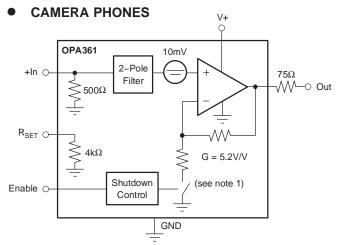

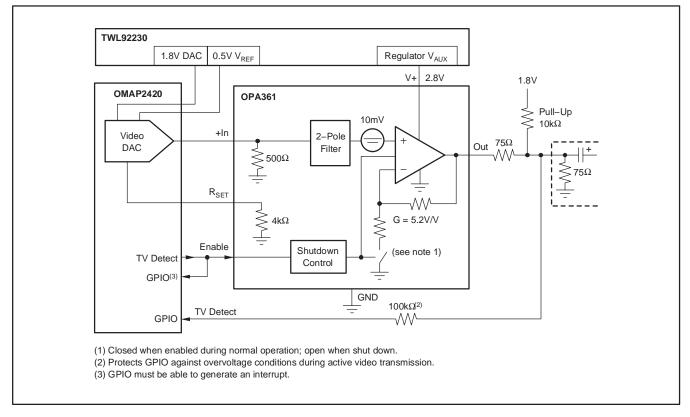

The OPA361 video amplifier has been optimized to fit seamlessly with Texas Instruments' OMAP242x Multimedia processor. The following features have been integrated to provide excellent video performance.

- Internal gain setting resistors (G = 5.2V/V) reduce the number of external components needed in the video circuit.

- Integration of the 500Ω video encoder load resistor and 4kΩ R<sub>SET</sub> resistor used by the OMAP242x helps minimize the number of external components and also ensures excellent ratio and temperature tracking. This feature helps to keep the overall gain accurate and stable over temperature.

- TV-detection support in connection with an OMAP242x multimedia processor. This feature

SBOS334A - SEPTEMBER 2005 - REVISED JANUARY 2006

helps to automate start/stop operation of the TV-out function and minimizes power consumption.

- A 2-pole filter is incorporated for DAC signal reconstruction.

- The OPA361 employs an internal level shift circuit that avoids sync pulse clipping and allows DC-coupled output.

- A shutdown feature reduces quiescent current to less than 1.5μA—crucial for portable applications

Although OPA361 is optimized for the OMAP242x processor, it is also suitable to interface with any digital media processor that outputs a video signal on the order of  $0.4V_{PP}$  to  $0.5V_{PP}$ .

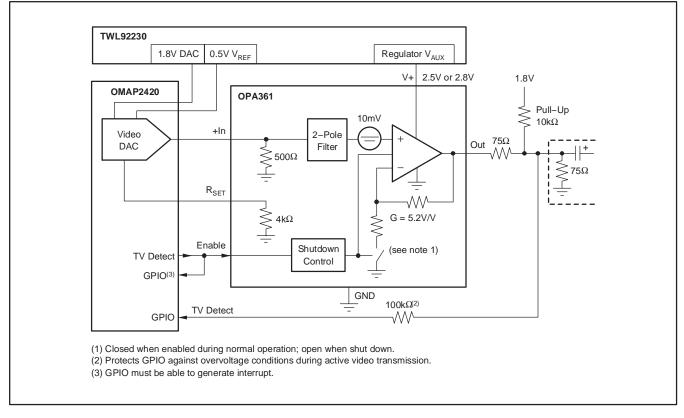

Figure 1 shows a typical application drawing with the OMAP242x processor and the TWL92230 Energy Management Chip.

Figure 1. Typical Application using the OMAP242x and the TWL92230

#### OPERATING VOLTAGE

The OPA361 is fully specified from 2.5V to 3.3V over a temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C. Parameters that vary significantly with operating voltages or temperature are shown in the Typical Characteristics. Power-supply pins should be bypassed with 100nF ceramic capacitors.

#### INPUT VOLTAGE

The input common-mode range of the OPA361 series extends from GND to 0.55V on a 3.3V supply. The input range is limited by the internal gain in conjunction with the maximum output swing capability and the power-supply voltage.

#### INPUT OVERVOLTAGE PROTECTION

All OPA361 pins are static-protected with internal ESD protection diodes connected to the supplies. These diodes will provide input overdrive protection if the current is externally limited to 10mA.

#### ENABLE/SHUTDOWN

The OPA361 has a shutdown feature that disables the output and reduces the quiescent current to less than  $1.5\mu$ A. This feature is especially useful for portable video applications, where the device is infrequently connected to a television (TV) or other video device.

The Enable logic input voltage is referenced to the OPA361 GND pin. A logic level HIGH applied to the enable pin enables the op amp. The logic levels are compatible with 1.8V CMOS logic levels. A valid logic HIGH is defined as > 1.3V above GND. A valid logic LOW is defined as < 0.35V above GND. If the Enable pin is not connected, internal pull-up circuitry will enable the amplifier.

RUMENTS

When disabling the OPA361, internal circuitry also disconnects the internal gain setting feedback. This feature is in support of the TV-detection function. See the *TV-Detect Function* section for more detailed information.

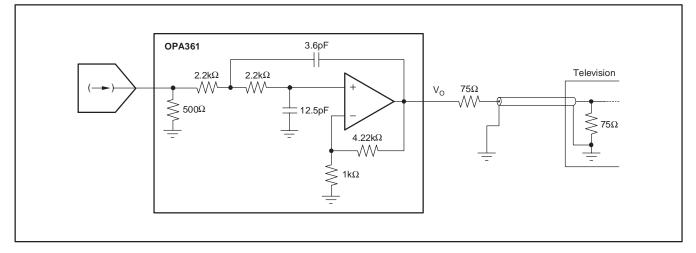

#### **INTERNAL 2-POLE FILTER**

The OPA361 filter is a Sallen-Key topology with a 9MHz cutoff frequency. Figure 2 shows a detailed drawing of the filter components. This filter allows video signals to pass without any visible distortion, as shown in Figure 3 through Figure 6. The video encoder embedded in the OMAP242x processor typically samples at 54MHz. At this frequency, the attenuation is typically 23dB, which effectively attenuates the sampling aliases.

The internal 500 $\Omega$  resistor on the input to GND converts the output current of the OMAP2420 internal video DAC into a voltage. It is also part of the Sallen-Key filter. Using an external resistor to adjust the input voltage range will also alter the filter characteristics.

Figure 2. Filter Structure of the OPA361

#### **Video Performance**

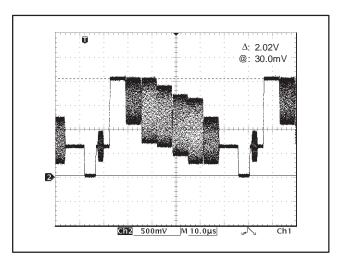

The color bar signal in Figure 3 shows excellent amplitude characteristics and no attenuation of colors with respect to the luminance signal.

Figure 3. 100/75 Color Bar Signal at Output of OPA361

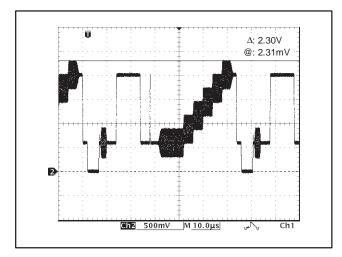

The CCIR330/5 test pattern requires one of the greatest dynamic ranges, and therefore tests the OPA361 output voltage swing capability. The scope plot shown in Figure 4 has been taken with a 2.8V supply and shows no clipping on the top side of the signal.

Figure 4. CCIR330/5: No Clipping, Even On 2.8V Supply

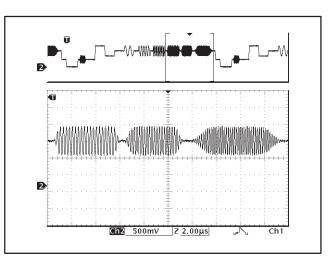

The multiburst test patterns have different sine-wave burst sections with the following frequencies: 0.5MHz, 1MHz, 2MHz, 4MHz, 4.8MHz and 5.8MHz with 420mV<sub>PP</sub>. There is no visible attenuation even at the highest frequencies, which indicates a very flat frequency response of the OPA361. As shown in Figure 5 and Figure 6, the top line illustrates the full signal and the bottom line is a more detailed view of the last three sine wave bursts.

Figure 5. Multiburst Signal (CCIR 18/1) Shows Very Flat Frequency Response

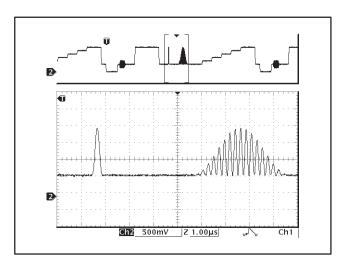

The CCIR17 test pattern contains a 2T and a 20T pulse, as shown in Figure 6. The 2T pulse is used to check for pulse distortion and reflection, and the 20T pulse is used to check for amplitude and group delay between chrominance and luminance. Neither pulse exhibits any distortion or group delay artifacts.

Figure 6. CCIR 17 2T and 20T Pulses Show No Visible Distortion

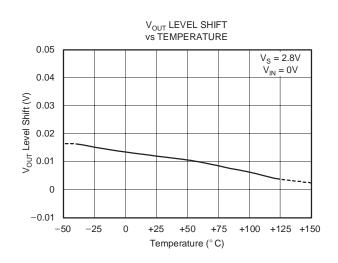

#### INTERNAL LEVEL SHIFT

Many common video DACs embedded in digital media processors, like the new OMAP242x processors, operate on a single supply (no negative supply). Typically, the lowest point of the sync pulse output by these video DACs is close to 0V. With a 0V input, the output of a common single-supply op amp saturates at a voltage > 0V. This effect would clip the sync pulse, and therefore degrade the video signal integrity. The OPA361 employs an internal level shift circuit to avoid clipping. The input signal is typically shifted by approximately 11mV. This shift is well within the linear output voltage range of the OPA361 with a standard 150 $\Omega$  video load.

#### **Output Swing Capability**

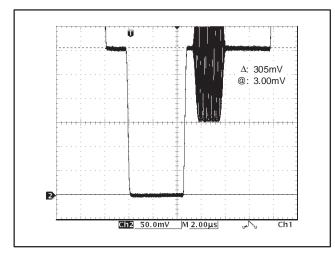

Figure 7 shows the true output swing capability of the OPA361 by taking the tip of the input sync pulse to a slightly negative voltage. Even when the output sync tip is at 3mV, the output after the 75 $\Omega$  series termination still shows no clipping of the sync pulse.

Figure 7. No Clipping of the Sync Pulse

#### **TV-Detect Function**

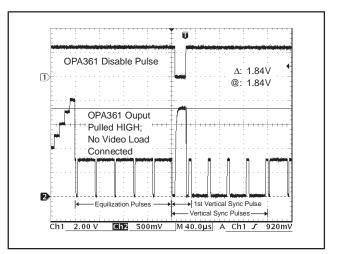

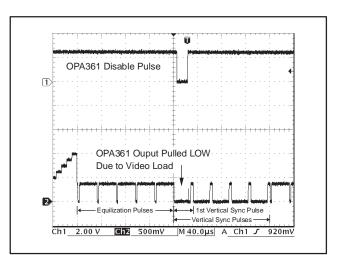

The TV-detection feature of the OPA361 works in conjunction with the OMAP242x (or other processors) to detect if a television is connected to the video output of the device. In order to detect a TV load, the OPA361 is briefly turned off, ideally during the first vertical sync pulse. For the detection, a simple pull-up resistor to the processor logic supply is used on the output of the OPA361. The

voltage level is pulled LOW if the TV (or other video equipment) is connected, or HIGH if nothing is connected. A GPIO in the processor can be used to read this logic level and decide if a video load is connected. Figure 8 shows a scope plot with the TV disconnected and Figure 9 shows a scope plot with the TV connected; the upper line in both figures is the disable pulse. Figure 10 shows a circuit drawing using the TV-detect signal to disable or enable the OPA361.

Figure 8. Output of OPA361 Pulled Up To 1.8V During Disable: TV Disconnected

Figure 9. Output of OPA361 Pulled Down: TV Connected.

#### Figure 10. Using TV-Detect Signal to Disable/Enable the OPA361

Disabling the OPA361 also disconnects the internal feedback resistors' path to GND, and therefore there is no current flowing from the logic supply through the pull-up resistor to GND if no video load is connected; this helps to conserve battery life. The typical leakage when the output is pulled high and OPA361 is disabled is only about 300pA.

The following functionality can be achieved by implementing TV-detection:

- Automatic video start by *polling* the video line periodically.

- Automatic video stop if the TV (or other equipment) is disconnected.

Proper implementation allows to significantly simplify the user interface.

For more information, see Application Report SBOA109, *OPA361 and TV Detection*, available for download at www.ti.com.

#### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                 |              |              |

| OPA361AIDCKR          | Active | Production    | SC70 (DCK)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | AUY          |

| OPA361AIDCKR.A        | Active | Production    | SC70 (DCK)   6 | 3000   LARGE T&R      | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | AUY          |

| OPA361AIDCKT          | Active | Production    | SC70 (DCK)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | AUY          |

| OPA361AIDCKT.A        | Active | Production    | SC70 (DCK)   6 | 250   SMALL T&R       | Yes  | NIPDAU        | Level-2-260C-1 YEAR | -40 to 125   | AUY          |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

OTHER QUALIFIED VERSIONS OF OPA361 :

www.ti.com

• Automotive : OPA361-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

### PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

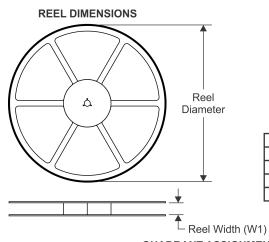

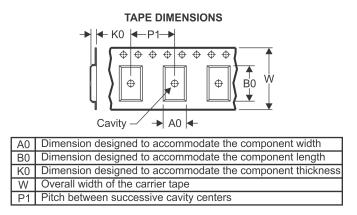

#### TAPE AND REEL INFORMATION

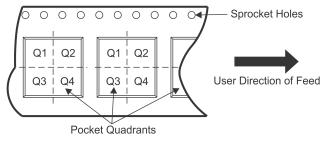

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA361AIDCKR | SC70            | DCK                | 6 | 3000 | 178.0                    | 9.0                      | 2.4        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA361AIDCKR | SC70            | DCK                | 6 | 3000 | 179.0                    | 8.4                      | 2.2        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA361AIDCKT | SC70            | DCK                | 6 | 250  | 178.0                    | 9.0                      | 2.4        | 2.5        | 1.2        | 4.0        | 8.0       | Q3               |

| OPA361AIDCKT | SC70            | DCK                | 6 | 250  | 179.0                    | 8.4                      | 2.25       | 2.4        | 1.22       | 4.0        | 8.0       | Q3               |

TEXAS INSTRUMENTS

www.ti.com

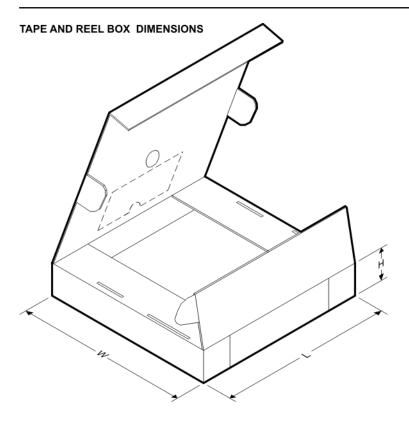

### PACKAGE MATERIALS INFORMATION

5-Jan-2021

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| OPA361AIDCKR | SC70         | DCK             | 6    | 3000 | 180.0       | 180.0      | 18.0        |

| OPA361AIDCKR | SC70         | DCK             | 6    | 3000 | 213.0       | 191.0      | 35.0        |

| OPA361AIDCKT | SC70         | DCK             | 6    | 250  | 180.0       | 180.0      | 18.0        |

| OPA361AIDCKT | SC70         | DCK             | 6    | 250  | 213.0       | 191.0      | 35.0        |

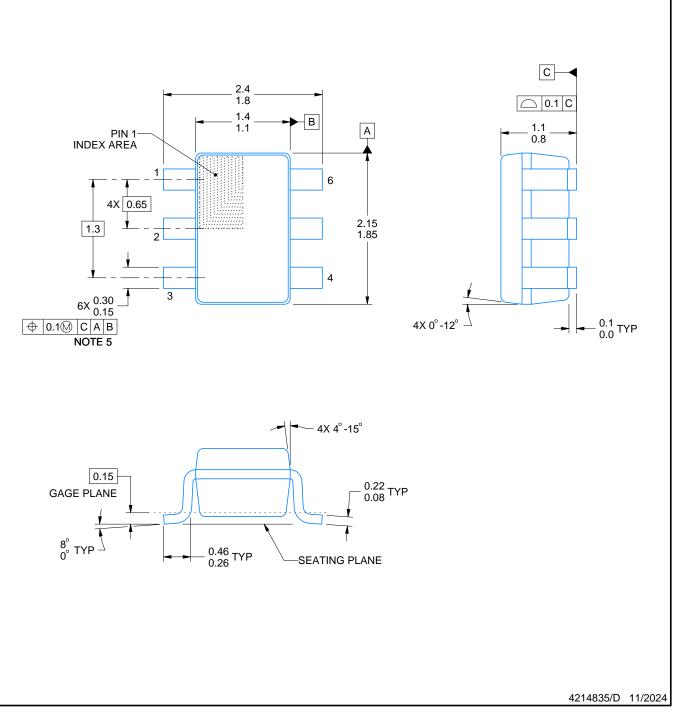

## **DCK0006A**

### **PACKAGE OUTLINE**

### SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing an integration of a constraint of the minimeters. Any dimensions in parentnesis are for reference only. Dimensioning and to per ASME Y14.5M.

This drawing is subject to change without notice.

Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.15 per side.

Falls within JEDEC MO-203 variation AB.

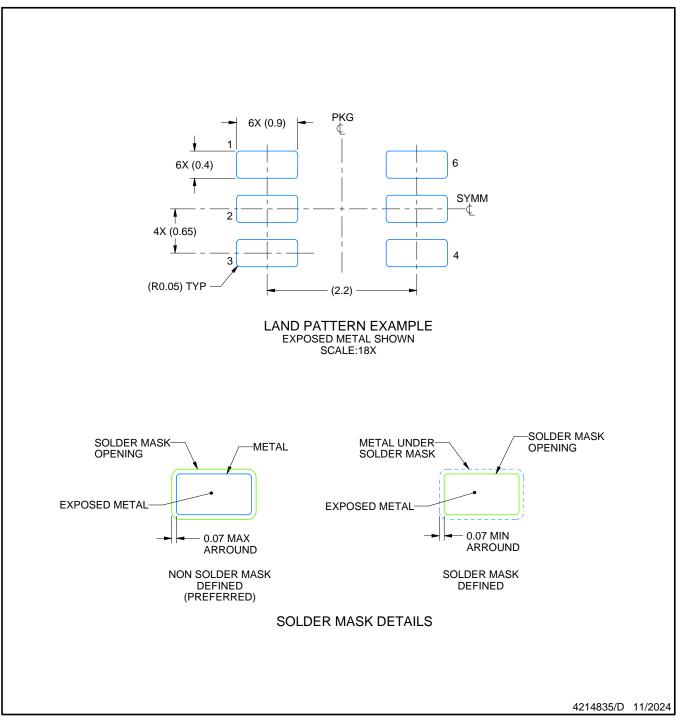

### **DCK0006A**

## **EXAMPLE BOARD LAYOUT**

### SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

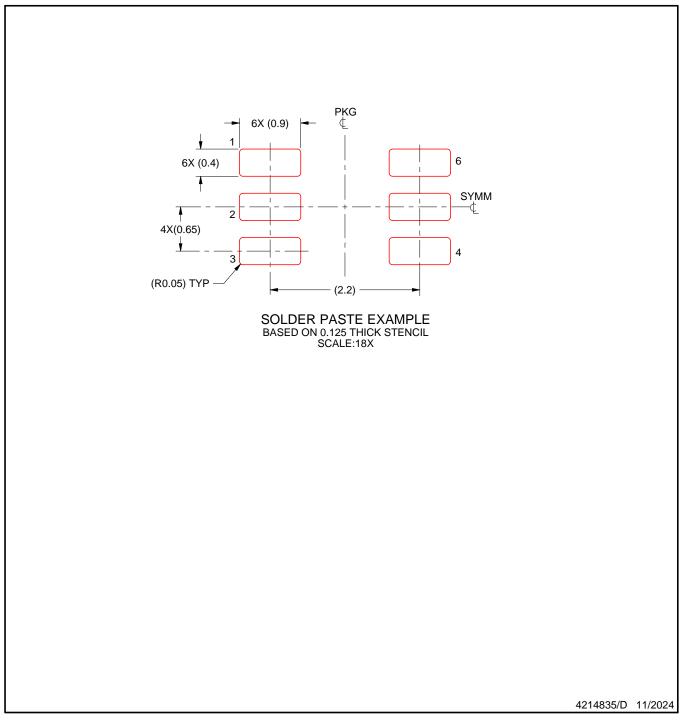

### **DCK0006A**

## **EXAMPLE STENCIL DESIGN**

### SOT - 1.1 max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Board assembly site may have different recommendations for stencil design.

<sup>7.</sup> Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated