# LP5862 2 × 18 LED Matrix Driver with 8-Bit Analog and 8-/16-Bit PWM Dimming

#### 1 Features

- LED matrix topology:

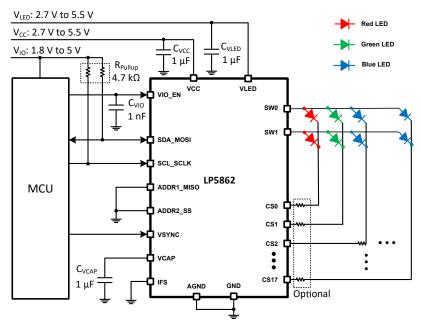

- 18 constant current sinks with 2 scan switches for 36 LED dots

- Configurable for 1 to 2 scan switches

- Operating voltage range:

- V<sub>CC</sub>/V<sub>LED</sub> range: 2.7V to 5.5V

- Logic pins compatible with 1.8V, 3.3V, and 5V

- 18 constant current sinks with high precision:

- 50mA per current sink when V<sub>CC</sub> ≥ 3.3V

- Device-to-device error: ±5%

- Channel-to-channel error: ±5%

- Phase-shift for balanced transient power

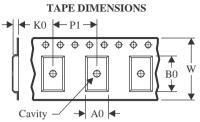

- Ultra-low power consumption:

- Shutdown mode: I<sub>CC</sub> ≤ 2µA when EN = Low

- Standby mode: I<sub>CC</sub> ≤ 10µA when EN = High and CHIP\_EN = 0 (data retained)

- Active mode: I<sub>CC</sub> = 3mA (typ.) when channel current = 5mA

- Flexible dimming options:

- Individual ON, OFF control for each LED dot

- Analog dimming (current gain control)

- Global 3-bit Maximum Current (MC) setting for all LED dots

- 3 groups of 7-bit Color Current (CC) setting for red, green, and blue

- Individual 8-bit Dot Current (DC) setting for each LED dot

- PWM dimming with audible-noise-free frequency

- Global 8-bit PWM dimming for all LED dots

- 3 programmable groups of 8-bit PWM dimming for LED dot arbitrary mapping

- Individual 8-bit or 16-bit PWM dimming for each LED dot

- Full addressable SRAM to minimize data traffic

- Individual LED dot open and short detection

- Deghosting and low brightness compensation

- Interface options:

- 1MHz (max.) I<sup>2</sup>C interface when IFS = Low

- 12MHz (max.) SPI interface when IFS = High

### 2 Applications

- · LED animation and indication for:

- Keyboard, mouse, and gaming accessories

- Major and smart home appliances

- Smart speaker, wired and wireless speaker

- Audio mixer, DJ equipment, and broadcast

- Access equipment, switches, and servers

- Constant current sinks for optical module

### 3 Description

Electronic devices are becoming smarter, requiring larger quantity of LEDs for animation and indication purposes. A high-performance LED matrix driver is required to improve user experience with small solution size.

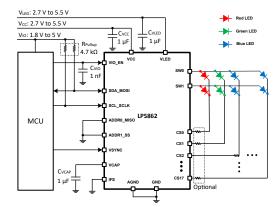

The LP586x devices are a family of high performance LED matrix drivers. The device integrates 18 constant current sinks with N (N = 1/2/4/6/8/11) switching MOSFETs to support N × 18 LED dots or N × 6 RGB LEDs. The LP5862 integrates two MOSFETs for up to 36 LED dots or 12 RGB LEDs.

The LP5862 supports both analog dimming and PWM dimming methods. For analog dimming, each LED dot can be adjusted with 256 steps. For PWM dimming, the integrated 8-bit or 16-bit configurable PWM generators enable smooth and audible-noisefree dimming control. Each LED dot can also be arbitrarily mapped into 8-bit Group PWM to achieve dimming control together.

The LP5862 device implements full addressable SRAM to minimize the data traffic. The ghostcancellation circuitry is integrated to eliminate both upside and downside ghosting. The LP5862 also supports LED open and short detection functions. Both 1-MHz (maximum) I<sup>2</sup>C and 12-MHz (maximum) SPI are available in LP5862.

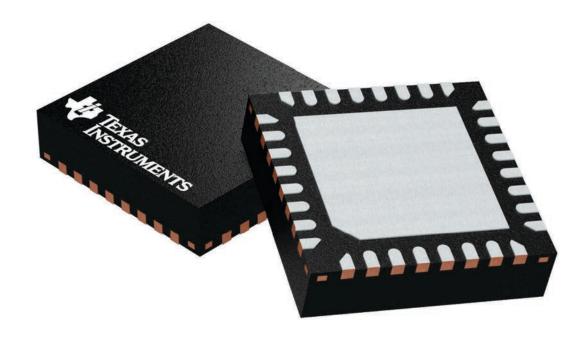

#### **Device Information**

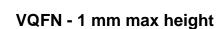

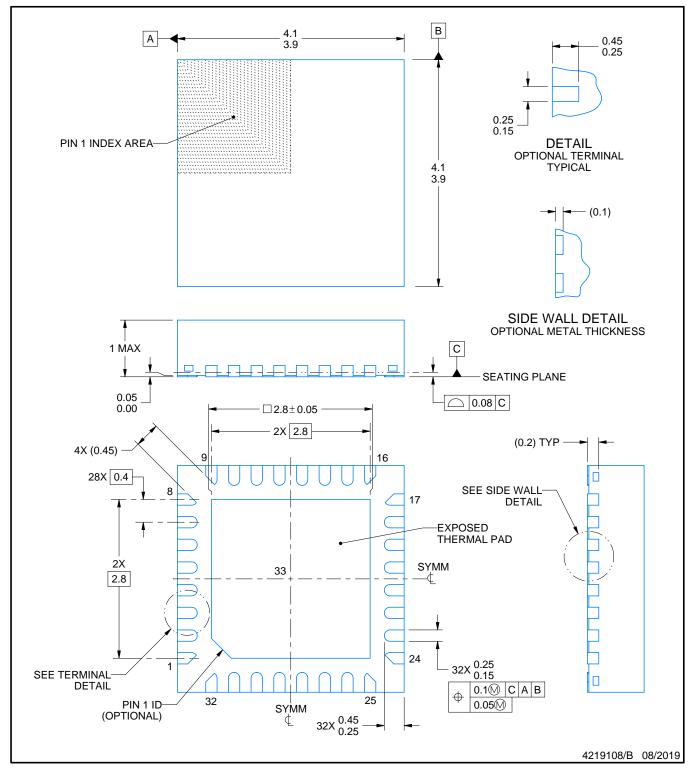

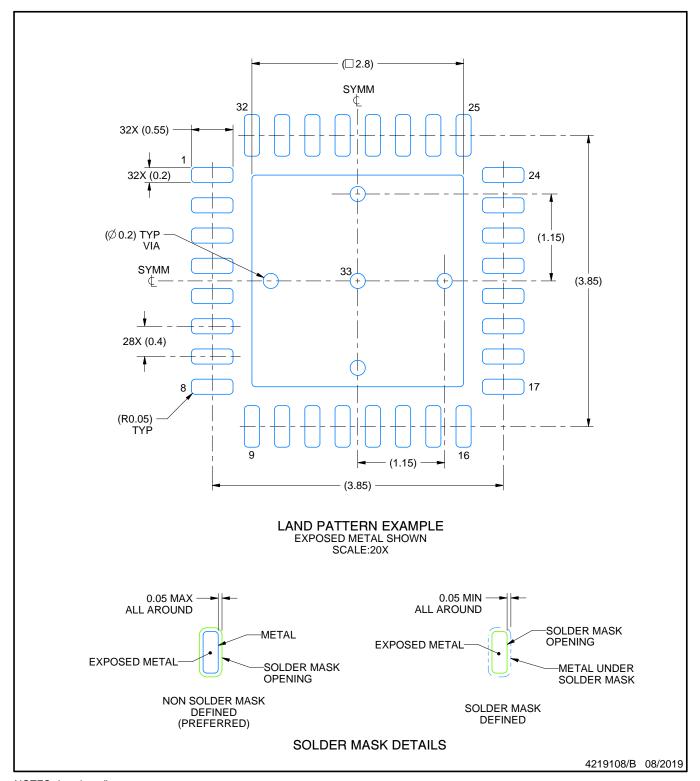

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM) |  |

|-------------|------------------------|-----------------|--|

| LP5862      | VQFN (32)              | 4.00mm × 4.00mm |  |

|             | TSSOP (38)             | 9.70mm × 4.40mm |  |

For all available packages, see the orderable addendum at the end of the data sheet.

**Simplified Schematic**

# **Table of Contents**

| 1 Features                           | 1              | 7.5 Programming                                      | . 25 |

|--------------------------------------|----------------|------------------------------------------------------|------|

| 2 Applications                       |                | 7.6 Register Maps                                    |      |

| 3 Description                        |                | 8 Application and Implementation                     |      |

| 4 Device Comparison                  |                | 8.1 Application Information                          |      |

| 5 Pin Configuration and Functions    | 4              | 8.2 Typical Application                              |      |

| 6 Specifications                     | <b>7</b>       | 9 Power Supply Recommendations                       |      |

| 6.1 Absolute Maximum Ratings         |                | 10 Layout                                            |      |

| 6.2 ESD Ratings                      |                | 10.1 Layout Guidelines                               |      |

| 6.3 Recommended Operating Conditions | <mark>7</mark> | 10.2 Layout Example                                  |      |

| 6.4 Thermal Information              | 7              | 11 Device and Documentation Support                  |      |

| 6.5 Electrical Characteristics       | 8              | 11.1 Receiving Notification of Documentation Updates | 38   |

| 6.6 Timing Requirements              | 9              | 11.2 Support Resources                               | . 38 |

| 6.7 Typical Characteristics          | 12             | 11.3 Trademarks                                      |      |

| 7 Detailed Description               |                | 11.4 Electrostatic Discharge Caution                 |      |

| 7.1 Overview                         |                | 11.5 Glossary                                        |      |

| 7.2 Functional Block Diagram         | 14             | 12 Revision History                                  |      |

| 7.3 Feature Description              |                | 13 Mechanical, Packaging, and Orderable              |      |

| 7.4 Device Functional Modes          |                | Information                                          | 39   |

|                                      |                |                                                      |      |

# **4 Device Comparison**

| PART NUMBER | MATERIAL                   | LED DOT NUMBER | PACKAGE <sup>(2)</sup> | SOFTWARE<br>COMPATIBLE |  |

|-------------|----------------------------|----------------|------------------------|------------------------|--|

| LP5861      | LP5861RSMR                 | 18 × 1 = 18    | VQFN-32                |                        |  |

| LP5862      | LP5862RSMR                 | 18 × 2 = 36    | VQFN-32                |                        |  |

|             | LP5862DBTR                 | 10 ^ 2 - 30    | TSSOP-38               |                        |  |

| LP5864      | LP5864RSMR                 | 18 × 4 = 72    | VQFN-32                |                        |  |

| LF3004      | LP5864MRSMR <sup>(1)</sup> | 10 ^ 4 - 72    | VQFN-32                |                        |  |

|             | LP5866RKPR                 |                | VQFN-40                | Yes                    |  |

| LP5866      | LP5866DBTR                 | 18 × 6 = 108   | TSSOP-38               |                        |  |

|             | LP5866MDBTR <sup>(1)</sup> |                | 1330F-30               |                        |  |

| LP5868      | LP5868RKPR                 | 18 × 8 = 144   | VQFN-40                |                        |  |

| LP5860      | LP5862RKPR                 | 18 × 11 = 198  | VQFN-40                |                        |  |

| LF3000      | LP5862MRKPR <sup>(1)</sup> | 10 ^ 11 - 190  | v Qr 1N-40             |                        |  |

<sup>(1)</sup> Extended Temperature devices, supporting –55°C to approximately 125°C operating ambient temperature.

<sup>(2)</sup> The same packages are hardware compatible.

# **5 Pin Configuration and Functions**

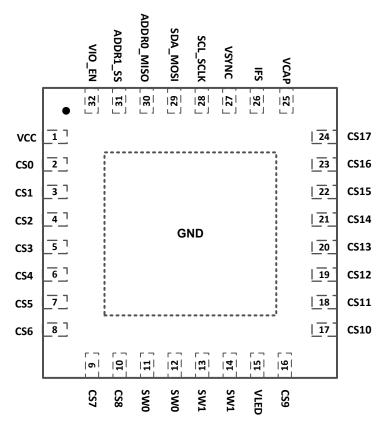

Figure 5-1. LP5862 RSM Package 32-Pin VQFN with Exposed Thermal Pad Top View

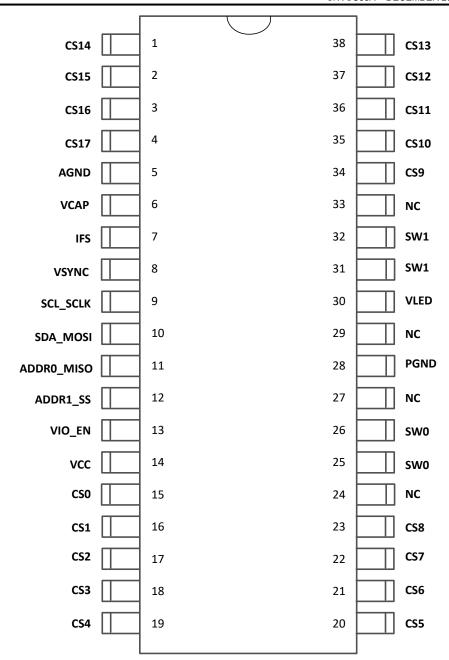

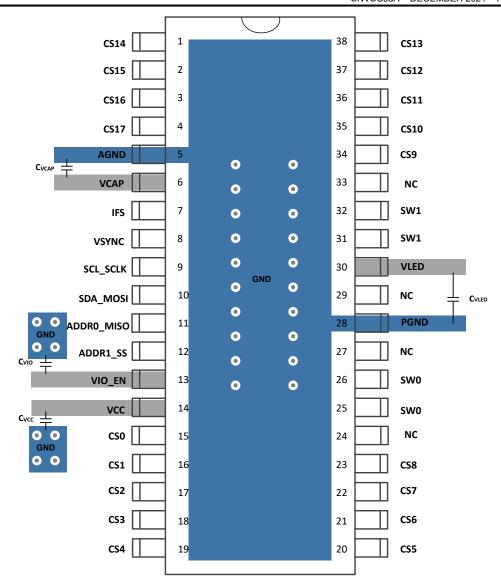

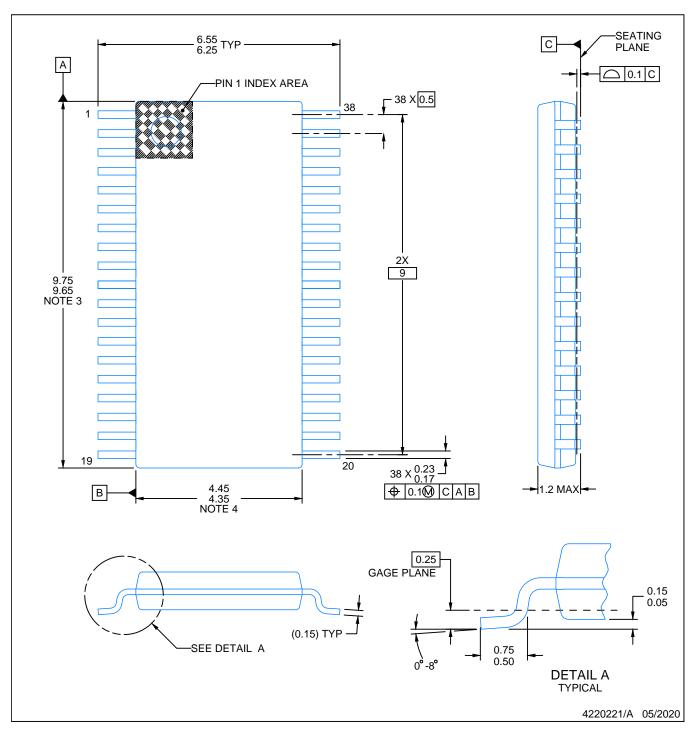

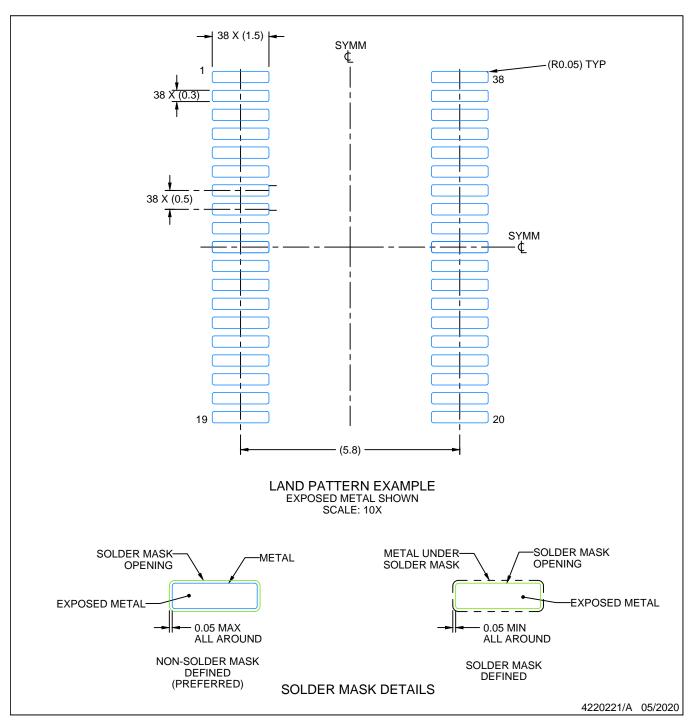

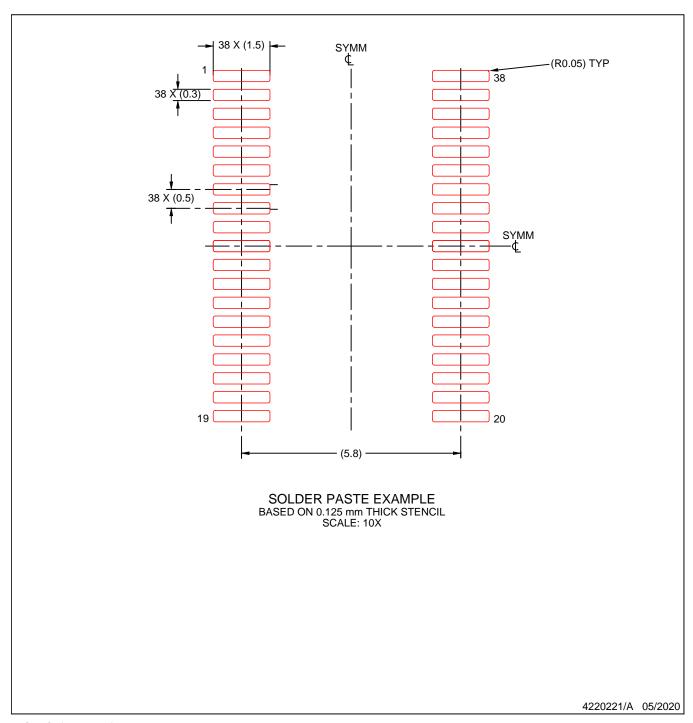

Figure 5-2. LP5862 DBT Package 38-Pin TSSOP Top View

**Table 5-1. Pin Functions**

|      | PIN     |         | I/O   | DESCRIPTION                                                                                                                             |  |  |

|------|---------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME | RSM NO. | DBT NO. | 1/0   | DESCRIPTION                                                                                                                             |  |  |

| VCC  | 1       | 14      | Power | Power supply for device. A 1-µF capacitor must be connected between this pin with GND and be placed as close to the device as possible. |  |  |

| CS0  | 2       | 15      | 0     | O Current sink 0. If not used, this pin must be left floating.                                                                          |  |  |

| CS1  | 3       | 16      | 0     | Current sink 1. If not used, this pin must be left floating.                                                                            |  |  |

| CS2  | 4       | 17      | 0     | Current sink 2. If not used, this pin must be left floating.                                                                            |  |  |

| CS3  | 5       | 18      | 0     | Current sink 3. If not used, this pin must be left floating.                                                                            |  |  |

| CS4  | 6       | 19      | 0     | Current sink 4. If not used, this pin must be left floating.                                                                            |  |  |

| CS5  | 7       | 20      | 0     | Current sink 5. If not used, this pin must be left floating.                                                                            |  |  |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

## Table 5-1. Pin Functions (continued)

|                | PIN                    |             | 1/0     | DECODIDETION                                                                                                                                                      |

|----------------|------------------------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | RSM NO.                | DBT NO.     | I/O     | DESCRIPTION                                                                                                                                                       |

| CS6            | 8                      | 21          | 0       | Current sink 6. If not used, this pin must be left floating.                                                                                                      |

| CS7            | 9                      | 22          | 0       | Current sink 7. If not used, this pin must be left floating.                                                                                                      |

| CS8            | 10                     | 23          | 0       | Current sink 8. If not used, this pin must be left floating.                                                                                                      |

| SW0            | 11/12                  | 25/26       | 0       | High-side PMOS switch output 0. Both 2 pins must be tied together. If not used, this pin must be left floating.                                                   |

| SW1            | 13/14                  | 31/32       | 0       | High-side PMOS switch output 1. Both 2 pins must be tied together. If not used, this pin must be left floating.                                                   |

| VLED           | 15                     | 30          | Power   | Power input for high-side switches.                                                                                                                               |

| CS9            | 16                     | 34          | 0       | Current sink 9. If not used, this pin must be left floating.                                                                                                      |

| CS10           | 17                     | 35          | 0       | Current sink 10. If not used, this pin must be left floating.                                                                                                     |

| CS11           | 18                     | 36          | 0       | Current sink 11. If not used, this pin must be left floating.                                                                                                     |

| CS12           | 19                     | 37          | 0       | Current sink 12. If not used, this pin must be left floating.                                                                                                     |

| CS13           | 20                     | 38          | 0       | Current sink 13. If not used, this pin must be left floating.                                                                                                     |

| CS14           | 21                     | 1           | 0       | Current sink 14. If not used, this pin must be left floating.                                                                                                     |

| CS15           | 22                     | 2           | 0       | Current sink 15. If not used, this pin must be left floating.                                                                                                     |

| CS16           | 23                     | 3           | 0       | Current sink 16. If not used, this pin must be left floating.                                                                                                     |

| CS17           | 24                     | 4           | 0       | Current sink 17. If not used, this pin must be left floating.                                                                                                     |

| VCAP           | 25                     | 6           | 0       | Internal LDO output. An 1-µF capacitor must be connected between this pin with GND. Place the capacitor as close to the device as possible.                       |

| IFS            | 26                     | 7           | I       | Interface type select. I <sup>2</sup> C is selected when IFS is low. SPI is selected when IFS is high. A resistor must be connected between VIO and this pin.     |

| VSYNC          | 27                     | 8           | I       | External synchronize signal for display mode 2 and mode 3.                                                                                                        |

| SCL_SCLK       | 28                     | 9           | I       | I <sup>2</sup> C clock input or SPI clock input. Pull up to VIO when configured as I <sup>2</sup> C.                                                              |

| SDA_MOSI       | 29                     | 10          | I/O     | I <sup>2</sup> C data input or SPI leader output follower input. Pull up to VIO when configured as I <sup>2</sup> C.                                              |

| ADDR0_MIS<br>O | 30                     | 11          | I/O     | I <sup>2</sup> C address select 0 or SPI leader input follower output.                                                                                            |

| ADDR1_SS       | 31                     | 12          | 1       | I <sup>2</sup> C address select 1 or SPI follower select.                                                                                                         |

| VIO_EN         | 32                     | 13          | Power,I | Power supply for digital circuits and chip enable. A 1-nF capacitor must be connected between this pin with GND and be placed as close to the device as possible. |

| GND            | Exposed<br>Thermal Pad | 5/28        | Ground  | Common ground plane.                                                                                                                                              |

| NC             | -                      | 24/27/29/33 |         | No connection.                                                                                                                                                    |

## **6 Specifications**

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                                                                                                 |                      | MIN  | MAX | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----|------|

| Voltage on V <sub>CC</sub> / V <sub>LED</sub> / VIO /<br>EN / CS / SW / SDA / SCL / SCLK /<br>MOSI / MISO / SS / ADDR0 / ADDR1 /<br>VSYNC / IFS |                      | -0.3 | 6   | V    |

| Voltage on VCAP                                                                                                                                 |                      | -0.3 | 2   | V    |

| TJ                                                                                                                                              | Junction temperature | -55  | 150 | °C   |

| T <sub>stg</sub>                                                                                                                                | Storage temperature  | -65  | 150 | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                                            |                                                                                     |                                                                                 | VALUE | UNIT |

|--------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------|------|

| V                                          | Electrostatic discharge                                                             | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup> | ±3000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±1000                                                                           | V     |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                                         |                               | MIN  | NOM MAX | UNIT |

|-------------------------------------------------------------------------|-------------------------------|------|---------|------|

| Input voltage on V <sub>CC</sub>                                        | Supply voltage                | 2.7  | 5.5     | V    |

| Input voltage on V <sub>LED</sub>                                       | LED supply voltage            | 2.7  | 5.5     | V    |

| Input voltage on VIO_EN                                                 |                               | 1.65 | 5.5     | V    |

| Voltage on SDA / SCL / SCLK / MOSI /<br>MISO / SS / ADDRx / VSYNC / IFS |                               |      | VIO     | V    |

| T <sub>A</sub>                                                          | Operating ambient temperature | -40  | 85      | °C   |

### **6.4 Thermal Information**

|                       |                                              | LP         | 5862        |      |

|-----------------------|----------------------------------------------|------------|-------------|------|

|                       | THERMAL METRIC (1)                           | RSM (VQFN) | DBT (TSSOP) | UNIT |

|                       |                                              | 32 Pins    | 38 Pins     |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 32,9       | 67.0        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 29.2       | 20.1        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.3       | 27.4        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4        | 1.0         | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 12.3       | 27.0        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.7        | n/a         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

$V_{CC}$  = 3.3 V,  $V_{LED}$  = 3.8 V, VIO = 1.8 V and  $T_A$  = -40 °C to +85 °C; Typical values are at  $T_A$  = 25 °C (unless otherwise specified)

|                     | PARAMETER                                                                                                                    | TEST CONDITIONS                                                                                                                                  | MIN        | TYP  | MAX  | UNIT |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------|------|

| Power su            | upplies                                                                                                                      |                                                                                                                                                  |            |      |      |      |

| V <sub>CC</sub>     | Device supply voltage                                                                                                        |                                                                                                                                                  | 2.7        |      | 5.5  | V    |

| V <sub>UVR</sub>    | Undervoltage restart                                                                                                         | V <sub>CC</sub> rising, Test mode                                                                                                                |            |      | 2.5  | V    |

| V <sub>UVF</sub>    | Undervoltage shutdown                                                                                                        | V <sub>CC</sub> falling, Test mode                                                                                                               | 1.9        |      |      | V    |

| V <sub>UV_HYS</sub> | Undervoltage shutdown hysteresis                                                                                             |                                                                                                                                                  |            | 0.3  |      | V    |

| V <sub>CAP</sub>    | Internal LDO output                                                                                                          | V <sub>CC</sub> = 2.7 V to 5.5 V                                                                                                                 |            | 1.78 |      | V    |

|                     | Shutdown supply current I <sub>SHUTDOWN</sub>                                                                                | $V_{EN}$ = 0 V, CHIP_EN = 0 (bit), measure the total current from $V_{CC}$ and $V_{LED}$                                                         |            | 0.1  | 1    | μΑ   |

| I <sub>CC</sub>     | Standby supply current I <sub>STANDBY</sub>                                                                                  | $V_{\text{EN}}$ = 3.3 V, CHIP_EN = 0 (bit), measure the total current from $V_{\text{CC}}$ and $V_{\text{LED}}$                                  |            | 5.5  | 10   | μΑ   |

|                     | Active mode supply current I <sub>NORMAL</sub>                                                                               | $V_{EN}$ = 3.3 V, CHIP_EN = 1 (bit), all channels I <sub>OUT</sub> = 5 mA (MC = 1, CC = 127, DC = 256), measure the current from V <sub>CC</sub> |            | 4.3  | 6    | mA   |

| V <sub>LED</sub>    | LED supply voltage                                                                                                           |                                                                                                                                                  | 2.7        |      | 5.5  | V    |

| V <sub>VIO</sub>    | VIO supply voltage                                                                                                           |                                                                                                                                                  | 1.65       |      | 5.5  | V    |

| I <sub>VIO</sub>    | VIO supply current                                                                                                           | Interface idle                                                                                                                                   |            |      | 5    | μA   |

| Output S            | tages                                                                                                                        |                                                                                                                                                  |            |      | - 11 |      |

|                     | Constant current sink output range (CS0                                                                                      | 2.7 <= V <sub>CC</sub> < 3.3 V, PWM = 100%                                                                                                       | 0.1        |      | 40   | mA   |

| I <sub>CS</sub>     | - CS17)                                                                                                                      | V <sub>CC</sub> >= 3.3 V PWM = 100%                                                                                                              | 0.1        |      | 50   | mA   |

| I <sub>LKG</sub>    | Leakage current (CS0 - CS17)                                                                                                 | channels off, up_deghost = 0, V <sub>CS</sub> = 5 V                                                                                              |            | 0.1  | 1    | μA   |

|                     | Device to device current error, I <sub>ERR_DD</sub> = (I <sub>AVE</sub> - I <sub>SET</sub> ) / I <sub>SET</sub> × 100%       | All channels ON. Current set to 0.1 mA.<br>MC = 0 CC = 42 DC = 25 PWM = 100%                                                                     | -7         |      | 7    | %    |

|                     |                                                                                                                              | All channels ON. Current set to 1 mA. MC = 2 CC = 127 DC = 25 PWM = 100%                                                                         | <b>–</b> 5 |      | 5    | %    |

| I <sub>ERR_DD</sub> |                                                                                                                              | All channels ON. Current set to 10 mA.  MC = 2 CC = 127 DC = 255 PWM =  100%                                                                     | -3.5       |      | 3.5  | %    |

|                     |                                                                                                                              | All channels ON. Current set to 25 mA. MC = 7 CC = 64 DC = 255 PWM = 100%                                                                        | -3.5       |      | 3.5  | %    |

|                     |                                                                                                                              | All channels ON. Current set to 50 mA.  MC = 7 CC = 127 DC = 255 PWM = 100%                                                                      | -3         |      | 3    | %    |

|                     |                                                                                                                              | All channels ON. Current set to 0.1 mA. MC = 0 CC = 42 DC = 25 PWM = 100%                                                                        | -5.5       |      | 5.5  | %    |

|                     |                                                                                                                              | All channels ON. Current set to 1 mA. MC = 2 CC = 127 DC = 25 PWM = 100%                                                                         | -5         |      | 5    | %    |

| I <sub>ERR_CC</sub> | Channel to channel current error,<br>I <sub>ERR_CC</sub> = (I <sub>OUTX</sub> - I <sub>AVE</sub> ) / I <sub>AVE</sub> × 100% | All channels ON. Current set to 10 mA.  MC = 2 CC = 127 DC = 255 PWM = 100%                                                                      | -4         |      | 4    | %    |

|                     |                                                                                                                              | All channels ON. Current set to 25 mA. MC = 7 CC = 64 DC = 255 PWM = 100%                                                                        | -3.5       |      | 3.5  | %    |

|                     |                                                                                                                              | All channels ON. Current set to 50 mA.  MC = 7 CC = 127 DC = 255 PWM = 100%                                                                      | -3         |      | 3    | %    |

| f                   | LED DWM fraguency                                                                                                            | PWM_Fre = 1, PWM = 100%                                                                                                                          |            | 62.5 |      | KHz  |

| f <sub>PWM</sub>    | LED PWM frequency                                                                                                            | PWM Fre = 0, PWM = 100%                                                                                                                          |            | 125  |      | KHz  |

## **6.5 Electrical Characteristics (continued)**

$V_{CC}$  = 3.3 V,  $V_{LED}$  = 3.8 V, VIO = 1.8 V and  $T_A$  = -40 °C to +85 °C; Typical values are at  $T_A$  = 25 °C (unless otherwise specified)

|                       | PARAMETER                                                               | TEST CONDITIONS                                                                          | MIN       | TYP                  | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------|----------------------|------|------|

|                       |                                                                         | I <sub>OUT</sub> = 50 mA, decreasing output voltage, when the LED current has dropped 5% |           |                      | 0.45 | V    |

| $V_{SAT}$             | Output saturation voltage                                               | I <sub>OUT</sub> = 30 mA, decreasing output voltage, when the LED current has dropped 5% |           |                      | 0.4  | V    |

|                       |                                                                         | I <sub>OUT</sub> = 10 mA, decreasing output voltage, when the LED current has dropped 5% |           |                      | 0.35 | V    |

|                       |                                                                         | V <sub>LED</sub> = 2.7 V, I <sub>SW</sub> = 200 mA                                       |           | 450                  |      | mΩ   |

| $R_{SW}$              | High-side PMOS ON resistance                                            | V <sub>LED</sub> = 3.8 V, I <sub>SW</sub> = 200 mA                                       |           | 380                  |      | mΩ   |

|                       |                                                                         | V <sub>LED</sub> = 5 V, I <sub>SW</sub> = 200 mA                                         |           | 310                  |      | mΩ   |

| Logic Inte            | erfaces                                                                 |                                                                                          |           |                      |      |      |

| V <sub>LOGIC_IL</sub> | Low-level input voltage, SDA, SCL,<br>SCLK, MOSI, SS, ADDRx, VSYNC, IFS |                                                                                          |           | 0.3 ×                | VIO  | V    |

| V <sub>LOGIC_IH</sub> | High-level input voltage, SDA, SCL, SCLK, MOSI, SS, ADDRx, VSYNC, IFS   |                                                                                          | 0.7 × VIO |                      |      | V    |

| V <sub>EN_IL</sub>    | Low-level input voltage of EN                                           |                                                                                          |           |                      | 0.4  | V    |

| V <sub>EN_IH</sub>    | High-level input voltage of EN                                          | When V <sub>CAP</sub> powered up                                                         | 1.4       |                      |      | V    |

| I <sub>LOGIC_I</sub>  | Input current, SDA, SCL, SCLK, MOSI, SS, ADDRx                          |                                                                                          | -1        |                      | 1    | μA   |

| V <sub>LOGIC_O</sub>  | Low-level output voltage, SDA, MISO                                     | I <sub>PULLUP</sub> = 3 mA                                                               |           |                      | 0.4  | V    |

| V <sub>LOGIC_O</sub>  | High-level output voltage, MISO                                         | I <sub>PULLUP</sub> = –3 mA                                                              | 0.7 × VIO |                      |      | V    |

| Protection            | n Circuits                                                              |                                                                                          |           |                      |      |      |

| V <sub>LOD_TH</sub>   | Thershold for channel open detection                                    |                                                                                          |           | 0.25                 |      | V    |

| V <sub>LSD_TH</sub>   | Thershold for channel short detection                                   |                                                                                          |           | V <sub>LED</sub> – 1 |      | V    |

| T <sub>TSD</sub>      | Thermal-shutdown junction temperature                                   |                                                                                          |           | 150                  |      | °C   |

| T <sub>HYS</sub>      | Thermal shutdown temperature hysteresis                                 |                                                                                          |           | 15                   |      | °C   |

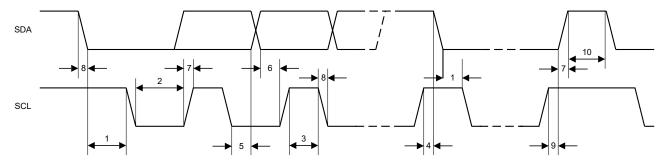

# **6.6 Timing Requirements**

|                      |                                                               | MIN  | NOM  | MAX | UNIT |

|----------------------|---------------------------------------------------------------|------|------|-----|------|

| MISC. Tim            | ming Requirements                                             |      |      |     |      |

| f <sub>OSC</sub>     | Internal oscillator frequency                                 |      | 31.2 |     | MHz  |

| f <sub>OSC_ERR</sub> | Device to device oscillator frequency error                   | -3%  |      | 3%  |      |

| t <sub>POR_H</sub>   | Wait time from UVLO disactive to device NORMAL                |      |      | 500 | μs   |

| t <sub>CHIP_EN</sub> | Wait time from setting Chip_EN (Register) =1 to device NORMAL |      |      | 100 | μs   |

| t <sub>RISE</sub>    | LED output rise time                                          |      | 10   |     | ns   |

| t <sub>FALL</sub>    | LED output fall time                                          |      | 15   |     | ns   |

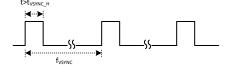

| t <sub>VSYNC_H</sub> | The minimum high-level pulse width of VSYNC                   | 200  |      |     | μs   |

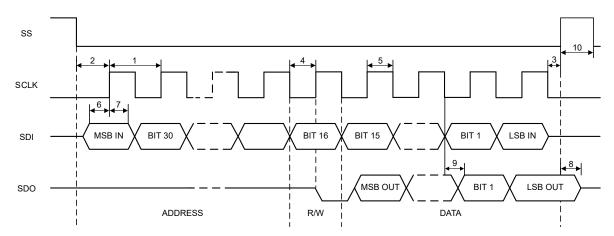

| SPI timing           | requirements                                                  |      |      |     |      |

| f <sub>SCLK</sub>    | SPI Clock frequency                                           |      |      | 12  | MHz  |

| 1                    | Cycle time                                                    | 83.3 |      |     | ns   |

| 2                    | SS active lead-time                                           | 50   |      |     | ns   |

| 3                    | SS active leg time                                            | 50   |      |     | ns   |

| 4                    | SCLK low time                                                 | 36   |      |     | ns   |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

# 6.6 Timing Requirements (continued)

|                                              |                                                    | MIN  | NOM MAX | UNIT |

|----------------------------------------------|----------------------------------------------------|------|---------|------|

| 5                                            | SCLK high time                                     | 36   |         | ns   |

| 3                                            | MOSI set-up time                                   | 20   |         | ns   |

| 7                                            | MOSI hold time                                     | 20   |         | ns   |

| 3                                            | MISO disable time                                  |      | 30      | ns   |

| 9                                            | MISO data valid time                               |      | 35      | ns   |

| 10                                           | SS inactive time                                   | 50   |         | ns   |

| C <sub>b</sub>                               | Bus capacitance                                    | 5    | 40      | pF   |

| l <sup>2</sup> C star                        | ndard mode timing requirements                     |      |         |      |

| f <sub>SCL</sub>                             | I <sup>2</sup> C clock frequency                   | 0    | 100     | KHz  |

| 1                                            | Hold time (repeated) START condition               | 4    |         | μs   |

| 2                                            | Clock low time                                     | 4.7  |         | μs   |

| 3                                            | Clock high time                                    | 4    |         | μs   |

| 4                                            | Setup time for a repeated START condition          | 4.7  |         | μs   |

| 5                                            | Data hold time                                     | 0    |         | μs   |

| <del></del>                                  | Data setup time                                    | 250  |         | ns   |

| 7                                            | Rise time of SDA and SCL                           |      | 1000    | ns   |

| 8                                            | Fall time of SDA and SCL                           |      | 300     | ns   |

| 9                                            | Setup time for STOP condition                      | 4    |         | μs   |

| 10                                           | Bus free time between a STOP and a START condition | 4.7  |         | μs   |

| l <sup>2</sup> C fast                        | mode timing requirements                           |      | I       |      |

| SCL                                          | I <sup>2</sup> C clock frequency                   | 0    | 400     | KHz  |

| 1                                            | Hold time (repeated) START condition               | 0.6  |         | μs   |

| 2                                            | Clock low time                                     | 1.3  |         | μs   |

| 3                                            | Clock high time                                    | 0.6  |         | us . |

| 4                                            | Setup time for a repeated START condition          | 0.6  |         | us . |

| 5                                            | Data hold time                                     | 0    |         | μs   |

| 3                                            | Data setup time                                    | 100  |         | ns   |

| 7                                            | Rise time of SDA and SCL                           |      | 300     | ns   |

| <br>B                                        | Fall time of SDA and SCL                           |      | 300     | ns   |

| 9                                            | Setup time for STOP condition                      | 0.6  |         | μs   |

| 10                                           | Bus free time between a STOP and a START condition | 1.3  |         | μs   |

|                                              | mode plus timing requirements                      |      |         | ,    |

| SCL                                          | I <sup>2</sup> C clock frequency                   | 0    | 1000    | KHz  |

| 1                                            | Hold time (repeated) START condition               | 0.26 |         | μs   |

| ·<br>2                                       | Clock low time                                     | 0.5  |         | μs   |

| <br>3                                        | Clock high time                                    | 0.26 |         | μs   |

| 1                                            | Setup time for a repeated START condition          | 0.26 |         | μs   |

| <u>.                                    </u> | Data hold time                                     | 0.20 |         | μs   |

| 3<br>3                                       | Data setup time                                    | 50   |         | ns   |

| 7                                            | Rise time of SDA and SCL                           | 30   | 120     | ns   |

| ,<br>3                                       | Fall time of SDA and SCL                           |      | 120     | ns   |

| 9<br>                                        | Setup time of STOP condition                       | 0.26 | 120     |      |

|                                              |                                                    |      |         | μs   |

| 10                                           | Bus free time between a STOP and a START condition | 0.5  |         | μs   |

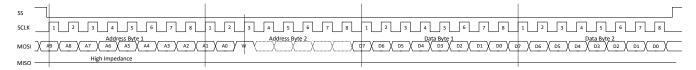

Figure 6-1. SPI Timing Parameters

Figure 6-2. I<sup>2</sup>C Timing Parameters

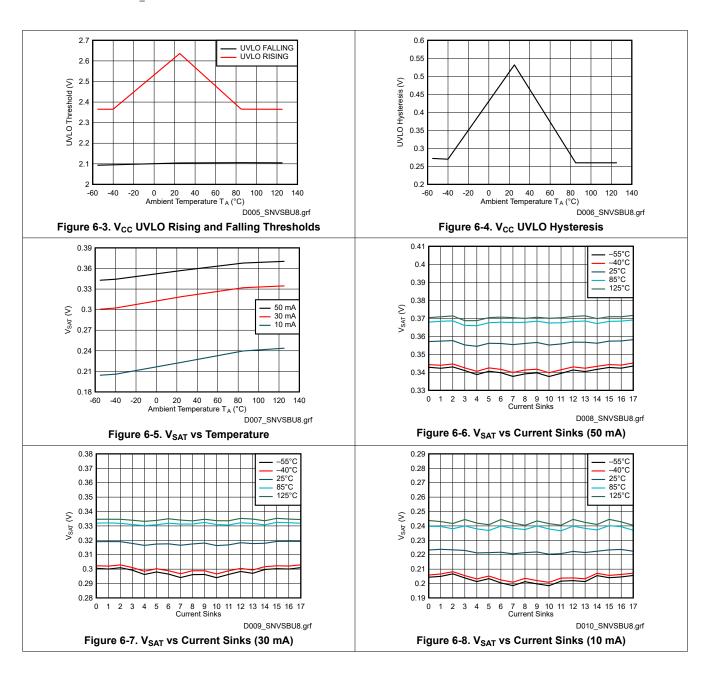

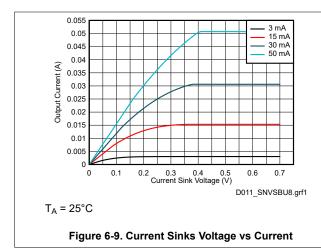

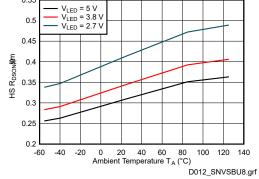

### 6.7 Typical Characteristics

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-55^{\circ}C < T_A < +125^{\circ}C$  for LP5860MRKPR, LP5864MRSMR, and LP5866MDBTR while  $-40^{\circ}C < T_A < +85^{\circ}C$  for the other devices),  $V_{CC} = 3.3$  V,  $V_{IO} = 3.3$  V,  $V_{LED} = 5$  V,  $I_{LED\ Peak} = 50$  mA,  $C_{VLED} = 1$   $\mu$ F,  $C_{VCC} = 1$   $\mu$ F.

## **6.7 Typical Characteristics (continued)**

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-55^{\circ}C < T_A < +125^{\circ}C$  for LP5860MRKPR, LP5864MRSMR, and LP5866MDBTR while  $-40^{\circ}C < T_A < +85^{\circ}C$  for the other devices),  $V_{CC}$  = 3.3 V,  $V_{IO}$  = 3.3 V,  $V_{LED}$  = 5 V,  $I_{LED\_Peak}$  = 50 mA,  $C_{VLED}$  = 1  $\mu$ F,  $C_{VCC}$  = 1  $\mu$ F.

0.55

Figure 6-10. High-Side Switch R<sub>DSON</sub>

## 7 Detailed Description

#### 7.1 Overview

The LP5862 is an 2 × 18 LED matrix driver. The device integrates 2 switching FETs with 18 constant current sinks. One LP5862 device can drive up to 36 LED dots or 12 RGB pixels by using time-multiplexing matrix scheme.

The LP5862 supports both analog dimming and PWM dimming methods. For analog dimming, the current gain of each individual LED dot can be adjusted with 256 steps through 8-bits dot correction. For PWM dimming, the integrated 8-bits or 16-bits configurable, > 20KHz PWM generators for each LED dot enable smooth, vivid animation effects without audible noise. Each LED can also be mapped into a 8-bits group PWM to achieve the group control with minimum data traffic.

The LP5862 device implements full addressable SRAM. The device supports entire SRAM data refresh and partial SRAM data update on demand to minimize the data traffic. The LP5862 implements the ghost cancellation circuit to eliminate both upside and downside ghosting. The LP5862 also uses low brightness compensation technology to support high density LED pixels. Both 1MHz (maximum) I<sup>2</sup>C and 12MHz (maximum) SPI interfaces are available in the LP5862.

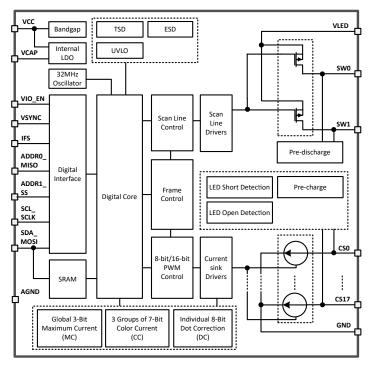

## 7.2 Functional Block Diagram

### 7.3 Feature Description

## 7.3.1 Time-Multiplexing Matrix

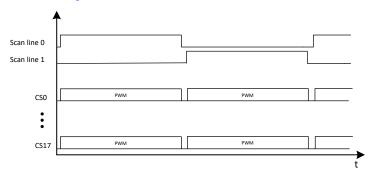

The LP5862 device uses time-multiplexing matrix scheme to support up to 36 LED dots with one chip. The device integrates 18 current sinks with 2 scan lines to drive  $18 \times 2 = 36$  LED dots or  $6 \times 2 = 12$  RGB pixels. In matrix control scheme, the device scans from Line 0 to Line 1 sequentially as shown in Figure 7-1. Current gain and PWM duty registers are programmable for each LED dot to support individual analog and PWM dimming.

Submit Document Feedback

Figure 7-1. Scan Line Control Scheme

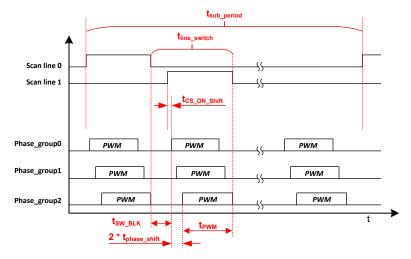

There are two high-side p-channel MOSFETs (PMOS) integrated in LP5862 device. Users can flexibly set the active scan numbers from 1 to 2 by configuring the 'Max\_Line\_Num' in Dev\_initial register. The time-multiplexing matrix timing sequence follows the Figure 7-2.

Figure 7-2. Time-Multiplexing Matrix Timing Sequence

One cycle time of the line switching can be calculated as below:

$$t_{line\ switch} = t_{PWM} + t_{SW\ BLK} + 2 \times t_{phase\ shift}$$

(1)

- t<sub>PWM</sub> is the current sink active time, which equals to 8μs (PWM frequency set at 125kHz) or 16μs (PWM frequency set at 62.5kHz) by configuring 'PWM\_Fre' in Dev\_initial register.

- t<sub>SW\_BLK</sub> is the switch blank time, which equals to 1 us or 0.5μs by configuring 'SW\_BLK' in Dev\_config1 register.

- t<sub>phase\_shift</sub> is the PWM phase shift time, which equals to 0 or 125ns by configuring 'PWM\_Phase\_Shift' in Dev\_config1 register.

Total display time for one complete sub-period is  $t_{sub-period}$  and it can be calculated by the following equation:

$$t_{sub\_period} = t_{line\_switch} \times Scan\_line\#$$

(2)

· Scan line# is the scan line number determined by 'Max Line Num' in Dev initial register.

The time-multiplexing matrix scheme time diagram is shown in Figure 7-3. The t<sub>CS\_ON\_Shift</sub> is the current sink turning on shift by configuring 'CS\_ON\_Shift' bit in Dev\_config1 register.

Figure 7-3. Time-Multiplexing Matrix Timing Diagram

The LP5862 device implements deghosting and low brightness compensation to remove the side effects of matrix topology:

- **Deghosting**: both upside deghosting and downside deghosting are implemented to eliminate the LED unexpected weak turn-on.

- Upside\_deghosting: discharge each scan line during its off state. By configuring the 'Up\_Deghost' in

Dev config3 register, the LP5862 discharges and clamps the scan line switch to a certain voltage.

- Downside\_deghosting: pre-charge each current sink voltage during its off state. The deghosting capability can be adjusted through the 'Down Deghost' in Dev config3 register.

- Low Brightness Compensation: three groups compensation are implemented to overcome the colorshift and non-uniformity in low brightness conditions. The compensation capability can be through 'Comp\_Group1', 'Comp\_Group2', and 'Comp\_Group3' in Dev\_config2 register.

- Compensation group 1: CS0, CS3, CS6, CS9, CS12, CS15

- Compensation group 2: CS1, CS4, CS7, CS10, CS13, CS16

- Compensation group 3: CS2, CS5, CS8, CS11, CS14, CS17

### 7.3.2 Analog Dimming (Current Gain Control)

Analog dimming of LP5862 is achieved by configuring the current gain control. There are several methods to control the current gain of each LED.

- Global 3-bits Maximum Current (MC) setting without external resistor

- 3 Groups of 7-bits Color Current (CC) setting

- Individual 8-bit Dot Current (DC) setting

#### Global 3-Bits Maximum Current (MC) Setting

The MC is used to set the maximum current, I<sub>OUT\_MAX</sub>, for each current sink, and this current is the maximum peak current for each LED dot. The MC can be set with 3 bits (8 steps) from 3mA to 50mA. When the device is powered on, the MC data is set to default value, which is 15mA.

For data refresh Mode 1, MC data is effective immediately after new data updated. For Mode 2 and Mode 3, to avoid unexpected MC data change during high speed data refreshing, MC data must be changed when all channels are off and new MC data is only be updated when the 'Chip\_EN' bit in Chip\_en register is set to 0, and after the 'Chip\_EN' returns to 1, the new MC data is effective. 'Down\_Deghost' and 'Up\_Deghost' in Dev\_config3 work in the similar way with MC.

Submit Document Feedback

Table 7-1. Maximum Current (MC) Register Setting

| 3-BITS MAXIMUM_C |             | I <sub>OUT_MAX</sub> |

|------------------|-------------|----------------------|

| Binary           | Decimal     | mA                   |

| 000              | 0           | 3                    |

| 001              | 1           | 5                    |

| 010              | 2           | 10                   |

| 011 (default)    | 3 (default) | 15 (default)         |

| 100              | 4           | 20                   |

| 101              | 5           | 30                   |

| 110              | 6           | 40                   |

| 111              | 7           | 50                   |

### 3 Groups of 7-Bits Color Current (CC) Setting

The LP5862 device can adjust the output current of three color groups separately. For each color, it has 7-bits data in 'CC\_Group1', 'CC\_Group2', and 'CC\_Group3'. Thus, all color group currents can be adjusted in 128 steps from 0% to 100% of the maximum output current, I<sub>OUT\_MAX</sub>.

The 18 current sinks have fixed mapping to the three color groups:

- CC-Group 1: CS0, CS3, CS6, CS9, CS12, CS15

- CC-Group 2: CS1, CS4, CS7, CS10, CS13, CS16

- CC-Group 3: CS2, CS5, CS8, CS11, CS14, CS17

Table 7-2. 3 Groups of 7-bits Color Current (CC) Setting

| 7-BITS CC_GROUP1/CC_GRO | UP2/CC_GROUP3 REGISTER | RATIO OF OUTPUT CURRENT TO I <sub>OUT_MAX</sub> |

|-------------------------|------------------------|-------------------------------------------------|

| Binary                  | Decimal                | %                                               |

| 000 0000                | 0                      | 0                                               |

| 000 0001                | 1                      | 0.79                                            |

| 000 0010                | 2                      | 1.57                                            |

|                         |                        |                                                 |

| 100 0000 (default)      | 64 (default)           | 50.4 (default)                                  |

|                         |                        |                                                 |

| 111 1101                | 125                    | 98.4                                            |

| 111 1110                | 126                    | 99.2                                            |

| 111 1111                | 127                    | 100                                             |

### Individual 8-bit Dot Current (DC) Setting

The LP5862 can individually adjust the output current of each LED by using dot current function through DC setting. The device allows the brightness deviations of the LEDs to adjusted be individually. Each output DC is programmed with a 8-bit depth, so the value can be adjusted with 256 steps within the range from 0% to 100% of ( $I_{OUT\ MAX} \times CC/127$ ).

Table 7-3. Individual 8-bit Dot Current (DC) Setting

| 8-BIT DC I          | REGISTER      | RATIO OF OUTPUT CURRENT TO I <sub>OUT_MAX</sub> × CC/127 |  |  |  |  |

|---------------------|---------------|----------------------------------------------------------|--|--|--|--|

| Binary              | Decimal       | %                                                        |  |  |  |  |

| 0000 0000           | 0             | 0                                                        |  |  |  |  |

| 0000 0001           | 1             | 0.39                                                     |  |  |  |  |

| 0000 0010           | 2             | 0.78                                                     |  |  |  |  |

|                     |               |                                                          |  |  |  |  |

| 1000 0000 (default) | 128 (default) | 50.2 (default)                                           |  |  |  |  |

Table 7-3. Individual 8-bit Dot Current (DC) Setting (continued)

| 8-BIT DC I | REGISTER | RATIO OF OUTPUT CURRENT TO I <sub>OUT_MAX</sub> × CC/127 |  |  |  |  |

|------------|----------|----------------------------------------------------------|--|--|--|--|

| Binary     | Decimal  | %                                                        |  |  |  |  |

|            |          |                                                          |  |  |  |  |

| 1111 1101  | 253      | 99.2                                                     |  |  |  |  |

| 1111 1110  | 254      | 99.6                                                     |  |  |  |  |

| 1111 1111  | 255      | 100                                                      |  |  |  |  |

In summary, the current gain of each current sink can be calculated as below:

$$I_{OUT}$$

(mA) =  $I_{OUT\ MAX} \times (CC/127) \times (DC/255)$  (3)

For time-multiplexing scan scheme, if the scan number is N, each LED dot average current I<sub>AVG</sub> is shown as below:

$$I_{AVG}$$

(mA) =  $I_{OUT}$  / N =  $I_{OUT\ MAX}$  × (CC/127) × (DC/255)/N (4)

### 7.3.3 PWM Dimming

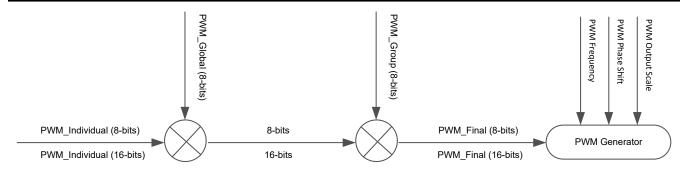

There are several methods to control the PWM duty cycle of each LED dot.

#### Individual 8-bit / 16-bit PWM for Each LED Dot

Every LED has an individual 8-bit or 16-bit PWM register that is used to change the LED brightness by PWM duty. The LP5862 uses an enhanced spectrum PWM (ES-PWM) algorithm to achieve 16-bit depth with high refresh rate and this can avoid flicker under high speed camera. Comparing with conventional 8-bit PWM, 16-bit PWM can help to achieve ultimate high dimming resolution in LED animation applications.

#### 3 Programmable Groups of 8-bit PWM Dimming

The group PWM Control is used to select LEDs into 1 to 3 groups where each group has a separate register for duty cycle control. Every LED has 2-bit selection in LED\_DOT\_GROUP Registers (x = 0, 1, ..., 9) to select whether it belongs to one of the three groups or not:

- 00: not a member of any group

- 01: member of group 1

- 10: member of group 2

- 11: member of group 3

#### 8-bit PWM for Global Dimming

The Global PWM Control function affects all LEDs simultaneously.

The final PWM duty cycle can be calculated as below:

$$PWM\_Final(16 bit) = PWM\_Individual(16 bit) \times PWM\_Group(8 bit) \times PWM\_Global(8 bit)$$

(6)

The LP5862 supports 125kHz or 62.5kHz PWM output frequency. The PWM frequency is selected by configuring the 'PWM\_Fre' in Dev\_initial register. An internal 32MHz oscillator is used for generating PWM outputs. The oscillator's high accuracy design ( $f_{OSC\_ERR} \le \pm 2\%$ ) enables a better synchronization if multiple LP5862 devices are connected together.

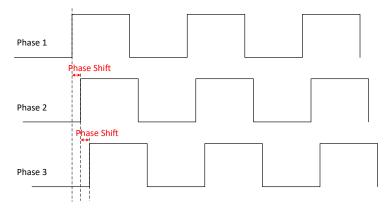

A PWM phase-shifting scheme is implemented in each current sink to avoid the current overshot when turning on simultaneously. As the LED drivers are not activated simultaneously, the peak load current from the pre-stage power supply is significantly decreased. This scheme also reduces input-current ripple and ceramic-capacitor audible ringing. LED drivers are grouped into three different phases. By configuring the 'PWM\_Phase\_Shift' in

Submit Document Feedback

Dev\_config1 register, which is default off, the LP5862 supports  $t_{phase\_shift}$  = 125ns shifting time shown in Figure 7-4.

- Phase 1: CS0, CS3, CS6, CS9, CS12, CS15

- Phase 2: CS1, CS4, CS7, CS10, CS13, CS16

- Phase 3: CS2, CS5, CS8, CS11, CS14, CS17

Figure 7-4. Phase Shift

To avoid high current sinks output ripple during line switching, current sinks can be configured to turn on with 1 clock delay (62.5ns or 31.25ns according to the PWM frequency) after lines turn on, as shown in Figure 7-3. This function an be configured by 'CS\_ON\_Shift' in Dev\_config1 register.

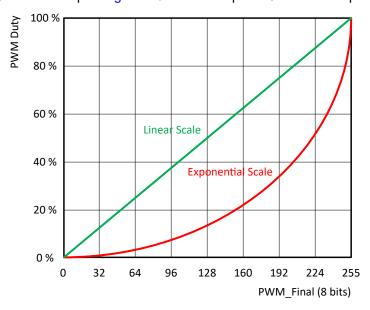

The LP5862 allows users to configure the dimming scale either exponentially (Gamma Correction) or linearly through the 'PWM\_Scale\_Mode' in Dev\_config1 register. If a human-eye-friendly dimming curve is desired, using the internal fixed exponential scale is an easy approach. If a special dimming curve is desired, using the linear scale with software correction is recommended. The LP5862 supports both linear and exponential dimming curves under 8-bit and 16-bit PWM depth. Figure 7-5 is an example of 8-bit PWM depth.

Figure 7-5. Linear and Exponential Dimming Curves

In summary, the PWM control method is illustrated as Figure 7-6:

Figure 7-6. PWM Control Scheme

#### 7.3.4 ON and OFF Control

The LP5862 device supports the individual ON and OFF control of each LED. For indication purpose, users can turn on and off the LED directly by writing 1-bit ON and OFF data to the corresponding Dot\_onoffx (x = 0, 1, ..., 5) register.

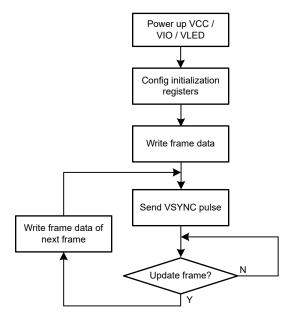

#### 7.3.5 Data Refresh Mode

The LP5862 supports three data refresh modes: Mode 1, Mode 2, and Mode 3, by configuring 'Data\_Ref\_Mode' in Dev initial register.

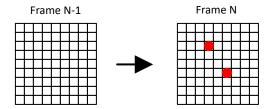

**Mode 1**: 8-bit PWM data without VSYNC command. Data is sent out for display instantly after received. With Mode 1, users can refresh the corresponding dots' data only instead of updating the whole SRAM. It is called 'on demand data refresh', which can save the total data volume effectively. As shown in Figure 7-7, the red LED dots can be refreshed after sending the corresponding data while the others kept the same with last frame.

Figure 7-7. On Demand Data Refresh - Mode 1

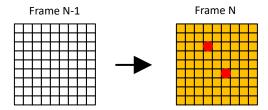

**Mode 2**: 8-bit PWM data with VSYNC command. Data is held and sent out simultaneously by frame after receiving the VSYNC command.

**Mode 3**: 16-bit PWM data with VSYNC command. Data is held and sent out simultaneously by frame after receiving the VSYNC command.

Frame control is implemented in Mode 2 and Mode 3. Instead of refreshing the output instantly after data is received (Mode 1), the device holds the data and refreshes the whole frame data by a fixed frame rate,  $f_{VSYNC}$ . Usually, 24Hz, 50Hz, 60Hz, 120Hz or even higher frame rate is selected to achieve vivid animation effects. Whole SRAM Data Refresh is shown in Figure 7-8, a new frame is updated after receiving the VSYNC command.

Figure 7-8. Whole SRAM Data Refresh

Submit Document Feedback

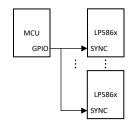

Comparing with Mode 1, Mode 2 and Mode 3 provide a better synchronization when multiple LP5862 devices used together. A high-level pulse width longer than  $t_{SYNC\_H}$  is required at the beginning of each VSYNC frame. Figure 7-9 shows the VSYNC connections and Figure 7-10 shows the timing requirements.

Figure 7-9. Multiple Devices Sync

Figure 7-10. VSYNC Timing

Table 8-4 is the summary of the three data refresh modes.

#### Table 7-4. Data Refresh Mode

| MODE TYPE | PWM RESOLUTION | PWM OUTPUT            | EXTERNAL VSYNC |

|-----------|----------------|-----------------------|----------------|

| Mode 1    | 8 bits         | Data update instantly | No             |

| Mode 2    | 8 bits         | Data update by frame  | Yes            |

| Mode 3    | 16 bits        | Data update by frame  | 165            |

#### 7.3.6 Full Addressable SRAM

SRAM is implemented inside the LP5862 device to support data writing and reading at the same time.

Although data refresh mechanisms are not the same for Mode 1 and Mode 2 and 3, the data writing and reading follow the same method. Uses can update partial of the SRAM data only or the whole SRAM page simultaneously. The LP5862 supports auto-increment function to minimize data traffic and increase data transfer efficiency.

Please be noted that 16-bit PWM (Mode 3) and 8-bit PWM (Mode 1 and Mode 2) are assigned with different SRAM addresses.

#### 7.3.7 Protections and Diagnostics

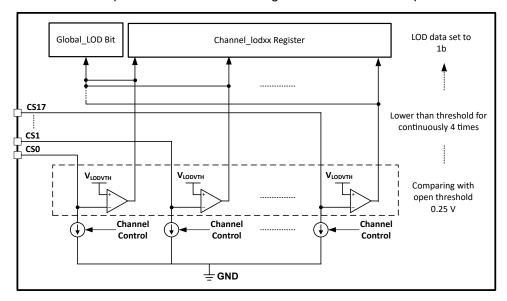

### **LED Open Detection**

The LP5862 includes LED open detection (LOD) for the fault caused by any opened LED dot. The threshold for LED open is 0.25V typical. LED open detection is only performed when PWM  $\geq$  25 (Mode 1 and Mode 2) or PWM  $\geq$  6400 (Mode 3) and voltage on CSn is detected lower than open threshold for continuously 4 sub-periods.

Figure 7-11 shows the detection circuit of LOD function. When open fault is detected, 'Global\_LOD' bit in Fault\_state register is set to 1 and detailed fault state for each LED is also monitored in register Dot\_lodx (x = 0, 1, ..., 5). All open fault indicator bits can be cleared by setting LOD\_clear = 0Fh after the open condition is removed.

LOD removal function can be enabled by setting 'LOD\_removal' bit in Dev\_config2 register to 1. This function turns off the current sink of the open channel when scanning to the line where the opened LED is included.

Figure 7-11. LOD Circuits

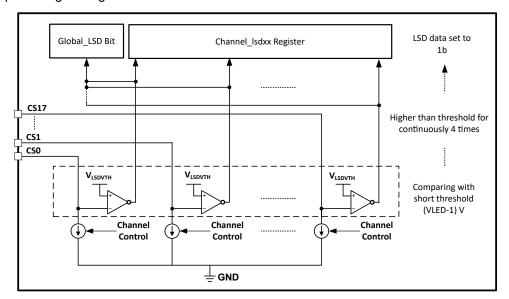

#### **LED Short Detection**

The LP5862 includes LED short detection (LSD) for the fault caused by any shorted LED. Threshold for channel short is (VLED - 1) V typical. LED short detection only performed when PWM  $\geq$  25 (Mode 1 and Mode 2)

Product Folder Links: LP5862

or PWM  $\geq$  6400 (Mode 3) and voltage on CSn is detected higher than short threshold for continuously 4 sub-periods. As there is parasitic capacitance for the current sink, to make sure the LSD result is correct, TI recommends to set the LED current higher than 0.5mA.

Figure 7-12 shows the detection circuit of LSD function. When short fault is detected, 'Global\_LSD bit' in Fault\_state register is set to 1 and detailed fault state for every channel is also monitored in register Dot\_lsdx (x = 0, 1, ..., 5). All short fault indicator bits can be cleared by setting LSD\_clear = 0Fh after the short condition is removed.

LSD removal function can be enabled by setting 'LSD\_removal' bit in Dev\_config2 register to 1. This function turns off the upside deghosting function of the scan line where short LED is included.

Figure 7-12. LSD Circuit

#### Thermal Shutdown

The LP5862 device implements thermal shutdown mechanism to protect the device from damage due to overheating. When the junction temperature rises to 160°C (typical) and above, the device switches into shutdown mode. The LP5862 exits thermal shutdown when the junction temperature of the device drops to 145°C (typical) and below.

### **UVLO (Undervoltage Lock Out)**

The LP5862 has an internal comparator that monitors the voltage at VCC. When VCC is below V<sub>UVF</sub>, reset is active and the LP5862 enters INITIALIZATION state.

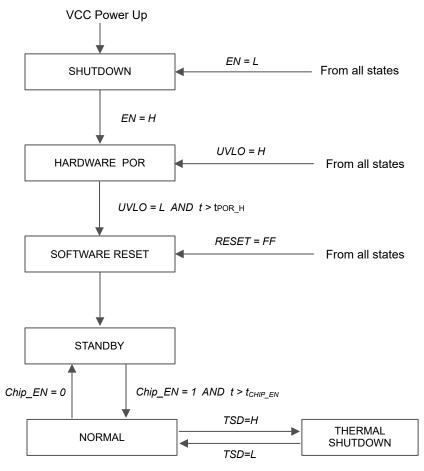

#### 7.4 Device Functional Modes

Figure 7-13. Device Functional Modes

- Shutdown: The device enters into shutdown mode from all states on VCC power up or EN pin is low.

- Hardware POR: The device enters into hardware POR when Enable pin is high or VCC fall under V<sub>UVF</sub> causing UVLO = H from all states.

- Software reset: The device enters into software reset mode when VCC rise higher than V<sub>UVR</sub> with the time t > t<sub>POR\_H</sub>. In this mode, all the registers are reset. Entry can also be from any state when the RESET (register) = FFh or UVLO is low.

- Standby: The device enters the standby mode when Chip\_EN (register) = 0. In this mode, the device enters into low power mode, but the I<sup>2</sup>C/SPI are still available for Chip\_EN only and the register data is retained.

- Normal: The device enters the normal mode when 'Chip\_EN' = 1 with the time t > t<sub>CHIP\_EN</sub>.

- Thermal shutdown: The device automatically enters the thermal shutdown mode when the junction temperature exceeds 160°C (typical). If the junction temperature decreases below 145°C (typical), the device returns to the normal mode.

Submit Document Feedback

### 7.5 Programming

#### Interface Selection

The LP5862 supports two communication interfaces:  $I^2C$  and SPI. If IFS is high, the device enters into SPI mode. If IFS is low, the device enters into  $I^2C$  mode.

Table 7-5. Interface Selection

| INTERFACE TYPE   | ENTRY CONDITION |  |  |  |

|------------------|-----------------|--|--|--|

| I <sup>2</sup> C | IFS = Low       |  |  |  |

| SPI              | IFS = High      |  |  |  |

#### I<sup>2</sup>C Interface

The LP5862 is compatible with I<sup>2</sup>C standard specification. The device supports both fast mode (400-KHz maximum) and fast plus mode (1-MHz maximum).

#### I<sup>2</sup>C Data Transactions

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when clock signal is LOW. START and STOP conditions classify the beginning and the end of the data transfer session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The bus leader always generates START and STOP conditions. The bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the bus leader can generate repeated START conditions. First START and repeated START conditions are functionally equivalent.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the leader. The leader releases the SDA line (HIGH) during the acknowledge clock pulse. The device pulls down the SDA line during the 9<sup>th</sup> clock pulse, signifying an acknowledge. The device generates an acknowledge after each byte has been received.

There is one exception to the acknowledge after every byte rule. When the leader is the receiver, it must indicate to the transmitter an end of data by not acknowledging (negative acknowledge) the last byte clocked out of the follower. This negative acknowledge still includes the acknowledge clock pulse (generated by the leader), but the SDA line is not pulled down.

#### I<sup>2</sup>C Data Format

The address and data bits are transmitted MSB first with 8-bits length format in each cycle. Each transmission is started with Address Byte 1, which are divided into 5-bits of the chip address, 2 higher bits of the register address, and 1 read and write bit. The other 8 lower bits of register address are put in Address Byte 2. The device supports both independent mode and broadcast mode. The auto-increment feature allows writing and reading several consecutive registers within one transmission. If not consecutive, a new transmission must be started.

Table 7-6. I<sup>2</sup>C Data Format

| Address Byte 1 |                     |                     | Chip Address        | Register            | R/W                 |                     |                     |                     |  |  |  |  |

|----------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|--|--|

|                | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               |  |  |  |  |

| Independent    | 1                   | 0                   | 0                   | ADDR1               | ADDR0               | 9 <sup>th</sup> bit | 8 <sup>th</sup> bit | R: 1 W: 0           |  |  |  |  |

| Broadcast      | 1                   | 0                   | 1                   | 0                   | 1                   | 9 DIL               | O DIL               | K. I W. U           |  |  |  |  |

|                |                     | Register Address    |                     |                     |                     |                     |                     |                     |  |  |  |  |

| Address Byte 2 | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               |  |  |  |  |

|                | 7 <sup>th</sup> bit | 6 <sup>th</sup> bit | 5 <sup>th</sup> bit | 4 <sup>th</sup> bit | 3 <sup>th</sup> bit | 2 <sup>th</sup> bit | 1 <sup>th</sup> bit | 0 <sup>th</sup> bit |  |  |  |  |

Copyright © 2025 Texas Instruments Incorporated

Submit Document Feedback

Figure 7-14. I<sup>2</sup>C Write Timming

Figure 7-15. I<sup>2</sup>C Read Timing

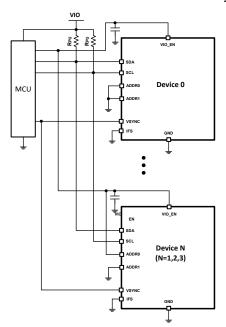

#### **Multiple Devices Connection**

The LP5862 enters into I<sup>2</sup>C mode if IFS is connected to GND. The ADDR0/1 pin is used to select the unique I<sup>2</sup>C follower address for each device. The SCL and SDA lines must each have a pullup resistor (4.7 K $\Omega$  for 400 KHz, 2 K $\Omega$  for 1 MHz) placed somewhere on the line and remain HIGH even when the bus is idle. VIO\_EN can either be connected with VIO power supply or GPIO. TI suggests to put one 1-nF cap as closer to VIO\_EN pin as possible. Up to four LP5862 follower devices can share the same I<sup>2</sup>C bus by the different ADDR configurations.

Figure 7-16. I<sup>2</sup>C Multiple Devices Connection

#### **SPI Interface**

The LP5862 is compatible with SPI serial-bus specification, and it operates as a follower. The maximum frequency supported by LP5862 is 12 MHz.

#### SPI Data Transactions

MISO output is normally in a high impedance state. When the follower-select pin SS for the device is active (low) the MISO output is pulled low for read only. During write cycle MISO stays in high-impedance state. The follower-select signal SS must be low during the cycle transmission. SS resets the interface when high. Data is clocked in on the rising edge of the SCLK clock signal, while data is clocked out on the falling edge of SCLK.

#### SPI Data Format

Submit Document Feedback

The address and data bits are transmitted MSB first with 8-bits length format in each cycle. Each transmission is started with Address Byte 1, which contains 8 higher bits of the register address. The Address Byte 2 is started with 2 lower bits of the register address and 1 read and write bit. The auto-increment feature allows writing and reading several consecutive registers within one transmission. If not consecutive, a new transmission must be started.

**Table 7-7. SPI Data Format**

| Address<br>Byte 1 | Register Address    |                     |                     |                     |                     |                     |                     |                     |  |  |

|-------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|--|--|

|                   | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               |  |  |

|                   | 9 <sup>th</sup> bit | 8 <sup>th</sup> bit | 7 <sup>th</sup> bit | 6 <sup>th</sup> bit | 5 <sup>th</sup> bit | 4 <sup>th</sup> bit | 3 <sup>th</sup> bit | 2 <sup>th</sup> bit |  |  |

| Address<br>Byte 2 | Register            | Register Address    |                     |                     |                     |                     |                     |                     |  |  |

|                   | Bit 7               | Bit 6               | Bit 5               | Bit 4               | Bit 3               | Bit 2               | Bit 1               | Bit 0               |  |  |

|                   | 1 <sup>th</sup> bit | 0 <sup>th</sup> bit | R: 0 W: 1           | Do not care         |                     |                     |                     |                     |  |  |

Figure 7-17. SPI Write Timing

Figure 7-18. SPI Read Timing

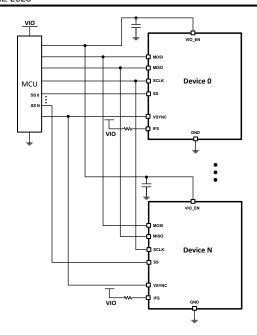

### **Multiple Devices Connection**

The device enters into SPI mode if IFS is pulled high to VIO through a pullup resistor (4.7 K $\Omega$  recommended). VIO\_EN can either be connected with VIO power supply or GPIO. TI suggests to put one 1-nF cap as closer to VIO\_EN pin as possible. In SPI mode host can address as many devices as there are follower select pins on host.

Figure 7-19. SPI Multiple Devices Connection

# 7.6 Register Maps

This section provides a summary of the register maps. For detailed register functions and descriptions, please refer to *LP5860 11x18 LED Matrix Driver Register Maps*.

Table 7-8. Register Section/Block Access Type Codes

| Access Type            | Code | Description                            |

|------------------------|------|----------------------------------------|

| Read Type              |      |                                        |

| R                      | R    | Read                                   |

| RC                     | R    | Read                                   |

|                        | С    | to Clear                               |

| R-0                    | R    | Read                                   |

|                        | -0   | Returns 0s                             |

| Write Type             |      |                                        |

| W                      | W    | Write                                  |

| W0CP                   | W    | W                                      |

|                        | 0C   | 0 to clear                             |

|                        | P    | Requires privileged access             |

| Reset or Default Value |      |                                        |

| -n                     |      | Value after reset or the default value |

| Register<br>Acronym | Address | Туре | D7       | D6                        | D5       | D4                   | D3            | D2                 | D1                  | D0                        | Default |

|---------------------|---------|------|----------|---------------------------|----------|----------------------|---------------|--------------------|---------------------|---------------------------|---------|

| Chip_en             | 000h    | R/W  | Reserved |                           |          | •                    |               |                    | •                   | Chip_EN                   | 00h     |