# LP5815 3-Channel I<sup>2</sup>C Interface RGB LED Driver with Instant Blinking and Auto Animation Control

# 1 Features

- Operating voltage range

- V<sub>CC</sub> range: 2.5V to 5.5V

- Logic pins compatible with 1.8V, 3.3V, and 5V

- Output voltage up to 5.5V

- 3-constant current sinks with high precision

- 0.1mA to 51mA per channel

- Device-to-device error: ±8% (max.)

- Channel-to-channel error: ±3% (max.)

- Ultra-low headroom voltage: 135mV (max.) at 25.5mA; 275mV (max.) at 51mA

- Ultra-low power consumption

- Shutdown:  $I_{SD} = 0.1 \mu A$  (typ.)

- Standby:  $I_{STB} = 22\mu A$  (typ.)

- Active:

- I<sub>NOR</sub> = 0.15mA(typ.), disable output channel

- I<sub>NOR</sub> = 0.23mA(typ.), LED current = 25.5mA

- Analog dimming (current gain control)

- Global 1-bit Maximum Current (MC) 25.5mA/ 51mA

- Individual 8-bits Dot Current (DC) setting

- PWM dimming up to audible-noise-free 23kHz

- Individual 8-bits PWM dimming resolution

- Linear or exponential dimming curves

- Autonomous animation engine control

- Instant blinking via STAT pin control

- 1MHz (max.) I<sup>2</sup>C interface ٠

- ESD: 4kV HBM, 1.5kV CDM •

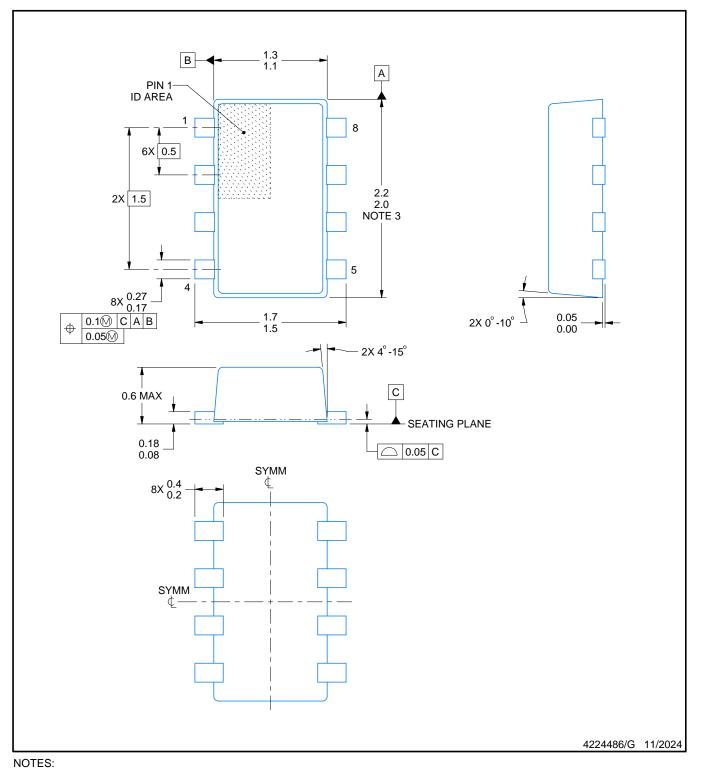

- Package

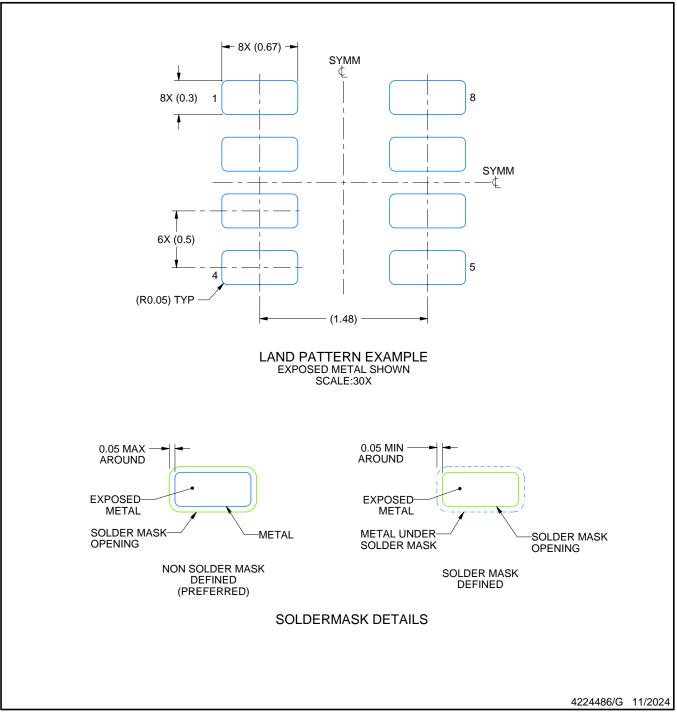

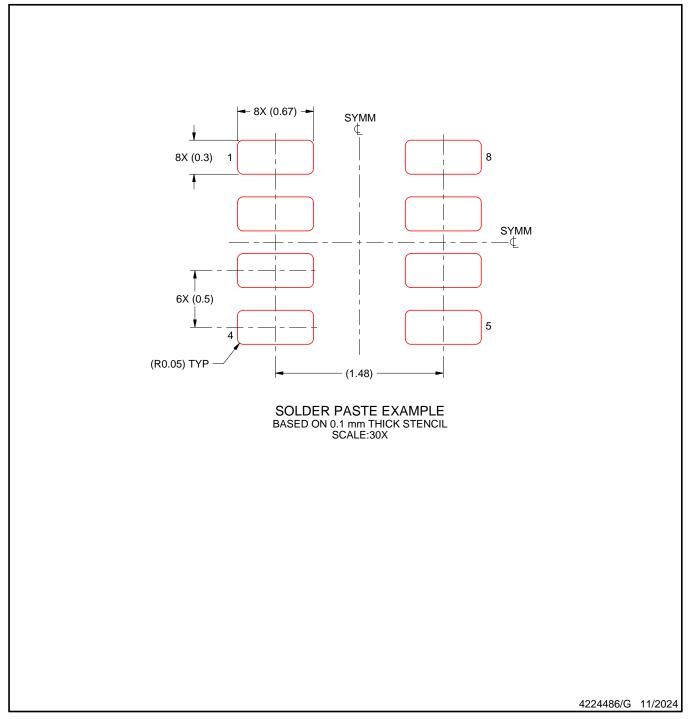

- 1.6x2.1mm SOT583-8 with 0.5mm pitch

- 1.36x0.8mm DSBGA-8 with 0.35mm pitch

- -40°C to 125°C operating temperature range

# 2 Applications

LED animation and indication for:

- **Personal Electronics**

- Virtual Reality (VR) Headset

- Gaming Controller and Peripherals

- Electronic and Robotic Toys

- Smart Speaker

- Wireless Speaker

- Solid State Drive (SSD)

- Electronic Smart Lock

- Headsets/Headphones and Earbuds

- GPS Personal Navigation Device

- WLAN/Wi-Fi Access Point

- Video Doorbell

- Video Conference System

# **3 Description**

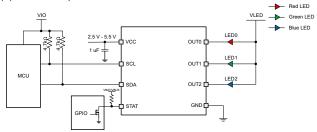

The LP5815 is a 3-channel RGB LED driver with autonomous animation engine control and controllable Instant Blinking feature. The device has ultra-low operation current with 0.1µA (typical) in shutdown mode, 0.1mA (typical) when enable device and 0.2mA (typical) when illuminate LEDs.

Both analog dimming and PWM dimming methods are adopted to achieve powerful dimming performance. The output current of each LED can be adjusted with 256 steps from 0.1mA to 25.5mA or 0.2mA to 51mA. The 8-bits PWM generator enables smooth and audible-noise-free dimming control for LED brightness.

The autonomous animation engine can significantly reduce the real-time loading of controller. Each LED can be configured through the related registers to realize vivid and fancy lighting effects.

The Instant Blinking via STAT pin control feature can provide automatic blinking on OUT0 channel without I<sup>2</sup>C communication after powering up.

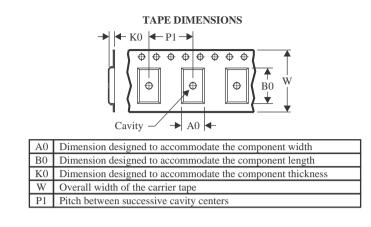

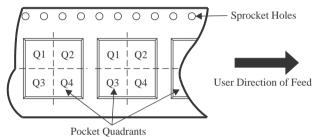

**Package Information**

| PART NUMBER | PACKAGE                  | PACKAGE SIZE (NOM) |

|-------------|--------------------------|--------------------|

| LP5815DRL   | SOT583 (8)               | 1.6mm × 2.1mm      |

| LP5815YCH   | DSBGA (8) <sup>(1)</sup> | 1.36mm × 0.8mm     |

Product preview.. (1)

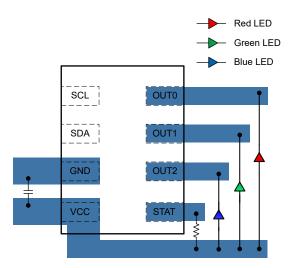

LP5815 Simplified Schematic

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features                           | 1              |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        | 1              |

| 4 Device Comparison                  | 3              |

| 5 Pin Configuration and Functions    | 4              |

| 6 Specifications                     |                |

| 6.1 Absolute Maximum Ratings         | 5              |

| 6.2 ESD Ratings                      |                |

| 6.3 Recommended Operating Conditions | 5              |

| 6.4 Thermal Information              | 5              |

| 6.5 Electrical Characteristics       | 6              |

| 6.6 Timing Requirements              | 7              |

| 6.7 Timing Diagrams                  | <mark>8</mark> |

| 6.8 Typical Characteristics          | <mark>8</mark> |

| 7 Detailed Description               | 12             |

| 7.1 Overview                         | 12             |

| 7.2 Functional Block Diagram         | 12             |

| 7.3 Feature Description              | 13             |

| 7.4 Device Functional Modes                          | 21              |

|------------------------------------------------------|-----------------|

| 7.5 Programming                                      | 24              |

| 7.6 Register Maps                                    |                 |

| 8 Application and Implementation                     |                 |

| 8.1 Application Information                          |                 |

| 8.2 Typical Application                              |                 |

| 8.3 Power Supply Recommendations                     | 67              |

| 8.4 Layout                                           | 67              |

| 9 Device and Documentation Support                   | 68              |

| 9.1 Documentation Support                            | <mark>68</mark> |

| 9.2 Receiving Notification of Documentation Updates. | 68              |

| 9.3 Support Resources                                | <mark>68</mark> |

| 9.4 Trademarks                                       | 68              |

| 9.5 Electrostatic Discharge Caution                  | 68              |

| 9.6 Glossary                                         | 68              |

| 10 Revision History                                  | <mark>68</mark> |

| 11 Mechanical, Packaging, and Orderable              |                 |

| Information                                          | 69              |

|                                                      |                 |

# **4 Device Comparison**

| PART<br>NUMBER | PACKAGE (1) | MATERIAL   | LED<br>NUMBER | AUTO<br>ANIMATIO | INSTANT<br>BLINKING | I <sup>2</sup> C<br>ADDRESS | SOFTWARE<br>COMPATIBLE |

|----------------|-------------|------------|---------------|------------------|---------------------|-----------------------------|------------------------|

| LP5814         | SOT583-8    | LP5814DRLR | 4             |                  | No                  | 0x2C                        |                        |

| LF 3014        | DSBGA-8     | LP5814YCHR | 4             | Yes              | NO                  | 0,20                        |                        |

| LP5815         | SOT583-8    | LP5815DRLR | 3             | Tes              | Voo                 | 0x2D                        |                        |

| LF3013         | DSBGA-8     | LP5815YCHR |               |                  | Yes                 | UX2D                        | Yes                    |

| LP5816         | SOT583-8    | LP5816DRLR | No No         |                  | 0x2C                | 0.200                       | Tes                    |

| LF3010         | DSBGA-8     | LP5816YCHR |               | 4                |                     |                             |                        |

| LP5817         | SOT583-8    | LP5817DRLR |               | INO              | No                  | 0x2D                        |                        |

|                | DSBGA-8     | LP5817YCHR | 3             |                  |                     | 0,20                        |                        |

Product Folder Links: LP5815

(1) For the most up-to-date packaging information refer to the Mechanical, Packaging, and Orderable Information.

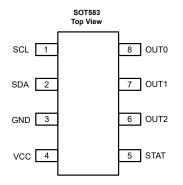

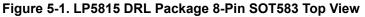

# **5** Pin Configuration and Functions

#### Table 5-1. Pin Functions

|      | PIN |     |     | DESCRIPTION                                                                                                                                                  |

|------|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | DRL | YCH |     | DESCRIPTION                                                                                                                                                  |

| SCL  | 1   | A1  | I   | I <sup>2</sup> C serial interface clock input.                                                                                                               |

| SDA  | 2   | B1  | I/O | I <sup>2</sup> C serial interface data input/output.                                                                                                         |

| GND  | 3   | C1  | Р   | Ground.                                                                                                                                                      |

| VCC  | 4   | D1  | Р   | Power supply of the device. A 1 $\mu F$ capacitor is recommended to be connected between this pin with GND and be placed as close to the device as possible. |

| STAT | 5   | D2  | I   | Instant blinking control input.                                                                                                                              |

| OUT2 | 6   | C2  | 0   | Constant current sink output 2.                                                                                                                              |

| OUT1 | 7   | B2  | 0   | Constant current sink output 1.                                                                                                                              |

| OUT0 | 8   | A2  | 0   | Constant current sink output 0.                                                                                                                              |

# **6** Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                            |                                       | MIN  | MAX | UNIT |

|----------------------------|---------------------------------------|------|-----|------|

| Voltage range at terminals | VCC, SCL, SDA, STAT, OUT0, OUT1, OUT2 | -0.3 | 6   | V    |

| TJ                         | Junction temperature                  | -40  | 150 | °C   |

| T <sub>stg</sub>           | Storage temperature                   | -65  | 150 | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|                    |                         |                                                                                     | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>     | ±4000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per ANSI/ESDA/<br>JEDEC JS-002, all pins <sup>(2)</sup> | ±1500 | V    |

(1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                   | MIN | NOM | MAX | UNIT |

|------------------|-----------------------------------|-----|-----|-----|------|

| V <sub>CC</sub>  | Input voltage range               | 2.5 |     | 5.5 | V    |

| C <sub>IN</sub>  | Effective input capacitance range | 1   | 4.7 |     | μF   |

| OUT0, OUT1, OUT2 | Voltage on OUT0, OUT1, OUT2 pins  | 0   |     | 5.5 | V    |

| SCL, SDA, STAT   | Voltage on SCL, SDA, STAT pins    | 0   |     | 5.5 | V    |

| T <sub>A</sub>   | Ambient temperature               | -40 |     | 85  | °C   |

| TJ               | Operating junction temperature    | -40 |     | 125 | °C   |

### 6.4 Thermal Information

|                       |                                              | LP5815       |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DRL (SOT583) | UNIT |

|                       |                                              | 8 PINS       |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 118.9        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 47.1         | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 27.5         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.4          | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 27.2         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# **6.5 Electrical Characteristics**

Unless specified otherwise, typical characteristics apply over the full ambient temperature range (–40°C <  $T_A$  < +85°C ),  $V_{CC}$  = 3.6V,  $C_{IN}$  = 1µF.

|                       | PARAMETER                                                                            | TEST CONDITIONS                                                                                                                     | MIN | TYP  | MAX   | UNIT |

|-----------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|------|

| Power Sup             | oply                                                                                 |                                                                                                                                     |     |      |       |      |

| V <sub>CC</sub>       | Input voltage range                                                                  |                                                                                                                                     | 2.5 |      | 5.5   | V    |

|                       |                                                                                      | V <sub>CC</sub> rising                                                                                                              | 2.2 | 2.3  | 2.4   | V    |

| V <sub>CC_UVLO</sub>  | Under-voltage lockout threshold                                                      | V <sub>CC</sub> falling                                                                                                             | 2   | 2.1  | 2.2   | V    |

| I <sub>SD</sub>       | Shutdown current into VCC pin                                                        | V <sub>CC</sub> = 3.6V                                                                                                              |     | 0.1  | 0.3   | μA   |

| I <sub>STB</sub>      | Standby current into VCC pin                                                         | V <sub>CC</sub> = 3.6V, CHIP_EN = 0 (bit)                                                                                           |     | 22   | 26    | μA   |

| I <sub>NOR</sub>      | Normal operation current into VCC pin                                                | V <sub>CC</sub> = 3.6V, CHIP_EN = 1 (bit), OUT0_EN =<br>OUT1_EN = OUT2_EN = 0 (bit)                                                 |     | 0.15 | 0.17  | mA   |

| I <sub>NOR</sub>      | Normal operation current into VCC pin                                                |                                                                                                                                     |     | 0.23 | 0.29  | mA   |

| LED Drive             | r Output                                                                             |                                                                                                                                     |     |      |       |      |

| 1                     | Constant ourrant sink output range                                                   | V <sub>CC</sub> = 3.6V, VLED = 5V, MAX_CURRENT = 0 (bit),<br>OUTx_MANUAL_PWM = FFh (100% ON)                                        | 0.1 |      | 25.5  | mA   |

| l <sub>cs</sub>       | Constant current sink output range                                                   | V <sub>CC</sub> = 3.6V, VLED = 5V, MAX_CURRENT = 1 (bit),<br>OUTx_MANUAL_PWM = FFh (100% ON)                                        | 0.2 |      | 51    | mA   |

| I <sub>CS_LKG</sub>   | Constant current sink leakage current                                                | V <sub>CC</sub> = 3.6V, OUTx = 1V, OUTx_MANUAL_PWM = 0<br>(0%)                                                                      |     | 0.1  | 1     | μA   |

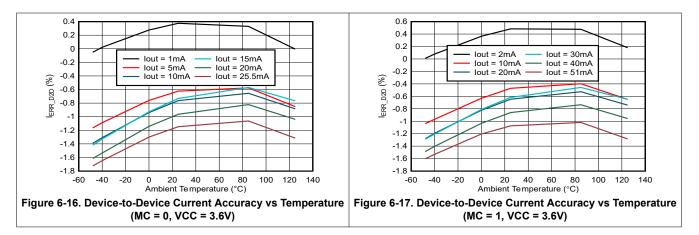

| 1                     | Device to device current error,                                                      | All LEDs turn ON. Current set to 25.5mA<br>(MAX_CURRENT = 0 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh)                         | -8  |      | 8     | %    |

| I <sub>ERR_</sub> D2D | I <sub>ERR_D2D</sub> = (I <sub>AVE</sub> -I <sub>SET</sub> )/I <sub>SET</sub> ×100%  | All LEDs turn ON. Current set to 51mA<br>(MAX_CURRENT = 1 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh)                           | -8  |      | 8     | %    |

| I                     | Channel to Channel current error                                                     | All LEDs turn ON. Current set to 25.5mA<br>(MAX_CURRENT = 0 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh)                         | -3  |      | 3     | %    |

| I <sub>ERR_C2C</sub>  | I <sub>ERR_C2C</sub> = (I <sub>OUTX</sub> -I <sub>AVE</sub> )/I <sub>AVE</sub> ×100% | All LEDs turn ON. Current set to 51mA<br>(MAX_CURRENT = 1 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh)                           | -2  |      | 2     | %    |

|                       |                                                                                      | All LEDs turn ON. Current set to 25.5mA<br>(MAX_CURRENT = 0 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh), V <sub>CC</sub> = 3.6V |     |      | 0.135 | V    |

|                       |                                                                                      | All LEDs turn ON. Current set to 51mA<br>(MAX_CURRENT = 1 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh), V <sub>CC</sub> = 3.6V   |     |      | 0.275 | V    |

| V <sub>HR</sub>       | LED driver output headroom voltage                                                   | All LEDs turn ON. Current set to 25.5mA<br>(MAX_CURRENT = 0 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh), V <sub>CC</sub> = 2.5V |     |      | 0.15  | V    |

|                       |                                                                                      | All LEDs turn ON. Current set to 51mA<br>(MAX_CURRENT = 1 (bit), OUTx_DC = FFh,<br>OUTx_MANUAL_PWM = FFh), , V <sub>CC</sub> = 2.5V |     |      | 0.3   | V    |

| f <sub>LED_PWM</sub>  | PWM dimming frequency                                                                |                                                                                                                                     |     | 23   |       | kHz  |

| f <sub>osc</sub>      | Internal oscillator frequency                                                        |                                                                                                                                     |     | 6    |       | MHz  |

Unless specified otherwise, typical characteristics apply over the full ambient temperature range (–40°C <  $T_A$  < +85°C ),  $V_{CC}$  = 3.6V,  $C_{IN}$  = 1µF.

|                       | PARAMETER                                      | TEST CONDITIONS              | MIN | TYP | MAX | UNIT |

|-----------------------|------------------------------------------------|------------------------------|-----|-----|-----|------|

| Logic Inter           | face                                           | ·                            |     |     |     |      |

| V <sub>STAT_H</sub>   | STAT logic high                                | VCC > 2.5V                   | 2.3 |     |     | V    |

| V <sub>STAT_L</sub>   | STAT logic low                                 | VCC > 2.5V                   |     |     | 0.4 | V    |

| VIH_LOGIC             | High level input voltage of SDA, SCL           |                              | 1.4 |     |     | V    |

| VIL_LOGIC             | Low level input voltage of SDA, SCL            |                              |     |     | 0.4 | V    |

| V <sub>OL_LOGIC</sub> | Low level output voltage of SDA                |                              |     |     | 0.4 | V    |

| Protection            |                                                | ·                            |     |     |     |      |

| T <sub>SD</sub>       | Thermal shutdown threshold for LED driver part | T <sub>J</sub> rising        |     | 150 |     | °C   |

| T <sub>SD_HYS</sub>   | Thermal shutdown hysteresis                    | $T_J$ falling below $T_{SD}$ |     | 15  |     | °C   |

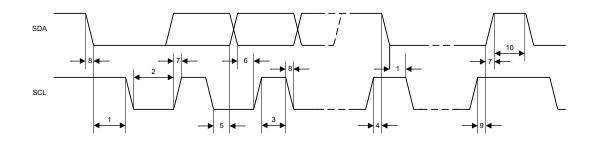

# 6.6 Timing Requirements

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}C < TA < +85^{\circ}C$ ), V<sub>CC</sub> = 3.6V, C<sub>IN</sub> = 1µF.

|                  | I <sup>2</sup> C Timing Requirements                                                         | MIN | NOM MAX |       |

|------------------|----------------------------------------------------------------------------------------------|-----|---------|-------|

| Standar          | rd-mode                                                                                      |     |         |       |

| f <sub>SCL</sub> | SCL clock frequency                                                                          | 0   | 10      | ) kHz |

| 1                | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4   |         | μs    |

| 2                | LOW period of the SCL clock                                                                  | 4.7 |         | μs    |

| 3                | HIGH period of the SCL clock                                                                 | 4   |         | μs    |

| 4                | Set-up time for a repeated START condition                                                   | 4.7 |         | μs    |

| 5                | Data hold time                                                                               | 0   |         | μs    |

| 6                | Data set-up time                                                                             | 250 |         | ns    |

| 7                | Rise time of both SDA and SCL signals                                                        |     | 100     | ) ns  |

| 8                | Fall time of both SDA and SCL signals                                                        |     | 30      | ) ns  |

| 9                | Set-up time for STOP condition                                                               | 4   |         | μs    |

| 10               | Bus free time between a STOP and START condition                                             | 4.7 |         | μs    |

| C <sub>b</sub>   | Capacitive load for each bus line                                                            |     | 40      | ) pF  |

| Fast-mo          | ode                                                                                          |     |         |       |

| f <sub>SCL</sub> | SCL clock frequency                                                                          | 0   | 400     | ) kHz |

| 1                | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6 |         | μs    |

| 2                | LOW period of the SCL clock                                                                  | 1.3 |         | μs    |

| 3                | HIGH period of the SCL clock                                                                 | 0.6 |         | μs    |

| 4                | Set-up time for a repeated START condition                                                   | 0.6 |         | μs    |

| 5                | Data hold time                                                                               | 0   |         | μs    |

| 6                | Data set-up time                                                                             | 100 |         | ns    |

| 7                | Rise time of both SDA and SCL signals                                                        |     | 30      | ) ns  |

| 8                | Fall time of both SDA and SCL signals                                                        |     | 30      | ) ns  |

| 9                | Set-up time for STOP condition                                                               | 0.6 |         | μs    |

| 10               | Bus free time between a STOP and START condition                                             | 1.3 |         | μs    |

| C <sub>b</sub>   | Capacitive load for each bus line                                                            |     | 40      | ) pF  |

| Fast-mo          | ode Plus                                                                                     | 1   |         |       |

| f <sub>SCL</sub> | SCL clock frequency                                                                          | 0   | 100     | ) kHz |

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}C < TA < +85^{\circ}C$ ), V<sub>CC</sub> = 3.6V, C<sub>IN</sub> = 1µF.

|                | I <sup>2</sup> C Timing Requirements                                                         | MIN  | NOM | MAX | UNIT |

|----------------|----------------------------------------------------------------------------------------------|------|-----|-----|------|

| 1              | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26 |     |     | μs   |

| 2              | LOW period of the SCL clock                                                                  | 0.5  |     |     | μs   |

| 3              | HIGH period of the SCL clock                                                                 | 0.26 |     |     | μs   |

| 4              | Set-up time for a repeated START condition                                                   | 0.26 |     |     | μs   |

| 5              | Data hold time                                                                               | 0    |     |     | μs   |

| 6              | Data set-up time                                                                             | 50   |     |     | ns   |

| 7              | Rise time of both SDA and SCL signals                                                        |      |     | 120 | ns   |

| 8              | Fall time of both SDA and SCL signals                                                        |      |     | 120 | ns   |

| 9              | Set-up time for STOP condition                                                               | 0.26 |     |     | μs   |

| 10             | Bus free time between a STOP and START condition                                             | 0.5  |     |     | μs   |

| C <sub>b</sub> | Capacitive load for each bus line                                                            |      |     | 550 | pF   |

# 6.7 Timing Diagrams

Figure 6-1. I<sup>2</sup>C Timing Parameters

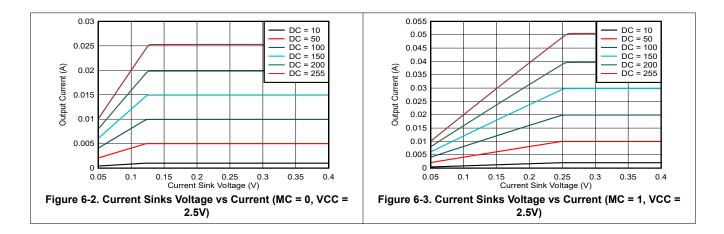

# 6.8 Typical Characteristics

Unless specified otherwise, typical characteristics apply over the full ambient temperature range (-40°C <  $T_A$  < +85°C ),  $V_{CC}$  = 3.6V,  $C_{IN}$  = 1 $\mu$ F

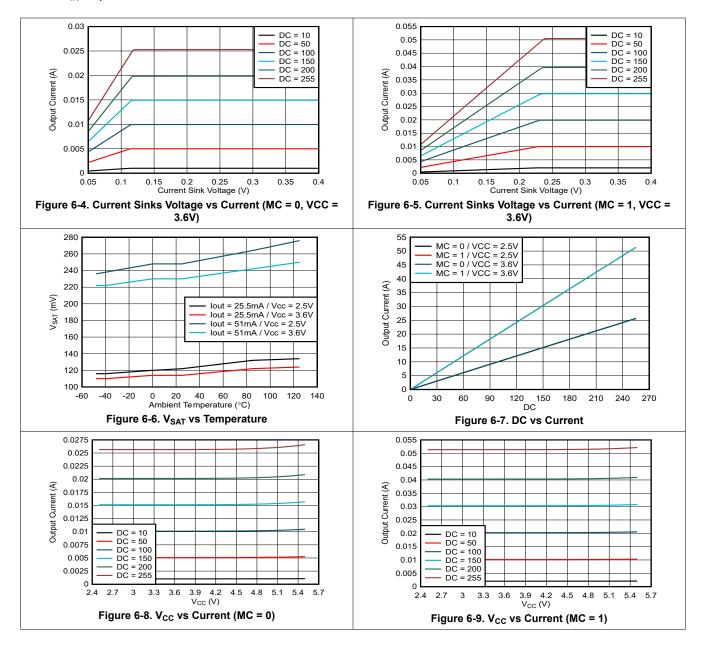

# 6.8 Typical Characteristics (continued)

Unless specified otherwise, typical characteristics apply over the full ambient temperature range ( $-40^{\circ}C < T_A < +85^{\circ}C$ ), V<sub>CC</sub> = 3.6V, C<sub>IN</sub> = 1µF

# 6.8 Typical Characteristics (continued)

Unless specified otherwise, typical characteristics apply over the full ambient temperature range (–40°C <  $T_A$  < +85°C ),  $V_{CC}$  = 3.6V,  $C_{IN}$  = 1µF

# 6.8 Typical Characteristics (continued)

Unless specified otherwise, typical characteristics apply over the full ambient temperature range (–40°C <  $T_A$  < +85°C ),  $V_{CC}$  = 3.6V,  $C_{IN}$  = 1µF

# 7 Detailed Description

# 7.1 Overview

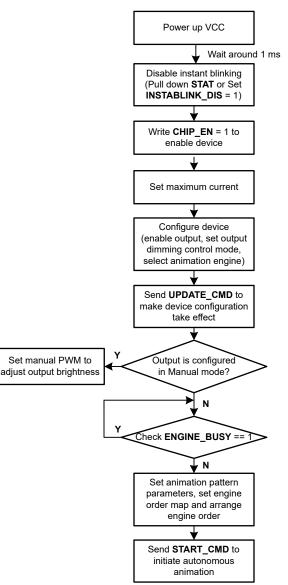

The LP5815 is a 3 channel RGB LED driver with instant blinking and autonomous animation control. The maximum output current of each channel is up to 51mA and can be adjusted by 256 steps from 0 to the full current. Besides the annalog dimming, every channel supports 8-bit PWM dimming in both manaul mode and autonomous animation mode.

The LP5815 features ultra-low shutdown current that is about 0.1uA. Two approaches are provided to control the LP5815 enter shutdown mode, sending shutdown command or constantly pulling down SCL, which improves the flexibility in system design for different application requirements.

The LP5815 integrates advanced autonomous animation control architecture. Four basic configurable independent pattern units can be selected and organized for each channel arbitrarily to realize both simple and complicated pattern effects.

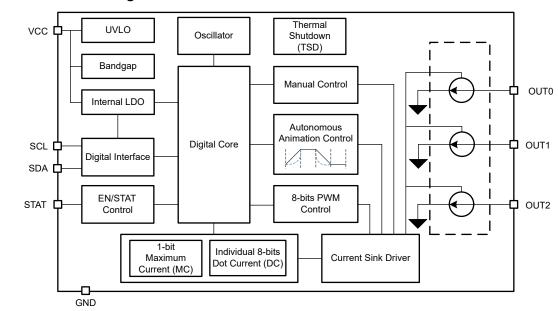

# 7.2 Functional Block Diagram

Figure 7-1. LP5815 Function Block

# 7.3 Feature Description

# 7.3.1 Analog Dimming

There are two methods to control the current gain of each output channel.

- Global 1-bit Maximum Current (MC) control for all channels without external resistor

- Individual 8-bit Dot Current (DC) control for each channel

The maximum output current  $I_{OUT_max}$  of each channel can be programmed by the 1 bit MAX\_CURRENT. When the device is powered on, the default value of MC is 0h, which is 25.5mA.

#### Table 7-1. Maximum Current (MC) Bit Setting

| 1-bit Maximun | l           |                             |  |  |  |

|---------------|-------------|-----------------------------|--|--|--|

| Binary        | Decimal     | – I <sub>OUT_MAX</sub> (mA) |  |  |  |

| 0 (default)   | 0 (default) | 25.5 (default)              |  |  |  |

| 1             | 1           | 51                          |  |  |  |

The LP5815 can individually adjust the analog output current of each channel by using Dot Current (DC) function. The brightness deviation among the LED bins can be miminized to achieve uniform display performance through the DC setting. The DC is programmed in an 8-bit depth, so the analog current can be adjusted with 256 steps from 0 to 100% of  $I_{OUT\_MAX.}$ . The default value of all DC is 0h, which is not current output.

#### Table 7-2. Dot Current (DC) Bits Setting

| 8-bits Dot Curre    | 8-bits Dot Current (DC) Register |                               |  |  |  |  |  |

|---------------------|----------------------------------|-------------------------------|--|--|--|--|--|

| Binary              | Decimal                          | Ratio of I <sub>OUT_MAX</sub> |  |  |  |  |  |

| 0000 0000 (default) | 0 (default)                      | 0% (default)                  |  |  |  |  |  |

| 0000 0001           | 1                                | 0.39%                         |  |  |  |  |  |

| 0000 0010           | 2                                | 0.78%                         |  |  |  |  |  |

|                     |                                  |                               |  |  |  |  |  |

| 1000 0000           | 128                              | 50.2%                         |  |  |  |  |  |

|                     |                                  |                               |  |  |  |  |  |

| 1111 1101           | 253                              | 99.2%                         |  |  |  |  |  |

| 1111 1110           | 254                              | 99.6%                         |  |  |  |  |  |

| 1111 1111           | 255                              | 100%                          |  |  |  |  |  |

By configuring the MC and DC, the analog output current of each channel can be calculated as Equation 1:

$$I_{OUT}\left(mA\right) = I_{OUT\_MAX} \times \frac{DC}{255} \tag{1}$$

The average output current of each channel can be caculated asEquation 2:

$$I_{AVE}\left(mA\right) = I_{OUT\_MAX} \times \frac{DC}{255} \times D_{PWM}$$

<sup>(2)</sup>

• D<sub>PWM</sub> is the PWM duty.

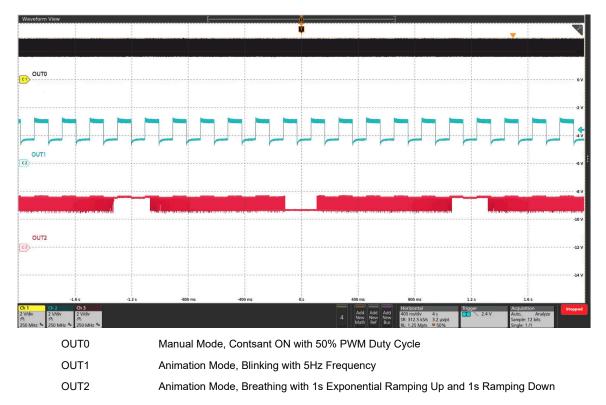

### 7.3.2 PWM Dimming

The LP5815 supports 8-bit PWM dimming with 23kHz frequency in both manual mode and autonomous animation mode. The device integrates an internal 6MHz oscillator to generate the PWM clock.

- Manual Mode: When OUT0\_AUTO\_EN, OUT1\_AUTO\_EN, OUT2\_AUTO\_EN bit in DEV\_CONFIG3 register is set as 0. The output PWM value of each channel is controlled by OUT0\_MANUAL\_PWM, OUT1\_MANUAL\_PWM, OUT2\_MANUAL\_PWM separately. In manual mode, if OUT0\_FADE\_EN, OUT1\_FADE\_EN, OUT2\_FADE\_EN bit in DEV\_CONFIG2 register is set as 0, the output PWM value updates immeditaly to the latest received PWM set value. If OUT0\_FADE\_EN, OUT1\_FADE\_EN, OUT2\_FADE\_EN bit in DEV\_CONFIG2 register is set as 1, the fade in or out function is enabled, the output PWM ramps up or down smoothly to the latest received PWM value within the time defined by OUT FADE\_TIME automatically.

- Autonomous Animation Mode: When OUT0\_AUTO\_EN, OUT1\_AUTO\_EN, OUT2\_AUTO\_EN bit in DEV\_CONFIG3 register is set as 1. The PWM output value of each channel is controlled by the autonomous animation pattern PWM value. Refer to the Autonomous Animation Control for detailed description.

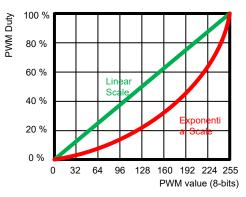

The LP5815 allows users to configure the dimming scale as exponential curve or linear curve for each channel separately through the OUT0\_EXP\_EN, OUT1\_EXP\_EN, OUT2\_EXP\_EN in DEV\_CONFIG3 register. A human-eye-friendly visual performance can be achieved by using the internal exponential scale. The linear scale has great linearity between PWM duty cycle and PWM setting value, which provides flexible approach for external controlled gamma correction algorithm. The 8-bit linear and exponential curves are shown as Figure 7-2.

Figure 7-2. Linear and Exponential PWM Dimming Curves

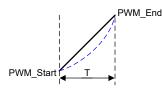

#### 7.3.3 Sloper

In manual control mode, output fade in or out is supported when LED0\_FADE\_EN, LED1\_FADE\_EN, LED2\_FADE\_EN bit in DEV\_CONFIG2 register is set as 1. Sloper is the basic element to achieve autonomous fade in and fade out animations. The output can achieve 256 steps fade in or fade out effects from 'PWM\_Start' to 'PWM\_End' within a specified time period T as shown in Figure 7-3. Exponential dimming curve can also be supported in the sloper.

Figure 7-3. Sloper Curve Demonstration

The programable time T is selectable from 0 to around 8s with 16 levels shown in Table 7-3.

| Regist | ter Value | 0h | 1h    | 2h   | 3h    | 4h   | 5h    | 6h   | 7h    | 8h   | 9h    | Ah   | Bh | Ch | Dh | Eh | Fh |

|--------|-----------|----|-------|------|-------|------|-------|------|-------|------|-------|------|----|----|----|----|----|

| Time   | е (Тур.)  | 0s | 0.05s | 0.1s | 0.15s | 0.2s | 0.25s | 0.3s | 0.35s | 0.4s | 0.45s | 0.5s | 1s | 2s | 4s | 6s | 8s |

#### 7.3.4 Autonomous Animation Control

The LP5815 supports autonomous animation control for each channel. With the animation engine the device can realize vivid lighting effects while releasing the loading of external controller.

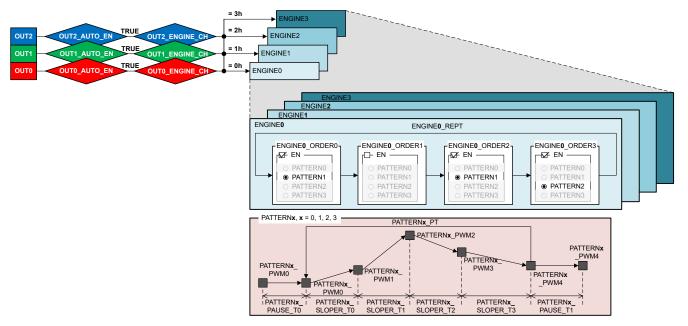

As showed in Figure 7-4, the LP5815 has 4 independent configurable animation engine units, ENGINE0, ENGINE1, ENGINE2 and ENGINE3. Any one of the 4 engines can be selected by each output channel. There are 4 engine orders to construct one engine unit. For each engine order, one pattern unit can be selected to execute when the engine order is enabled. At the bottom layer, there are 4 independent configurable pattern units.

Figure 7-4. Animation Pattern Overview

#### 7.3.4.1 Animation Engine Unit

The LP5815 has 4 independent animation engine units ENGINE0, ENGINE1, ENGIN2 and ENGINE3. For each output, any one of the 4 engines can be selected by setting the register  $OUTx_ENGINE_CH$  bits in DEV\_CONFIG4 register (x = 0, 1, 2).

- OUTx\_ENGINE\_CH = 0, ENGINE0 is selected

- OUTx\_ENGINE\_CH = 1, ENGINE1 is selected

- OUTx\_ENGINE\_CH = 2, ENGINE2 is selected

- OUTx\_ENGINE\_CH = 3, ENGINE3 is selected

There are 4 engine orders, ENGINEx\_ORDER0, ENGINEx\_ORDER1, ENGINEx\_ORDER2 and ENGINEx\_ORDER3, to construct one engine unit ENGINEx (x = 0, 1, 2, 3). The 4 engine orders in one engine unit is executed sequentially. But any one of the 4 engine orders can be skipped by disabling the engine order through setting the corresponding ExOy\_EN bit as 0 (x, y = 0, 1, 2, 3) in ENGINE\_CONFIG4 and ENGINE\_CONFIG5 registers.

If 4 engine orders in one engine unit are all disabled, the engine unit is not started after sending the Start\_command. The corresponding internal engine busy flag is not set as shown in Figure 7-7.

The engine unit ENGINEx can be defined to execute repeately as the times specified in ENGINEx\_REPT in ENGINE\_CONFIG6 register.

- ENGINEx\_REPT = 0, ENGINEx doesn't repeat

- ENGINEx\_REPT = 1, ENGINEx repeats 1 time

- ENGINEX\_REPT = 2, ENGINEX repeats 2 times

• ENGINEx\_REPT = 3, ENGINEx repeats infinitely

Engine order is enabled by setting the corresponding  $ExOy_EN$  bit as 1. Any one of 4 basic patterns can be selected through the ENGINEx\_ORDERy from ENGINE\_CONFIG0 to ENGINE\_CONFIG3 registers (x, y = 0, 1, 2, 3).

- ENGINEx\_ORDERy = 0, PATTERN0 is selected

- ENGINEx\_ORDERy = 1, PATTERN1 is selected

- ENGINEx\_ORDERy = 2, PATTERN2 is selected

- ENGINEx\_ORDERy = 3, PATTERN3 is selected

### 7.3.4.2 Animation Pattern Unit

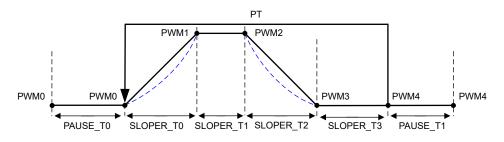

The LP5815 has 4 independent configurable pattern units, PATTERN0, PATTERN1, PATTERN2 and PATTERN3. Every pattern unit has 5 PWM values, 6 time values and 1 play times value.

For PATTERN*x* (*x* = 0, 1, 2, 3),

- The 5 PWM values are stored in PATTERN*x*\_PWM0, PATTERN*x*\_PWM1, PATTERN*x*\_PWM2, PATTERN*x*\_PWM3 and PATTERN*x*\_PWM4. The 8 bits PWM value can be programmed from 0 to 255. Exponential dimming curve can also be supported in the sloper time.

- The 6 time values are devided into 2 types, pause time and sloper time. There are 2 pause time, PATTERNx\_PAUSE\_T0 and PATTERNx\_PAUSE\_T1. 4 sloper time, PATTERNx\_SLOPER\_T0, PATTERNx\_SLOPER\_T1, PATTERNx\_SLOPER\_T2 and PATTERNx\_SLOPER\_T3. Evey time value can be configured from 0 to 8s with 16 options.

- The pattern play times value is stored in PATTERNx\_PT and can be configued from 0 to infinite times with 16 options. When the PATTERNx\_PT = 0, the 2 pause time, output PWM0 for PAUSE\_T0 and output PWM4 for PAUSE\_T1, are still executed to construct the pattern unit.

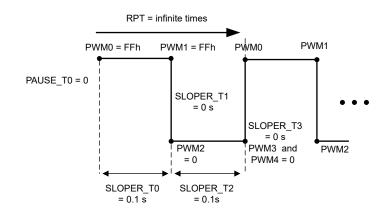

Typical breathing effect example is illustrated as shown in Figure 7-5.

Figure 7-5. Animation Pattern Unit - Example 1

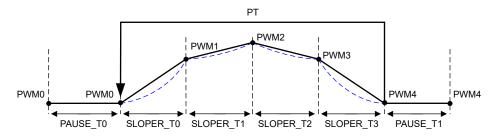

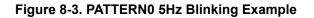

Advanced breathing effect example is shown in Figure 7-6. There are 2 different fading speeds are set in the PWM rising and falling phases, to achieve a complex animation.

Figure 7-6. Animation Pattern Unit - Example 2

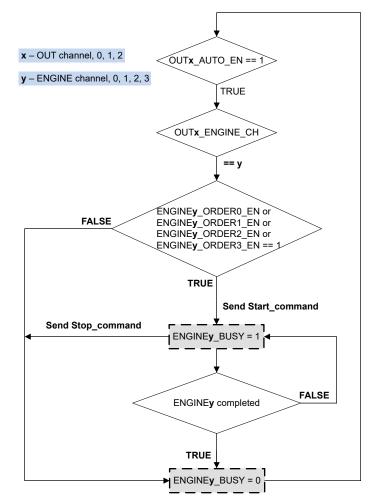

#### 7.3.4.3 Animation Control

The LP5815 has individual engine busy flag for each output channel, OUT0\_ENGINE\_BUSY, OUT1\_ENGINE\_BUSY and OUT2\_ENGINE\_BUSY, to indicate whether the engine selected by the output channel is under running or not. Besides the individule output busy flag there is a global engine busy flag, ENGINE\_BUSY, to indicate if there is engine under running or not.

When the ENGINE\_BUSY is set as 1, the engine configure registers and pattern configure registers shown in Table 7-4 are locked for modification protection. These engine busy lock registers can only be modified when **ENGINE\_BUSY = 0**.

| Description                 | Register Address | Register Acronym                                                                                                                                                                                                                                                               |

|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Engine configure registers  | 0x06 to 0x0C     | ENGINE_CONFIG0 to ENGINE_CONFIG6                                                                                                                                                                                                                                               |

| Pattern configure registers | 0x1C to 0x3F     | <ul> <li>PATTERNx_PAUSE_TIME</li> <li>PATTERNx_REPEAT_TIME</li> <li>PATTERNx_PWM0</li> <li>PATTERNx_PWM1</li> <li>PATTERNx_PWM2</li> <li>PATTERNx_PWM3</li> <li>PATTERNx_PWM4</li> <li>PATTERNx_SLOPER_TIME1</li> <li>PATTERNx_SLOPER_TIME2</li> <li>x = 0, 1, 2, 3</li> </ul> |

#### Table 7-4. Engine Busy Lock Registers

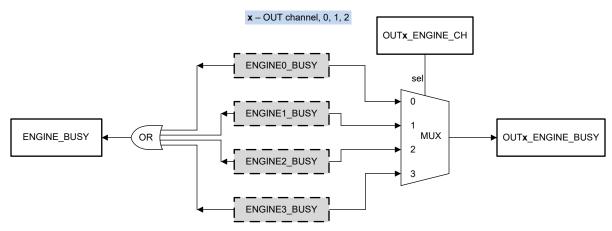

The LP5815 has 4 internal engine busy flags, ENGINE0\_BUSY, ENGINE1\_BUSY, ENGINE2\_BUSY and ENGINE3\_BUSY, as shown in Figure 7-7. The ENGINEy\_BUSY is set as 1 after Start\_command is received with all the below conditions.

- The engine has been selected by at least one channel, for example OUTx, and there is at least one engine order enabled in this engine

- The autonomous enable bit is set as 1 of the OUTx

The internal ENGINEy\_BUSY flag keeps as 1 until the engine has completed or there is Stop\_command received.

Figure 7-7. Internal Engine Busy Status

Any one of the internal engine busy flag, ENGINEx\_BUSY, set to 1 leads to the global engine busy flag, ENGINE\_BUSY, being 1, as shown in Figure 7-8.

The individual engine busy flag, OUTx\_ENGINE\_BUSY, is dependent on the internal engine busy flag selected by the correpsonding engine channel register value.

Figure 7-8. Individual and Global Engine Busy Flag

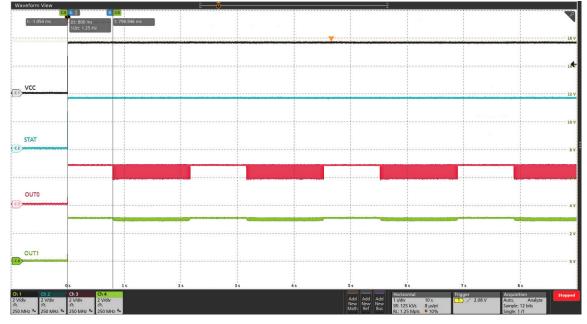

## 7.3.5 Instant Blinking

The LP5815 provides instant blinking via STAT control function for applications that require LED indication before controller is ready to send command. When VCC voltage is higher than  $V_{CC\_UVLO}$  and instant blinking function is not disabled (INSTABLINK\_DIS = 0), the OUT0 waits 300ms blank time to start blinking after STAT being pulled high. The timing is shown in Figure 7-9.

During the 300ms blank time after STAT being pulled high,

- if the instant blinking function is not disabled (INSTABLINK\_DIS = 0 (default)), the LP5815 doesn't respond to the 5 dedicated software commands as described in Command Description and the OUT0 of the LP5815 starts running the blinking pattern as showed in Instant Blinking Pattern after the blank time.

- if the instant blinking function is disabled by setting the INSTABLINK\_DIS as 1 through the I<sup>2</sup>C interface, the LP5815 responds to the 5 dedicated software commands as described in Command Description except for the Shutdown\_command that the LP5815 doesn't enter SHUTDOWN mode until the STAT is pulled low. The OUT0 doesn't run the blinking pattern after the blank time.

While the LP5815 staying in INSTANT BLINKING mode,

- the OUT0 keeps running the blinking pattern if STAT is kept high (STAT = H) and instant blinking function is not disabled (INSTABLINK\_DIS = 0).

- the 5 dedicated software commands don't work as described in Command Description.

- the OUT0 stops running the blinking pattern if STAT is pulled low (STAT = L) or instant blinking function is disabled (INSTABLINK\_DIS = 1).

Figure 7-9. Instant Blinking Timing

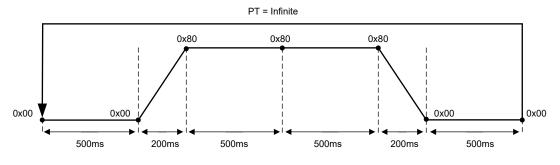

Figure 7-10 shows the parameters of 1 cycle blinking pattern.

At the beginning, there is 500ms pause time before PWM starts ramping up. After the pause time, the PWM ramps up from 0 to 50% in 200ms, then keeps 50% for 1s. Next, it starts ramping down from 50% to 0 in 200ms. At last, the PWM keeps off for another 500ms pause time before the next cycle starts.

The maximum current setting for the instant blinking is 25.5mA with OUT0\_DC = 0xFF, MAX\_CURRENT = 0.

Figure 7-10. Instant Blinking Pattern

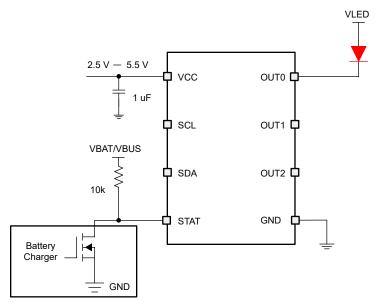

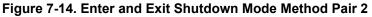

Figure 7-11 shows a typical application circuit that provides the instant blinking function. The STAT pin is pulled up by an external resistor to the battery voltage or bus voltage of the charger. And there is a LED connected to OUT0.

When the battery voltage drops below the charging threshold, the charger starts to work and can turn off the STAT pulling down switch. Then the LED connected to OUT0 starts blinking as long as the VCC voltage of the LP5815 is higher than the  $V_{CC\_UVLO}$  threshold, which indicates the charging status. When the battery charging is completed, the charger can turn on the STAT pulling down switch to pull down the STAT to make the LP5815 exit the instant blinking state. Then the LED stops blinking to indicate the charging is completed.

Figure 7-11. Instant Blinking Application Circuit

# 7.3.6 Protections

### 7.3.6.1 UVLO

The LP5815 has an internal comparator that monitors the voltage at VCC. When  $V_{CC}$  is below  $V_{CC\_UVLO}$ , the device resets and keeps in Power On Reset (POR) state. When  $V_{CC}$  ramps above  $V_{CC\_UVLO}$ , the device enters INITIALIZATION mode and the POR flag is set. The POR flag needs manual clear by setting POR\_CLR bit when CHIP\_EN = 1.

#### 7.3.6.2 Thermal Shutdown

The LP5815 implements a thermal shutdown mechanism to protect the device from damage due to overheating. When the junction temperature of the device rises to  $155^{\circ}$ C (typical), the device turns off all output channels. The TSD flag is set to indicate thermal shutdown is triggered. The LP5815 releases thermal shutdown when the junction temperature reduces to  $140^{\circ}$ C (typical). The TSD flag needs manual clear by setting TSD\_CLR bit when CHIP\_EN = 1.

# 7.4 Device Functional Modes

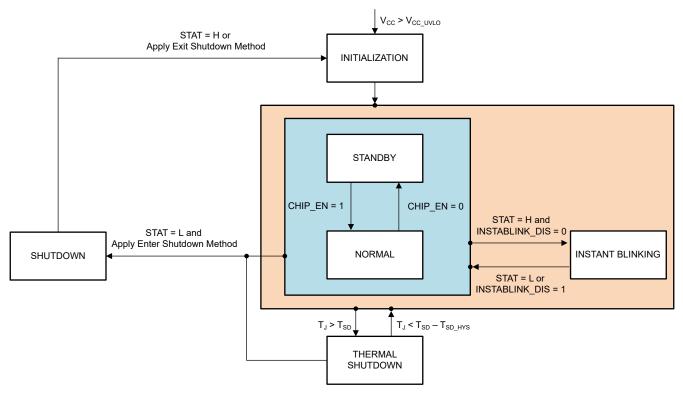

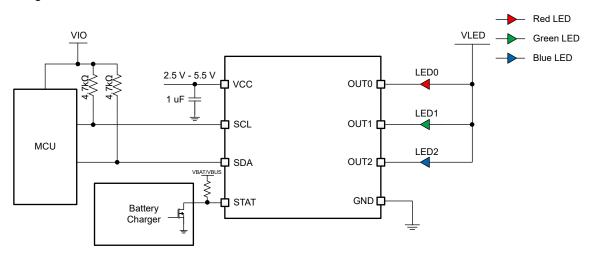

The Figure 7-12 shows the function modes of the LED driver.

Figure 7-12. Functional Modes

### 7.4.1 Initialization Mode

The LP5815 enters INITIALIZATION mode when VCC voltage ramps above the  $V_{CC\_UVLO}$  or exits from SHUTDOWN mode. The LP5815 reset all registers to default value in INITIALIZATION mode. The POR flag is set to 1 after exiting from INITIALIZATION mode to indicate the reset history.

#### 7.4.2 Standby and Normal Mode

The LP5815 enters STANDBY mode when CHIP\_EN = 0 or NORMAL mode when CHIP\_EN = 1 after exiting from INITIALIZATION mode, INSTANT BLINKING mode or THERMAL SHUTDOWN mode.

While staying in STANDBY or NORMAL mode,

- when STAT is pulled high (STAT = H) and instant blinking function is not disabled (INSTABLINK\_DIS = 0), the LP5815 enters INSTANT BLINKING mode after the 300ms blank time as described in Instant Blinking.

- when STAT is pulled low (STAT = L) and Enter Shutdown Method is applied, the LP5815 enters SHUTDOWN mode. The Enter Shutdown Method is described in Shutdown Mode.

- when instant blinking function is disabled (INSTABLINK\_DIS = 1) and STAT is pulled high (STAT = H), the LP5815 doesn't enter SHUTDOWN mode even though Enter Shutdown Method is applied. But the internal trigger of entering shutdown mode is recorded and the LP5815 enters SHUTDOWN mode immediately as long as the STAT is pulled low.

- when the junction temperature of the LP5815 rises above the thermal shutdown threshold T<sub>SD</sub>, the LP5815 turns off all output channels and enters THERMAL SHUTDOWN mode.

#### 7.4.3 Instant Blinking Mode

The OUT0 of the LP5815 keeps running the blinking pattern as shown in Instant Blinking Pattern while the LP5815 staying in INSTANT BLINKING mode.

The LP5815 exits INSTANT BLINKING mode when STAT is pulled down (STAT = L) or instant blinking function is disabled through setting the INSTABLINK\_DIS bit as 1.

In INSTANT BLINKING mode, the LP5815 doesn't respond to the 5 dedicated software commands, Shutdown\_command, Reset\_command, Update\_command, Start\_command and Stop\_command.

#### 7.4.4 Shutdown Mode

The LP5815 supports shutdown mode to minimize the power consumption from VCC. The quscient current from VCC decreases to 0.1 uA (typical) in SHUTDOWN mode. The LP5815 provides two pairs of methods to control the device enter and exit SHUTDOWN mode.

- Figure 7-13 shows the method 1

- Enter shutdown, send Shutdown\_command by writing 0x33 to register 0xD though I<sup>2</sup>C communication when STAT is pulled down.

- Exit shutdown,

- Toggle SDA 8 times to generate 8 falling edges while keeping SCL as high. The supported maximum toggle frequency for SDA is 100kHz.

- Or pull up STAT regardless of the SCL and SDA state.

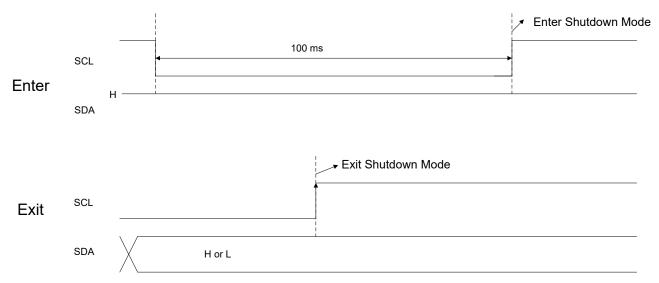

- Figure 7-14 shows the method 2

- Enter shutdown, pull down SCL for 100ms while keeping SDA as high when STAT is pulled down.

- Exit shutdown,

- Pull up SCL to generate one rising edge regardless of SDA state.

- Or pull up STAT regardless of the SCL and SDA state.

|        |     | Enter Shutdown Mode                 |    |

|--------|-----|-------------------------------------|----|

| Enter  | SCL |                                     |    |

| LIIIEI | SDA | Write 0x33 to SHUTDOWN_CMD register |    |

|        |     |                                     |    |

|        | SCL | ۱                                   |    |

| Exit   | SDA |                                     |    |

|        |     | Exit Shutdown Mo                    | de |

Figure 7-13. Enter and Exit Shutdown Mode Method Pair 1

#### 7.4.5 Thermal Shutdown Mode

All output channels are turned off while the LP5815 staying in THERMAL SHUTDOWN mode. The I2C interface is still active and the LP5815 enters SHUTDOWN mode when STAT is pulled low (STAT = L) and Enter Shutdown Method is applied.

When the junction temperature of LP5815 falles blow the thermal shutdown threshold, the LP5815 enters STANDBY mode when CHIP\_EN = 0 or NORMAL mode when CHIP\_EN = 1 after exiting from THERMAL SHUTDOWN mode. The TSD flag needs manual clear through setting TSD\_CLR bit when CHIP\_EN = 1.

# 7.5 Programming

The LP5815 is compatible with I<sup>2</sup>C standard specification. The device supports standard mode (100kHz maximum), fast mode (400kHz maximum) and fast plus mode (1MHz maximum). The device chip address is 0x2D.

# 7.5.1 I<sup>2</sup>C Data Tansactions

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when clock signal is LOW. START and STOP conditions classify the beginning and the end of the data transfer session. A START condition is defined as the SDA signal transitioning from and the end of the data transfer session. A START condition is defined as the SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The bus leader always generates START and STOP conditions. The bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the bus leader can generate repeated START conditions. First START and repeated START conditions are functionally equivalent.

Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the leader. The leader releases the SDA line (HIGH) during the acknowledge clock pulse. The device pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The device generates an acknowledge after each byte has been received.

There is one exception to the acknowledge after every byte rule. When the leader is the receiver, the receiver must indicate to the transmitter an end of data by not acknowledging (negative acknowledge) the last byte clocked out of the follower. This negative acknowledge still includes the acknowledge clock pulse (generated by the leader), but the SDA line is not pulled down.

### 7.5.2 I<sup>2</sup>C Data Format

The address and data bits are transmitted MSB first with 8-bits length format in each cycle. Each transmission is started with Address Byte 1, which are divided into 7 bits of the chip address and 1 read/write bit. The 8 bits of register address are put in Address Byte 2. The device supports both independent mode and broadcast mode. The auto-increment feature allows writing / reading several consecutive registers within one transmission. If not consecutive, a new transmission must be started.

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | Table 7-5. I <sup>2</sup> | <sup>2</sup> C Data For | mat                 |                     |                     |             |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------|-------------------------|---------------------|---------------------|---------------------|-------------|--|--|--|

| Address Byte1 | Chip Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                           |                         |                     |                     |                     |             |  |  |  |

|               | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 6               | Bit 5                     | Bit 4                   | Bit 3               | Bit 2               | Bit 1               | Bit 0       |  |  |  |

| Independent   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                   | 0                         | 1                       | 1                   | 0                   | 1                   | R: 1 W: 0   |  |  |  |

| Broadcast     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                   | 1                         | 0                       | 1                   | 0                   | 0                   | - K. I W. U |  |  |  |

|               | Register Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |                           |                         |                     |                     |                     |             |  |  |  |

| Address Byte2 | Bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 6               | Bit 5                     | Bit 4                   | Bit 3               | Bit 2               | Bit 1               | Bit 0       |  |  |  |

|               | 7 <sup>th</sup> bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6 <sup>th</sup> bit | 5 <sup>th</sup> bit       | 4 <sup>th</sup> bit     | 3 <sup>rd</sup> bit | 2 <sup>nd</sup> bit | 1 <sup>st</sup> bit | 0 bit       |  |  |  |

|               | SDA CA7 CA6 CA3 CA2 CA1 W CACK CA3 CA2 CA1 W CAX CAX CA3 CA2 CA1 W CAX CAX CAX CA3 CA2 CA1 W CAX CAX CAX CA3 CA2 CA1 W CAX CAX CAX CA3 CA2 CA1 W |                     |                           |                         |                     |                     |                     |             |  |  |  |

### Figure 7-15. I<sup>2</sup>C Write Timming

# Figure 7-16. I<sup>2</sup>C Read Timming

#### 7.5.3 Command Description

The LP5815 has 5 dedicated software commands, Shutdown\_command, Reset\_command, Update\_command, Start\_command and Stop\_command. Besides the 5 software commands, there is another PAUSE\_CONTINUE bit used to control the execution of the autonomous animation.

- Send Shutdown\_command is one of the 2 methods to make the device enter SHUTDOWN mode as described in Shutdown Mode. In INSTANT BLINKING mode, the LP5815 doesn't respond to the Shutdown\_command.

- Send **Reset\_command** to reset all registers to default value. In INSTANT BLINKING mode, the LP5815 doesn't respond to the Reset\_command.

- Send Update\_command to make the modified value in the device configuration registers as shown in Table 7-6 to take effect. The LP5815 responds to the Update\_command only when CHIP\_EN = 1 and not in INSTANT BLINKING mode.

- Send **Start\_command** to start running the configured autonomous animation patterns on the outputs. The LP5815 responds to the Start\_command only when CHIP\_EN = 1 and not in INSTANT BLINKING mode.

- Send **Stop\_command** to stop running the configured autonomous animation patterns on the outputs. The LP5815 responds to the Stop\_command only when CHIP\_EN = 1 and not in INSTANT BLINKING mode.

- Set PAUSE\_CONTINUE bit as 1 to pause the running of the configured autonomous animation patterns on the outputs. Clear PAUSE\_CONTINUE bit as 0 to continue the running of the previous paused autonomous animation patterns on the outputs. When the PAUSE\_CONTINUE = 1, the configured autonomous animation pattern is not started after Start\_command is sent.

#### Table 7-6. Update\_command Control Registers

| Register Address | Register Acronym                               |  |

|------------------|------------------------------------------------|--|

| 0x01 to 0x05     | DEV_CONGIF <i>x</i> , <i>x</i> = 0, 1, 2, 3, 4 |  |

# 7.6 Register Maps

# Table 7-7. Register Maps

| Address | Acronym               | Bit 7                                 | Bit 6                             | Bit 5           | Bit 4           | Bit 3        | Bit 2            | Bit 1            | Bit 0              |

|---------|-----------------------|---------------------------------------|-----------------------------------|-----------------|-----------------|--------------|------------------|------------------|--------------------|

| 0h      | CHIP_EN               | RESERVE                               | RESERVED INSTABLI CHIP_<br>NK_DIS |                 |                 |              |                  |                  | CHIP_EN            |

| 1h      | DEV_CONFIG0           | RESERVE                               | RESERVED MAX_CU<br>RRENT          |                 |                 |              |                  |                  |                    |

| 2h      | DEV_CONFIG1           | RESERVE                               | D                                 |                 |                 |              | OUT2_EN          | OUT1_EN          | OUT0_EN            |

| 3h      | DEV_CONFIG2           | LED_FADE                              | E_TIME                            |                 |                 | RESERV<br>ED | OUT2_FA<br>DE_EN | OUT1_FA<br>DE_EN | OUT0_FA<br>DE_EN   |

| 4h      | DEV_CONFIG3           | RESERV<br>ED                          | OUT2_EX<br>P_EN                   | OUT1_EX<br>P_EN | OUT0_EX<br>P_EN | RESERV<br>ED | OUT2_AU<br>TO_EN | OUT1_AU<br>TO_EN | OUT0_AU<br>TO_EN   |

| 5h      | DEV_CONFIG4           | RESERVE                               | D                                 | OUT2_EN         | GINE_CH         | OUT1_EN      | GINE_CH          | OUT0_EN          | GINE_CH            |