Order

Now

#### LMZ20502

Reference

Design

SNVS852D - JUNE 2012 - REVISED AUGUST 2018

# LMZ20502 2-A Nano Module

Technical

Documents

#### 1 Features

- Integrated Inductor

- Miniature 3.5 mm × 3.5 mm × 1.75 mm Package

- 2-A Maximum Load Current

- Input Voltage Range of 2.7 V to 5.5 V

- Adjustable Output Voltage Range of 0.8 V to 3.6 V

- ± 1% Feedback Tolerance Over Temperature

- 2.4-µA (maximum) Quiescent Current In Shutdown

- 3-MHz Fixed PWM Switching Frequency

- –40°C to 125°C Junction Temperature Range

- Power Good Flag Function

- Pin-Selectable Switching Modes

- · Internal Compensation and Soft Start

- Current Limit, Thermal Shutdown, and UVLO

Protection

- Create a Custom Design Using the LMZ20502 With WEBENCH<sup>®</sup> Power Designer

### 2 Applications

- Point of Load Regulation

- Space Constrained Applications

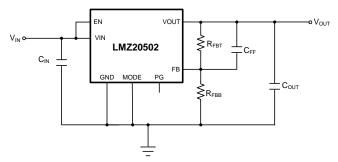

#### **Simplified Schematic**

### 3 Description

Tools &

Software

The LMZ20502 nano module regulator is an easy-touse synchronous step-down DC/DC converter capable of driving up to 2 A of load from an input of up to 5.5 V, with exceptional efficiency and output accuracy in a very small solution size. The innovative package contains the regulator and inductor in a small 3.5 mm × 3.5 mm × 1.75 mm volume, thus saving board space and eliminating the time and expense of inductor selection. The LMZ20502 requires only five external components and has a pinout designed for simple, optimum PCB layout. The device provides an easy-to-use complete design with a minimum number of external components and the TI WEBENCH<sup>®</sup> design tool. TI's WEBENCH tool includes features such as external component calculation, electrical simulation, and WebTherm<sup>™</sup>. For soldering information, refer to the following document: SNOA401.

Support &

Community

20

#### **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE /<br>DRAWING | BODY SIZE (NOM)   |  |  |

|-------------|----------------------|-------------------|--|--|

| LMZ20502    | μSIP (8)             | 3.50 mm × 3.50 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

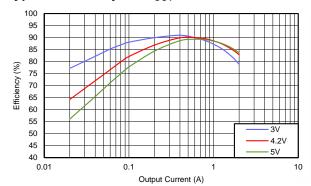

#### Typical Efficiency for V<sub>OUT</sub> = 1.8 V Auto Mode

Features ..... 1

Applications ..... 1

Description ..... 1

Revision History..... 2

Pin Configuration and Functions ...... 3

Specifications...... 4

6.1 Absolute Maximum Ratings ...... 4

6.6 System Characteristics ...... 7

6.7 Typical Characteristics ...... 8

ESD Ratings ..... 4

Recommended Operating Conditions ...... 4

1

2

3

4

5

6

7

6.2

6.3

6.4

7.3

# **Table of Contents**

| 8  | Арр  | lication and Implementation                     | 15 |

|----|------|-------------------------------------------------|----|

|    | 8.1  | Application Information                         | 15 |

|    | 8.2  | Typical Application                             | 16 |

|    | 8.3  | Do's and Don'ts                                 | 23 |

| 9  | Pow  | er Supply Recommendations                       | 23 |

| 10 | Lay  | out                                             | 24 |

|    | 10.1 | Layout Guidelines                               | 24 |

|    | 10.2 | Layout Example                                  | 25 |

|    | 10.3 | Soldering Information                           | 25 |

| 11 | Dev  | ice and Documentation Support                   | 27 |

|    | 11.1 | Device Support                                  | 27 |

|    | 11.2 | Receiving Notification of Documentation Updates | 28 |

|    | 11.3 | Community Resources                             | 28 |

|    | 11.4 | Trademarks                                      | 28 |

|    | 11.5 | Electrostatic Discharge Caution                 | 28 |

|    | 11.6 | Glossary                                        | 28 |

| 12 | Mec  | hanical, Packaging, and Orderable               |    |

|    | Info | rmation                                         | 28 |

|    | 12.1 | Tape and Reel Information                       | 29 |

### 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision C (April 2015) to Revision D                                                                                                                                                              | Page |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Remove Simple Switcher branding; add links for WEBENCH, top navigator icon for TI reference of content                                                                                                          | •    |

| Changes from Revision B (December 2014) to Revision C                                                                                                                                                           | Page |

| Added the package option addendum manually                                                                                                                                                                      | 1    |

| Changes from Revision A (July 2013) to Revision B                                                                                                                                                               | Page |

| <ul> <li>Changed Device Information and Handling Rating tables, Feature Description, Device Functional<br/>Application and Implementation, Power Supply Recommendations, Layout, Device and Document</li> </ul> |      |

Application and Implementation, Power Supply Recommendations, Layout, Device and Documentation Support, and

. . . .

www.ti.com

#### LMZ20502 SNVS852D – JUNE 2012–REVISED AUGUST 2018

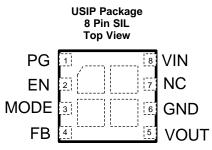

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PI     | N    |      | DESCRIPTION                                                                                                                                  |  |  |  |

|--------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NUMBER | NAME | TTPE | DESCRIPTION                                                                                                                                  |  |  |  |

| 1      | PG   | 0    | Power good flag; open drain. Connect to logic supply through a resistor. High = power good; Low = power bad. If not used, leave unconnected. |  |  |  |

| 2      | EN   | I    | Enable input. High = On, Low = Off. A valid input voltage, on pin 8, must be present before EN is<br>asserted. Do not float.                 |  |  |  |

| 3      | MODE | Ι    | Mode selection input. High = forced PWM. Low = AUTO mode, with PFM at light load . Do not float.                                             |  |  |  |

| 4      | FB   | I    | Feedback input to controller. Connect to output through feedback divider.                                                                    |  |  |  |

| 5      | VOUT | Р    | Regulated output voltage; connect to C <sub>OUT</sub> .                                                                                      |  |  |  |

| 6      | GND  | G    | Ground for all circuitry. Reference point for all voltages.                                                                                  |  |  |  |

| 7      | NC   |      | This pin must be left floating. Do not connect to ground or any other node.                                                                  |  |  |  |

| 8      | VIN  | Р    | Input supply to regulator. Connect to input capacitor(s) as close as possible to the VIN pin and GND pin of the module.                      |  |  |  |

| EP     | EP   | G    | Ground and heat-sink connection. See Layout Guidelines section for more information.                                                         |  |  |  |

(1) G = Ground, I = Input, O = Output, P = Power

### 6 Specifications

#### 6.1 Absolute Maximum Ratings

Under the recommended operating junction temperature range of -40°C to 125°C (unless otherwise noted) <sup>(1)</sup>

|                                                            | MIN  | MAX                  | UNIT |

|------------------------------------------------------------|------|----------------------|------|

|                                                            | WIIN | WAA                  |      |

| VIN to GND                                                 | -0.2 | 6                    |      |

| EN, MODE, FB, PG, to GND <sup>(2)</sup>                    | -0.2 | V <sub>IN</sub> +0.2 | V    |

| VOUT to GND <sup>(2)</sup>                                 | -0.2 | V <sub>IN</sub> +0.2 |      |

| Junction temperature                                       |      | 150                  | °C   |

| Peak soldering reflow temperature for Pb <sup>(3)</sup>    |      | 240                  |      |

| Peak soldering reflow temperature for No-Pb <sup>(3)</sup> |      | 260                  | °C   |

| Storage temperature range                                  | -65  | 150                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The absolute maximum voltage on this pin must not exceed 6V with respect to ground. Do not allow the voltage on the output pin to exceed the voltage on the input pin by more than 0.2 V.

(3) For soldering information, refer to the following document: SNOA401.

### 6.2 ESD Ratings

|                    |                         |                                                                                                | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                    | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{pins^{(2)}}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Under the recommended operating junction temperature range of -40°C to 125°C (unless otherwise noted) <sup>(1)</sup>

|                                     | MIN | NOM MAX | UNIT |

|-------------------------------------|-----|---------|------|

| Input voltage                       | 2.7 | 5.5     | V    |

| Output voltage programming          | 0.8 | 3.6     | V    |

| Output voltage range <sup>(2)</sup> | 0   | 3.6     | V    |

| Load current                        | 0   | 2       | А    |

| Power good flag current             | 0   | 4       | mA   |

| Junction temperature                | -40 | 125     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Under no conditions should the output voltage be allowed to fall below zero volts.

### 6.4 Thermal Information

|                       |                                              | LMZ20502   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | USIP (SIL) | UNIT |

|                       |                                              | 8 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 42.6       |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 20.8       |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 9.4        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 1.5        | C/VV |

| ΨЈВ                   | Junction-to-board characterization parameter | 9.3        |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.8        |      |

(1) The values given in this table are only valid for comparison with other packages and can not be used for design purposes. For design information please see the *Maximum Ambient Temperature* section. For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report.

#### LMZ20502

SNVS852D-JUNE 2012-REVISED AUGUST 2018

www.ti.com

#### 6.5 Electrical Characteristics

Limits apply over the recommended operating junction temperature range of  $-40^{\circ}$ C to  $125^{\circ}$ C, unless otherwise noted. Minimum and maximum limits are verified through test, design, or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}$ C, and are provided for reference purposes only. Unless otherwise stated the following conditions apply:  $V_{IN} = 3.6$  V

|                     | PARAMETER                                              | TEST CONDITIONS                                  | MIN <sup>(1)</sup> | TYP  | MAX <sup>(1)</sup> | UNIT |  |

|---------------------|--------------------------------------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| V <sub>FB</sub>     | Feedback voltage                                       | V <sub>IN</sub> = 3.6 V                          | 0.594              | 0.6  | 0.606              | V    |  |

| I <sub>Q_AUTO</sub> | Operating quiescent current in AUTO mode               | AUTO mode, $V_{FB} = 0.8V$                       |                    | 72   | 90                 | μA   |  |

| I <sub>Q_PWM</sub>  | Operating quiescent current in<br>forced PWM mode      | PWM mode, V <sub>FB</sub> = 0.8V                 |                    | 490  | 620                | μA   |  |

| I <sub>Q_off</sub>  | Shutdown quiescent current <sup>(2)</sup>              | V <sub>IN</sub> = 3.6 V, V <sub>EN</sub> = 0.0 V |                    | 0.7  | 1.5                |      |  |

|                     |                                                        | V <sub>IN</sub> = 5.5 V, V <sub>EN</sub> = 0.0 V |                    | 1.0  | 2.4                | μA   |  |

| V <sub>UVLO</sub>   | Input supply under-voltage                             | Rising                                           |                    | 2.5  |                    | V    |  |

|                     | lock-out thresholds                                    | Falling                                          |                    | 2.3  |                    | v    |  |

| V <sub>EN</sub>     | High Level Input Voltage                               | V <sub>IH</sub>                                  | 1.4                |      |                    | V    |  |

|                     | Low Level Input Voltage                                | V <sub>IL</sub>                                  |                    |      | 0.4                | v    |  |

| V <sub>MODE</sub>   | High Level Input Voltage                               | V <sub>IH</sub>                                  | 1.2                |      |                    | V    |  |

|                     | Low Level Input Voltage                                | V <sub>IL</sub>                                  | 0.4                |      |                    | v    |  |

| I <sub>LIM</sub>    | Peak switch current limit <sup>(3)</sup>               |                                                  | 2.1                | 2.7  |                    | А    |  |

| Fosc                | Internal oscillator frequency                          |                                                  | 2.5                | 3.0  | 3.2                | MHz  |  |

| T <sub>ON</sub>     | Minimum switch on-time <sup>(4)</sup>                  |                                                  |                    | 50   |                    | ns   |  |

| T <sub>ss</sub>     | Soft start time <sup>(4)</sup>                         |                                                  |                    | 800  |                    | μs   |  |

| R <sub>PG</sub>     | Power good flag pull-down<br>R <sub>dson</sub>         |                                                  | 40                 | 70   | 110                | Ω    |  |

| V <sub>PG1</sub>    | Power good flag, under-<br>voltage trip <sup>(5)</sup> | % of feedback voltage, rising                    |                    | 92%  |                    |      |  |

| V <sub>PG2</sub>    | Power good flag, under-<br>voltage trip <sup>(5)</sup> | % of feedback voltage, falling                   |                    | 88%  |                    |      |  |

| V <sub>PG3</sub>    | Power good flag, over-voltage trip <sup>(5)</sup>      | % of feedback voltage, rising                    |                    | 112% |                    |      |  |

| V <sub>PG4</sub>    | Power good flag, over-voltage trip <sup>(5)</sup>      | % of feedback voltage, falling                   |                    | 108% |                    |      |  |

| T <sub>SD</sub>     | Thermal shutdown <sup>(4)</sup>                        | Rising threshold                                 |                    | 159  |                    | °C   |  |

|                     | Thermal shutdown hysteresis <sup>(4)</sup>             |                                                  |                    | 15   |                    | °C   |  |

(1) MIN and MAX limits are 100% production tested at 25°C. Limits over the operating temperature range are verified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate Average Outgoing Quality Level (AOQL).

(2) Shutdown current includes leakage current of the switching transistors.

(3) This is the peak switch current limit measured with a slow current ramp. Due to inherent delays in the current limit comparator, the peak current limit measured at 3MHz will be larger.

(4) This parameter is not tested in production.

(5) See Power Good Flag Function for explanation of voltage levels.

#### 6.6 System Characteristics

The following specifications apply to the circuit found in Figure 16 with the appropriate modifications from Table 2. These parameters are not tested in production and represent typical performance only. Unless otherwise stated the following conditions apply:  $T_A = 25^{\circ}C$ .

|                    | PARAMETER                                                                 | TEST CONDITIONS                                                                                          | MIN TYP | MAX | UNIT     |  |

|--------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------|-----|----------|--|

|                    |                                                                           | $V_{OUT} = 1.2 \text{ V},$<br>$V_{IN} = 5 \text{ V}, I_{OUT} = 0 \text{ A to } 2 \text{ A}, \text{ PWM}$ | 0.4%    |     |          |  |

| Load<br>Regulation | Percent output voltage change for the given load current change           | $V_{OUT} = 1.8 V$<br>$V_{IN} = 5 V$ , $I_{OUT} = 0 A$ to 2 A, PWM                                        | 0.4%    |     |          |  |

|                    |                                                                           | $V_{OUT} = 3.3 V$<br>$V_{IN} = 5 V$ , $I_{OUT} = 0 A$ to 2 A, PWM                                        | 0.2%    |     |          |  |

|                    |                                                                           |                                                                                                          | 0.2%    |     |          |  |

| Line<br>Regulation | Percent output voltage change<br>for the given change in input<br>voltage | $V_{OUT}$ = 1.8 V $I_{OUT}$ = 2 A, $V_{IN}$ = 3 V to 5 V, PWM                                            | 0.15%   |     |          |  |

|                    | lonago                                                                    | $V_{OUT} = 3.3 V$<br>$I_{OUT} = 2 A, V_{IN} = 4 V \text{ to 5 V}, PWM$                                   | 0.18%   |     |          |  |

|                    |                                                                           | $V_{OUT} = 1.2 V$<br>$I_{OUT} = 1 A, V_{IN} = 5 V, PWM$                                                  | 3.3     |     |          |  |

| V <sub>R-PWM</sub> | Output voltage ripple in PWM                                              | $V_{OUT} = 1.8 V$<br>$I_{OUT} = 1 A, V_{IN} = 5 V, PWM$                                                  | 3.3     |     | mV pk-pk |  |

|                    |                                                                           | $V_{OUT} = 3.3V$<br>$I_{OUT} = 1 \text{ A}, V_{IN} = 5 \text{ V}, \text{PWM}$                            | 4.2     |     |          |  |

|                    |                                                                           | $V_{OUT} = 1.2V$<br>$I_{OUT} = 1 \text{ mA}, V_{IN} = 3 \text{ V}, \text{PFM}$                           | 22      |     |          |  |

| V <sub>R-PFM</sub> | Output voltage ripple in PFM                                              | $V_{OUT} = 1.8 V$<br>$I_{OUT} = 1 mA, V_{IN}=3 V, PFM$                                                   | 22      |     | mV pk-pk |  |

|                    |                                                                           | $V_{OUT} = 3.3 V$<br>$I_{OUT} = 1 mA, V_{IN} = 5 V, PFM$                                                 | 40      |     |          |  |

|                    | Output voltage deviation from<br>nominal due to a load current<br>step    | $V_{OUT}$ = 1.2 V $V_{IN}$ = 5 V, $I_{OUT}$ = 0 A to 2 A, Tr = Tf = 2 $\mu s,$ PWM                       | ±115    |     | mV       |  |

| Load<br>Transient  |                                                                           | $V_{OUT}$ = 1.8 V $V_{IN}$ = 5 V, $I_{OUT}$ = 0 A to 2 A, Tr = Tf = 2 $\mu s,$ PWM                       | ±100    |     |          |  |

|                    |                                                                           | $V_{OUT}$ = 3.3 V $V_{IN}$ = 5 V, $I_{OUT}$ = 0 A to 2 A, Tr = Tf = 2 $\mu s, PWM$                       | ±150    |     |          |  |

|                    |                                                                           | $V_{OUT}$ = 1.2V $I_{OUT}$ = 1 A, $V_{IN}$ = 3 V to 5 V, Tr = Tf = 50 $\mu s,$ PWM                       | 25      |     |          |  |

| Line<br>Transient  | Output voltage deviation due to<br>an input voltage step                  | $V_{OUT}$ = 1.8 V $I_{OUT}$ = 1 A, $V_{IN}$ = 3 V to 5 V, Tr = Tf = 50 $\mu s,$ PWM                      | 30      |     | mV pk-pk |  |

|                    |                                                                           | $V_{OUT}$ = 3.3 V $I_{OUT}$ = 1 A, $V_{IN}$ = 4 V to 5 V, Tr = Tf = 50 $\mu s,$ PWM                      | 20      |     |          |  |

|                    |                                                                           | V <sub>OUT</sub> = 1.2 V<br>V <sub>IN</sub> = 3 V                                                        | 87%     |     |          |  |

|                    | Peak efficiency                                                           | V <sub>OUT</sub> = 1.8 V<br>V <sub>IN</sub> = 3 V                                                        | 91%     |     |          |  |

|                    |                                                                           | V <sub>OUT</sub> = 3.3 V<br>V <sub>IN</sub> = 4.2 V                                                      | 94%     |     |          |  |

| η                  |                                                                           | V <sub>OUT</sub> = 1.2 V<br>V <sub>IN</sub> = 3 V, I <sub>OUT</sub> = 2 A                                | 74%     |     |          |  |

|                    | Full load efficiency                                                      | V <sub>OUT</sub> = 1.8 V<br>V <sub>IN</sub> = 3 V, I <sub>OUT</sub> = 2 A                                | 79%     |     |          |  |

|                    |                                                                           | V <sub>OUT</sub> = 3.3 V<br>V <sub>IN</sub> = 4.2 V, I <sub>OUT</sub> = 2 A                              | 89%     |     |          |  |

LMZ20502

SNVS852D-JUNE 2012-REVISED AUGUST 2018

Texas Instruments

www.ti.com

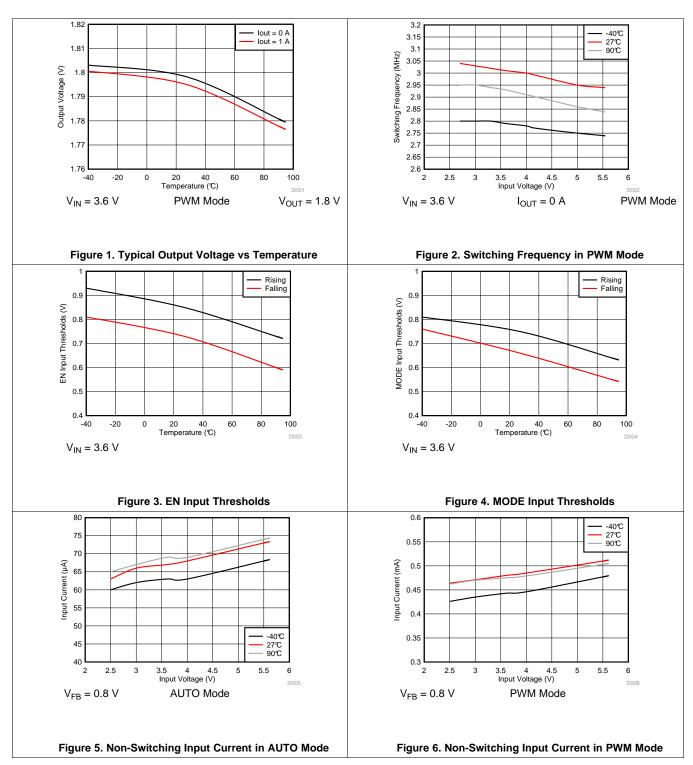

#### 6.7 Typical Characteristics

Unless otherwise specified the following conditions apply:  $V_{IN}$  = 3.6 V,  $T_A$  = 25°C.

### 7 Detailed Description

#### 7.1 Overview

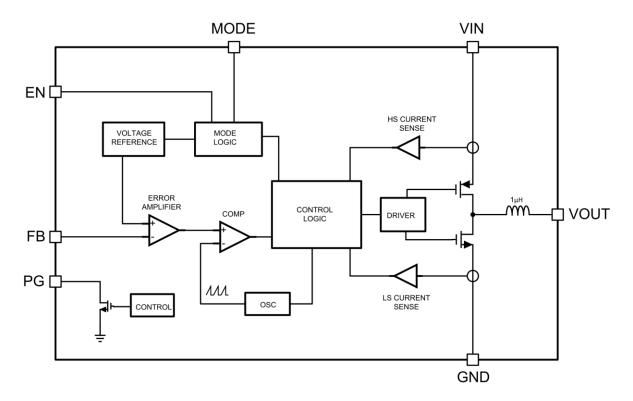

The LMZ20502 Nano Module is a voltage mode buck regulator with an integrated inductor. Input voltage feedforward is used to compensate for loop gain variation with input voltage. Two operating modes allow the user to tailor the regulator to their specific requirements. In forced PWM mode, the regulator operates as a full synchronous device with a 3 MHz (typ.) switching frequency and very low output voltage ripple. In AUTO mode, the regulator moves into PFM when the load current drops below the mode change threshold (see *Application Curves*). In PFM, the device regulates the output voltage between wider ripple limits than in PWM. This results in much smaller supply current than in PWM, at light loads and high efficiency. A simplified block diagram is shown in *Functional Block Diagram*.

### 7.2 Functional Block Diagram

#### 7.3 Feature Description

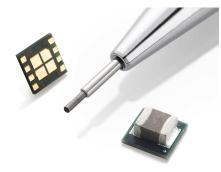

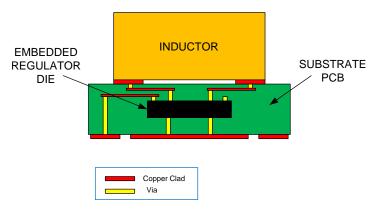

#### 7.3.1 Nano Scale Package

The LMZ20502 incorporates world-class package technology to provide a 2 A power supply with a total volume of only 21 mm<sup>3</sup> (excluding external components). All that is required for a complete power supply is the addition of feed-back resistors to set the output voltage and the input and output filter capacitors. Figure 7 and Figure 8 show the LMZ20502 package. The regulator die is embedded into a PCB substrate while the power inductor is mounted on top. Vias and copper clad are used to make the connections to the die, inductor and the external components. This package is MSL3 compliant.

#### **Feature Description (continued)**

Figure 7. Package Photo

Figure 8. Package Side View Drawing

#### 7.3.2 Internal Synchronous Rectifier

The LMZ20502 uses an internal NMOS FET as a synchronous rectifier to minimize switch voltage drop and increase efficiency. The NMOS is designed to conduct through its body diode during switch dead time. This dead time is imposed to prevent supply current "shoot-through".

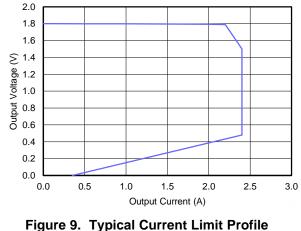

#### 7.3.3 Current Limit Protection

The LMZ20502 incorporates cycle-by-cycle peak current limit on both the high and low side MOSFETs. This feature limits the output current in case the output is overloaded. During the overload, the peak inductor current is limited to that value found in the *Electrical Characteristics* table under the heading of "I<sub>LIM</sub>".

In addition to current limit, a short circuit protection mode is also implemented. When the feedback voltage is brought down to less than 300 mV, but greater than 150 mV, by a short circuit, the synchronous rectifier is turned off. This provides more voltage across the inductor to help maintain the required volt-second balance. If a "harder" short brings the feedback voltage to below 150 mV, the current limit and switching frequency are both reduced to about  $\frac{1}{2}$  of the nominal values. In addition, when the current limit is tripped, the device stops switching for about 85 µs. At the end of the time-out, switching resumes and the cycle repeats until the short is removed.

The effect of both overload and short circuit protection can be seen in Figure 9. This graph demonstrates that the device will supply slightly more than 2 A to the load when in overload and much less current during fold-back mode. This is typical behavior for any regulator with this type of current limit protection.

#### **Feature Description (continued)**

$V_{\rm IN} = 5 \text{ V}, \text{ } V_{\rm OUT} = 1.8 \text{ V}$

#### 7.3.4 Start-Up

Start-up and shutdown of the LMZ20502 is controlled by the EN input. The characteristics of this input are found in the *Electrical Characteristics* table. A valid input voltage must be present on VIN before the enable control is asserted. The maximum voltage on the EN pin is 5.5 V or  $V_{IN}$ , whichever is smaller. Do not allow this input to float.

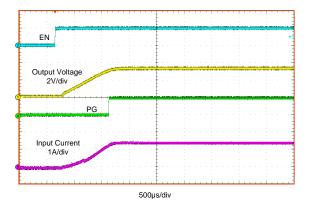

The LMZ20502 features a current limit based soft-start, that prevents large inrush currents and output overshoots as the regulator is starting up. The peak inductor current is stepped-up in a staircase fashion during the soft start period. A typical start-up event is shown in Figure 10:

Figure 10. Typical Start-Up Waveforms,  $V_{IN} = 5 V$ ,  $V_{OUT} = 3.3 V$ ,  $I_{OUT} = 1 A$

#### 7.3.5 Dropout Behavior

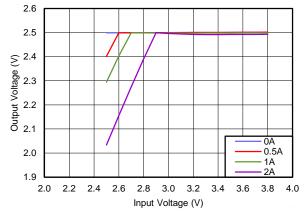

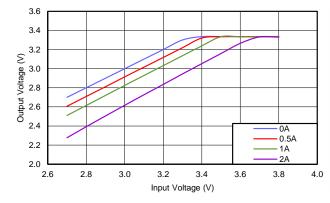

When the input voltage is close to the output voltage the regulator will operate at very large duty cycles. Normal time delays of the internal circuits prevents the attainment of controlled duty cycles near 100%. In this condition the LMZ20502 will skip switching cycles in order to maintain regulation with the highest possible input-to-output ratio. Some increase in output voltage ripple may appear as the regulator skips cycles. As the input voltage gets closer to the output voltage, the regulator will eventually reach 100% duty cycle, with the high side switch turned on. The output will then follow the input voltage minus the drop across the high side switch and inductor resistance. Figure 11 and Figure 12 show typical drop-out behavior for output voltages of 2.5 V and 3.3 V.

TEXAS INSTRUMENTS

www.ti.com

#### Feature Description (continued)

Since the internal gate drive levels of the LMZ20502 are dependent on input voltage, the  $R_{dson}$  of the power FETs will increase at low input voltages. This will result in degraded efficiency at output currents of greater than 1 A and input voltages below about 2.9 V. Also, combinations of low input voltage and high output voltage increases the effective switch duty cycle which may result in increased output voltage ripple.

Figure 11. Typical Drop-Out Behavior, V<sub>OUT</sub> = 2.5 V

Figure 12. Typical Drop-Out Behavior, V<sub>OUT</sub> = 3.3 V

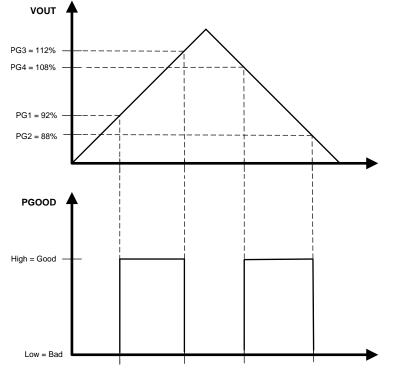

### 7.3.6 Power Good Flag Function

The operation of the power good flag function is described in the diagram shown in Figure 13.

#### LMZ20502 SNVS852D – JUNE 2012–REVISED AUGUST 2018

#### Feature Description (continued)

Figure 13. Typical Power Good Flag Operation

This output consists of an open drain NMOS with an  $R_{dson}$  of about 70  $\Omega$ . When used, the power good flag should be connected to a logic supply through a pull-up resistor. It can also be pulled-up to either  $V_{IN}$  or  $V_{OUT}$ , through an appropriate resistor, as desired. If this function is not needed, the PG output should be left floating. The current through this flag pin should be limited to less than 4 mA. A pull-up resistor of  $\geq 1.5 \ k\Omega$  will satisfy this requirement. When the EN input is pulled low, the PG flag output will also be forced low, assuming a valid input voltage is present at the VIN pin.

#### 7.3.7 Thermal Shutdown

The LMZ20502 incorporates a thermal shutdown feature to protect the device from excessive die temperatures. The device will stop switching when the internal die temperature reaches about 159°C. Switching will resume when the die temperature drops to about 144°C.

#### 7.4 Device Functional Modes

Please refer to Table 1 and the following paragraphs for a detailed description of the functional modes of the LMZ20502. These modes are controlled by the MODE input as shown in Table 1. The maximum voltage on the MODE pin is 5.5 V or  $V_{IN}$ , whichever is smaller. This input must not be allowed to float.

| MODE PIN VOLTAGE | OPERATION                                                                                                                                                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| > 1.2 V          | Forced PWM: The regulator operates in constant frequency, PWM mode for all loads from<br>no-load to full load; no diode emulation is used.                                                                        |

| < 0.4 V          | AUTO Mode: The regulator operates in constant frequency mode for loads greater than the mode change threshold. For loads less than the mode change threshold, the regulator operates in PFM with diode emulation. |

#### **Table 1. Mode Selection**

#### LMZ20502

SNVS852D-JUNE 2012-REVISED AUGUST 2018

#### 7.4.1 PWM Operation

In forced PWM mode, the converter operates as a constant frequency voltage mode regulator with input voltage feed-forward. This provides excellent line and load regulation and low output voltage ripple. This operation is maintained, even at no-load, by allowing the inductor current to reverse its normal direction. While in PWM mode, the output voltage is regulated by switching at a constant frequency and modulating the duty cycle to control the power to the load. This mode trades off reduced light load efficiency for low output voltage ripple and constant switching frequency. In this mode, a negative current limit of about 750mA is imposed to prevent damage to the regulator power FETs.

#### 7.4.2 PFM Operation

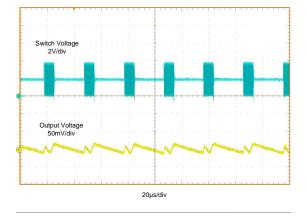

When in AUTO mode, and at light loads, the device enters PFM. The regulator estimates the load current by measuring both the high side and low side switch currents. This estimate is only approximate, and the exact load current threshold, to trigger PFM, can vary greatly with input and output voltage. The *Application Curves* show mode change thresholds for several typical operating points. When the regulator detects this threshold, the reference voltage is increased by approximately 10 mV. This causes the output voltage to rise to meet the new regulation point. When this point is reached, the converter stops switching and much of the internal circuitry is shut off, while the reference is returned to the PWM value. This saves supply current while the output voltage naturally starts to fall under the influence of the load current. When the output voltage reaches the PWM regulation point, switching is again started and the reference voltage is again increased by about 10 mV; thus starting the next cycle. Typical waveforms are shown in Figure 14:

Figure 14. Typical PFM Mode Waveforms: V<sub>IN</sub> = 3.6 V,  $V_{OUT}$  = 1.8 V,  $I_{OUT}$  = 10 mA

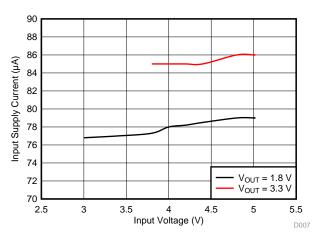

Figure 15. Typical No Load Input Supply Current

The actual output voltage ripple will depend on the feedback divider ratio and on the delay in the PFM comparator. The frequency of the PFM "bursts" will depend on the input voltage, output voltage, load and output capacitor. Within each "burst" the device switches at 3 MHz (typ.). If the load current increases above the threshold, normal PWM operation is resumed. This mode provides high light load efficiency by reducing the amount of supply current required to regulate the output at small load currents. This mode trades off very good light load efficiency for larger output voltage ripple and variable switching frequency. An example of the typical input supply current, while regulating with no load, is shown in Figure 15.

Because of normal part-to-part variation, the LMZ20502 may not switch into PFM mode at high input voltages. This may be seen with output voltages of about 1.2 V and below, at input voltages of about 4.2 V and above.

### 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The LMZ20502 is a step down DC-to-DC regulator. It is typically used to convert a higher DC voltage to a lower DC voltage with a maximum output current of 2 A. The following design procedure can be used to select components for the LMZ20502. Alternately, the WEBENCH design tool may be used to generate a complete design. WEBENCH utilizes an iterative design procedure and has access to a comprehensive database of components. This allows the tool to create an optimized design and allows the user to experiment with various design options.

LMZ20502 SNVS852D – JUNE 2012–REVISED AUGUST 2018

#### 8.2 Typical Application

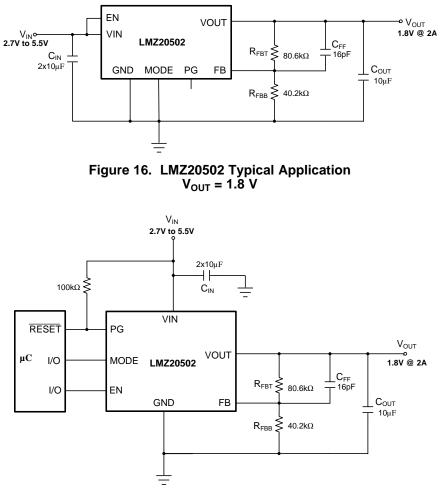

Figure 16 shows the minimum required application circuit, set up for a 1.8 V output. Figure 17 shows a full featured application circuit. Please refer to Figure 16 and Figure 17 during the following design procedures.

Figure 17. LMZ20502 Full Featured Application

#### **Typical Application (continued)**

#### 8.2.1 Detailed Design Procedure

#### 8.2.1.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMZ20502 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- · Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

Please refer to Table 2 while following the detailed design procedure. This procedure applies to both Figure 16 and to Figure 17. Also, the *Application Curves* apply to both schematics.

| V <sub>OUT</sub> (V) | $R_{FBB}$ (k $\Omega$ ) | $R_{FBT}$ (k $\Omega$ ) | C <sub>OUT</sub> (μF) | EFFECTIVE C <sub>OUT</sub> (µF) <sup>(2)</sup> | C <sub>FF</sub> (pF) | C <sub>IN</sub> (μF) | EFFECTIVE C <sub>IN</sub> (µF) <sup>(2)</sup> |

|----------------------|-------------------------|-------------------------|-----------------------|------------------------------------------------|----------------------|----------------------|-----------------------------------------------|

| 0.8                  | 121                     | 40.2                    | 2 x 10                | 18 µF                                          | 39                   | 2 x 10               | 14                                            |

| 1.2                  | 30.1                    | 30.1                    | 10                    | 8.8 µF                                         | 20                   | 2 x 10               | 14                                            |

| 1.8                  | 40.2                    | 80.6                    | 10                    | 8.4 µF                                         | 16                   | 2 x 10               | 14                                            |

| 2.5                  | 47.5                    | 150                     | 10                    | 7.8 µF                                         | 12                   | 2 x 10               | 14                                            |

| 3.3                  | 53.2                    | 237                     | 10                    | 7.1 µF                                         | 82                   | 2 x 10               | 14                                            |

| 3.6                  | 53.2                    | 267                     | 10                    | 6.8 µF                                         | 82                   | 2 x 10               | 14                                            |

Table 2. Recommended Component Values<sup>(1)</sup>

(1)  $C_{IN} = C_{OUT} = 10 \ \mu$ F, 16 V, 0805, X7R, Samsung CL21B106KOQNNNE.  $C_{OUT}$  measured at V<sub>OUT</sub>;  $C_{IN}$  measured at 3.3 V.

(2) The effective value takes into account the capacitor voltage coefficient.

#### 8.2.1.2 Setting The Output Voltage

The LMZ20502 regulates its feedback voltage to 0.6 V (typ). A feedback divider, shown in Figure 16, is used to set the desired output voltage. Equation 1 can be used to select  $R_{FBB}$ .

$$\mathbf{R}_{\rm FBB} = \frac{0.6}{\left(\mathbf{V}_{\rm OUT} - 0.6\right)} \cdot \mathbf{R}_{\rm FBT} \tag{1}$$

For best results,  $R_{FBT}$  should be chosen between 30 k $\Omega$  and 300 k $\Omega$ . See Table 2 for recommended values for typical output voltages.

#### 8.2.1.3 Output and Feed-Forward Capacitors

The LMZ20502 is designed to work with low ESR ceramic capacitors. The **effective** value of these capacitors is defined as the actual capacitance under voltage bias and temperature. All ceramic capacitors have large voltage coefficients, in addition to normal tolerances and temperature coefficients. Under D.C. bias, the capacitance value drops considerably. Larger case sizes and/or higher voltage capacitors are better in this regard. To help mitigate these effects, multiple small capacitors can be used in parallel to bring the minimum **effective** capacitance up to the desired value. This can also ease the RMS current requirements on a single capacitor. Typically, 10 V, X5R, 0805 capacitors are adequate for the output, while 16-V caps may be used on the input. Some recommended component values are provided in Table 2. Also, shown are the measured values of **effective** input and output capacitance for the given capacitor. If smaller values of output capacitance are used, C<sub>FF</sub> must be adjusted to give good phase margin. In any case, load transient response will be compromised with lower values of output capacitance. Values much lower than those found in Table 2 should be avoided.

Copyright © 2012–2018, Texas Instruments Incorporated

LMZ20502

SNVS852D - JUNE 2012 - REVISED AUGUST 2018

Copyright © 2012–2018, Texas Instruments Incorporated

In practice, the output capacitor and C<sub>FF</sub>, are adjusted for the best transient response and highest loop phase margin. Load transient testing and Bode plots are the best way to validate any given design. Application report SLVA289 should prove helpful when optimizing the feed-forward capacitor. Also, SNVA364 details a simple method of creating a Bode plot with basic laboratory equipment. The values of C<sub>FF</sub> found in Table 2 provide a good starting point.

A careful study of the temperature and bias voltage variation of any candidate ceramic capacitor should be made in order to ensure that the minimum values of effective capacitance are provided. The best way to obtain an optimum design is to use the Texas Instruments WEBENCH tool.

The maximum value of total output capacitance should be limited to between 100 µF and 200 µF. Large values of output capacitance can prevent the regulator from starting-up correctly and adversely affect the loop stability. If values in the range given above, or larger, are to be used, then a careful study of start-up at full load and loop stability must be performed.

### 8.2.1.4 Input Capacitors

The ceramic input capacitors provide a low impedance source to the regulator in addition to supplying ripple current and isolating switching noise from other circuits. An effective value of at least 14 µF is normally sufficient for the input capacitor. If the main input capacitor(s) can not be placed close to the module, then a small 10 nF to 100 nF capacitor should be placed directly at the module, across the supply and ground pins.

Many times it is desirable to use an electrolytic capacitor on the input, in parallel with the ceramics. This is especially true if long leads/traces are used to connect the input supply to the regulator. The moderate ESR of this capacitor can help damp any ringing on the input supply caused by long power leads. This method can also help to reduce voltage spikes that may exceed the maximum input voltage rating of the LMZ20502. The use of this additional capacitor will also help with voltage dips caused by input supplies with unusually high impedance.

Most of the switching current passes through the input ceramic capacitor(s). The approximate RMS value of this current can be calculated with Equation 2 and should be checked against the manufactures maximum ratings.

$$I_{\rm RMS} \approx \frac{I_{\rm OUT}}{2}$$

(2)

### 8.2.1.5 Maximum Ambient Temperature

Submit Documentation Feedback

18

As with any power conversion device, the LMZ20502 will dissipate internal power while operating. The effect of this power dissipation is to raise the internal temperature of the converter, above ambient. The internal die temperature is a function of the ambient temperature, the power loss and the effective thermal resistance  $R_{\theta,IA}$  of the device and PCB combination. The maximum internal die temperature for the LMZ20502 is 125°C, thus establishing a limit on the maximum device power dissipation and therefore load current at high ambient temperatures. Equation 3 shows the relationships between the important parameters.

$$I_{OUT} = \frac{(T_J - T_A)}{R_{\theta JA}} \cdot \frac{\eta}{(1 - \eta)} \cdot \frac{1}{V_{OUT}}$$

(3)

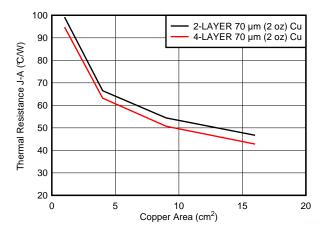

It is easy to see that larger ambient temperatures and larger values of  $R_{\theta JA}$  will reduce the maximum available output current. As stated in SPRA953, the values given in the Thermal Information table are not valid for design purposes and must not be used to estimate the thermal performance of the application. The values reported in that table were measured under a specific set of conditions that never obtain in an actual application. The effective R<sub>0JA</sub> is a critical parameter and depends on many factors such as power dissipation, air temperature, PCB area, copper heatsink area, air flow, and adjacent component placement. The resources found in Table 3 can be used as a guide to estimate the  $R_{\theta JA}$  for a given application environment. A typical example of  $R_{\theta JA}$ versus copper board area is shown in Figure 18. The copper area in this graph is that for each layer; the inner layers are 1 oz. (35µm). An R<sub>BJA</sub> of 44°C/W is the approximate value for the LMZ20502 evaluation board. The efficiency found in the equation, η, should be taken at the elevated ambient temperature. For the LMZ20502 the efficiency is about two to three percent lower at high temperatures. Therefore, a slightly lower value than the typical efficiency can be used in the calculation. In this way Equation 3 can be used to estimate the maximum output current for a given ambient, or to estimate the maximum ambient for a given load current.

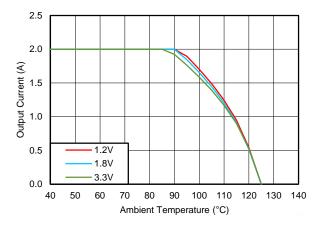

A typical curve of maximum load current vs. ambient temperature is shown in Figure 19. This graph assumes a  $R_{\theta,JA}$  of 44°C/W and an input voltage of 5 V.

2)

Figure 18.  $R_{\theta JA}$  versus Copper Board Area

Figure 19. Maximum Output Current Vs. Ambient Temperature,  $R_{\theta JA} = 44^{\circ}C/W$ ,  $V_{IN} = 5 V$

#### 8.2.1.6 Options

The circuit in Figure 17 highlights the use of the features of the LMZ20502. The PG output is open drain, and requires a pull-up resistor to a logic supply that is commensurate with the system logic voltage levels. If a reset function is not needed, the PG pin should be left open. The EN and MODE inputs are digital inputs, requiring only simple logic levels for proper operation. If the system does not need to control these features, the inputs should be connected to either VIN or GND, as appropriate. Please see *Feature Description* for details.

LMZ20502 SNVS852D – JUNE 2012–REVISED AUGUST 2018

www.ti.com

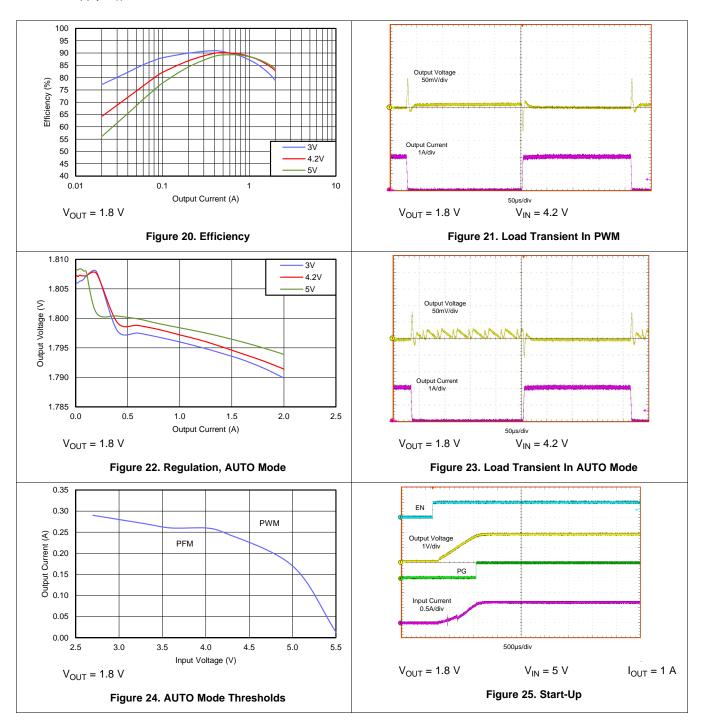

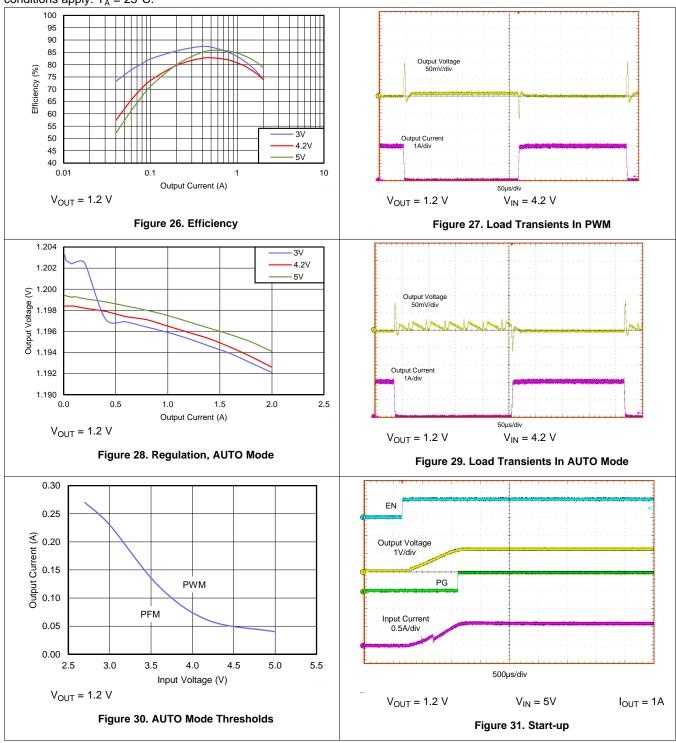

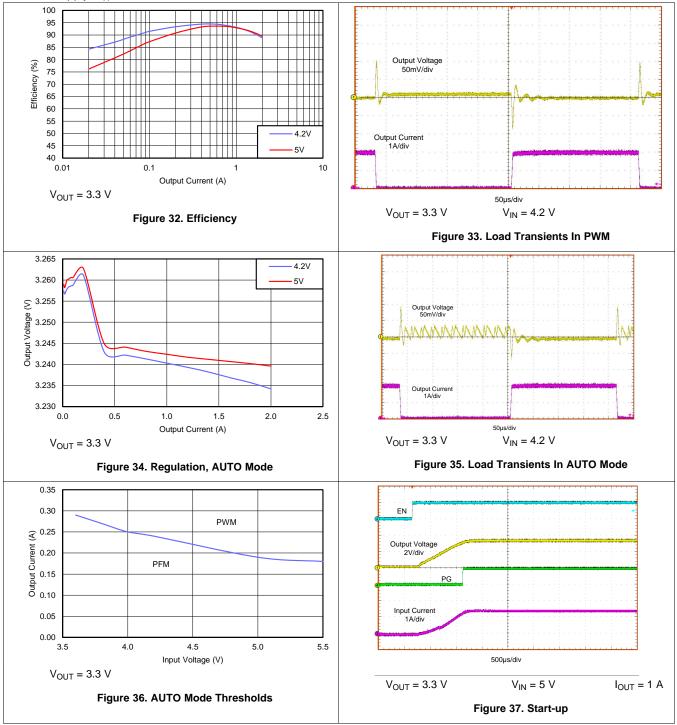

#### 8.2.2 Application Curves

The following specifications apply to the circuit found in Figure 16 or Figure 17 with the appropriate modifications from Table 2. These parameters are not tested and represent typical performance only. Unless otherwise stated the following conditions apply:  $T_A = 25^{\circ}C$ .

The following specifications apply to the circuit found in Figure 16 or Figure 17 with the appropriate modifications from Table 2. These parameters are not tested and represent typical performance only. Unless otherwise stated the following conditions apply:  $T_A = 25^{\circ}C$ .

STRUMENTS

EXAS

# The following specifications apply to the circuit found in Figure 16 or Figure 17 with the appropriate modifications from Table 2. These parameters are not tested and represent typical performance only. Unless otherwise stated the following conditions apply: $T_A = 25^{\circ}C$ .

#### 8.3 Do's and Don'ts

- **Don't:** Exceed the *Absolute Maximum Ratings*.

- Don't: Exceed the ESD Ratings .

- **Don't:** Exceed the *Recommended Operating Conditions*.

- **Don't:** Allow the EN or MODE input to float.

- **Don't:** Allow the voltage on the EN or MODE input to exceed the voltage on the VIN pin.

- **Don't:** Allow the output voltage to exceed the input voltage.

- Don't: Use the thermal data given in the Thermal Information table to design your application.

- Do: Follow all of the guidelines and/or suggestions found in this data sheet, before committing your design to

production. TI Application Engineers are ready to help critique your design and PCB layout to help make your

project a success.

- **Do:** Refer to the helpful documents found in Table 3 and Table 4.

### 9 Power Supply Recommendations

The characteristics of the input supply must be compatible with the *Absolute Maximum Ratings* and *Recommended Operating Conditions* found in this data sheet. In addition, the input supply must be capable of delivering the required input current to the loaded regulator. The average input current can be estimated with Equation 4

$$I_{IN} = \frac{V_{OUT} \cdot I_{OUT}}{V_{IN} \cdot \eta}$$

(4)

LMZ20502

SNVS852D - JUNE 2012 - REVISED AUGUST 2018

If the regulator is connected to the input supply through long wires or PCB traces, special care is required to achieve good performance. The parasitic inductance and resistance of the input cables can have an adverse effect on the operation of the regulator. The parasitic inductance, in combination with the low ESR ceramic input capacitors, can form an under-damped resonant circuit. This circuit may cause over-voltage transients at the VIN pin, each time the input supply is cycled on and off. The parasitic resistance will cause the voltage at the VIN pin to dip when the load on the regulator is switched on, or exhibits a transient. If the regulator is operating close to the minimum input voltage, this dip may cause the device to shutdown and/or reset. The best way to solve these kinds of issues is to reduce the distance from the input supply to the regulator and/or use an aluminum or tantalum input capacitor in parallel with the ceramics. The moderate ESR of these types of capacitors will help to damp the input resonant circuit and reduce any voltage overshoots. A value in the range of 20  $\mu$ F to 100  $\mu$ F is usually sufficient to provide input damping and help to hold the input voltage steady during large load transients.

Sometimes, for other system considerations, an input filter is used in front of the regulator module. This can lead to instability, as well as some of the effects mentioned above, unless it is designed carefully. The following user guide provides helpful suggestions when designing an input filter for any switching regulator: SNVA489.

In some cases a Transient Voltage Suppressor (TVS) is used on the input of regulators. One class of this device has a "snap-back" V-I characteristic (thyristor type). The use of a device with this type of characteristic is not recommend. When the TVS "fires", the clamping voltage drops to a very low value. If this holding voltage is less than the output voltage of the regulator, the output capacitors will be discharged through the regulator back to the input. This uncontrolled current flow could damage the regulator.

### 10 Layout

#### 10.1 Layout Guidelines

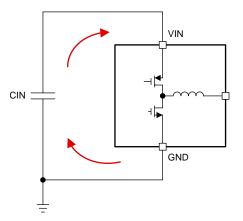

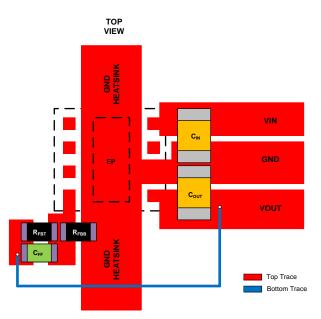

The PCB layout of any DC/DC converter is critical to the optimal performance of the design. Bad PCB layout can disrupt the operation of an otherwise good schematic design. Even if the converter regulates correctly, bad PCB layout can mean the difference between a robust design and one that cannot be mass produced. Furthermore, the EMI performance of the regulator is dependent on the PCB layout, to a great extent. In a buck converter, the most critical PCB feature is the loop formed by the input capacitor and the module ground, as shown in Figure 38. This loop carries fast transient currents that can cause large transient voltages when reacting with the trace inductance. These unwanted transient voltages will disrupt the proper operation of the converter. Because of this, the traces in this loop should be wide and short, and the loop area as small as possible to reduce the parasitic inductance. Figure 39 shows a recommended layout for the critical components of the LMZ20502; the top side metal is shown in red. This PCB layout is a good guide for any specific application. The following important guidelines should also be followed:

- 1. Place the input capacitor CIN as close as possible to the VIN and GND terminals. VIN (pin 8) and GND (pin 6) are on the same side of the module, simplifying the input capacitor placement.

- Place the feedback divider as close as possible to the FB pin on the module. The divider and C<sub>FF</sub> should be close to the module, while the length of the trace from VOUT to the divider can be somewhat longer. However, this latter trace should not be routed near any noise sources that can capacitively couple to the FB input.

- 3. Connect the EP pad to the GND plane. This pad acts as a heat-sink connection and a ground connection for the module. It must be solidly connected to a ground plane. The integrity of this connection has a direct bearing on the effective  $R_{\theta JA}$ .

- 4. Provide enough PCB area for proper heat-sinking. As stated in the Maximum Ambient Temperature section, enough copper area must be used to provide a low R<sub>θJA</sub>, commensurate with the maximum load current and ambient temperature. The top and bottom PCB layers should be made with two ounce copper; and no less than one ounce.

- 5. The resources in Table 4 provide additional important guidelines

Figure 38. Current Loops With Fast Transient Currents

#### 10.2 Layout Example

Figure 39. Example PCB Layout

#### **10.3 Soldering Information**

Proper operation of the LMZ20502 requires that it be correctly soldered to the PCB. This is especially true regarding the EP. This pad acts as a quiet ground reference for the device and a heatsink connection. Use the following recommendations when utilizing machine placement of the device:

- Dimension of area for pick-up: 2 mm x 2.5 mm.

- Use a nozzle size of less than 1.3 mm in diameter, so that the head does not touch the outer area of the package.

- Use a soft tip pick-and-place head.

- Add 0.05 mm to the component thickness so that the device will be released 0.05 mm into the solder paste without putting pressure or splashing the solder paste.

- Slow the pick arm when picking the part from the tape and reel carrier and when depositing the device on the board.

- If the machine releases the component by force, use the minimum force and no more than 3 N.

- For PCBs with surface mount components on both sides, it is suggested to put the LMZ20502 on the top side. In case the application requires bottom side placement, a re-flow fixture may be required to protect the module during the second reflow.

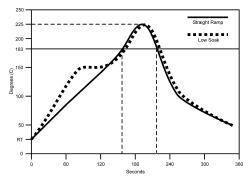

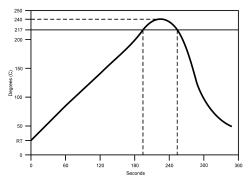

In addition, please follow the important guidelines found in: SNOA401. The curves in Figure 40 and Figure 41 show typical soldering temperature profiles.

### **Soldering Information (continued)**

Figure 40. Typical Re-flow Profile Eutectic (63sn/37pb) Solder Paste

Figure 41. Typical Re-flow Profile Lead-Free (Sca305 Or Sac405) Solder Paste

### **11** Device and Documentation Support

#### **11.1 Device Support**

#### 11.1.1 Third-Party Products Disclaimer

TI'S PUBLICATION OF INFORMATION REGARDING THIRD-PARTY PRODUCTS OR SERVICES DOES NOT CONSTITUTE AN ENDORSEMENT REGARDING THE SUITABILITY OF SUCH PRODUCTS OR SERVICES OR A WARRANTY, REPRESENTATION OR ENDORSEMENT OF SUCH PRODUCTS OR SERVICES, EITHER ALONE OR IN COMBINATION WITH ANY TI PRODUCT OR SERVICE.

#### 11.1.2 Development Support

#### 11.1.2.1 Custom Design With WEBENCH® Tools

Click here to create a custom design using the LMZ20502 device with the WEBENCH® Power Designer.

- 1. Start by entering the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), and output current ( $I_{OUT}$ ) requirements.

- 2. Optimize the design for key parameters such as efficiency, footprint, and cost using the optimizer dial.

- 3. Compare the generated design with other possible solutions from Texas Instruments.

The WEBENCH Power Designer provides a customized schematic along with a list of materials with real-time pricing and component availability.

In most cases, these actions are available:

- Run electrical simulations to see important waveforms and circuit performance

- Run thermal simulations to understand board thermal performance

- Export customized schematic and layout into popular CAD formats

- Print PDF reports for the design, and share the design with colleagues

Get more information about WEBENCH tools at www.ti.com/WEBENCH.

#### 11.1.3 Documentation Support

#### 11.1.3.1 Related Documentation

#### Table 3. Resources For Estimating $R_{\theta JA}$

| TITLE                                                                                              | LINK    |

|----------------------------------------------------------------------------------------------------|---------|

| AN-2020 Thermal Design By Insight, Not<br>Hindsight                                                | SNVA419 |

| AN-2026 The Effect of PCB Design on the<br>Thermal Performance of SIMPLE<br>SWITCHER Power Modules | SNVA424 |

| AN-1520 A Guide to Board Layout for Best<br>Thermal Resistance for Exposed Packages                | SNVA183 |

| AN-1187 Leadless Lead-frame Package<br>(LLP)                                                       | SNOA401 |

| SPRA953B Semiconductor and IC Package<br>Thermal Metrics                                           | SPRA953 |

TEXAS INSTRUMENTS

www.ti.com

#### Table 4. PCB Layout Resources

| TITLE                                                     | LINK    |

|-----------------------------------------------------------|---------|

| AN-1149 Layout Guidelines for Switching<br>Power Supplies | SNVA021 |

| AN-1229 SIMPLE SWITCHER PCB Layout<br>Guidelines          | SNVA054 |

| Constructing Your Power Supply- Layout<br>Considerations  | SLUP230 |

#### **11.2 Receiving Notification of Documentation Updates**

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### **11.3 Community Resources**

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 11.4 Trademarks

WebTherm, E2E are trademarks of Texas Instruments. WEBENCH is a registered trademark of Texas Instruments. All other trademarks are the property of their respective owners.

#### 11.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

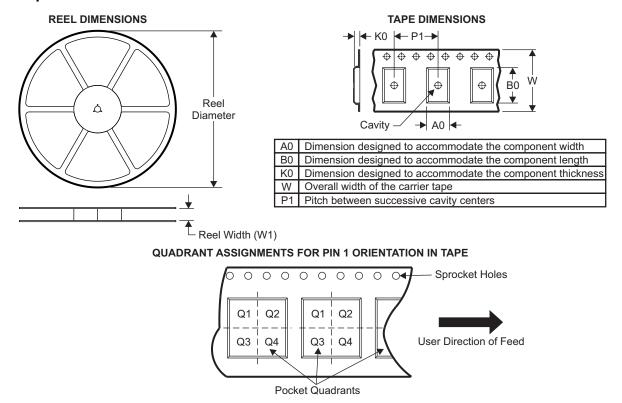

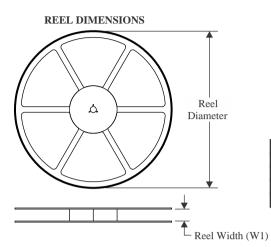

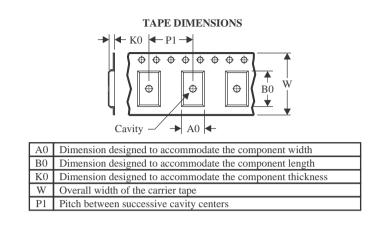

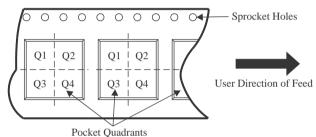

#### 12.1 Tape and Reel Information

| Device       | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMZ20502SILR | uSiP            | SIL                | 8    | 3000 | 330.0                    | 12.4                     | 3.75       | 3.75       | 2.2        | 8.0        | 12.0      | Q2               |

| LMZ20502SILT | uSiP            | SIL                | 8    | 250  | 178.0                    | 13.2                     | 3.75       | 3.75       | 2.2        | 8.0        | 12.0      | Q2               |

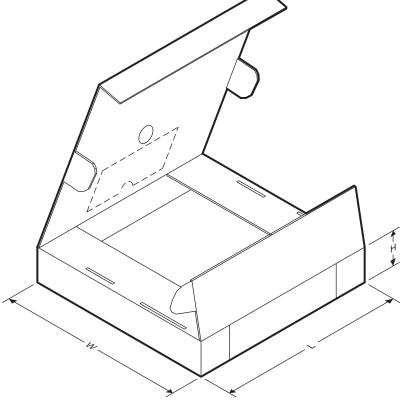

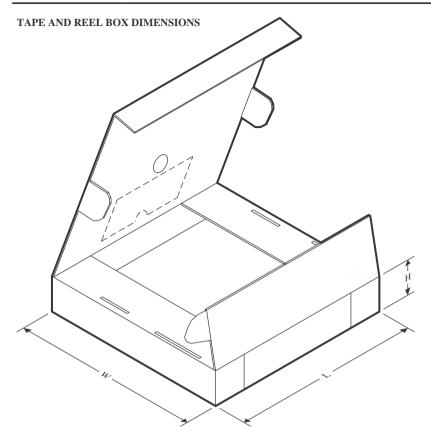

#### TAPE AND REEL BOX DIMENSIONS

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMZ20502SILR | uSiP         | SIL             | 8    | 3000 | 383.0       | 353.0      | 58.0        |

| LMZ20502SILT | uSiP         | SIL             | 8    | 250  | 223.0       | 194.0      | 35.0        |

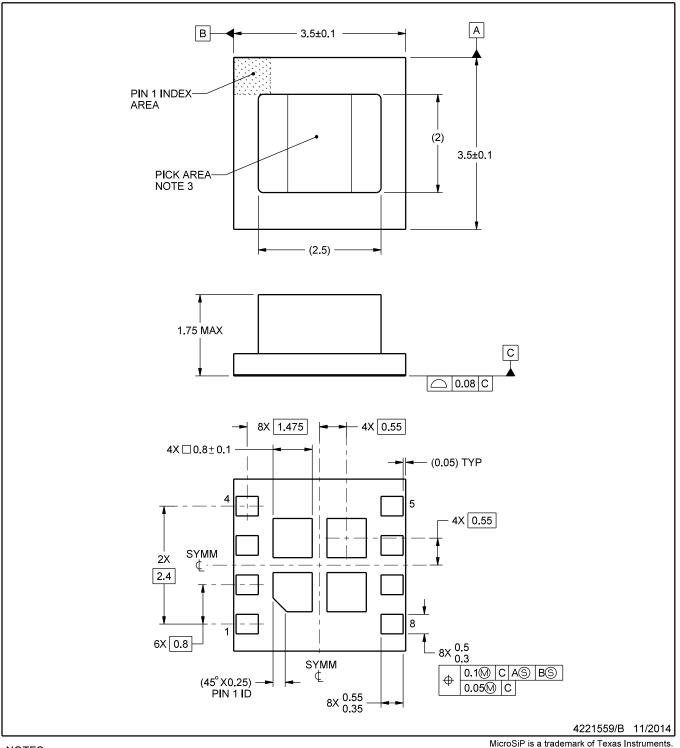

# **SIL0008F**

# **PACKAGE OUTLINE**

# MicroSiP<sup>™</sup>- 1.75 mm max height

MICRO SYSTEM IN PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice. 3. Pick and place nozzle  $\emptyset$  1.3 mm or smaller recommended.

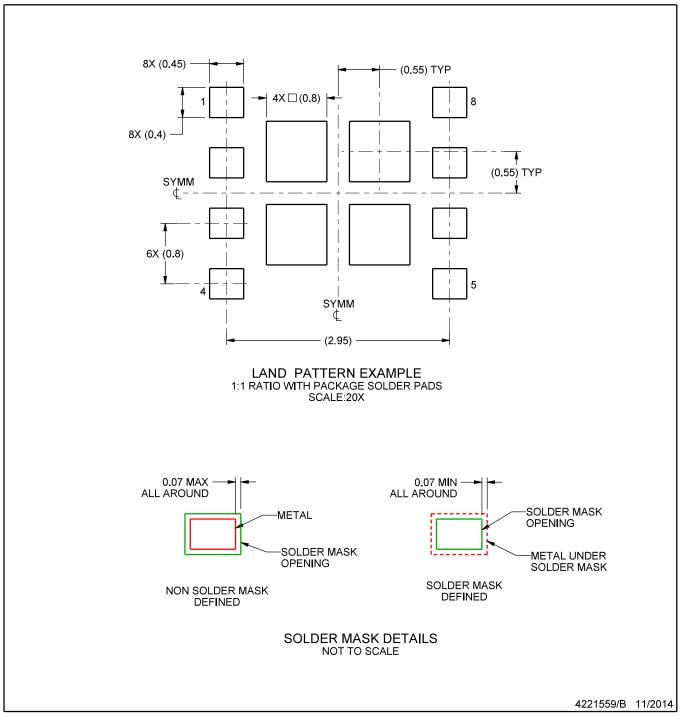

# SIL0008F

# **EXAMPLE BOARD LAYOUT**

### MicroSiP<sup>™</sup>- 1.75 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

# SIL0008F

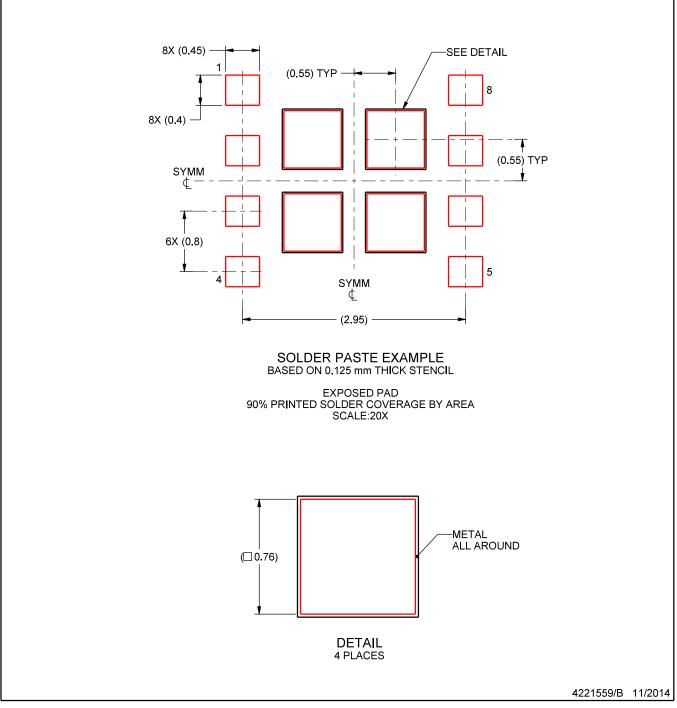

# **EXAMPLE STENCIL DESIGN**

# MicroSiP<sup>™</sup>- 1.75 mm max height

MICRO SYSTEM IN PACKAGE

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/         | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|---------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material | Peak reflow         |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                 |              |              |

| LMZ20502SILR          | Active | Production    | uSiP (SIL)   8 | 3000   LARGE T&R      | Yes  | NIAU          | Level-3-260C-168 HR | -40 to 125   | 0502 7543 EC |

| LMZ20502SILR.A        | Active | Production    | uSiP (SIL)   8 | 3000   LARGE T&R      | Yes  | NIAU          | Level-3-260C-168 HR | -40 to 125   | 0502 7543 EC |

| LMZ20502SILR.B        | Active | Production    | uSiP (SIL)   8 | 3000   LARGE T&R      | -    | Call TI       | Call TI             | -40 to 125   |              |

| LMZ20502SILT          | Active | Production    | uSiP (SIL)   8 | 250   SMALL T&R       | Yes  | NIAU          | Level-3-260C-168 HR | -40 to 125   | 0502 7543 EC |

| LMZ20502SILT.A        | Active | Production    | uSiP (SIL)   8 | 250   SMALL T&R       | Yes  | NIAU          | Level-3-260C-168 HR | -40 to 125   | 0502 7543 EC |

| LMZ20502SILT.B        | Active | Production    | uSiP (SIL)   8 | 250   SMALL T&R       | -    | Call TI       | Call TI             | -40 to 125   |              |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

18-Jul-2025

Texas

STRUMENTS

#### TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *A | l dimensions are nominal |                 |                    |   |      |                          |                          |            |            |            |            |           |                  |

|----|--------------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Γ  | Device                   | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|    | LMZ20502SILR             | uSiP            | SIL                | 8 | 3000 | 330.0                    | 12.4                     | 3.75       | 3.75       | 2.2        | 8.0        | 12.0      | Q2               |

|    | LMZ20502SILT             | uSiP            | SIL                | 8 | 250  | 178.0                    | 13.2                     | 3.75       | 3.75       | 2.2        | 8.0        | 12.0      | Q2               |

# PACKAGE MATERIALS INFORMATION

6-Jun-2025

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMZ20502SILR | uSiP         | SIL             | 8    | 3000 | 383.0       | 353.0      | 58.0        |

| LMZ20502SILT | uSiP         | SIL             | 8    | 250  | 223.0       | 194.0      | 35.0        |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated