LMX2694-EP SNAS785D - NOVEMBER 2019 - REVISED MARCH 2022

# LMX2694-EP 15-GHz Wideband PLLatinum™ RF Synthesizer With Phase **Synchronization**

#### 1 Features

- VID V62/19616-01XE

- 39.3-MHz to 15.1-GHz output frequency

- -110 dBc/Hz phase noise at 100-kHz offset with 15-GHz carrier

- 54-fs RMS jitter at 8 GHz (100 Hz to 100 MHz)

- Programmable output power

- PLL key specifications

- Figure of merit: –236 dBc/Hz

- Normalized 1/f noise: –129 dBc/Hz

- Up to 200-MHz phase detector frequency

- Synchronization of output phase across multiple devices

- Support for SYSREF with 9-ps resolution programmable delay

- 3.3-V single power supply operation

- Operating temperature range: -55°C to 125°C

## 2 Applications

- Defense radio

- Electronic warfare

- Radar

- Active antenna system mMIMO (AAS)

- Macro remote radio unit

- Outdoor backhaul unit

- Data acquisition

- Wireless communications test equipment

## 3 Description

The LMX2694-EP device is a high-performance, wideband phase-locked loop (PLL) with an integrated voltage-controlled oscillator (VCO) and voltage regulators that can output any frequency between 39.3 MHz and 15.1 GHz without a doubler, eliminating the need for ½ harmonic filters. The VCO on this device covers an entire octave to complete the frequency coverage down to 39.3 MHz. The highperformance PLL, with a -236-dBc/Hz figure of merit and high-phase detector frequency, can achieve very low in-band noise and integrated jitter.

The LMX2694-EP allows designers to synchronize the output of multiple instances of the device. This means that deterministic phase can be obtained from a device in any use case, including one with the fractional engine or output divider enabled. The device also allows designers to generate or repeat SYSREF (compliant to JESD204B standard) to use the device as a low-noise clock source for high-speed data converters.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| LMX2694-EP  | VQFN (48) | 7.00 mm × 7.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

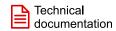

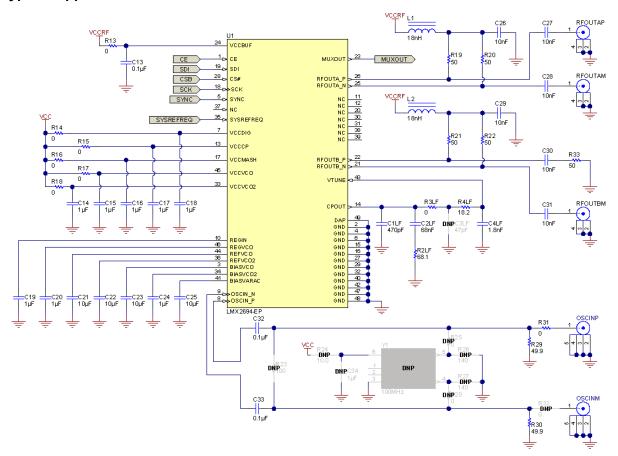

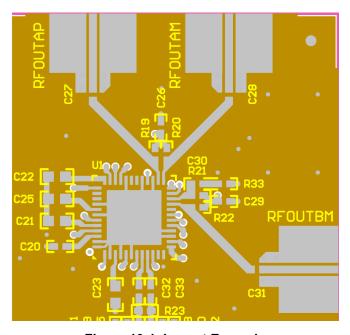

**Simplified Schematic**

## **Table of Contents**

| 1 Features                           | 1              | 7.5 Programming                                | <u>2</u> 6 |

|--------------------------------------|----------------|------------------------------------------------|------------|

| 2 Applications                       |                | 7.6 Register Maps                              |            |

| 3 Description                        |                | 8 Application and Implementation               |            |

| 4 Revision History                   |                | 8.1 Application Information                    |            |

| 5 Pin Configuration and Functions    |                | 8.2 Typical Application                        |            |

| 6 Specifications                     |                | 9 Power Supply Recommendations                 |            |

| 6.1 Absolute Maximum Ratings         |                | 10 Layout                                      |            |

| 6.2 ESD Ratings                      |                | 10.1 Layout Guidelines                         |            |

| 6.3 Recommended Operating Conditions |                | 10.2 Layout Example                            |            |

| 6.4 Thermal Information              | <mark>5</mark> | 11 Device and Documentation Support            |            |

| 6.5 Electrical Characteristics       | 6              | 11.1 Device Support                            |            |

| 6.6 Timing Requirements              | <mark>8</mark> | 11.2 Documentation Support                     |            |

| 6.7 Timing Diagrams                  |                | 11.3 Receiving Notification of Documentation L |            |

| 6.8 Typical Characteristics          |                | 11.4 Support Resources                         |            |

| 7 Detailed Description               |                | 11.5 Trademarks                                |            |

| 7.1 Overview                         |                | 11.6 Electrostatic Discharge Caution           |            |

| 7.2 Functional Block Diagram         |                | 11.7 Glossary                                  |            |

| 7.3 Feature Description              |                | 12 Mechanical, Packaging, and Orderable        |            |

| 7.4 Device Functional Modes          |                | Information                                    | 80         |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision C (October 2021) to Revision D (March 2022)                              | Page    |

|------------------------------------------------------------------------------------------------|---------|

| Changed VID V62/19616 orderable number to "VID V62/19616-01XE" in Features                     | 1       |

| • Moved the VID V62/19616-01XE orderable number in the Device Information table to the Page    | ckaging |

| Information table at the end of the data sheet                                                 | 1       |

| Changes from Revision B (May 2020) to Revision C (October 2021)                                | Page    |

| Removed equivalent division value of 72 in Table 7-8                                           | 18      |

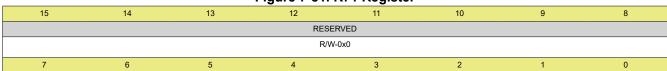

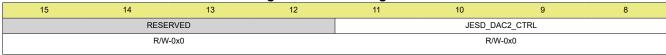

| Changed the JESD_DACx values in Table 7-15                                                     | 23      |

| Changed the R1 register bit name 3 in Figure 7-11 from: 1 to: MUXOUT_CTRL                      | 37      |

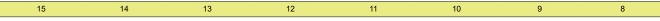

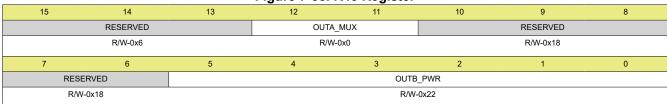

| Changed the OUTA_MUX register description in Table 7-65                                        | 51      |

| Changed the OUTB_MUX register description in Table 7-66                                        |         |

| Changes from Revision A (December 2019) to Revision B (May 2020)                               | Page    |

| Changed maximum operating temperature to 125°C                                                 | 1       |

| <ul> <li>Changed maximum T<sub>C</sub> to 125°C in Recommended Operating Conditions</li> </ul> |         |

| Changed maximum T <sub>C</sub> to 125°C in Electrical Characteristics                          | 6       |

| Changed maximum T <sub>C</sub> to 125°C in Timing Requirements                                 |         |

| Changes from Revision * (November 2019) to Revision A (December 2019)                          | Page    |

| Changed custom data sheet release to catalog                                                   | 1       |

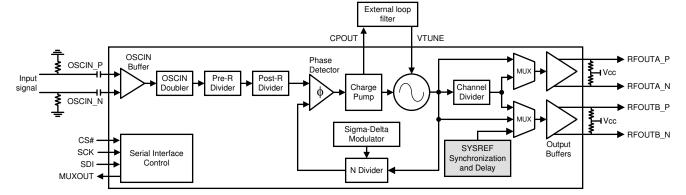

# **5 Pin Configuration and Functions**

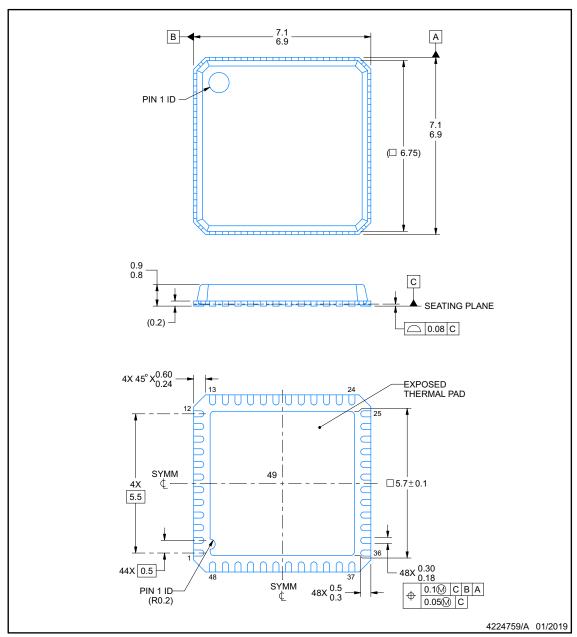

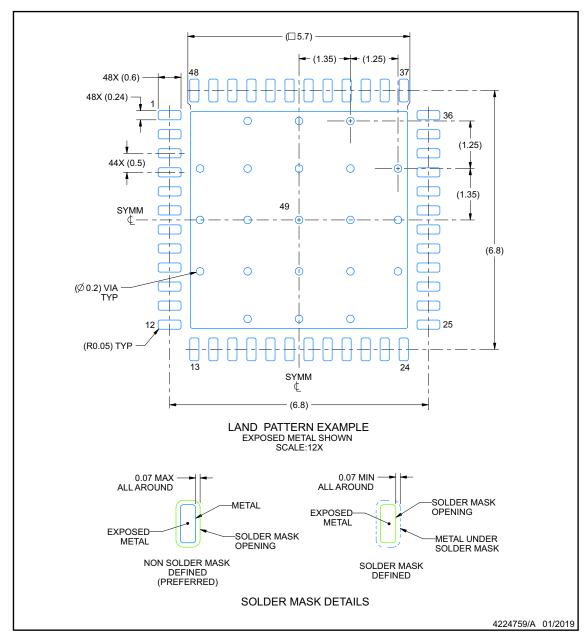

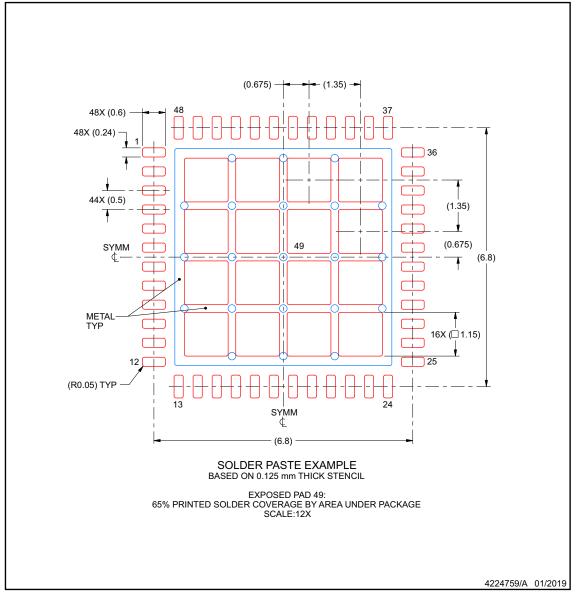

Figure 5-1. RTC Package 48-Pin VQFN Top View

Table 5-1. Pin Functions

|           | PIN I/O                           |     | DESCRIPTION                                                                                                         |  |  |

|-----------|-----------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.                               | 1/0 | DESCRIPTION                                                                                                         |  |  |

| BIASVARAC | 41                                | BP  | VCO varactor bias. Connect a 10-μF decoupling capacitor to ground.                                                  |  |  |

| BIASVCO   | 3                                 | BP  | VCO bias. Connect a 10-μF decoupling capacitor to ground. Place close to pin.                                       |  |  |

| BIASVCO2  | 34                                | BP  | VCO bias. Connect a 1-μF decoupling capacitor to ground. Place close to pin.                                        |  |  |

| CE        | 1                                 | I   | Chip Enable. High impedance CMOS input. 1.8-V to 3.3-V logic. Active HIGH powers on the device.                     |  |  |

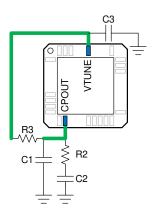

| CPOUT     | 14                                | 0   | Charge pump output. Recommend connecting C1 of loop filter close to this pin.                                       |  |  |

| CS#       | 28                                | I   | PI latch. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                          |  |  |

| GND       | 2, 4, 32, 40, 42, 47              | G   | VCO ground.                                                                                                         |  |  |

| GND       | 6, 16, 48                         | G   | Digital ground.                                                                                                     |  |  |

| GND       | 15                                | G   | Charge pump ground.                                                                                                 |  |  |

| GND       | 27, 29                            | G   | Buffer ground.                                                                                                      |  |  |

| MUXOUT    | 23                                | 0   | Multiplexed output. Can output: lock detect, SPI readback and diagnostics.                                          |  |  |

| NC        | 11, 12, 20, 30, 31, 37,<br>38, 39 | NC  | Pins may be grounded or left unconnected.                                                                           |  |  |

| OSCIN_N   | 9                                 | I   | Reference input clock (–). High impedance self-biasing pin. Requires AC-coupling capacitor. (0.1 µF recommended)    |  |  |

| OSCIN_P   | 8                                 | 1   | Reference input clock (+). High impedance self-biasing pin. Requires AC-coupling capacitor. (0.1 µF recommended)    |  |  |

| REFVCO    | 44                                | BP  | VCO supply reference. Connect a 10-μF decoupling capacitor to ground.                                               |  |  |

| REFVCO2   | 36                                | BP  | VCO supply reference. Connect a 10-μF decoupling capacitor to ground.                                               |  |  |

| REGIN     | 10                                | BP  | Input reference path regulator decoupling. Connect a 1-µF decoupling capacitor to ground. Place close to pin.       |  |  |

| REGVCO    | 46                                | BP  | VCO regulator node. Connect a 1-µF decoupling capacitor to ground.                                                  |  |  |

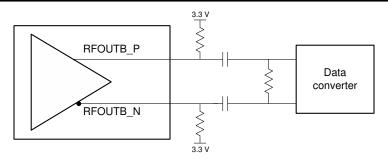

| RFOUTA_N  | 25                                | 0   | Differential output A (–). Requires connecting $50-\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin. |  |  |

## **Table 5-1. Pin Functions (continued)**

|             | PIN | I/O | PESCHIPTION                                                                                                                                                                      |

|-------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO. | 1/0 | DESCRIPTION                                                                                                                                                                      |

| RFOUTA_P    | 26  | 0   | Differential output A (+). Requires connecting $50-\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin.                                                              |

| RFOUTB_N    | 21  | 0   | Differential output B (–). Requires connecting 50- $\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin.                                                             |

| RFOUTB_P    | 22  | 0   | Differential output B (+). Requires connecting $50-\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin.                                                              |

| SCK         | 18  | ı   | SPI clock. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                      |

| SDI         | 19  | I   | SPI data. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                       |

| SYNC        | 5   | ı   | Phase synchronization input. Has programmable threshold. Connect to ground if not being used.                                                                                    |

| SYSREFREQ   | 35  | I   | SYSREF request input for JESD204B support. Connect to ground if not being used.                                                                                                  |

| VCCBUF      | 24  | Р   | Output buffer supply. Connect to 3.3-V and a 0.1-µF decoupling capacitor to ground.                                                                                              |

| VCCCP       | 13  | Р   | Charge pump supply. Connect to 3.3-V and a 0.1-µF decoupling capacitor to ground.                                                                                                |

| VCCDIG      | 7   | Р   | Digital supply. Connect to 3.3-V and a 0.1-μF decoupling capacitor to ground.                                                                                                    |

| VCCMASH     | 17  | Р   | Digital supply. Connect to 3.3-V and a 1-µF decoupling capacitor to ground.                                                                                                      |

| VCCVCO      | 45  | Р   | VCO supply. Connect to 3.3-V and a 1-µF decoupling capacitor to ground.                                                                                                          |

| VCCVCO2     | 33  | Р   | VCO supply. Connect to 3.3-V and a 1-µF decoupling capacitor to ground.                                                                                                          |

| VTUNE       | 43  | I   | VCO tuning voltage input. Connect a 1.5-nF or more capacitor to VCO ground. See<br>External Loop Filter for details.                                                             |

| Thermal pad | _   | _   | Connect the GND pin to the exposed thermal pad for correct operation. Connect the thermal pad to any internal PCB ground plane using multiple vias for good thermal performance. |

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  | · · · · · · · · · · · · · · · · · · · | MIN  | MAX                   | UNIT |

|------------------|---------------------------------------|------|-----------------------|------|

| V <sub>CC</sub>  | Power supply voltage                  | -0.3 | 3.6                   | V    |

| V <sub>IN</sub>  | IO input voltage                      |      | V <sub>CC</sub> + 0.3 | V    |

| TJ               | Junction temperature                  | -55  | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature                   | -65  | 150                   | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                        | ±1000 | V    |

| V <sub>(ESD)</sub> | Lieurostano disorial ge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1000 | V    |

- (1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                      | MIN | NOM | MAX  | UNIT |

|-----------------|----------------------|-----|-----|------|------|

| T <sub>C</sub>  | Case temperature     | -55 |     | 125  | °C   |

| V <sub>CC</sub> | Supply input voltage | 3.2 | 3.3 | 3.45 | V    |

## **6.4 Thermal Information**

|                       |                                              | LMX2694-EP |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTC (VQFN) | UNIT |

|                       |                                              | 48 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 22.4       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 10.0       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.1        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.0        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

$3.2 \text{ V} \le \text{V}_{\text{CC}} \le 3.45 \text{ V}, -50^{\circ}\text{C} \le \text{T}_{\text{C}} \le 125^{\circ}\text{C}$ . Typical values are at  $\text{V}_{\text{CC}} = 3.3 \text{ V}, 25^{\circ}\text{C}$  (unless otherwise noted)

|                       | PARAMETER                                | TEST COND                                                                                                                                                                        | ITIONS                                           | MIN   | TYP  | MAX   | UNIT            |  |

|-----------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------|------|-------|-----------------|--|

| POWER SU              | PPLY                                     |                                                                                                                                                                                  |                                                  |       |      | '     |                 |  |

| I <sub>CC</sub>       | Supply current                           | OUTA_PD = 0; OUTB_PD = 1;<br>OUTA_MUX = OUTB_MUX = 1;<br>OUTA_PWR = 31; CPG = 7;<br>f <sub>OSC</sub> = f <sub>PD</sub> = 100 MHz; f <sub>VCO</sub> = f <sub>OUT</sub> = 14.5 GHz |                                                  |       | 360  |       | mA              |  |

|                       | Power on reset current                   | RESET = 1                                                                                                                                                                        |                                                  |       | 289  |       |                 |  |

|                       | Power down current                       | POWERDOWN = 1                                                                                                                                                                    |                                                  |       | 6    |       |                 |  |

| OUTPUT CI             | HARACTERISTICS                           |                                                                                                                                                                                  | 1                                                |       |      | 1     |                 |  |

| -                     | Single-ended output power <sup>(1)</sup> | 50-Ω resistor pull-up                                                                                                                                                            | f <sub>OUT</sub> = 8 GHz                         |       | 2    |       | -ID:            |  |

|                       | (2)                                      | OUTx_PWR = 31                                                                                                                                                                    | f <sub>OUT</sub> = 15 GHz                        |       | 0    |       | dBm             |  |

| INPUT SIGN            | NAL PATH                                 |                                                                                                                                                                                  |                                                  |       |      |       |                 |  |

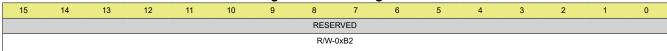

| f                     | Reference input frequency                | OSC_2X = 0                                                                                                                                                                       |                                                  | 5     |      | 1000  | MHz             |  |

| osc                   |                                          | OSC_2X = 1                                                                                                                                                                       |                                                  | 5     |      | 200   |                 |  |

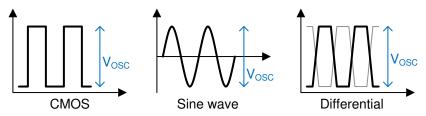

|                       | Reference input voltage <sup>(3)</sup>   | f <sub>OSC</sub> ≥ 20 MHz                                                                                                                                                        |                                                  | 0.4   |      | 2     | V <sub>PP</sub> |  |

| $V_{OSC}$             |                                          | 10 MHz ≤ f <sub>OSC</sub> < 20 MHz                                                                                                                                               |                                                  | 0.8   |      | 2     |                 |  |

|                       |                                          | 5 MHz ≤ f <sub>OSC</sub> < 10 MHz                                                                                                                                                |                                                  | 1.6   |      | 2     |                 |  |

| PHASE DE              | TECTOR AND CHARGE PUMP                   |                                                                                                                                                                                  |                                                  |       |      | '     |                 |  |

| £                     | Dhose detector frequency (4)             | MASH_ORDER = 0                                                                                                                                                                   |                                                  | 0.125 |      | 250   | NAL I-          |  |

| f <sub>PD</sub>       | Phase detector frequency <sup>(4)</sup>  | MASH_ORDER > 0                                                                                                                                                                   |                                                  | 5     |      | 200   | MHz             |  |

|                       | Charge-pump leakage current              | CPG = 0                                                                                                                                                                          |                                                  |       | 20   |       | nA              |  |

| I <sub>CPOUT</sub>    | Effective charge pump current            | Sum of the up and down co                                                                                                                                                        | urrents                                          | 3     |      | 15    | mA              |  |

| PN <sub>PLL_1/f</sub> | Normalized PLL 1/f noise                 | f = 100 MH=: f = 12.0                                                                                                                                                            | - 100 MHz: f - 12 CHz(5)                         |       | -129 |       | dBc/Hz          |  |

| PN <sub>PLL_FOM</sub> | Normalized PLL noise floor               | 11PD - 100 MITZ, 1 <sub>VCO</sub> = 12 (                                                                                                                                         | 00 MHz; f <sub>VCO</sub> = 12 GHz <sup>(5)</sup> |       | -236 |       | uDC/HZ          |  |

| VCO CHAR              | ACTERISTICS                              |                                                                                                                                                                                  | 1                                                |       |      |       |                 |  |

| f <sub>VCO</sub>      | VCO frequency                            |                                                                                                                                                                                  |                                                  | 7550  |      | 15100 | MHz             |  |

$3.2 \text{ V} \le \text{V}_{co} \le 3.45 \text{ V} -50 ^{\circ}\text{C} \le \text{T}_{c} \le 125 ^{\circ}\text{C}$ . Typical values are at  $\text{V}_{co} = 3.3 \text{ V} \cdot 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                   | PARAMETER                           | TEST CON                                                                           | DITIONS        | MIN TYP N        | MAX | UNIT    |  |

|-------------------|-------------------------------------|------------------------------------------------------------------------------------|----------------|------------------|-----|---------|--|

|                   |                                     |                                                                                    | 100 kHz        | -106.5           |     |         |  |

|                   |                                     | VCO1                                                                               | 1 MHz          | -128             |     |         |  |

|                   |                                     | f <sub>VCO</sub> = 8.1 GHz                                                         | 10 MHz         | -147.5           |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -154             |     |         |  |

|                   |                                     |                                                                                    | 100 kHz        | -105             |     |         |  |

|                   |                                     | VCO2                                                                               | 1 MHz          | -126.5           |     |         |  |

|                   |                                     | f <sub>VCO</sub> = 9.3 GHz                                                         | 10 MHz         | -146.5           |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -154             |     |         |  |

|                   |                                     |                                                                                    | 100 kHz        | -103.5           |     |         |  |

|                   |                                     | V002                                                                               | 1 MHz          | -125.5           |     |         |  |

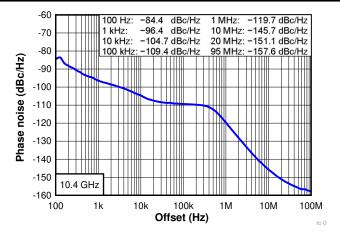

|                   |                                     | VCO3<br>f <sub>VCO</sub> = 10.4 GHz                                                | 10 MHz         | -146             |     |         |  |

| PN <sub>VCO</sub> |                                     | 100                                                                                | 100 MHz        | -158             |     |         |  |

|                   |                                     |                                                                                    | 100 kHz        | -102.5           |     |         |  |

|                   |                                     |                                                                                    | 1 MHz          | -102.5<br>-124.5 |     |         |  |

|                   | VCO phase noise                     | VCO4<br>f <sub>VCO</sub> = 11.4 GHz                                                |                |                  |     | dBc/H   |  |

|                   |                                     | 1,000 1111 3112                                                                    | 10 MHz         | -145<br>160      |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -160<br>100 F    |     |         |  |

|                   |                                     |                                                                                    | 100 kHz        | -100.5           |     |         |  |

|                   |                                     | VCO5<br>f <sub>VCO</sub> = 12.5 GHz                                                | 1 MHz          | -122.5           |     |         |  |

|                   |                                     |                                                                                    | 10 MHz         | -143.5           |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -154.5           |     |         |  |

|                   |                                     | VCO6<br>f <sub>VCO</sub> = 13.6 GHz                                                | 100 kHz        | -99.5            |     |         |  |

|                   |                                     |                                                                                    | 1 MHz          | -122             |     |         |  |

|                   |                                     |                                                                                    | 10 MHz         | -142.5           |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -154             |     |         |  |

|                   |                                     | VCO7<br>f <sub>VCO</sub> = 14.7 GHz                                                | 100 kHz        | -98              |     |         |  |

|                   |                                     |                                                                                    | 1 MHz          | -120.5           |     |         |  |

|                   |                                     |                                                                                    | 10 MHz         | -141.5           |     |         |  |

|                   |                                     |                                                                                    | 100 MHz        | -155             |     |         |  |

| VCOCAL            | VCO calibration time <sup>(6)</sup> | Switch across the entire find $f_{OSC} = f_{PD} = 100 \text{ MHz};$<br>VCO_SEL = 7 | requency band; | 650              |     | μs      |  |

|                   |                                     | 8.1 GHz                                                                            |                | 94               |     |         |  |

|                   |                                     | 9.3 GHz                                                                            |                | 106              |     |         |  |

|                   |                                     | 10.4 GHz                                                                           |                | 122              |     |         |  |

| vco               | VCO Gain                            | 11.4 GHz                                                                           |                | 148              |     | MHz/\   |  |

|                   |                                     | 12.5 GHz                                                                           |                | 185              |     |         |  |

|                   |                                     | 13.6 GHz                                                                           |                | 202              |     |         |  |

|                   |                                     | 14.7 GHz                                                                           | 233            |                  |     |         |  |

| ΔT <sub>CL</sub>  | Allowable temperature drift         | VCO not being re-calibrat                                                          | ed             | 125              |     | °C      |  |

| 12                | VCO second harmonic                 | f <sub>VCO</sub> = 8 GHz; divider disa                                             |                | -30              |     |         |  |

| 13                | VCO third harmonic                  | f <sub>VCO</sub> = 8 GHz; divider disa                                             |                | -25              |     | dBc     |  |

|                   | NTERFACE                            | ,                                                                                  |                | <u> </u>         |     |         |  |

| ′ін               | High-level input voltage            |                                                                                    |                | 1.4              |     | V       |  |

| / <sub>IL</sub>   | Low-level input voltage             |                                                                                    |                | •••              | 0.4 |         |  |

|                   | High-level input current            |                                                                                    |                | -100             | 100 | ν<br>μΑ |  |

| IH<br>IL          | Low-level input current             |                                                                                    |                |                  | 100 |         |  |

| L                 | Low-level input current             |                                                                                    |                | -100             | 100 | μA      |  |

$3.2 \text{ V} \le \text{V}_{\text{CC}} \le 3.45 \text{ V}, -50 ^{\circ}\text{C} \le \text{T}_{\text{C}} \le 125 ^{\circ}\text{C}.$  Typical values are at  $\text{V}_{\text{CC}} = 3.3 \text{ V}, 25 ^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER |                              | TEST CONDITIO        | MIN           | TYP                   | MAX | UNIT |   |

|-----------|------------------------------|----------------------|---------------|-----------------------|-----|------|---|

| Vo        | OH High-level output voltage | Load current = -5 mA | MUXOUT pin    | V <sub>CC</sub> – 0.6 |     |      | V |

| Vc        | OL High-level output current | Load current = 5 mA  | INIOACOT PIII |                       |     | 0.6  | V |

- (1) Single ended output power obtained after de-embedding microstrip trace losses and matching with a manual tuner. Unused port terminated to 50-Ω load.

- (2) Output power, spurs, and harmonics can vary based on board layout and components.

- (3) Single-ended AC coupled sine wave input with complementary side AC coupled to ground with  $50-\Omega$  resistor.

- (4) For lower VCO frequencies, the N divider minimum value can limit the phase-detector frequency.

- (5) The PLL noise contribution is measured using a clean reference and a wide loop bandwidth and is composed into flicker and flat components. PLL\_flat = PLL\_FOM + 20 x log(f<sub>VCO</sub>/f<sub>PD</sub>) + 10 x log(f<sub>PD</sub>/1 Hz). PLL\_flicker (offset) = PLL\_1/f + 20 x log(f<sub>VCO</sub>/1 GHz) 10 x log(offset/10 kHz). Once these two components are found, the total PLL noise can be calculated as PLL\_Noise = 10 x log(10<sup>PLL\_Flat/10</sup> + 10<sup>PLL\_flicker/10</sup>).

- (6) See Section 7.3.7.1 for details.

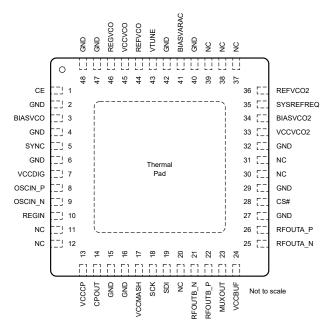

#### 6.6 Timing Requirements

$3.2~\text{V} \le \text{V}_{\text{CC}} \le 3.45~\text{V}, -50^{\circ}\text{C} \le \text{T}_{\text{C}} \le 125^{\circ}\text{C}.$  Typical values are at  $\text{V}_{\text{CC}} = 3.3~\text{V}, 25^{\circ}\text{C}$  (unless otherwise noted)

|                           |                                                  |                                             | MIN | NOM MAX | UNIT |

|---------------------------|--------------------------------------------------|---------------------------------------------|-----|---------|------|

| SYNC AND S                | YSREFREQ TIMING                                  |                                             |     |         |      |

| t <sub>SETUP</sub>        | Setup time for pin relative to OSCIN rising edge | See Figure 6-1                              | 9   |         | ns   |

| t <sub>HOLD</sub>         | Hold time for pin relative to OSCIN rising edge  | See Figure 0-1                              | 4   |         | ns   |

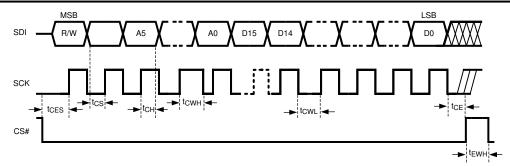

| DIGITAL INTE              | RFACE WRITE SPECIFICATIONS                       |                                             |     |         |      |

| f <sub>SPI</sub> Write    | SPI write speed                                  | t <sub>CWL</sub> + t <sub>CWH</sub> ≥ 25 ns |     | 40      | MHz  |

| t <sub>CE</sub>           | Clock to enable low time                         |                                             | 5   |         | ns   |

| t <sub>CS</sub>           | Data to clock setup time                         |                                             | 2   |         | ns   |

| t <sub>CH</sub>           | Data to clock hold time                          | See Figure 6-2                              | 2   |         | ns   |

| t <sub>CWH</sub>          | Clock pulse width high                           |                                             | 5   |         | ns   |

| t <sub>CWL</sub>          | Clock pulse width low                            |                                             | 5   |         | ns   |

| t <sub>CES</sub>          | Enable to clock setup time                       |                                             | 5   |         | ns   |

| t <sub>EWH</sub>          | Enable pulse width high                          |                                             | 2   |         | ns   |

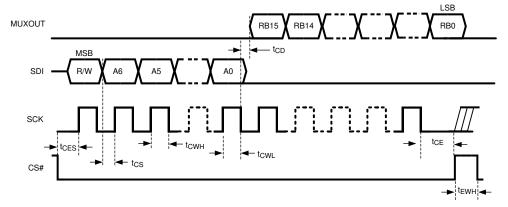

| DIGITAL INTE              | RFACE READBACK SPECIFICATIONS                    |                                             |     |         |      |

| f <sub>SPI</sub> Readback | SPI readback speed                               |                                             |     | 40      | MHz  |

| t <sub>CE</sub>           | Clock to enable low time                         |                                             | 5   |         | ns   |

| t <sub>CS</sub>           | Clock to data wait time                          |                                             | 2   |         | ns   |

| t <sub>CH</sub>           | Clock to data hold time                          |                                             | 2   |         | ns   |

| t <sub>CWH</sub>          | Clock pulse width high                           | See Figure 6-3                              | 10  |         | ns   |

| t <sub>CWL</sub>          | Clock pulse width low                            |                                             | 10  |         | ns   |

| t <sub>CES</sub>          | Enable to clock setup time                       |                                             | 5   |         | ns   |

| t <sub>EWH</sub>          | Enable pulse width high                          |                                             | 2   |         | ns   |

| t <sub>CD</sub>           | Falling clock edge to data wait time             |                                             |     | 8       | ns   |

## 6.7 Timing Diagrams

Figure 6-1. Trigger Signals Timing Diagram

Figure 6-2. Serial Data Input Timing Diagram

There are several other considerations for writing on the SPI:

- The R/W bit must be set to 0.

- The data on SDI pin is clocked into a shift register on each rising edge on the SCK pin.

- The CS# must be held low for data to be clocked. Device will ignore clock pulses if CS# is held high.

- The CS# transition from high to low must occur when SCK is low.

- When SCK and SDI lines are shared between devices, TI recommends to hold the CS# line high on the

device that is not to be clocked.

Figure 6-3. Serial Data Readback Timing Diagram

There are several other considerations for SPI readback:

- The R/W bit must be set to 1.

- The MUXOUT pin will always be low for the address portion of the transaction.

- The data on MUXOUT becomes available momentarily after the falling edge of SCK, and therefore, should be read back on the rising edge of SCK.

- The data portion of the transition on the SDI line is always ignored.

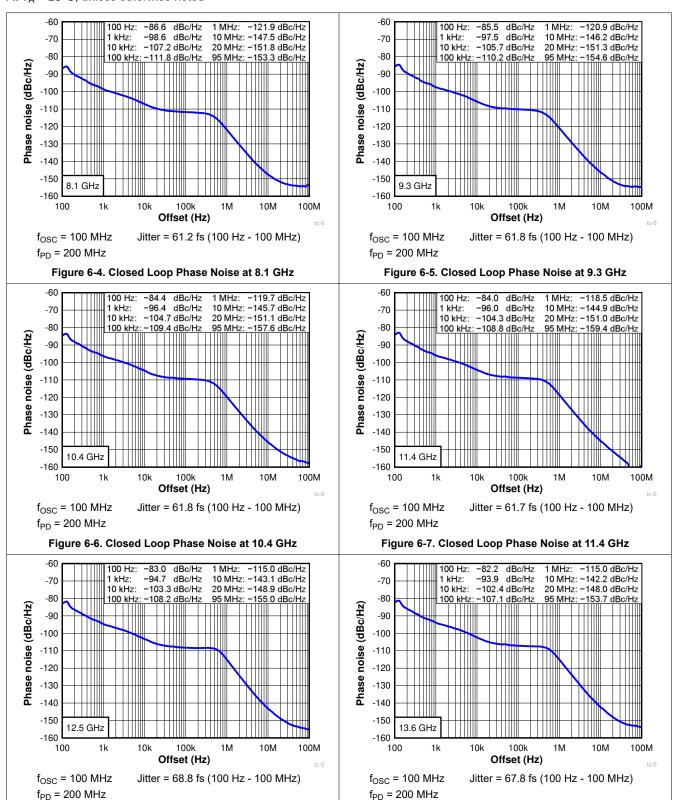

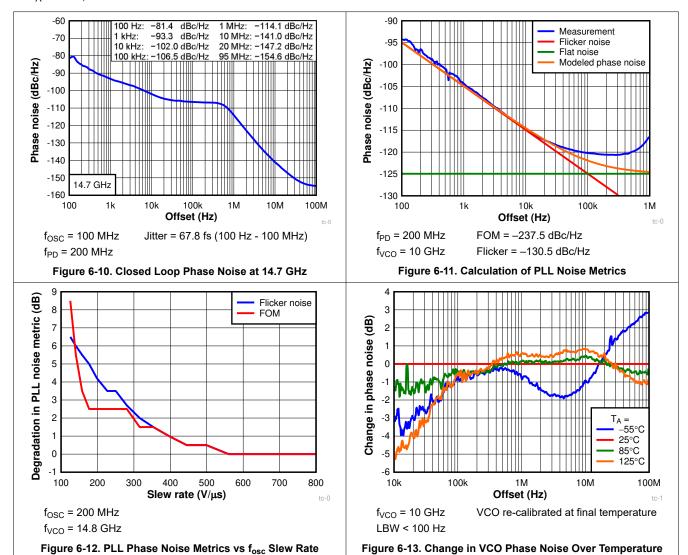

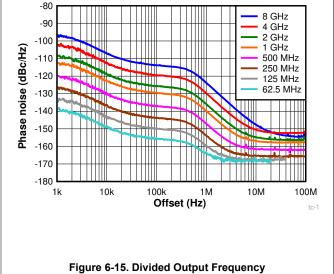

## 6.8 Typical Characteristics

At  $T_A = 25$ °C, unless otherwise noted

Figure 6-8. Closed Loop Phase Noise at 12.5 GHz

Figure 6-9. Closed Loop Phase Noise at 13.6 GHz

## **6.8 Typical Characteristics (continued)**

#### At $T_A = 25$ °C, unless otherwise noted

## **6.8 Typical Characteristics (continued)**

At T<sub>A</sub> = 25°C, unless otherwise noted

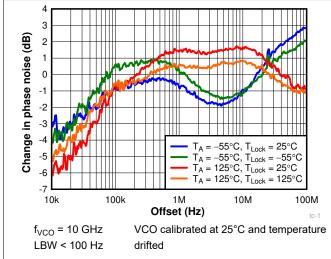

Figure 6-14. Change in VCO Phase Noise Over Temperature

## 7 Detailed Description

#### 7.1 Overview

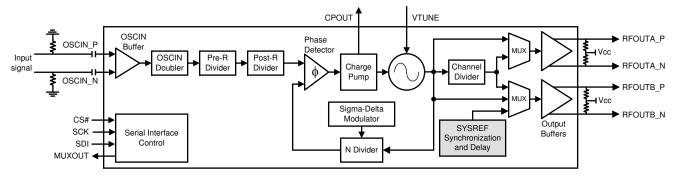

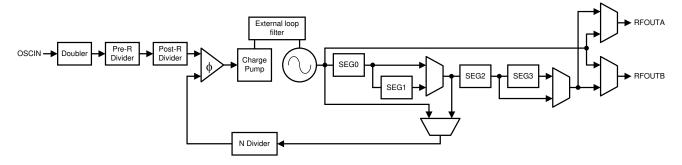

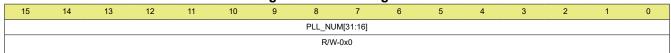

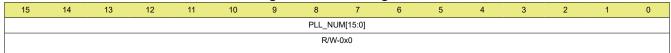

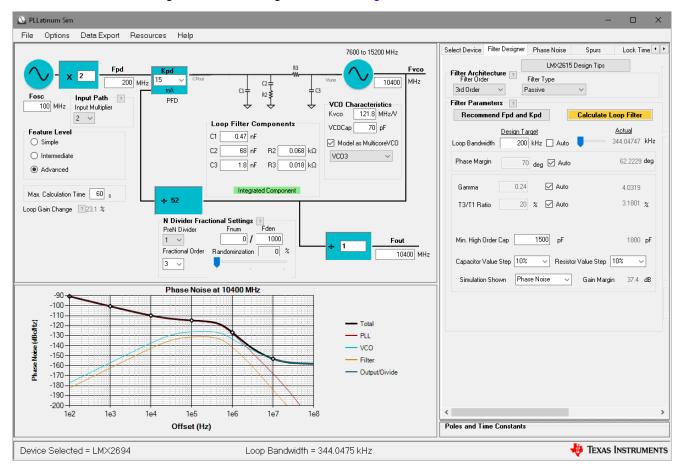

The LMX2694-EP is a high-performance, wideband frequency synthesizer with an integrated VCO and output divider. The VCO operates from 7550 to 15100 MHz, and can be combined with the output divider to produce any frequency in the range of 39.3 MHz to 15.1 GHz. There are two dividers within the input path.

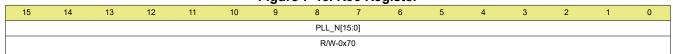

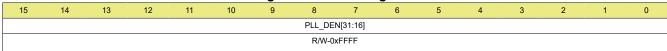

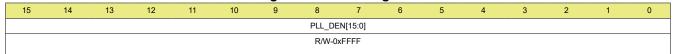

The PLL is fractional-N PLL with a programmable delta-sigma modulator up to the 3<sup>rd</sup> order. The fractional denominator is a programmable 32-bit long that can provide fine frequency steps easily below 1-Hz resolution, as well as be used to do exact fractions like 1/3, 7/1000, and so on.

For applications where deterministic or adjustable phase is desired, the SYNC pin can be used to get the phase relationship between the OSCIN and RFOUTx pins deterministic. Once this is done, the phase can be adjusted in very fine steps of the VCO period divided by the fractional denominator.

The ultra-fast VCO calibration is designed for applications where the frequency must be swept or abruptly changed. The frequency can be manually programmed.

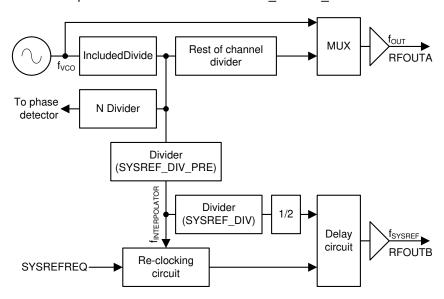

For JESD204B support, the RFOUTB output can be used as a differential SYSREF output that can be either a single pulse or a series of pulses that occur at a programmable distance away from the rising edges of the output signal.

The LMX2694-EP device requires only a single 3.3-V power supply. The internal power supplies are provided by integrated LDOs, eliminating the need for high-performance external LDOs.

Table 7-1 shows the range of several of the doubler, dividers, and fractional settings.

Table 7-1. Range of Doubler, Divider, and Fractional Settings

| PARAMETER                          | MIN              | MAX                              | COMMENTS                                                                                                                                                   |

|------------------------------------|------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIN doubler                      | 0 (1X)           | 1 (2X)                           | The low noise doubler can be used to increase the phase detector frequency to improve phase noise and avoid spurs. This is in reference to the OSC_2X bit. |

| Pre-R divider                      | 1 (bypass)       | 128                              | Only use the Pre-R divider if the input frequency is too high for the Post-R divider.                                                                      |

| Post-R divider                     | 1 (bypass)       | 255                              | The maximum input frequency for the Post-R divider is 250 MHz. Use the Pre-R divider if necessary.                                                         |

| N divider                          | ≥ 28             | 524287                           | The minimum divide depends on modulator order and VCO frequency. See <i>N Divider and Fractional Circuitry</i> for more details.                           |

| Fractional numerator / denominator | 1 (integer mode) | 2 <sup>32</sup> – 1 = 4294967295 | The fractional denominator is programmable and can assume any value between 1 and 2 <sup>32</sup> – 1. It is not a fixed denominator.                      |

| Fractional order                   | 0                | 3                                | Order 0 is integer mode, and the order can be programmed.                                                                                                  |

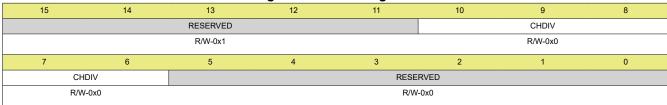

| Channel divider                    | 1 (bypass)       | 192                              | This is the series of several dividers. Also, be aware that above 10 GHz, the maximum allowable channel divider value is 6.                                |

| Output frequency                   | 39.3 MHz         | 15.1 GHz                         | This is implied by the minimum VCO frequency divided by the maximum channel divider value.                                                                 |

#### 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Reference Oscillator Input

The OSCIN pins are used as a frequency reference input to the device. The input is high impedance and requires AC-coupling caps at the pin. The OSCIN pins can be driven single-ended with a CMOS clock or XO. Differential clock input is also supported, making it easier to interface with high-performance system clock devices such as TI's LMK series clock devices. As the OSCIN signal is used as a clock for the VCO calibration, a proper reference signal must be applied at the OSCIN pin at the time of programming FCAL EN.

#### 7.3.2 Reference Path

The reference path consists of an OSCIN doubler (OSC 2X), Pre-R divider, and a Post-R divider.

Figure 7-1. Reference Path Diagram

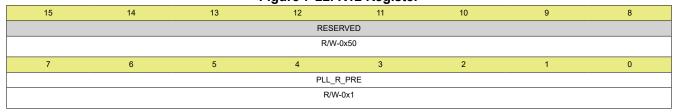

The OSCIN doubler (OSC\_2X) can double up low OSCIN frequencies. Pre-R (PLL\_R\_PRE) and Post-R (PLL\_R) dividers both divide frequency down. Use Equation 1 to calculate the phase detector frequency, f<sub>PD</sub>:

$$f_{PD} = f_{OSC} \times OSC \ 2X / (PLL \ R \ PRE \times PLL \ R)$$

(1)

- If the OSCIN doubler is used, the OSCIN signal should have a 50% duty cycle as both the rising and falling edges are used.

- If the OSCIN doubler is not used, only rising edges of the OSCIN signal are used and duty cycle is not critical.

#### 7.3.2.1 OSCIN Doubler (OSC 2X)

The OSCIN doubler allows the user to double the input reference frequency at up to 400 MHz, while adding minimal noise. It may be advantageous to use the doubler to go higher than the maximum phase detector frequency in some situations, because the Pre-R divider may be able to divide down this frequency to a phase detector frequency that is advantageous for fractional spurs.

#### 7.3.2.2 Pre-R Divider (PLL R PRE)

The Pre-R divider is useful for reducing the input frequency to help meet the maximum 250-MHz input frequency limitation to the PLL-R divider. Otherwise, it does not have to be used.

#### 7.3.2.3 Post-R Divider (PLL R)

The Post-R divider can be used to further divide down the frequency to the phase detector frequency. When PLL\_R > 1, the input frequency to this divider is limited to 250 MHz.

#### 7.3.3 State Machine Clock

The state machine clock is a divided-down version of the OSCIN signal that is used internally in the device. This divide value 1, 2, 4, 8, 16, or 32 and is determined by CAL\_CLK\_DIV programming word (described in the *Programming* section). This state machine clock impacts various features like the VCO calibration. The state machine clock is calculated as  $f_{SM} = f_{OSC} / 2^{CAL\_CLK\_DIV}$ .

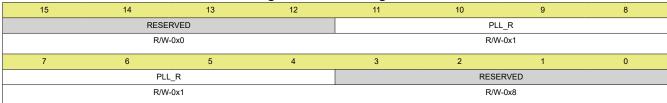

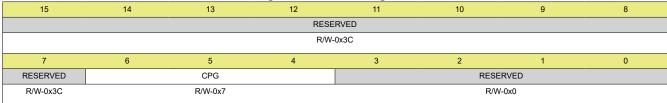

#### 7.3.4 PLL Phase Detector and Charge Pump

The phase detector compares the outputs of the Post-R divider and N divider, and will generate a correction current corresponding to the phase error until the two signals are aligned in-phase. This charge-pump current is software-programmable to many different levels, which allows the user to modify the closed-loop bandwidth of the PLL.

## 7.3.5 N Divider and Fractional Circuitry

The N divider includes fractional compensation that can achieve any fractional denominator from 1 to  $(2^{32}-1)$ . The integer portion of N is the whole part of the N divider value, while the fractional portion (N<sub>frac</sub> = NUM / DEN) is the remaining fraction. In general, the total N divider value is determined by N + NUM / DEN. The N, NUM and DEN are software-programmable. The higher the denominator, the finer the resolution step of the output. For example, even when using  $f_{PD}$  = 200 MHz, the output can increment in steps of 200 MHz / ( $2^{32}-1$ ) = 0.047 Hz. Equation 2 shows the relationship between the phase detector and VCO frequencies. Note that in SYNC mode, there is an extra divider that is not shown in Equation 2.

$$f_{VCO} = f_{PD} \times [N + NUM/DEN]$$

(2)

The sigma-delta modulator that controls this fractional division is also programmable from integer mode to the third order. To make the fractional spurs consistent, the modulator is reset any time that the R0 register is programmed.

The N divider has minimum value restrictions based on the modulator order (MASH\_ORDER) and VCO frequency. Furthermore, the PFD\_DLY\_SEL bit must be programmed in accordance to Table 7-2. IncludedDivide may be larger than one in SYNC mode. In all other modes, IncludedDivide is just one.

| MASH_ORDER | f <sub>VCO</sub> / IncludedDivide (MHz) | MINIMUM N | PFD_DLY_SEL |

|------------|-----------------------------------------|-----------|-------------|

| 0          | ≤ 12500                                 | 29        | 1           |

| O O        | > 12500                                 | 33        | 2           |

|            | ≤ 10000                                 | 30        | 1           |

| 1          | 10000 - 12500                           | 34        | 2           |

|            | > 12500                                 | 38        | 3           |

|            | ≤ 4000 (SYNC mode)                      | 31        | 1           |

| 2          | 4000 - 7500 (SYNC mode)                 | 31        | 2           |

| 2          | 7500 - 10000                            | 32        | 2           |

|            | > 10000                                 | 36        | 3           |

|            | ≤ 4000 (SYNC mode)                      | 33        | 1           |

| 3          | 4000 - 7500 (SYNC mode)                 | 37        | 2           |

| 3          | 7500 - 10000                            | 41        | 3           |

|            | > 10000                                 | 45        | 4           |

Table 7-2. Minimum N Divider Restrictions

#### 7.3.6 MUXOUT Pin

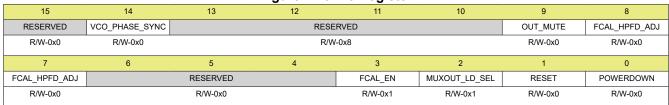

The MUXOUT pin can be configured as either a lock detect indicator for the PLL or as a serial data output for the SPI interface to read back registers. Field MUXOUT\_LD\_SEL (register R0[2]) configures this output.

Table 7-3. MUXOUT Pin Configurations

| MUXOUT_LD_SEL | FUNCTION                        |

|---------------|---------------------------------|

| 0             | Serial data output for readback |

| 1             | Lock detect indicator           |

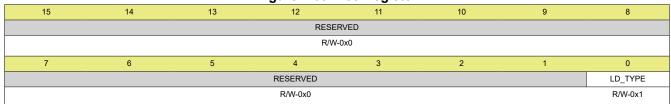

When the lock detect indicator is selected, there are two types of indicators that can be selected with the field LD\_TYPE (register R59[0]). The first indicator is called "VCOCal" (LD\_TYPE = 0), and the second indicator is called "Vtune and VCOCal" (LD\_TYPE = 1).

## 7.3.6.1 Serial Data Output for Readback

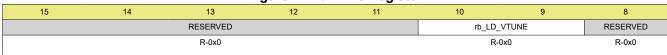

In this mode, the MUXOUT pin can be used as a the serial data output of the SPI interface. This output cannot be in a tri-state condition, therefore no line sharing is possible. Details of this pin operation are described in *Timing Requirements*. Readback is very useful when a device is used in full-assist mode, because the VCO calibration data are retrieved and saved for future use. It can also be used to read back the lock detect status using the field rb LD VTUNE(register R110[10:9]).

#### 7.3.6.2 Lock Detect Indicator Set as Type "VCOCal"

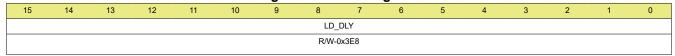

In this mode, the MUXOUT pin will be low when the VCO is calibrating or when the lock detect delay timer is running. Otherwise, the MUXOUT will be high. The programmable timer (LD\_DLY, register R60[15:0]) adds an additional delay after the VCO calibration finishes and before the lock detect indicator is asserted high. LD\_DLY is a 16-bit unsigned quantity that corresponds to the 4 times the number of phase detector cycles in absolute delay. For example, a phase detector frequency of 100 MHz and the LD\_DLY = 10000 will add a delay of 400 µs before the indicator is asserted. This indicator will remain in its current state (high or low) until register R0 is programmed with FCAL\_EN = 1 with a valid input reference. In other words, if the PLL goes out of lock or the input reference goes away when the current state is high, then the current state will remain high.

## 7.3.6.3 Lock Detect Indicator Set as Type "Vtune and VCOCal"

In this mode the MUXOUT pin will be high when the VCO calibration has finished, the lock detect delay timer is finished running, and the PLL is locked. This indicator may remain in its current state (high or low) if the OSCin signal is lost. The true status of the indicator will be updated and resume its operation only when a valid input reference to the OSCin pin is returned. An alternative method to monitor the OSCin of the PLL is recommended. This indicator is reliable as long as the reference to OSCin is present.

The output of the device can be automatically muted when lock detect indicator "Vtune and VCOCal" is low. This feature is enabled with the field OUT\_MUTE (register R0[9]) asserted.

## 7.3.7 VCO (Voltage-Controlled Oscillator)

The LMX2694-EP includes a fully integrated VCO. The VCO takes the voltage from the loop filter and converts this into a frequency. The VCO frequency is related to the other frequencies and as follows:

$$f_{VCO} = f_{PD} \times N \text{ divider} \times \text{IncludedDivide}$$

(3)

#### 7.3.7.1 VCO Calibration

To reduce the VCO tuning gain, and therefore improve the VCO phase-noise performance, the VCO frequency range is divided into several different frequency bands. The entire range (7550 to 15100 MHz) covers an octave that allows the divider to take care of frequencies below the lower bound. This creates the need for frequency calibration to determine the correct frequency band given a desired output frequency. The frequency calibration routine is activated any time that the R0 register is programmed with the FCAL\_EN = 1. It is important that a valid OSCIN signal must present before VCO calibration begins.

The VCO also has an internal amplitude calibration algorithm to optimize the phase noise, which is also activated any time the R0 register is programmed.

The optimum internal settings for this are temperature-dependent. If the temperature is allowed to drift too much without being recalibrated, some minor phase noise degradation could result. The maximum allowable drift for

continuous lock,  $\Delta T_{CL}$ , is stated in the electrical specifications. For this device, a number of 125°C means the device never loses lock if the device is operated under recommended operating conditions.

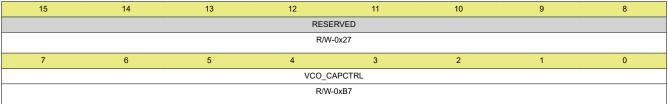

The LMX2694-EP allows the user to assist the VCO calibration. In general, there are three kinds of assistance, as shown in Table 7-4.

Table 7-4. Assisting the VCO Calibration Speed

| ASSISTANCE<br>LEVEL | DESCRIPTION                                                                                                                             | VCO_SEL            | VCO_SEL_FORCE<br>VCO_CAPCTRL_FORCE<br>VCO_DACISET_FORCE | VCO_CAPCTRL<br>VCO_DACISET |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------|----------------------------|

| No assist           | User does nothing to improve VCO calibration speed.                                                                                     | 7                  | 0                                                       | Don't care                 |

| Partial assist      | Upon every frequency change, before the FCAL_EN bit is checked, the user provides the initial starting VCO_SEL.                         | Choose by table    | 0                                                       | Don't care                 |

| Full assist         | The user forces the VCO core (VCO_SEL), amplitude settings (VCO_DACISET), and frequency band (VCO_CAPCTRL) and manually sets the value. | Choose by readback | 1                                                       | Choose by readback         |

For the no-assist method, just set VCO SEL = 7 and this is done. For partial-assist, the VCO calibration speed can be improved by changing the VCO SEL bit according to frequency. Note that the frequency is not the actual VCO core range, but actually favors choosing the VCO. This is not only optimal for VCO calibration speed, but required for reliable locking.

Table 7-5. Minimum VCO\_SEL for Partial Assist

| fvco              | VCO CORE (MIN) |

|-------------------|----------------|

| 7550 - 8740 MHz   | VCO1           |

| 8740 - 10000 MHz  | VCO2           |

| 10000 - 10980 MHz | VCO3           |

| 10980 - 12100 MHz | VCO4           |

| 12100 - 13080 MHz | VCO5           |

| 13080 - 14180 MHz | VCO6           |

| 14180 - 15100 MHz | VCO7           |

|                   |                |

For fastest calibration time, it is ideal to use the minimum VCO core as recommended in Table 7-5. The Table 7-6 shows typical VCO calibration times (in µs) for this choice in bold as well as showing how long the calibration time is increased if a higher than necessary VCO core is chosen. Realize that these calibration times are specific to these f<sub>OSC</sub> and f<sub>PD</sub> conditions specified and at the boundary of two cores, sometimes the calibration time can be increased.

Table 7-6. Typical Calibration Times for f<sub>OSC</sub> = f<sub>PD</sub> = 100 MHz Based on VCO\_SEL

|                        | J.   | VCO_SEL     |             |      |             |      |         |

|------------------------|------|-------------|-------------|------|-------------|------|---------|

| f <sub>VCO</sub> (GHz) | VCO7 | VCO6        | VCO5        | VCO4 | VCO3        | VCO2 | VCO1    |

| 8.1                    | 650  | 540         | 550         | 440  | 360         | 230  | 110     |

| 9.3                    | 610  | 530         | 540         | 430  | 320         | 220  | Invalid |

| 10.4                   | 590  | 520         | 530         | 430  | 240 Invalid |      | alid    |

| 11.4                   | 340  | 290         | 280         | 180  | 180 Invalid |      |         |

| 12.5                   | 270  | 170         | 120 Invalid |      |             |      |         |

| 13.6                   | 240  | 130 Invalid |             |      |             |      |         |

| 14.7                   | 160  |             | Invalid     |      |             |      |         |

#### 7.3.7.2 Determining the VCO Gain

The VCO gain varies between the seven cores, and is the lowest at the lowest end of the band and highest at the highest end of each band. For a more accurate estimation, use Table 7-7.

| Tab | ا ما | 7_7 | V | CC | ) Ga | ain |

|-----|------|-----|---|----|------|-----|

|     |      |     |   |    |      |     |

| f1    | f2    | K <sub>VCO</sub> 1 | K <sub>VCO</sub> 2 |

|-------|-------|--------------------|--------------------|

| 7550  | 8740  | 78                 | 114                |

| 8740  | 10000 | 91                 | 125                |

| 10000 | 10980 | 112                | 136                |

| 10980 | 12100 | 136                | 168                |

| 12100 | 13080 | 171                | 206                |

| 13080 | 14180 | 188                | 218                |

| 14180 | 15100 | 218                | 248                |

Based ion Table 7-7, Equation 4 can estimate the VCO gain for an arbitrary VCO frequency of f<sub>VCO</sub>:

$$K_{VCO} = K_{VCO}1 + (K_{VCO}2 - K_{VCO}1) \times (f_{VCO} - f_1) / (f_2 - f_1)$$

(4)

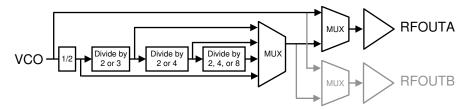

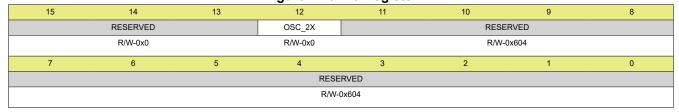

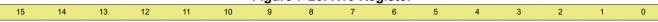

#### 7.3.8 Channel Divider

To go below the VCO lower bound of 7550 MHz, the channel divider can be used. The channel divider consists of four segments, and the total division value is equal to the multiplication of them. Therefore, not all values are valid.

Figure 7-2. Channel Divider

When the channel divider is used, there are limitations on the values. Table 7-8 shows how these values are implemented and which segments are used.

**Table 7-8. Channel Divider Segments**

| EQUIVALENT     | FREQUENCY                   | OUTPUT FREQUENCY (MHz) |          | CHDIV[4:0] | SEG0 | SEG1 | SEG2 | SEG3 |

|----------------|-----------------------------|------------------------|----------|------------|------|------|------|------|

| DIVISION VALUE | LIMITATION                  | MIN                    | MAX      | CHDIV[4.0] | SEGU | SEGI | SEG2 | 3203 |

| 2              |                             | 3775                   | 7550     | 0          | 2    | 1    | 1    | 1    |

| 4              | None                        | 1887.5                 | 3775     | 1          | 2    | 2    | 1    | 1    |

| 6              |                             | 1258.333               | 2516.667 | 2          | 2    | 3    | 1    | 1    |

| 8              |                             | 943.75                 | 1437.5   | 3          | 2    | 2    | 2    | 1    |

| 12             |                             | 629.167                | 958.333  | 4          | 2    | 3    | 2    | 1    |

| 16             |                             | 471.875                | 718.75   | 5          | 2    | 2    | 4    | 1    |

| 24             |                             | 314.583                | 469.167  | 6          | 2    | 3    | 4    | 1    |

| 32             | f < 11 F CU =               | 235.938                | 359.375  | 7          | 2    | 2    | 8    | 1    |

| 48             | f <sub>VCO</sub> ≤ 11.5 GHz | 157.292                | 239.583  | 8          | 2    | 3    | 8    | 1    |

| 64             |                             | 117.969                | 179.688  | 9          | 2    | 2    | 8    | 2    |

| 96             |                             | 78.646                 | 119.792  | 10         | 2    | 3    | 8    | 2    |

| 128            |                             | 58.984                 | 89.844   | 11         | 2    | 2    | 8    | 4    |

| 192            |                             | 39.323                 | 59.896   | 12         | 2    | 3    | 8    | 4    |

| Invalid        | n/a                         | n/a                    | n/a      | 13 - 31    | n/a  | n/a  | n/a  | n/a  |

The channel divider is powered up whenever an output (OUTx\_MUX) is selected to the channel divider or SYSREF, regardless of whether it is powered down or not. When an output is not used, TI recommends selecting the VCO output to ensure that the channel divider is not unnecessarily powered up.

# Instruments

#### Table 7-9. Channel Divider

| OUTA MUX        | OUTB MUX                  | CHANNEL DIVIDER |  |

|-----------------|---------------------------|-----------------|--|

| Channel Divider | X                         | Powered up      |  |

| X               | Channel Divider or SYSREF | Powered up      |  |

| All other       | Powered down              |                 |  |

#### 7.3.9 Output Buffer

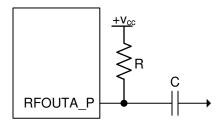

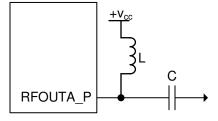

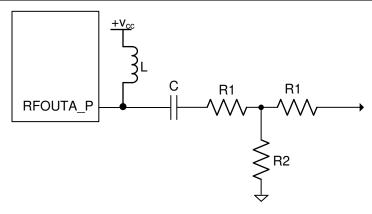

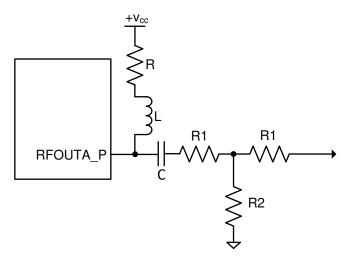

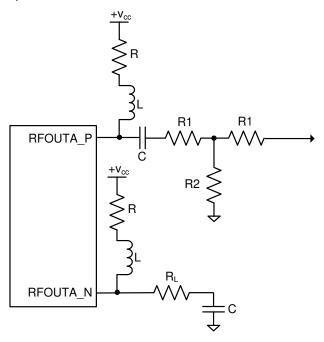

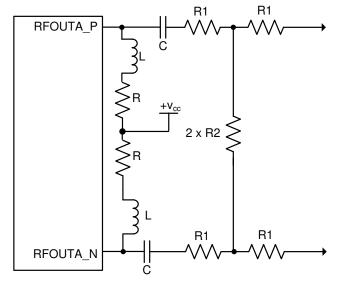

The RF output buffer type is open-collector that requires an external pullup to  $V_{CC}$ . This component may be a  $50-\Omega$  resistor or an inductor. The inductor has less controlled impedance, but higher power. For the inductor case, it is often helpful to follow this with a resistive pad. The output power can be programmed to various levels or disabled while still keeping the PLL in lock.

Table 7-10. OUTx\_PWR Recommendations

| f <sub>OUT</sub>                  | RESTRICTIONS  | COMMENTS                                                                                                                                              |

|-----------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 MHz ≤ f <sub>OUT</sub> ≤ 5 GHz | None          | At lower frequencies, the output buffer impedance is high, so the 50- $\Omega$ pullup will make the output impedance look somewhat like 50 $\Omega$ . |

| 5 GHz ≤ f <sub>OUT</sub> ≤ 10 GHz | OUTx_PWR ≤ 31 | In this range, parasitic inductances have some impact, so the output setting is restricted.                                                           |

| 10 GHz < f <sub>OUT</sub>         | OUTx_PWR ≤ 20 | At these higher frequency ranges, it is best to keep below 20 for highest power and optimal noise floor.                                              |

#### 7.3.10 Powerdown Modes

The LMX2694-EP can be powered up and down using the CE pin or the POWERDOWN bit. When the device comes out of the powered-down state, either by resuming the POWERDOWN bit to zero or by pulling back CE pin HIGH (if it was powered down by CE pin), register R0 must be programmed with FCAL EN high again to recalibrate the device.

#### 7.3.11 Treatment of Unused Pins

This device has several pins for many features and there is a preferred way to treat these pins if not needed. For the input pins, a series resistor is recommend, but they can be directly shorted.

Table 7-11. Recommended Treatment of Pins

| PINS             | RECOMMENDED TREATMENT IF NOT USED                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE               | $V_{CC}$ with 1 k $\Omega$ .                                                                                                                                                           |

| SYNC, SYSREFREQ  | Ground with 1 $k\Omega$ .                                                                                                                                                              |

| OSCIN_P, OSCIN_N | Ground with 50 $\Omega$ after AC-coupling capacitors. If one of the complimentary sides is used and other side is not, impedance looking out should be similar for both of these pins. |

| SCK, SDI         | Ground with 1 $k\Omega$ .                                                                                                                                                              |

| CS#              | $V_{CC}$ with 1 k $\Omega$ .                                                                                                                                                           |

| RFOUTx           | $V_{CC}$ with 50 $\Omega$ . If one of the complimentary sides is used and the other side is not, impedance looking out should be similar for both of these pins.                       |

| MUXOUT           | Ground with 10 $k\Omega$ .                                                                                                                                                             |

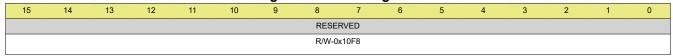

## 7.3.12 Phase Synchronization

#### 7.3.12.1 General Concept

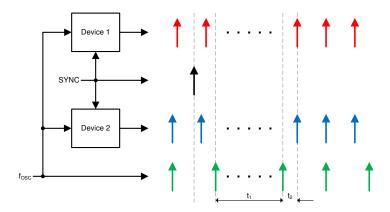

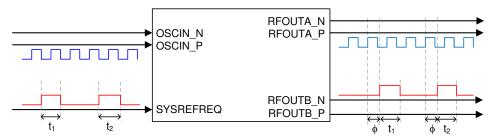

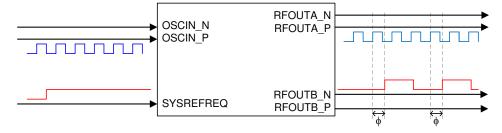

The SYNC pin allows the user to synchronize the LMX2694-EP such that the delay from the rising edge of the OSCIN signal to the output signal is deterministic. Initially, the devices are locked to the input, but are not synchronized. The user sends a synchronization pulse that is reclocked to the next rising edge of the OSCIN pulse. After a given time, t<sub>1</sub>, the phase relationship from OSCIN to f<sub>OUT</sub> will be deterministic. This time is dominated by the sum of the VCO calibration time, the analog setting time of the PLL loop, and the MASH RST CNT if used in fractional mode.

Figure 7-3. Phase SYNC Mechanism

When the SYNC feature is enabled, part of the channel divide may be included in the feedback path.

Table 7-12. IncludedDivide With VCO PHASE SYNC = 1

| 10.010 1 1=1010                 |                                  |                 |

|---------------------------------|----------------------------------|-----------------|

| OUTx_MUX                        | CHANNEL DIVIDER                  | IncludedDivide  |

| OUTA_MUX = OUTB_MUX = 1 ("VCO") | Don't care                       | 1               |

| All other valid conditions      | Divisible by 3 but NOT 24 or 192 | SEG0 x SEG1 = 6 |

| All other valid conditions      | All other values                 | SEG0 x SEG1 = 4 |

Figure 7-4. Phase SYNC Diagram

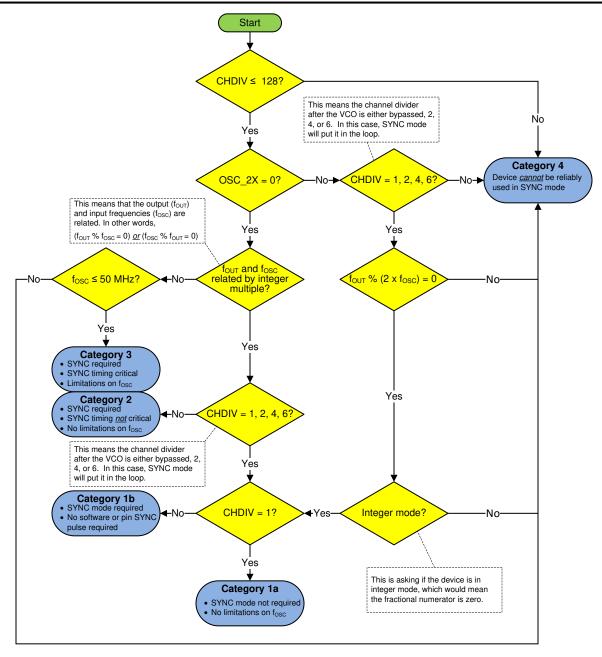

## 7.3.12.2 Categories of Applications for SYNC

The requirements for SYNC depend on certain setup conditions. In cases that the SYNC is not timing critical, it can be done through software by toggling the VCO\_PHASE\_SYNC bit from 0 to 1. Figure 7-5 gives the different categories. When it is timing critical, then it must be done through the pin and the setup and hold times for the OSCIN pin are critical. For timing critical SYNC (Category 3 only), adhere to the following guidelines.

Table 7-13. SYNC Pin Timing Characteristics for Category 3 SYNC

|                    | PARAMETER                                      | MIN | MAX | UNIT |

|--------------------|------------------------------------------------|-----|-----|------|

| f <sub>OSC</sub>   | Input reference frequency                      |     | 40  | MHz  |

| t <sub>SETUP</sub> | Setup time between SYNC and OSCIN rising edges | 9   |     | ns   |

| t <sub>HOLD</sub>  | Hold time between SYNC and OSCIN rising edges  | 4   |     | ns   |

Submit Document Feedback

Copyright © 2022 Texas Instruments Incorporated

Figure 7-5. Determining the SYNC Category

#### 7.3.12.3 Procedure for Using SYNC

This procedure must be used to put the device in SYNC mode.

- 1. Use the flowchart to determine the SYNC category.

- 2. Make determinations for OSCIN and using SYNC based on the category.

- a. If category 4, SYNC cannot be performed in this setup.

- b. If category 3, ensure that the maximum f<sub>OSC</sub> frequency for SYNC is not violated and there are hardware accommodations to use the SYNC pin.

- 3. If the channel divide is used, determine the included channel divide value which will be 2 × SEG1 of the channel divide.

- a. If OUTA\_MUX is not channel divider and OUTB\_MUX is not channel divider or SYSREF, then IncludedDivide = 1.

- b. Otherwise, IncludedDivide = 2 × SEG1. In the case that the channel divider is 2, then IncludedDivide = 4.

- 4. If not done already, divide the N divider and fractional values by the included channel divide to account for the included channel divide.

- 5. Program the device with the VCO\_PHASE\_SYNC = 1. Note that this does not count as applying a SYNC to device (for category 2).

- 6. Apply the SYNC, if required.

- a. If category 2, VCO\_PHASE\_SYNC can be toggled from 0 to 1. Alternatively, a rising edge can be sent to the SYNC pin and the timing of this is not critical.

- b. If category 3, the SYNC pin must be used, and the timing must be away from the rising edge of the OSCIN signal.

#### 7.3.12.4 SYNC Input Pin

If not using SYNC mode (VCO\_PHASE\_SYNC = 0), the INPIN\_IGNORE bit must be set to one, otherwise it causes issues with lock detect. If the pin is desired for to be used and VCO\_PHASE\_SYNC = 1, then set  $INPIN_IGNORE = 0$ .

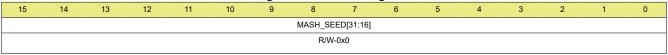

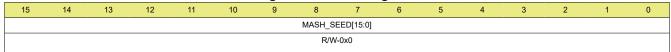

#### 7.3.13 Phase Adjust

The MASH\_SEED word can use the sigma-delta modulator to shift output signal phase with respect to the input reference. If a SYNC pulse is sent (software or pin) or the MASH is reset with MASH\_RST\_N, then this phase shift is from the initial phase of zero. If the MASH\_SEED word is written to, then this phase is added. The phase shift is calculated as below.

For example:

MASH\_SEED = 1; PLL\_DEN = 12; CHDIV = 16

If VCO PHASE SYNC = 0, Phase shift = 360 × (1 / 12) × (1 / 16) = 1.875 degrees.

If VCO PHASE SYNC = 1, Phase shift = 360 × (1 / 12) × (4 / 16) = 7.5 degrees.

There are several considerations when using MASH\_SEED.

- Phase shift can be done with a PLL\_NUM = 0, but MASH\_ORDER must be greater than zero. For MASH\_ORDER = 1, the phase shifting only occurs when MASH\_SEED is a multiple of PLL\_DEN.

- For the  $2^{nd}$  order modulator, PLL  $N \ge 45$ . For the  $3^{rd}$  order modulator, PLL  $N \ge 49$ .

When using MASH\_SEED in the case where IncludedDivide > 1, there are several additional considerations in order to get the phase shift to be monotonically increasing with MASH\_SEED.

- TI recommends to use MASH\_ORDER ≤ 2.

- When using the 2<sup>nd</sup> order modulator for VCO frequencies below 10 GHz (when IncludedDivide = 6) or 9 GHz (when IncludedDivide = 4), it may be necessary to increase the PLL\_N value much higher or change to the 1<sup>st</sup> order modulator. When this is necessary depends on the VCO frequency, IncludedDivide, and PLL\_N value.

#### 7.3.14 Fine Adjustments for Phase Adjust and Phase SYNC

Phase SYNC refers to the process of getting the same phase relationship for every power up cycle and each time assuming that a given programming procedure is followed. However, there are some adjustments that can be made to get the most accurate results. As for the consistency of the phase SYNC, the only source of variation could be if the VCO calibration chooses a different VCO core and capacitor, which can introduce a bimodal distribution with about 10 ps of variation. If this 10 ps is not desirable, then it can be eliminated by reading back the VCO core, capcode, and DACISET values and forcing these values to ensure the same calibration settings every time. The delay through the device varies from part to part and can be on the order of 60 ps. This part to part variation can be calibrated out with the MASH\_SEED. The variation in delay through the device also changes on the order of +2.5 ps/°C, but devices on the same board likely have similar temperatures, so this will somewhat track. In summary, the device can be made to have consistent delay through the part and there are

Submit Document Feedback

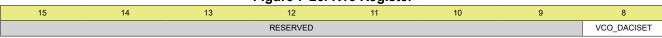

Copyright © 2022 Texas Instruments Incorporated