# LMX1205 Low-Noise, High-Frequency JESD Buffer/Multiplier/Divider

#### 1 Features

- Output frequency: 300MHz to 12.8GHz

- Noiseless adjustable input delay up to 60ps with 1.1ps resolution

- Individual adjustable output delays up to 55ps with 0.9ps resolution

- Ultra-low noise

- Noise floor: –159dBc/Hz at 6GHz output

- Additive jitter (DC to f<sub>CLK</sub>): 36fs

- Additive jitter (100Hz to 100MHz): 10fs

- Four high-frequency clocks with corresponding SYSREF outputs

- Shared divide by 1 (Bypass), 2, 3, 4, 5, 6, 7,

- Shared programmable multiplier x2, x3, x4, x5, x6, x7 and x8

- LOGICLK output with corresponding SYSREF

- On separate divide bank

- 1, 2, 4 pre-divider

- 1 (bypass), 2, ..., 1023 post divider

- Second logic clock option with additional divider 1, 2, 4 & 8

- Six programmable output power levels

- Synchronized SYSREF clock outputs

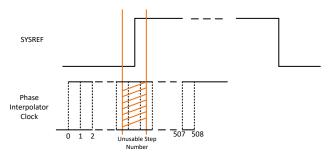

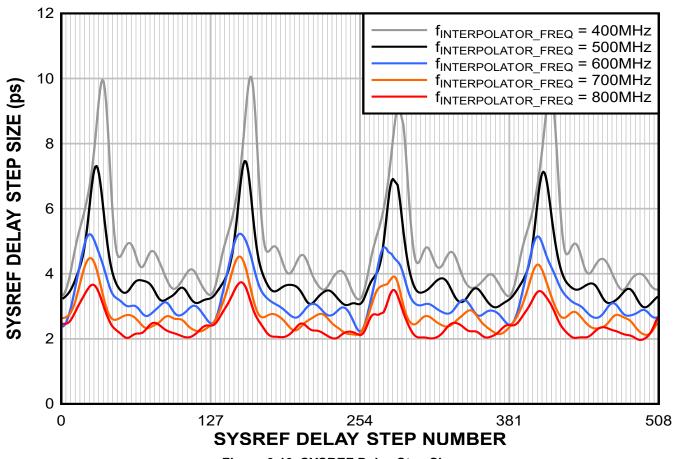

- 508 delay step adjustments of less than 2.5ps at 12.8GHz

- Generator, repeater and repeater retime modes

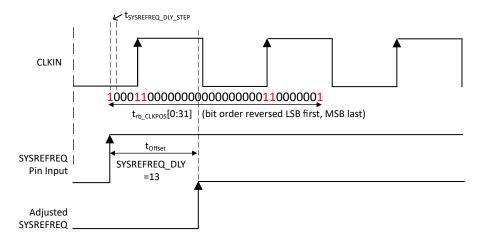

- Windowing feature for SYSREFREQ pins to optimize timing

- SYNC feature to all divides and multiple devices

- Operating voltage: 2.5V

- Operating temperature: -40°C to +85°C

### 2 Applications

- Test & Measurement:

- Oscilloscope

- Wireless equipment testers

- Wideband digitizers

- Aerospace & Defense:

- Radar

- Electronic warfare

- Seeker Front end

- Munitions

- Phase array antenna / Beam forming

- General Purpose:

- Data converter clocking

- Clock buffer distribution / division

### 3 Description

The high frequency capability, extremely low jitter and programmable clock input and output delay of this device, makes a great approach to clock high precision, high-frequency data converters without degradation of signal-to-noise ratio. Each of the four high frequency clock outputs and additional LOGICLK outputs with larger divider range, is paired with a SYSREF output clock signal. The SYSREF signal for JESD204B/C interfaces can either be internally generated or passed in as an input and re-clocked to the device clocks. The noiseless delay adjustment at input path of the high frequency clock input and individual clock output paths insures low skew clocks in multi-channel system. For data converter clocking application, having the jitter of the clock less than the aperture jitter of the data converter is important. In applications where more than four data converters need to be clocked, a variety of cascading architectures can be developed using multiple devices to distribute all the high frequency clocks and SYSREF signals required. This device, combined with an ultra-low noise reference clock source, is an exemplary choice for clocking data converters, especially when sampling above 3GHz.

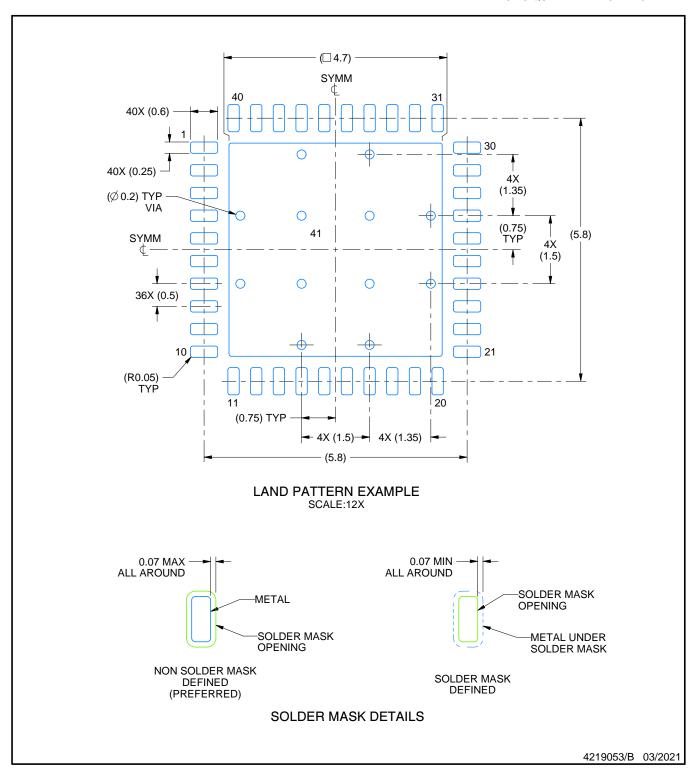

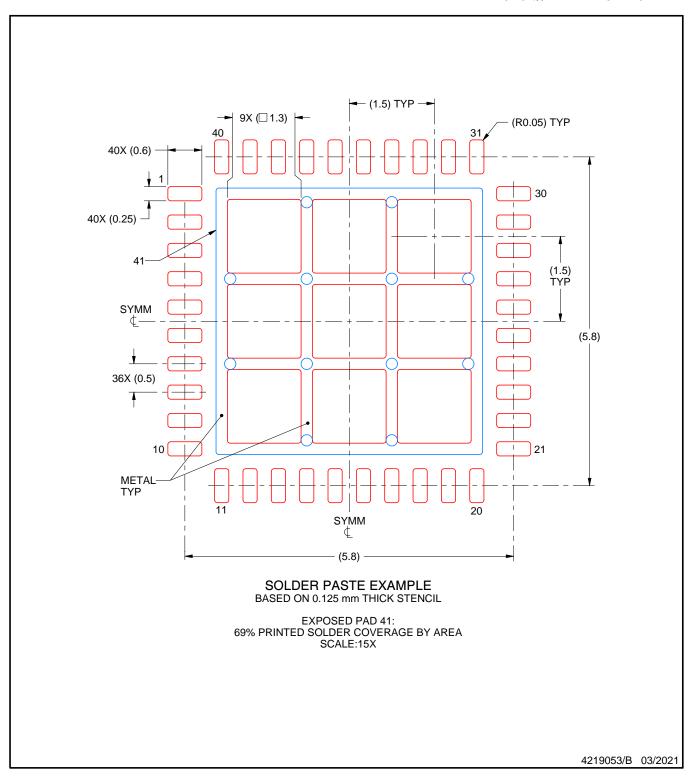

### **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| LMX1205     | RHA (VQFN, 40)         | 6mm × 6mm                   |

- For all available packages, see Section 11.

- The package size (length × width) is a nominal value and includes pins, where applicable.

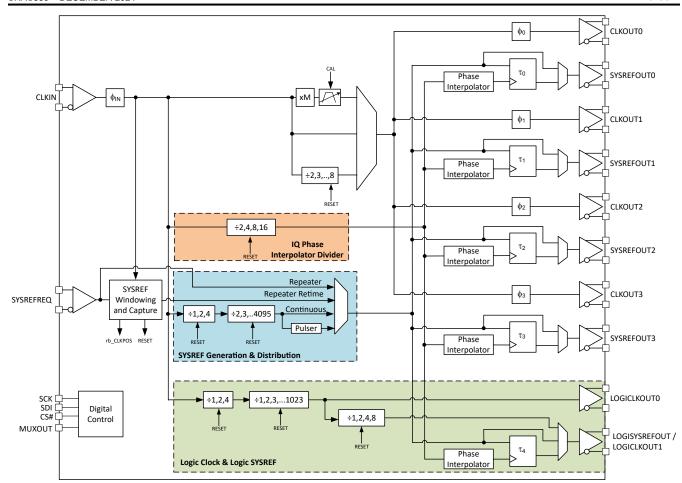

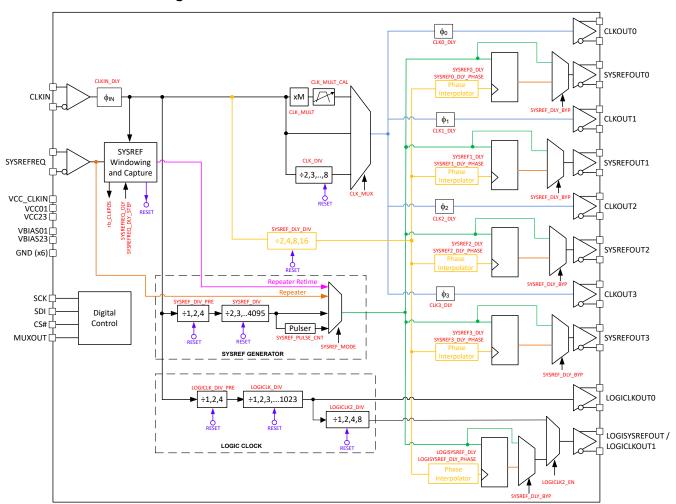

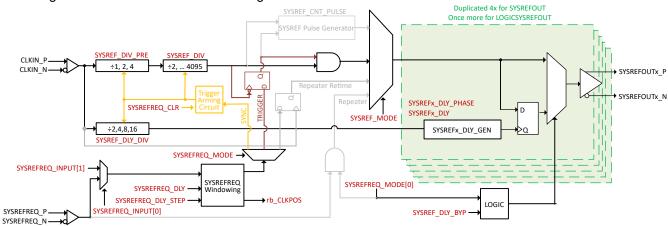

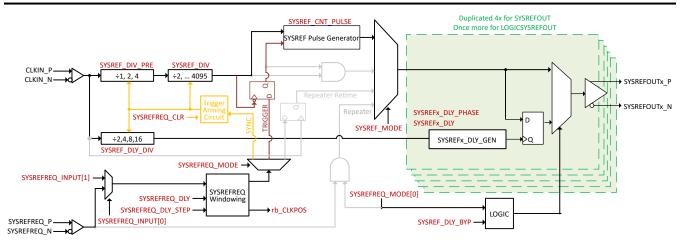

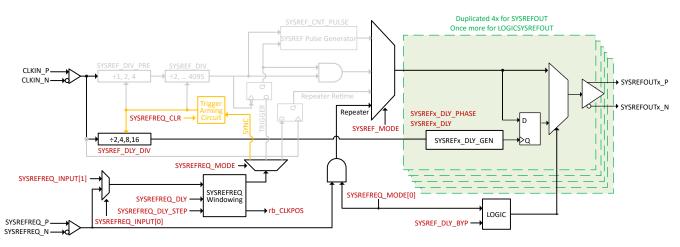

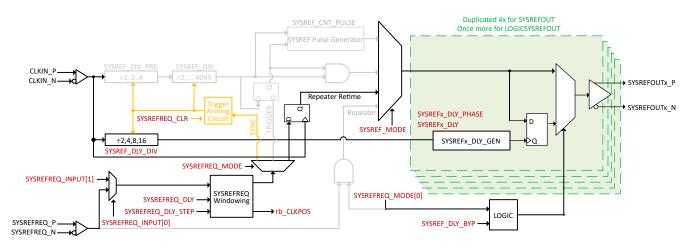

**Block Diagram**

# **Table of Contents**

| 1 Features                                 | 1  | 7 Register Map                                       | 37 |

|--------------------------------------------|----|------------------------------------------------------|----|

| 2 Applications                             |    | 7.1 Device Registers                                 |    |

| 3 Description                              |    | 8 Application and Implementation                     |    |

| 4 Pin Configuration and Functions          |    | 8.1 Reference                                        |    |

| 5 Specifications                           |    | 8.2 Power Supply Recommendations                     | 60 |

| 5.1 Absolute Maximum Ratings               |    | 8.3 Layout                                           | 60 |

| 5.2 ESD Ratings                            |    | 9 Device and Documentation Support                   |    |

| 5.3 Recommended Operating Conditions       | 6  | 9.1 Device Support                                   | 61 |

| 5.4 Thermal Information                    |    | 9.2 Documentation Support                            | 62 |

| 5.5 Electrical Characteristics             | 7  | 9.3 Receiving Notification of Documentation Updates. |    |

| 5.6 Timing Requirements                    |    | 9.4 Support Resources                                |    |

| 5.7 Timing Diagram                         |    | 9.5 Trademarks                                       |    |

| 5.8 Typical Characteristics                |    | 9.6 Electrostatic Discharge Caution                  | 62 |

| 6 Detailed Description                     |    | 9.7 Glossary                                         |    |

| 6.1 Overview                               |    | 10 Revision History                                  |    |

| 6.2 Functional Block Diagram               | 19 | 11 Mechanical, Packaging, and Orderable              |    |

| 6.3 Feature Description                    | 20 | Information                                          | 62 |

| 6.4 Device Functional Modes Configurations | 35 |                                                      |    |

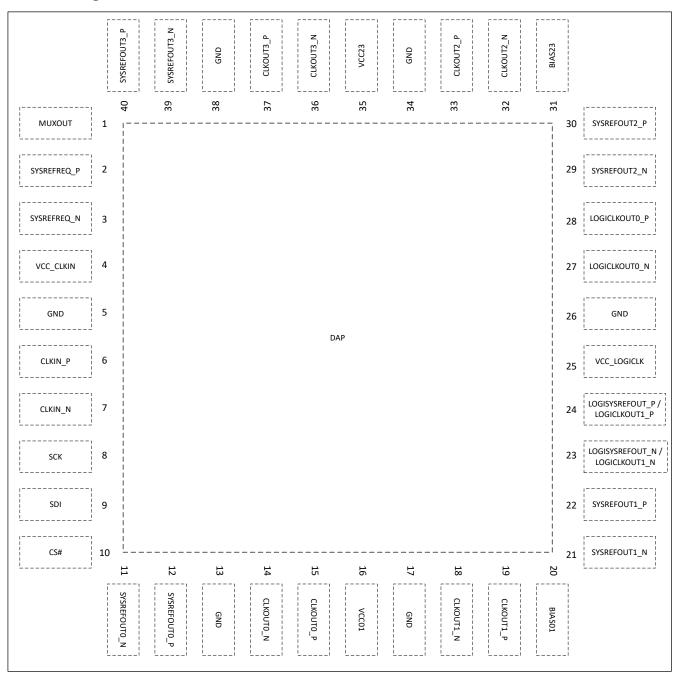

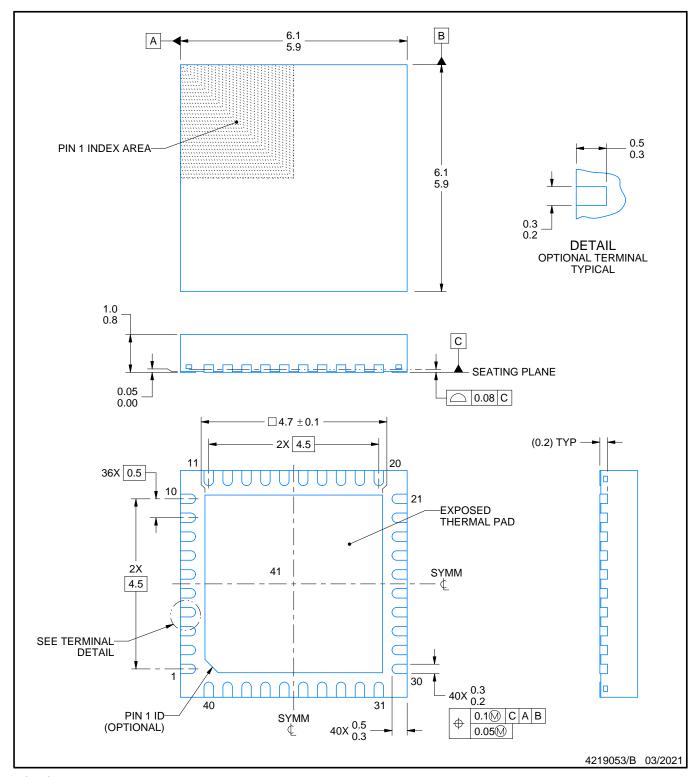

# **4 Pin Configuration and Functions**

Figure 4-1. RHA Package 40-Pin VQFN Top View

Submit Document Feedback

### Table 4-1. Pin Functions

|                                    |                  |                     | 4-1. Pin Functions                                                                                                                                                                                                                              |

|------------------------------------|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                               | NO.              | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                     |

| BIAS01                             | 20               | BYP                 | If not using the multiplier, this pin can be left open. If using the multiplier, bypass this pin to GND with a 10nF capacitor for optimal noise performance.                                                                                    |

| BIAS23                             | 31               | ВҮР                 | If not using the multiplier, this pin can be left open. If using the multiplier, bypass this pin to GND with a $10\mu F$ and $0.1\mu F$ capacitor for optimal noise performance.                                                                |

| CLKIN_N                            | 7                |                     | Differential clock input pair. Internal $50\Omega$ termination at each pin. AC-couple                                                                                                                                                           |

| CLKIN_P                            | 6                | I                   | with a capacitor appropriate to the input frequency (typically $0.1\mu F$ or smaller). If using single-ended, provide the input at CLKIN_N pin and terminate unused CLKIN_P with a series AC-coupling capacitor and $50\Omega$ resistor to GND. |

| CLKOUT0_N                          | 14               |                     |                                                                                                                                                                                                                                                 |

| CLKOUT0_P                          | 15               |                     |                                                                                                                                                                                                                                                 |

| CLKOUT1_N                          | 18               |                     | Differential clock output pairs. Each pin is an open-collector output with                                                                                                                                                                      |

| CLKOUT1_P                          | 19               | 0                   | internally integrated $50\Omega$ resistor with programmable output swing. AC                                                                                                                                                                    |

| CLKOUT2_N                          | 32               | O                   | coupling is required. The pin expects $100\Omega$ differential load or $50\Omega$ load at                                                                                                                                                       |

| CLKOUT2_P                          | 33               |                     | each pin.                                                                                                                                                                                                                                       |

| CLKOUT3_N                          | 36               |                     |                                                                                                                                                                                                                                                 |

| CLKOUT3_P                          | 37               |                     |                                                                                                                                                                                                                                                 |

| CS#                                | 10               | I                   | SPI chip select. High impedance CMOS input. Accepts up to 3.3V. This pin requires $200\Omega$ resistor in series.                                                                                                                               |

| DAP                                | DAP              | CND                 | Customed the second size                                                                                                                                                                                                                        |

| GND                                | 5,13,17,26,34,38 | GND                 | Ground these pins.                                                                                                                                                                                                                              |

| LOGICLKOUT0_N                      | 27               |                     | Differential Logic clock output pair. Selectable CML or LVDS format. LVDS                                                                                                                                                                       |

| LOGICLKOUT0_P                      | 28               | 0                   | format has programmable common-mode voltage. CML format requires external pull resistors.                                                                                                                                                       |

| LOGISYSREFOUT_N /<br>LOGICLKOUT1_N | 23               | 0                   | Differential Logic clock output pair. Selectable CML or LVDS format. LVDS format has programmable common-mode voltage. CML format requires                                                                                                      |

| LOGISYSREFOUT_P /<br>LOGICLKOUT1_P | 24               | O                   | external pull resistors.                                                                                                                                                                                                                        |

| MUXOUT                             | 1                | 0                   | Multiplexed pin serial data readback and lock status of the multiplier.                                                                                                                                                                         |

| SCK                                | 8                | I                   | SPI clock. High impedance CMOS input. Accepts up to 3.3V. This pin requires $200\Omega$ resistor in series.                                                                                                                                     |

| SDI                                | 9                | I                   | SPI data input. High impedance CMOS input. Accepts up to 3.3V. This pin requires $200\Omega$ resistor in series.                                                                                                                                |

| SYSREFREQ_N                        | 3                |                     | Differential SYSREF request input for JESD204B/C support. Internal 50Ω                                                                                                                                                                          |

| SYSREFREQ_P                        | 2                | I                   | termination at each pin. Supports AC and DC coupling which can directly accept a common mode voltage of 1.2V to 2V.                                                                                                                             |

| SYSREFOUT0_N                       | 11               |                     |                                                                                                                                                                                                                                                 |

| SYSREFOUT0_P                       | 12               |                     |                                                                                                                                                                                                                                                 |

| SYSREFOUT1_N                       | 21               |                     |                                                                                                                                                                                                                                                 |

| SYSREFOUT1_P                       | 22               | •                   | Differential SYSREF CML output pairs for JESD204B/C support. Supports                                                                                                                                                                           |

| SYSREFOUT2_N                       | 29               | 0                   | AC and DC coupling with programmable common-mode voltage of 0.5V to 1.5V. The pin expects a $100\Omega$ differential load.                                                                                                                      |

| SYSREFOUT2_P                       | 30               |                     | , , ,                                                                                                                                                                                                                                           |

| SYSREFOUT3_N                       | 39               |                     |                                                                                                                                                                                                                                                 |

| SYSREFOUT3_P                       | 40               |                     |                                                                                                                                                                                                                                                 |

| VCC_CLKIN                          | 4                |                     |                                                                                                                                                                                                                                                 |

| VCC_LOGICLK                        | 25               |                     | Connect to a 2.5V supply. Recommend a shunt high frequency capacitor                                                                                                                                                                            |

| VCC01                              | 16               | PWR                 | (typically 0.1µF or smaller) closest to the pin in parallel with larger capacitors (typically 1µF and 10µF).                                                                                                                                    |

| VCC23                              | 35               |                     |                                                                                                                                                                                                                                                 |

|                                    |                  |                     |                                                                                                                                                                                                                                                 |

(1) BYP = Bypass; GND = Ground; I = Input; O = Output; PWR = Power

## **5 Specifications**

### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                  | MIN  | MAX                   | UNIT |

|------------------|----------------------------------|------|-----------------------|------|

| $V_{DD}$         | Power supply voltage             | -0.3 | 2.75                  | V    |

| V <sub>IN</sub>  | DC Input Voltage (SCK, SDI, CSB) | GND  | 3.6                   | V    |

| V <sub>IN</sub>  | DC Input Voltage (SYSREFREQ)     | GND  | V <sub>DD</sub> + 0.3 | V    |

| V <sub>IN</sub>  | AC Input Voltage (CLKIN)         |      | $V_{DD}$              | Vpp  |

| TJ               | Junction temperature             |      | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature              | -65  | 150                   | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 5.2 ESD Ratings

|                                            |                                                                                          |                                                                             | VALUE | UNIT |

|--------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatio discharge                                                                  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup> | ±2500 | V    |

|                                            | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500                                                                        | V     |      |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## 5.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                      | MIN | NOM | MAX | UNIT |

|----------------|----------------------|-----|-----|-----|------|

| $V_{DD}$       | Supply voltage       | 2.4 | 2.5 | 2.6 | V    |

| T <sub>A</sub> | Ambient temperature  | -40 |     | 85  | °C   |

| TJ             | Junction temperature |     |     | 125 | °C   |

#### 5.4 Thermal Information

| SYMBOL                | THERMAL METRIC(1)                            | VALUE | UNIT |

|-----------------------|----------------------------------------------|-------|------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 24.7  | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 12.8  | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 6.8   | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.1   | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 6.7   | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.5   | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

## **5.5 Electrical Characteristics**

2.4 V ≤ VCC ≤ 2.6 V, -40°C ≤ TA ≤ +85°C. Typical values are at VCC = 2.5 V, 25°C (unless otherwise noted)

| PARAMETER             |                                        | TEST CONDITIONS                                                        |                                                                   | MIN TYP |           | MAX  | UNIT     |

|-----------------------|----------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|---------|-----------|------|----------|

| Current Co            | nsumption                              |                                                                        |                                                                   |         |           |      |          |

|                       |                                        | Powered up, all Clock<br>SYSREFs on                                    | outputs and                                                       |         | 1130      |      |          |

| I <sub>CC</sub>       | Supply Current (1)                     | Powered up, all Clock<br>SYSREF off                                    | outputs on, all                                                   |         | 700       |      | mA       |

|                       |                                        | Powered up, all Clock off                                              | outputs and SYSREF                                                |         | 370       |      |          |

|                       |                                        | Powered down                                                           |                                                                   |         | 13.5      |      |          |

|                       | Additive output current                | OUTx_PWR = 6                                                           |                                                                   |         | 64        |      |          |

|                       | Multiplier current                     | Divide, CLK_DIV = 8                                                    |                                                                   |         | 60        |      |          |

| I <sub>ADD</sub>      | waitiplier current                     | Multiplier, CLK_MULT                                                   | = x8                                                              |         | 360       |      | mA       |

| ADD                   | SYSREF current                         | Running at 100MHz<br>Generation mode, all                              | outputs on                                                        |         | 425       |      |          |

|                       | LOGICLK current                        | LOGICLK enabled wit                                                    | h LOGISYSREF                                                      |         | 85        |      |          |

| SYSREF                |                                        |                                                                        |                                                                   |         |           |      |          |

| f <sub>SYSREF</sub>   | SYSREF output frequency                | Generator mode                                                         | Generator mode                                                    |         |           | 200  | MHz      |

| f <sub>SYSREF</sub>   | SYSREF output frequency                | Repeater mode                                                          | Repeater mode                                                     |         |           | 100  | MHz      |

| T <sub>SYNC</sub>     | Pulse width required for SYNC signal   | Tsync = 6xT of f <sub>CLKIN</sub> ,                                    | f <sub>CLKIN</sub> = 6GHz                                         | 1000    |           |      | ps       |

| Δt                    | SYSREF delay step size                 | Δt = SYSREF_DLY_D<br>f <sub>CLKIN)</sub> , f <sub>CLKIN</sub> = 12.8GH |                                                                   |         | 3         |      | ps       |

|                       |                                        | SYSREFOUT                                                              |                                                                   |         | 45        |      | ps       |

| t <sub>RISE</sub>     | Rise time (20% to 80%)                 | LOCIOVODEFOLIT                                                         | CML                                                               |         | 65        |      | ps       |

|                       |                                        | LOGISYSREFOUT                                                          | LVDS                                                              |         | 120       | 175  | ps       |

|                       |                                        | SYSREFOUT                                                              |                                                                   |         | 45        |      | ps       |

| t <sub>FALL</sub>     | Fall time (20% to 80%)                 | LOGISYSREFOUT                                                          | CML<br>LVDS                                                       |         | 65<br>120 | 175  | ps<br>ps |

|                       |                                        | SYSREFOUT, SYSREFx_PWR = 4,<br>SYSREFx_VCM = 10                        |                                                                   |         | 0.9       | 173  | Vpp      |

| $V_{OD}DIFF$          | Differential pk-pk output voltage      | 313KLI X_VCIVI = 10                                                    | CML                                                               |         | 0.9       |      | Vpp      |

|                       |                                        | LOGISYSREFOUT                                                          | LVDS                                                              |         | 0.7       |      | Vpp      |

|                       |                                        | 0.400000                                                               | CML<br>SYSREFx_VCM=41<br>, 100Ω Differential<br>Load              | 1.35    | 1.5       | 1.65 | V        |

| V <sub>SYSREFCM</sub> | Common mode voltage                    | SYSREFOUT                                                              | CML<br>SYSREFx_VCM=4,<br>100Ω Differential<br>Load                | 0.45    | 0.5       | 0.55 | V        |

|                       |                                        | LOGISYSREFOUT                                                          | LVDS<br>100Ω Differential<br>Load                                 | 0.75    |           | 1.4  | V        |

| SYSREFRE              | Q Pins                                 |                                                                        |                                                                   |         |           |      |          |

| V <sub>SYSREFIN</sub> | Differential pk-pk Voltage input range | AC differential voltage                                                |                                                                   | 0.8     |           | 2    | Vpp      |

| V <sub>SYSREFIN</sub> | Single-ended voltage input range       | AC Coupled to<br>SYSREFREQ_P;<br>SYSREFREQ_N AC<br>coupled to GND      | AC Coupled to<br>SYSREFREQ_P;<br>SYSREFREQ_N<br>AC coupled to GND | 0.6     |           | 1.7  | Vpp      |

| V <sub>CM</sub>       | Input common mode voltage              | Differential 100Ω Termination, DC coupled Set externally               |                                                                   | 1.2     | 1.3       | 2    | V        |

| Clock Input           | t                                      | 1                                                                      |                                                                   |         |           |      |          |

$2.4 \text{ V} \le \text{VCC} \le 2.6 \text{ V} -40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ . Typical values are at VCC =  $2.5 \text{ V} \cdot 25^{\circ}\text{C}$  (unless otherwise noted)

|                           | PARAMETER                                    | TEST COM                                                  | IDITIONS                                                    | MIN  | TYP    | MAX  | UNIT    |

|---------------------------|----------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|------|--------|------|---------|

| f <sub>IN</sub>           | Input frequency                              |                                                           |                                                             | 0.3  |        | 12.8 | GHz     |

| P <sub>IN</sub>           | Input power                                  | Single-ended power at CLKIN_P or CLKIN_N                  |                                                             | 0    |        | 10   | dBm     |

| φ <sub>IN</sub>           | Input delay range                            |                                                           |                                                             |      | 60     |      | ps      |

| $\Delta_{IN}$             | Input delay programmable step                |                                                           |                                                             |      | 1.1    |      | ps      |

| Clock Outp                | uts                                          |                                                           |                                                             |      |        |      |         |

| f <sub>OUT</sub>          | Output frequency                             | Divide-by-2                                               |                                                             | 0.15 |        | 6.4  |         |

| f <sub>OUT</sub>          | Output frequency                             | Buffer Mode                                               |                                                             | 0.3  |        | 12.8 | GHz     |

| f <sub>OUT</sub>          | Output frequency                             | Multiplier Mode                                           |                                                             | 6.4  |        | 12.8 |         |

| f <sub>OUT</sub>          | Output frequency                             | LOGICLK output                                            |                                                             | 1    |        | 800  | MHz     |

| t <sub>CAL</sub>          | Calibration-time                             | Multiplier calibration time                               | f <sub>IN</sub> = 6.4GHz; x2<br>f <sub>SMCLK</sub> = 28 MHz |      | 750    |      | μs      |

| Роит                      | Output power                                 | Single-Ended                                              | f <sub>CLKLOUT</sub> = 6GHz<br>OUTx_PWR = 6                 |      | 4.8    |      | dBm     |

| t <sub>RISE</sub>         | Rise time (20% to 80%)                       | f <sub>CLKOUT</sub> = 300 MHz                             |                                                             |      | 45     |      | ps      |

| t <sub>FALL</sub>         | Fall time (20% to 80%)                       | f <sub>CLKOUT</sub> = 300 MHz                             |                                                             |      | 45     |      | ps      |

| V <sub>LOGICLKCM</sub>    | Common mode voltage                          | LOGICLKOUT0                                               | LVDS                                                        | 0.7  | 1.2    | 1.5  | V       |

| ΦIN                       | Output delay range                           |                                                           |                                                             |      | 55     |      | ps      |

| ΔφιΝ                      | Output delay programmable step size          |                                                           |                                                             |      | 0.9    |      | ps      |

| Propagatio                | n Delay and Skew                             |                                                           |                                                             |      |        |      |         |

| t <sub>SKEW</sub>         | Magnitude of skew between outputs            | CLKOUTx to CLKOUT                                         | y, not LOGICLK                                              |      | 1      | 10   | ps      |

| t <sub>SKEW</sub>         | Magnitude of skew between CLKOUT and SYSREF  | SYSREF Continuous/<br>Pulse Mode                          | SYSREF delay gen bypass                                     |      | 60     |      | ps      |

| t <sub>SKEW</sub>         | Magnitude of skew between CLKOUT and SYSREF  | SYSREF Repeater retime Mode                               | SYSREF delay gen bypass                                     |      | 100    |      | ps      |

| $\Delta t_{DLY}/\Delta T$ | Propagation delay variation over temperature | Buffer mode                                               |                                                             | 0.02 | 0.06   | 0.10 | ps/°C   |

|                           |                                              | Buffer mode                                               |                                                             |      | 165    |      | ps      |

| $t_{DLY}$                 | Propagation delay                            | Divider Mode                                              | T <sub>A</sub> = 25°C                                       |      | 175    |      | ps      |

|                           |                                              | Multiplier Mode                                           |                                                             |      | 155    |      | ps      |

| t <sub>DLY</sub>          | Propagation delay                            | SYSREF out<br>Repeater mode                               | T <sub>A</sub> = 25°C                                       |      | 185    |      | ps      |

| Noise, Jitte              | r, and Spurs                                 |                                                           |                                                             |      |        |      |         |

|                           |                                              |                                                           | Buffer Mode                                                 |      | 10     |      |         |

|                           |                                              |                                                           | x2 Multiplier                                               |      | 21     |      |         |

|                           |                                              |                                                           | x3 Multiplier                                               |      | 25     |      |         |

| <b>a</b>                  | CLKOUT Additive jitter                       | Additive Jitter. 100Hz to 100MHz integration              | x4 Multiplier                                               |      | 33     |      | fo rmo  |

| σ <sub>CLKOUT</sub>       | CEROOT Additive litter                       | bandwidth.                                                | x5 Multiplier                                               |      | 35     |      | fs, rms |

|                           |                                              |                                                           | x6 Multiplier                                               |      | 48     |      |         |

|                           |                                              |                                                           | x7 Multiplier                                               |      | 50     |      |         |

|                           |                                              |                                                           | x8 Multiplier                                               |      | 60     |      |         |

| 1/f <sub>CLKOUT</sub>     | 1/f flicker noise                            | Slew Rate > 8 V/ns,<br>f <sub>CLK</sub> =6GHz             | Buffer Mode                                                 |      | -154   |      | dBc/Hz  |

|                           |                                              |                                                           | Buffer Mode                                                 |      | -159   |      |         |

|                           |                                              | f <sub>OUT</sub> = 6.4GHz;                                | Divide-by-2                                                 |      | -158.5 |      |         |

| NF <sub>CLKOUT</sub>      | Noise Floor                                  | f <sub>OUT</sub> = 6.4GHz;<br>f <sub>Offset</sub> =100MHz | Multiplier<br>(x2,x3,x4,x5,x6,x7,x                          |      | -159.5 | dBc  | dBc/Hz  |

### 2.4 V ≤ VCC ≤ 2.6 V, -40°C ≤ TA ≤ +85°C. Typical values are at VCC = 2.5 V, 25°C (unless otherwise noted)

|                        | PARAMETER                              | TEST CON                                     | IDITIONS                        | MIN | TYP MAX         | UNIT         |

|------------------------|----------------------------------------|----------------------------------------------|---------------------------------|-----|-----------------|--------------|

| NE                     | Naise Floor                            | LOGICLK output, 300                          | CML                             | -1  | 50.5            | -ID - /I I - |

| NF <sub>LOGICLK</sub>  | Noise Floor                            | MHz                                          | LVDS                            | -1  | 51.5            | dBc/Hz       |

|                        |                                        | Buffer Mode                                  | Differential                    |     | -25             |              |

| H2                     | Second harmonic                        | f <sub>OUT</sub> =6.4GHz                     | Single-Ended                    |     | <b>-15</b>      | dBc          |

|                        |                                        | Divide by 2<br>f <sub>OUT</sub> =6.4GHz      | Single-Ended                    |     | <b>–17</b>      | 420          |

|                        |                                        | f <sub>OUT</sub> = 12GHz<br>(differential)   | x2 (f <sub>SPUR</sub> = 6GHz)   |     | -40             |              |

|                        |                                        | f <sub>OUT</sub> = 12GHz<br>(differential)   | x3 (f <sub>SPUR</sub> = 4GHz)   |     | <b>-40</b>      |              |

|                        |                                        | f <sub>OUT</sub> = 12GHz<br>(differential)   | x4 (f <sub>SPUR</sub> = 3GHz)   |     | <b>-</b> 50     |              |

| H <sub>1/M</sub>       | Input clock leakage spur               | f <sub>OUT</sub> = 12GHz<br>(differential)   | x6 (f <sub>SPUR</sub> = 2GHz)   |     | -50             | dBc          |

|                        |                                        | f <sub>OUT</sub> = 10GHz<br>(differential)   | x5 (f <sub>SPUR</sub> = 2GHz)   |     | -50             |              |

|                        |                                        | f <sub>OUT</sub> = 10.5GHz<br>(differential) | x7 (f <sub>SPUR</sub> = 1.5GHz) |     | -52             |              |

|                        |                                        | f <sub>OUT</sub> = 12GHz<br>(differential)   | x8 (f <sub>SPUR</sub> = 1.5GHz) |     | -55             |              |

|                        | LOGICLK to CLKOUT                      | f <sub>SPUR</sub> = 300MHz (differential)    |                                 |     | <del>-7</del> 0 | dBc          |

| P <sub>crosstalk</sub> | SYSREFOUT to CLKOUT                    | Generation mode                              |                                 |     | -70             | dBc          |

|                        | STOKETOOT TO CERCOT                    | repeater mode                                |                                 |     | -65             | dBc          |

| P <sub>LEAK</sub>      | CLKIN to CLKOUT Leakage in Buffer Mode | Differential Input                           |                                 |     | -70             | dBc          |

| Digital Inte           | rface (SCK, SDI, CS#, MUXOUT)          |                                              |                                 |     |                 |              |

| $V_{IH}$               | High-level input voltage               | SCK, SDI, CS#                                |                                 | 1.4 | 3.3             |              |

| V <sub>IL</sub>        | Low-level input voltage                |                                              |                                 | 0   | 0.4             |              |

| V <sub>OH</sub>        | High-level output voltage              | I <sub>OH</sub> = 5mA                        |                                 | 1.4 | Vcc             | V            |

| ▼ UH                   | Thigh level output voltage             | I <sub>OH</sub> = 0.1mA                      |                                 | 2.2 | Vcc             |              |

| V <sub>OL</sub>        | Low-level output voltage               | I <sub>OL</sub> = 5mA                        |                                 |     | 0.45            |              |

| I <sub>IH</sub>        | High-level input current               |                                              |                                 | -42 | 42              | μA           |

| I <sub>IL</sub>        | Low-level input current                |                                              |                                 | -25 | 25              | μΛ           |

Unless Otherwise Stated, f<sub>CLKIN</sub>=6.4GHz, CLK\_MUX=Buffer, All clocks on with OUTx\_PWR=6, SYSREFREQ\_MODE=1

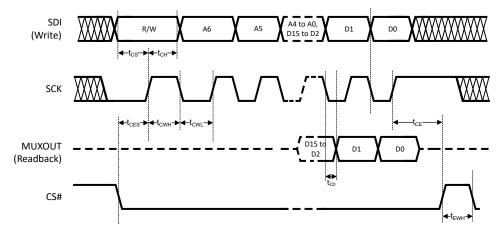

## 5.6 Timing Requirements

|                  |                                      | MIN NOM MA | X UNIT |

|------------------|--------------------------------------|------------|--------|

| Timing           | Requirements                         | ·          |        |

| f <sub>SPI</sub> | SPI Read/Write Speed                 | 2          | 0 MHz  |

| t <sub>CE</sub>  | Clock to enable low time             | 20         | ns     |

| t <sub>CS</sub>  | Clock to data wait time              | 10         | ns     |

| t <sub>CH</sub>  | Clock to data hold time              | 5          | ns     |

| t <sub>CWH</sub> | Clock pulse width high               | 10         | ns     |

| t <sub>CWL</sub> | Clock pulse width low                | 10         | ns     |

| t <sub>CES</sub> | Enable to clock setup time           | 15         | ns     |

| t <sub>EWH</sub> | Enable pulse width high              | 15         | ns     |

| t <sub>CD</sub>  | Falling clock edge to data wait time | 40         | ns     |

### 5.7 Timing Diagram

Figure 5-1. Serial Data Input Timing Diagram

There are several other considerations for writing on the SPI:

- The R/W bit must be set to 0.

- The data on SDI pin is clocked into a shift register on each rising edge on the SCK pin.

- The CS# must be held low for data to be clocked. The device ignores clock pulses if CS# is held high.

- Recommended SPI settings for this device are CPOL=0 and CPHA=0.

- When SCK and SDI lines are shared between devices, TI recommends to hold the CS# line high on the

device that is not to be clocked.

There are several other considerations for SPI readback:

- The R/W bit must be set to 1.

- The MUXOUT pin remains tri-stated for the address portion of the transaction.

- The data on MUXOUT is clocked out at the falling edge of SCK. In other words, the readback data is

available at the MUXOUT pin t<sub>CD</sub> after the clock falling edge.

- The data portion of the transition on the SDI line is always ignored.

- The MUXOUT pin is automatically enabled during the readback transaction. After readback activity is over, it is automatically tri-stated. MUXOUT pin has dual functionality in multiplier mode, as multiplier lock status is also indicated on MUXOUT pin. When sharing the SPI bus readback pin with other devices, make sure to set LD DIS=1, if readback is required in multiplier mode.

- If READBACK\_CTRL is set to 0, the values read back even for R/W bits are not always the value written but

rather an internal device state that takes into account the programmed value as well as other factors, such as

pin states.

Submit Document Feedback

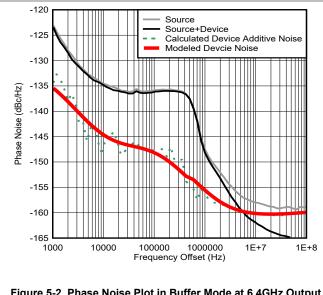

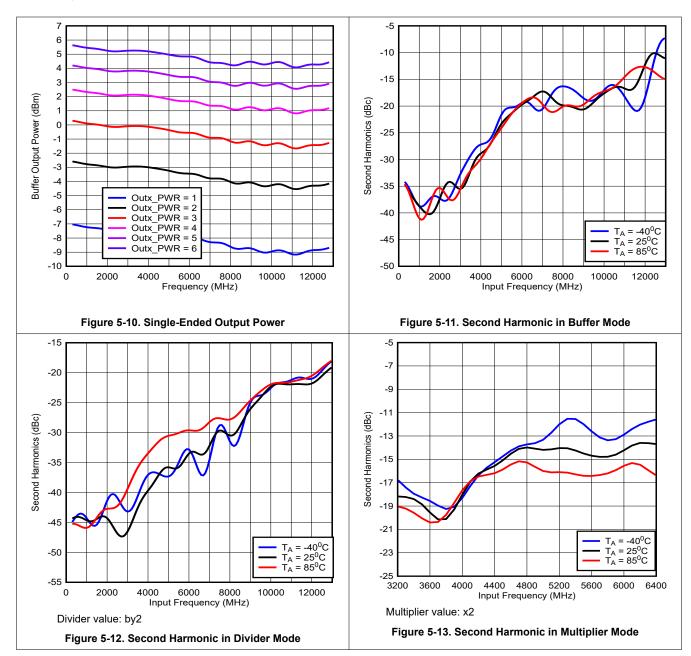

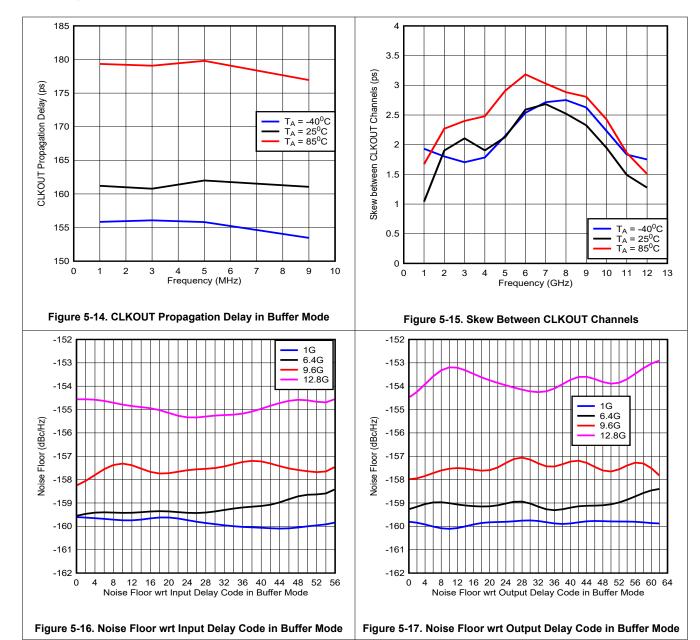

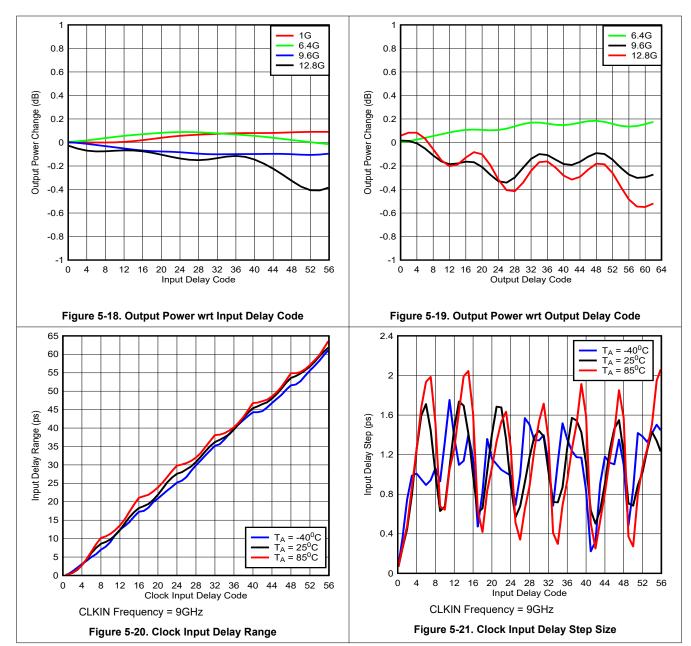

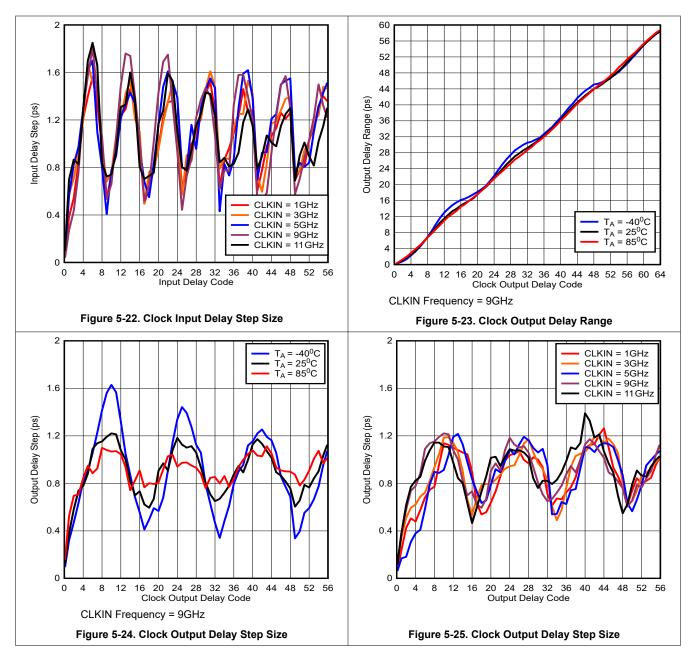

### 5.8 Typical Characteristics

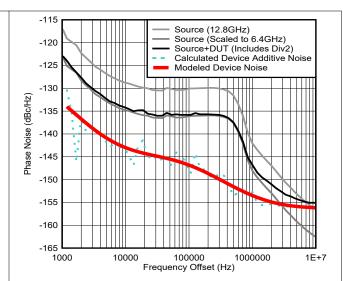

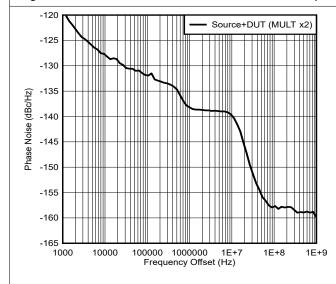

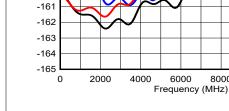

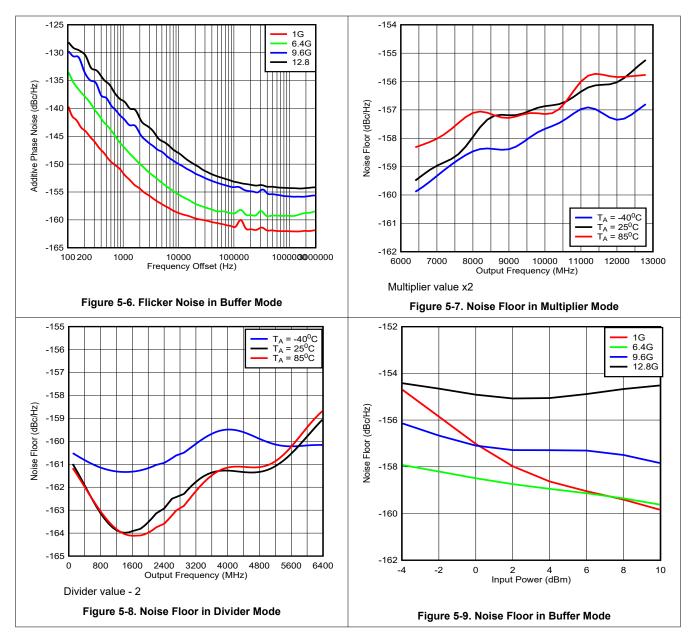

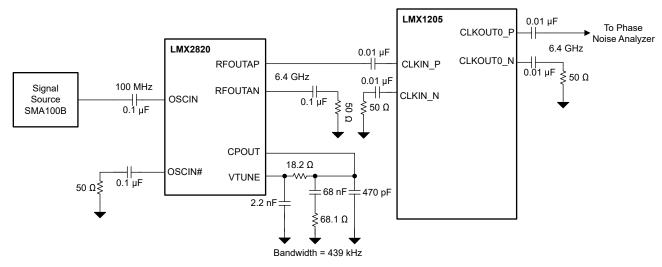

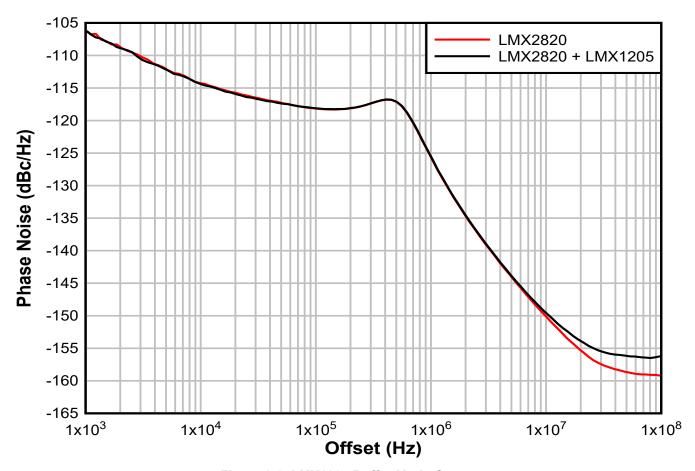

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Figure 5-2. Phase Noise Plot in Buffer Mode at 6.4GHz Output

Figure 5-3. Phase Noise Plot in Divider Mode at 6.4GHz Output

-151

-152 -153

-154

-155

-156

-157

-158 -159

-160

Noise Floor (dBc/Hz)

Figure 5-4. Phase Noise Plot in Multiplier Mode at 6.4GHz

Figure 5-5. Noise Floor in Buffer Mode

8000

$T_A = -40^0 C$

$T_A = 25^0 C$   $T_A = 85^0 C$

10000

12000

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Submit Document Feedback

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Submit Document Feedback

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

Submit Document Feedback

Unless stated otherwise, the following conditions can be assumed: Temperature = 25°C, Vcc = 2.5V, OUTx\_PWR=6, CLKIN\_N driven single ended with 10dBm at pin. Signal source used is SMA100B with ultra-low noise option B711. Phase noise analyzer is FSWP50.

## 6 Detailed Description

#### 6.1 Overview

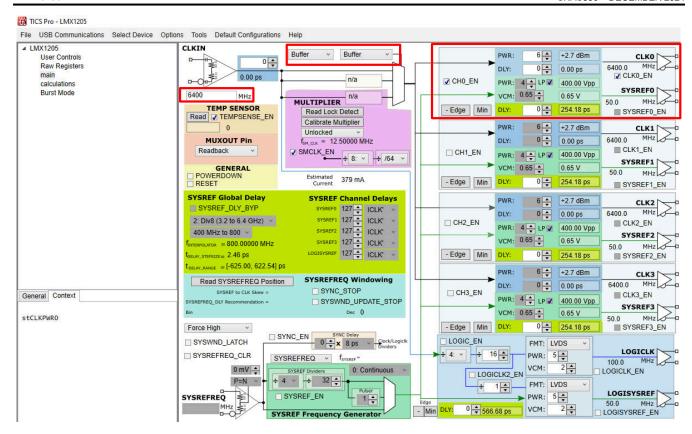

The LMX1205 has four main clock outputs and one LOGICLK output. The main clock outputs are all the same frequency. This frequency can be the same, divided, or multiplied relative to the input clock. Each of these clock outputs has independent programmable power level. The LOGICLK output frequency can be divided or same frequency as clock input and has programmable output format (CML and LVDS) and power level. Second LOGICLK can be generated at LOGISYSREF output pin with the additional division of 1, 2, 4 and 8 at the LOGICLK0 path.

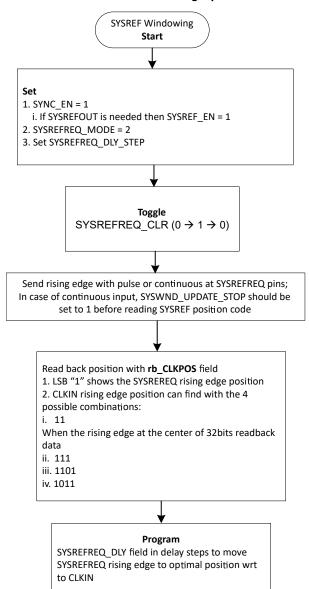

The SYSREF can be generated by either repeating the input from the SYSREFREQ pins, or internally generated. There is an internal SYSREF windowing feature that allows the internal timing of the device to be adjusted to optimize setup/hold times of the SYSREFREQ input with respect to the CLKIN input. This feature requires that the delay between the SYSREF edge and the next rising clock edge is consistent. Each of the five outputs has a corresponding SYSREF output that has individual programmable delays and programmable common mode. For the LOGISYSREF output, the output format is programmable as CML and LVDS.

### 6.1.1 Range of Dividers and Multiplier

Frequency dividers allow the main and LOGICLK outputs to be a divided value of the input clock. SYSREF dividers are used to divide the input clock for purposes of SYSREF generation and delays. The multiplier allows the output clocks to be a higher frequency than the input clock.

Table 6-1. Range of Dividers and Multiplier

| Table 0-1. Italige of Dividers and Multiplier |                             |           |                     |                                                                                 |  |  |  |

|-----------------------------------------------|-----------------------------|-----------|---------------------|---------------------------------------------------------------------------------|--|--|--|

| C                                             | ATEGORY                     |           | RANGE               | COMMENTS                                                                        |  |  |  |

|                                               | Ви                          | ıffer     |                     |                                                                                 |  |  |  |

| Main Clocks                                   | Div                         | /ider     | 2, 3, 4, 5, 6, 7, 8 | Odd divides (except 1) do not have 50% duty cycle                               |  |  |  |

|                                               | Multiplier                  |           | 2, 3, 4, 5, 6, 7, 8 |                                                                                 |  |  |  |

|                                               |                             | PreDivide | 1, 2, 4             | TotalDivide = PreDivide × Divide0                                               |  |  |  |

| LOGICLK                                       | Divide                      | Divide0   | 1, 2, 3, 1023       | Odd divides (except 1) do not have 50% duty cycle                               |  |  |  |

|                                               |                             | Divide1   | 1, 2, 4, 8          | Logic CLK2 TotalDivide = PreDivide x Divide0 x Divide1                          |  |  |  |

|                                               | Divide for                  | PreDivide | 1,2, 4              | Pre-divides clock for SYSREF generation.                                        |  |  |  |

| SYSREF                                        | frequency generation Divide |           | 2, 3, 4, 4095       | TotalDivide = PreDivide×Divide Odd divides do not have 50% duty cycle           |  |  |  |

| OTORE                                         | Divide for delay generation | Divide    | 2, 4, 8, 16         | This divide is for phase interpolator and set according to the input frequency. |  |  |  |

## 6.2 Functional Block Diagram

Figure 6-1. Functional Block Diagram

### 6.3 Feature Description

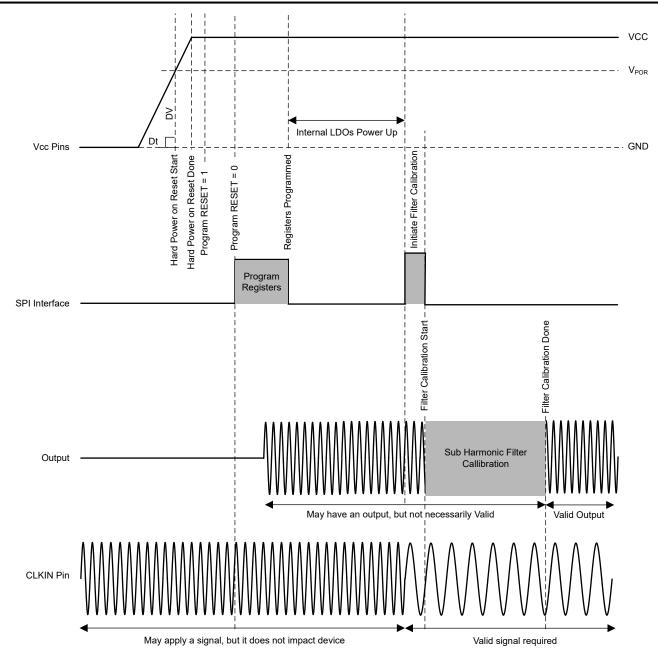

#### 6.3.1 Power On Reset

When the device is powered up, the power on reset (POR) resets all registers to a default state as well as resets all state machines and dividers. For the power on reset state, all SYSREF outputs are disabled and all the dividers are bypassed; the device functions as a 4-output buffer. Users must wait 100µs after the power supply rails before programming other registers to verify that the RESET is finished. If the power on reset happens when there is no device clock present, the device functions properly, however, the current changes once an input clock is presented.

\Performing a software power on reset by writing RESET=1 in the SPI bus is both possible and generally good practice. The RESET bit self-clears once any other register is written to. The SPI bus can be used to override these states to the desired settings.

Although the device does have an automatic power on reset, the device can be impacted by different ramp rates on the different supply pins, especially in the presence of a strong input clock signal. Performing a software reset after POR is recommended. This reset can be done by programming RESET=1. The reset bit can be cleared by programming any other register or setting RESET back to zero. Even at maximum allowed SPI bus speed, the software reset event always completes before the subsequent SPI write.

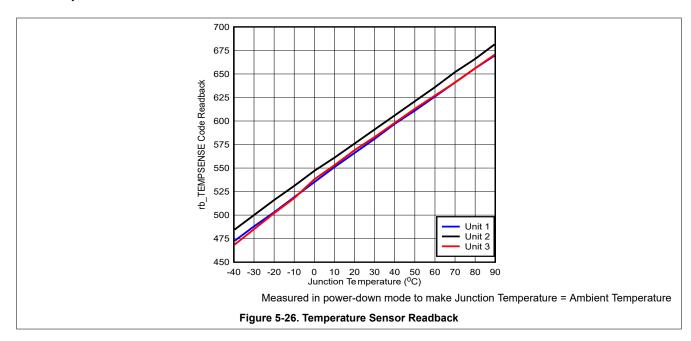

### 6.3.2 Temperature Sensor

The junction temperature can be read back for purposes such as characterization or to make adjustments based on temperature. Such adjustments can include adjusting CLKx\_PWR to make the output power more stable or using external or digital delays to compensate for changes in propagation delay over temperature.

The junction temperature is typically higher than the ambient temperature due to power dissipation from the outputs and other functions on the device. Equation 1 shows the relationship between the code read back and the junction temperature.

Temperature =

$$0.65 \times \text{Code} - 351$$

(1)

Equation 1 is based on a best-fit line created from three devices from slow, nominal, and fast corner lots (nine parts total). The worst-case variation of the actual temperature from the temperature predicted by the best-fit line is 13°C, which works out to 20 codes.

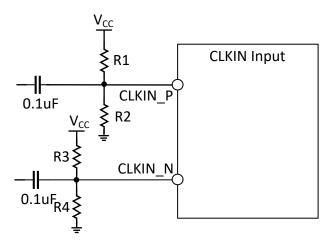

### 6.3.3 Clock Input

Clock input to the CLKIN\_P and CLKIN\_N pins must be AC coupled. For single ended clock input, provide the input at CLKIN\_N pin for optimal phase noise performance.

Based on the device internal architecture, for optimal device performance, a voltage offset between pin CLKIN\_P and CLKIN\_N required. To create a offset, the CLKIN\_P and CLKIN\_N pins must be biased using external resistors. The bias network circuits should be as below. The recommendated resistor values are R2 = 9.5k, R3 = 7.5K and make R1 and R4 as do not populate.

Figure 6-2. CLKIN Input Pins External Bias Network

#### 6.3.3.1 Clock Input Adjustable Delay

The clock input allows the user to add an adjustable delay of 0 to 60ps range with the typical average step size of 1.1ps.

### 6.3.4 Clock Outputs

This device has four main output clocks which share a common frequency. This does not include the additional lower frequency LOGICLKs output.

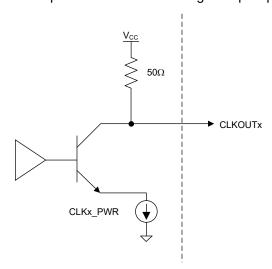

#### 6.3.4.1 Clock Output Buffers

The output buffers have a format that is open collector with an integrated pullup resistor, similar to CML.

Figure 6-3. CLKOUT Output Buffer

The CLKx\_EN bits can enable the output buffers. The output power of the buffers can be individually set with the CLKx\_PWR field. However, these fields only control the output buffer, not the internal channel path that drives this buffer. To power down the entire path, disable the CHx\_EN bit.

**Table 6-2. Clock Output Power**

| CHx_EN | INTERNAL CHANNEL PATH | CLKx_EN    | CLKx_PWR   | OUTPUT BUFFER |  |

|--------|-----------------------|------------|------------|---------------|--|

| 0      | Powered Down          | Don't Care | Don't Care | Powered Down  |  |

### **Table 6-2. Clock Output Power (continued)**

| CHx_EN | INTERNAL CHANNEL<br>PATH | CLKx_EN | CLKx_PWR   | OUTPUT BUFFER |

|--------|--------------------------|---------|------------|---------------|

|        |                          | 0       | Don't Care | Powered Down  |

|        |                          |         | 0          | Minimum       |

| 1      | Powered Up               | 1       | 1          |               |

|        |                          | I I     |            |               |

|        |                          |         | 6          | Maximum       |

#### 6.3.4.2 Clock Output Adjustable Delay

The clock outputs all have individually programmable delays that can be set from 0 to 55ps range with the typical average step size of 0.9ps. For best noise performance below 1.5GHz output frequency, it is recommended to use output delay code >= 4.

#### 6.3.4.3 Clock MUX

The four main clocks must be the same frequency, but this frequency can be bypassed, multiplied, or divided. This is determined by the CLK MUX word.

Table 6-3. Clock MUX

| CLK_MUX | OPTION          | VALUES SUPPORTED           |

|---------|-----------------|----------------------------|

| 0       | Buffer Mode     | ÷1 (bypass)                |

| 1       | Divider Mode    | ÷2, 3, 4, 5, 6, 7, and 8   |

| 2       | Multiplier Mode | x2, x3, x4, x5, x6, x7, x8 |

#### 6.3.4.4 Clock Divider

Set the CLK MUX to Divided to a divide value by 2, 3, 4, 5, 6, 7, or 8. This is set by the CLK DIV word. When using the clock divider, any change to the input frequency requires the CLK DIV RST bit to be toggled from 1 to 0.

Table 6-4. Clock Divider

| CLK_DIV | DIVIDE   | DUTY CYCLE |

|---------|----------|------------|

| 0       | Reserved | n/a        |

| 1       | 2        | 50%        |

| 2       | 3        | 33%        |

| 3       | 4        | 50%        |

| 4       | 5        | 40%        |

| 5       | 6        | 50%        |

| 6       | 7        | 43%        |

| 7       | 8        | 50%        |

#### 6.3.4.5 Clock Multiplier

### 6.3.4.5.1 General Information About the Clock Multiplier

The clock multiplier can be used to multiply up the input clock frequency by a factor of ×2, ×3, ×4, ×5, ×6, ×7 or ×8. The multiply value is set by the CLK MULT field. As the multiplier is PLL-based and includes an integrated VCO, the multiplier has a state machine clock, requires calibration and has a lock detect feature.

### 6.3.4.5.2 State Machine Clock for the Clock Multiplier

The state machine clock frequency (f<sub>SMCLK</sub>) is derived by dividing down the input clock frequency by a programmed divider value. The state machine clock is also necessary for the multiplier calibration and lock detect. If there are concerns about the state machine clock creating spurs, then the state machine clock can be shut off, provided that the multiplier calibration is not running and the lock detect feature is not in use.

#### 6.3.4.5.2.1 State Machine Clock

A valid state machine clock is required (SMCLK\_EN=1 and signal present at CLKIN pins) in below circumstances:

- 1. Multiplier is being calibrated.

- 2. Lock Detect from the multiplier is being monitored.

- 3. Clock divide value is being changed to 6 or 8.

- 4. For the device to perform a proper power on reset.

- a. Note that SMCLK\_EN=1 is enabled by the power on reset, but an input clock is also required to allow the power on reset before SMCLK\_EN can be set to 0.

When the state machine clock is enabled, the clock needs to be less than 30MHz and the frequency is as follows:

f<sub>SMCLK</sub> = f<sub>CLKIN</sub> / (SMCLK\_DIV\_PRE \* SMCLK\_DIV)

When the state machine clock is not required, the clock can be disabled by setting SMCLK\_EN=0 to minimize crosstalk and spurs.

#### 6.3.4.5.3 Calibration for the Clock Multiplier

For optimal phase noise, the VCO in the multiplier divides up the frequency range into many different bands and cores and has optimized amplitude settings for each band and core. For this reason, upon initial use or whenever the frequency is changed, the user must run a calibration routine to determine the correct core, frequency band, and amplitude setting. Program the R0 register with a valid input signal to perform a calibration. To provide reliable multiplier calibration, the state machine clock frequency must be at least twice the SPI write speed, but no more than 30MHz. Whenever the CLK\_MUX mode is changed or the multiplier is calibrated for the first time, the calibration time is substantially longer, on the order of 5ms.

### 6.3.4.5.4 Lock Detect for the Clock Multiplier

The lock detect status of the multiplier can be read back through the rb\_LOCK\_DETECT field or from the MUXOUT pin. The state machine clock must be running for the lock detect to work properly.

### 6.3.5 LOGICLK Outputs

The two LOGICLK outputs can be used to drive devices using lower frequency clocks, such as FPGAs. If only one LOGICLK required, the corresponding SYSREF output also be used as JESD204B/C interface clock. The LOGICLK output has a programmable output format and a corresponding SYSREF output.

#### **6.3.5.1 LOGICLK Output Format**

The LOGICLKOUT0 & LOGICLKOUT1 output format can be programmed to LVDS and CML modes. Depending on the format, the common mode can be programmable or external components can be required (see Table 6-5).

LOGICLKOUT1 output common mode and format can be programmable as shown LOGISYSREFOUT configuration.

Table 6-5. LOGICLKOUT0 Formats and Properties

| LOGICLK_FMT | FORMAT | EXTERNAL COMPONENTS REQUIRED | OUTPUT LEVEL                     | COMMON MODE                                                   |

|-------------|--------|------------------------------|----------------------------------|---------------------------------------------------------------|

| 0           | LVDS   | None                         | Programmable through LOGICLK_PWR | Programmable through LOGICLK_VCM.                             |

| 2           | CML    | -                            | 0                                | LOGICLK_VCM has no impact, but this changes with LOGICLK_PWR. |

table shows the logic clock LVDS format single ended swing and supported common mode voltage over programmable LOGICLK\_VCM settings.

Table 6-6. LOGICLK LVDS Common Mode Voltage vs LOGICLK VCM

| LOGICLK_VCM | LOGICLK VOD swing - Single ended pk-pk (V) | LOGICLK Common Mode Voltage (V) |

|-------------|--------------------------------------------|---------------------------------|

| 6           | 0.37                                       | 0.81                            |

| 5           | 0.36                                       | 0.90                            |

| 4           | 0.35                                       | 0.99                            |

| 3           | 0.34                                       | 1.09                            |

| 2           | 0.33                                       | 1.18                            |

| 1           | 0.31                                       | 1.27                            |

The following table shows the logic clock LVDS format supported LOGICLK\_VCM range corresponding to LOGICLK PWR setting.

Table 6-7. Supported LOGICLK\_VCM settings

| LOGICLK_PWR | LOGICLK VOD swing -    | Supported VOCM range | Supported LOGICLK_VCM range |          |  |

|-------------|------------------------|----------------------|-----------------------------|----------|--|

|             | Single ended pk-pk (V) |                      | Min code                    | Max code |  |

| 0           | 0.1                    | 0.8 to 1.4           | 0                           | 6        |  |

| 1           | 0.15                   | 0.8 to 1.4           | 0                           | 6        |  |

| 2           | 0.2                    | 0.8 to 1.4           | 0                           | 6        |  |

| 3           | 0.25                   | 0.75 to 1.35         | 0                           | 6        |  |

| 4           | 0.3                    | 0.8 to 1.3           | 1                           | 6        |  |

| 5           | 0.35                   | 0.8 to 1.3           | 1                           | 6        |  |

| 6           | 0.4                    | 0.9 to 1.3           | 2                           | 6        |  |

| 7           | 0.5                    | 0.9 to 1.2           | 3                           | 6        |  |

#### 6.3.5.2 LOGICLK Dividers

The LOGICLK DIV PRE divider, LOGICLK DIV and LOGICLK2 DIV dividers are used for the LOGICLK outputs. The LOGICLK DIV PRE divider is necessary to divide the frequency down to verify that the input to the LOGICLK DIV divider is 3.2GHz or less. The LOGICLK2 DIV is an additional divider to generate LOGICLKOUT1 output. When LOGICLK DIV is not even and not bypassed, the duty cycle is not 50%. All the LOGICLK dividers are synchronized by the SYNC feature, which allows synchronization across multiple devices.

Table 6-8. Minimum N-Divider Restrictions

| f <sub>CLKIN</sub> (MHz)                | LOGICLK_DIV_PRE | LOGICLK_DIV   | LOGICLK2_DIV | LOGICLKOUT0<br>TOTAL DIVIDE<br>RANGE       | LOGICLKOUT1<br>TOTAL DIVIDE<br>RANGE |

|-----------------------------------------|-----------------|---------------|--------------|--------------------------------------------|--------------------------------------|

| f <sub>CLKIN</sub> ≤ 3.2GHz             | ÷1, 2, 4        | ÷1, 2, 3,1023 | ÷1, 2, 4, 8  | [1, 2,1023]<br>[2, 4, 2046]<br>[4, 8,4092] | [1, 2,32736]                         |

| 3.2GHz < f <sub>CLKIN</sub> ≤<br>6.4GHz | ÷2, 4           | ÷1, 2, 3,1023 | ÷1, 2, 4, 8  | [2, 4, 2046]<br>[4, 8,4092]                | [2, 4,32736]                         |

| f <sub>CLKIN</sub> > 6.4GHz             | ÷4              | 1, 2, 3,1023  | ÷1, 2, 4, 8  | [4, 8,4092]                                | [4, 8,32736]                         |

#### **6.3.6 SYSREF**

SYSREF allows a low frequency JESD204B/C compliant signal to be produced that is reclocked to a main clock outputs or LOGICLK outputs. The delays between the CLKOUT and SYSREF outputs are adjustable with software. The SYSREF output can be configured as a generator using the internal SYSREF divider, or as a

repeater duplicating the signal on the SYSREFREQ pins. The SYSREF generator for both the main clocks and the LOGICLK output are the same.

Table 6-9. SYSREF Modes

| SYSREF_MODE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0           | Generator Mode Internal generator creates a continuous stream of SYSREF pulses. The SYSREFREQ_INPUT bits setting used to gate the SYSREF divider through SYSREFREQ pins or logic high from the channels for improved noise isolation without disrupting the synchronization of the SYSREF dividers. The SYSREFREQ_INPUT bits must be set for SYSREFREQ pins input or force high with changing bit from SYSREFREQ_INPUT[1] → 0 to 1 for a SYSREF output to come out. |  |  |  |  |

| 1           | Pulser Internal generator generates a burst of 1 - 16 pulses that is set by SYSREF_PULSE_CNT that occurs with the SYSREFREQ_INPUT settings for rising edge on the SYSREFREQ pins or force high with changing bit from SYSREFREQ_INPUT[1] → 0 to 1                                                                                                                                                                                                                   |  |  |  |  |

| 2           | Repeater Mode SYSREFREQ pins input are bypass to the SYSREFOUT outputs pins. If the delay is needed, the SYSREFREQ pins input are reclocked to clock outputs accordance to the SYSREF_DLY_BYP field before sent to the SYSREFOUT output pins.                                                                                                                                                                                                                       |  |  |  |  |

| 3           | Repeater Retime Mode SYSREFREQ pins input are reclocked to clock input and then delayed in accordance to the SYSREF_DLY_BYP field before sent to the SYSREFOUT output pins.                                                                                                                                                                                                                                                                                         |  |  |  |  |

Below figures show the functional block diagrams for different SYSREF modes.

Figure 6-4. Functional Block Diagram of SYSREF Circuitry in Generator Mode

Figure 6-5. Functional Block Diagram of SYSREF Circuitry in Pulser Mode

Figure 6-6. Functional Block Diagram of SYSREF Circuitry in Repeater Mode

Figure 6-7. Functional Block Diagram of SYSREF Circuitry in Repeater Retime Mode

### 6.3.6.1 SYSREF Output Buffers

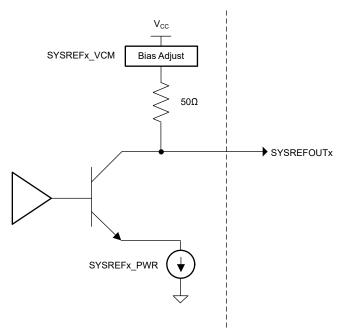

## 6.3.6.1.1 SYSREF Output Buffers for Main Clocks (SYSREFOUT)

The SYSREF outputs within the clock output channels have the same output buffer structure as the clock output buffer, with the addition of circuitry to adjust the common-mode voltage. The SYSREF outputs are CML outputs

with a common-mode voltage that can be adjusted with the SYSREFx\_VCM field, and the output level that can be programmed with the SYSREFx\_PWR field. This feature is to allow DC coupling. Note that the CLKOUT outputs do not have adjustable common-mode voltage and must be AC coupled for optimal noise performance.

Figure 6-8. SYSREF Output Buffer

The common-mode voltage and output power can be simulated assuming a  $100\Omega$  differential load and no DC path to ground. The SYSREF output swing and corresponding supported common mode voltage as shown below. For each SYSREFx\_VCM settings, the output common mode voltage variation can be within  $\pm 10\%$  of change value.

| SYSREFx_<br>PWR | Swing VOD (single ended pk-pk)           |          | Sup      | Supported SYSREFx_VCM code |          |         | Supported VCM range (V)                                             |         |         |       |

|-----------------|------------------------------------------|----------|----------|----------------------------|----------|---------|---------------------------------------------------------------------|---------|---------|-------|

|                 | SYSREFx_ SYSREFx_<br>PWR_LO PWR_LO       |          |          |                            |          |         | SYSREFx_PWR_LOW SYSREFx_PWR_LO = 1 Low Power (V) = 0 High Power (V) |         |         | _     |

|                 | W = 1 Low W = 0 Power (V) High Power (V) | Min code | Max code | Min code                   | Max code | Min VCM | Max VCM                                                             | Min VCM | Max VCM |       |

| 0               | 0.23                                     | 0.46     | 4        | 44                         | 10       | 44      | 0.500                                                               | 1.500   | 0.650   | 1.500 |

| 1               | 0.29                                     | 0.58     | 6        | 44                         | 12       | 42      | 0.550                                                               | 1.500   | 0.700   | 1.450 |

| 2               | 0.35                                     | 0.69     | 7        | 44                         | 15       | 40      | 0.575                                                               | 1.500   | 0.775   | 1.400 |

| 3               | 0.40                                     | 0.79     | 8        | 44                         | 18       | 36      | 0.600                                                               | 1.500   | 0.850   | 1.300 |

| 4               | 0.46                                     | 0.89     | 10       | 44                         | 20       | 31      | 0.650                                                               | 1.500   | 0.900   | 1.175 |

| 5               | 0.51                                     | 0.97     | 11       | 44                         | 22       | 26      | 0.675                                                               | 1.500   | 0.950   | 1.050 |

| 6               | 0.57                                     | 1.04     | 12       | 44                         | 2        | 3       | 0.700                                                               | 1.500   | 0.9     | 75    |

| 7               | 0.62                                     |          | 13       | 41                         |          |         | 0.725                                                               | 1.425   |         |       |

### 6.3.6.1.2 LOGISYSREF Output Buffer

The LOGISYSREFOUT / LOGICLKOUT1 output supports LVDS and CML output formats. The LOGISYSREF\_EN enables the output buffer and LOGISYSREF\_FMT sets the format. LVDS mode allows programmable output power and common mode voltage. CML output format require external components and allows programmable output power.

## Table 6-10, LOGISYSREFOUT / LOGICLKOUT1 Output Buffer Configuration

|               | garane         |                      |                                            |                                           |                                                                     |  |

|---------------|----------------|----------------------|--------------------------------------------|-------------------------------------------|---------------------------------------------------------------------|--|

| LOGISYSREF_EN | LOGISYSREF_FMT | LOGISYSREF<br>FORMAT | EXTERNAL<br>TERMINIATION<br>REQUIRED       | OUTPUT POWER                              | OUTPUT COMMON<br>MODE                                               |  |

| 0             |                | Powered Down         |                                            |                                           |                                                                     |  |

|               | 0              | LVDS                 | None                                       | Programmable<br>through<br>LOGISYSREF_PWR | Programmable<br>through<br>LOGISYSREF_VCM.                          |  |