www.ti.com

SNOSAV0E - MARCH 2006 - REVISED MARCH 2013

# Single and Dual Precision, 17 MHz, Low Noise, CMOS Input Amplifiers

Check for Samples: LMP7715, LMP7716, LMP7716Q

### **FEATURES**

- Unless Otherwise Noted,

Typical Values at V<sub>S</sub> = 5V.

- Input Offset Voltage ±150 μV (Max)

- Input Bias Current 100 fA

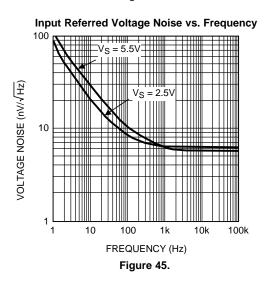

- Input Voltage Noise 5.8 nV/√Hz

- Gain Bandwidth Product 17 MHz

- Supply Current (LMP7715) 1.15 mA

- Supply Current (LMP7716/LMP7716Q) 1.30 mA

- Supply Voltage Range 1.8V to 5.5V

- THD+N @ f = 1 kHz 0.001%

- Operating Temperature Range −40°C to 125°C

- Rail-to-rail Output Swing

- Space Saving SOT-23 Package (LMP7715)

- 8-Pin VSSOP Package (LMP7716/LMP7716Q)

- LMP7716Q is AEC-Q100 Grade 1 Qualified and is Manufactured on an Automotive Grade Flow

#### **APPLICATIONS**

- Active Filters and Buffers

- Sensor Interface Applications

- Transimpedance Amplifiers

- Automotive

#### DESCRIPTION

The LMP7715/LMP7716/LMP7716Q are single and dual low noise, low offset, CMOS input, rail-to-rail output precision amplifiers with high gain bandwidth products. The LMP7715/LMP7716/LMP7716Q are part of the LMP<sup>™</sup> precision amplifier family and are ideal for a variety of instrumentation applications.

Utilizing a CMOS input stage, the LMP7715/LMP7716/LMP7716Q achieve an input bias current of 100 fA, an input referred voltage noise of 5.8 nV/ $\sqrt{\text{Hz}}$ , and an input offset voltage of less than ±150 µV. These features make the LMP7715/LMP7716/LMP7716Q superior choices for precision applications.

Consuming only 1.15 mA of supply current, the LMP7715 offers a high gain bandwidth product of 17 MHz, enabling accurate amplification at high closed loop gains.

The LMP7715/LMP7716/LMP7716Q have a supply voltage range of 1.8V to 5.5V, which makes these ideal choices for portable low power applications with low supply voltage requirements.

The LMP7715/LMP7716/LMP7716Q are built with TI's advanced VIP50 process technology. The LMP7715 is offered in a 5-pin SOT-23 package and the LMP7716/LMP7716Q is offered in an 8-pin VSSOP.

The LMP7716Q incorporates enhanced manufacturing and support processes for the automotive market, including defect detection methodologies. Reliability qualification is compliant with the requirements and temperature grades defined in the AEC-Q100 standard.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LMP is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# **Typical Performance**

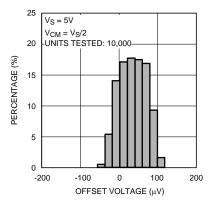

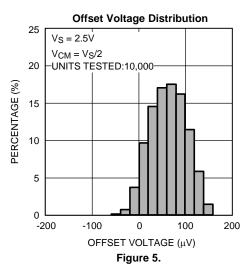

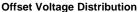

Figure 1. Offset Voltage Distribution

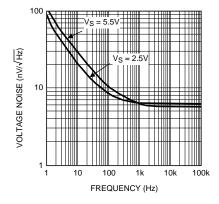

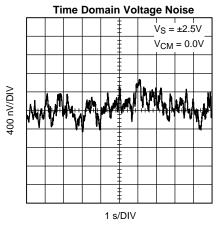

Figure 2. Input Referred Voltage Noise

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)

| Human Body Model                   | 2000V                                                              |  |  |

|------------------------------------|--------------------------------------------------------------------|--|--|

| Machine Model                      | 200V                                                               |  |  |

| Charge-Device Model                | 1000V                                                              |  |  |

| V <sub>IN</sub> Differential       |                                                                    |  |  |

| Supply Voltage $(V_S = V^+ - V^-)$ |                                                                    |  |  |

|                                    | V <sup>+</sup> +0.3V, V <sup>−</sup> −0.3V                         |  |  |

|                                    | -65°C to 150°C                                                     |  |  |

|                                    | +150°C                                                             |  |  |

| Infrared or Convection (20 sec)    | 235°C                                                              |  |  |

| Wave Soldering Lead Temp. (10 sec) | 260°C                                                              |  |  |

|                                    | Machine Model Charge-Device Model  Infrared or Convection (20 sec) |  |  |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics Tables.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (3) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC)Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- (4) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

# Operating Ratings<sup>(1)</sup>

| Temperature Range <sup>(2)</sup>                             | -40°C to 125°C                 |              |

|--------------------------------------------------------------|--------------------------------|--------------|

| Supply Voltage $(V_S = V^+ - V^-)$                           | 0°C ≤ T <sub>A</sub> ≤ 125°C   | 1.8V to 5.5V |

|                                                              | -40°C ≤ T <sub>A</sub> ≤ 125°C | 2.0V to 5.5V |

| Package Thermal Resistance (θ <sub>JA</sub> <sup>(2)</sup> ) | 5-Pin SOT-23                   | 180°C/W      |

|                                                              | 8-Pin VSSOP                    | 236°C/W      |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics Tables.

- (2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

## 2.5V Electrical Characteristics

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 2.5V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                        | Co                                                                    | Min <sup>(1)</sup>                                                                                                                            | Typ <sup>(2)</sup> | Max <sup>(1)</sup>  | Units               |        |

|--------------------|----------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|---------------------|--------|

| V <sub>OS</sub>    | Innut Offset Valtage             | -20°C ≤ T <sub>A</sub> ≤ 85°0                                         | $-20^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85^{\circ}\text{C}$<br>$-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le 125^{\circ}\text{C}$ |                    |                     | ±180<br>±330        | \/     |

|                    | Input Offset Voltage             | -40°C ≤ T <sub>A</sub> ≤ 125                                          |                                                                                                                                               |                    |                     | ±180<br>±430        | μV     |

| TC V <sub>OS</sub> | Input Offset Voltage Temperature | LMP7715                                                               |                                                                                                                                               |                    | -1                  | ±4                  | \//00  |

|                    | Drift <sup>(3)(4)</sup>          | LMP7716/LMP77                                                         | 16Q                                                                                                                                           |                    | -1.75               |                     | μV/°C  |

| I <sub>B</sub>     | Input Bias Current               | $V_{CM} = 1.0V^{(4)(5)}$                                              | -40°C ≤ T <sub>A</sub> ≤ 85°C                                                                                                                 |                    | 0.05                | 1<br><b>25</b>      | pA     |

|                    | input bias outrent               | VCM = 1.0V                                                            | -40°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                |                    | 0.05                | 1<br><b>100</b>     | pΑ     |

| I <sub>OS</sub>    | Input Offset Current             | $V_{CM} = 1V^{(4)}$                                                   |                                                                                                                                               |                    | 0.006               | 0.5<br><b>50</b>    | pA     |

| CMRR               | Common Mode Rejection Ratio      | 0V ≤ V <sub>CM</sub> ≤ 1.4V                                           |                                                                                                                                               | 83<br><b>80</b>    | 100                 |                     | dB     |

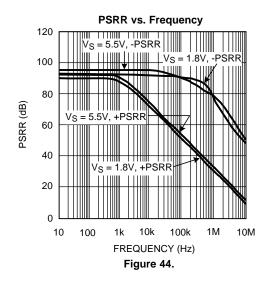

| PSRR               | Power Supply Paiestion Patio     | $2.0V \le V^+ \le 5.5V$<br>$V^- = 0V, V_{CM} = 0$                     |                                                                                                                                               | 85<br><b>80</b>    | 100                 |                     | dD     |

|                    | Power Supply Rejection Ratio     | $1.8V \le V^+ \le 5.5V$<br>$V^- = 0V, V_{CM} = 0$                     |                                                                                                                                               | 85                 | 98                  |                     | - dB   |

| CMVR               | Common Mode Voltage Range        | CMRR ≥ 80 dB<br>CMRR ≥ 78 dB                                          | -0.3<br>- <b>0.3</b>                                                                                                                          |                    | 1.5<br><b>1.5</b>   | V                   |        |

| A <sub>VOL</sub>   |                                  | LMP7715, $V_0 = 0$<br>$R_L = 2 k\Omega \text{ to } V^+/2$             | 88<br><b>82</b>                                                                                                                               | 98                 |                     |                     |        |

|                    | Open Loop Voltage Gain           | LMP7716/LMP777<br>$R_L = 2 k\Omega \text{ to V}^+/2$                  | 84<br><b>80</b>                                                                                                                               | 92                 |                     | dB                  |        |

|                    |                                  | LMP7715, $V_0 = 0$<br>$R_L = 10 \text{ k}\Omega \text{ to V}^+/2$     | 92<br><b>88</b>                                                                                                                               | 110                |                     | ub                  |        |

|                    |                                  | LMP7716/ LMP77<br>$R_L = 10 \text{ k}\Omega \text{ to V}^+/2$         | $^{1}$ 16Q, $V_{O} = 0.15$ to 2.2V                                                                                                            | 90<br><b>86</b>    | 95                  |                     |        |

| V <sub>OUT</sub>   | Output Voltage Swing             | $R_L = 2 k\Omega \text{ to } V^+/2$                                   |                                                                                                                                               |                    | 25                  | 70<br><b>77</b>     |        |

|                    | High                             | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                           |                                                                                                                                               | 20                 | 60<br><b>66</b>     | mV from either rail |        |

|                    | Output Voltage Swing             | $R_L = 2 k\Omega \text{ to } V^+/2$                                   |                                                                                                                                               |                    | 30                  | 70<br><b>73</b>     |        |

|                    | Low                              | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                           | 2                                                                                                                                             |                    | 15                  | 60<br><b>62</b>     |        |

| I <sub>OUT</sub>   |                                  | Sourcing to V <sup>-</sup><br>V <sub>IN</sub> = 200 mV <sup>(6)</sup> |                                                                                                                                               | 36<br><b>30</b>    | 52                  |                     |        |

|                    | Output Current                   | Sinking to V <sup>+</sup><br>$V_{IN} = -200 \text{ mV}^{(6)}$         |                                                                                                                                               | 7.5<br><b>5.0</b>  | 15                  |                     | mA     |

| I <sub>S</sub>     | 0                                | LMP7715                                                               |                                                                                                                                               |                    | 0.95                | 1.30<br><b>1.65</b> |        |

|                    | Supply Current                   | LMP7716/LMP77                                                         |                                                                                                                                               | 1.10               | 1.50<br><b>1.85</b> | mA                  |        |

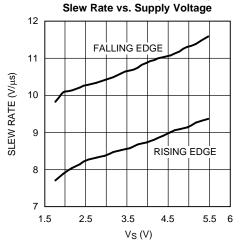

| SR                 | Claus Bata                       | $A_V = +1$ , Rising (1                                                | A <sub>V</sub> = +1, Rising (10% to 90%)                                                                                                      |                    |                     |                     | 1//110 |

|                    | Slew Rate                        | $A_V = +1$ , Falling (9                                               | 90% to 10%)                                                                                                                                   |                    | 10.3                |                     | V/µs   |

<sup>(1)</sup> Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using the Statistical Quality Control (SQC) method.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

<sup>(3)</sup> Offset voltage average drift is determined by dividing the change in V<sub>OS</sub> at the temperature extremes by the total temperature change.

<sup>(4)</sup> This parameter is specified by design and/or characterization and is not tested in production.

<sup>5)</sup> Positive current corresponds to current flowing into the device.

<sup>6)</sup> The short circuit test is a momentary open loop test.

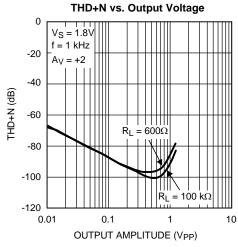

## 2.5V Electrical Characteristics (continued)

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 2.5V$ ,  $V^- = 0V$ ,  $V_O = V_{CM} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol         | Parameter                             | Conditions                                                                            | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup> | Units              |  |

|----------------|---------------------------------------|---------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|--------------------|--|

| GBW            | Gain Bandwidth                        |                                                                                       |                    | 14                 |                    | MHz                |  |

| e <sub>n</sub> | Innuit Deferred Voltage Naige Density | f = 400 Hz                                                                            |                    | 6.8                |                    | nV/                |  |

|                | Input Referred Voltage Noise Density  | f = 1 kHz                                                                             |                    | 5.8                |                    | IIV/               |  |

| i <sub>n</sub> | Input Referred Current Noise Density  | f = 1 kHz                                                                             |                    | 0.01               |                    | pA/√ <del>Hz</del> |  |

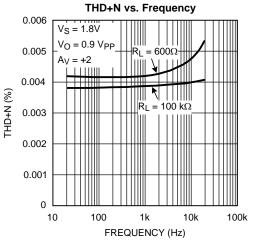

| THD+N          | Total Harmonic Distortion + Noise     | $f = 1 \text{ kHz}, A_V = 1, R_L = 100 \text{ k}\Omega$<br>$V_O = 0.9 \text{ V}_{PP}$ |                    | 0.003              |                    | 0/                 |  |

|                | otal Harmonic Distortion + Noise      | $f = 1 \text{ kHz}, A_V = 1, R_L = 600\Omega$<br>$V_O = 0.9 V_{PP}$                   |                    | 0.004              |                    | %                  |  |

### **5V Electrical Characteristics**

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                                     | Co                                                                                | Min <sup>(1)</sup>             | Typ <sup>(2)</sup>   | Max <sup>(1)</sup> | Units               |            |

|------------------|-----------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|----------------------|--------------------|---------------------|------------|

| V <sub>OS</sub>  | Input Offset Voltage                          | -20°C ≤ T <sub>A</sub> ≤ 85°0                                                     | -20°C ≤ T <sub>A</sub> ≤ 85°C  |                      | ±10                | ±150<br>±300        | \/         |

|                  |                                               | -40°C ≤ T <sub>A</sub> ≤ 125                                                      | °C                             |                      | ±10                | ±150<br><b>±400</b> | μV         |

| $TC V_{OS}$      | Input Offset Voltage Temperature Drift (3)(4) | LMP7715                                                                           |                                |                      | -1                 | ±4                  | \//90      |

|                  | Drift <sup>(3)(4)</sup>                       | LMP7716/LMP77                                                                     | 16Q                            |                      | -1.75              |                     | μV/°C      |

| I <sub>B</sub>   | Input Biog Current                            | $V_{CM} = 2.0V^{(4)(5)}$                                                          | -40°C ≤ T <sub>A</sub> ≤ 85°C  |                      | 0.1                | 1<br><b>25</b>      | <b>n</b> A |

|                  | Input Bias Current                            | V <sub>CM</sub> = 2.0V · · · ·                                                    | -40°C ≤ T <sub>A</sub> ≤ 125°C |                      | 0.1                | 1<br><b>100</b>     | рA         |

| I <sub>OS</sub>  | Input Offset Current                          | $V_{CM} = 2.0V^{(4)}$                                                             |                                | 0.01                 | 0.5<br><b>50</b>   | pA                  |            |

| CMRR             | Common Mode Rejection Ratio                   | 0V ≤ V <sub>CM</sub> ≤ 3.7V                                                       | 85<br><b>82</b>                | 100                  |                    | dB                  |            |

| PSRR             | Daniel Deinstein Deite                        | $2.0V \le V^+ \le 5.5V$<br>$V^- = 0V, V_{CM} = 0$                                 | 85<br><b>80</b>                | 100                  |                    | .ID                 |            |

|                  | Power Supply Rejection Ratio                  | $1.8V \le V^{+} \le 5.5V$<br>$V^{-} = 0V, V_{CM} = 0$                             |                                | 85                   | 98                 |                     | dB         |

| CMVR             | Common Mode Voltage Range                     | CMRR ≥ 80 dB<br>CMRR ≥ 78 dB                                                      |                                | -0.3<br>- <b>0.3</b> |                    | 4<br><b>4</b>       | V          |

| A <sub>VOL</sub> |                                               | LMP7715, $V_0 = 0$<br>$R_L = 2 k\Omega \text{ to } V^+/2$                         | 88<br><b>82</b>                | 107                  |                    |                     |            |

|                  | Open Loop Voltage Gain                        | LMP7716/LMP77<br>$R_L = 2 k\Omega \text{ to V}^+/2$                               | 84<br><b>80</b>                | 90                   |                    | ٩D                  |            |

|                  |                                               | LMP7715, $V_O = 0$<br>$R_L = 10 \text{ k}\Omega \text{ to V}^{+/2}$               | 92<br><b>88</b>                | 110                  |                    | dB                  |            |

|                  |                                               | LMP7716/LMP77 $^{\circ}$<br>R <sub>L</sub> = 10 kΩ to V <sup>+</sup> / $^{\circ}$ | 90<br><b>86</b>                | 95                   |                    |                     |            |

Limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlations using the Statistical Quality Control (SQC) method.

<sup>(2)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not specified on shipped production material.

<sup>(3)</sup> Offset voltage average drift is determined by dividing the change in V<sub>OS</sub> at the temperature extremes by the total temperature change.

<sup>(4)</sup> This parameter is specified by design and/or characterization and is not tested in production.

<sup>(5)</sup> Positive current corresponds to current flowing into the device.

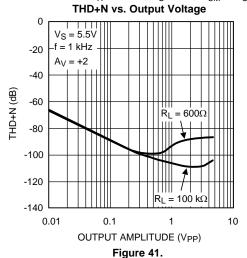

# **5V Electrical Characteristics (continued)**

Unless otherwise specified, all limits are ensured for  $T_A = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                             | Conditions                                                                          | Min <sup>(1)</sup> | Typ <sup>(2)</sup> | Max <sup>(1)</sup>  | Units              |  |  |

|------------------|---------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|---------------------|--------------------|--|--|

| V <sub>OUT</sub> | Output Voltage Swing                  | $R_L = 2 k\Omega$ to $V^+/2$                                                        |                    | 32                 | 70<br><b>77</b>     |                    |  |  |

|                  | High                                  | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                         |                    | 22                 | 60<br><b>66</b>     | mV from            |  |  |

|                  |                                       | $R_L = 2 k\Omega \text{ to } V^+/2 $ (LMP7715)                                      |                    | 42                 | 70<br><b>73</b>     | either rail        |  |  |

|                  | Output Voltage Swing<br>Low           | $R_L = 2 k\Omega \text{ to V}^+/2 $ (LMP7716/LMP7716Q)                              |                    | 45                 | 75<br><b>78</b>     |                    |  |  |

|                  |                                       | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                                         |                    | 20                 | 60<br><b>62</b>     |                    |  |  |

| I <sub>OUT</sub> | Output Ourset                         | Sourcing to V <sup>-</sup><br>V <sub>IN</sub> = 200 mV <sup>(6)</sup>               | 46<br><b>38</b>    | 66                 |                     | ^                  |  |  |

|                  | Output Current                        | Sinking to V <sup>+</sup><br>$V_{IN} = -200 \text{ mV}^{(6)}$                       | 10.5<br><b>6.5</b> | 23                 |                     | - mA               |  |  |

| I <sub>S</sub>   | 0                                     | LMP7715                                                                             |                    | 1.15               | 1.40<br><b>1.75</b> |                    |  |  |

|                  | Supply Current                        | LMP7716/LMP7716Q (per channel)                                                      |                    | 1.30               | 1.70<br><b>2.05</b> | - mA               |  |  |

| SR               | Claus Bata                            | A <sub>V</sub> = +1, Rising (10% to 90%)                                            | 6.0                | 9.5                |                     | 1///               |  |  |

|                  | Slew Rate                             | $A_V = +1$ , Falling (90% to 10%)                                                   | 7.5                | 11.5               |                     | V/µs               |  |  |

| GBW              | Gain Bandwidth                        |                                                                                     |                    | 17                 |                     | MHz                |  |  |

| e <sub>n</sub>   | Lawret Defended Veltage Naise Density | f = 400 Hz                                                                          |                    | 7.0                |                     | nV/√Hz             |  |  |

|                  | Input Referred Voltage Noise Density  | f = 1 kHz                                                                           |                    | 5.8                |                     | nv/vmz             |  |  |

| in               | Input Referred Current Noise Density  | f = 1 kHz                                                                           |                    | 0.01               |                     | pA/√ <del>Hz</del> |  |  |

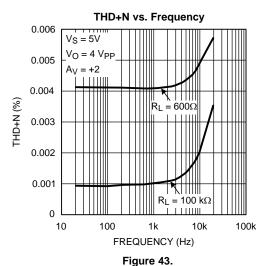

| THD+N            | Total Hamanaia Dietartian , Naisa     | $f = 1 \text{ kHz}, A_V = 1, R_L = 100 \text{ k}\Omega$<br>$V_O = 4 \text{ V}_{PP}$ |                    | 0.001              |                     | 0/                 |  |  |

|                  | Total Harmonic Distortion + Noise     | $f = 1 \text{ kHz}, A_V = 1, R_L = 600\Omega$<br>$V_O = 4 V_{PP}$                   |                    | 0.004              |                     | %                  |  |  |

(6) The short circuit test is a momentary open loop test.

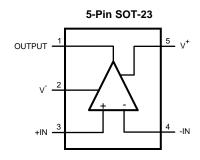

# **Connection Diagram**

Figure 3. Top View

Figure 4. Top View

# **Typical Performance Characteristics**

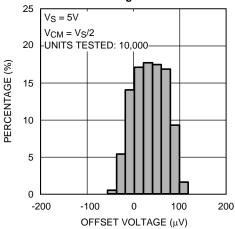

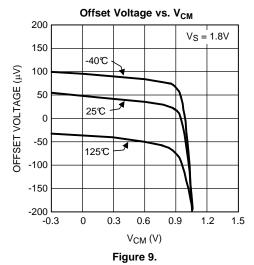

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5$ V,  $V_{CM} = V_S/2$ .

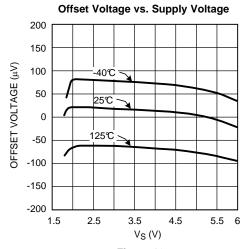

Figure 7.

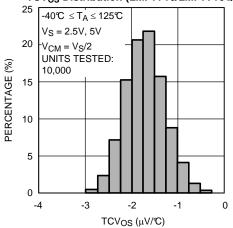

TCV<sub>OS</sub> Distribution (LMP7715)

Figure 6.

### TCV<sub>OS</sub> Distribution (LMP7716/LMP7716Q)

Figure 8.

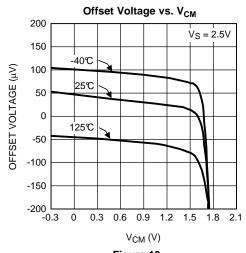

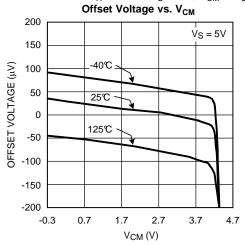

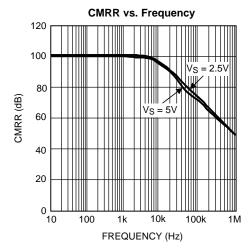

Figure 10.

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

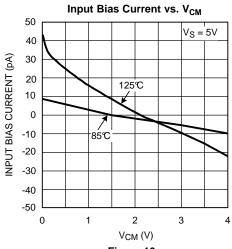

Figure 11.

Input Bias Current vs. V<sub>CM</sub>

-2000 -2500 -3000 0 1 2 3 4

Figure 15.

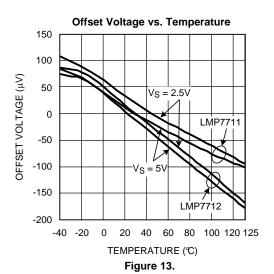

Figure 12.

Figure 14.

Figure 16.

1000

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5$ V,  $V_{CM} = V_S/2$ .

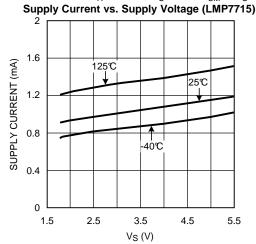

Figure 17.

Figure 19.

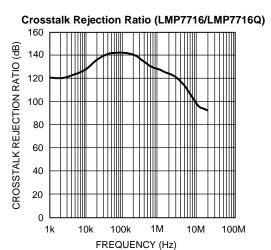

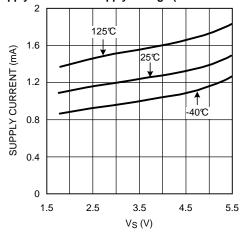

Supply Current vs. Supply Voltage (LMP7716/LMP7716Q)

Figure 18.

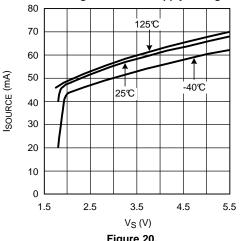

Figure 20.

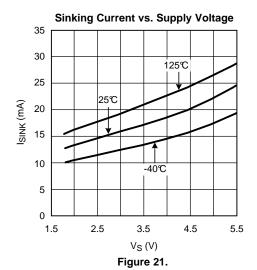

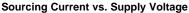

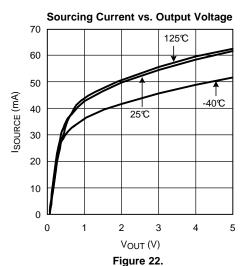

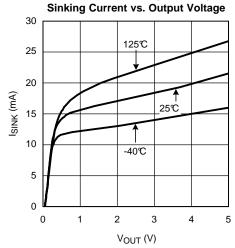

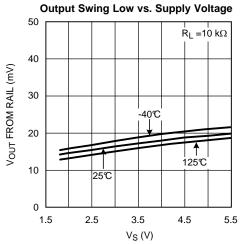

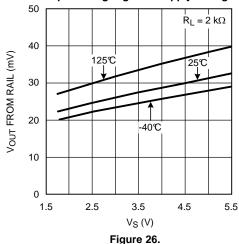

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

Figure 23.

Figure 25.

Figure 24.

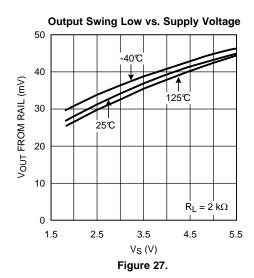

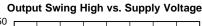

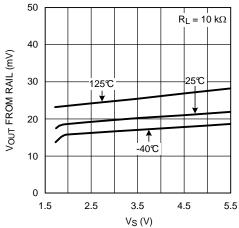

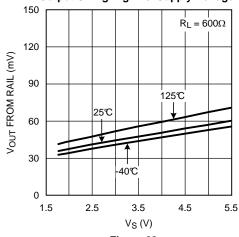

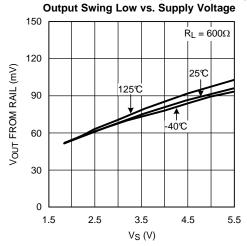

#### **Output Swing High vs. Supply Voltage**

J

#### Output Swing High vs. Supply Voltage

Figure 28.

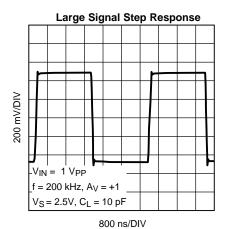

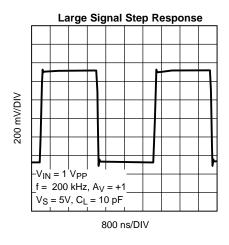

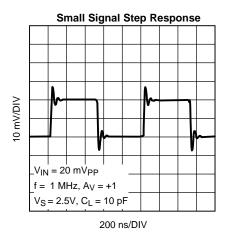

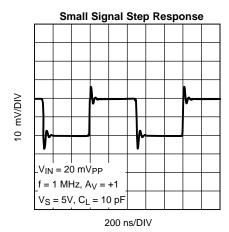

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

Figure 29.

Figure 33.

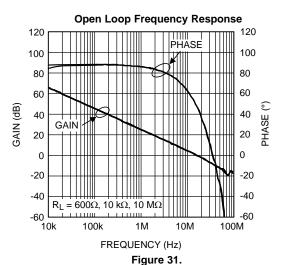

**Open Loop Frequency Response** 120 PHASE 100 80 80  $C_L = 50 pF$ 60 60 ||||||| | 1<del>11|</del> ||C<sub>L</sub> = 100 pF GAIN (dB) 40 40 20 20 = 20 pF-20 -20 = 50 pF -40 -40  $C_1 = 100 pF$ -60 -60 1k 10k 100k 1M 10M 100M FREQUENCY (Hz)

Figure 30.

Figure 34.

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

Figure 35.

Figure 37.

Figure 39.

Figure 36.

Figure 38.

Figure 40.

Unless otherwise noted:  $T_A = 25$ °C,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

Figure 42.

Figure 46.

Unless otherwise noted:  $T_A = 25^{\circ}C$ ,  $V_S = 5V$ ,  $V_{CM} = V_S/2$ .

Figure 47.

Figure 48.

#### **APPLICATION INFORMATION**

# LMP7715/LMP7716/LMP7716Q

The LMP7715/LMP7716/LMP7716Q are single and dual, low noise, low offset, rail-to-rail output precision amplifiers with a wide gain bandwidth product of 17 MHz and low supply current. The wide bandwidth makes the LMP7715/LMP7716Q ideal choices for wide-band amplification in portable applications.

The LMP7715/LMP7716Q are superior for sensor applications. The very low input referred voltage noise of only 5.8 nV/ $\sqrt{\text{Hz}}$  at 1 kHz and very low input referred current noise of only 10 fA/ $\sqrt{\text{Hz}}$  mean more signal fidelity and higher signal-to-noise ratio.

The LMP7715/LMP7716/LMP7716Q have a supply voltage range of 1.8V to 5.5V over a wide temperature range of 0°C to 125°C. This is optimal for low voltage commercial applications. For applications where the ambient temperature might be less than 0°C, the LMP7715/LMP7716/LMP7716Q are fully operational at supply voltages of 2.0V to 5.5V over the temperature range of −40°C to 125°C.

The outputs of the LMP7715/LMP7716/LMP7716Q swing within 25 mV of either rail providing maximum dynamic range in applications requiring low supply voltage. The input common mode range of the LMP7715/LMP7716/LMP7716Q extends to 300 mV below ground. This feature enables users to utilize this device in single supply applications.

The use of a very innovative feedback topology has enhanced the current drive capability of the LMP7715/LMP7716/LMP7716Q, resulting in sourcing currents of as much as 47 mA with a supply voltage of only 1.8V.

The LMP7715 is offered in the space saving SOT-23 package and the LMP7716/LMP7716Q is offered in an 8-pin VSSOP. These small packages are ideal solutions for applications requiring minimum PC board footprint.

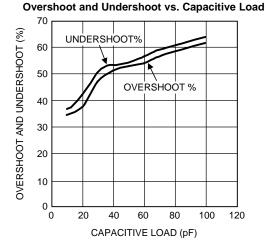

#### **CAPACITIVE LOAD**

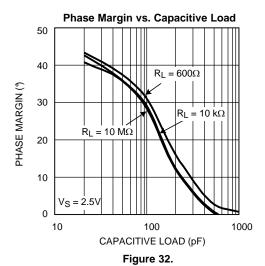

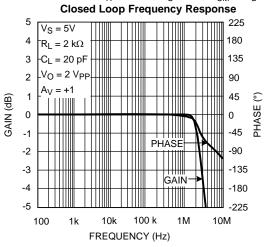

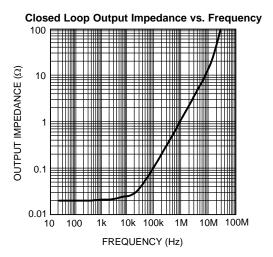

The unity gain follower is the most sensitive configuration to capacitive loading. The combination of a capacitive load placed directly on the output of an amplifier along with the output impedance of the amplifier creates a phase lag which in turn reduces the phase margin of the amplifier. If phase margin is significantly reduced, the response will be either underdamped or the amplifier will oscillate.

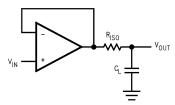

The LMP7715/LMP7716/LMP7716Q can directly drive capacitive loads of up to 120 pF without oscillating. To drive heavier capacitive loads, an isolation resistor,  $R_{\rm ISO}$  as shown in Figure 49, should be used. This resistor and  $C_L$  form a pole and hence delay the phase lag or increase the phase margin of the overall system. The larger the value of  $R_{\rm ISO}$ , the more stable the output voltage will be. However, larger values of  $R_{\rm ISO}$  result in reduced output swing and reduced output current drive.

Figure 49. Isolating Capacitive Load

#### INPUT CAPACITANCE

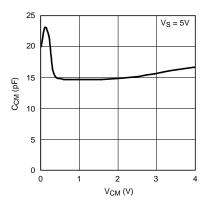

CMOS input stages inherently have low input bias current and higher input referred voltage noise. The LMP7715/LMP7716Q enhance this performance by having the low input bias current of only 50 fA, as well as, a very low input referred voltage noise of 5.8 nV/ $\sqrt{\text{Hz}}$ . In order to achieve this a larger input stage has been used. This larger input stage increases the input capacitance of the LMP7715/LMP7716/LMP7716Q. Figure 50 shows typical input common mode capacitance of the LMP7715/LMP7716Q.

Figure 50. Input Common Mode Capacitance

This input capacitance will interact with other impedances, such as gain and feedback resistors which are seen on the inputs of the amplifier, to form a pole. This pole will have little or no effect on the output of the amplifier at low frequencies and under DC conditions, but will play a bigger role as the frequency increases. At higher frequencies, the presence of this pole will decrease phase margin and also cause gain peaking. In order to compensate for the input capacitance, care must be taken in choosing feedback resistors. In addition to being selective in picking values for the feedback resistor, a capacitor can be added to the feedback path to increase stability.

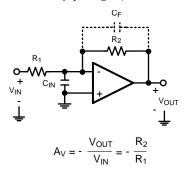

The DC gain of the circuit shown in Figure 51 is simply  $-R_2/R_1$ .

Figure 51. Compensating for Input Capacitance

For the time being, ignore C<sub>F</sub>. The AC gain of the circuit in Figure 51 can be calculated as follows:

$$\frac{V_{OUT}}{V_{IN}}(s) = \frac{-R_2/R_1}{\left[1 + \frac{s}{\left(\frac{A_0 R_1}{R_1 + R_2}\right)} + \frac{s^2}{\left(\frac{A_0}{C_{IN} R_2}\right)}\right]}$$

(1)

This equation is rearranged to find the location of the two poles:

$$P_{1,2} = \frac{-1}{2C_{IN}} \left[ \frac{1}{R_1} + \frac{1}{R_2} \pm \sqrt{\left(\frac{1}{R_1} + \frac{1}{R_2}\right)^2 - \frac{4A_0C_{IN}}{R_2}} \right]$$

(2)

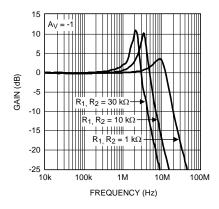

As shown in Equation 2, as the values of  $R_1$  and  $R_2$  are increased, the magnitude of the poles are reduced, which in turn decreases the bandwidth of the amplifier. Figure 52 shows the frequency response with different value resistors for  $R_1$  and  $R_2$ . Whenever possible, it is best to chose smaller feedback resistors.

Figure 52. Closed Loop Frequency Response

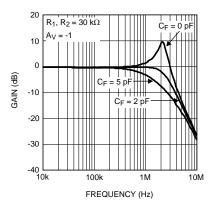

As mentioned before, adding a capacitor to the feedback path will decrease the peaking. This is because  $C_F$  will form yet another pole in the system and will prevent pairs of poles, or complex conjugates from forming. It is the presence of pairs of poles that cause the peaking of gain. Figure 53 shows the frequency response of the schematic presented in Figure 51 with different values of  $C_F$ . As can be seen, using a small value capacitor significantly reduces or eliminates the peaking.

Figure 53. Closed Loop Frequency Response

### TRANSIMPEDANCE AMPLIFIER

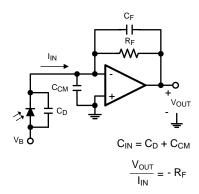

In many applications the signal of interest is a very small amount of current that needs to be detected. Current that is transmitted through a photodiode is a good example. Barcode scanners, light meters, fiber optic receivers, and industrial sensors are some typical applications utilizing photodiodes for current detection. This current needs to be amplified before it can be further processed. This amplification is performed using a current-to-voltage converter configuration or transimpedance amplifier. The signal of interest is fed to the inverting input of an op amp with a feedback resistor in the current path. The voltage at the output of this amplifier will be equal to the negative of the input current times the value of the feedback resistor. Figure 54 shows a transimpedance amplifier configuration.  $C_D$  represents the photodiode parasitic capacitance and  $C_{CM}$  denotes the common-mode capacitance of the amplifier. The presence of all of these capacitances at higher frequencies might lead to less stable topologies at higher frequencies. Care must be taken when designing a transimpedance amplifier to prevent the circuit from oscillating.

With a wide gain bandwidth product, low input bias current and low input voltage and current noise, the LMP7715/LMP7716Q are ideal for wideband transimpedance applications.

Figure 54. Transimpedance Amplifier

A feedback capacitance  $C_F$  is usually added in parallel with  $R_F$  to maintain circuit stability and to control the frequency response. To achieve a maximally flat,  $2^{nd}$  order response,  $R_F$  and  $C_F$  should be chosen by using Equation 3

$$C_F = \sqrt{\frac{C_{IN}}{GBWP * 2 \pi R_F}}$$

(3)

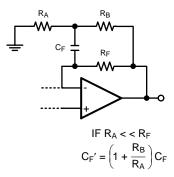

Calculating  $C_F$  from Equation 3 can sometimes result in capacitor values which are less than 2 pF. This is especially the case for high speed applications. In these instances, it is often more practical to use the circuit shown in Figure 55 in order to allow more sensible choices for  $C_F$ . The new feedback capacitor,  $C_F$ , is (1+  $R_B/R_A$ )  $C_F$ . This relationship holds as long as  $R_A << R_F$ .

Figure 55. Modified Transimpedance Amplifier

#### SENSOR INTERFACE

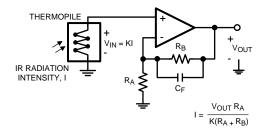

The LMP7715/LMP7716Q have low input bias current and low input referred noise, which make them ideal choices for sensor interfaces such as thermopiles, Infra Red (IR) thermometry, thermocouple amplifiers, and pH electrode buffers.

Thermopiles generate voltage in response to receiving radiation. These voltages are often only a few microvolts. As a result, the operational amplifier used for this application needs to have low offset voltage, low input voltage noise, and low input bias current. Figure 56 shows a thermopile application where the sensor detects radiation from a distance and generates a voltage that is proportional to the intensity of the radiation. The two resistors,  $R_A$  and  $R_B$ , are selected to provide high gain to amplify this signal, while  $C_F$  removes the high frequency noise.

Figure 56. Thermopile Sensor Interface

#### PRECISION RECTIFIER

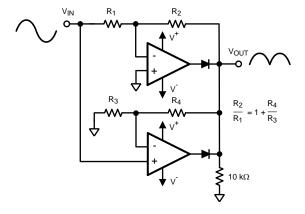

Rectifiers are electrical circuits used for converting AC signals to DC signals. Figure 57 shows a full-wave precision rectifier. Each operational amplifier used in this circuit has a diode on its output. This means for the diodes to conduct, the output of the amplifier needs to be positive with respect to ground. If  $V_{IN}$  is in its positive half cycle then only the output of the bottom amplifier will be positive. As a result, the diode on the output of the bottom amplifier will conduct and the signal will show at the output of the circuit. If  $V_{IN}$  is in its negative half cycle then the output of the top amplifier will be positive, resulting in the diode on the output of the top amplifier conducting and delivering the signal from the amplifier's output to the circuit's output.

For  $R_2/R_1 \ge 2$ , the resistor values can be found by using the equation shown in Figure 57. If  $R_2/R_1 = 1$ , then  $R_3$  should be left open, no resistor needed, and  $R_4$  should simply be shorted.

Figure 57. Precision Rectifier

### www.ti.com

# **REVISION HISTORY**

| Changes from Revision D (March 2013) to Revision E |                                                    |  |    |

|----------------------------------------------------|----------------------------------------------------|--|----|

| •                                                  | Changed layout of National Data Sheet to TI format |  | 18 |

Product Folder Links: LMP7715 LMP7716 LMP7716Q

www.ti.com

24-Jul-2025

### **PACKAGING INFORMATION**

| Orderable part number | Status | Material type | Package   Pins     | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C)     | Part marking (6) |

|-----------------------|--------|---------------|--------------------|-----------------------|------|-------------------------------|----------------------------|------------------|------------------|

|                       |        |               |                    |                       |      | (4)                           | (5)                        |                  |                  |

| LMP7715MF/NOPB        | Active | Production    | SOT-23 (DBV)   5   | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MF/NOPB.A      | Active | Production    | SOT-23 (DBV)   5   | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFE/NOPB       | Active | Production    | SOT-23 (DBV)   5   | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFE/NOPB.A     | Active | Production    | SOT-23 (DBV)   5   | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFE/NOPB.B     | Active | Production    | SOT-23 (DBV)   5   | 250   SMALL T&R       | -    | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFX/NOPB       | Active | Production    | SOT-23 (DBV)   5   | 3000   LARGE T&R      | Yes  | Call TI   Sn                  | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFX/NOPB.A     | Active | Production    | SOT-23 (DBV)   5   | 3000   LARGE T&R      | Yes  | Call TI                       | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7715MFX/NOPB.B     | Active | Production    | SOT-23 (DBV)   5   | 3000   LARGE T&R      | -    | Call TI                       | Level-1-260C-UNLIM         | -40 to 125       | AV3A             |

| LMP7716MM/NOPB        | Active | Production    | VSSOP (DGK)   8    | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716MM/NOPB.A      | Active | Production    | VSSOP (DGK)   8    | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716MME/NOPB       | Active | Production    | VSSOP (DGK)   8    | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716MME/NOPB.A     | Active | Production    | VSSOP (DGK)   8    | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716MMX/NOPB       | Active | Production    | VSSOP (DGK)   8    | 3500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716MMX/NOPB.A     | Active | Production    | VSSOP (DGK)   8    | 3500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AX3A             |

| LMP7716Q-MDA.A        | Active | Production    | DIESALE (Y)   0    | 374   NOT REQUIRED    | Yes  | Call TI                       | Level-1-NA-UNLIM           | See LMP7716Q-MDA |                  |

| LMP7716Q-MWA.A        | Active | Production    | WAFERSALE (YS)   0 | 1   NOT REQUIRED      | -    | Call TI                       | Level-1-NA-UNLIM           | -40 to 125       |                  |

| LMP7716QMM/NOPB       | Active | Production    | VSSOP (DGK)   8    | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMM/NOPB.A     | Active | Production    | VSSOP (DGK)   8    | 1000   SMALL T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMME/NOPB      | Active | Production    | VSSOP (DGK)   8    | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMME/NOPB.A    | Active | Production    | VSSOP (DGK)   8    | 250   SMALL T&R       | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMMX/NOPB      | Active | Production    | VSSOP (DGK)   8    | 3500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMMX/NOPB.A    | Active | Production    | VSSOP (DGK)   8    | 3500   LARGE T&R      | Yes  | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

| LMP7716QMMX/NOPB.B    | Active | Production    | VSSOP (DGK)   8    | 3500   LARGE T&R      | -    | SN                            | Level-1-260C-UNLIM         | -40 to 125       | AR5A             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

PACKAGE OPTION ADDENDUM

www.ti.com 24-Jul-2025

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF LMP7716, LMP7716-Q1:

Catalog : LMP7716

Automotive: LMP7716-Q1

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Automotive Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 1-Aug-2025

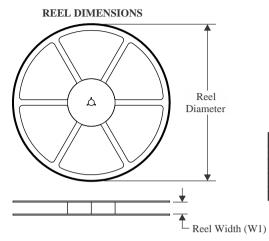

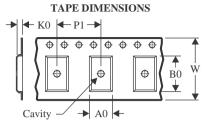

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

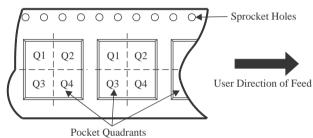

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMP7715MF/NOPB   | SOT-23          | DBV                | 5 | 1000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP7715MFE/NOPB  | SOT-23          | DBV                | 5 | 250  | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP7715MFX/NOPB  | SOT-23          | DBV                | 5 | 3000 | 178.0                    | 8.4                      | 3.2        | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

| LMP7716MM/NOPB   | VSSOP           | DGK                | 8 | 1000 | 177.8                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMP7716MME/NOPB  | VSSOP           | DGK                | 8 | 250  | 177.8                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMP7716MMX/NOPB  | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMP7716QMM/NOPB  | VSSOP           | DGK                | 8 | 1000 | 177.8                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMP7716QMME/NOPB | VSSOP           | DGK                | 8 | 250  | 177.8                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| LMP7716QMMX/NOPB | VSSOP           | DGK                | 8 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 1-Aug-2025

\*All dimensions are nominal

| All difficultions are norminal |              |                 |      |      |             |            |             |

|--------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| LMP7715MF/NOPB                 | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMP7715MFE/NOPB                | SOT-23       | DBV             | 5    | 250  | 208.0       | 191.0      | 35.0        |

| LMP7715MFX/NOPB                | SOT-23       | DBV             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LMP7716MM/NOPB                 | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LMP7716MME/NOPB                | VSSOP        | DGK             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LMP7716MMX/NOPB                | VSSOP        | DGK             | 8    | 3500 | 356.0       | 356.0      | 35.0        |

| LMP7716QMM/NOPB                | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LMP7716QMME/NOPB               | VSSOP        | DGK             | 8    | 250  | 208.0       | 191.0      | 35.0        |

| LMP7716QMMX/NOPB               | VSSOP        | DGK             | 8    | 3500 | 356.0       | 356.0      | 35.0        |

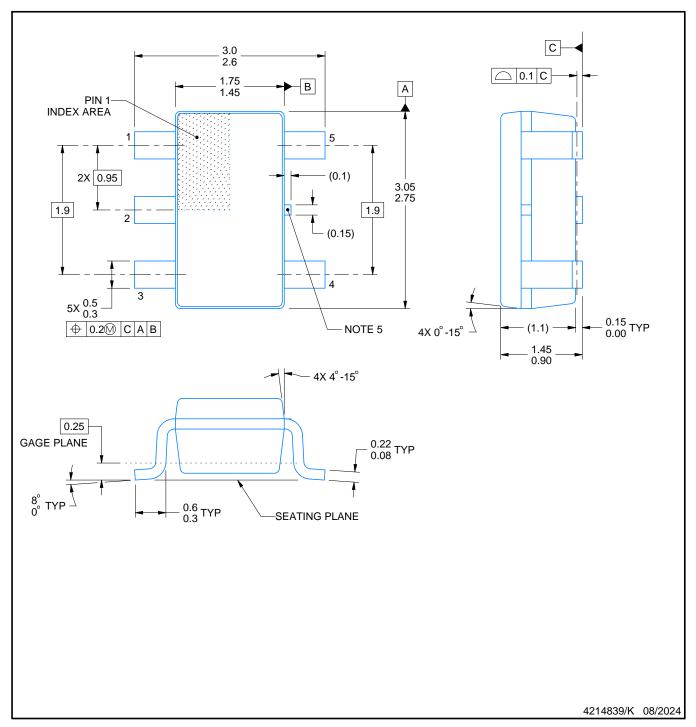

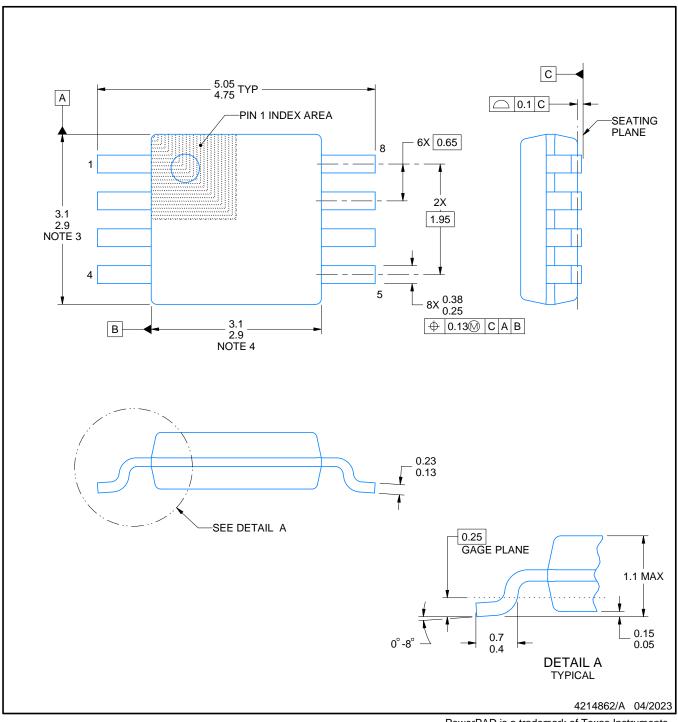

SMALL OUTLINE TRANSISTOR

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

- 4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

- 5. Support pin may differ or may not be present.

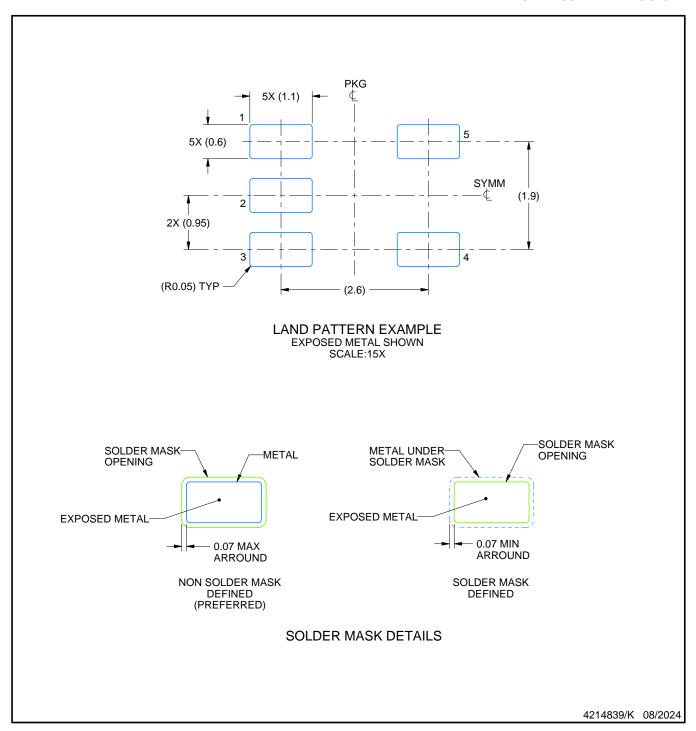

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

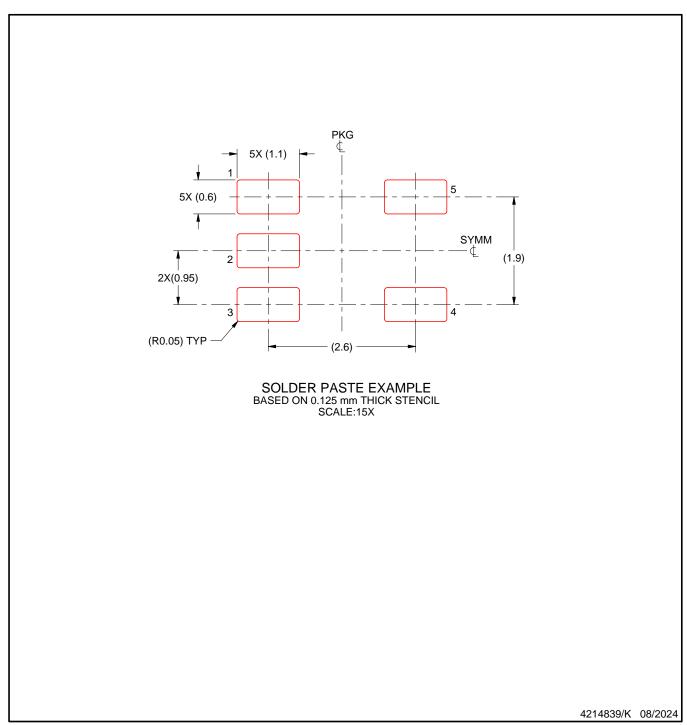

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

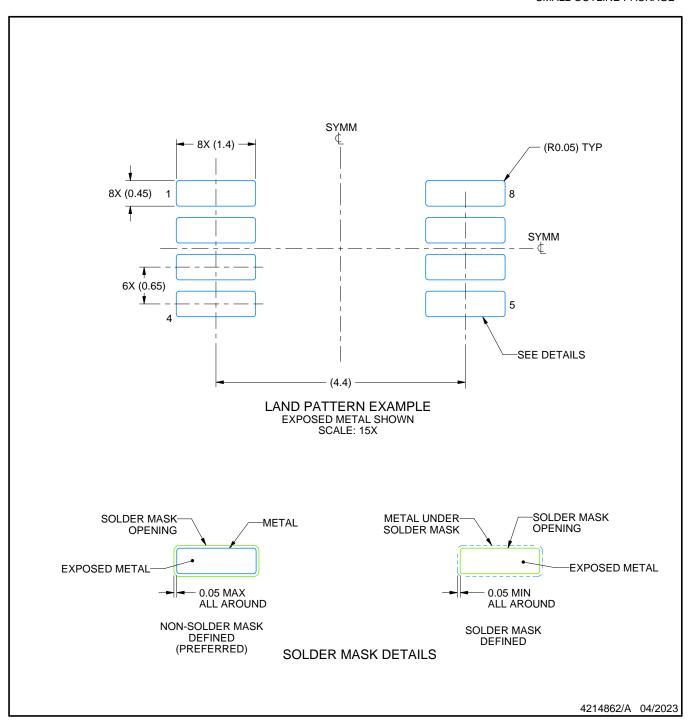

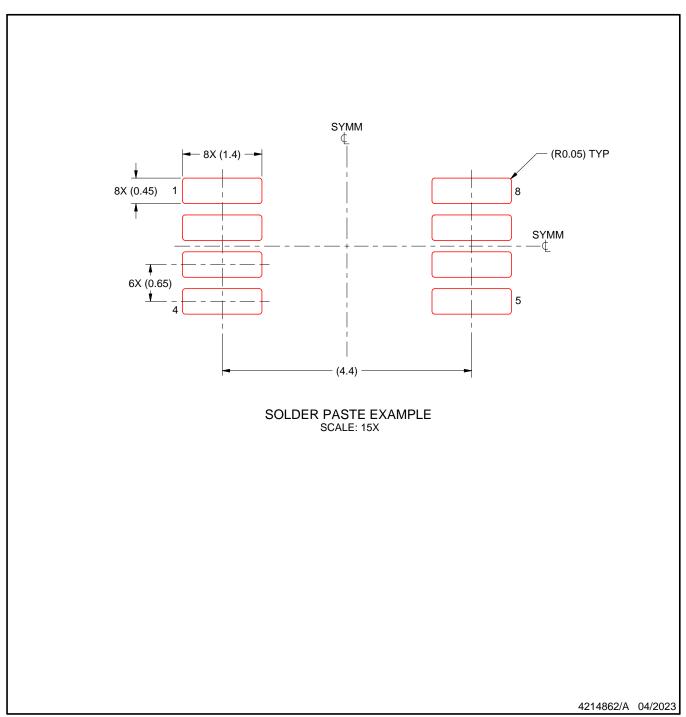

SMALL OUTLINE PACKAGE

#### NOTES:

PowerPAD is a trademark of Texas Instruments.

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 6. Publication IPC-7351 may have alternate designs.

- 7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

- 8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

- 9. Size of metal pad may vary due to creepage requirement.

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 12. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated