Technical documentation

TEXAS INSTRUMENTS

LM5146 SNVSBV0A – JUNE 2021 – REVISED JUNE 2021

# LM5146 100-V Synchronous Buck DC/DC Controller With Wide Duty Cycle Range

# **1** Features

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Versatile synchronous buck DC/DC controller

- Wide input voltage range of 5.5 V to 100 V

- 150°C maximum junction temperature

- 0.8-V reference with ±1% feedback accuracy

- Adjustable output voltage from 0.8 V to 60 V

- 40-ns t<sub>ON(min)</sub> for high V<sub>IN</sub> / V<sub>OUT</sub> ratio

- 140-ns t<sub>OFF(min)</sub> for low dropout

- Lossless R<sub>DS(on)</sub> or shunt current sensing

- Optimized for CÍSPR 11 and CISPR 32 Class B EMI requirements

- Switching frequency from 100 kHz to 1 MHz

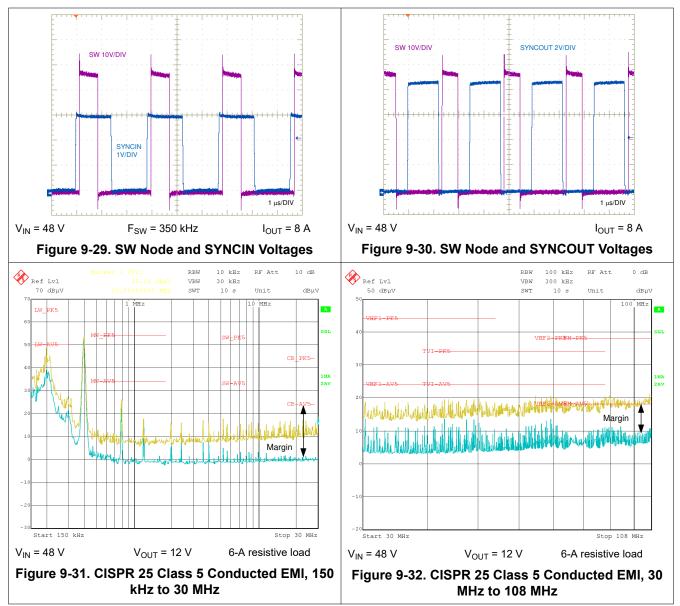

- SYNC in and SYNC out capability

- Selectable diode emulation or FPWM

- 7.5-V gate drivers for standard  $V_{TH}$  MOSFETs

- 14-ns adaptive dead-time control

- 2.3-A source and 3.5-A sink capability

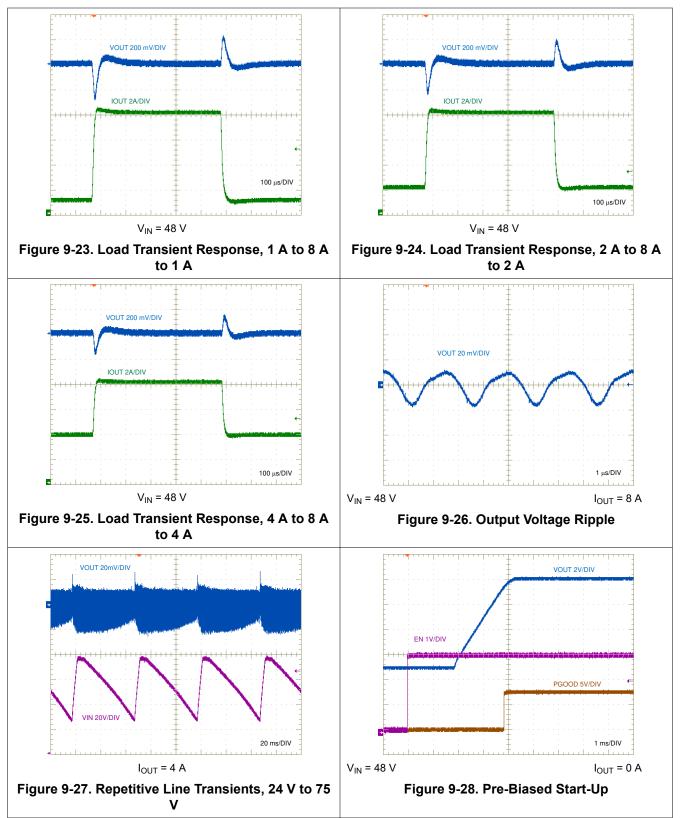

- Fast line and load transient response

- Voltage-mode control with line feedforward

- High gain-bandwidth error amplifier

- Inherent protection features for robust design

- Adjustable output voltage soft start

- Hiccup-mode overcurrent protection

- Input UVLO with hysteresis

- VCC and gate-drive UVLO protection

- Precision enable input and open-drain PGOOD indicator for sequencing and control

- Thermal shutdown protection with hysteresis

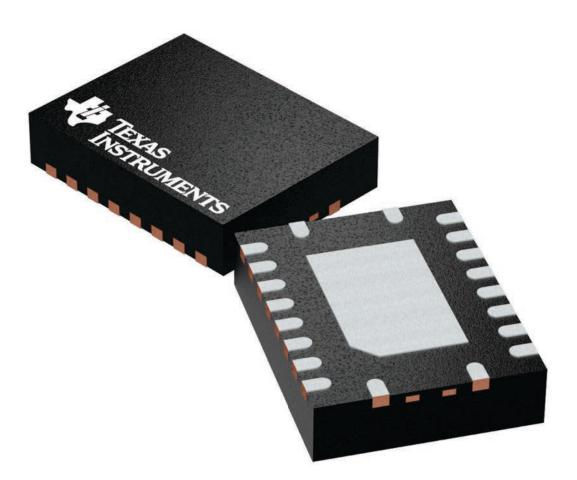

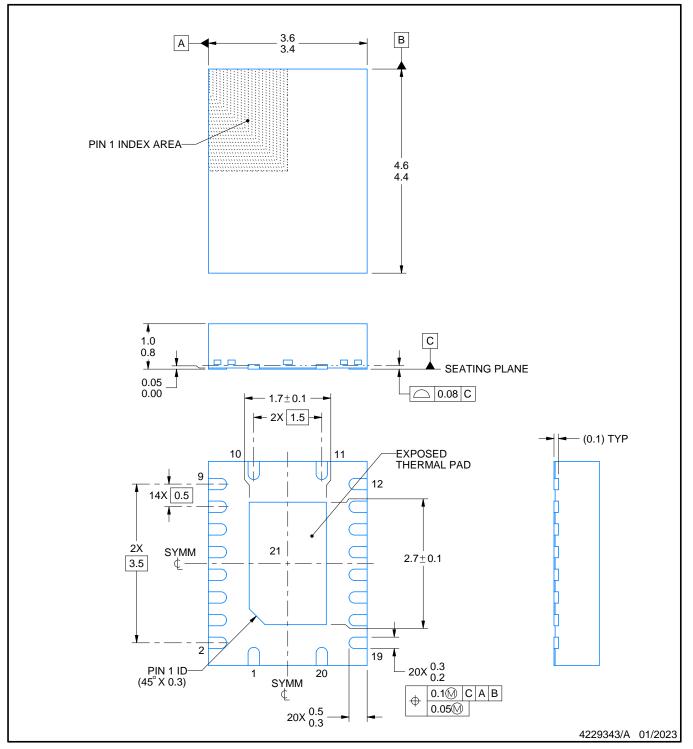

- 20-pin VQFN package with wettable flanks

- Create a custom design using the LM5146 with WEBENCH<sup>®</sup> Power Designer

# 2 Applications

- Wireless infrastructure, cloud computing

- Industrial motor drives, test and measurement

- Personal transport vehicle: electric bike

- Asset tracking and fleet management systems

- Non-isolated PoE, IP cameras

- Inverting buck-boost regulators

# **3 Description**

The LM5146 100-V synchronous buck controller regulates from a high input voltage source or from an input rail subject to high-voltage transients, minimizing the need for external surge suppression components. A high-side switch minimum on-time of 40 ns gives large step-down ratios, enabling the direct step-down conversion from a 48-V nominal input to low-voltage rails for reduced system complexity and solution cost. The LM5146 continues to operate during input voltage dips as low as 5.5 V, at nearly 100% duty cycle if needed, making it an excellent choice for high-performance industrial controls, robotics, datacom, and RF applications.

Forced-PWM (FPWM) operation eliminates switching frequency variation to minimize EMI, while user-selectable diode emulation lowers current consumption at light-load conditions. The adjustable switching frequency as high as 1 MHz can be synchronized to an external clock source to eliminate beat frequencies in noise-sensitive applications.

**Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| LM5146      | VQFN (20)              | 4.50 mm × 3.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

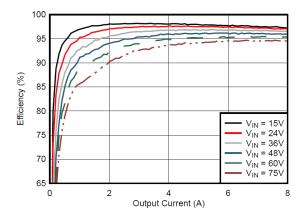

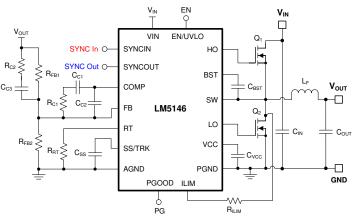

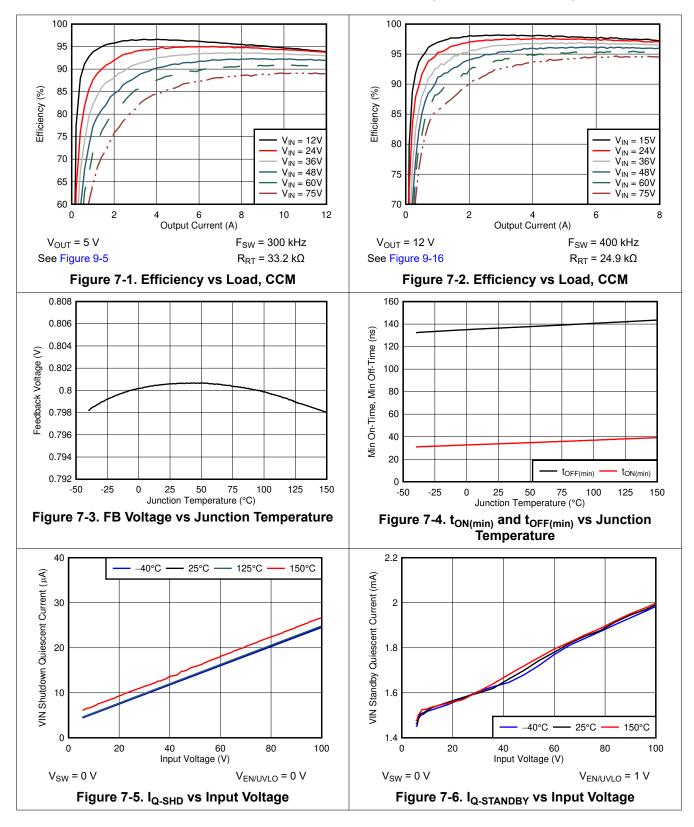

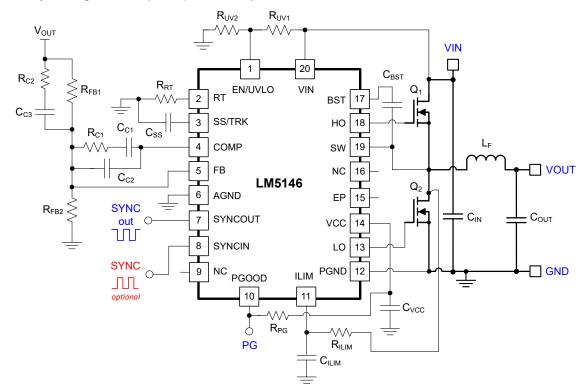

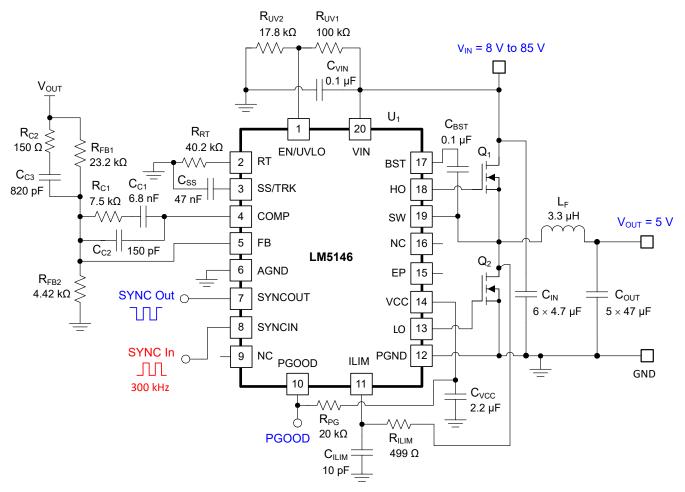

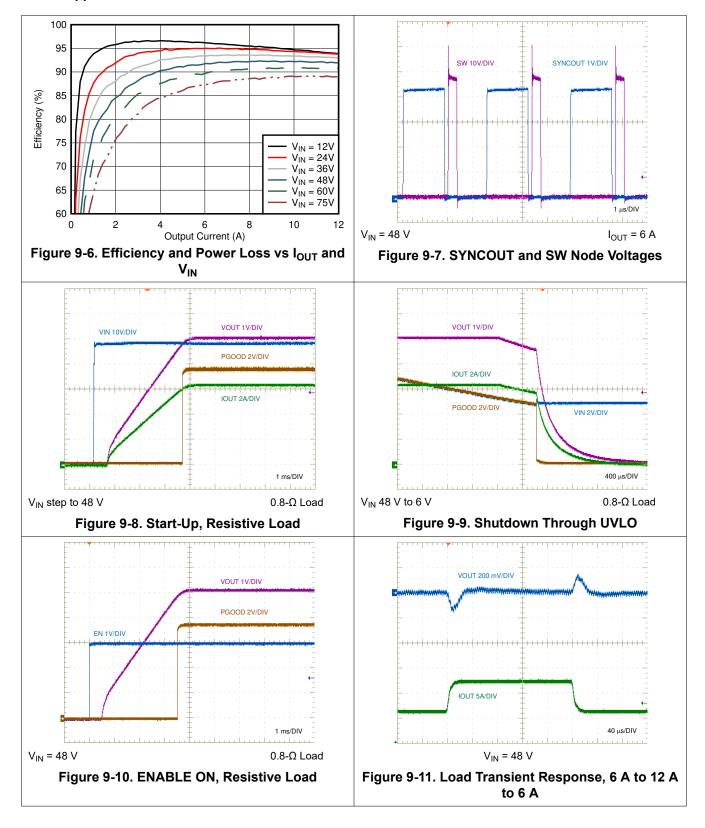

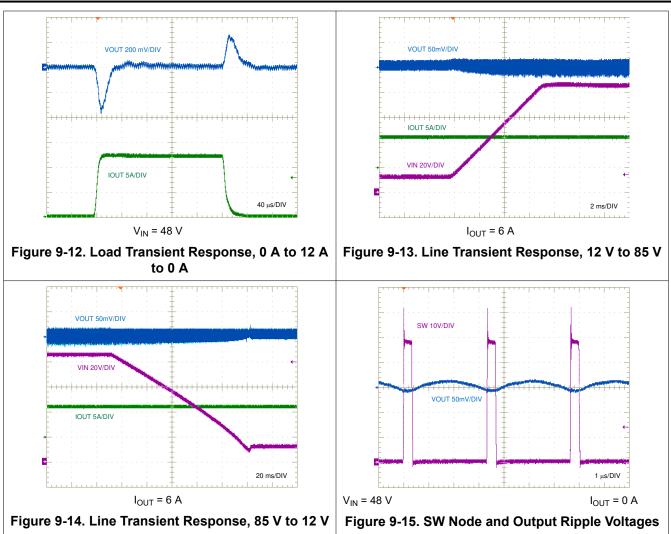

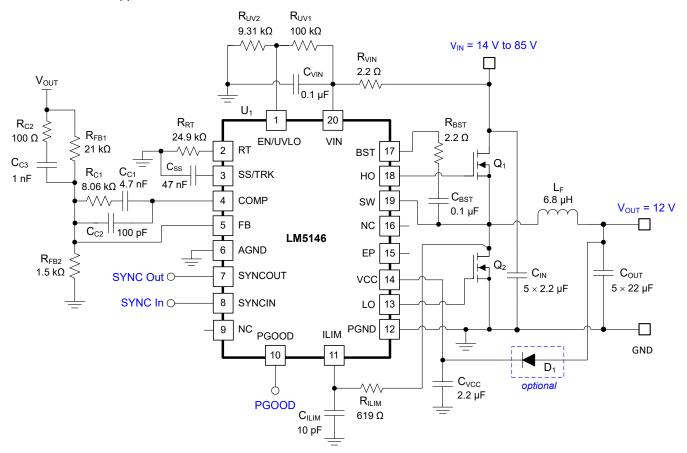

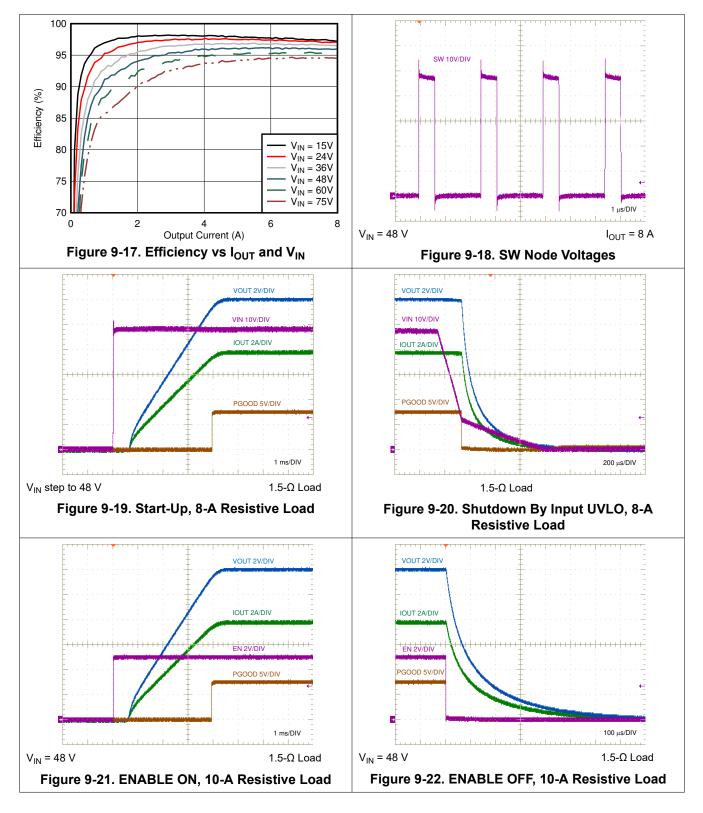

Typical Application Circuit and Efficiency Performance, V<sub>OUT</sub> = 12 V, F<sub>SW</sub> = 400 kHz

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 | Features                             | 1 |

|---|--------------------------------------|---|

| 2 | Applications                         | 1 |

| 3 | Description                          | 1 |

|   | Revision History                     |   |

| 5 | Description (continued)              | 3 |

| 6 | Pin Configuration and Functions      | 1 |

|   | 6.1 Wettable Flanks                  | 5 |

| 7 | Specifications                       | 3 |

|   | 7.1 Absolute Maximum Ratings         | 6 |

|   | 7.2 ESD Ratings                      | 3 |

|   | 7.3 Recommended Operating Conditions | 7 |

|   | 7.4 Thermal Information              | 7 |

|   | 7.5 Electrical Characteristics       | 3 |

|   | 7.6 Switching Characteristics10      | ) |

|   | 7.7 Typical Characteristics11        | 1 |

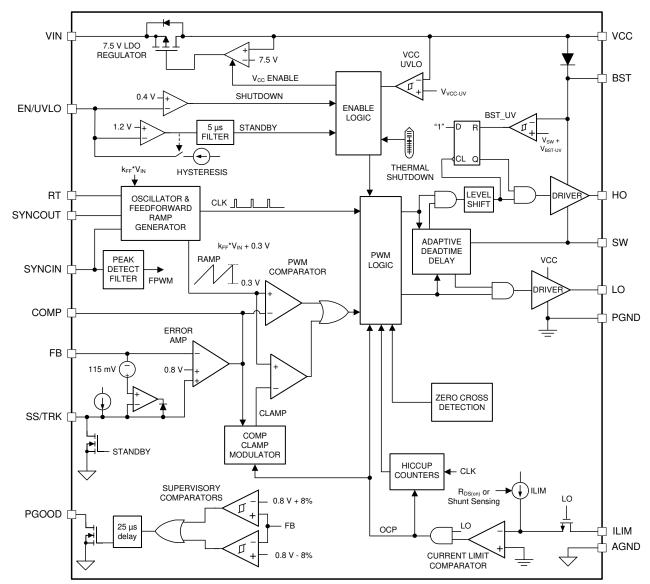

| 8 | Detailed Description16               | 3 |

|   | 8.1 Overview                         | 3 |

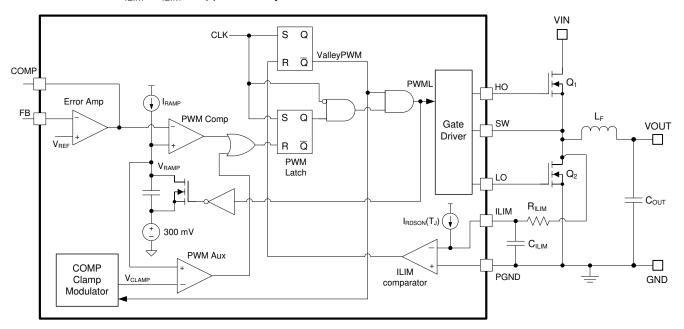

|   | 8.2 Functional Block Diagram16       |   |

|   | 8.3 Feature Description17            | 7 |

|   |                                      |   |

| 8.4 Device Functional Modes                           | .25  |

|-------------------------------------------------------|------|

| 9 Application and Implementation                      |      |

| 9.1 Application Information                           |      |

| 9.2 Typical Applications                              |      |

| 10 Power Supply Recommendations                       |      |

| 11 Layout                                             |      |

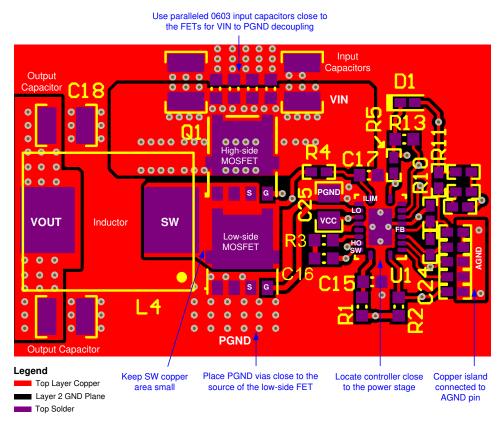

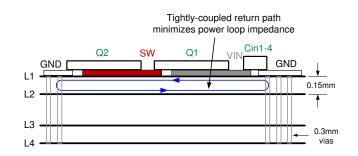

| 11.1 Layout Guidelines                                |      |

| 11.2 Layout Example                                   |      |

| 12 Device and Documentation Support                   |      |

| 12.1 Device Support                                   |      |

| 12.2 Documentation Support                            | . 52 |

| 12.3 Receiving Notification of Documentation Updates. |      |

| 12.4 Support Resources                                |      |

| 12.5 Trademarks                                       |      |

| 12.6 Electrostatic Discharge Caution                  |      |

| 12.7 Glossary                                         |      |

| 13 Mechanical, Packaging, and Orderable               |      |

| Information                                           | 54   |

|                                                       |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision * (June 2021) to Revision A (June 2021) | Page |

|----|--------------------------------------------------------------|------|

| •  | Updated functional safety link                               | 1    |

# **5** Description (continued)

The LM5146 voltage-mode controller with line feedforward drives external high-side and low-side N-channel power switches with robust 7.5-V gate drivers suitable for standard-threshold MOSFETs. Adaptively-timed gate drivers with 2.3-A source and 3.5-A sink capability minimize body diode conduction during switching transitions, reducing switching losses and improving thermal performance when driving MOSFETs at high input voltage and high frequency. The LM5146 can be powered from the output of the switching regulator or another available source, further improving efficiency.

A 180° out-of-phase clock output relative to the internal oscillator at SYNCOUT works well for cascaded or multi-channel power supplies to reduce input capacitor ripple current and EMI filter size. Additional features of the LM5146 include a configurable soft start, an open-drain power-good monitor for fault reporting and output monitoring, monotonic start-up into prebiased loads, integrated VCC bias supply regulator and bootstrap diode, external power supply tracking, precision enable input with hysteresis for adjustable line undervoltage lockout (UVLO), hiccup-mode overload protection, and thermal shutdown protection with automatic recovery.

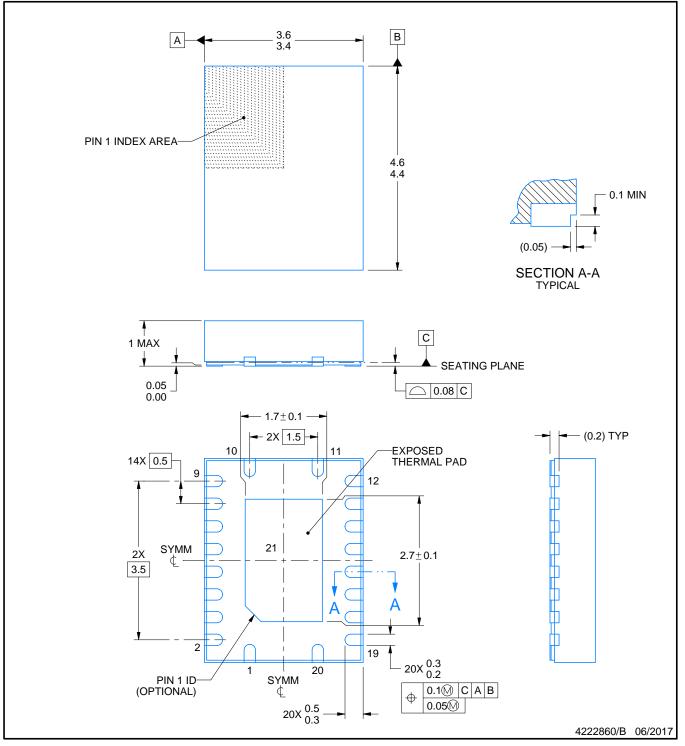

The LM5146 controller is offered in a 4.5-mm × 3.5-mm thermally enhanced, 20-pin VQFN package with additional spacing for high-voltage pins and wettable flanks for optical inspection of solder joint fillets.

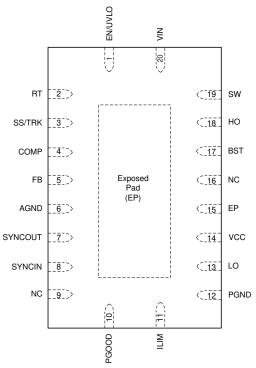

# **6** Pin Configuration and Functions

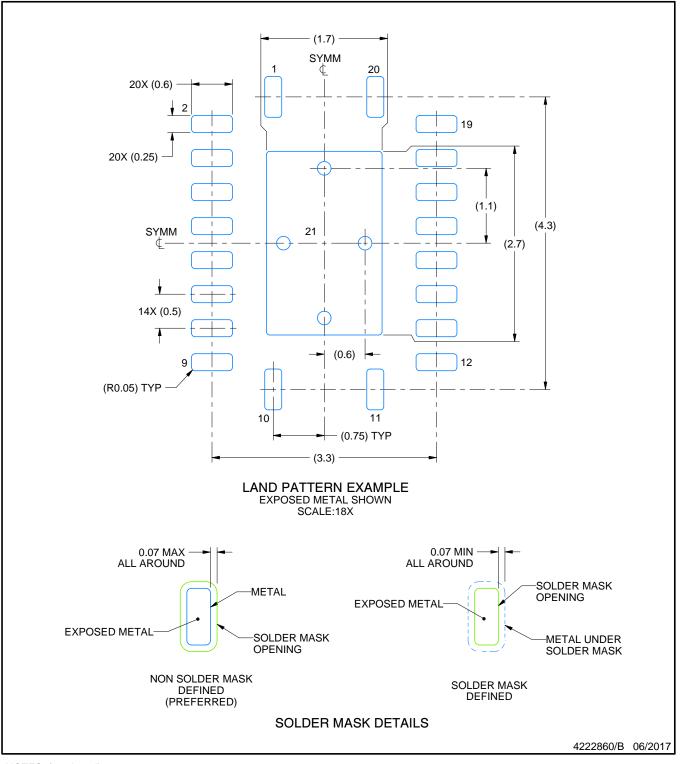

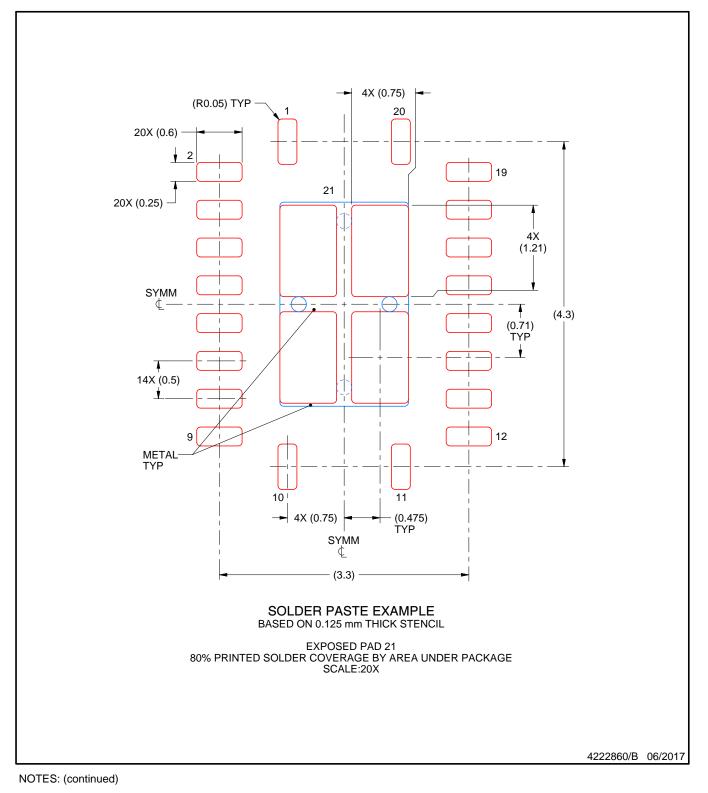

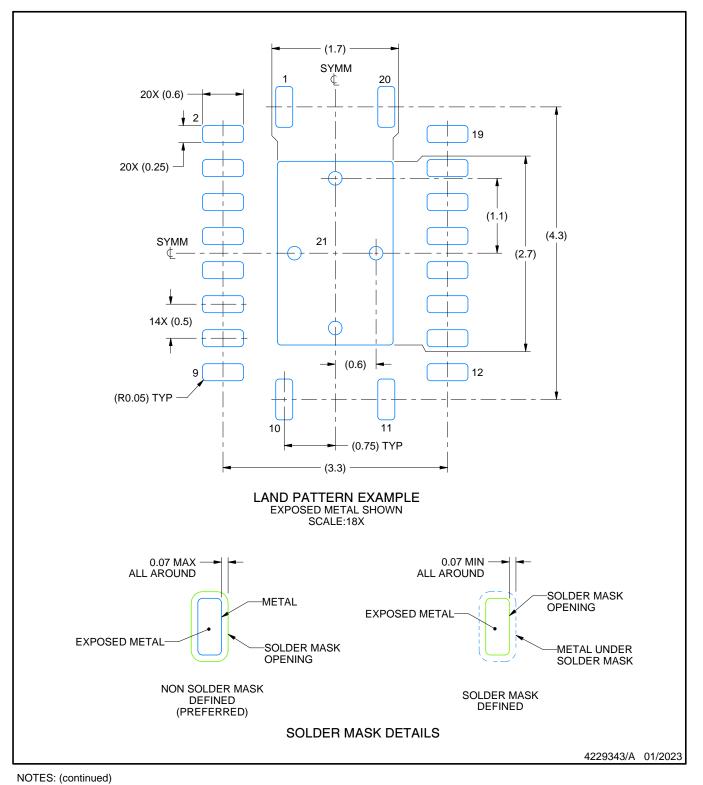

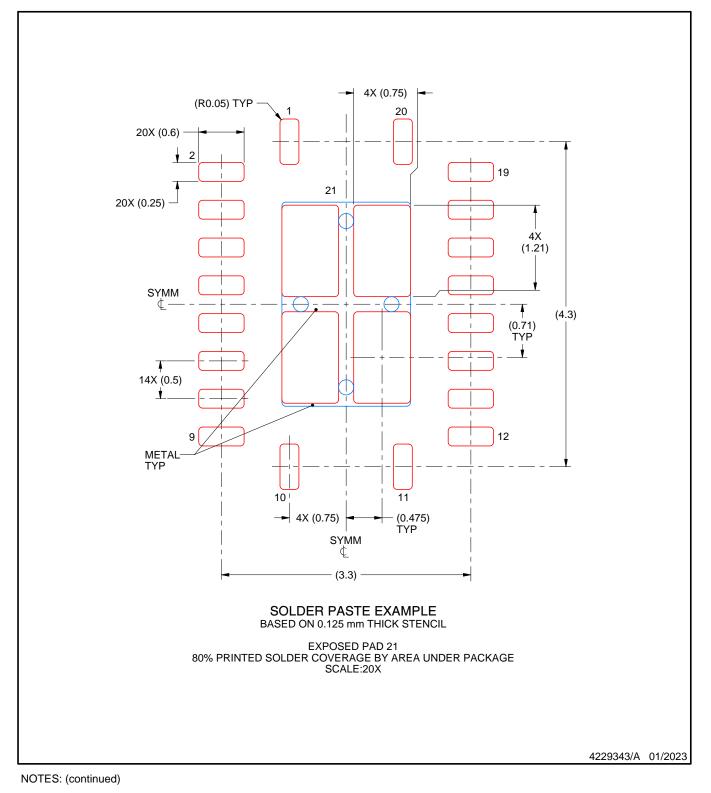

Connect Exposed Pad on bottom to AGND and PGND on the PCB.

### Figure 6-1. 20-Pin VQFN With Wettable Flanks in RGY Package (Top View)

#### Table 6-1. Pin Functions

| PIN |         | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----|---------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. |         |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

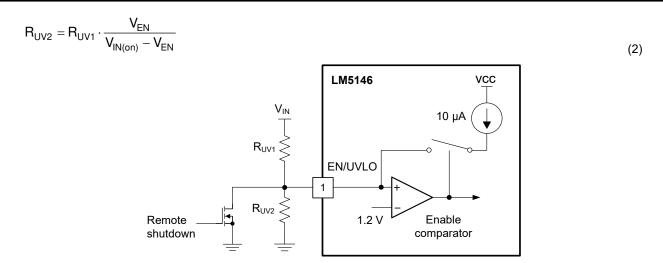

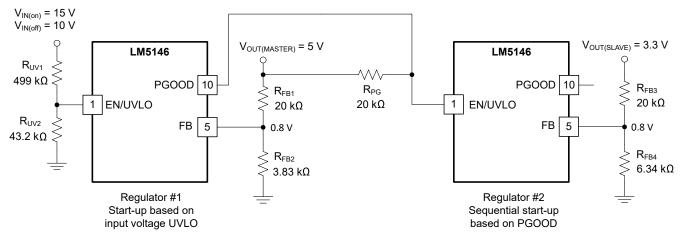

| 1   | EN/UVLO | I                  | Enable input and undervoltage lockout programming pin. If the EN/UVLO voltage is below 0.4 V, the controller is in shutdown mode with all functions disabled. If the EN/UVLO voltage is greater than 0.4 V and less than 1.2 V, the regulator is in standby mode with the VCC regulator operational, the SS pin grounded, and no switching at the HO and LO outputs. If the EN/UVLO voltage is above 1.2 V, the SS/TRK voltage can ramp and pulse-width modulated gate-drive signals are delivered to the HO and LO pins. A 10-µA current source is enabled when EN/UVLO exceeds 1.2 V and flows through the external UVLO resistor divider to provide hysteresis. Hysteresis can be adjusted by varying the resistance of the external divider.                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 2   | RT      | I                  | Oscillator frequency adjust pin. The internal oscillator is programmed with a single resistor between RT and the AGND. TI recommends a maximum oscillator frequency of 1 MHz. An RT pin resistor is required even when using the SYNCIN pin to synchronize to an external clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

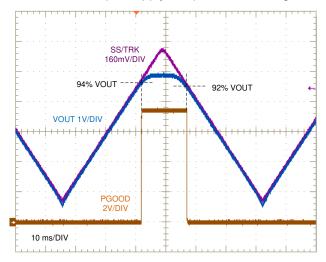

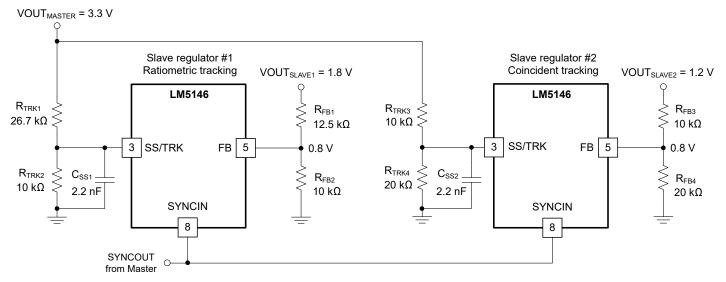

| 3   | SS/TRK  | I                  | Soft start and voltage-tracking pin. An external capacitor and an internal 10- $\mu$ A current source set the ramp<br>rate of the error amplifier reference during start-up. When the SS/TRK pin voltage is less than 0.8 V, the<br>SS/TRK voltage controls the noninverting input of the error amp. When the SS/TRK voltage exceeds 0.8 V, the<br>amplifier is controlled by the internal 0.8-V reference. SS/TRK is discharged to ground during standby and fault<br>conditions. After start-up, the SS/TRK voltage is clamped 115 mV above the FB pin voltage. If FB falls due to a<br>load fault, SS/TRK is discharged to a level 115 mV above FB to provide a controlled recovery when the fault is<br>removed. Voltage tracking can be implemented by connecting a low impedance reference between 0 V and 0.8<br>V to the SS/TRK pin. The 10- $\mu$ A SS/TRK charging current flows into the reference and produces a voltage error<br>if the impedance is not low. Connect a minimum capacitance from SS/TRK to AGND of 2.2 nF. |  |  |  |  |

| 4   | COMP    | 0                  | Low impedance output of the internal error amplifier. Connect the loop compensation network between the COMP pin and the FB pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 5   | FB      | I                  | Feedback connection to the inverting input of the internal error amplifier. A resistor divider from the output to this pin sets the output voltage level. The regulation threshold at the FB pin is nominally 0.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 6   | AGND    | Р                  | Analog ground. Return for the internal 0.8-V voltage reference and analog circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

#### Table 6-1. Pin Functions (continued)

| PIN     |                                                                                                     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | 1/0(.,                                                                                              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

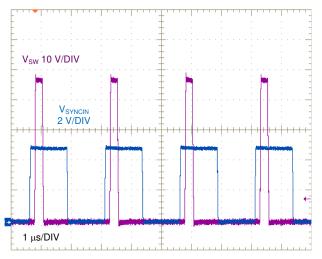

| SYNCOUT | 0                                                                                                   | Synchronization output. Logic output that provides a clock signal that is 180° out-of-phase with the high-side FET gate drive. Connect SYNCOUT of the master LM5146 to the SYNCIN pin of a second LM5146 to operate two controllers at the same frequency with 180° interleaved high-side FET switch turn-on transitions. Note that the SYNCOUT pin does not provide 180° interleaving when the controller is operating from an external clock that is different from the free-running frequency set by the RT resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SYNCIN  | I                                                                                                   | Dual function pin to provide an optional clock input and enable diode emulation by the low-side MOSFET.<br>Connecting a clock signal to the SYNCIN pin synchronizes switching to the external clock. Diode emulation<br>by the low-side MOSFET is disabled when the controller is synchronized to an external clock, and negative<br>inductor current can flow in the low-side MOSFET with light loads. A continuous logic low state at the<br>SYNCIN pin enables diode emulation to prevent reverse current flow in the inductor. Diode emulation results in<br>discontinuous mode operation (DCM) at light loads, which improves efficiency. A logic high state at the SYNCIN<br>pin disables diode emulation, producing forced-PWM (FPWM) operation. During soft start when SYNCIN is high<br>or a clock signal is present, the LM5146 operates in diode emulation mode until the output is in regulation, then<br>gradually increases the SW zero-cross threshold, resulting in a gradual transition from DCM to FPWM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NC      | —                                                                                                   | No electrical connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PGOOD   | 0                                                                                                   | Power-good indicator. This pin is an open-drain output. A high state indicates that the voltage at the FB pin is within a specified tolerance window centered at 0.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

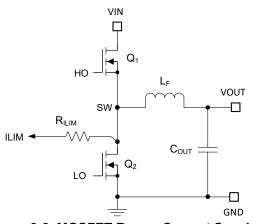

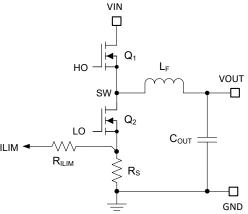

| ILIM    | I                                                                                                   | Current limit adjust and current sense comparator input. A current sourced from the ILIM pin through an external resistor programs the threshold voltage for valley current limiting. The opposite end of the threshold adjust resistor can be connected to either the drain of the low-side MOSFET for R <sub>DS(on)</sub> sensing or to a current sense resistor connected to the source of the low-side FET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PGND    | Ρ                                                                                                   | Power ground return pin for the low-side MOSFET gate driver. Connect directly to the source of the low-side MOSFET or the ground side of a shunt resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LO      | Ρ                                                                                                   | Low-side MOSFET gate drive output. Connect to the gate of the low-side synchronous rectifier FET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

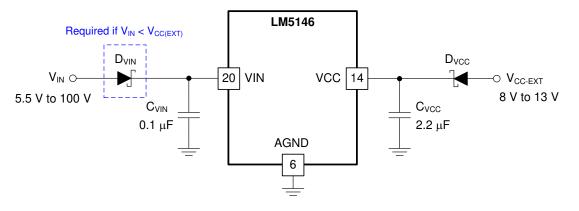

| VCC     | 0                                                                                                   | Output of the 7.5-V bias regulator. Locally decouple to PGND using a low-ESR/ESL capacitor located as close as possible to the controller. Controller bias can be supplied from an external supply that is greater than the internal VCC regulation voltage. Use caution when applying external bias to ensure that the applied voltage is not greater than the minimum $V_{IN}$ voltage and does not exceed the VCC pin maximum operating rating. See the <i>Recommended Operation Conditions</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EP      |                                                                                                     | Pin is internally connected to exposed pad of the package. Connect to GND at the exposed pad to improve heat spreading.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NC      | _                                                                                                   | No electrical connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| BST     | 0                                                                                                   | Bootstrap supply for the high-side gate driver. Connect to the bootstrap (boot) capacitor. The bootstrap capacitor supplies current to the high-side FET gate and must be placed as close as possible to controller. If an external bootstrap diode is used to reduce the time required to charge the bootstrap capacitor, connect the cathode of the diode to the BST pin and anode to VCC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| НО      | Ρ                                                                                                   | High-side MOSFET gate drive output. Connect to the gate of the high-side MOSFET through a short, low inductance path.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SW      | Ρ                                                                                                   | Switching node of the buck controller. Connect to the bootstrap capacitor, the source terminal of the high-side MOSFET, and the drain terminal of the low-side MOSFET using short, low inductance paths.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VIN     | Р                                                                                                   | Supply voltage input for the VCC LDO regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| EP      | _                                                                                                   | Exposed pad of the package. Electrically isolated. Solder to the system ground plane to reduce thermal resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | NAME<br>SYNCOUT<br>SYNCIN<br>SYNCIN<br>PGOOD<br>ILIM<br>ILIM<br>ILIM<br>IC<br>IC<br>SW<br>SW<br>VIN | NAME I/O(1)<br>SYNCOUT O<br>SYNCIN O<br>SYNCIN O<br>PGOOD O<br>ILIM O<br>ILIM O<br>ILIM O<br>ILO |

(1) P = Power, G = Ground, I = Input, O = Output

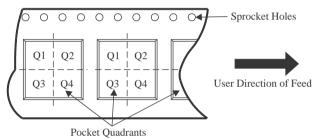

#### 6.1 Wettable Flanks

100% automated visual inspection (AVI) post-assembly is typically required to meet requirements for high reliability and robustness. Standard quad-flat no-lead (VQFN) packages do not have solderable or exposed pins and terminals that are easily viewed. Therefore, it is difficult to visually determine whether or not the package is successfully soldered onto the printed-circuit board (PCB). The wettable-flank process was developed to resolve the issue of side-lead wetting of leadless packaging. The LM5146 is assembled using a 20-pin VQFN package with wettable flanks to provide a visual indicator of solderability, which reduces the inspection time and manufacturing costs.

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over the recommended operating junction temperature of -40°C to +150°C (unless otherwise noted).<sup>(1)</sup>

| Input voltage         VIN         MAX         UNIT           SW $-0.3$ $100$ $-0.3$ $100$ SW (20-ns transient) $5$ $100$ $5$ $100$ SW (20-ns transient) $5$ $100$ $5$ $5$ $100$ EN/UVLO $0.3$ $100$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $5$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ $55$ -                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                      |      |     |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------|------|-----|------|

| SW        1         100           SW (20-ns transient)        5         100           ILIM        1         100           EN/UVLO         -0.3         100           VCC         -0.3         100           VCC         -0.3         14           FB, COMP, SS/TRK, RT         -0.3         14           SYNCIN         -0.3         14           BST to VCC         -0.3         110           BST to VCC         100         100           BST to SW         -0.3         110           VCC to BST (20-ns transient)         -0.3         14           VCC to BST (20-ns transient)         -0.3         14           VCC to BST (20-ns transient)         -0.3         14           VCC to BST (20-ns transient)         -3         -7           LO (20-ns transient)         -3         -3           PGOOD         -0.3         14           Operating junction-tmperature, T_J         150         °C |                                                |                                      | MIN  | MAX | UNIT |