LDC3114-Q1 SNOSDC7B - DECEMBER 2021 - REVISED DECEMBER 2021

# LDC3114-Q1 4-Channel Hybrid Inductive Touch and Inductance to Digital Converter

#### 1 Features

- AEC-Q100 qualified with the following results:

- Device temperature grade 1: –40°C to +125°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- Multiple modes of operation:

- Raw data mode: access pre-processed inductance measurement data to enable advanced algorithms on MCU for linear sensing

- Button mode: button press detection with baseline tracking and advanced on-chip post processing

- Force level measurement of touch buttons

- Pin and register compatible to LDC2114

- Robust EMI performance allows for CISPR 22 and CISPR 24 compliance

- Four independent channel operation

- Configurable scan rates:

- 0.625 SPS to 160 SPS

- Continuous scanning option

- Advanced button press detection algorithms:

- Adjustable force threshold per button

- Environmental shift compensation

- Simultaneous button press detection

- Low current consumption:

- One button: 6 µA at 0.625 SPS

- Two buttons: 72 μA at 20 SPS

- Interface:

- 1.8-V and 3.3-V compliant I<sup>2</sup>C and INTB

- 1.8-V logic output per channel for buttons

#### 2 Applications

- Automotive

- Touch buttons and force touch buttons:

- Steering wheel control

- Automotive display module

- Automotive head unit

- Door handle module

- Powertrain position sensor

- Automatic transmission

### 3 Description

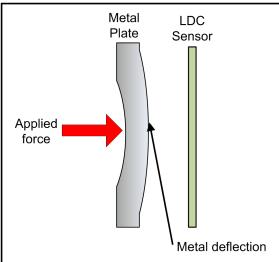

The LDC3114-Q1 is an inductive sensing device that enables touch button design for human machine interface (HMI) on a wide variety of materials by measuring small deflections of conductive targets using a coil that can be implemented on a small printed circuit board (PCB) located behind the panel. This technology can be used for precise linear position sensing of metal targets for automotive, consumer and industrial applications by allowing access to the raw data representing the inductance value. Inductive sensing solution is insensitive to humidity or non-conductive contaminants such as oil and dirt.

The button mode of LDC3114-Q1 is able to automatically correct for any deformation in the conductive targets. The LDC3114-Q1 offers wellmatched channels, which allow for differential ratiometric measurements which and enable compensation of environmental and aging conditions such as temperature and mechanical drift. The LDC3114-Q1 includes an ultra-low power mode intended for power on/off buttons or position sensors in battery powered applications.

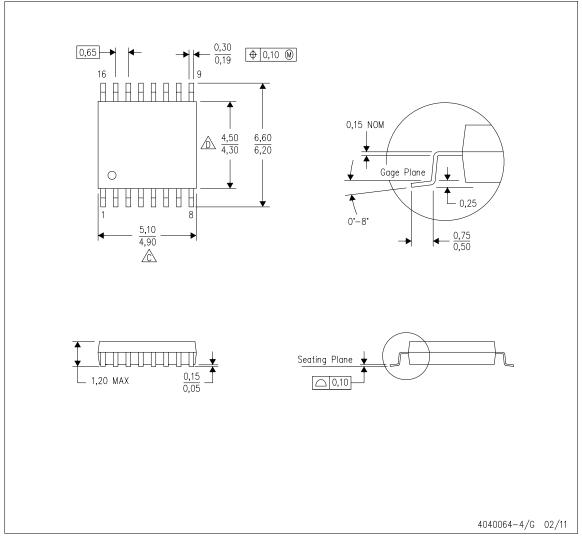

The LDC3114-Q1 is easily configured through an I<sup>2</sup>C interface. The LDC3114-Q1 is available in a 16-pin TSSOP package.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LDC3114-Q1  | TSSOP (16) | 5.00 mm × 4.40 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

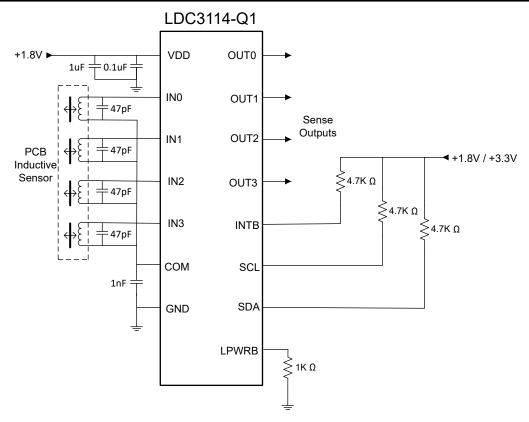

LDC3114-Q1 Simplified Schematic

# **Table of Contents**

| 1 Features                           | 1 | 7.4 Device Functional Modes                          | 14   |

|--------------------------------------|---|------------------------------------------------------|------|

| 2 Applications                       | 1 | 7.5 Register Maps                                    |      |

| 3 Description                        |   | 8 Application and Implementation                     |      |

| 4 Revision History                   |   | 8.1 Application Information                          |      |

| 5 Pin Configuration and Functions    |   | 8.2 Typical Application                              |      |

| 6 Specifications                     |   | 9 Power Supply Recommendations                       |      |

| 6.1 Absolute Maximum Ratings         |   | 10 Layout                                            |      |

| 6.2 ESD Ratings                      |   | 10.1 Layout Guidelines                               |      |

| 6.3 Recommended Operating Conditions |   | 10.2 Layout Example                                  |      |

| 6.4 Thermal Information              | 4 | 11 Device and Documentation Support                  | 52   |

| 6.5 Electrical Characteristics       | 4 | 11.1 Documentation Support                           |      |

| 6.6 Digital Interface                | 5 | 11.2 Receiving Notification of Documentation Updates |      |

| 6.7 I <sup>2</sup> C Interface       |   | 11.3 Support Resources                               | . 52 |

| 6.8 Timing Diagram                   |   | 11.4 Trademarks                                      |      |

| 6.9 Typical Characteristics          | 7 | 11.5 Electrostatic Discharge Caution                 | 52   |

| 7 Detailed Description               |   | 11.6 Glossary                                        | 52   |

| 7.1 Overview                         |   | 12 Mechanical, Packaging, and Orderable              |      |

| 7.2 Functional Block Diagram         |   | Information                                          | . 52 |

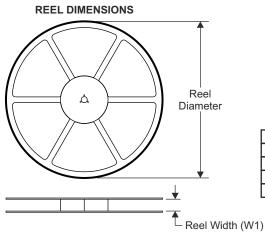

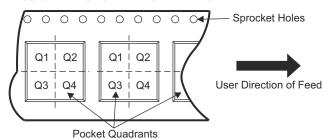

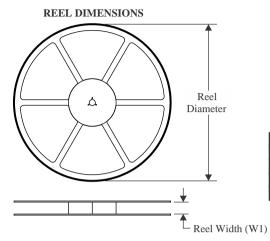

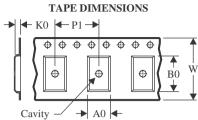

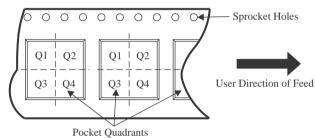

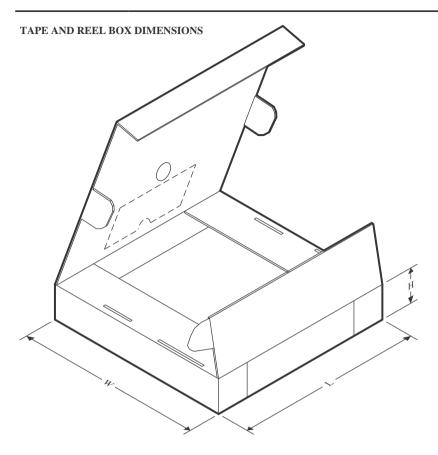

| 7.3 Feature Description              |   | 12.1 Tape and Reel Information                       |      |

| ·                                    |   | •                                                    |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (December 2021) to Revision B (December 2021)                        | Page             |

|----------------------------------------------------------------------------------------------|------------------|

| Changed the MSBs and LSBs of the four raw data output registers                              | 15               |

| Changes from Revision * (April 2021) to Revision A (December 2021)                           | Page             |

| Changed data sheet status from: Advanced Information to: Production Data                     | 1                |

| Updated 4-ch normal mode high-temp max current limit                                         | 4                |

| Updated 2-ch normal mode high-temp max current limit                                         | 4                |

| Updated low-power mode max current limit                                                     | 4                |

| Updated supply current normal power and standby mode curves                                  |                  |

| Corrected typo for data register address range from 0x05 to 0x09                             | 11               |

| · Changed table title "Button Scan Rate" to "Scan Rate" to make name generic for either butt | on or raw data   |

| mode                                                                                         |                  |

| • Removed "button" where appropriate to clarify the difference between "button scan rate" an | d "raw data scan |

| rate" text                                                                                   | 40               |

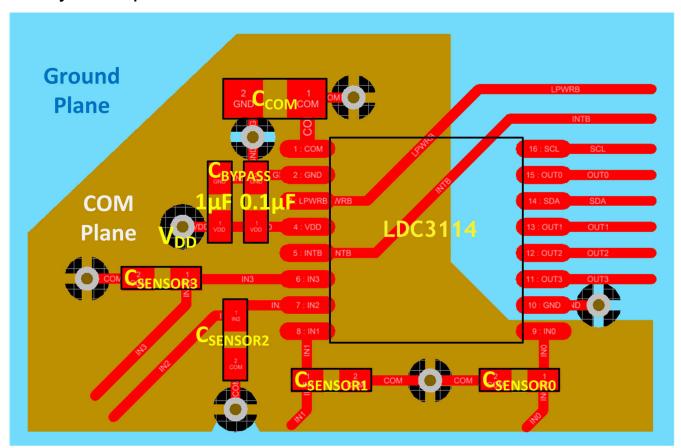

| Corrected PCB layout Figure 10-1 to have correct device name "LDC3114"                       |                  |

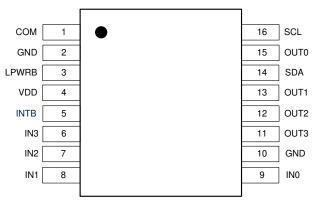

# **5 Pin Configuration and Functions**

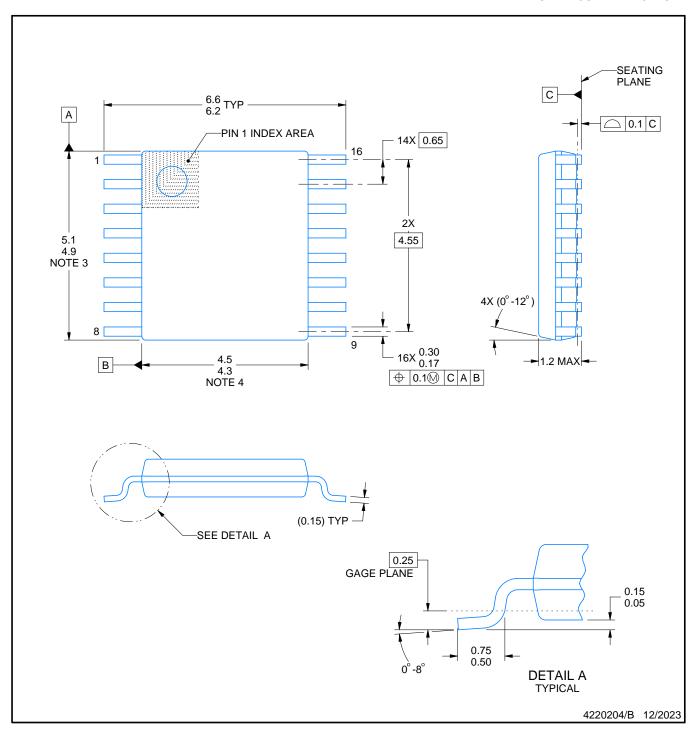

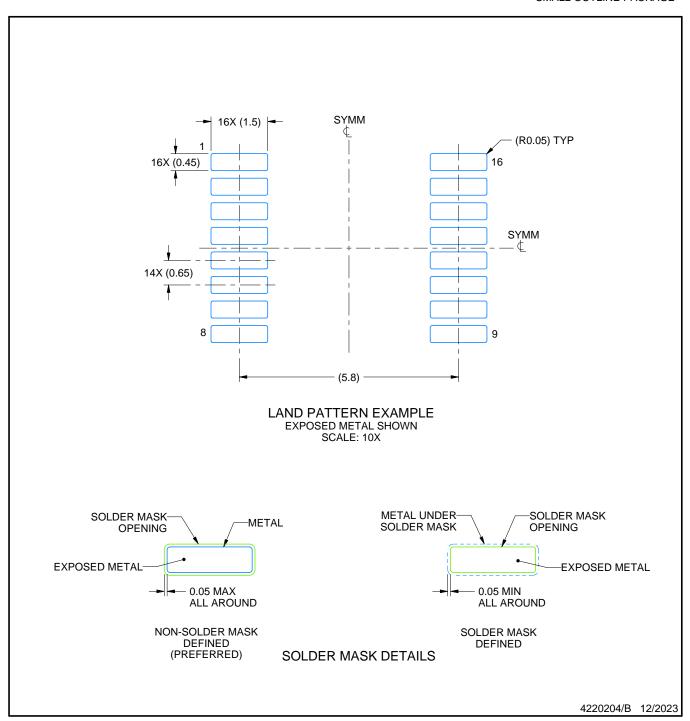

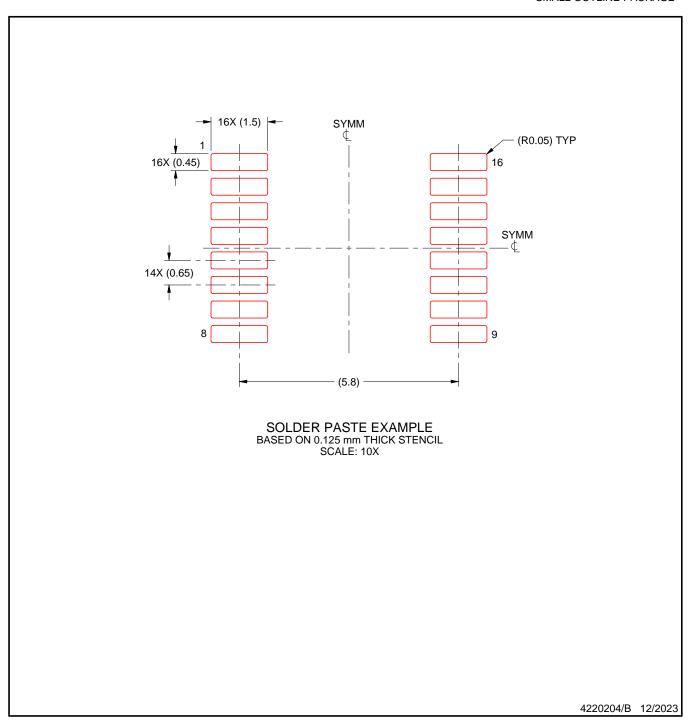

Figure 5-1. LDC3114-Q1 PW Package 16-Pin TSSOP Top View

Table 5-1. Pin Functions

|       | PIN | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                       |

|-------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME  | NO. | 1/0(*/             | DESCRIPTION                                                                                                                                       |

| VDD   | 4   | Р                  | Power supply                                                                                                                                      |

| GND   | 2   | G                  | Ground <sup>(2)</sup>                                                                                                                             |

| GND   | 10  |                    | Glound                                                                                                                                            |

| INTB  | 5   | 0                  | Interrupt output Polarity can be configured in Register 0x11.                                                                                     |

| LPWRB | 3   | I                  | Normal / Low Power Mode select<br>Set LPWRB to V <sub>DD</sub> for Normal Power Mode or ground for Low Power Mode.                                |

| СОМ   | 1   | А                  | Common return current path for all LC resonator sensors A capacitor should be connected from this pin to GND. Refer to Setting COM Pin Capacitor. |

| IN0   | 9   | Α                  | Channel 0 LC sensor input                                                                                                                         |

| IN1   | 8   | Α                  | Channel 1 LC sensor input                                                                                                                         |

| IN2   | 7   | Α                  | Channel 2 LC sensor input                                                                                                                         |

| IN3   | 6   | Α                  | Channel 3 LC sensor input                                                                                                                         |

| OUT0  | 15  | 0                  | Channel 0 logic output Polarity can be configured in Register 0x1C.                                                                               |

| OUT1  | 13  | 0                  | Channel 1 logic output Polarity can be configured in Register 0x1C.                                                                               |

| OUT2  | 12  | 0                  | Channel 2 logic output Polarity can be configured in Register 0x1C.                                                                               |

| OUT3  | 11  | 0                  | Channel 3 logic output Polarity can be configured in Register 0x1C.                                                                               |

| SCL   | 16  | I                  | I <sup>2</sup> C clock                                                                                                                            |

| SDA   | 14  | I/O                | I <sup>2</sup> C data<br>I <sup>2</sup> C address = 0x2A.                                                                                         |

<sup>(1)</sup> I = Input, O = Output, P=Power, G=Ground, A=Analog

<sup>(2)</sup> Both pins should be connected to the system ground on the PCB.

### **6 Specifications**

### 6.1 Absolute Maximum Ratings

Over operating temperature range unless otherwise noted. (1)

|                  |                           | MIN  | MAX                | UNIT |

|------------------|---------------------------|------|--------------------|------|

| $V_{DD}$         | Supply voltage            |      | 2.2                | V    |

| V                | Voltage on SCL, SDA. INTB | -0.3 | 3.6                | V    |

| V <sub>I</sub>   | Voltage on any other pin  | -0.3 | 2.2 <sup>(2)</sup> | V    |

| TJ               | Junction temperature      | -40  | 135                | °C   |

| T <sub>STG</sub> | Storage temperature       | -65  | 125                | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |  |                                 |                               | VALUE | UNIT |

|--------------------|--|---------------------------------|-------------------------------|-------|------|

|                    |  | Human body model (HBM), per AEC | Q100-002 <sup>(1)</sup>       | ±2000 |      |

| V <sub>(ESD)</sub> |  | Charged device model (CDM), per | Corner pins (1, 8, 9, and 16) | ±750  | V    |

|                    |  | AEC Q100-011                    | Other pins                    | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

### **6.3 Recommended Operating Conditions**

Over operating temperature range unless otherwise noted.

|                |                     | MIN  | NOM | MAX  | UNIT |

|----------------|---------------------|------|-----|------|------|

| $V_{DD}$       | Supply voltage      | 1.71 |     | 1.89 | V    |

| T <sub>A</sub> | Ambient temperature | -40  |     | 125  | ů    |

#### **6.4 Thermal Information**

|                       |                                              | LDC3114-Q1 |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | TSSOP      | UNIT |

|                       |                                              | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 105.1      | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case (top) thermal resistance    | 40.3       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 50.2       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 3.6        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 49.6       | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

Over operating temperature range unless otherwise noted.

Over operating V<sub>DD</sub> range unless otherwise noted.

| PARAMETER |                | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |  |

|-----------|----------------|-----------------|------|-----|------|------|--|

| POWER     |                |                 |      |     |      |      |  |

| $V_{DD}$  | Supply voltage |                 | 1.71 | 1.8 | 1.89 | V    |  |

<sup>(2)</sup> Maximum voltage across any two pins (not including SCL or SDA) is  $V_{DD} + 0.3 \text{ V}$ .

Over operating temperature range unless otherwise noted.

Over operating V<sub>DD</sub> range unless otherwise noted.

|                          | PARAMETER                                                                                  | TEST CONDITIONS                                                                                                           | MIN                                                                                                                     | TYP   | MAX   | UNIT |

|--------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------|-------|------|

| 1                        | Normal power mode supply current (4 channels) <sup>(1)</sup> (2)                           | 4 channels, 40 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = $V_{DD}$<br>-40°C ≤ $T_A$ ≤ 125°C         |                                                                                                                         | 0.46  | 2     | mA   |

| I <sub>DDNP</sub>        | Normal power mode supply current (2 channels) <sup>(1)</sup> (2)                           | 2 channels, 40 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = $V_{DD}$<br>-40°C $\leq T_A \leq 125$ °C  |                                                                                                                         | 0.31  | 1     | mA   |

| I <sub>DDLP</sub>        | Low power mode supply current (1)                                                          | 1 channel, 1.25 SPS per channel,<br>1 ms sampling window per channel,<br>LPWRB = Ground<br>-40°C ≤ T <sub>A</sub> ≤ 125°C | 1 ms sampling window per channel, LPWRB = Ground $10$ 35 $-40^{\circ}\text{C} \le T_{\text{A}} \le 125^{\circ}\text{C}$ |       | μА    |      |

| I <sub>DDSB</sub>        | Standby supply current                                                                     | No button active (EN = 0x00) $-40^{\circ}\text{C} \le T_{A} \le 125^{\circ}\text{C}$ 7 22                                 |                                                                                                                         | μΑ    |       |      |

| SENSOR                   |                                                                                            |                                                                                                                           |                                                                                                                         |       |       |      |

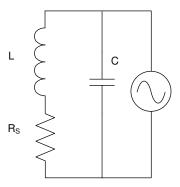

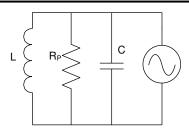

| I <sub>SENSOR, MAX</sub> | Maximum sensor current drive                                                               | Registers SENSOR <i>n</i> _CONFIG: RP <i>n</i> = 0 <sup>(3)</sup>                                                         |                                                                                                                         | 2.5   |       | mA   |

| R <sub>P, MIN</sub>      | Minimum sensor parallel resonant impedance                                                 |                                                                                                                           |                                                                                                                         | 350   |       | Ω    |

| R <sub>P, MAX</sub>      | Maximum sensor parallel resonant impedance                                                 |                                                                                                                           |                                                                                                                         | 10    |       | kΩ   |

| f <sub>SENSOR</sub>      | Sensor resonant frequency <sup>(4)</sup>                                                   |                                                                                                                           | 5                                                                                                                       |       | 30    | MHz  |

| Q <sub>SENSOR, MIN</sub> | Minimum sensor quality factor                                                              |                                                                                                                           |                                                                                                                         | 5     |       |      |

| Q <sub>SENSOR, MAX</sub> | Maximum sensor quality factor                                                              |                                                                                                                           |                                                                                                                         | 30    |       |      |

| V <sub>SENSOR, PP</sub>  | Sensor oscillation peak-to-peak voltage                                                    | Measured on the INn (3) pins with reference to COM.                                                                       |                                                                                                                         | 0.9   |       | V    |

| C <sub>IN</sub>          | Sensor input pin capacitance                                                               |                                                                                                                           |                                                                                                                         | 17    |       | pF   |

| CONVERTER                |                                                                                            |                                                                                                                           |                                                                                                                         |       |       |      |

| SR <sub>NP, MIN</sub>    | Minimum normal power mode scan rate <sup>(5)</sup>                                         | LPWRB = V <sub>DD</sub>                                                                                                   | 7                                                                                                                       | 10    | 13    | SPS  |

| SR <sub>NP, MAX</sub>    | Maximum normal power mode scan rate <sup>(5)</sup>                                         | LPWRB = V <sub>DD</sub>                                                                                                   | 56                                                                                                                      | 80    | 104   | SPS  |

| SR <sub>LP, MIN</sub>    | Minimum low power mode scan rate <sup>(5)</sup>                                            | LPWRB = Ground                                                                                                            | 0.438                                                                                                                   | 0.625 | 0.813 | SPS  |

| SR <sub>LP, MAX</sub>    | Maximum low power mode scan rate <sup>(5)</sup>                                            | LPWRB = Ground                                                                                                            | 3.5                                                                                                                     | 5     | 6.5   | SPS  |

| f <sub>REF_CLK</sub>     | Internal Reference clock frequency                                                         | T <sub>A</sub> =25°C                                                                                                      |                                                                                                                         | 44    |       | MHz  |

| f <sub>REF_CLK_TC</sub>  | Internal Reference clock frequency variation from T <sub>A</sub> =25°C to over temperature | -40°C ≤ T <sub>A</sub> ≤ 125°C                                                                                            |                                                                                                                         | 3     |       | %    |

- (1) Sensor configuration:  $L_{SENSOR}$  = 0.85  $\mu$ H,  $C_{SENSOR}$  = 58 pF,  $Q_{SENSOR}$  = 11,  $R_P$  = 0.7  $k\Omega$ .

- (2) I<sup>2</sup>C communication and pull-up resistors current is not included.

- (3) The italic n is the channel index, n = 0, 1, 2, or 3 for LDC3114.

- (4) For optimal performance, configure the sensor frequency to be greater than 3 MHz

- (5) For typical distribution of the scan rates, refer to Figure 6-9.

### 6.6 Digital Interface

Over operating temperature range unless otherwise noted. Pins: LPWRB, INT\_DR, OUT0, OUT1, OUT2, OUT3, and ADDR.

|                 | PARAMETER                     | TEST CONDITIONS | MIN                   | TYP MAX              | UNIT |  |  |  |  |  |

|-----------------|-------------------------------|-----------------|-----------------------|----------------------|------|--|--|--|--|--|

| VOLTAGE LE      | VOLTAGE LEVELS                |                 |                       |                      |      |  |  |  |  |  |

| V <sub>IH</sub> | Input high voltage, LPWRB pin |                 | 0.8 × V <sub>DD</sub> |                      | V    |  |  |  |  |  |

| V <sub>IL</sub> | Input low voltage, LPWRB pin  |                 |                       | 0.2 × V <sub>D</sub> | ) V  |  |  |  |  |  |

Over operating temperature range unless otherwise noted. Pins: LPWRB, INT\_DR, OUT0, OUT1, OUT2, OUT3, and ADDR.

| PARAMETER            |                                | TEST CONDITIONS              | MIN                 | TYP MAX               | UNIT |

|----------------------|--------------------------------|------------------------------|---------------------|-----------------------|------|

| V <sub>OH</sub>      | Output high voltage, OUTx pins | I <sub>SOURCE</sub> = 400 μA | $0.8 \times V_{DD}$ |                       | V    |

| V <sub>OL</sub>      | Output low voltage, OUTx pins  | I <sub>SINK</sub> = 400 μA   |                     | 0.2 × V <sub>DD</sub> | V    |

| IL                   | Digital input leakage current  |                              | -500                | 500                   | nA   |

| V <sub>OL_INTB</sub> | Output low voltage, INTB pin   | 3 mA sink current            |                     | 0.4                   | V    |

### 6.7 I<sup>2</sup>C Interface

|                         |                                                                                  |                                                        | MIN                    | TYP MAX               | UNIT |

|-------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|-----------------------|------|

| VOLTAGE                 | LEVELS                                                                           |                                                        |                        |                       |      |

| V <sub>IH_I2C</sub>     | Input high voltage                                                               |                                                        | 0.7 × V <sub>DD</sub>  |                       | V    |

| V <sub>IL_I2C</sub>     | Input low voltage                                                                |                                                        |                        | 0.3 × V <sub>DD</sub> | V    |

| V <sub>OL_I2C</sub>     | Output low voltage                                                               | 3 mA sink current                                      |                        | 0.2 × V <sub>DD</sub> | V    |

| HYS <sub>I2C</sub>      | Hysteresis                                                                       |                                                        | 0.05 × V <sub>DD</sub> |                       | V    |

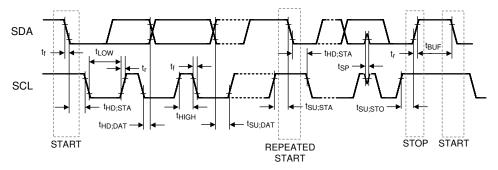

| I <sup>2</sup> C TIMINO | CHARACTERISTICS                                                                  |                                                        |                        |                       |      |

| f <sub>SCL</sub>        | Clock frequency                                                                  |                                                        |                        | 400                   | kHz  |

| t <sub>LOW</sub>        | Clock low time                                                                   |                                                        | 1.3                    |                       | μs   |

| t <sub>HIGH</sub>       | Clock high time                                                                  |                                                        | 0.6                    |                       | μs   |

| t <sub>HD;STA</sub>     | Hold time repeated START condition                                               | After this period, the first clock pulse is generated. | 0.6                    |                       | μs   |

| t <sub>SU;STA</sub>     | Set-up time for a repeated START condition                                       |                                                        | 0.6                    |                       | μs   |

| t <sub>HD;DAT</sub>     | Data hold time                                                                   |                                                        | 0                      |                       | μs   |

| t <sub>SU;DAT</sub>     | Data set-up time                                                                 |                                                        | 100                    |                       | ns   |

| t <sub>SU;STO</sub>     | Set-up time for STOP condition                                                   |                                                        | 0.6                    |                       | μs   |

| t <sub>BUF</sub>        | Bus free time between a STOP and START condition                                 |                                                        | 1.3                    |                       | μs   |

| t <sub>VD;DAT</sub>     | Data valid time                                                                  |                                                        |                        | 0.9                   | μs   |

| t <sub>VD;ACK</sub>     | Data valid acknowledge time                                                      |                                                        |                        | 0.9                   | μs   |

| t <sub>SP</sub>         | Pulse width of spikes that must be suppressed by the input filter <sup>(1)</sup> |                                                        |                        | 50                    | ns   |

(1) This parameter is specified by design and/or characterization and is not tested in production.

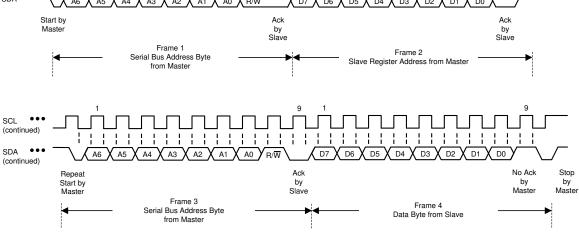

## **6.8 Timing Diagram**

Figure 6-1. I<sup>2</sup>C Timing Diagram

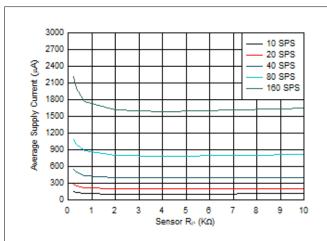

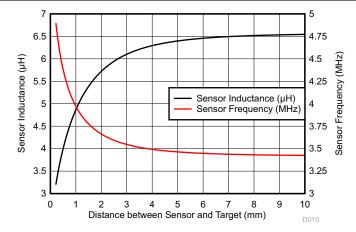

### 6.9 Typical Characteristics

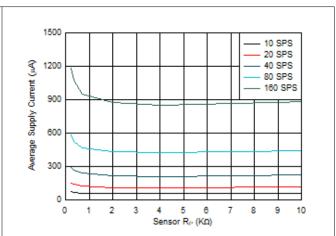

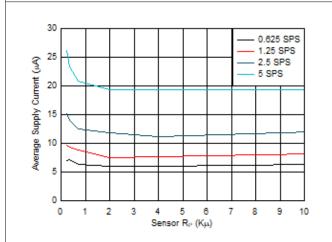

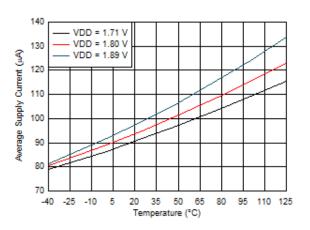

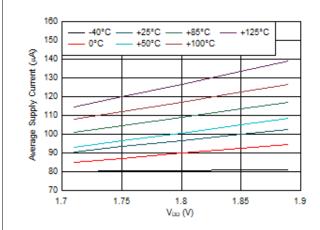

Over recommended operating conditions unless specified otherwise.  $V_{DD}$  = 1.8 V,  $T_{J}$  = 25°C. One channel enabled with a button sampling window of 1 ms unless specified otherwise.

Figure 6-2. Supply Current vs Sensor  $R_P$  for Normal Power Mode. Sensor Frequency = 10 MHz. Sampling Window = 2mS. Four Channels Enabled.

Figure 6-3. Supply Current vs Sensor  $R_P$  for Normal Power Mode. Sensor Frequency = 10 MHz. Sampling Window = 2mS. Two Channels Enabled.

Figure 6-4. Supply Current vs Sensor  $R_P$  for Low Power Mode. Sensor Frequency = 10 MHz.

Figure 6-5. Supply Current vs Temperature. Sensor  $R_P$  = 720  $\Omega$ , Scan Rate = 40 SPS, Sensor Frequency = 20 MHz.

Figure 6-6. Supply Current vs.  $V_{DD}$ . Sensor  $R_P$  = 720  $\Omega$ , Scan Rate = 40 SPS, Sensor Frequency = 20 MHz.

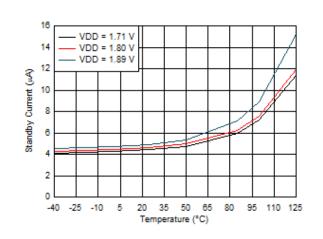

Figure 6-7. Standby Current vs. Temperature

## **6.9 Typical Characteristics (continued)**

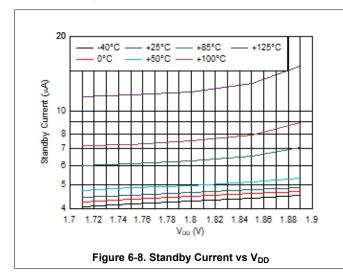

Over recommended operating conditions unless specified otherwise.  $V_{DD}$  = 1.8 V,  $T_{J}$  = 25°C. One channel enabled with a button sampling window of 1 ms unless specified otherwise.

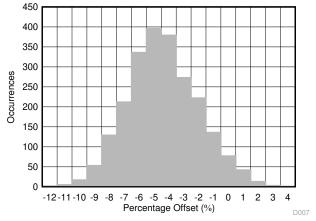

Figure 6-9. Scan Rate Distribution at 30°C

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

### 7 Detailed Description

#### 7.1 Overview

The LDC3114-Q1 is a hybrid multichannel, low-noise, high-resolution inductance-to-digital converter (LDC) optimized for inductive touch applications as well as linear position sensing. Button presses form micro-deflections in the conductive targets which cause frequency shifts in the resonant sensors. The LDC3114-Q1 can measure such frequency shifts and determine when button presses occur. With adjustable sensitivity per input channel, the LDC3114-Q1 can reliably operate with a wide range of physical button structures and materials. The high resolution measurement enables the implementation of force level buttons. The LDC3114-Q1 incorporates customizable post-processing algorithms for enhanced robustness.

The LDC3114-Q1 additionally implements a raw data access mode. The MCU can read directly the data representing the effective inductance of the sensor and implement further post processing. In this mode, additional post processing features such as baseline tracking and algorithms for false button detection are ignored. This mode is useful for linear or rotary position sensing with inductive sensors while having excellent EMI performance across wide range of applications. This mode can also be used to measure the micro-deflection for button-like applications as well.

The LDC3114-Q1 can operate in an ultra-low power mode for optimal battery life, or can be toggled into a higher scan rate for more responsive button press detection for game play or other low latency applications. The LDC3114-Q1 is operational from  $-40^{\circ}$ C to  $+125^{\circ}$ C with a 1.8 V  $\pm$  5% power supply voltage.

The LDC3114-Q1 is configured through 400-kHz I<sup>2</sup>C. Button presses can be reported through the I<sup>2</sup>C interface or with configurable polarity dedicated push-pull outputs. Besides the LC resonant sensors, the only external components necessary for operation are supply bypassing capacitors and a COM pin capacitor to ground.

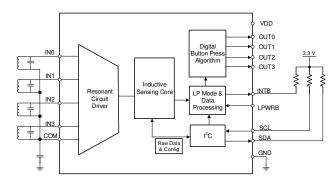

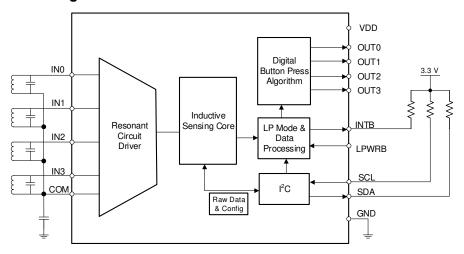

#### 7.2 Functional Block Diagram

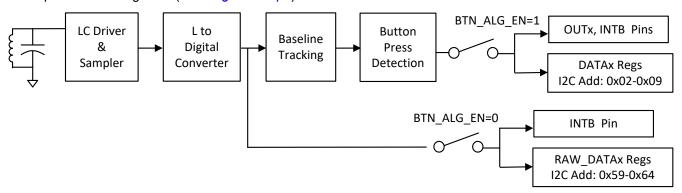

Figure 7-1. Block Diagram of LDC3114-Q1

#### 7.3 Feature Description

#### 7.3.1 Multimode Operation

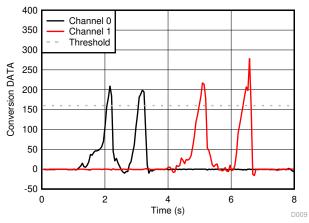

LDC3114-Q1 offers two main modes of operations: raw data access mode and button algorithm mode which is controlled by the *BTN\_ALG\_EN* field in *Register INTPOL Address 0x11*. Figure 7-2 shows conceptually how these two modes are implemented.

Raw data access mode allows an external MCU to extract data from the signal after the inductance-to-digital converter from registers through  $I^2C$  (see *Raw Data Output*). There is no further processing on this raw data such as baseline tracking, integrated button algorithms and button thresholding. This mode gives MCU full control over the measured raw data to implement algorithms for linear position sensing, rotational encoder applications, metal presence/deflection applications, smart button algorithms and for multimodal sensor fusion applications.

The second mode is button algorithm mode. Here further processing with parameters defined by the user (see *Baseline Tracking* and *Integrated Button Algorithms*) is done on the data and a button thresholding as defined by the user is applied. The processed data are available in separate registers to be read by I<sup>2</sup>C and any button press detection is indicated on the OUTx pins (see *Button Output Interfaces*) This mode is used to implement button press functionality and can also be used to implement the measurement of force applied for button press along with detection to implement multilevel button press.

For register settings that are applicable to button mode versus raw access data mode are clearly identified in the descriptions of the registers (see *Register Maps*).

Figure 7-2. Multimode Operation in LDC3114-Q1

### 7.3.2 Multichannel and Single-Channel Operation

The LDC3114-Q1 provides four independent sensing channels. In the following sections, some parameters, such as DATA*n* and SENSOR*n* CONFIG, contain a channel index *n*.

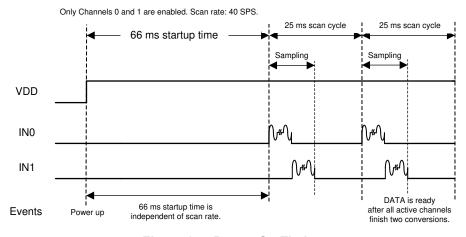

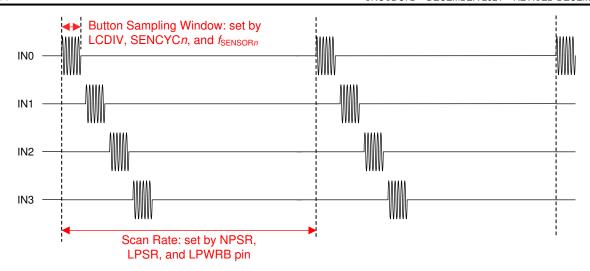

Any of the four channels available in the LDC3114-Q1 can be independently enabled by setting the ENn and LPENn (n = 0, 1, 2, or 3) bit fields in *Register EN* (*Address 0x0C*). The low-power-enable bit LPENn only takes effect if the corresponding ENn bit is also set. If only one channel is set active, the LDC3114-Q1 periodically samples the single active channel at the configured scan rate. When several channels are set active, the LDC3114-Q1 operates in multichannel mode, and the device sequentially samples the active channels at the configured scan rate. Each channel of the LDC3114-Q1 can be independently enabled in Low Power Mode and Normal Power Mode.

#### 7.3.3 Raw Data Output

Raw data mode is enabled by setting BTN\_ALG\_EN=0x0 field in Register INTPOL Address 0x11. Figure 7-2 shows that this operation will extract data directly from the output of the inductance-to-digital converter.

The data is read from the  $I^2C$  interface of the LDC3114-Q1. The *DATA\_RDY* field in *Register OUT (Address 0x01)* indicates when new data is available for reading. In the raw data mode, the INTB pin also assserted when new data is available and can be used by the MCU as an interrupt. The raw data can be extracted by reading, the output RAW\_DATA $n_x$  registers (n = 0, 1, 2, or 3, for each channel, x = 1, 2, or 3 splitting 24-bit data over 3 8-bit register fields). Equation 1 shows the relationship between 24-bit data and the sensor frequency.

$$f_{SENSOR} = \frac{30 \times W \times f_{REF\_CLK}}{raw\_data}$$

(1)

#### where:

- $f_{sensor}$  is the instantaneous frequency of the inductive sensor

- f<sub>REF CLK</sub> is the internal reference clock frequency as specified in *Electrical Characteristics*

- raw\_data is the decimal representation of 24-bit binary data read from the RAW\_DATAn\_x for a particular channel

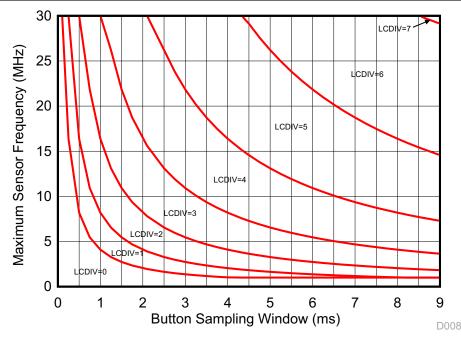

- W calculated in Equation 2 (see Programming Button or Raw Data Sampling Window for details):

$$W = 128 \times (1 + SENCYn) \times 2^{LCDIV}$$

(2)

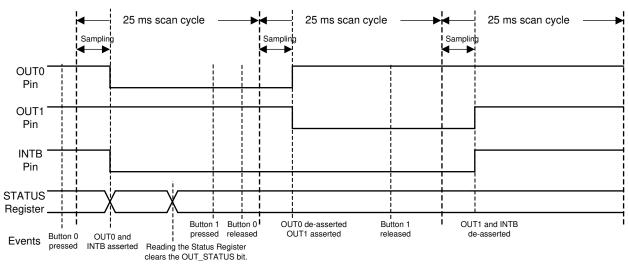

#### 7.3.4 Button Output Interfaces

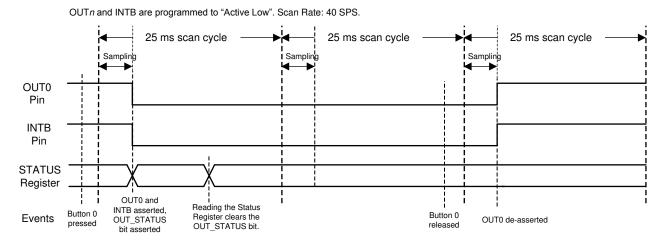

Button events may be reported by using two methods. The first method is to monitor the OUTn pins (n = 0, 1, 2, or 3), which are push-pull outputs and can be used as interrupts to a microcontroller. The polarities of these pins are programmable through  $Register\ OPOL\_DPOL\ (Address\ 0x1C)$ . Any button press or error condition is also reported by the open-drain pin, INTB. The INTB pin polarity is configurable through  $Register\ INTPOL\ (Address\ 0x11)$ . Any assertion of INTB is cleared upon reading  $Register\ STATUS\ (Address\ 0x00)$ . Each push-pull output must be assigned to a dedicated general-purpose input pin on the microcontroller to avoid potential current fights.

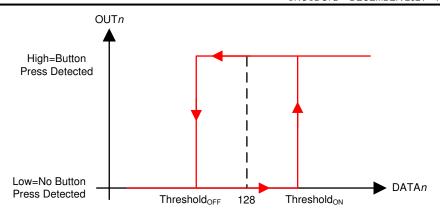

The second method is through the  $I^2C$  interface. The *Register OUT* (*Address 0x01*) contains the fields OUT0, OUT1, OUT2, and OUT3, which indicate when a button press has been detected. For more advanced button press measurements, the output DATA*n* registers (n = 0, 1, 2, or 3, *Register DATA0\_LSB - Address 0x02*), which are 12-bit two's complements, can be retrieved for all active buttons, and processed on a microcontroller. A valid button push is represented by a positive value. The polarity is configurable in *Register OPOL\_DPOL* (*Address 0x1C*). The DATA*n* values can be used to implement multilevel buttons, where the data value is correlated to the amount of force applied to the button.

#### 7.3.5 Programmable Button Sensitivity

The GAIN*n* registers (Addresses *0x0E*, *0x10*, *0x12*, and *0x14*) enable sensitivity enhancement of individual buttons to ensure consistent behavior of different mechanical structures. The sensitivity has a 64-level gain factor for a normalized gain between 1 and 232. Each gain step increases the gain by an average of 9%.

The gain required for an application is primarily determined by the mechanical rigidity of each individual button. The individual gain steps are listed in the *Gain Table*.

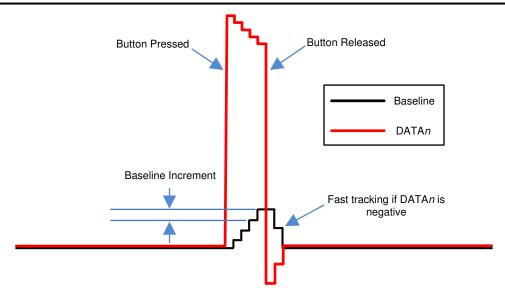

#### 7.3.6 Baseline Tracking

The LDC3114-Q1 incorporates a baseline tracking algorithm to automatically compensate for any slow change in the sensor output caused by environmental variations, such as temperature drift. The baseline tracking is configured independently for Normal Power Mode and Low Power Mode. For more information, refer to *Tracking Baseline*.

#### Note

The baseline tracking feature is applicable only for button algorithm functionality and cannot be bypassed. To disable baseline tracking, LDC3114-Q1 must be used in raw data access mode. See *Multimode Operation* for details.

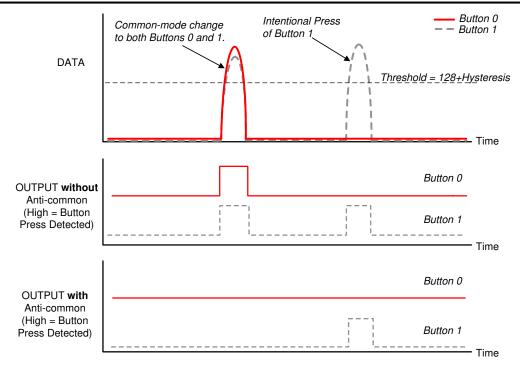

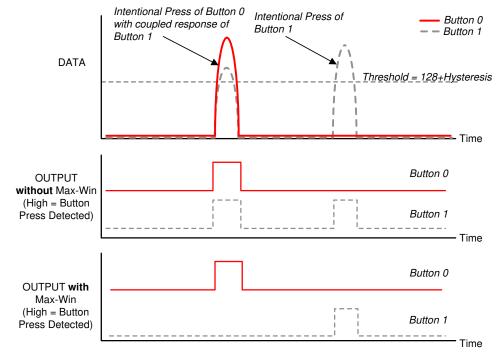

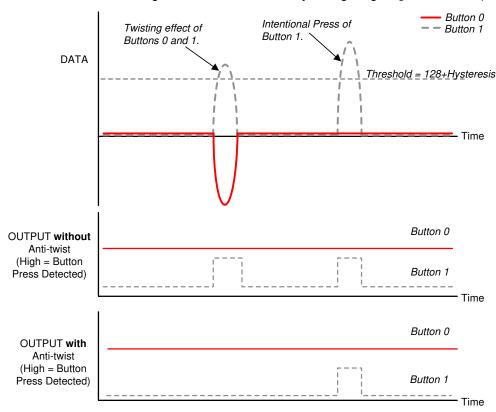

#### 7.3.7 Integrated Button Algorithms

The LDC3114-Q1 features several algorithms that can mitigate false button detections due to mechanical non-idealities. The algorithms look for correlated button responses, such as similar or opposite responses between two neighboring buttons, to determine if there is any undesirable mechanical crosstalk. For more information, refer to *Mitigating False Button Detections*.

#### 7.3.8 I<sup>2</sup>C Interface

The LDC3114-Q1 features an  $I^2C$  Interface that can be used to program the internal registers and read channel data. Before reading the OUT (Address 0x01) or channel DATAn (n = 0, 1, 2 or 3, Addresses 0x02 through 0x09) registers for button press data or raw channel data, RAW\_DATAn\_x (n = 0, 1, 2, or 3, for each channel, x= 1, 2, or 3 splitting 24-bit data over 3 8-bit register fields), the user should always read *Register STATUS* (*Address 0x00*) first to lock the data. The LDC3114-Q1 supports burst mode with auto-incrementing register addresses. The LDC3114-Q1 has a fixed  $I^2C$  address of 0x2A.

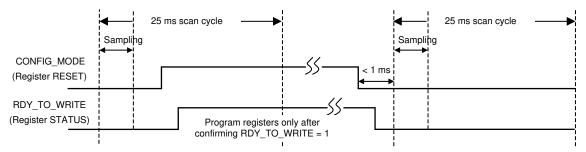

For the write sequence, there is a special handshake process that has to take place to ensure data integrity. The sequence of register writes is:

Set CONFIG MODE (Register RESET, Address 0x0A) bit = 1 to start the register write session.

- Poll for RDY\_TO\_WRITE (Register STATUS, Address 0x00) bit = 1.

- Perform I<sup>2</sup>C write to configure registers.

- Set CONFIG\_MODE (Register RESET, Address 0x0A) bit = 0 to terminate the register write session.

After CONFIG\_MODE is de-asserted, the new scan cycle will start in less than 1 ms. Figure 7-3 shows the waveform of the above process.

Figure 7-3. Timing Diagram Representing the States of the CONFIG\_MODE and RDY\_TO\_WRITE Bits for an I<sup>2</sup>C Write Handshake

#### **Note**

The I<sup>2</sup>C interface pin, the SDA, the SCL, and the INTB pins are all open-drain and 3.3-V compatible. These pins can be used to connect to an MCU which is supplied by 3.3-V supply without requiring voltage level translation between LDC3114-Q1 and the MCU.

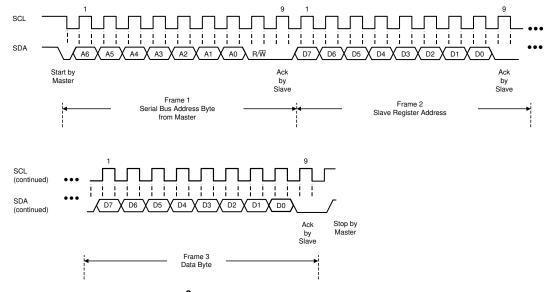

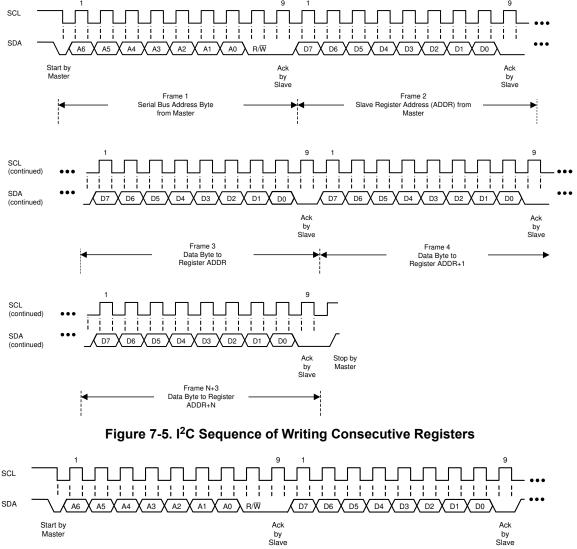

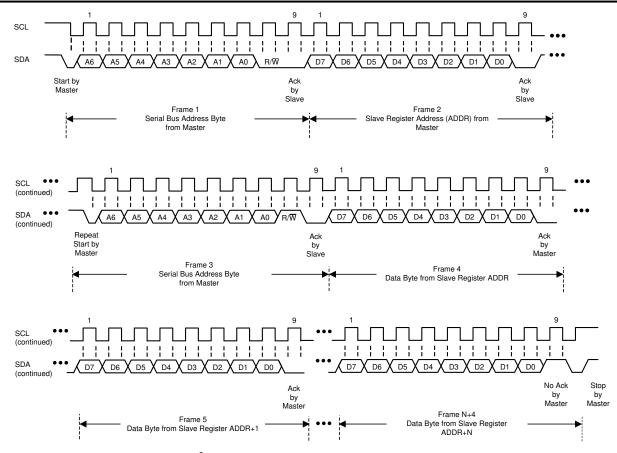

#### 7.3.8.1 I<sup>2</sup>C Interface Specifications

The maximum speed of the I<sup>2</sup>C interface is 400 kHz. This sequence uses the standard I<sup>2</sup>C 7-bit target address followed by an 8-bit pointer to set the register address. For both write and read, the address pointer will auto-increment as long as the controller acknowledges.

Figure 7-4. I<sup>2</sup>C Sequence of Writing a Single Register

Figure 7-6. I<sup>2</sup>C Sequence of Reading a Single Register

Figure 7-7. I<sup>2</sup>C Sequence of Reading Consecutive Registers

#### 7.3.8.2 I<sup>2</sup>C Bus Control

The LDC3114-Q1 cannot drive the I<sup>2</sup>C clock (SCL), that is the device does not support clock stretching. In the unlikely event where the SCL is stuck LOW, power cycle any device that is holding the SCL to activate its internal Power-On Reset (POR) circuit. If the LDC is connected to the same power supply as that device, there will be about 66-ms setup time before the LDC becomes active again. For more information, refer to *Defining Power-On Timing*. If the data line (SDA) is stuck LOW, the I<sup>2</sup>C controller should send nine clock pulses. The device that is holding the bus LOW should release the bus sometime within those nine clocks. If not, then power cycle to clear the bus.

The LDC3114-Q1 has built-in monitors to check that the device is currently working. In the unlikely event of a device fault, the device state will be reset internally, and all the registers will be reset with default settings. For system robustness, TI recommends to check the value of a modified register periodically to monitor the device status and reload the register settings, if needed.

#### 7.4 Device Functional Modes

The LDC3114-Q1 supports two power modes of operation: a Normal Power Mode for active sampling at 10, 20, 40, or 80 SPS, and a Low Power Mode for reduced current consumption at 0.625, 1.25, 2.5, or 5 SPS. The device can also be configured in Normal Power Mode for additional faster sampling rate of 160 SPS or for a continuous sampling rate. Refer to *Configuring Button or Raw Data Scan Rate* for details.

#### 7.4.1 Normal Power Mode

When the LPWRB input pin is set to  $V_{DD}$ , all enabled channels operate in Normal Power Mode. Each channel can be enabled independently through *Register EN (Address 0x0C)*. For the electrical specification of Normal Power Mode Scan Rate, refer to the *Electrical Characteristics* table.

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

#### 7.4.2 Low Power Mode

When the LPWRB input pin is set to ground, only the low-power-enabled channels are active. Each channel can be enabled independently to operate in Low Power Mode through *Register EN (Address 0x0C)*. For a channel to operate in the Low Power Mode, both the LPEN*n* and EN*n* bits (*n* is the channel index) must be set to 1. The Low Power Mode allows for energy-saving monitoring of button activity. In this mode, the device is in an inactive power-saving state for the majority of the time. Lower scan rates correspond to lower current consumption. In addition, the individual button sampling window should be set to the lowest effective setting (this is system dependent, but typically 0.8 ms to 1 ms). For the electrical specification of the configurable Low Power Mode Scan Rate, refer to the *Electrical Characteristics* table.

If a channel is operational in both Low Power Mode and Normal Power Mode, TI recommends to toggle the LPWRB pin only after the button associated with that channel is released.

The Low Power Mode is also applicable for raw data access mode.

### 7.4.3 Configuration Mode

Before configuring any register settings, the device must be put into the configuration mode first. Setting CONFIG\_MODE = 1 through *Register RESET (Address 0x0A)* stops data conversion and holds the device in configuration mode. Any device configuration changes can then be made. The current consumption in this mode is typically 0.3 mA. After all changes have been written, set CONFIG\_MODE = 0 for normal operation. Refer to  $I^2C$  Interface for more information.

#### 7.5 Register Maps

#### 7.5.1 LDC3114 Registers

LDC3114 Registers lists the memory-mapped registers for the LDC3114 registers. All register offset addresses not listed in LDC3114 Registers should be considered as reserved locations and the register contents should not be modified.

Table 7-1. LDC3114 Registers

| Offset | Acronym      | Register Name                                                  | Section          |

|--------|--------------|----------------------------------------------------------------|------------------|

| 0h     | STATUS       | Device status                                                  | Section 7.5.1.1  |

| 1h     | OUT          | Channel output logic states                                    | Section 7.5.1.2  |

| 2h     | DATA0_LSB    | The lower 8 bits of the Button 0 data (Two's complement        | Section 7.5.1.3  |

| 3h     | DATA0_MSB    | The upper 4 bits of the Button 0 data (Two's complement)       | Section 7.5.1.4  |

| 4h     | DATA1_LSB    | The lower 8 bits of the Button 1 data (Two's complement)       | Section 7.5.1.5  |

| 5h     | DATA1_MSB    | The upper 4 bits of the Button 1 data (Two's complement)       | Section 7.5.1.6  |

| 6h     | DATA2_LSB    | The lower 8 bits of the Button 2 data (Two's complement)       | Section 7.5.1.7  |

| 7h     | DATA2_MSB    | The upper 4 bits of the Button 2 data (Two's complement)       | Section 7.5.1.8  |

| 8h     | DATA3_LSB    | The lower 8 bits of the Button 3 data (Two's complement)       | Section 7.5.1.9  |

| 9h     | DATA3_MSB    | The upper 4 bits of the Button 3 data (Two's complement)       | Section 7.5.1.10 |

| Ah     | RESET        | Reset device and register configurations                       | Section 7.5.1.11 |

| Ch     | EN           | Enable channels and low power modes                            | Section 7.5.1.12 |

| Dh     | NP_SCAN_RATE | Normal Power Mode scan rate                                    | Section 7.5.1.13 |

| Eh     | GAIN0        | Gain for Channel 0 sensitivity adjustment for button algorithm | Section 7.5.1.14 |

| Fh     | LP_SCAN_RATE | Low Power Mode scan rate                                       | Section 7.5.1.15 |

|        |              |                                                                |                  |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

Table 7-1. LDC3114 Registers (continued)

| Offset | Acronym             | Register Name                                                  | Section          |

|--------|---------------------|----------------------------------------------------------------|------------------|

| 10h    | GAIN1               | Gain for Channel 1 sensitivity adjustment for button algorithm | Section 7.5.1.16 |

| 11h    | INTPOL              | Interrupt polarity                                             | Section 7.5.1.17 |

| 12h    | GAIN2               | Gain for Channel 2 sensitivity adjustment for button algorithm | Section 7.5.1.18 |

| 13h    | LP_BASE_INC         | Low power base increment for button algorithm                  | Section 7.5.1.19 |

| 14h    | GAIN3               | Gain for Channel 3 sensitivity adjustment for button algorithm | Section 7.5.1.20 |

| 15h    | NP_BASE_INC         | Normal power base increment for button algorithm               | Section 7.5.1.21 |

| 16h    | BTPAUSE_MAXWIN      | Baseline tracking pause and Max-win for button algorithm       | Section 7.5.1.22 |

| 17h    | LC_DIVIDER          | LC oscillation frequency divider                               | Section 7.5.1.23 |

| 18h    | HYST                | Hysteresis for threshold for button algorithm                  | Section 7.5.1.24 |

| 19h    | TWIST               | Anti-twist for button algorithm                                | Section 7.5.1.25 |

| 1Ah    | COMMON_DEFORM       | Anti-common and anti-deformation for button algorithm          | Section 7.5.1.26 |

| 1Ch    | OPOL_DPOL           | Output polarity for button data and output                     | Section 7.5.1.27 |

| 1Eh    | CNTSC               | Counter scale                                                  | Section 7.5.1.28 |

| 20h    | SENSOR0_CONFIG      | Sensor 0 cycle count, frequency, RP range                      | Section 7.5.1.29 |

| 22h    | SENSOR1_CONFIG      | Sensor 1 cycle count, frequency, RP range                      | Section 7.5.1.30 |

| 24h    | SENSOR2_CONFIG      | Sensor 2 cycle count, frequency, RP range                      | Section 7.5.1.31 |

| 25h    | FTF0                | Sensor 0 fast tracking factor for button algorithm             | Section 7.5.1.32 |

| 26h    | SENSOR3_CONFIG      | Sensor3 cycle count, frequency, RP range                       | Section 7.5.1.33 |

| 28h    | FTF1_2              | Sensors 1 and 2 fast tracking factors for button algorithm     | Section 7.5.1.34 |

| 2Bh    | FTF3                | Sensor 3 fast tracking factor for button algorithm             | Section 7.5.1.35 |

| 59h    | RAW_DATA0_3         | Sensor 0 pre-processed raw data                                | Section 7.5.1.36 |

| 5Ah    | RAW_DATA0_2         | Sensor 0 pre-processed raw data                                | Section 7.5.1.37 |

| 5Bh    | RAW_DATA0_1         | Sensor 0 pre-processed raw data                                | Section 7.5.1.38 |

| 5Ch    | RAW_DATA1_3         | Sensor 1 pre-processed raw data                                | Section 7.5.1.39 |

| 5Dh    | RAW_DATA1_2         | Sensor 1 pre-processed raw data                                | Section 7.5.1.40 |

| 5Eh    | RAW_DATA1_1         | Sensor 1 pre-processed raw data                                | Section 7.5.1.41 |

| 5Fh    | RAW_DATA2_3         | Sensor 2 pre-processed raw data                                | Section 7.5.1.42 |

| 60h    | RAW_DATA2_2         | Sensor 2 pre-processed raw data                                | Section 7.5.1.43 |

| 61h    | RAW_DATA2_1         | Sensor 2 pre-processed raw data                                | Section 7.5.1.44 |

| 62h    | RAW_DATA3_3         | Sensor 3 pre-processed raw data                                | Section 7.5.1.45 |

| 63h    | RAW_DATA3_2         | Sensor 3 pre-processed raw data                                | Section 7.5.1.46 |

| 64h    | RAW_DATA3_1         | Sensor 3 pre-processed raw data                                | Section 7.5.1.47 |

| FCh    | MANUFACTURER_ID_LSB | Manufacturer ID lower byte                                     | Section 7.5.1.48 |

| FDh    | MANUFACTURER_ID_MSB | Manufacturer ID upper byte                                     | Section 7.5.1.49 |

| FEh    | DEVICE_ID_LSB       | Device ID lower byte                                           | Section 7.5.1.50 |

| FFh    | DEVICE_ID_MSB       | Device ID upper byte                                           | Section 7.5.1.51 |

Complex bit access types are encoded to fit into small table cells. LDC3114 Access Type Codes shows the codes that are used for access types in this section.

Table 7-2. LDC3114 Access Type Codes

| 145.6 : 2. 22 00 : 1 / 100000 : 3 po 00400 |                        |                                        |  |  |  |

|--------------------------------------------|------------------------|----------------------------------------|--|--|--|

| Access Type                                | Code                   | Description                            |  |  |  |

| Read Type                                  |                        |                                        |  |  |  |

| R                                          | R                      | Read                                   |  |  |  |

| Write Type                                 |                        |                                        |  |  |  |

| W                                          | W                      | Write                                  |  |  |  |

| Reset or Default                           | Reset or Default Value |                                        |  |  |  |

| -n                                         |                        | Value after reset or the default value |  |  |  |

# 7.5.1.1 STATUS Register (Offset = 0h) [Reset = 40h]

STATUS is shown in STATUS Register Field Descriptions.

Return to the LDC3114 Registers.

Device status

**Table 7-3. STATUS Register Field Descriptions**

| Bit | Field        | Туре | Reset | Description                                                                                                                                                                                                            |

|-----|--------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | OUT_STATUS   | R    | Oh    | Output Status Logic OR of output OUTx bits. This field is cleared by reading this register.                                                                                                                            |

| 6   | CHIP_READY   | R    | 1h    | Chip Ready Status  0h = Chip not ready after internal reset  1h = Chip ready after internal reset                                                                                                                      |

| 5   | RDY_TO_WRITE | R    | 0h    | Ready to Write Indicates if registers are ready to be written. See I2C Interface section for more information.  0h = Registers not ready 1h = Registers ready                                                          |

| 4   | MAXOUT       | R    | 0h    | Maximum Output Code Indicates if any channel button output data reaches the maximum value (+0x7FF or -0x800). Cleared by a read of the status register.  0h = No maximum output code 1h = Maximum output code          |

| 3   | FSM_WD       | R    | 0h    | Finite-State Machine Watchdog Error Reports an error has occurred and conversions have been halted. Cleared by a read of the status register. 0h = No error in finite-state machine 1h = Error in finite-state machine |

| 2   | LC_WD        | R    | 0h    | LC Sensor Watchdog Error Reports an error when any LC oscillator fails to start. Cleared by a read of the status register.  0h = No error in LC oscillator initialization  1h = Error in LC oscillator initialization  |

| 1   | TIMEOUT      | R    | Oh    | Button Timeout Reports when any button is asserted for more than 50 seconds. Cleared by a read of the status register. When DIS_BTN_TO is set, no timeout is asserted  0h = no timeout error  1h = timeout error       |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

**Table 7-3. STATUS Register Field Descriptions (continued)**

| Bit | Field         | Туре | Reset | Description                                                                                                                                                                                     |

|-----|---------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | REGISTER_FLAG | R    |       | Register Integrity Flag Reports if any register's value has an unexpected change. Cleared by a read of the status register.  0h = No unexpected register change 1h = Unexpected register change |

### 7.5.1.2 OUT Register (Offset = 1h) [Reset = 00h]

OUT is shown in OUT Register Field Descriptions.

Return to the LDC3114 Registers.

Channel output logic states

**Table 7-4. OUT Register Field Descriptions**

| Bit | Field    | Туре | Reset | Description Description                                                                                                                                |

|-----|----------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | RESERVED | R    | 0h    | Reserved                                                                                                                                               |

| 4   | DATA_RDY | R    | Oh    | Output Logic State for pre-processed data capture for any enabled channel. Bit cleared on read.  0h = Data Capture in progress 1h = New Data available |

| 3   | ОПТЗ     | R    | Oh    | Button output output Logic State for Channel 3 0h = No button press detected on Channel 3 1h = Button press detected on Channel 3                      |

| 2   | OUT2     | R    | Oh    | Button output Logic State for Channel 2 0h = No button press detected on Channel 2 1h = Button press detected on Channel 2                             |

| 1   | OUT1     | R    | Oh    | Button output Logic State for Channel 1 0h = No button press detected on Channel 1 1h = Button press detected on Channel 1                             |

| 0   | OUT0     | R    | Oh    | Button output Logic State for Channel 0 0h = No button press detected on Channel 0 1h = Button press detected on Channel 0.                            |

#### 7.5.1.3 DATA0\_LSB Register (Offset = 2h) [Reset = 00h]

DATA0\_LSB is shown in DATA0\_LSB Register Field Descriptions.

Return to the LDC3114 Registers.

The lower 8 bits of the Button 0 data (Two's complement

#### Table 7-5. DATA0\_LSB Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                   |

|-----|------------|------|-------|---------------------------------------------------------------|

| 7-0 | DATA0[7:0] | R    | 0h    | The lower 8 bits of Channel 0 button data (Two's complement). |

#### 7.5.1.4 DATA0\_MSB Register (Offset = 3h) [Reset = 00h]

DATA0\_MSB is shown in DATA0\_MSB Register Field Descriptions.

Return to the LDC3114 Registers.

The upper 4 bits of the Button 0 data (Two's complement)

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

Table 7-6. DATA0\_MSB Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                   |

|-----|-------------|------|-------|---------------------------------------------------------------|

| 7-4 | RESERVED    | R    | 0h    | Reserved                                                      |

| 3-0 | DATA0[11:8] | R    | 0h    | The upper 4 bits of Channel 0 button data (Two's complement). |

#### 7.5.1.5 DATA1 LSB Register (Offset = 4h) [Reset = 00h]

DATA1\_LSB is shown in DATA1\_LSB Register Field Descriptions.

Return to the LDC3114 Registers.

The lower 8 bits of the Button 1 data (Two's complement)

Table 7-7. DATA1\_LSB Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                   |

|-----|------------|------|-------|---------------------------------------------------------------|

| 7-0 | DATA1[7:0] | R    | 0h    | The lower 8 bits of Channel 1 button data (Two's complement). |

### 7.5.1.6 DATA1\_MSB Register (Offset = 5h) [Reset = 00h]

DATA1 MSB is shown in DATA1 MSB Register Field Descriptions.

Return to the LDC3114 Registers.

The upper 4 bits of the Button 1 data (Two's complement)

Table 7-8. DATA1\_MSB Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                   |

|-----|-------------|------|-------|---------------------------------------------------------------|

| 7-4 | RESERVED    | R    | 0h    | Reserved                                                      |

| 3-0 | DATA1[11:8] | R    | 0h    | The upper 4 bits of Channel 1 button data (Two's complement). |

### 7.5.1.7 DATA2\_LSB Register (Offset = 6h) [Reset = 00h]

DATA2\_LSB is shown in DATA2\_LSB Register Field Descriptions.

Return to the LDC3114 Registers.

The lower 8 bits of the Button 2 data (Two's complement)

Table 7-9. DATA2 LSB Register Field Descriptions

|     |            |      | _     | • • • • • • • • • • • • • • • • • • •                         |

|-----|------------|------|-------|---------------------------------------------------------------|

| Bit | Field      | Туре | Reset | Description                                                   |

| 7-0 | DATA2[7:0] | R    | 0h    | The lower 8 bits of Channel 2 button data (Two's complement). |

#### 7.5.1.8 DATA2\_MSB Register (Offset = 7h) [Reset = 00h]

DATA2\_MSB is shown in DATA2\_MSB Register Field Descriptions.

Return to the LDC3114 Registers.

The upper 4 bits of the Button 2 data (Two's complement)

#### Table 7-10. DATA2 MSB Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                   |

|-----|-------------|------|-------|---------------------------------------------------------------|

| 7-4 | RESERVED    | R    | 0h    | Reserved                                                      |

| 3-0 | DATA2[11:8] | R    | 0h    | The upper 4 bits of Channel 2 button data (Two's complement). |

Copyright © 2021 Texas Instruments Incorporated

### 7.5.1.9 DATA3\_LSB Register (Offset = 8h) [Reset = 00h]

DATA3\_LSB is shown in DATA3\_LSB Register Field Descriptions.

Return to the LDC3114 Registers.

The lower 8 bits of the Button 3 data (Two's complement)

### Table 7-11. DATA3\_LSB Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                   |

|-----|------------|------|-------|---------------------------------------------------------------|

| 7-0 | DATA3[7:0] | R    | 0h    | The lower 8 bits of Channel 3 button data (Two's complement). |

### 7.5.1.10 DATA3\_MSB Register (Offset = 9h) [Reset = 00h]

DATA3 MSB is shown in DATA3 MSB Register Field Descriptions.

Return to the LDC3114 Registers.

The upper 4 bits of the Button 3 data (Two's complement)

### Table 7-12. DATA3\_MSB Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                   |

|-----|-------------|------|-------|---------------------------------------------------------------|

| 7-4 | RESERVED    | R    | 0h    | Reserved                                                      |

| 3-0 | DATA3[11:8] | R    | 0h    | The upper 4 bits of Channel 3 button data (Two's complement). |

### 7.5.1.11 RESET Register (Offset = Ah) [Reset = 00h]

RESET is shown in RESET Register Field Descriptions.

Return to the LDC3114 Registers.

Reset device and register configurations

#### Table 7-13. RESET Register Field Descriptions

| Bit | Field       | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                    |

|-----|-------------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | RESERVED    | R/W  | 0h    | Reserved                                                                                                                                                                                                                                                                                                                       |

| 4   | FULL_RESET  | R/W  | Oh    | Device Reset  Oh = Normal operation  The Resets the device and register configurations. All registers will be returned to default values. Normal operation will not resume until STATUS:CHIP_READY = 1.                                                                                                                        |

| 3-1 | RESERVED    | R/W  | 0h    | Reserved                                                                                                                                                                                                                                                                                                                       |

| 0   | CONFIG_MODE | R/W  | Oh    | Configuration Mode Any device configuration changes should be made with this bit set to 1. After all configuration changes have been written, set this bit to 0 for normal operation.  Oh = Normal operation  1h = Holds the device in configuration mode (no data conversion), but maintains current register configurations. |

### 7.5.1.12 EN Register (Offset = Ch) [Reset = 1Fh]

EN is shown in EN Register Field Descriptions.

Return to the LDC3114 Registers.

Enable channels and low power modes

| Table 7-14. EN Register Field Descriptions |       |      |       |                                                                                                                                            |  |  |  |  |

|--------------------------------------------|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit                                        | Field | Туре | Reset | Description                                                                                                                                |  |  |  |  |

| 7                                          | LPEN3 | R/W  | 0h    | Channel 3 Low-Power-Enable  0h = Disable Channel 3 in Low Power Mode  1h = Enable Channel 3 in Low Power Mode. EN3 must also be set to  1. |  |  |  |  |

| 6                                          | LPEN2 | R/W  | 0h    | Channel 2 Low-Power-Enable 0h = Disable Channel 2 in Low Power Mode 1h = Enable Channel 2 in Low Power Mode. EN2 must also be set to 1.    |  |  |  |  |

| 5                                          | LPEN1 | R/W  | 0h    | Channel 1 Low-Power-Enable  Oh = Disable Channel 1 in Low Power Mode  1h = Enable Channel 1 in Low Power Mode. EN1 must also be set to  1. |  |  |  |  |

| 4                                          | LPEN0 | R/W  | 1h    | Channel 0 Low-Power-Enable 0h = Disable Channel 0 in Low Power Mode 1h = Enable Channel 0 in Low Power Mode. EN0 must also be set to 1.    |  |  |  |  |

| 3                                          | EN3   | R/W  | 1h    | Channel 3 Enable  0h = Disable Channel 2  1h = Enable Channel 2                                                                            |  |  |  |  |

| 2                                          | EN2   | R/W  | 1h    | Channel 2 Enable  0h = Disable Channel 2  1h = Enable Channel 2                                                                            |  |  |  |  |

| 1                                          | EN1   | R/W  | 1h    | Channel 1 Enable 0h = Disable Channel 1 1h = Enable Channel 1                                                                              |  |  |  |  |

| 0                                          | EN0   | R/W  | 1h    | Channel 0 Enable 0h = Disable Channel 0 1h = Enable Channel 0                                                                              |  |  |  |  |

## 7.5.1.13 NP\_SCAN\_RATE Register (Offset = Dh) [Reset = 01h]

NP\_SCAN\_RATE is shown in NP\_SCAN\_RATE Register Field Descriptions.

Return to the LDC3114 Registers.

Normal Power Mode scan rate

Table 7-15. NP\_SCAN\_RATE Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                                                                                                                                                                                                         |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 | RESERVED | R/W  | 0h    | Reserved                                                                                                                                                                                                                                                                            |

| 3   | NPFSR    | R/W  | 0h    | Normal Power Mode Fast Scan Rate of 160SPS. When set, this bit will override setting in NPSR only and not NPCS.                                                                                                                                                                     |

| 2   | NPCS     | R/W  | 0h    | Continuous key scan in Normal Power mode When set, the scan cycle is continuous without delay in the Normal Power mode. The base increment value is fixed. This bit has no effect if the chip is in Low Power mode. This bit will override the setting in NPSR and NPFSR registers. |

### Table 7-15. NP\_SCAN\_RATE Register Field Descriptions (continued)

| Bit | Field | Туре | Reset | Description                                                                                                                                               |

|-----|-------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0 | NPSR  | R/W  | 1h    | Normal Power Mode Scan Rate Refer to Configuring Button Scan Rate section for more information. 0h = 80 SPS 1h = 40 SPS (Default) 2h = 20 SPS 3h = 10 SPS |

### 7.5.1.14 GAIN0 Register (Offset = Eh) [Reset = 28h]

GAIN0 is shown in GAIN0 Register Field Descriptions.

Return to the LDC3114 Registers.

Gain for Channel 0 sensitivity adjustment for button algorithm

## Table 7-16. GAIN0 Register Field Descriptions

| Bit | it | Field    | Туре | Reset | Description                                                                            |

|-----|----|----------|------|-------|----------------------------------------------------------------------------------------|

| 7-6 | 6  | RESERVED | R/W  | 0h    | Reserved                                                                               |

| 5-0 | 0  | GAIN0    | R/W  | _     | Gain for Button Data for Channel 0 Refer to the Gain Table for detailed configuration. |

### 7.5.1.15 LP\_SCAN\_RATE Register (Offset = Fh) [Reset = 10h]

LP\_SCAN\_RATE is shown in LP\_SCAN\_RATE Register Field Descriptions.

Return to the LDC3114 Registers.

Low Power Mode scan rate

#### Table 7-17. LP\_SCAN\_RATE Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                                                                                                 |

|-----|----------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-2 | RESERVED | R/W  | 4h    | Reserved                                                                                                                                                    |

| 1-0 | LPSR     | R/W  |       | Low Power Mode Scan Rate Refer to Configuring Button Scan Rate section for more information. 0h = 5 SPS 1h = 2.5 SPS 2h = 1.25 SPS (Default) 3h = 0.625 SPS |

### 7.5.1.16 GAIN1 Register (Offset = 10h) [Reset = 28h]

GAIN1 is shown in GAIN1 Register Field Descriptions.

Return to the LDC3114 Registers.

Gain for Channel 1 sensitivity adjustment for button algorithm

### Table 7-18. GAIN1 Register Field Descriptions

| Bit | Field    | Туре | Reset | Description                                                                            |

|-----|----------|------|-------|----------------------------------------------------------------------------------------|

| 7-6 | RESERVED | R/W  | 0h    | Reserved                                                                               |

| 5-0 | GAIN1    | R/W  | 28h   | Gain for Button Data for Channel 1 Refer to the Gain Table for detailed configuration. |

### 7.5.1.17 INTPOL Register (Offset = 11h) [Reset = 18h]

INTPOL is shown in INTPOL Register Field Descriptions.

Return to the LDC3114 Registers.

Interrupt polarity

Table 7-19. INTPOL Register Field Descriptions

| Bit | Field      | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-5 | RESERVED   | R/W  | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |