# ISO7841x High-Performance, 8000V<sub>PK</sub> Reinforced Quad-Channel Digital Isolator

#### 1 Features

- Signaling Rate: Up to 100Mbps

- Wide Supply Range: 2.25V to 5.5V

- 2.25V to 5.5V Level Translation

- Wide Temperature Range: -55°C to 125°C

- Low-Power Consumption, Typical 1.7mA per Channel at 1Mbps

- Low Propagation Delay: 11ns Typical (5V Supplies)

- Industry leading CMTI (Min): ±100kV/µs

- Robust Electromagnetic Compatibility (EMC)

- System-Level ESD, EFT, and Surge Immunity

- Low Emissions

- Isolation Barrier Life: >40 Years

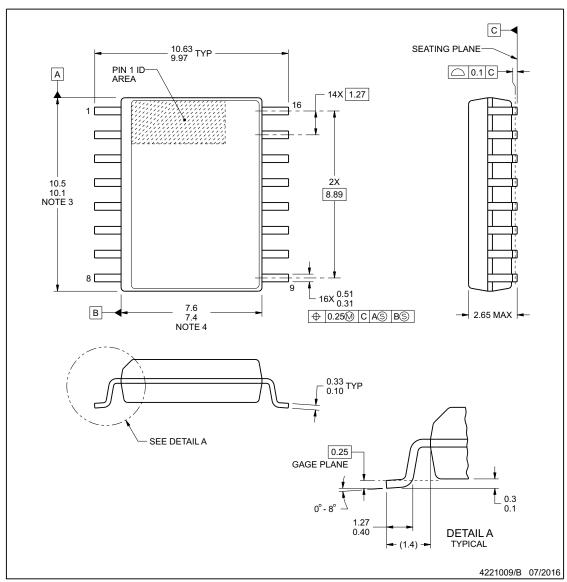

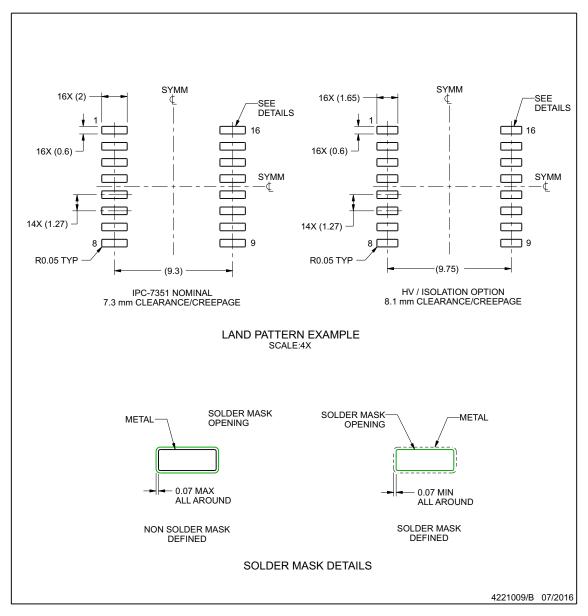

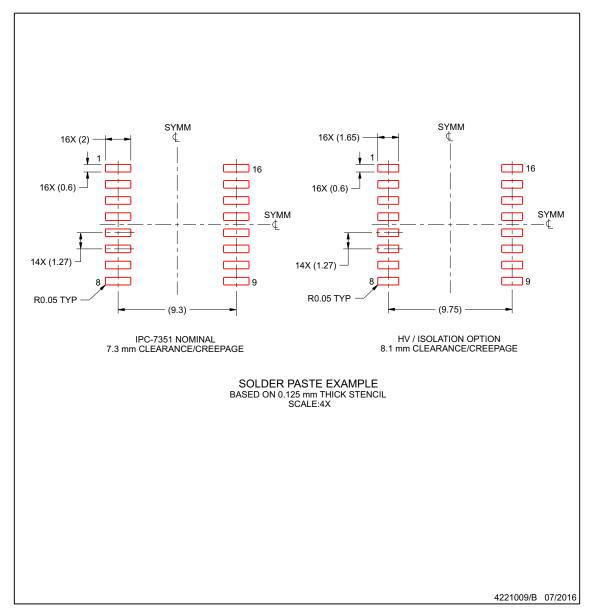

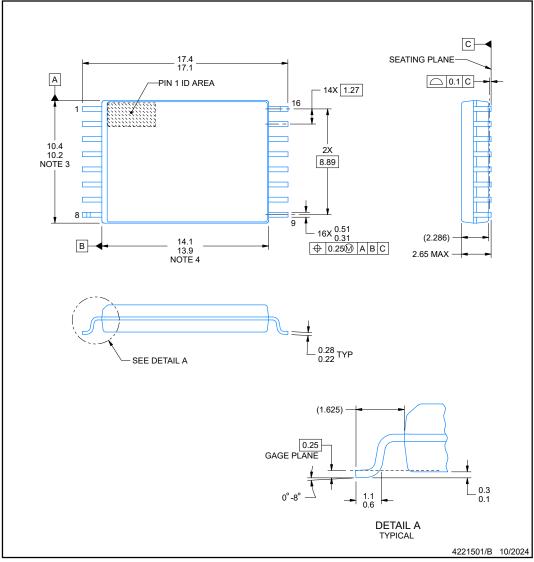

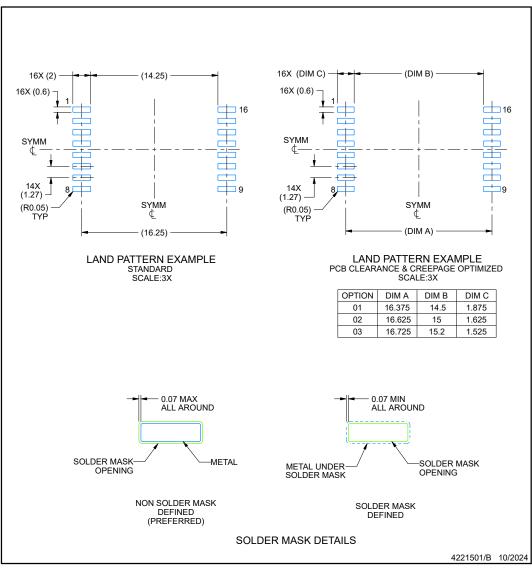

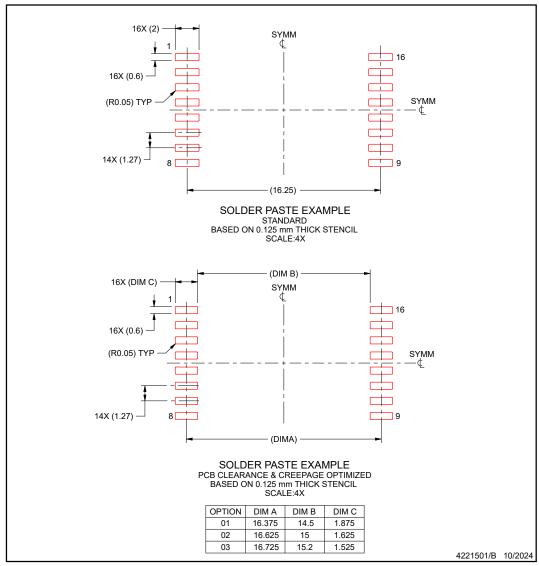

- Wide Body SOIC-16 Package and Extra-Wide Body SOIC-16 Package Options

- Safety and Regulatory Approvals:

- 8000V<sub>PK</sub> Reinforced Isolation per DIN EN IEC 60747-17 (VDE 0884-17)

- 5.7kV<sub>RMS</sub> Isolation for 1 Minute per UL 1577

- CSA Component Acceptance Notice 5A, IEC 60950-1 and IEC 60601-1 End Equipment Standards

- CQC Certification per GB4943.1

- TUV Certification per EN 61010-1 and EN 62368-1

## 2 Applications

- **Industrial Automation**

- **Motor Control**

- Power Supplies

- Solar Inverters

- Medical Equipment

- Hybrid Electric Vehicles

## 3 Description

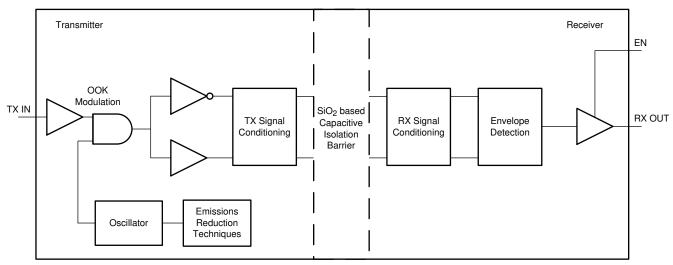

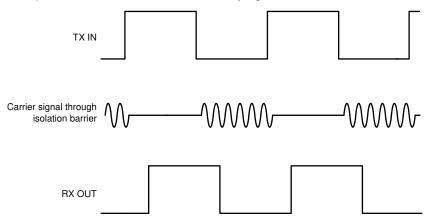

The ISO7841x device is a high-performance, quadchannel digital isolator with a 8000V<sub>PK</sub> isolation This device has reinforced isolation certifications according to VDE, CSA, CQC, and TUV. The isolator provides high electromagnetic immunity and low emissions at low-power consumption while isolating CMOS or LVCMOS digital I/Os. Each isolation channel has a logic input and output buffer separated by a silicon-dioxide (SiO<sub>2</sub>) insulation barrier.

This device comes with enable pins that can be used to put the respective outputs in high impedance for multi-controller driving applications and to reduce power consumption. The ISO7841 device has three forward and one reverse-direction channels. If the input power or signal is lost, the default output is high for the ISO7841 device and low for the ISO7841F device. See the Device Functional Modes section for further details.

Used in conjunction with isolated power supplies, this device helps prevent noise currents on a data bus or other circuits from entering the local ground and interfering with or damaging sensitive circuitry. Through innovative chip design and layout techniques, electromagnetic compatibility of the ISO7841 device has been significantly enhanced to ease system-level ESD, EFT, surge, and emissions compliance.

The ISO7841 device is available in 16-pin SOIC widebody (DW) and extra-wide body (DWW) packages.

### **Package Information**

| PART<br>NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE<br>SIZE <sup>(2)</sup> | BODY SIZE<br>(NOM)  |

|----------------|------------------------|--------------------------------|---------------------|

| ISO7841        | DW (16)                | 10.30mm ×<br>10.30mm           | 10.30mm ×<br>7.50mm |

| ISO7841F       | DWW (16)               | 10.30mm ×<br>17.25mm           | 10.30mm ×<br>14.0mm |

- For all available packages, see the orderable addendum at the end of the data sheet.

- The package size (length × width) is a nominal value and includes pins, where applicable.

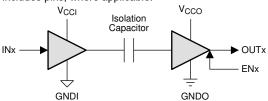

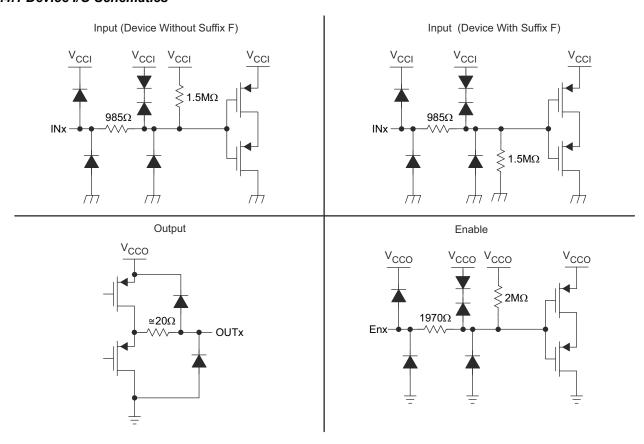

V<sub>CCI</sub> and GNDI are supply and ground connections respectively for the input channels.

V<sub>CCO</sub> and GNDO are supply and ground connections respectively for the output channels.

#### Simplified Schematic

## **Table of Contents**

| 1 Features1                                        | 5.19 Typical Characteristics1        | ľ  |

|----------------------------------------------------|--------------------------------------|----|

| 2 Applications1                                    |                                      |    |

| 3 Description1                                     |                                      |    |

| 4 Pin Configuration and Functions2                 | 7.1 Overview2                        | 2( |

| Pin Functions2                                     | 7.2 Functional Block Diagram2        | 2( |

| 5 Specifications3                                  | 7.3 Feature Description2             | 2. |

| 5.1 Absolute Maximum Ratings3                      | 7.4 Device Functional Modes2         | 2. |

| 5.2 ESD Ratings3                                   | 8 Application and Implementation2    | 22 |

| 5.3 Recommended Operating Conditions3              | 8.1 Application Information2         | 2  |

| 5.4 Thermal Information4                           | 8.2 Typical Application2             | 2  |

| 5.5 Power Ratings4                                 | 8.3 Power Supply Recommendations2    | 2  |

| 5.6 Insulation Specifications5                     |                                      |    |

| 5.7 Safety-Related Certifications6                 | 9 Device and Documentation Support2  | 26 |

| 5.8 Safety Limiting Values6                        |                                      | 26 |

| 5.9 Electrical Characteristics—5V Supply7          |                                      |    |

| 5.10 Supply Current Characteristics—5V Supply8     |                                      |    |

| 5.11 Electrical Characteristics—3.3V Supply9       |                                      | 26 |

| 5.12 Supply Current Characteristics—3.3V Supply 10 |                                      |    |

| 5.13 Electrical Characteristics—2.5V Supply11      | 9.6 Electrostatic Discharge Caution2 | 26 |

| 5.14 Supply Current Characteristics—2.5V Supply 12 | 9.7 Glossary2                        | 26 |

| 5.15 Switching Characteristics—5V Supply13         |                                      | 26 |

| 5.16 Switching Characteristics—3.3V Supply14       |                                      |    |

| 5.17 Switching Characteristics—2.5V Supply15       |                                      | )  |

| 5.18 Insulation Characteristics Curves 16          |                                      |    |

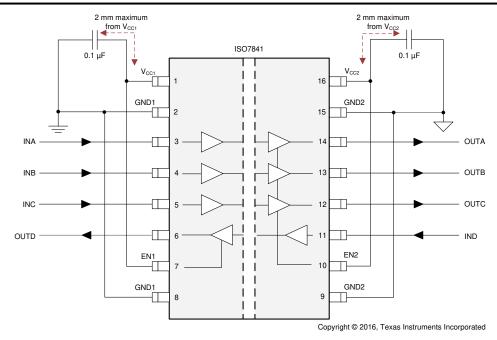

## **4 Pin Configuration and Functions**

## **Pin Functions**

| PIN              |          | Type <sup>(1)</sup> | DESCRIPTION                                                                                                              |

|------------------|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------|

| NAME             | NAME NO. |                     | DESCRIPTION                                                                                                              |

| EN1              | 7        | I                   | Output enable 1. Output pins on side 1 are enabled when EN1 is high or open and in high-impedance state when EN1 is low. |

| EN2              | 10       | I                   | Output enable 2. Output pins on side 2 are enabled when EN2 is high or open and in high-impedance state when EN2 is low. |

| GND1             | 2        |                     | Cround connection for V                                                                                                  |

| GNDT             | 8        | _                   | Ground connection for V <sub>CC1</sub>                                                                                   |

| GND2             | 9        |                     | Ground connection for V <sub>CC2</sub>                                                                                   |

| GNDZ             | 15       |                     | Ground connection for V <sub>CC2</sub>                                                                                   |

| INA              | 3        | I                   | Input, channel A                                                                                                         |

| INB              | 4        | I                   | Input, channel B                                                                                                         |

| INC              | 5        | I                   | Input, channel C                                                                                                         |

| IND              | 11       | I                   | Input, channel D                                                                                                         |

| OUTA             | 14       | 0                   | Output, channel A                                                                                                        |

| OUTB             | 13       | 0                   | Output, channel B                                                                                                        |

| OUTC             | 12       | 0                   | Output, channel C                                                                                                        |

| OUTD             | 6        | 0                   | Output, channel D                                                                                                        |

| V <sub>CC1</sub> | 1        | _                   | Power supply, V <sub>CC1</sub>                                                                                           |

| V <sub>CC2</sub> | 16       | _                   | Power supply, V <sub>CC2</sub>                                                                                           |

(1) I = Input, O = Output

## 5 Specifications

## 5.1 Absolute Maximum Ratings

#### See (1)

|                                        |              |                   | MIN  | MAX                                   | UNIT |

|----------------------------------------|--------------|-------------------|------|---------------------------------------|------|

| V <sub>CC1</sub> ,<br>V <sub>CC2</sub> | Supply volta | ge <sup>(2)</sup> | -0.5 | 6                                     | V    |

|                                        |              | INx               | -0.5 | $V_{CCX} + 0.5^{(3)}$                 |      |

|                                        | Voltage      | OUTx              | -0.5 | $V_{CCX} + 0.5^{(3)}$                 | V    |

|                                        |              | ENx               | -0.5 | V <sub>CCX</sub> + 0.5 <sup>(3)</sup> |      |

| Io                                     | Output curre | nt                | -15  | 15                                    | mA   |

|                                        | Surge immu   | nity              |      | 12.8                                  | kV   |

| T <sub>stg</sub>                       | Storage tem  | perature          | -65  | 150                                   | °C   |

- (1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

- (2) All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values.

- (3) Maximum voltage must not exceed 6V

### 5.2 ESD Ratings

|                                            |                                                                                          | VALUE | UNIT |

|--------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

|                                            | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±6000 |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500 | V    |

- (1) JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

- 2) JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

## **5.3 Recommended Operating Conditions**

|                                     |                                     |                                      | MIN                                   | NOM | MAX                        | UNIT |

|-------------------------------------|-------------------------------------|--------------------------------------|---------------------------------------|-----|----------------------------|------|

| V <sub>CC1</sub> , V <sub>CC2</sub> | Supply voltage                      |                                      | 2.25                                  |     | 5.5                        | V    |

|                                     |                                     | V <sub>CCO</sub> <sup>(2)</sup> = 5V | -4                                    |     |                            |      |

| I <sub>OH</sub>                     | High-level output current           | $V_{CCO}^{(2)} = 3.3V$               | -2                                    |     |                            | mA   |

|                                     |                                     | $V_{CCO}^{(2)} = 2.5V$               | -1                                    |     |                            |      |

|                                     |                                     | V <sub>CCO</sub> <sup>(2)</sup> = 5V |                                       | 4   |                            |      |

| I <sub>OL</sub>                     | Low-level output current            | $V_{CCO}^{(2)} = 3.3V$               |                                       | 2   |                            | mA   |

|                                     |                                     | $V_{CCO}^{(2)} = 2.5V$               |                                       | 1   |                            |      |

| V <sub>IH</sub>                     | High-level input voltage            | ·                                    | 0.7 × V <sub>CCI</sub> <sup>(2)</sup> |     | V <sub>CCI</sub> (2)       | V    |

| V <sub>IL</sub>                     | Low-level input voltage             |                                      | 0                                     |     | $0.3 \times V_{CCI}^{(2)}$ | V    |

| DR                                  | Signaling Rate                      |                                      | 0                                     |     | 100                        | Mbps |

| TJ                                  | Junction temperature <sup>(1)</sup> |                                      | -55                                   |     | 150                        | °C   |

| T <sub>A</sub>                      | Ambient temperature                 |                                      | -55                                   | 25  | 125                        | °C   |

- (1) To maintain the recommended operating conditions for T<sub>J</sub>, see Section 5.4.

- (2)  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

## **5.4 Thermal Information**

|                          | ISO7841                                      |           |                                      |      |

|--------------------------|----------------------------------------------|-----------|--------------------------------------|------|

|                          | THERMAL METRIC(1)                            | DW (SOIC) | DWW (SOIC)                           | UNIT |

|                          | I HERMAL METRICITY                           | 16 Pins   | 78.9<br>41.1<br>49.5<br>15.2<br>48.8 |      |

| R <sub>θJA</sub>         | Junction-to-ambient thermal resistance       | 78.9      | 78.9                                 | °C/W |

| R <sub>0JC(top)</sub>    | Junction-to-case(top) thermal resistance     | 41.6      | 41.1                                 | °C/W |

| $R_{\theta JB}$          | Junction-to-board thermal resistance         | 43.6      | 49.5                                 | °C/W |

| ΨЈТ                      | Junction-to-top characterization parameter   | 15.5      | 15.2                                 | °C/W |

| $\Psi_{JB}$              | Junction-to-board characterization parameter | 43.1      | 48.8                                 | °C/W |

| R <sub>0JC(bottom)</sub> | Junction-to-case(bottom) thermal resistance  | N/A       | N/A                                  | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

## 5.5 Power Ratings

$V_{CC1}$  =  $V_{CC2}$  = 5.5V,  $T_J$  = 150°C,  $C_L$  = 15pF, input a 50MHz 50% duty cycle square wave

|                 | PARAMETER                                       | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|-------------------------------------------------|-----------------|-----|-----|-----|------|

| P <sub>D</sub>  | Maximum power dissipation by ISO7841x           |                 |     |     | 200 | mW   |

| P <sub>D1</sub> | Maximum power dissipation by side-1 of ISO7841x |                 |     |     | 75  | mW   |

| P <sub>D2</sub> | Maximum power dissipation by side-2 of ISO7841x |                 |     |     | 125 | mW   |

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

## 5.6 Insulation Specifications

|                   | DADAMETER                                           | TEST COMPLETIONS                                                                                                                                                                                                             | SPECIFI           | CATION            | T.11411          |

|-------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|

|                   | PARAMETER                                           | TEST CONDITIONS                                                                                                                                                                                                              | DW                | DWW               | UNIT             |

| GENER             | RAL                                                 |                                                                                                                                                                                                                              |                   |                   |                  |

| CL D              | []tampalalaanana(1)                                 | Shortest pin-to-pin distance through air                                                                                                                                                                                     | >8                | >14.5             | mm               |

| CLR               | External clearance <sup>(1)</sup>                   | Shortest pin-to-pin distance through air (typical)                                                                                                                                                                           |                   | 15.0              | mm               |

|                   |                                                     | Shortest pin-to-pin distance across the package surface                                                                                                                                                                      | >8                | >14.5             | mm               |

| CPG               | External creepage <sup>(1)</sup>                    | Shortest pin-to-pin distance across the package surface (typical)                                                                                                                                                            |                   | 15.0              | mm               |

| DTI               | Distance through the insulation                     | Minimum internal gap (internal clearance)                                                                                                                                                                                    | >21               | >21               | μm               |

| CTI               | Comparative tracking index                          | DIN EN 60112 (VDE 0303-11); IEC 60112; UL 746A                                                                                                                                                                               | >600              | >600              | V                |

|                   | Material group                                      |                                                                                                                                                                                                                              | I                 | I                 |                  |

|                   | Overvoltage category per IEC                        | Rated mains voltage ≤ 600V <sub>RMS</sub>                                                                                                                                                                                    | I–IV              | I–IV              |                  |

|                   | 60664-1                                             | Rated mains voltage ≤ 1000V <sub>RMS</sub>                                                                                                                                                                                   | I–III             | I–IV              |                  |

| DIN EN            | IEC 60747-17 (VDE 0884-17) <sup>(2)</sup>           |                                                                                                                                                                                                                              | I                 | 1                 |                  |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage           |                                                                                                                                                                                                                              | 2121              | 2828              | V <sub>PK</sub>  |

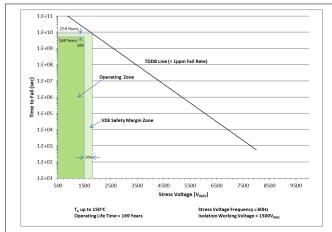

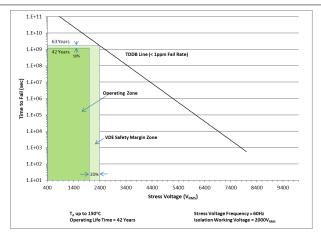

| V <sub>IOWM</sub> | Maximum isolation working                           | AC voltage (sine wave); Time dependent dielectric breakdown (TDDB) Test, see Figure 5-1 and Figure 5-2                                                                                                                       | 1500              | 2000              | V <sub>RMS</sub> |

|                   | voltage                                             | DC voltage                                                                                                                                                                                                                   | 2121              | 2828              | V <sub>DC</sub>  |

| $V_{IOTM}$        | Maximum transient isolation voltage                 | V <sub>TEST</sub> = 1.2 × V <sub>IOTM</sub><br>t = 60s (qualification)<br>t= 1s (100% production)                                                                                                                            | 8000              | 8000              | V <sub>PK</sub>  |

| V <sub>IMP</sub>  | Maximum impulse voltage (3)                         | Tested in air, 1.2/50µs waveform per IEC 62368-1                                                                                                                                                                             | 9800              | 9800              | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage (4)                 | V <sub>IOSM</sub> ≥ 1.3 x V <sub>IMP</sub> ; Tested in oil (qualification test),<br>1.2/50-µs waveform per IEC 62368-1                                                                                                       | 12800             | 12800             | V <sub>PK</sub>  |

|                   | Apparent charge <sup>(5)</sup>                      | Method a: After I/O safety test subgroup 2/3, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.2 \times V_{IOTM} = 2545V_{PK}$ (DW) and $3394V_{PK}$ (DWW), $t_m = 10s$                                               | ≤5                | ≤5                | рС               |

| q <sub>pd</sub>   |                                                     | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60s$ ; $V_{pd(m)} = 1.6 \times V_{IORM} = 3394 V_{PK}$ (DW) and $4525 V_{PK}$ (DWW), $t_m = 10s$                                           | ≤5                | ≤5                |                  |

|                   |                                                     | Method b: At routine test (100% production); $V_{ini} = 1.2 \times V_{IOTM}, t_{ini} = 1s; \\ V_{pd(m)} = 1.875 \times V_{IORM}, t_m = 1s \text{ (method b1) or } \\ V_{pd(m)} = V_{ini}, t_m = t_{ini} \text{ (method b2)}$ | ≤5                | ≤5                |                  |

| C <sub>IO</sub>   | Barrier capacitance, input to output <sup>(6)</sup> | $V_{IO} = 0.4 \times \sin(2\pi ft)$ , $f = 1MHz$                                                                                                                                                                             | 2                 | 2                 | pF               |

|                   |                                                     | V <sub>IO</sub> = 500V, T <sub>A</sub> = 25°C                                                                                                                                                                                | >10 <sup>12</sup> | >10 <sup>12</sup> |                  |

| $R_{IO}$          | Isolation resistance, input to output (6)           | V <sub>IO</sub> = 500V, 100°C ≤ T <sub>A</sub> ≤ 125°C                                                                                                                                                                       | >10 <sup>11</sup> | >10 <sup>11</sup> | Ω                |

|                   |                                                     | V <sub>IO</sub> = 500V at T <sub>S</sub> = 150°C                                                                                                                                                                             | >10 <sup>9</sup>  | >10 <sup>9</sup>  |                  |

|                   | Pollution degree                                    |                                                                                                                                                                                                                              | 2                 | 2                 |                  |

|                   | Climatic category                                   |                                                                                                                                                                                                                              | 55/125/21         | 55/125/21         |                  |

| UL 157            | 7                                                   |                                                                                                                                                                                                                              |                   |                   |                  |

| V <sub>ISO</sub>  | Withstand isolation voltage                         | $V_{TEST} = V_{ISO} = 5700V_{RMS}$ , t = 60s (qualification),<br>$V_{TEST} = 1.2 \times V_{ISO} = 6840V_{RMS}$ , t = 1s (100% production)                                                                                    | 5700              | 5700              | V <sub>RMS</sub> |

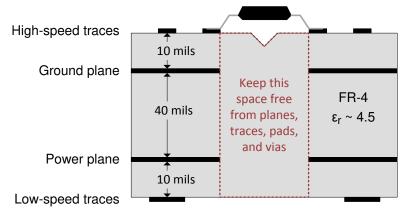

<sup>(1)</sup> Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal

- in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

- (2) This coupler is suitable for *safe electrical insulation* only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

- (3) Testing is carried out in air to determine the surge immunity of the package.

- (4) Testing is carried out in oil to determine the intrinsic surge immunity of the isolation barrier.

- (5) Apparent charge is electrical discharge caused by a partial discharge (pd).

- (6) All pins on each side of the barrier tied together creating a two-terminal device.

### 5.7 Safety-Related Certifications

| VDE                                                                                                                                                                                                                                    | CSA                                                                                                                                                                                                                                                                                                                                                      | UL                                                           | CQC                                                                                                                                        | TUV                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certified according to DIN<br>EN IEC 60747-17 (VDE<br>0884-17)                                                                                                                                                                         | Approved under CSA<br>Component Acceptance<br>Notice 5A, IEC 60950-1 and<br>IEC 60601-1                                                                                                                                                                                                                                                                  | Certified according to UL 1577 Component Recognition Program | Certified according to GB 4943.1                                                                                                           | Certified according to EN 61010-1 and EN 62368-1                                                                                                                                                                                                                                        |

| Reinforced insulation Maximum transient isolation voltage, 8000V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 2121V <sub>PK</sub> (DW), 2828V <sub>PK</sub> (DWW); Maximum surge isolation voltage, 12800V <sub>PK</sub> | Reinforced insulation per CSA 60950-1-07+A1+A2 and IEC 60950-1 2nd Ed., 800V <sub>RMS</sub> (DWV) and 1450V <sub>RMS</sub> (DWW) max working voltage (pollution degree 2, material group I); 2 MOPP (Means of Patient Protection) per CSA 60601-1:14 and IEC 60601-1 Ed. 3.1, 250V <sub>RMS</sub> (DW) and 400V <sub>RMS</sub> (DWW) max working voltage | Single protection,<br>5700V <sub>RMS</sub>                   | Reinforced Insulation, Altitude ≤ 5000m, Tropical Climate, 700V <sub>RMS</sub> (DW) and 1450V <sub>RMS</sub> (DWW) maximum working voltage | 5700 V <sub>RMS</sub> Reinforced insulation per EN 61010-1 up to working voltage of 600V <sub>RMS</sub> (DW) and 1000V <sub>RMS</sub> (DWW); 5700V <sub>RMS</sub> Reinforced insulation per EN 62368-1 up to working voltage of 800V <sub>RMS</sub> (DW) and 1450V <sub>RMS</sub> (DWW) |

| Certificate number: 40040142                                                                                                                                                                                                           | Master contract number: 220991                                                                                                                                                                                                                                                                                                                           | File number: E181974                                         | Certificate number:<br>CQC15001121716                                                                                                      | Client ID number: 77311                                                                                                                                                                                                                                                                 |

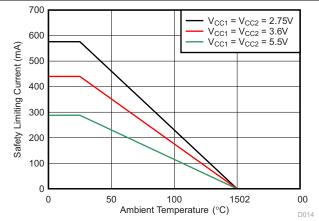

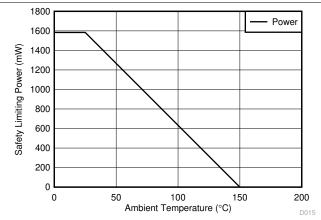

## 5.8 Safety Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry. A failure of the I/O can allow low resistance to ground or the supply and, without current limiting, dissipate sufficient power to overheat the die and damage the isolation barrier potentially leading to secondary system failures.

|                | PARAMETER                               | TEST CONDITIONS                                                                                   | MIN | TYP | MAX  | UNIT |

|----------------|-----------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|------|------|

|                | Safety input, output, or supply current | $R_{\theta JA} = 78.9$ °C/W, $V_I = 5.5$ V, $T_J = 150$ °C, $T_A = 25$ °C                         |     |     | 288  |      |

| Is             |                                         | R <sub>0JA</sub> = 78.9°C/W, V <sub>I</sub> = 3.6V, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C |     |     | 440  | mA   |

|                |                                         | $R_{\theta JA} = 78.9^{\circ}C/W, V_I = 2.75V, T_J = 150^{\circ}C, T_A = 25^{\circ}C$             |     |     | 576  |      |

| Ps             | Safety input, output, or total power    | R <sub>0JA</sub> = 78.9°C/W, T <sub>J</sub> = 150°C, T <sub>A</sub> = 25°C                        |     |     | 1584 | mW   |

| T <sub>S</sub> | Maximum safety temperature              |                                                                                                   |     |     | 150  | °C   |

The maximum safety temperature is the maximum junction temperature specified for the device. The power dissipation and junction-to-air thermal impedance of the device installed in the application hardware determines the junction temperature. The assumed junction-to-air thermal resistance in the Section 5.4 is that of a device installed on a high-K test board for leaded surface-mount packages. The power is the recommended maximum input voltage times the current. The junction temperature is then the ambient temperature plus the power times the junction-to-air thermal resistance.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

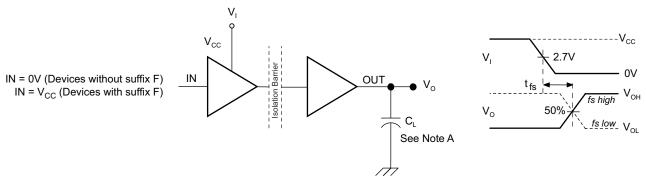

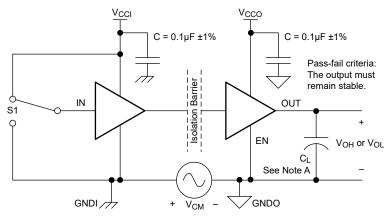

## 5.9 Electrical Characteristics—5V Supply

$V_{CC1} = V_{CC2} = 5V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

|                     | PARAMETER                          | TEST CONDITIONS                                                    | MIN                                   | TYP                                   | MAX | UNIT  |

|---------------------|------------------------------------|--------------------------------------------------------------------|---------------------------------------|---------------------------------------|-----|-------|

| V <sub>OH</sub>     | High-level output voltage          | I <sub>OH</sub> = –4mA; see Figure 6-1                             | V <sub>CCO</sub> <sup>(1)</sup> – 0.4 | V <sub>CCO</sub> <sup>(1)</sup> – 0.2 |     | V     |

| V <sub>OL</sub>     | Low-level output voltage           | I <sub>OL</sub> = 4mA; see Figure 6-1                              |                                       | 0.2                                   | 0.4 | V     |

| V <sub>I(HYS)</sub> | Input threshold voltage hysteresis |                                                                    | 0.1 × V <sub>CCI</sub> <sup>(1)</sup> |                                       |     | V     |

| I <sub>IH</sub>     | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx or ENx    |                                       |                                       | 10  | μΑ    |

| I <sub>IL</sub>     | Low-level input current            | V <sub>IL</sub> = 0V at INx or ENx                                 | -10                                   |                                       |     | μΑ    |

| СМТІ                | Common-mode transient immunity     | $V_I = V_{CCI}$ (1) or 0V, $V_{CM} = 1500V$ ; see Figure 6-4       | 100                                   |                                       |     | kV/µs |

| Cı                  | Input capacitance                  | $V_1 = V_{CC}/2 + 0.4 \times \sin(2\pi ft), f = 1MHz, V_{CC} = 5V$ |                                       | 2                                     |     | pF    |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

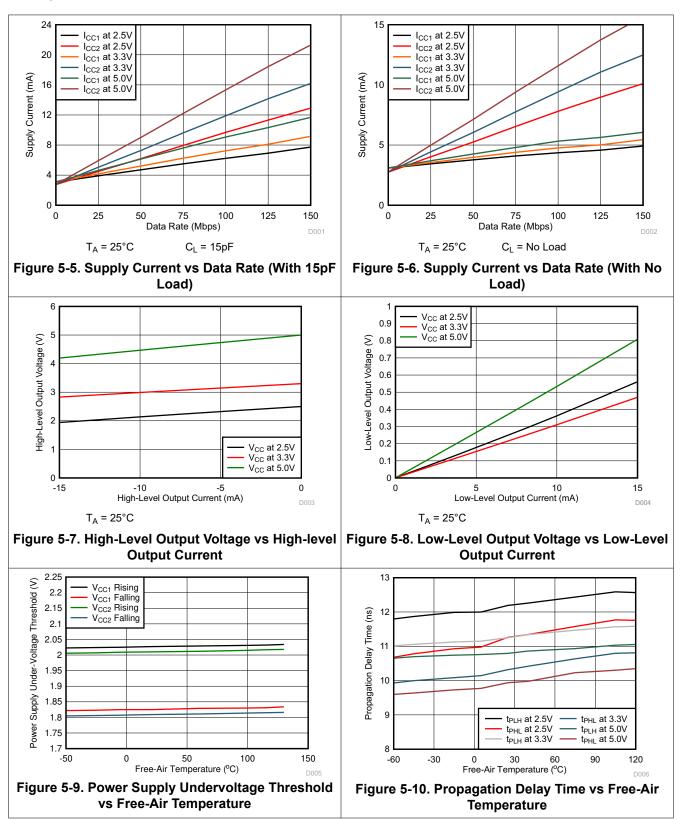

## 5.10 Supply Current Characteristics—5V Supply

$V_{CC1} = V_{CC2} = 5V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

| PARAMETER      | ,                                                                          | ded operating conditions unless o                                                                             | SUPPLY<br>CURRENT | MIN      | TYP  | MAX  | UNIT   |

|----------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------|----------|------|------|--------|

| ISO7841DW AN   | ID ISO7841FDW                                                              |                                                                                                               |                   |          |      |      |        |

|                |                                                                            | EN1 = EN2 = 0V, V <sub>I</sub> = 0V                                                                           | I <sub>CC1</sub>  |          | 1.1  | 1.8  | mA     |

|                | Disable                                                                    | $(ISO7841F), V_I = V_{CCI}^{(1)} (ISO7841)$                                                                   | I <sub>CC2</sub>  |          | 0.8  | 1.3  | mA     |

|                | Disable                                                                    | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> (1)                                                         | I <sub>CC1</sub>  |          | 4.5  | 6.6  | mA     |

|                |                                                                            | (ISO7841F), V <sub>I</sub> = 0V (ISO7841)                                                                     | I <sub>CC2</sub>  |          | 2    | 2.9  | ША     |

|                |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup>                              | I <sub>CC1</sub>  |          | 1.5  | 2.4  | mA     |

|                | DC signal                                                                  | (ISO7841)                                                                                                     | I <sub>CC2</sub>  |          | 2.1  | 3.1  | ША     |

| Supply current | DO Signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> = 0V                              | I <sub>CC1</sub>  |          | 5    | 7.3  | mA     |

| очрру саполс   |                                                                            | (ISO7841)                                                                                                     | I <sub>CC2</sub>  |          | 3.4  | 4.9  | ША     |

|                | All channels switching with square wave clock input; C <sub>L</sub> = 15pF | 1Mbps                                                                                                         | I <sub>CC1</sub>  |          | 3.3  | 4.9  | mA     |

|                |                                                                            | TWIDDS                                                                                                        | I <sub>CC2</sub>  |          | 2.9  | 4.2  | шл     |

|                |                                                                            | 10Mbps                                                                                                        | I <sub>CC1</sub>  |          | 3.9  | 5.5  | mA     |

|                |                                                                            |                                                                                                               | I <sub>CC2</sub>  |          | 4.4  | 5.7  | 111/-1 |

|                |                                                                            | 100Mbps                                                                                                       | I <sub>CC1</sub>  |          | 9.2  | 11.6 | mA     |

|                |                                                                            | Toolwisps                                                                                                     | I <sub>CC2</sub>  |          | 19   | 21.9 | ША     |

| SO7841DWW /    | AND ISO7841FDWW                                                            |                                                                                                               |                   |          |      |      |        |

|                |                                                                            | EN1 = EN2 = 0V, V <sub>I</sub> = 0V<br>(ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841) | I <sub>CC1</sub>  |          | 1.1  | 1.8  | mA     |

|                | Disable                                                                    |                                                                                                               | I <sub>CC2</sub>  |          | 0.8  | 1.3  | ША     |

|                | Disable                                                                    | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup>                                              | I <sub>CC1</sub>  |          | 4.5  | 6.6  | mA     |

|                |                                                                            | (ISO7841F), V <sub>I</sub> = 0V (ISO7841)                                                                     | I <sub>CC2</sub>  |          | 2    | 2.9  | ША     |

|                |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup>                              | I <sub>CC1</sub>  |          | 1.5  | 2.4  | mA     |

|                | DC signal                                                                  | (ISO7841)                                                                                                     | I <sub>CC2</sub>  |          | 2.1  | 3.3  | ША     |

| Supply current | DO signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> = 0V                              | I <sub>CC1</sub>  |          | 5    | 7.5  | mA     |

| эарріу сапсііс |                                                                            | (ISO7841)                                                                                                     | I <sub>CC2</sub>  |          | 3.4  | 5.2  | ША     |

|                |                                                                            | 1Mbps                                                                                                         | I <sub>CC1</sub>  |          | 3.4  | 5    | mA     |

|                |                                                                            | TIVIDPS                                                                                                       | I <sub>CC2</sub>  |          | 3    | 4.4  | ША     |

|                | All channels switching with square wave clock input;C <sub>L</sub>         | 10Mbps                                                                                                        | I <sub>CC1</sub>  |          | 4    | 5.6  | mA     |

|                | = 15pF                                                                     | TOWNERS                                                                                                       | I <sub>CC2</sub>  | <u> </u> | 4.5  | 6.1  | mA     |

|                |                                                                            | 100Mbps                                                                                                       | I <sub>CC1</sub>  |          | 9.4  | 12.1 | mΛ     |

|                |                                                                            | Toolinips                                                                                                     | I <sub>CC2</sub>  |          | 19.5 | 22.6 | mA     |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

## 5.11 Electrical Characteristics—3.3V Supply

$V_{CC1} = V_{CC2} = 3.3V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

|                     | PARAMETER                          | TEST CONDITIONS                                                                                    | MIN                                   | TYP                        | MAX | UNIT  |

|---------------------|------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------|-----|-------|

| V <sub>OH</sub>     | High-level output voltage          | I <sub>OH</sub> = -2mA; see Figure 6-1                                                             | V <sub>CCO</sub> <sup>(1)</sup> – 0.4 | V <sub>CCO</sub> (1) – 0.2 |     | V     |

| V <sub>OL</sub>     | Low-level output voltage           | I <sub>OL</sub> = 2mA; see Figure 6-1                                                              |                                       | 0.2                        | 0.4 | V     |

| V <sub>I(HYS)</sub> | Input threshold voltage hysteresis |                                                                                                    | 0.1 × V <sub>CCI</sub> <sup>(1)</sup> |                            |     | V     |

| I <sub>IH</sub>     | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx or ENx                                    |                                       |                            | 10  | μΑ    |

| I <sub>IL</sub>     | Low-level input current            | V <sub>IL</sub> = 0V at INx or ENx                                                                 | -10                                   |                            |     | μA    |

| CMTI                | Common-mode transient immunity     | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> or 0V, V <sub>CM</sub> = 1500V;<br>see Figure 6-4 | 100                                   |                            |     | kV/μs |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

## 5.12 Supply Current Characteristics—3.3V Supply

V<sub>CC1</sub> = V<sub>CC2</sub> = 3.3V ±10% (over recommended operating conditions unless otherwise noted)

| PARAMETER      | TEST CONDITIONS                                                            | ended operating conditions unles                                                                                 | SUPPLY<br>CURRENT | MIN TYP | MAX  | UNIT   |

|----------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|---------|------|--------|

| ISO7841DW AN   | ID ISO7841FDW                                                              |                                                                                                                  |                   |         |      |        |

|                |                                                                            | EN1 = EN2 = 0V, V <sub>I</sub> =                                                                                 | I <sub>CC1</sub>  | 1.1     | 1.8  |        |

|                | Disable                                                                    | 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841)                                        | I <sub>CC2</sub>  | 0.8     | 1.3  | mA     |

|                | Diodolo                                                                    | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> (1)                                                            | I <sub>CC1</sub>  | 4.5     | 6.6  | mA     |

|                |                                                                            | (ISO7841F), V <sub>I</sub> = 0V (ISO7841)                                                                        | I <sub>CC2</sub>  | 1.9     | 2.9  | IIIA   |

|                |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup>                                 | I <sub>CC1</sub>  | 1.5     | 2.4  | mA     |

| Supply current | DC signal                                                                  | (ISO7841)                                                                                                        | I <sub>CC2</sub>  | 2.1     | 3.1  | ША     |

|                | DO Signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> = 0V                                 | I <sub>CC1</sub>  | 5       | 7.3  | mA     |

|                |                                                                            | (ISO7841)                                                                                                        | I <sub>CC2</sub>  | 3.3     | 4.9  | 1117 ( |

|                | All channels switching with square wave clock input; C <sub>L</sub> = 15pF | 1Mbps                                                                                                            | I <sub>CC1</sub>  | 3.3     | 4.9  | mA     |

|                |                                                                            | TWISPS                                                                                                           | I <sub>CC2</sub>  | 2.8     | 4.1  |        |

|                |                                                                            | 10Mbps                                                                                                           | I <sub>CC1</sub>  | 3.7     | 5.3  | mA     |

|                |                                                                            | Townspa                                                                                                          | I <sub>CC2</sub>  | 3.9     | 5.2  | ША     |

|                |                                                                            | 100Mbps                                                                                                          | I <sub>CC1</sub>  | 7.4     | 9.3  | mA     |

|                |                                                                            | Toolvibps                                                                                                        | I <sub>CC2</sub>  | 14.5    | 16.9 | ША     |

| SO7841DWW A    | AND ISO7841FDWW                                                            |                                                                                                                  |                   |         |      |        |

|                |                                                                            | EN1 = EN2 = 0V, V <sub>I</sub> =<br>0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup><br>(ISO7841) | I <sub>CC1</sub>  | 1.1     | 1.8  |        |

|                | Disable                                                                    |                                                                                                                  | I <sub>CC2</sub>  | 0.8     | 1.3  | mA     |

|                | Biodalio                                                                   | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> (1)                                                            | I <sub>CC1</sub>  | 4.5     | 6.6  | m Λ    |

|                |                                                                            | (ISO7841F), $V_I = 0V$ (ISO7841)                                                                                 | I <sub>CC2</sub>  | 2       | 2.9  | mA     |

|                |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup>                                 | I <sub>CC1</sub>  | 1.5     | 2.4  | mΛ     |

|                | DC signal                                                                  | (ISO7841)                                                                                                        | I <sub>CC2</sub>  | 2.1     | 3.3  | mA     |

| Supply current | DC signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> = 0V                                 | I <sub>CC1</sub>  | 5       | 7.5  | mA     |

|                |                                                                            | (ISO7841)                                                                                                        | I <sub>CC2</sub>  | 3.4     | 5.2  | IIIA   |

|                |                                                                            | 1Mbps                                                                                                            | I <sub>CC1</sub>  | 3.4     | 5    | mA     |

|                |                                                                            | Tivibps                                                                                                          | I <sub>CC2</sub>  | 2.9     | 4.4  | IIIA   |

|                | All channels switching with square wave clock input;                       | 10Mbps                                                                                                           | I <sub>CC1</sub>  | 3.8     | 5.4  | mΛ     |

|                | $C_L = 15pF$                                                               | Ισινισμο                                                                                                         | I <sub>CC2</sub>  | 4       | 5.5  | mA     |

|                |                                                                            | 100Mbps                                                                                                          | I <sub>CC1</sub>  | 7.5     | 9.9  | mΔ     |

|                |                                                                            | Toolvinps                                                                                                        | I <sub>CC2</sub>  | 14.8    | 17.2 | mA     |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

## 5.13 Electrical Characteristics—2.5V Supply

$V_{CC1} = V_{CC2} = 2.5V \pm 10\%$  (over recommended operating conditions unless otherwise noted)

|                     | PARAMETER                          | TEST CONDITIONS                                                 | MIN                                   | TYP                        | MAX | UNIT  |

|---------------------|------------------------------------|-----------------------------------------------------------------|---------------------------------------|----------------------------|-----|-------|

| V <sub>OH</sub>     | High-level output voltage          | I <sub>OH</sub> = -1mA; see Figure 6-1                          | V <sub>CCO</sub> <sup>(1)</sup> – 0.4 | V <sub>CCO</sub> (1) – 0.2 |     | V     |

| V <sub>OL</sub>     | Low-level output voltage           | I <sub>OL</sub> = 1mA; see Figure 6-1                           |                                       | 0.2                        | 0.4 | V     |

| V <sub>I(HYS)</sub> | Input threshold voltage hysteresis |                                                                 | 0.1 × V <sub>CCI</sub> <sup>(1)</sup> |                            |     | V     |

| I <sub>IH</sub>     | High-level input current           | V <sub>IH</sub> = V <sub>CCI</sub> <sup>(1)</sup> at INx or ENx |                                       |                            | 10  | μΑ    |

| I <sub>IL</sub>     | Low-level input current            | V <sub>IL</sub> = 0V at INx or ENx                              | -10                                   |                            |     | μΑ    |

| СМТІ                | Common-mode transient immunity     | $V_I = V_{CCI}$ (1) or 0V, $V_{CM} = 1500V$ ; see Figure 6-4    | 100                                   |                            |     | kV/μs |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

## 5.14 Supply Current Characteristics—2.5V Supply

V<sub>CC1</sub> = V<sub>CC2</sub> = 2.5V ±10% (over recommended operating conditions unless otherwise noted)

| PARAMETER           | ·                                                                          | ONDITIONS                                                                                                        | SUPPLY<br>CURRENT | MIN | TYP  | MAX  | UNIT   |

|---------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|-----|------|------|--------|

| ISO7841DW AN        | D ISO7841FDW                                                               |                                                                                                                  |                   |     |      | -    |        |

|                     |                                                                            | EN1 = EN2 = 0V, V <sub>I</sub> = 0V                                                                              | I <sub>CC1</sub>  |     | 1.1  | 1.7  |        |

|                     | Disable                                                                    | (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841)                                           | I <sub>CC2</sub>  |     | 0.8  | 1.2  | mA     |

|                     | Disable                                                                    | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> (1)                                                            | I <sub>CC1</sub>  |     | 4.5  | 6.5  | A      |

|                     |                                                                            | (ISO7841F), V <sub>I</sub> = 0V (ISO7841)                                                                        | I <sub>CC2</sub>  |     | 1.9  | 2.8  | mA     |

|                     |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub>                                                | I <sub>CC1</sub>  |     | 1.6  | 2.3  | mA     |

|                     | DC signal                                                                  | <sup>(1)</sup> (ISO7841)                                                                                         | I <sub>CC2</sub>  |     | 2.2  | 3.1  | ША     |

| Supply current      | DC signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> =<br>0V (ISO7841)                    | I <sub>CC1</sub>  |     | 5.1  | 7.2  | mA     |

|                     |                                                                            |                                                                                                                  | I <sub>CC2</sub>  |     | 3.5  | 4.8  |        |

|                     | All channels switching with square wave clock input; C <sub>L</sub> = 15pF | 1Mbps                                                                                                            | I <sub>CC1</sub>  |     | 3.4  | 4.8  | mA     |

|                     |                                                                            | Πίιορο                                                                                                           | I <sub>CC2</sub>  |     | 2.9  | 4    | 111/   |

|                     |                                                                            | 10Mbps                                                                                                           | I <sub>CC1</sub>  |     | 3.7  | 5.1  | mA     |

|                     |                                                                            | TOMOPS                                                                                                           | I <sub>CC2</sub>  |     | 3.7  | 4.8  |        |

|                     |                                                                            | 100Mbps                                                                                                          | I <sub>CC1</sub>  |     | 6.8  | 8.1  | mA     |

|                     |                                                                            | Тоомвро                                                                                                          | I <sub>CC2</sub>  |     | 12   | 14.2 |        |

| ISO7841DWW <i>A</i> | AND ISO7841FDWW                                                            |                                                                                                                  |                   |     |      |      |        |

|                     | Disable                                                                    | EN1 = EN2 = 0V, V <sub>I</sub> = 0V<br>(ISO7841F), V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup><br>(ISO7841) | I <sub>CC1</sub>  |     | 1.1  | 1.7  | m Λ    |

|                     |                                                                            |                                                                                                                  | I <sub>CC2</sub>  |     | 8.0  | 1.2  | mA     |

|                     | Biodalio                                                                   | EN1 = EN2 = 0V, V <sub>I</sub> = V <sub>CCI</sub> (1)                                                            | I <sub>CC1</sub>  |     | 4.5  | 6.5  | Λ      |

|                     |                                                                            | (ISO7841F), V <sub>I</sub> = 0V (ISO7841)                                                                        | I <sub>CC2</sub>  |     | 1.9  | 2.8  | mA     |

|                     |                                                                            | V <sub>I</sub> = 0V (ISO7841F), V <sub>I</sub> = V <sub>CCI</sub>                                                | I <sub>CC1</sub>  |     | 1.6  | 2.4  | mA     |

|                     | DC signal                                                                  | (1) (ISO7841)                                                                                                    | I <sub>CC2</sub>  |     | 2.2  | 3.3  | ША     |

| Supply current      | DC signal                                                                  | V <sub>I</sub> = V <sub>CCI</sub> <sup>(1)</sup> (ISO7841F), V <sub>I</sub> =                                    | I <sub>CC1</sub>  |     | 5.1  | 7.5  | mA     |

| 11.7                |                                                                            | 0V (ISO7841)                                                                                                     | I <sub>CC2</sub>  |     | 3.5  | 5.2  | IIIA   |

|                     |                                                                            | 1Mbps                                                                                                            | I <sub>CC1</sub>  |     | 3.5  | 5    | mA     |

|                     |                                                                            | בקמואוז                                                                                                          | I <sub>CC2</sub>  |     | 3    | 4.3  |        |

|                     | All channels switching with square wave clock input; C <sub>L</sub>        | 10Mbps                                                                                                           | I <sub>CC1</sub>  |     | 3.8  | 5.3  | mA     |

|                     | = 15pF                                                                     | TOWNUPS                                                                                                          | I <sub>CC2</sub>  |     | 3.8  | 5.2  | ma<br> |

|                     |                                                                            | 100Mbps                                                                                                          | I <sub>CC1</sub>  |     | 6.9  | 8.8  | mA     |

|                     |                                                                            | TOOMINPO                                                                                                         | I <sub>CC2</sub>  |     | 12.3 | 14.2 | mA     |

<sup>(1)</sup>  $V_{CCI}$  = Input-side  $V_{CC}$ ;  $V_{CCO}$  = Output-side  $V_{CC}$ .

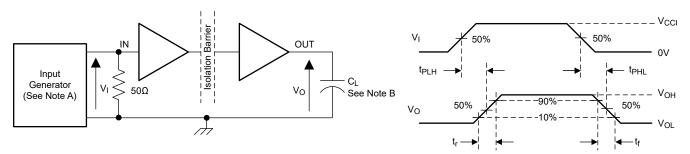

## 5.15 Switching Characteristics—5V Supply

V<sub>CC1</sub> = V<sub>CC2</sub> = 5V ±10% (over recommended operating conditions unless otherwise noted)

|                                     | PARAMETER                                                                  | TEST CONDITIONS                                                        | MIN | TYP  | MAX | UNIT |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | See Figure 6-1                                                         | 6   | 11   | 16  | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | See Figure 0-1                                                         |     | 0.55 | 4.1 | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew time <sup>(2)</sup>                         | Same-direction channels                                                |     |      | 2.5 | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew time <sup>(3)</sup>                                      |                                                                        |     |      | 4.5 | ns   |

| t <sub>r</sub>                      | Output signal rise time                                                    | - See Figure 6-1                                                       |     | 1.7  | 3.9 | ns   |

| t <sub>f</sub>                      | Output signal fall time                                                    | Gee i igure 0-1                                                        |     | 1.9  | 3.9 | ns   |

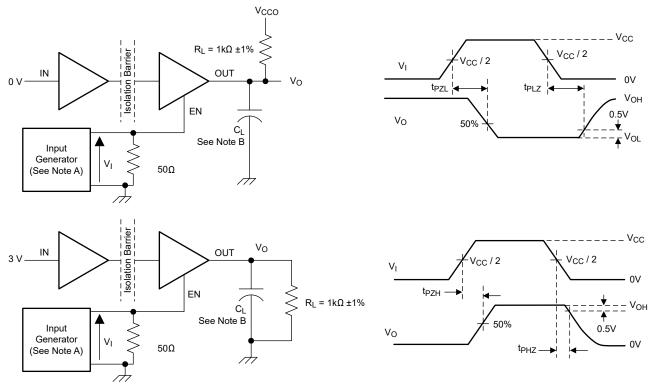

| t <sub>PHZ</sub>                    | Disable propagation delay, high-to-high impedance output                   |                                                                        |     | 12   | 20  | ns   |

| t <sub>PLZ</sub>                    | Disable propagation delay, low-to-high impedance output                    |                                                                        |     | 12   | 20  | ns   |

|                                     | Enable propagation delay, high impedance-to-high output for ISO7841        | See Figure 6.2                                                         |     | 10   | 20  | ns   |

| t <sub>PZH</sub>                    | Enable propagation delay, high impedance-to-high output for ISO7841F       | - See Figure 6-2                                                       |     | 2    | 2.5 | μs   |

|                                     | Enable propagation delay, high impedance-to-low output for ISO7841         |                                                                        |     | 2    | 2.5 | μs   |

| t <sub>PZL</sub>                    | Enable propagation delay, high impedance-to-low output for ISO7841F        |                                                                        |     | 10   | 20  | ns   |

| t <sub>fs</sub>                     | Default output delay time from input power loss                            | Measured from the time V <sub>CC</sub> goes below 1.7V. See Figure 6-3 |     | 0.2  | 9   | μs   |

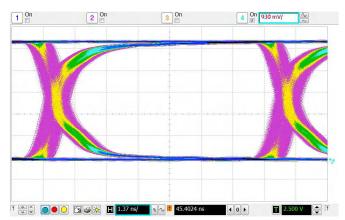

| t <sub>ie</sub>                     | Time interval error                                                        | 2 <sup>16</sup> – 1 PRBS data at 100Mbps                               |     | 0.90 |     | ns   |

<sup>(1)</sup> Also known as pulse skew.

<sup>(2)</sup> t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

<sup>(3)</sup>  $t_{sk(pp)}$  is the magnitude of the difference in propagation delay times between any terminals of different devices switching in the same direction while operating at identical supply voltages, temperature, input signals and loads.

## 5.16 Switching Characteristics—3.3V Supply

V<sub>CC1</sub> = V<sub>CC2</sub> = 3.3V ±10% (over recommended operating conditions unless otherwise noted)

|                                     | PARAMETER                                                                  | TEST CONDITIONS                                                        | MIN | TYP  | MAX | UNIT |

|-------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|-----|------|-----|------|

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation delay time                                                     | See Figure 6-1                                                         | 6   | 10.8 | 16  | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup>  t <sub>PHL</sub> - t <sub>PLH</sub> | See Figure 6-1                                                         |     | 0.7  | 4.2 | ns   |

| t <sub>sk(o)</sub>                  | Channel-to-channel output skew time(2)                                     | Same-direction channels                                                |     |      | 2.2 | ns   |

| t <sub>sk(pp)</sub>                 | Part-to-part skew time                                                     |                                                                        |     |      | 4.5 | ns   |

| t <sub>r</sub>                      | Output signal rise time                                                    | - See Figure 6-1                                                       |     | 0.8  | 3   | ns   |

| t <sub>f</sub>                      | Output signal fall time                                                    | - See Figure 0-1                                                       |     | 0.8  | 3   | ns   |

| t <sub>PHZ</sub>                    | Disable propagation delay, high-to-high impedance output                   |                                                                        |     | 17   | 32  | ns   |

| t <sub>PLZ</sub>                    | Disable propagation delay, low-to-high impedance output                    |                                                                        |     | 17   | 32  | ns   |

|                                     | Enable propagation delay, high impedance-to-high output for ISO7841        | See Figure 6-2                                                         |     | 17   | 32  | ns   |

| t <sub>PZH</sub>                    | Enable propagation delay, high impedance-to-high output for ISO7841F       | See Figure 0-2                                                         |     | 2    | 2.5 | μs   |

|                                     | Enable propagation delay, high impedance-to-low output for ISO7841         |                                                                        |     | 2    | 2.5 | μs   |

| t <sub>PZL</sub>                    | Enable propagation delay, high impedance-to-low output for ISO7841F        |                                                                        |     | 17   | 32  | ns   |

| t <sub>fs</sub>                     | Default output delay time from input power loss                            | Measured from the time V <sub>CC</sub> goes below 1.7V. See Figure 6-3 |     | 0.2  | 9   | μs   |

| t <sub>ie</sub>                     | Time interval error                                                        | 2 <sup>16</sup> – 1 PRBS data at 100Mbps                               |     | 0.91 |     | ns   |

<sup>(1)</sup> Also known as Pulse Skew.

Submit Document Feedback

Copyright © 2024 Texas Instruments Incorporated

<sup>(2)</sup> t<sub>sk(o)</sub> is the skew between outputs of a single device with all driving inputs connected together and the outputs switching in the same direction while driving identical loads.

## 5.17 Switching Characteristics—2.5V Supply

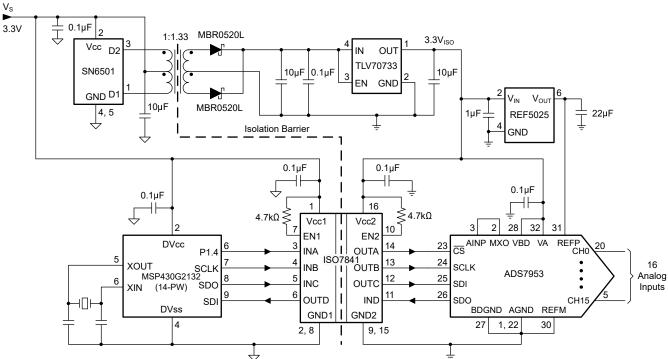

V<sub>CC1</sub> = V<sub>CC2</sub> = 2.5V ±10% (over recommended operating conditions unless otherwise noted)