HD3SS460

SLLSEM7D - JANUARY 2015-REVISED JANUARY 2017

## HD3SS460 4 x 6 Channels USB Type-C<sup>™</sup> Alternate Mode MUX

#### 1 Features

Texas

Instruments

- Provides MUX Solution for USB Type-C<sup>™</sup> Ecosystem Including Alternate Mode (AM)

- **Provides Wide Channel Selection Choices** Including USBSS and 2 Ch AM, 4 Ch AM

- Compatible with 5 Gbps USB3.1 Gen 1 and AM Including 5.4 Gbps DisplayPort 1.2a

- Compatible for Source/Host and Sink/Device Applications

- Provides Cross-point MUX for Low Speed SBU Pins

- Bidirectional "Mux/De-Mux" Differential Switch

- Supports Common Mode Voltage 0-2 V

- Low Power with  $1-\mu A$  Shutdown and 0.6 mA Active

- Single Supply Voltage VCC of 3.3 V ±10%

- Industrial Temperature Range of -40 to 85°C

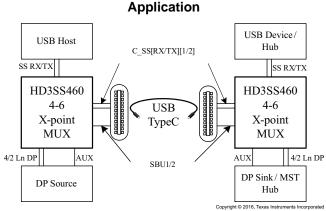

#### 2 Applications

- Flippable USB Type-C<sup>™</sup> Ecosystem

- Tablets, Laptops, Monitors, Phones

- **USB Host and Devices**

- **Docking Stations**

CRX1

CTX1

CTX

CRX2

AMSEL

POL

CSBU1

CSBU2

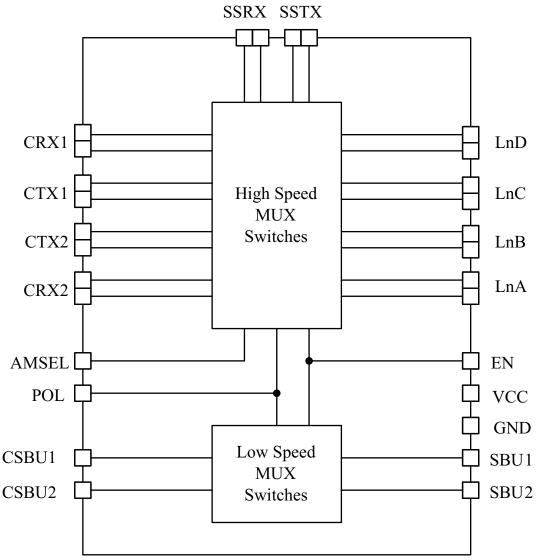

## 3 Description

The HD3SS460 is a high-speed bi-directional passive switch in mux or demux configurations. Based on control pin POL the device provides switching to accommodate connector flipping. The device also provides muxing between 2Ch Data / 2Ch Video and all 4Ch Video based on control pin AMSEL.

The device also provides cross points MUX for low speed pins as needed in flippable connector implementation.

The HD3SS460 is a generic analog differential passive switch that can work for any high speed interface applications as long as it is biased at a common mode voltage range of 0-2V and has differential signaling with differential amplitude up to 1800mVpp. It employs an adaptive tracking that ensures the channel remains unchanged for entire common mode voltage range.

Excellent dynamic characteristics of the device allow high speed switching with minimum attenuation to the signal eye diagram with very little added jitter. It consumes <2 mW of power when operational and <5µW in shutdown mode, exercisable by EN pin.

| Device Information <sup>(1)</sup> |  |

|-----------------------------------|--|

|-----------------------------------|--|

| PART NUMBER | PACKAGE        | BODY SIZE (NOM)   |  |  |  |

|-------------|----------------|-------------------|--|--|--|

| HD3SS460    |                | 2.50              |  |  |  |

| HD3SS460I   | QFN (RHR) (28) | 3.50 mm × 5.50 mm |  |  |  |

| HD3SS460    |                | 2 50 mm + 4 50 mm |  |  |  |

| HD3SS460I   | QFN (RNH) (30) | 2.50 mm × 4.50 mm |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### Simplified Schematic SSRX SSTX

High Speed

MUX

Switches

Low Speed

MÛX

Switches

LnD

LnC

LnB

LnA

VCC

SBU2

EN

Ċ.

ф GND

Ċ1 SBU1

Copyright @ 2016, Texas Ins

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

## **Table of Contents**

| 1 | Feat | ures 1                                             |

|---|------|----------------------------------------------------|

| 2 | Арр  | lications 1                                        |

| 3 | Des  | cription 1                                         |

| 4 | Revi | ision History 2                                    |

| 5 | Devi | ice Comparison Table 4                             |

| 6 | Pin  | Configuration and Functions 5                      |

| 7 | Spe  | cifications6                                       |

|   | 7.1  | Absolute Maximum Ratings 6                         |

|   | 7.2  | ESD Ratings6                                       |

|   | 7.3  | Recommended Operating Conditions 6                 |

|   | 7.4  | Thermal Information 6                              |

|   | 7.5  | Electrical Characteristics7                        |

|   | 7.6  | High Speed Port Performance Parameters             |

|   | 7.7  | High Speed Signal Path Switching Characteristics 8 |

| 8 | Deta | niled Description 10                               |

|   | 8.1  | Overview 10                                        |

|   | 8.2  | Functional Block Diagram 10                        |

|    | 8.3  | Feature Description 11                             |

|----|------|----------------------------------------------------|

|    | 8.4  | Device Functional Modes 11                         |

| 9  | Арр  | lication and Implementation 14                     |

|    | 9.1  | Application Information 14                         |

|    | 9.2  | USB SS and DP as Alternate Mode 14                 |

| 10 | Pov  | ver Supply Recommendations 23                      |

| 11 | Lay  | out 24                                             |

|    | 11.1 | Layout Guidelines 24                               |

|    | 11.2 | Layout Example 25                                  |

| 12 | Dev  | ice and Documentation Support 27                   |

|    | 12.1 | Receiving Notification of Documentation Updates 27 |

|    | 12.2 | Community Resources 27                             |

|    | 12.3 | Trademarks 27                                      |

|    | 12.4 | Electrostatic Discharge Caution 27                 |

|    | 12.5 | Glossary 27                                        |

| 13 |      | hanical, Packaging, and Orderable                  |

|    | Info | rmation 27                                         |

|    |      |                                                    |

## 4 Revision History

2

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cł | hanges from Revision C (December 2016) to Revision D | Page |

|----|------------------------------------------------------|------|

| •  | Deleted R187 from Figure 16                          | 21   |

| •  | Deleted R187 from Figure 19.                         | 23   |

#### Changes from Revision B (June 2016) to Revision C

| • | Added QFN (RNH) (30) to the Device Information table                                                                                                                | . 1 |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Added the RNH package option to the Device Comparison Table table                                                                                                   | . 4 |

| • | Added the RNH package option to the Pin Configuration and Functions section                                                                                         | . 5 |

| • | Changed the Description of pins LnBn, p, LnCn, p, LnDn, p, SSTXn, p, and SSRXn, p From: positive, negative To: negative, positive in the <i>Pin Functions</i> table | . 5 |

| • | Changed the Supply voltage MIN value From: 3.0 V To: 2.7 V in the Recommended Operating Conditions table                                                            | . 6 |

| • | Added the RNH package option to the Thermal Information table                                                                                                       | . 6 |

| • | Changed V <sub>IH</sub> to include a separate line entry for POL pin in the <i>Electrical Characteristics</i> table                                                 | . 7 |

|   |                                                                                                                                                                     |     |

#### Changes from Revision A (March 2015) to Revision B

| <ul> <li>Added Figure 5</li> <li>Added Figure 6</li> <li>Deleted Table <i>Pin Assignments for DP Source Pins and DP Sink Pins</i> in the <i>Detailed Design Procedure</i> section</li> <li>Added Table 2, Table 3, Table 4, and Table 5</li> <li>Added Figure 8 through Figure 13</li> <li>Changed image for Figure 16</li> <li>21</li> <li>Changed image for Figure 19</li> </ul> | • | Changed text and Figure 3, Figure 4 in the USB SS and DP as Alternate Mode section for clarity.            | 14 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>Deleted Table <i>Pin Assignments for DP Source Pins and DP Sink Pins</i> in the <i>Detailed Design Procedure</i> section</li></ul>                                                                                                                                                                                                                                        | • | Added Figure 5                                                                                             | 15 |

| <ul> <li>Added Table 2, Table 3, Table 4, and Table 5</li></ul>                                                                                                                                                                                                                                                                                                                    | • | Added Figure 6                                                                                             | 16 |

| <ul> <li>Added Figure 8 through Figure 13</li></ul>                                                                                                                                                                                                                                                                                                                                | • | Deleted Table Pin Assignments for DP Source Pins and DP Sink Pins in the Detailed Design Procedure section | 17 |

| Changed image for Figure 16 21                                                                                                                                                                                                                                                                                                                                                     | • | Added Table 2, Table 3, Table 4, and Table 5                                                               | 17 |

|                                                                                                                                                                                                                                                                                                                                                                                    | • | Added Figure 8 through Figure 13                                                                           | 17 |

| Changed image for Figure 19                                                                                                                                                                                                                                                                                                                                                        | • | Changed image for Figure 16                                                                                | 21 |

|                                                                                                                                                                                                                                                                                                                                                                                    | • | Changed image for Figure 19                                                                                | 23 |

## www.ti.com

ISTRUMENTS

EXAS

#### Page

#### Page

SLLSEM7D - JANUARY 2015 - REVISED JANUARY 2017

Changes from Original (January 2015) to Revision A

Page

• Added full data sheet specification complement

6

## 5 Device Comparison Table<sup>(1)</sup>

| OPERATING<br>TEMPERATURE (°C) | PART NUMBER  | PINS | TOP-SIDE MARKING |

|-------------------------------|--------------|------|------------------|

| 0 to 70 HD3SS460RHR           |              | 28   | 3SS460           |

| -40 to 85 HD3SS460IRHR        |              | 28   | 3SS460I          |

| 0 to 70                       | HD3SS460RNH  | 30   | 460RNH           |

| -40 to 85                     | HD3SS460IRNH | 30   | 460IRNH          |

(1) For all available packages, see the orderable addendum at the end of the data sheet. Package drawings, thermal data, and symbolization are available at www.ti.com/packaging

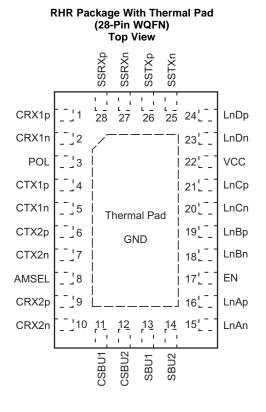

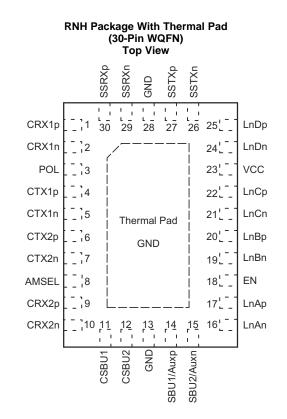

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN      |            |             |                  |                                                    |  |

|----------|------------|-------------|------------------|----------------------------------------------------|--|

| NAME     | RHR<br>NO. | RNH<br>NO.  |                  | DESCRIPTION                                        |  |

| VCC      | 22         | 23          | Р                | Power                                              |  |

| GND      | PAD        | 13, 28, PAD | G                | Ground                                             |  |

| POL      | 3          | 3           | Input            | rovides MUX control (Table 1)                      |  |

| AMSEL    | 8          | 8           | 3-Level<br>Input | rovides MUX configurations (Table 1)               |  |

| EN       | 17         | 18          | 3-Level<br>Input | Enable signal; also provides MUX control (Table 1) |  |

| CRX1p, n | 1, 2       | 1, 2        | I/O              | High Speed Signal Port CRX1 positive, negative     |  |

| CTX1p, n | 4, 5       | 4, 5        | I/O              | High Speed Signal Port CTX1 positive, negative     |  |

| CTX2p, n | 6, 7       | 6, 7        | I/O              | High Speed Signal Port CTX2 positive, negative     |  |

| CRX2p, n | 9, 10      | 9, 10       | I/O              | High Speed Signal Port CRX2 positive, negative     |  |

| LnAn, p  | 15, 16     | 16, 17      | I/O              | High Speed Signal Port LnA positive, negative      |  |

| LnBn, p  | 18, 19     | 19, 20      | I/O              | High Speed Signal Port LnB negative, positive      |  |

| LnCn, p  | 20, 21     | 21, 22      | I/O              | High Speed Signal Port LnC negative, positive      |  |

| LnDn, p  | 23, 24     | 24, 25      | I/O              | High Speed Signal Port LnD negative, positive      |  |

| SSTXn, p | 25, 26     | 26, 27      | I/O              | High Speed Signal Port SSTX negative, positive     |  |

| SSRXn, p | 27, 28     | 29, 30      | I/O              | High Speed Signal Port SSRX negative, positive     |  |

| CSBU1, 2 | 11, 12     | 11, 12      | I/O              | Low Speed Signal Port CSBU 1, 2                    |  |

| SBU1, 2  | 13, 14     | 14, 15      | I/O              | Low Speed Signal Port SBU 1, 2                     |  |

(1) High speed data ports (CRX[1/2][p/n], Ln[A-D][p,n], and SS[T/R]X[p/n]) incorporate 20kΩ pull down resistors that are switched in when a port is not selected and switched out when the port is selected.

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                                                                                      | MIN  | MAX | UNIT |

|--------------------------------------------------------------------------------------|------|-----|------|

| Supply Voltage, VCC                                                                  | -0.5 | 4   | V    |

| Differential High Speed I/O Voltages, C[R/T]X[1/2][p/n], Ln[A-D][p/n], SS[R/T]X[p/n] | -0.5 | 2.5 | V    |

| Low Speed I/O Voltages, CSBU[1/2], SBU[1/2]                                          | -0.5 | 4   | V    |

| Control signal voltages, POL, AMSEL, EN                                              | -0.5 | 4   | V    |

| Storage temperature, T <sub>stg</sub>                                                | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                                                                   |                                                                              | VALUE | UNIT |

|--------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±4000                                                                        | V     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                           | Charged-device model (CDM), per JEDEC specification JESD22- $\rm C101^{(2)}$ | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                      |           | MIN | NOM | MAX | UNIT |  |

|-----------------|--------------------------------------|-----------|-----|-----|-----|------|--|

| V <sub>CC</sub> | Supply voltage                       |           | 2.7 | 3.3 | 3.6 | V    |  |

| т               | Operating free air temperature       | HD3SS460  | 0   | 25  | 70  | °C   |  |

| IA              | Operating free air temperature       | HD3SS460I | -40 | 25  | 85  |      |  |

| V <sub>CM</sub> | High speed port common mode voltage  |           | 0   |     | 2   |      |  |

| V <sub>IN</sub> | Low Speed signal voltage             |           | 0   |     | VCC | ;    |  |

| Vdiff           | High speed port differential voltage |           | 0   |     | 1.8 | Vpp  |  |

### 7.4 Thermal Information

|                       |                                              | HD3       | HD3SS460  |      |  |

|-----------------------|----------------------------------------------|-----------|-----------|------|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | QFN (RNH) | QFN (RHR) | UNIT |  |

|                       |                                              | 30 PINS   | 28 PINS   |      |  |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 51.6      | 44.0      | °C/W |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 37.5      | 34.8      | °C/W |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 17.5      | 14.7      | °C/W |  |

| ΨJT                   | Junction-to-top characterization parameter   | 0.7       | 0.7       | °C/W |  |

| Ψјв                   | Junction-to-board characterization parameter | 17.3      | 24.5      | °C/W |  |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 6.8       | 6.9       | °C/W |  |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

typical values for all parameters are at V\_{DD} = 3.3 V and T\_A = 25 ^{\circ}C (unless otherwise noted)

|                                   | PARAMETER                                                                             | TEST CONDITIONS                                                                                                                                                         | MIN                     | TYP                | MAX                     | UNIT |

|-----------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|-------------------------|------|

| V <sub>IL</sub>                   | Input low voltage, control pins POL, AMSEL, EN                                        |                                                                                                                                                                         | -0.1                    |                    | 0.4                     |      |

| VIH                               | Input high voltage, control pins<br>AMSEL, EN                                         |                                                                                                                                                                         | V <sub>CC</sub> -0.4    |                    | V <sub>CC</sub> +0.1    | V    |

|                                   | Input high voltage, control pins POL                                                  |                                                                                                                                                                         | 1.7                     |                    | V <sub>CC</sub> +0.1    |      |

| V <sub>IM</sub>                   | Input mid-level voltage, control pins<br>AMSEL, EN                                    |                                                                                                                                                                         | V <sub>CC/</sub> 2 –0.3 | V <sub>CC</sub> /2 | V <sub>CC</sub> /2 +0.3 |      |

| I <sub>LK-DIFF-ACTIVE</sub>       | Leakage current on active<br>differential IO pins, VCC = 3.6 V,<br>pin at 0 or 2.4 V. |                                                                                                                                                                         |                         |                    | 1                       |      |

| I <sub>LK-DIFF-</sub><br>INACTIVE | Leakage current on inactive<br>differential IO pins, VCC = 3.6V, pin<br>at 2.4 V.     |                                                                                                                                                                         |                         |                    | 150                     |      |

| IIH                               | Input high current, control pins<br>POL, AMSEL, EN and signal pins<br>CSBU1/2, SBU1/2 |                                                                                                                                                                         |                         |                    | 1                       | μΑ   |

| I <sub>IL</sub>                   | Input low current, control pins POL,<br>AMSEL, EN and signal pins<br>CSBU1/2, SBU1/2  |                                                                                                                                                                         |                         |                    | 1                       |      |

| I <sub>IM</sub>                   | Input mid-level current, control pins<br>AMSEL, EN                                    |                                                                                                                                                                         |                         |                    | 1                       |      |

| I <sub>OFF</sub>                  | Device shutdown current                                                               |                                                                                                                                                                         |                         | 1                  | 5                       |      |

| I <sub>DD</sub>                   | Device active current, EN=H or M                                                      |                                                                                                                                                                         |                         | 0.6                | 0.9                     | mA   |

| R <sub>ON(HS)</sub>               | Switch ON resistance for high speed differential signals                              | $V_{CC} = 3.3 \text{ V}, V_{CM} = 0.2 \text{ V}, I_{O} = -8 \text{ mA}$                                                                                                 |                         | 8                  | 14                      |      |

| R <sub>ON(LS)</sub>               | Switch ON resistance for low speed signals                                            | $V_{CC} = 3.3 \text{ V}, V_{CM} = 0.2 \text{ V},$<br>$I_{O} = -8 \text{ mA}$                                                                                            |                         | 12                 |                         | Ω    |

| R <sub>FLAT(ON,HS)</sub>          | High speed differential signals' ON resistance flatness for a channel                 | $\begin{array}{l} (R_{ON(MAX)} - R_{ON(MIN)}) \text{ over } V_{CM} \\ \text{range } V_{CC} = 3.3 \ V, \ V_{CM} = 0\text{-}2 \ V, \\ I_{O} = \text{-}8 \ mA \end{array}$ |                         |                    | 1.5                     |      |

| C <sub>ON(HS)</sub>               | High speed differential signals' input capacitance                                    |                                                                                                                                                                         |                         |                    | 1                       | pF   |

TRUMENTS

XAS

### 7.6 High Speed Port Performance Parameters

under recommended operating conditions; R<sub>LOAD</sub>, R<sub>SC</sub> = 50  $\Omega$  (unless otherwise noted)

|                   | PARAMET                                               | MIN TYP          | MAX  | UNIT |     |  |

|-------------------|-------------------------------------------------------|------------------|------|------|-----|--|

|                   |                                                       | 100 Mhz SS Paths | -23  |      |     |  |

| DI                | Differential return loss                              | 2.5 Ghz SS Paths | -9   |      |     |  |

| RL                | Differential return loss                              | 100 MHz AM Paths | -23  |      |     |  |

|                   |                                                       | 2. 7GHz AM Paths | -13  |      |     |  |

|                   |                                                       | 100 Mhz SS Paths | -0.7 |      |     |  |

| IL                | Differential insertion loss                           | 2.5 Ghz SS Paths | -1.6 |      |     |  |

| IL                | Differential insertion loss                           | 100 MHz AM Paths | -0.7 |      |     |  |

|                   |                                                       | 2.7 GHz AM Paths | -1.4 |      |     |  |

|                   |                                                       | 100 Mhz          | -50  | dB   | dB  |  |

| OI                | Differential off isolation                            | 2.5 Ghz          | -26  |      |     |  |

|                   |                                                       | 2.7 GHz          | -25  |      |     |  |

|                   |                                                       | 100 Mhz          | -80  |      |     |  |

|                   | Differential cross talk, Between<br>CRX1/2 and CTX1/2 | 2.5 Ghz          | -30  |      |     |  |

| Vtalle            |                                                       | 2.7 Ghz          | -28  |      |     |  |

| Xtalk             | Differential cross talk, Between                      | 100 Mhz          | -50  |      |     |  |

|                   | CRX1 and CRX2 or CTX1 and                             | 2.5 Ghz          | -26  |      |     |  |

|                   | CTX2                                                  | 2.7 Ghz          | -25  |      |     |  |

| BW <sub>SS</sub>  | Differential -3 dB BW SS Paths                        |                  | 4.2  | 4.2  |     |  |

| BW <sub>AM</sub>  | Differential -3 dB BW AM Paths                        |                  | 5.4  |      | GHz |  |

| BW <sub>SBU</sub> | Low-speed switch -3 dB BW                             |                  | 500  |      | MHz |  |

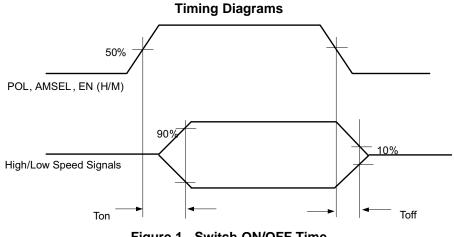

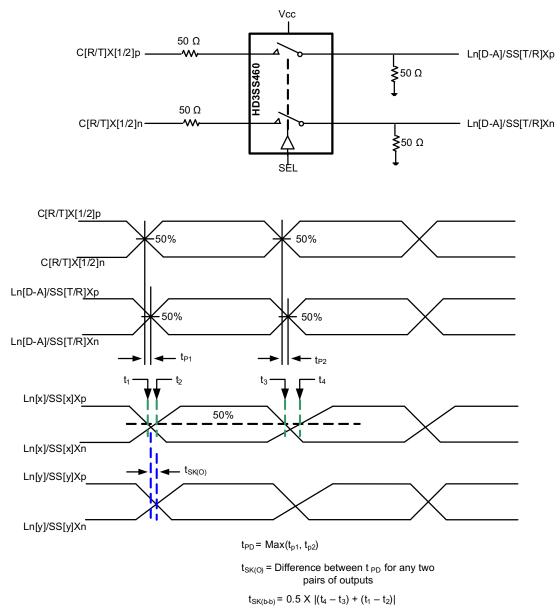

## 7.7 High Speed Signal Path Switching Characteristics

|                      | PARAMETER                                                         | TEST CONDITION                                   | MIN | ТҮР | MAX | UNIT |

|----------------------|-------------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| t <sub>PD</sub>      | Switch propagation delay                                          |                                                  |     |     | 100 |      |

| t <sub>SK(O)</sub>   | Inter-Pair output skew (CH-CH)                                    | $R_{SC}$ and $R_{LOAD}$ = 50 $\Omega$ , Figure 2 |     |     | 50  | ps   |

| t <sub>SK(b-b)</sub> | Intra-Pair output skew (bit-bit)                                  |                                                  | 5   |     | 5   |      |

| t <sub>ON</sub>      | Control signals POL, AMSEL and EN (H/M toggle) to switch ON time  | D and D 50.0 Figure 4                            |     |     | 3   |      |

| t <sub>OFF</sub>     | Control signals POL, AMSEL and EN (H/M toggle) to switch OFF time | $R_{SC}$ and $R_{LOAD} = 50 \Omega$ , Figure 1   |     |     | 1   | μs   |

Figure 2. Propagation Delay and Skew

### 8 Detailed Description

#### 8.1 Overview

The HD3SS460 is a high-speed bi-directional passive 4-6 cross-point switch in mux or demux configurations. Based on control pin POL the device provides switching to accommodate USB Type-C plug flipping. The device provides multiple signal switching options that allow system implementation flexibility.

The HD3SS460 is a generic analog, differential passive switch that can work for any high speed interface applications as long as it is biased at a common mode voltage range of 0-2 V and has differential signaling with differential amplitude up to 1800 mVpp. It employs an adaptive tracking that ensures the channel remains unchanged for entire common mode voltage range

Excellent dynamic characteristics of the device allow high speed switching with minimum attenuation to the signal eye diagram with very little added jitter.

#### 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 High Speed Differential Signal Switching

Based on control pin AMSEL the device provides muxing options of:

- 1. 1 port (RX and TX) USB3.1 SS data / 2Ch video (or any other Alternate Mode data)

- 2. All 4Ch video (or any other Alternate Mode data)

- 3. 1 port (RX and TX) USB3.1 SS data

- 4. 1 port (RX and TX) USB3.1 SS data / 2Ch video (or any other Alternate Mode data) with option of choosing video from two different source/sink

- 5. 1 port (RX and TX) USB3.1 SS data / 2Ch video (or any other Alternate Mode data) with option of choosing video 2 Ln Video or 1 Ln Video from two different source/sink

#### 8.3.2 Low Speed SBU Signal Switching

The device also provides cross point muxing for low speed SBU signals as needed in USB Type-C flippable connector implementation. The device provides the option to choose the USB only implementation where SBU ports are in tri-state.

#### 8.3.3 Output Enable and Power Savings

The HD3SS460 has two power modes, active/normal operating mode and standby/shutdown mode. During standby mode, the device consumes very little current to save the maximum power. To enter standby mode, the EN control pin is pulled low and must remain low. For active/normal operation, the EN control pin should be pulled high to VDD through a resistor or dynamically controlled to switch between H or M.

HD3SS460 consumes <2 mW of power when operational and <5  $\mu$ W in shutdown mode, exercisable by the EN pin.

### 8.4 Device Functional Modes

### 8.4.1 Device High Speed Switch Control Modes

#### Table 1. MUX Control for High Speed and Low Speed SBU Channels

| POL | AMSEL | EN | CONFIGURATIONS                  | HIGH SPEED SIGNAL<br>FLOW <sup>(1)</sup>                  | SBU SIGNAL FLOW                |

|-----|-------|----|---------------------------------|-----------------------------------------------------------|--------------------------------|

| L   | L     | н  | 2CH USBSS + 2CH AM<br>(Normal)  | SSRX SSTX<br>CRX1 LnD<br>CTX1 LnC<br>CTX2 LnB<br>CRX2 LnA | CSBU1<br>CSBU2<br>SBU2<br>SBU2 |

| н   | L     | н  | 2CH USBSS + 2CH AM<br>(Flipped) | SSRX SSTX<br>CRX1<br>CTX1<br>CTX2<br>CRX2<br>CRX2<br>CRX2 | CSBU1<br>CSBU2<br>SBU2<br>SBU2 |

(1) All positive signals connect to positive and negative to negative

HD3SS460

SLLSEM7D - JANUARY 2015 - REVISED JANUARY 2017

## **Device Functional Modes (continued)**

## Table 1. MUX Control for High Speed and Low Speed SBU Channels (continued)

| POL | AMSEL | EN | CONFIGURATIONS                 | HIGH SPEED SIGNAL<br>FLOW <sup>(1)</sup>                              | SBU SIGNAL FLOW                  |

|-----|-------|----|--------------------------------|-----------------------------------------------------------------------|----------------------------------|

| L   | н     | Н  | 4CH AM (Normal)                | SSRX SSTX<br>CRX1 LnD<br>CTX1 LnC<br>CTX2 LnB<br>CRX2 LnA             | CSBU1 SBU1<br>CSBU2 SBU2         |

| н   | Н     | Н  | 4CH AM (Flipped)               | SSRX SSTX<br>CRX1<br>CTX1<br>CTX2<br>CRX2<br>LnD<br>LnC<br>LnB<br>LnA | CSBU1<br>CSBU2<br>SBU2<br>SBU2   |

| L   | М     | Н  | 2CH USBSS (Normal)             | SSRX SSTX<br>CRX1 LnD<br>CTX1 LnC<br>CTX2 LnB<br>CRX2 LnA             | All Low Speed SBU<br>Ports HighZ |

| н   | М     | Н  | 2CH USBSS (Flipped)            | SSRX SSTX<br>CRX1<br>CTX1<br>CTX2<br>CRX2<br>LnD<br>LnC<br>LnB<br>LnA | All Low Speed SBU<br>Ports HighZ |

| L   | М     | М  | 2CH USBSS + 2CH AM<br>(Normal) | SSRX SSTX<br>CRX1 LnD<br>CTX1 LnC<br>CTX2 LnB<br>CRX2 LnA             | CSBU1 SBU1<br>CSBU2 SBU2         |

#### HD3SS460 SLLSEM7D – JANUARY 2015 – REVISED JANUARY 2017

www.ti.com

## **Device Functional Modes (continued)**

| POL | AMSEL | EN | CONFIGURATIONS                                     | HIGH SPEED SIGNAL<br>FLOW <sup>(1)</sup>                                      | SBU SIGNAL FLOW                  |

|-----|-------|----|----------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------|

| Н   | М     | М  | 2CH USBSS + 2CH AM<br>(Flipped)                    | SSRX SSTX<br>CRX1<br>CTX1<br>CTX2<br>CRX2<br>CRX2<br>LnD<br>LnC<br>LnB<br>LnA | CSBU1<br>CSBU2<br>SBU2<br>SBU2   |

| L   | L     | М  | 2CH USBSS + 2CH AM from<br>alternate GPU (Normal)  | SSRX SSTX<br>CRX1 LnD<br>CTX1 LnC<br>CTX2 LnB<br>CRX2 LnA                     | CSBU1 SBU1<br>CSBU2 SBU2         |

| Н   | L     | М  | 2CH USBSS + 2CH AM from<br>alternate GPU (Flipped) | SSRX SSTX<br>CRX1<br>CTX1<br>CTX2<br>CRX2<br>CRX2<br>CRX2                     | CSBU1<br>CSBU2<br>SBU2<br>SBU2   |

| L   | Н     | М  | Reserved                                           | Reserved                                                                      | Reserved                         |

| Н   | Н     | М  | Reserved                                           | Reserved                                                                      | Reserved                         |

| x   | х     | L  | All High Speed Ports HighZ                         | All High Speed Ports HighZ                                                    | All Low Speed SBU<br>Ports HighZ |

## Table 1. MUX Control for High Speed and Low Speed SBU Channels (continued)

### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

HD3SS460 can be utilized for a wide range of muxing needs. This is general purpose passive cross-point switch. The channels have independent adaptive common mode tracking allowing flexibility. As long as recommended electrical use conditions are met the device can be used number of ways as described in Table 1.

#### NOTE

HD3SS460 does not provide common mode biasing for the channel. Therefore it is required that the device is biased from either side for all active channels.

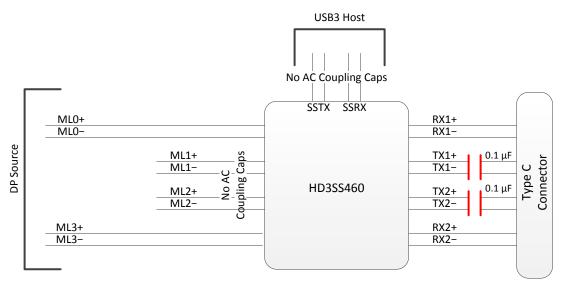

### 9.2 USB SS and DP as Alternate Mode

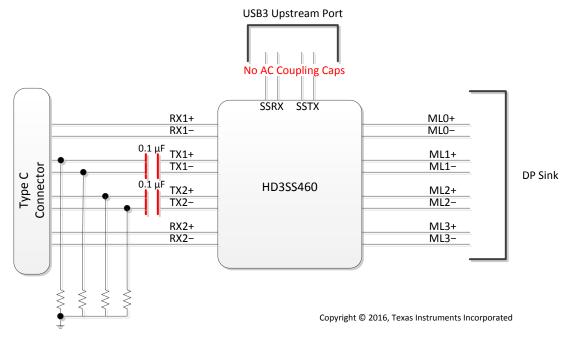

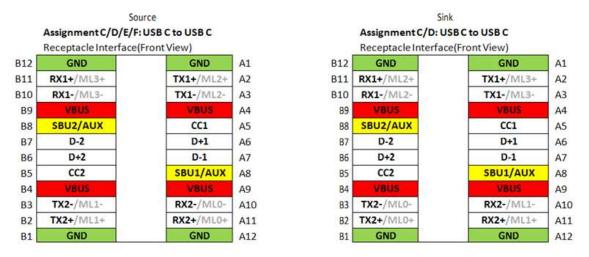

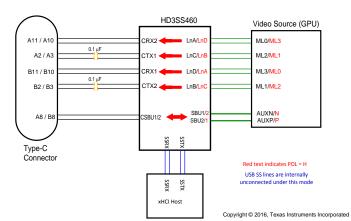

HD3SS460 can be used USB Type-C ecosystem with DP as alternate mode in two distinct application configurations – one is for DP Source/USB Host, the other one for the DP Sink/USB Device/Dock. Figure 3 and Figure 4 illustrate typical application block diagrams for these two cases. Detail schematics are illustrated in Detailed Design Procedure section. Other applications and or use cases possible where these examples can be used as general guidelines.

Figure 3 and Figure 4 depict the AC coupling capacitor placement examples. TI recommends placing the capacitors as shown in the illustrations for the backward compatibility and interoperability purposes as some of the existing USB systems may present Vcm, exceeding the typical range of 0–2 V on SS differential pairs.

Copyright © 2016, Texas Instruments Incorporated

#### Figure 3. Block Diagram for a Type C Interface Using DP as Alternate Mode – Source/Host

#### USB SS and DP as Alternate Mode (continued)

Figure 4. Diagram for a Type C Interface Using DP as Alternate Mode – Sink/Device/Dock

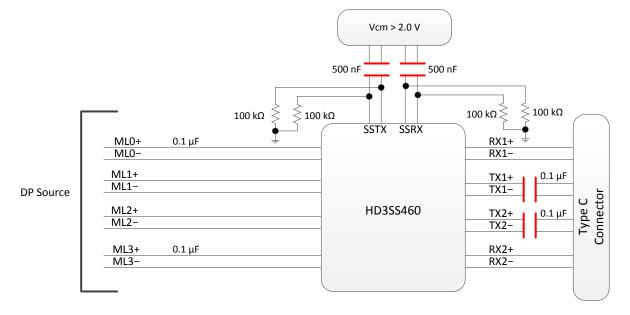

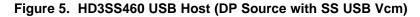

Figure 5 and Figure 6 depict the AC coupling capacitor recommendations in case the upstream or downstream port connected internally to the HD3SS460 presents Vcm greater than 2 V.

Copyright © 2016, Texas Instruments Incorporated

NSTRUMENTS

**FEXAS**

## USB SS and DP as Alternate Mode (continued)

### 9.2.1 Design Requirements

| DESIGN PARAMETERS     | EXAMPLE VALUES                                                                                                                   |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|

| VCC                   | 3.3 V                                                                                                                            |

| Decoupling capacitors | 0.1 µF                                                                                                                           |

| AC Capacitors         | 75-200nF (100nF shown) USBSS TX p and n lines require AC capacotprs. Alternate mode signals may or may not require AC capacitors |

| Control pins          | Controls pins can be dynamically controlled or pin-strapped. The POL signal is controlled by CC logic in the Type-C ecosystem.   |

Submit Documentation Feedback

16

#### 9.2.2 Detailed Design Procedure

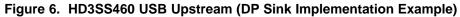

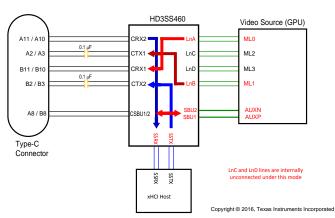

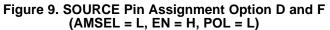

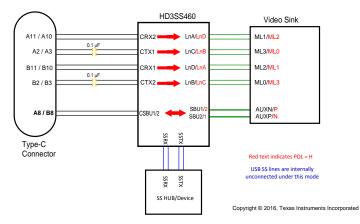

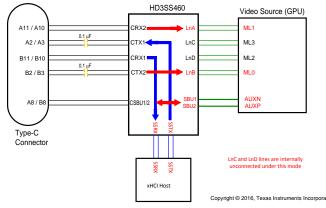

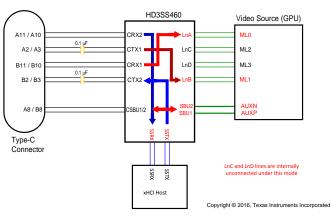

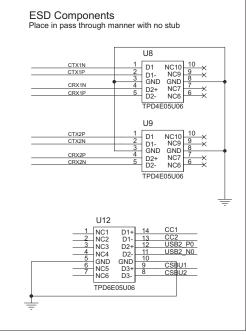

The reference schematics shown in this document are based upon the pin assignment defined in the Alternate mode over Type C specification as shown in Figure 7 below.

Figure 7. Pin Assignment – Alternate Mode Over Type C

Table 2 represents the example pin mapping to HD3SS460 for the DP Source pin assignments C, D, E and F, DP Sink pin assignments C and D.

| RECEPTACLE PIN | 460 PIN MAPPING TO | 460 PIN MAPPING TO DP SOURCE (GPU) |            |  |

|----------------|--------------------|------------------------------------|------------|--|

| NUMBER         | TYPE C CONNECTOR   | POL = L                            | POL = H    |  |

| A11/10         | CRX2               | LnA(ML0)                           | LnD(ML3)   |  |

| A2/3           | CTX1               | LnC(ML2)                           | LnB(ML1)   |  |

| B11/10         | CRX1               | LnD(ML3)                           | LnA(ML0)   |  |

| B2/3           | CTX2               | LnB(ML1)                           | LnC(ML2)   |  |

| A8             | CSBU1              | SBU1(AUXP)                         | SBU2(AUXN) |  |

| B8             | CSBU2              | SBU2(AUXN)                         | SBU1(AUXP) |  |

Table 2. SOURCE Pin Assignment Option C and E (AMSEL = H, EN = H)

Figure 8. SOURCE Pin Assignment Option C and E (AMSEL = H, EN = H)

TEXAS INSTRUMENTS

www.ti.com

| RECEPTACLE PIN | 460 PIN MAPPING TO | 460 PIN MAPPING TO DP SOURCE (GPU) |            |  |

|----------------|--------------------|------------------------------------|------------|--|

| NUMBER         | TYPE C CONNECTOR   | POL = L                            | POL = H    |  |

| A11/10         | CRX2               | LnA(ML0)                           | SSRX       |  |

| A2/3           | CTX1               | SSTX                               | LnB(ML1)   |  |

| B11/10         | CRX1               | SSRX                               | LnA(ML0)   |  |

| B2/3           | CTX2               | LnB(ML1)                           | SSTX       |  |

| A8             | CSBU1              | SBU1(AUXP)                         | SBU2(AUXN) |  |

| B8             | CSBU2              | SBU2(AUXN)                         | SBU1(AUXP) |  |

Table 3. SOURCE Pin Assignment Option D and F (AMSEL = L, EN = H)

Figure 10. SOURCE Pin Assignment Option D and F (AMSEL = L, EN = H, POL = H)

#### Table 4. SINK Pin Assignment Option C (AMSEL = H, EN = H)

| RECEPTACLE PIN | 460 PIN MAPPING TO | 460 PIN MAPPING TO DP SOURCE (GPU) |            |  |

|----------------|--------------------|------------------------------------|------------|--|

| NUMBER         | TYPE C CONNECTOR   | POL = L                            | POL = H    |  |

| A11/10         | CRX2               | LnA(ML1)                           | LnD(ML2)   |  |

| A2/3           | CTX1               | LnC(ML3)                           | LnB(ML0)   |  |

| B11/10         | CRX1               | LnD(ML2)                           | LnA(ML1)   |  |

| B2/3           | CTX2               | LnB(ML0)                           | LnC(ML3)   |  |

| A8             | CSBU1              | SBU1(AUXN)                         | SBU2(AUXP) |  |

| B8             | CSBU2              | SBU2(AUXP)                         | SBU1(AUXN) |  |

Figure 11. SINK Pin Assignment Option C (AMSEL = H, EN = H)

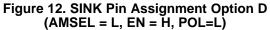

| RECEPTACLE PIN | 460 PIN MAPPING TO | 460 PIN MAPPING TO DP SOURCE (GPU) |            |  |  |

|----------------|--------------------|------------------------------------|------------|--|--|

| NUMBER         | TYPE C CONNECTOR   | POL = L                            | POL = H    |  |  |

| A11/10         | CRX2               | LnA(ML1)                           | SSRX       |  |  |

| A2/3           | CTX1               | SSTX                               | LnB(ML0)   |  |  |

| B11/10         | CRX1               | SSRX                               | LnA(ML1)   |  |  |

| B2/3           | CTX2               | LnB(ML0)                           | SSTX       |  |  |

| A8             | CSBU1              | SBU1(AUXN)                         | SBU2(AUXP) |  |  |

| B8             | CSBU2              | SBU2(AUXP)                         | SBU1(AUXN) |  |  |

Figure 13. SINK Pin Assignment Option D (AMSEL = L, EN = H, POL=H)

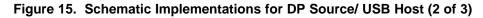

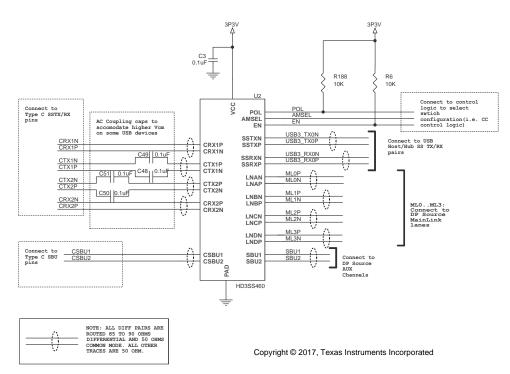

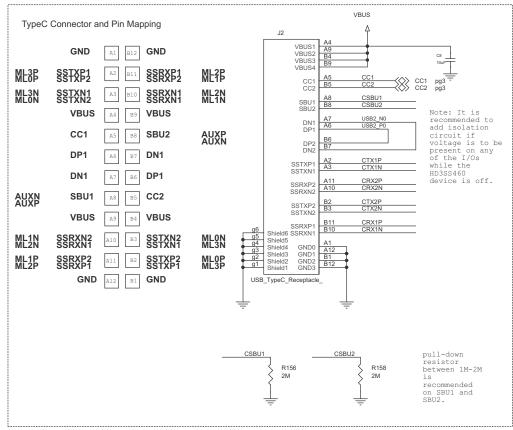

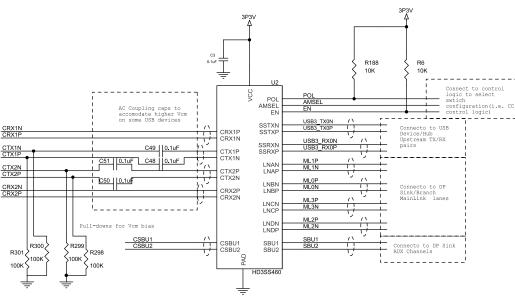

Schematic diagrams Figure 14, Figure 15, and Figure 16 show the DP Source/USB Host implementation; and, Figure 17, Figure 18, and Figure 19 show the DP Sink/USB Device/HUSB Hub/Dock implementation, respectively.

Copyright © 2016, Texas Instruments Incorporated

Figure 14. Schematic Implementations for DP Source/ USB Host (1 of 3)

Copyright © 2016, Texas Instruments Incorporated

Figure 16. Schematic Implementations for DP Source/ USB Host (3 of 3)

Copyright © 2016, Texas Instruments Incorporated

#### Figure 17. Schematic Implementations for DP Sink/ USB Device/HUB/Dock (1 of 3)

Copyright © 2016, Texas Instruments Incorporated

Figure 18. Schematic Implementations for DP Sink/ USB Device/HUB/Dock (2 of 3)

Copyright © 2017, Texas Instruments Incorporated

Figure 19. Schematic Implementations for DP Sink/ USB Device/HUB/Dock (3 of 3)

## **10** Power Supply Recommendations

There is no power supply sequence required for HD3SS460. However it is recommended that EN is asserted low after device supply VCC is stable and within specification. It is also recommended that ample decoupling capacitors are placed at the device  $V_{CC}$  near the pin.

## 11 Layout

### 11.1 Layout Guidelines

High performance layout practices are paramount for board layout for high speed signals to ensure good signal integrity. Even minor imperfection can cause impedance mismatch resulting reflection. Special care is warranted for traces, connections to device, and connectors.

#### 11.1.1 Critical Routing

The high speed differential signals must be routed with great care to minimize signal quality degradation between the connector and the source or sink of the high speed signals by following the guidelines provided in this document. Depending on the configuration schemes, the speed of each differential pair can reach a maximum speed of 5.4 Gbps. These signals are to be routed first before other signals with highest priority.

- Each differential pair should be routed together with controlled differential impedance of 85 to 90-Ω and 50-Ω common mode impedance. Keep away from other high speed signals. The number of vias should be kept to minimum. Each pair should be separated from adjacent pairs by at least 3 times the signal trace width. Route all differential pairs on the same group of layers (Outer layers or inner layers) if not on the same layer. No 90 degree turns on any of the differential pairs. If bends are used on high speed differential pairs, the angle of the bend should be greater than 135 degrees.

- Length matching:

- Keep high speed differential pairs lengths within 5 mil of each other to keep the intra-pair skew minimum.

- The inter-pair matching of the differential pairs is not as critical as intra-pair matching. The SSTX and SSRX pairs do not have to match while they need to be routed as short as possible.

- Keep high speed differential pair traces adjacent to ground plane.

- Do not route differential pairs over any plane split

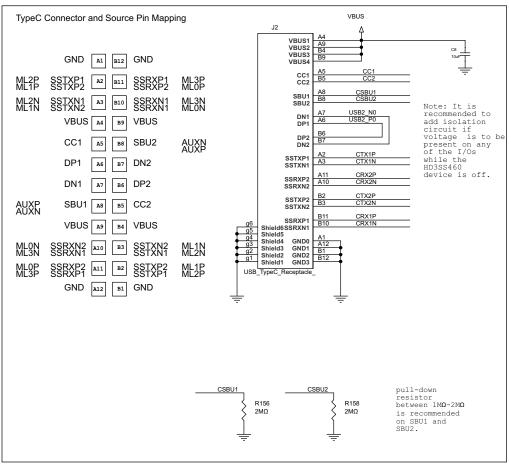

- ESD components on the high speed differential lanes should be placed nearest to the connector in a pass through manner without stubs on the differential path. In order to control impedance for transmission lines, a solid ground plane should be placed next to the high-speed signal layer. This also provides an excellent low-inductance path for the return current flow.

- Placement recommendation would be: Connector ESD Components --- HD3SS460

- For ease of routing, the P and N connection of the USB3.1 differential pairs to the HD3SS460 pins can be swapped as long as the corresponding pairs are swapped on the other end of the switch The example is shown in the reference EVM schematics section of this document. The P/N can be swapped on USB 3.1 connection of the switch for ease of routing purposes.

#### 11.1.2 General Routing/Placement Rules

- Route all high-speed signals first on un-routed PCB: SSTXP/N, SSRXT/N, LNAP/N, LNB P/N, LNC P/N, LND P/N, CTX\*P/N. The stub on USB2 D+ and D- pairs should not exceed 3.5mm.

- Follow 20H rule (H is the distance to reference plane) for separation of the high-speed trace from the edge of the plane

- Minimize parallelism of high speed clocks and other periodic signal traces to high speed lines

- All differential pairs should be routed on the top or bottom layer (microstrip traces) if possible or on the same group of layers. Vias should only be used in the breakout region of the device to route from the top to bottom layer when necessary. Avoid using vias in the main region of the board at all cost. Use a ground reference via next to signal via. Distance between ground reference via and signal need to be calculated to have similar impedance as traces.

- All differential signals should not be routed over plane split. Changing signal layers is preferable to crossing plane splits.

- Use of and proper placement of stitching caps when split plane crossing is unavoidable to account for high-frequency return current path

- Route differential traces over a continuous plane with no interruptions.

- Do not route differential traces under power connectors or other interface connectors, crystals, oscillators, or any magnetic source.

- Route traces away from etching areas like pads, vias, and other signal traces. Try to maintain a 20 mil keepout distance where possible.

#### Layout Guidelines (continued)

- Decoupling capacitors should be placed next to each power terminal on the HD3SS460. Care should be taken to minimize the stub length of the trace connecting the capacitor to the power pin.

- Avoid sharing vias between multiple decoupling capacitors.

- Place vias as close as possible to the decoupling capacitor solder pad.

- Widen VCC/GND planes to reduce effect of static and dynamic IR drop.

- The VBUS traces/planes must be wide enough to carry maximum of 2 A current.

### 11.2 Layout Example

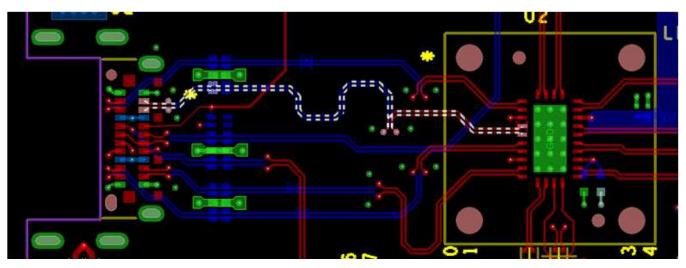

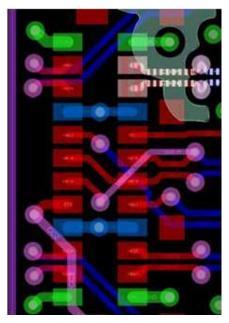

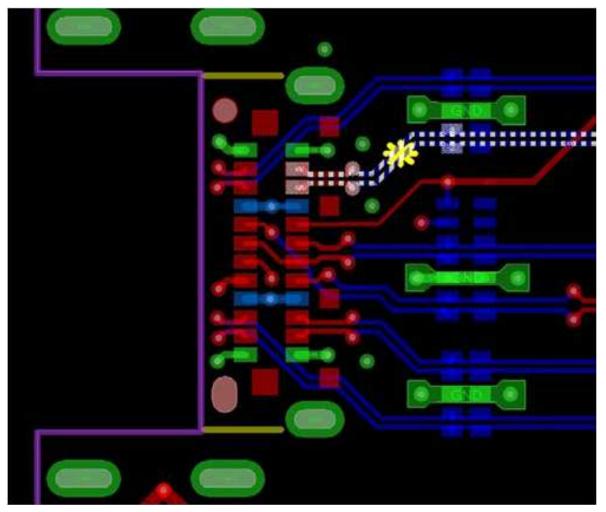

Figure 20, Figure 21, and Figure 22 illustrate some guidelines for layout. Actual layout should be optimized for various factors such as board geometry, connector type, and application.

Figure 20. USB Type C Connector to HD3SS460 Signal Routing

Figure 21. Dual SMT Mid-Mount Type C Connector Layout Example Zoom-in

HD3SS460

SLLSEM7D - JANUARY 2015 - REVISED JANUARY 2017

## Layout Example (continued)

Figure 22. Dual-row SMT Mid-mount Type C with ESD Components

## **12 Device and Documentation Support**

### 12.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates — go to the product folder for your device on ti.com. In the upper right-hand corner, click the *Alert me* button to register and receive a weekly digest of product information that has changed (if any). For change details, check the revision history of any revised document.

### 12.2 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support TI's Design Support** Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.3 Trademarks

E2E is a trademark of Texas Instruments. USB Type-C is a trademark of USB-IF, Inc.. All other trademarks are the property of their respective owners.

#### 12.4 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

### 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### PACKAGING INFORMATION

| Orderable part number | Status<br>(1) | Material type (2) | Package   Pins  | Package qty   Carrier | <b>RoHS</b> (3) | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|---------------|-------------------|-----------------|-----------------------|-----------------|-------------------------------|----------------------------|--------------|------------------|

|                       |               |                   |                 |                       |                 | (4)                           | (5)                        |              |                  |

| HD3SS460IRHRR         | Active        | Production        | WQFN (RHR)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 3SS460I          |

| HD3SS460IRHRR.B       | Active        | Production        | WQFN (RHR)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 3SS460I          |

| HD3SS460IRHRT         | Active        | Production        | WQFN (RHR)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 3SS460I          |

| HD3SS460IRHRT.B       | Active        | Production        | WQFN (RHR)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 3SS460I          |

| HD3SS460IRNHR         | Active        | Production        | WQFN (RNH)   30 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 460IRNH          |

| HD3SS460IRNHR.B       | Active        | Production        | WQFN (RNH)   30 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 460IRNH          |

| HD3SS460IRNHT         | Active        | Production        | WQFN (RNH)   30 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 460IRNH          |

| HD3SS460IRNHT.B       | Active        | Production        | WQFN (RNH)   30 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | -40 to 85    | 460IRNH          |

| HD3SS460RHRR          | Active        | Production        | WQFN (RHR)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 3SS460           |

| HD3SS460RHRR.B        | Active        | Production        | WQFN (RHR)   28 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 3SS460           |

| HD3SS460RHRT          | Active        | Production        | WQFN (RHR)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 3SS460           |

| HD3SS460RHRT.B        | Active        | Production        | WQFN (RHR)   28 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 3SS460           |

| HD3SS460RNHR          | Active        | Production        | WQFN (RNH)   30 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 460RNH           |

| HD3SS460RNHR.B        | Active        | Production        | WQFN (RNH)   30 | 3000   LARGE T&R      | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 460RNH           |

| HD3SS460RNHT          | Active        | Production        | WQFN (RNH)   30 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 460RNH           |

| HD3SS460RNHT.B        | Active        | Production        | WQFN (RNH)   30 | 250   SMALL T&R       | Yes             | NIPDAU                        | Level-1-260C-UNLIM         | 0 to 70      | 460RNH           |

<sup>(1)</sup> **Status:** For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

## PACKAGE OPTION ADDENDUM

30-Jun-2025

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

Texas

STRUMENTS

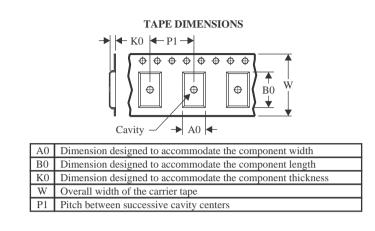

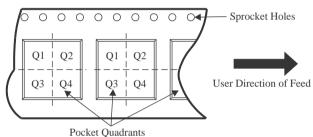

### TAPE AND REEL INFORMATION

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| HD3SS460IRHRR               | WQFN            | RHR                | 28 | 3000 | 330.0                    | 12.4                     | 3.8        | 5.8        | 1.2        | 8.0        | 12.0      | Q1               |

| HD3SS460IRHRT               | WQFN            | RHR                | 28 | 250  | 180.0                    | 12.4                     | 3.8        | 5.8        | 1.2        | 8.0        | 12.0      | Q1               |

| HD3SS460IRNHR               | WQFN            | RNH                | 30 | 3000 | 330.0                    | 12.4                     | 2.8        | 4.8        | 1.2        | 4.0        | 12.0      | Q1               |

| HD3SS460IRNHT               | WQFN            | RNH                | 30 | 250  | 180.0                    | 12.4                     | 2.8        | 4.8        | 1.2        | 4.0        | 12.0      | Q1               |

| HD3SS460RHRR                | WQFN            | RHR                | 28 | 3000 | 330.0                    | 12.4                     | 3.8        | 5.8        | 1.2        | 8.0        | 12.0      | Q1               |

| HD3SS460RHRT                | WQFN            | RHR                | 28 | 250  | 180.0                    | 12.4                     | 3.8        | 5.8        | 1.2        | 8.0        | 12.0      | Q1               |

| HD3SS460RNHR                | WQFN            | RNH                | 30 | 3000 | 330.0                    | 12.4                     | 2.8        | 4.8        | 1.2        | 4.0        | 12.0      | Q1               |

| HD3SS460RNHT                | WQFN            | RNH                | 30 | 250  | 180.0                    | 12.4                     | 2.8        | 4.8        | 1.2        | 4.0        | 12.0      | Q1               |

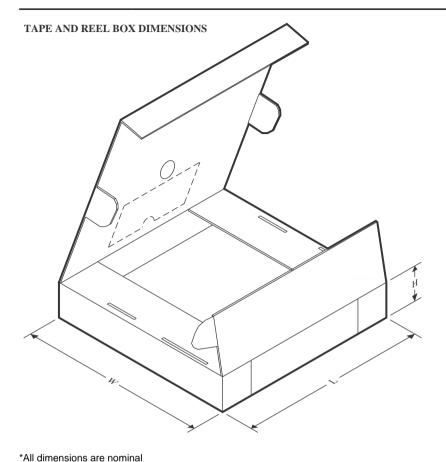

## PACKAGE MATERIALS INFORMATION

9-Oct-2024

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| HD3SS460IRHRR | WQFN         | RHR             | 28   | 3000 | 346.0       | 346.0      | 33.0        |

| HD3SS460IRHRT | WQFN         | RHR             | 28   | 250  | 182.0       | 182.0      | 20.0        |

| HD3SS460IRNHR | WQFN         | RNH             | 30   | 3000 | 367.0       | 367.0      | 35.0        |

| HD3SS460IRNHT | WQFN         | RNH             | 30   | 250  | 210.0       | 185.0      | 35.0        |

| HD3SS460RHRR  | WQFN         | RHR             | 28   | 3000 | 346.0       | 346.0      | 33.0        |

| HD3SS460RHRT  | WQFN         | RHR             | 28   | 250  | 182.0       | 182.0      | 20.0        |

| HD3SS460RNHR  | WQFN         | RNH             | 30   | 3000 | 367.0       | 367.0      | 35.0        |

| HD3SS460RNHT  | WQFN         | RNH             | 30   | 250  | 210.0       | 185.0      | 35.0        |

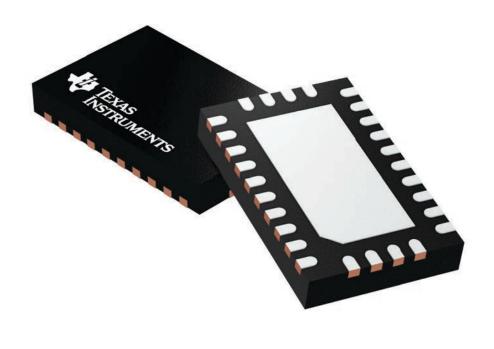

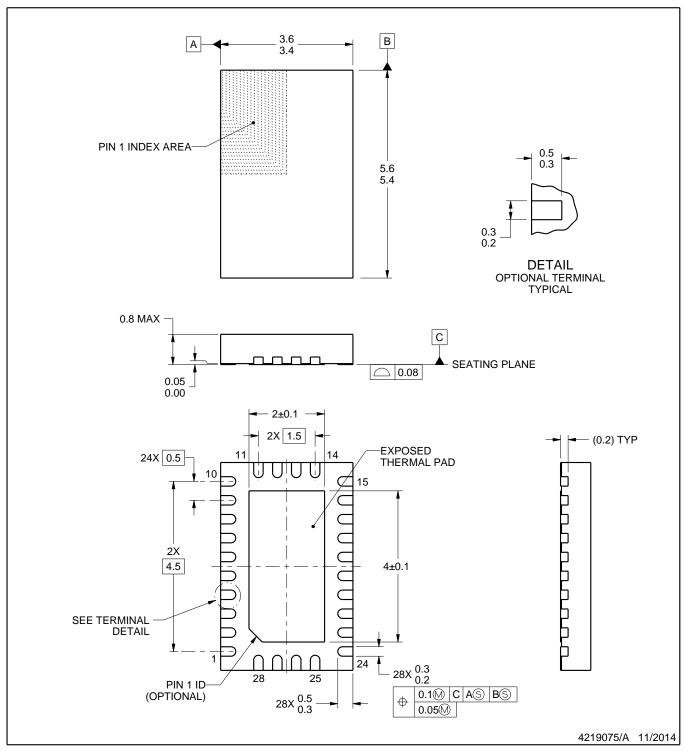

## **RHR 28**

3.5 x 5.5, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

## **RHR0028A**

## **PACKAGE OUTLINE**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

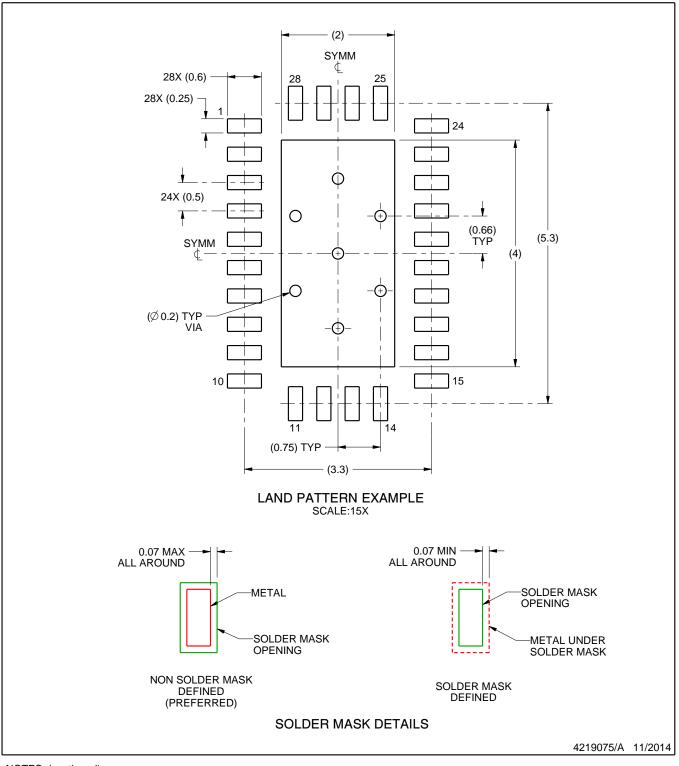

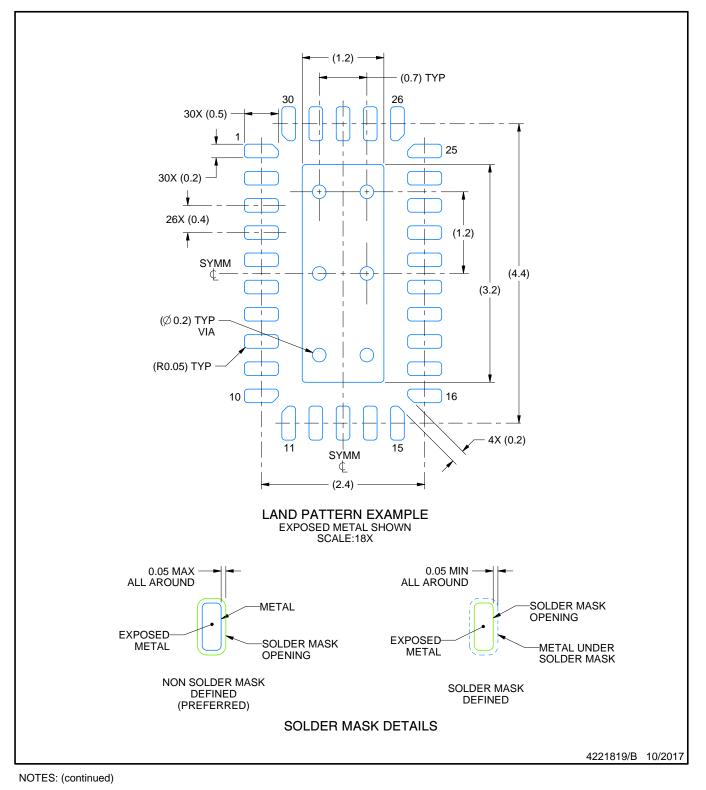

## RHR0028A

## **EXAMPLE BOARD LAYOUT**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

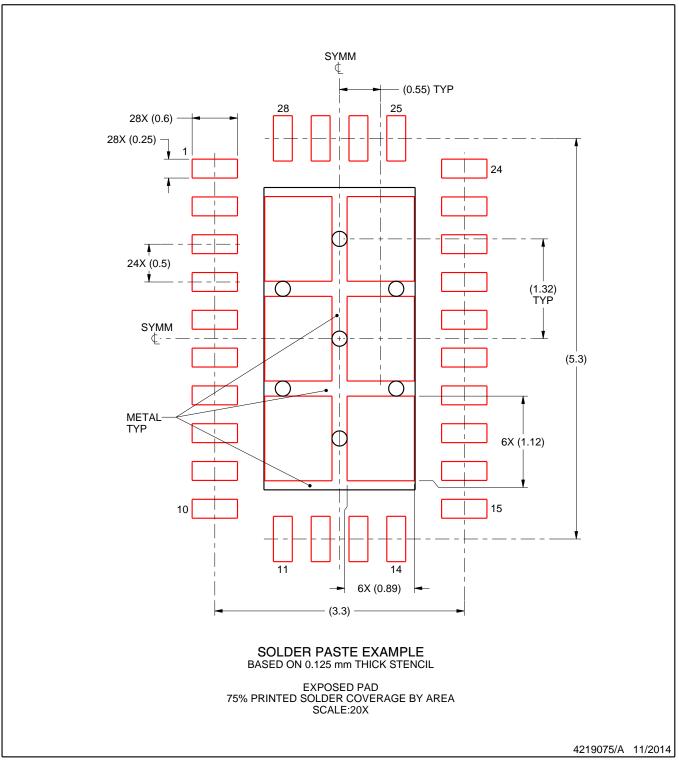

## **RHR0028A**

## **EXAMPLE STENCIL DESIGN**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

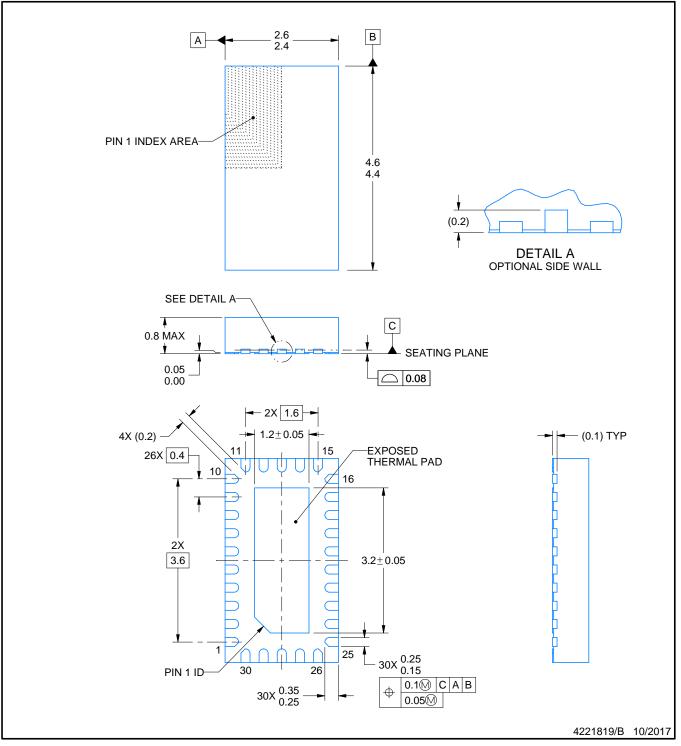

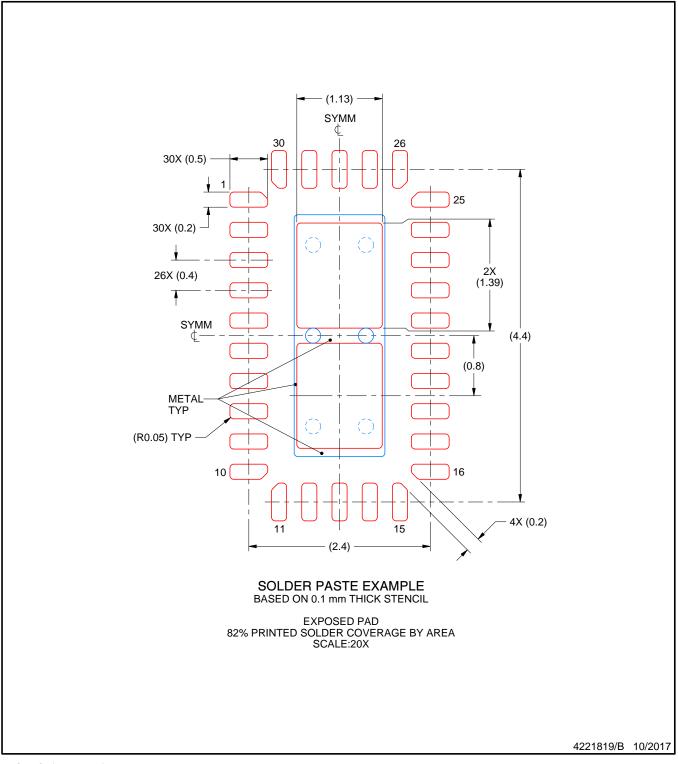

## **RNH0030A**

## **PACKAGE OUTLINE**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

## **RNH0030A**

## **EXAMPLE BOARD LAYOUT**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

## **RNH0030A**

## **EXAMPLE STENCIL DESIGN**

## WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

5. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated