**DRV8235** SLVSHO3 - APRIL 2024

# DRV8235 38V 3.7A Brushed DC Motor Driver with Integrated Speed Regulation and Stall Detection

# 1 Features

- N-channel H-bridge brushed DC motor driver

- 4.5V to 38V operating supply voltage range

- Integrated Voltage and Speed regulation

- Soft-Start and Stop feature for inrush current protection

- **600mΩ** R<sub>DS(on)</sub> (High-Side + Low-Side) ٠

- High output current capability: 3.7A Peak, 2A RMS

- PWM with I<sup>2</sup>C control interface

- Configuration and diagnostics on I<sup>2</sup>C registers

- Multi-follower operation support \_

- Supports standard and fast I<sup>2</sup>C mode

- Supports 3.3V, and 5V logic inputs ٠

- Integrated current sensing and current regulation

- Analog current sense output (IPROPI)

- Internal charge pump with 100% duty cycle

- Long battery life with low-power sleep mode

- < 1µA maximum sleep current</li>

- Small package and footprint

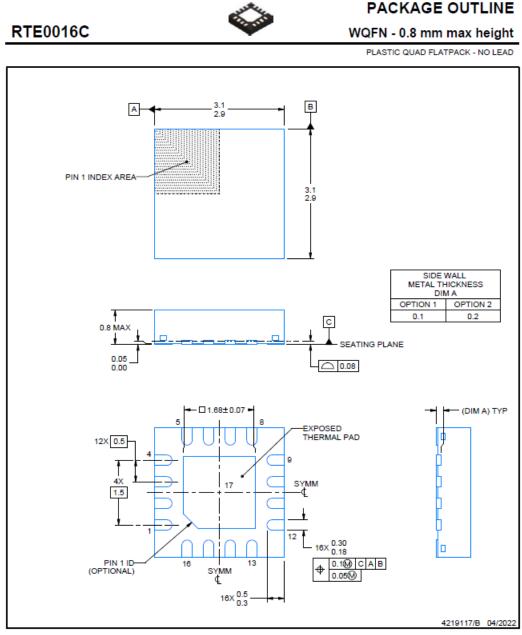

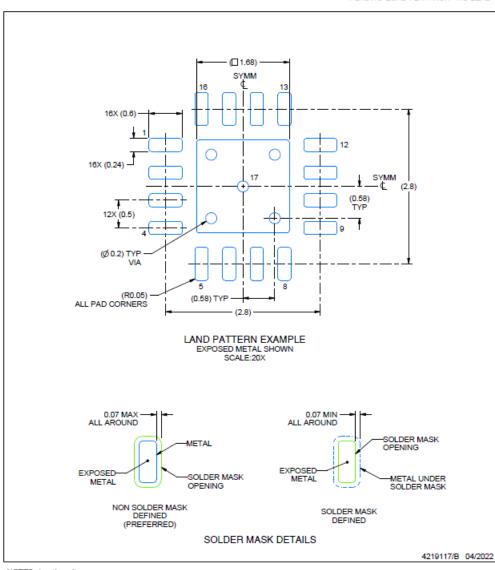

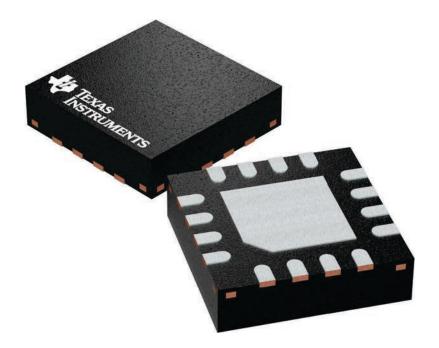

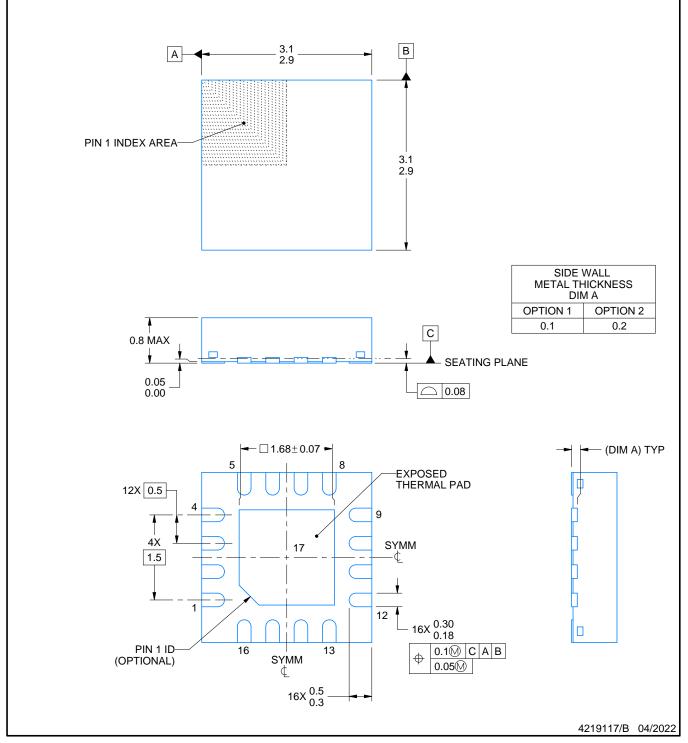

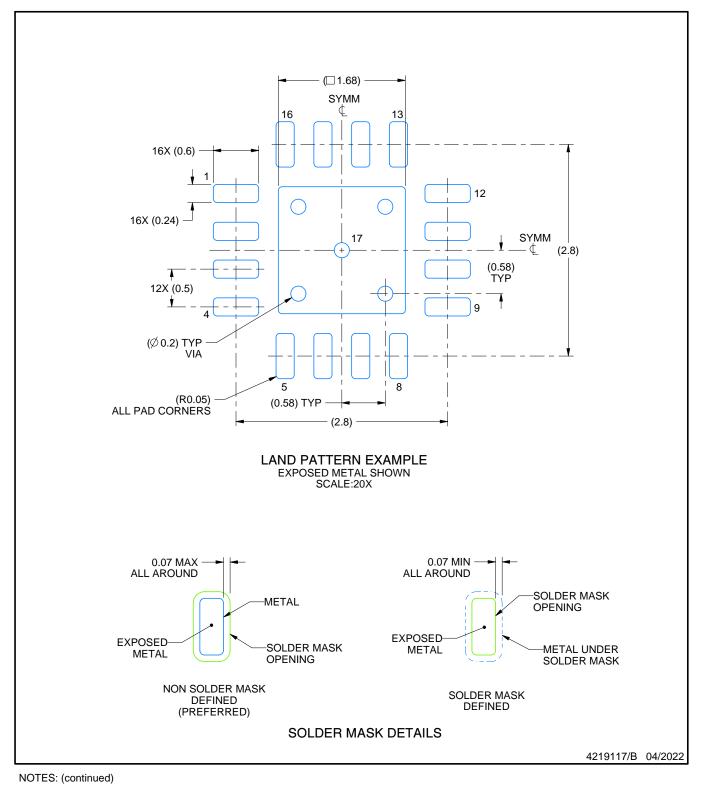

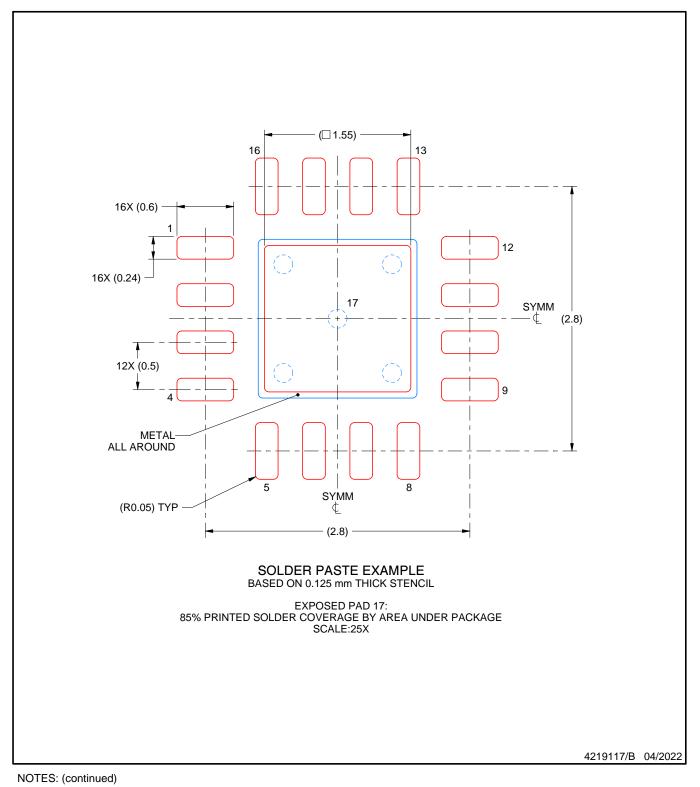

- 16-Pin WQFN with PowerPAD<sup>™</sup>, 3 × 3mm

- Integrated protection features

- VM undervoltage lockout (UVLO)

- Overcurrent protection (OCP)

- Thermal shutdown (TSD)

- Stall detection

- Overvoltage protection (OVP)

# 2 Applications

- Printers ٠

- Vacuum Robots

- Washers and Dryers

- **Coffee Machines** •

- **POS Printers**

- Electronic Hospital bed and bed control

- **Fitness Machine**

# 3 Description

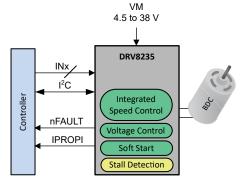

The DRV8235 is a high-performance integrated Hbridge motor driver with integrated speed regulation along with additional integrated features like stall detection, current sense output, current regulation, and protection circuitry.

The integrated speed and voltage regulation feature uses the motor voltage and current information to regulate motor speed or voltage eliminating the potential need for external sensors to detect speed. This reduces board size and design complexity, and saves on overall system cost. Integrated speed regulation is used to maintain constant motor speed over varying input supply voltages which minimizes current consumption and saves power over time. This is critical in applications that have different loading conditions or rely on battery power for operation where the input voltage is not constant. Soft-start and stop allows for a controlled turn-on and turn-off time, reducing large inrush currents to protect the motor windings from damage, thereby increasing system reliability and longevity.

An internal current mirror implements current sensing and regulation. This eliminates the need for a large power shunt resistor, saving board area and reducing system cost. The IPROPI current sense output allows a microcontroller to detect motor stall or changes in load conditions. Using the VREF pin, this device can regulate the motor current during startup and highload events without interaction from a microcontroller. The device supports sensorless motor stall detection and reporting to microcontroller.

## **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE<br>(NOM) <sup>(2)</sup> |  |  |

|-------------|------------------------|--------------------------------------|--|--|

| DRV8235     | WQFN (16)              | 3.00mm × 3.00mm                      |  |  |

For all available packages, see the orderable addendum at (1) the end of the data sheet.

The package size (length × width) is a nominal value and (2) includes pins, where applicable.

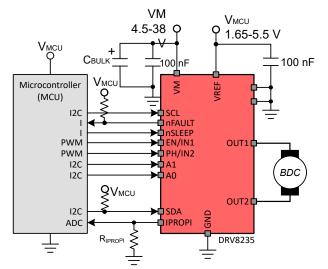

**Simplified Schematic**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features                            |    |

|---------------------------------------|----|

| 2 Applications                        |    |

| 3 Description                         | 1  |

| 4 Device Comparison                   |    |

| 5 Pin Configuration and Functions     | 4  |

| 6 Specifications                      | 5  |

| 6.1 Absolute Maximum Ratings          | 5  |

| 6.2 ESD Ratings                       | 5  |

| 6.3 Recommended Operating Conditions  |    |

| 6.4 Thermal Information               | 6  |

| 6.5 Electrical Characteristics        | 6  |

| 6.6 I2C Timing Requirements           | 7  |

| 6.7 Timing Diagrams                   |    |

| 6.8 Typical Operating Characteristics |    |

| 7 Detailed Description                | 10 |

| 7.1 Overview                          |    |

| 7.2 Functional Block Diagram          | 11 |

| 7.3 Feature Description               |    |

| 7.4 Device Functional Modes           |    |

|                                       |    |

| 7.5 Programming                                      | . 32 |

|------------------------------------------------------|------|

| 8 Register Map                                       |      |

| 8.1 DRV8235_STATUS Registers                         |      |

| 8.2 DRV8235_CONFIG Registers                         |      |

| 8.3 DRV8235_CTRL Registers                           |      |

| 9 Application and Implementation                     |      |

| 9.1 Application Information                          | . 65 |

| 9.2 Typical Application: Brushed DC Motor            | . 65 |

| 9.3 Power Supply Recommendations                     | 74   |

| 9.4 Layout                                           |      |

| 10 Device and Documentation Support                  |      |

| 10.1 Receiving Notification of Documentation Updates | 76   |

| 10.2 Support Resources                               | 76   |

| 10.3 Trademarks                                      |      |

| 10.4 Electrostatic Discharge Caution                 | 76   |

| 10.5 Glossary                                        | 76   |

| 11 Revision History                                  |      |

| 12 Mechanical, Packaging, and Orderable              |      |

| Information                                          | 77   |

|                                                      |      |

# **4 Device Comparison**

| Part Number | Package | Supply VM<br>(V) | R <sub>DS(ON)</sub> (mΩ) | RMS Current<br>Capacity (A) | Sensorless<br>Position<br>Sensing | Speed<br>Regulation | Stall<br>Detection | Package Size |

|-------------|---------|------------------|--------------------------|-----------------------------|-----------------------------------|---------------------|--------------------|--------------|

| DRV8214     | RTE     | 1.65 to 11       | 240                      | 2                           | Yes                               | Yes                 | Yes                | 3mm × 3mm    |

| DRV8215     | RTE     | 1.65 to 11       | 240                      | 2                           | No                                | Yes                 | Yes                | 3mm × 3mm    |

| DRV8234     | RTE     | 4.5 to 38        | 600                      | 2                           | Yes                               | Yes                 | Yes                | 3mm × 3mm    |

| DRV8235     | RTE     | 4.5 to 38        | 600                      | 2                           | No                                | Yes                 | Yes                | 3mm × 3mm    |

| DRV8213     | RTE     | 1.65 to 11       | 240                      | 2                           | No                                | No                  | Yes                | 3mm × 3mm    |

| DRV8213     | DSG     | 1.65 to 11       | 240                      | 2                           | No                                | No                  | No                 | 2mm × 2mm    |

# Table 4-1. Device Comparison Table

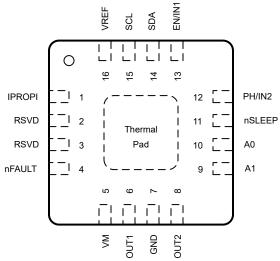

# **5** Pin Configuration and Functions

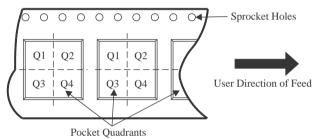

Figure 5-1. RTE Package 16-Pin WQFN Top View

| Table | 5-1. Pin | Functions |

|-------|----------|-----------|

|-------|----------|-----------|

| PIN    |     |     | DESCRIPTION                                                                                                                                                       |  |  |

|--------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | RTE |     | DESCRIPTION                                                                                                                                                       |  |  |

| IPROPI | 1   | PWR | Analog current output proportional to load current. Connect a resistor from IPROPI to ground.                                                                     |  |  |

| RSVD   | 2   | _   | Reserved. Leave this pin unconnected.                                                                                                                             |  |  |

| RSVD   | 3   | _   | Reserved. Leave this pin unconnected.                                                                                                                             |  |  |

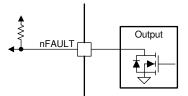

| nFAULT | 4   | OD  | Fault indicator output. Pulled low during a fault condition. Connect an external pullup resistor for open-drain operation.                                        |  |  |

| VM     | 5   | PWR | Motor power supply. Bypass this pin to the GND pin with a $0.1\mu$ F ceramic capacitor as well as sufficient bulk capacitance rated for VM.                       |  |  |

| OUT1   | 6   | 0   | H-bridge output. Connect directly to the motor.                                                                                                                   |  |  |

| GND    | 7   | PWR | Device ground. Connect to system ground.                                                                                                                          |  |  |

| OUT2   | 8   | 0   | H-bridge output. Connect directly to the motor.                                                                                                                   |  |  |

| A1     | 9   | I   | I <sup>2</sup> C base address select pin. Tri-level input.                                                                                                        |  |  |

| A0     | 10  | I   | I <sup>2</sup> C base address select pin. Tri-level input.                                                                                                        |  |  |

| nSLEEP | 11  | I   | Sleep mode input. Logic high to enable device. Logic low to enter low-power sleep mode. Internal pulldown resistor.                                               |  |  |

| PH/IN2 | 12  | I   | Controls the H-bridge output. Has internal pulldown.                                                                                                              |  |  |

| EN/IN1 | 13  | I   | Controls the H-bridge output. Has internal pulldown.                                                                                                              |  |  |

| SDA    | 14  | I   | I <sup>2</sup> C data signal. The SDA pin requires a pullup resistor.                                                                                             |  |  |

| SCL    | 15  | I   | I <sup>2</sup> C clock signal.                                                                                                                                    |  |  |

| VREF   | 16  | I   | Analog input to set current regulation and stall detection level.                                                                                                 |  |  |

| PAD    | —   | _   | Thermal pad. Connect to board ground. For good thermal dissipation, use large ground planes on multiple layers, and multiple nearby vias connecting those planes. |  |  |

(1) I = Input, O = Output, PWR = Power, OD = Open-Drain Output

# **6** Specifications

## 6.1 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                          |                                    | MIN                   | MAX                              | UNIT |

|----------------------------------------------------------|------------------------------------|-----------------------|----------------------------------|------|

| Power supply pin voltage                                 | VM                                 | -0.5                  | 40                               | V    |

| Power supply transient voltage ramp                      | VM                                 | 0                     | 2                                | V/µs |

| Logic pin voltage                                        | IN1, IN2, A1, A0, SDA, SCL, nSLEEP | -0.3                  | 5.75                             | V    |

| Open-drain output pin voltage                            | nFAULT                             | -0.3                  | 5.75                             | V    |

| Proportional current output pin voltage, VM $\ge$ 5.45 V | - IPROPI                           | -0.3                  | 5.75                             | V    |

| Proportional current output pin voltage, VM $$ < 5.45 V  |                                    | -0.3                  | V <sub>VM</sub> + 0.3            | V    |

| Reference input pin voltage                              | VREF                               | 0.3                   | 5.75                             | V    |

| Output pin voltage                                       | OUTx                               | -V <sub>SD</sub>      | V <sub>VM</sub> +V <sub>SD</sub> | V    |

| Output current                                           | OUTx                               | Internally<br>Limited | Internally<br>Limited            | А    |

| Ambient temperature, T <sub>A</sub>                      |                                    | -40                   | 125                              | °C   |

| Junction temperature, T <sub>J</sub>                     |                                    | -40                   | 150                              | °C   |

| Storage temperature, T <sub>stg</sub>                    |                                    | -65                   | 150                              | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |               |                                                                                | VALUE | UNIT |  |

|--------------------|---------------|--------------------------------------------------------------------------------|-------|------|--|

| V                  | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V    |  |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v    |  |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Pins listed as ± 2000 V may actually have higher performance.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Pins listed as ± 500 V may actually have higher performance.

## 6.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                                 |                                 |                                  | MIN | NOM MAX |       |

|---------------------------------|---------------------------------|----------------------------------|-----|---------|-------|

| V <sub>VM</sub>                 | Power supply voltage            | VM                               | 4.5 | 38      | 3 V   |

| V <sub>IN</sub>                 | Logic input voltage             | IN1, IN2,A1, A0, SDA, SCL,nSLEEP | 0   | 5.5     | 5 V   |

| f <sub>PWM</sub>                | PWM frequency                   | INx                              | 0   | 200     | ) kHz |

| V <sub>OD</sub>                 | Open drain pullup voltage       | nFAULT                           | 0   | 5.8     | 5 V   |

| I <sub>OD</sub>                 | Open drain output current       | nFAULT                           | 0   | ł       | 5 mA  |

| I <sub>OUT</sub> <sup>(1)</sup> | Peak output current             | OUTx                             | 0   | 3.7     | ΖΑ    |

| I <sub>IPROPI</sub>             | Current sense output current    | IPROPI                           | 0   | :       | 3 mA  |

| V <sub>VREF</sub>               | Current limit reference voltage | VREF                             | 0   | 3.3     | 3 V   |

| T <sub>A</sub>                  | Operating ambient temperature   | · ·                              | -40 | 125     | 5 °C  |

| TJ                              | Operating junction temperature  |                                  | -40 | 150     | O°C   |

(1) Power dissipation and thermal limits must be observed

# 6.4 Thermal Information

|                       |                                              | DEVICE     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                       |                                              | 16 PINS    |      |

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 47.8       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 48.2       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 22.4       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.1        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 22.4       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 8.6        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

$4.5 \text{ V} \le \text{V}_{\text{VM}} \le 38 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$  (unless otherwise noted). Typical values are at T<sub>J</sub> = 27^{\circ}\text{C}, V\_{\text{VM}} = 24 \text{ V}.

|                        | PARAMETER                             | TEST CONDITIONS                                             | MIN | TYP | MAX | UNIT |

|------------------------|---------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

| POWER SU               | PPLIES (VM)                           | •                                                           |     |     |     |      |

| I <sub>VMQ</sub>       | VM sleep mode current                 | nSLEEP = 0 V, V <sub>VM</sub> = 24 V, T <sub>J</sub> = 27°C |     | 0.1 | 1   | μA   |

| I <sub>VM</sub>        | VM active mode current                | nSLEEP = 3.3 V, IN1 = 3.3 V, IN2 = 0 V, $V_{VM}$ = 24 V     |     | 3.5 | 4   | mA   |

| t <sub>WAKE</sub>      | Turnon time                           | nSLEEP = 1 to I <sup>2</sup> C ready                        |     |     | 410 | μs   |

| LOGIC-LEV              | EL INPUTS (IN1, IN2, SDA, SCL, nSLEE  | P)                                                          |     |     |     |      |

| V <sub>IL</sub>        | Input logic low voltage               |                                                             | 0   |     | 0.5 | V    |

| V <sub>IH</sub>        | Input logic high voltage              |                                                             | 1.5 |     | 5.5 | V    |

| V <sub>HYS</sub>       | Input hysteresis                      |                                                             |     | 160 |     | mV   |

| V <sub>HYS</sub>       | Input hysterisis                      | nSLEEP pin                                                  |     | 60  |     |      |

| IIL                    | Input logic low current               | V <sub>1</sub> = 0 V                                        | -1  |     | 1   | μA   |

| I <sub>IH</sub>        | Input logic high current              | V <sub>1</sub> = 5 V                                        |     | 33  | 100 | μA   |

| R <sub>PD</sub>        | Input pulldown resistance, INx        | To GND                                                      |     | 100 |     | kΩ   |

| t <sub>DEGLITCH</sub>  | Input logic deglitch, INx             |                                                             |     | 50  |     | ns   |

| TRI-LEVEL              | INPUTS (A1, A0)                       |                                                             |     |     |     |      |

| V <sub>TIL</sub>       | Tri-level input logic low voltage     |                                                             | 0   |     | 0.6 | V    |

| V <sub>TIHZ</sub>      | Tri-level input Hi-Z voltage          |                                                             | 1.8 | 2   | 2.2 | V    |

| V <sub>TIH</sub>       | Tri-level input logic high voltage    |                                                             | 2.7 |     | 5.5 | V    |

| R <sub>TPD</sub>       | Tri-level pulldown resistance         | to GND                                                      |     | 200 |     | kΩ   |

| I <sub>TPU</sub>       | Tri-level pullup current              | to 3.3 V                                                    |     | 10  |     | μA   |

| OPEN-DRA               | IN OUTPUTS (nFAULT, SDA)              | · · ·                                                       |     |     |     |      |

| V <sub>OL</sub>        | Output logic low voltage              | I <sub>OD</sub> = 5 mA                                      |     |     | 0.3 | V    |

| I <sub>OZ</sub>        | Output logic high current             | V <sub>OD</sub> = 3.3 V                                     | -1  |     | 1   | μA   |

| t <sub>PW_nFAULT</sub> | nFAULT low pulse width                | RC Count overflow, RC_REP = 11b                             | 30  | 50  | 70  | μs   |

| C <sub>B</sub>         | SDA capacitive load for each bus line |                                                             |     |     | 400 | pF   |

| DRIVER OL              | ITPUTS (OUTx)                         |                                                             |     |     |     |      |

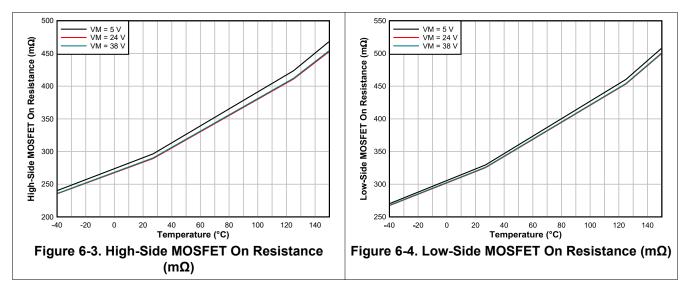

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance        | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 25 °C             |     | 300 | 360 | mΩ   |

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance        | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 125 °C            |     | 450 | 540 | mΩ   |

| R <sub>DS(ON)_HS</sub> | High-side MOSFET on resistance        | I <sub>OUTx</sub> = 1 A; T <sub>J</sub> = 150 °C            |     | 500 | 600 | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance         | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 25 °C            |     | 300 | 360 | mΩ   |

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance         | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 125 °C           |     | 450 | 540 | mΩ   |

TEXAS INSTRUMENTS www.ti.com

|                        | PARAMETER                                            | TEST CONDITIONS                                                                          | MIN  | TYP  | MAX  | UNIT |

|------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|------|

| R <sub>DS(ON)_LS</sub> | Low-side MOSFET on resistance                        | I <sub>OUTx</sub> = -1 A; T <sub>J</sub> = 150 °C                                        |      | 500  | 600  | mΩ   |

| V <sub>SD</sub>        | Body diode forward voltage                           | I <sub>OUTx</sub> = -1 A                                                                 |      | 0.8  |      | V    |

| t <sub>RISE</sub>      | Output rise time                                     | $V_{\text{OUTx}}$ rising from 10% to 90% of $V_{\text{VM}}$                              |      | 200  |      | ns   |

| t <sub>FALL</sub>      | Output fall time                                     | $V_{\text{OUTx}}$ falling from 90% to 10% of $V_{\text{VM}}$                             |      | 140  |      | ns   |

| t <sub>PD</sub>        | Input to output propagation delay                    | Input to OUTx                                                                            |      | 650  |      | ns   |

| t <sub>DEAD</sub>      | Output dead time                                     |                                                                                          |      | 200  |      | ns   |

| CURRENT S              | SENSE AND REGULATION (IPROPI, VRE                    | F)                                                                                       |      |      | 1    |      |

| V <sub>REF_INT</sub>   | Internal reference voltage                           | INT_VREF = 1b                                                                            | 2.88 | 3    | 3.12 | V    |

| AIPROPI                | Current scaling factor                               |                                                                                          |      | 1500 |      | µA/A |

| A <sub>ERR</sub>       | Current mirror total error                           | I <sub>OUT</sub> = 0.1 A, V <sub>VM</sub> ≥ 5.5 V                                        | -10  |      | 10   | %    |

| A <sub>ERR</sub>       | Current mirror total error                           | 0.15 A ≤ I <sub>OUT</sub> < 0.5 A, V <sub>VM</sub> ≥ 5.5 V                               | -7   |      | 7    | %    |

| A <sub>ERR</sub>       | Current mirror total error                           | I <sub>OUT</sub> ≥ 0.5 A, V <sub>VM</sub> ≥ 5.5 V                                        | -5   |      | 5    | %    |

| t <sub>OFF</sub>       | Current regulation off time                          |                                                                                          |      | 20   |      | μs   |

| t <sub>BLANK</sub>     | Current sense blanking time                          | TBLANK = 0b                                                                              |      | 1.8  |      | μs   |

| t <sub>BLANK</sub>     | Current sense blanking time                          | TBLANK = 1b                                                                              |      | 1    |      | μs   |

| t <sub>DEG</sub>       | Current regulation and stall detection deglitch time | TDEG = 0b                                                                                |      | 2    |      | μs   |

| t <sub>DEG</sub>       | Current regulation and stall detection deglitch time | TDEG = 1b                                                                                |      | 1    |      | μs   |

| t <sub>INRUSH</sub>    | Inrush time blanking for stall detection             |                                                                                          | 5    |      | 6716 | ms   |

| Voltage reg            | ulation                                              | 1                                                                                        |      |      |      |      |

| $\Delta V_{LINE}$      | Line regulation                                      | 5.5 V $\leq$ V <sub>VM</sub> $\leq$ 38 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 2 A |      | ±2%  |      |      |

| $\Delta V_{LOAD}$      | Load regulation                                      | V <sub>VM</sub> = 24 V, V <sub>OUT</sub> = 5 V, I <sub>OUT</sub> = 100 mA<br>to 2 A      |      | ±1%  |      |      |

| PROTECTIO              | ON CIRCUITS                                          | l I                                                                                      |      |      | I    |      |

| . <i>(</i>             |                                                      | Supply rising                                                                            | 4.15 | 4.3  | 4.45 | V    |

| V <sub>UVLO_VM</sub>   | VM supply undervoltage lockout (UVLO)                | Supply falling                                                                           | 4.05 | 4.2  | 4.35 | V    |

| V <sub>UVLO_HYS</sub>  | Supply UVLO hysteresis                               | Rising to falling threshold                                                              |      | 100  |      | mV   |

| t <sub>UVLO</sub>      | Supply undervoltage deglitch time                    | V <sub>VM</sub> falling to OUTx disabled                                                 |      | 10   |      | μs   |

| V <sub>RST</sub>       | VM UVLO reset                                        | VM falling, device reset, no I <sup>2</sup> C communications                             |      |      | 3.9  | V    |

| V <sub>OVP_TH</sub>    | Overvoltage protection threshold                     | V <sub>OUT</sub> - V <sub>VM</sub>                                                       |      | 200  |      | mV   |

| t <sub>OVP_ON</sub>    | Overvoltage protection turn-on time                  |                                                                                          |      | 10   |      | μs   |

| t <sub>OVP_OFF</sub>   | Overvoltage protection turn-off time                 |                                                                                          |      | 250  |      | μs   |

| I <sub>OCP</sub>       | Overcurrent protection trip point                    |                                                                                          | 3.7  |      |      | A    |

| t <sub>OCP</sub>       | Overcurrent protection deglitch time                 |                                                                                          |      | 2    |      | μs   |

| t <sub>RETRY</sub>     | Retry time                                           |                                                                                          |      | 1.7  |      | ms   |

| T <sub>TSD</sub>       | Thermal shutdown temperature                         |                                                                                          | 150  | 175  |      | °C   |

| T <sub>HYS</sub>       | Thermal shutdown hysteresis                          |                                                                                          |      | 40   |      | °C   |

$4.5 \text{ V} \le \text{V}_{\text{VM}} \le 38 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$  (unless otherwise noted). Typical values are at T<sub>J</sub> = 27^{\circ}\text{C}, V\_{\text{VM}} = 24 \text{ V}.

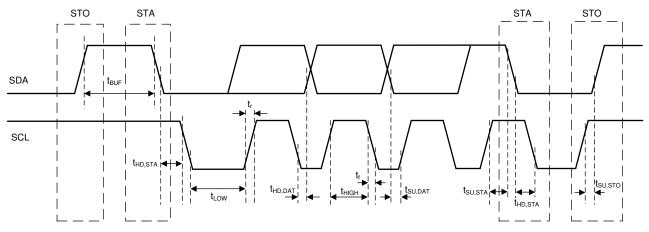

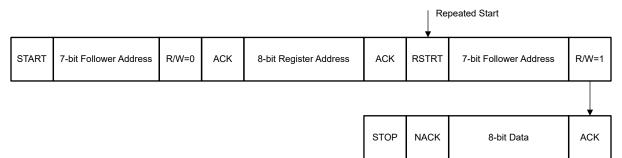

# 6.6 I2C Timing Requirements

|                     |                                                                                             | MIN | NOM MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------------------|-----|---------|------|

| STANDARD MODE       |                                                                                             |     |         |      |

| f <sub>SCL</sub>    | SCL Clock frequency                                                                         | 0   | 100     | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 4   |         | μs   |

Copyright © 2024 Texas Instruments Incorporated

|                     |                                                                                             | MIN   | NOM | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------------------|-------|-----|------|------|

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                 | 4.7   |     |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                | 4     |     |      | μs   |

| t <sub>SU,STA</sub> | Setup time for a repeated START condition                                                   | 4.7   |     |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time: For I2C bus devices                                                         | 0.035 |     | 3.45 | μs   |

| t <sub>SU,DAT</sub> | Data set-up time                                                                            | 250   |     |      | ns   |

| t <sub>R</sub>      | SDA and SCL rise time                                                                       |       |     | 1000 | ns   |

| t <sub>F</sub>      | SDA and SCL fall time                                                                       |       |     | 300  | ns   |

| t <sub>su,sто</sub> | Set-up time for STOP condition                                                              | 4     |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                            | 4.7   |     |      | μs   |

| FAST MODE           | · · · · · · · · · · · · · · · · · · ·                                                       |       |     |      |      |

| f <sub>SCL</sub>    | SCL Clock frequency                                                                         | 0     |     | 400  | kHz  |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated | 0.6   |     |      | μs   |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                 | 1.3   |     |      | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                | 0.6   |     |      | μs   |

| t <sub>SU,STA</sub> | Setup time for a repeated START condition                                                   | 0.6   |     |      | μs   |

| t <sub>HD,DAT</sub> | Data hold time: For I2C bus devices                                                         | 0.035 |     | 0.9  | μs   |

| t <sub>SU,DAT</sub> | Data set-up time                                                                            | 250   |     |      | ns   |

| t <sub>R</sub>      | SDA and SCL rise time                                                                       |       |     | 300  | ns   |

| t <sub>F</sub>      | SDA and SCL fall time                                                                       |       |     | 300  | ns   |

| t <sub>su,sтo</sub> | Set-up time for STOP condition                                                              | 0.6   |     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                            | 1.3   |     |      | μs   |

| t <sub>SP</sub>     | Pulse width of spikes to be supressed by input noise filter                                 |       | 50  |      | ns   |

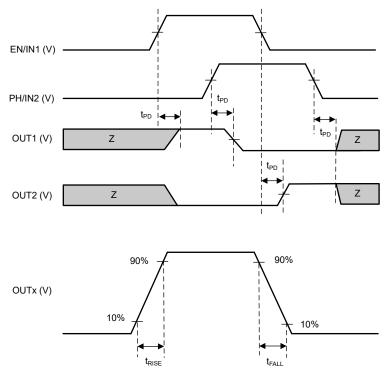

# 6.7 Timing Diagrams

# Figure 6-1. Input-to-Output Timing Diagram

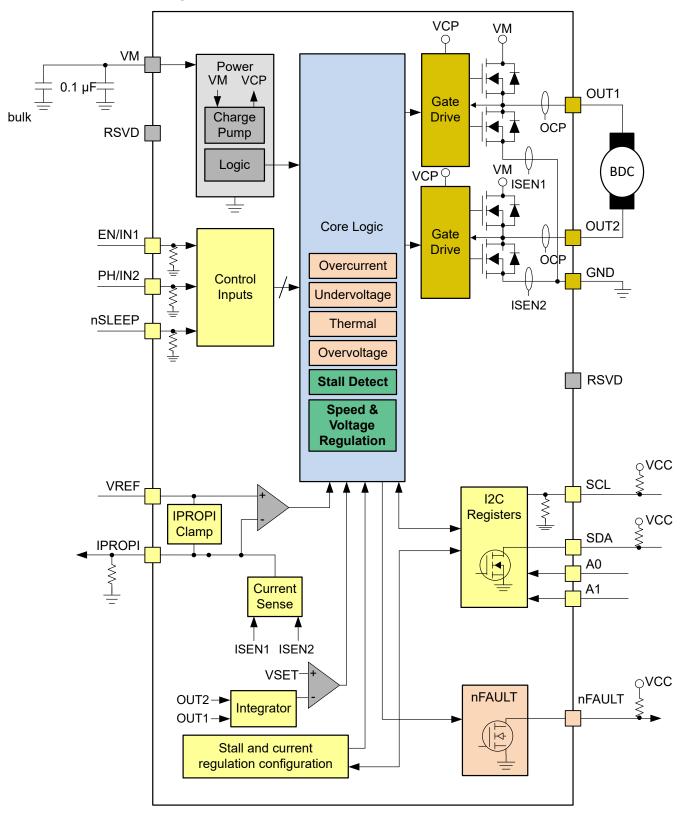

# 7 Detailed Description

# 7.1 Overview

The DRV8235 is a high-performance integrated H-bridge motor driver with integrated speed and voltage regulation along with additional integrated features like stall detection, current sense output, current regulation, and protection circuitry.

The integrated speed regulation feature maintains maintains constant motor speed over varying battery voltages. The voltage regulation feature saves energy by driving the motor with a programmable lower terminal voltage. control in the device thereby reducing external components on a PCB and saving cost. The principle is based on counting the number of current ripples appearing in the motor current waveform due to commutations.

The DRV8235 contains PWM and PH/EN interfaces along with an I<sup>2</sup>C interface for configuration and detailed diagnostics. The EN/IN1 & PH/IN2 pins control the full bridge, which consists of four N-channel MOSFETs that have a typical  $R_{DS(ON)}$  of 600m $\Omega$  (including one high-side and one low-side FET). Motor speed can be controlled with pulse-width modulation (PWM), at frequencies between 0 to 200kHz. The PMODE bit in I<sup>2</sup>C registers allows to control the H-bridge solely through I<sup>2</sup>C commands, reducing the number of GPIO inputs.

The integrated current regulation feature limits motor current to a predefined maximum based on the VREF and IPROPI settings. The IPROPI signal can provide current feedback to a microcontroller during both the drive and brake/slow-decay states of the H-bridge. The DRV8235 also has I<sup>2</sup>C programmable registers to configure a hardware stall detection feature based on the IPROPI current sensing signal.

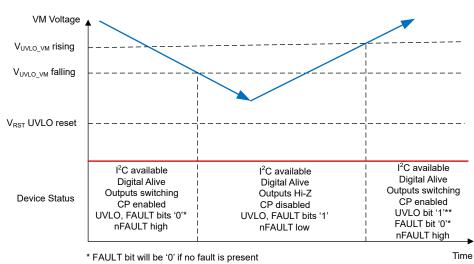

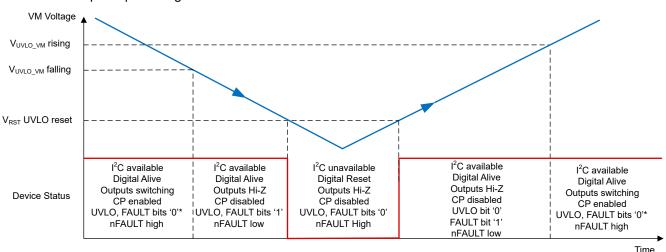

The integrated protection features protect the device in case of a system fault. These include undervoltage lockout (UVLO), overcurrent protection (OCP), and overtemperature shutdown (TSD). Fault conditions are indicated on the nFAULT pin. Additionally, the overvoltage protection (OVP) feature puts the driver into the brake state when the motor is spun manually while the device is in sleep mode or when the H-bridge is disabled. This prevents the back EMF induced high voltages on the supply rail that could potentially damage the driver and other circuits in the system.

To reduce area and external components on a printed circuit board, the device integrates a charge pump regulator and the corresponding capacitors. The nSLEEP pin provides an ultra-low power mode to minimize current draw during system inactivity.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

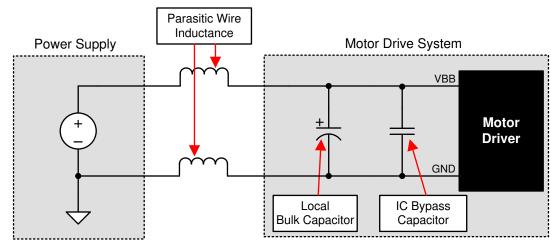

## 7.3.1 External Components

## Table 7-1 lists the recommended external components for the device.

| Table 7-1. Recommended External Components |                     |        |                                                                     |  |  |

|--------------------------------------------|---------------------|--------|---------------------------------------------------------------------|--|--|

| COMPONENT                                  | PIN 1               | PIN 2  | RECOMMENDED                                                         |  |  |

| C <sub>VM1</sub>                           | VM                  | GND    | 0.1µF, low ESR ceramic capacitor, VM-rated.                         |  |  |

| C <sub>VM2</sub>                           | VM                  | GND    | Bulk Capacitance, VM-rated.                                         |  |  |

| R <sub>IPROPI</sub>                        | IPROPI              | GND    | Resistor from IPROPI pin to GND, sets the current regulation level. |  |  |

| R <sub>nFAULT</sub>                        | System<br>VCC       | nFAULT | 10kΩ                                                                |  |  |

| R <sub>Pull-up</sub>                       | SDA, SCL,<br>A0, A1 | VM     | 2.2kΩ                                                               |  |  |

## 7.3.2 Summary of Features

This section includes a summary of the key and advanced features of DRV8235.

- 1. DRV8235 Functional Block Diagram

- 2. Current Sense and Regulation (IPROPI)

- 3. Bridge Control

- 4. Protection

- 5. Advanced: Stall Detection

- 6. Advanced: Speed and Voltage Regulation

- 7. Advanced: Soft-Start and Soft-Stop using t<sub>INRUSH</sub>

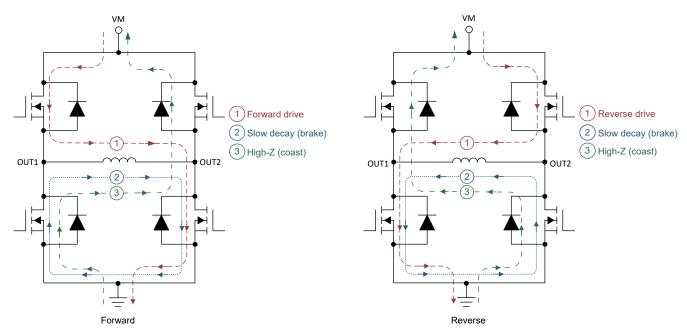

## 7.3.3 Bridge Control

The DRV8235 output consists of four N-channel MOSFETs designed to drive high current. These outputs are controlled by the two inputs EN/IN1 and PH/IN2 or the I<sup>2</sup>C bits I2C\_EN\_IN1 and I2C\_PH\_IN2.

The I2C\_BC bit determines whether the bridge is controlled by the EN/IN1 and PH/IN2 pins or the I2C\_EN\_IN1 and I2C\_PH\_IN2 bits, as shown below.

| I2C_BC | Description                                                            |  |  |

|--------|------------------------------------------------------------------------|--|--|

| Ob     | Bridge control configured by using the EN/IN1 and PH/IN2 pins.         |  |  |

| 1b     | Bridge control configured by using the I2C_EN_IN1 and I2C_PH_IN2 bits. |  |  |

Table 7-2. H-Bridge Control Interface

The control interface is selected by the PMODE bit. DRV8235 allows users to choose either Phase-Enable mode or PWM mode, as described below.

## Table 7-3. PMODE Functions

| PMODE | Control Mode |

|-------|--------------|

| Ob    | PH/EN        |

| 1b    | PWM          |

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. Following diagram shows how the motor current flows through the H-bridge. The input pins can be powered before VM is applied.

Figure 7-1. H-Bridge Current Paths

The truth tables for each control mode are shown below. Note that these tables do not take into account the internal current regulation feature. Additionally, when an output changes from driving high to driving low (or driving low to driving high), dead time is automatically inserted to prevent shoot-through.

PH/EN mode allows for the H-bridge to be controlled with a speed and direction type of interface. The truth table for PH/EN mode is shown below.

| nSLEEP | Enable | Phase | OUT1   | OUT2   | Description                               |

|--------|--------|-------|--------|--------|-------------------------------------------|

| 0      | Х      | Х     | High-Z | High-Z | Sleep Mode (H-bridge High-Z)              |

| 1      | 1      | 0     | L      | Н      | Reverse (Current OUT2 $\rightarrow$ OUT1) |

| 1      | 1      | 1     | Н      | L      | Forward (Current OUT1 $\rightarrow$ OUT2) |

| 1      | 0      | Х     | L      | L      | Brake; low-side slow decay                |

Table 7-4. PH/EN Control Mode (PMODE = 0b)

#### Note

Enable refers to the EN pin when bridge control is external (I2C\_BC=0b), and the I2C\_EN\_IN1 bit when bridge control is internal (I2C\_BC=1b).

Phase refers to the PH pin when bridge control is external (I2C\_BC=0b), and the I2C\_PH\_IN2 bit when bridge control is internal (I2C\_BC=1b).

PWM mode allows for the H-bridge to enter the High-Z state while the device is awake. The truth table for PWM mode is shown below.

| Table 7-5. FWM Control Mode (FMODE – Tb) |        |        |        |        |                                           |

|------------------------------------------|--------|--------|--------|--------|-------------------------------------------|

| nSLEEP                                   | Input1 | Input2 | OUT1   | OUT2   | Description                               |

| 0                                        | Х      | Х      | High-Z | High-Z | Sleep Mode (H-bridge High-Z)              |

| 1                                        | 0      | 0      | High-Z | High-Z | Coast (H-bridge High-Z)                   |

| 1                                        | 0      | 1      | L      | Н      | Reverse (Current OUT2 $\rightarrow$ OUT1) |

| 1                                        | 1      | 0      | Н      | L      | Forward (Current OUT1 $\rightarrow$ OUT2) |

| 1                                        | 1      | 1      | L      | L      | Brake; low-side slow decay                |

# Table 7-5. PWM Control Mode (PMODE = 1b)

#### Note

Input1 refers to the IN1 pin when bridge control is external (I2C\_BC=0b), and the I2C\_EN\_IN1 bit when bridge control is internal (I2C\_BC=1b).

Input2 refers to the IN2 pin when bridge control is external (I2C\_BC=0b), and the I2C\_PH\_IN2 bit when bridge control is internal (I2C\_BC=1b).

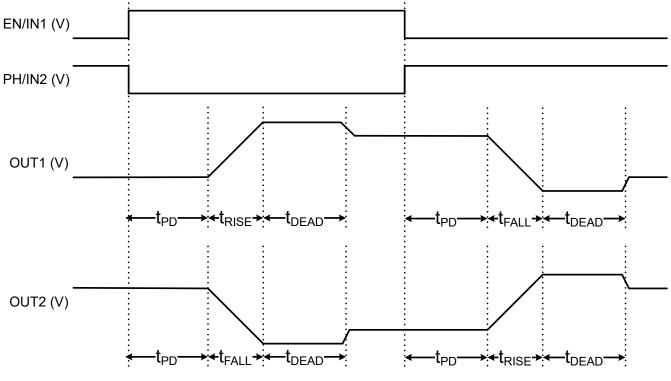

The following timing diagram shows the timing of the inputs and outputs of the motor driver.

The  $t_{DEAD}$  time is the time in the middle when the output is High-Z. The output pin voltage during  $t_{DEAD}$  depends on the direction of the output current. If the current is sourced from the pin, the voltage is a diode voltage drop below ground. If the current is sunk to pin, the voltage is a diode voltage drop above VM. This diode is the body diode of the high-side or low-side FET.

The propagation delay time  $(t_{PD})$  is measured as the time between an input edge to output change. This time accounts for input deglitch time and other internal logic propagation delays. The input deglitch time prevents noise on the input pins from affecting the output state. Additional output slew delay timing accounts for FET turn on or turn off times ( $t_{RISE}$  and  $t_{FALL}$ ).

## 7.3.4 Current Sense and Regulation (IPROPI)

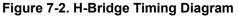

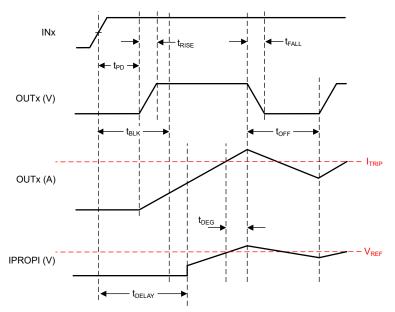

The DRV8235 integrates current sensing, regulation, and current sense feedback. The internal current mirror allows the device to sense the output current without an external sense resistor or sense circuitry, thereby reducing system size, cost, and complexity. The current regulation feature allows for the device to limit the output current in case of motor stall or high load torque events. The IPROPI output provides a current output proportional to the load current. This  $I_{IPROPI}$  current can be converted to a  $V_{IPROPI}$  output voltage by connecting a suitable resistor  $R_{IPROPI}$  from this pin to the circuit ground. The following diagram shows the IPROPI timings specified in the Electrical Characteristics table.

## 7.3.4.1 Current Sensing

The IPROPI pin outputs an analog current proportional to the current flowing through the low-side power MOSFETs in the H-bridge and scaled by the current mirror gain ( $A_{IPROPI}$ ). The IPROPI output current can be calculated by the following equation. The I<sub>LSx</sub> in the equation is only valid when the current flows from drain to source in the low-side MOSFET. If current flows from source to drain or through the body diode, the value of I<sub>LSx</sub> for that channel is zero. For instance, if the bridge is in the brake, slow-decay state, then the current out of IPROPI is only proportional to the current in one of the low-side MOSFETs.

$$I_{PROPI}$$

( $\mu A$ ) = ( $I_{LS1}$  +  $I_{LS2}$ ) (A) x A<sub>IPROPI</sub> ( $\mu A/A$ )

(1)

The  $A_{ERR}$  parameter in the Electrical Characteristics table is the error associated with the  $A_{IPROPI}$  gain. It indicates the combined effect of offset error added to the  $I_{OUT}$  current and gain error. The current mirror gain  $A_{IPROPI}$  is fixed at 1500  $\mu$ A/A.

The motor current is measured by an internal current mirror architecture on the low-side FETs which removes the need for an external power sense resistor as shown below. The current mirror architecture senses motor winding current in both the drive and brake low-side slow-decay periods, therefore allowing continuous current monitoring in typical bidirectional brushed DC motor applications. In coast mode, the current is freewheeling and cannot be sensed because it flows from source to drain. However, the current can be sampled by briefly reenabling the driver in either drive or slow-decay modes and measuring the current before switching back to coast mode again.

Copyright © 2017, Texas Instruments Incorporated

## Figure 7-4. Integrated Current Sensing

The IPROPI pin should be connected to an external resistor ( $R_{IPROPI}$ ) to ground in order to generate a proportional voltage ( $V_{IPROPI}$ ) on the IPROPI pin with the  $I_{IPROPI}$  analog current output. This allows for the load current to be measured as the voltage drop across the  $R_{IPROPI}$  resistor with a standard analog to digital converter (ADC). The  $R_{IPROPI}$  resistor can be sized based on the expected load current in the application so that the full range of the controller ADC is utilized. Additionally, the DRV8235 implements an internal IPROPI voltage clamp circuit to limit  $V_{IPROPI}$  with respect to  $V_{VREF}$  on the VREF pin and protect the external ADC in case of output overcurrent or unexpected high current events. TI recommends designing for at least 1.25 V of headroom between  $V_{VM}$  and the maximum  $V_{IPROPI}$  voltage to be measured by the ADC,  $V_{IPROPI\_MAX}$ . This ensures good accuracy across the range of VIPROPI voltages measured by the ADC. For instance, if  $V_{VM}$  is 4.55 V to 11 V,  $V_{IPROPI\_MAX}$  can be as high as 3.3 V. However, if  $V_{VM}$  is 3.3 V, then VIPROPI will have good accuracy up to 2.05 V.

The corresponding IPROPI voltage to the output current can be calculated as shown below -

$$V_{IPROPI}(V) = I_{PROPI}(A) \times R_{IPROPI}(\Omega)$$

(2)

The IPROPI output bandwidth is limited by the sense delay time ( $t_{DELAY}$ ) of the internal current sensing circuit. This time is the delay from the low-side MOSFET enable command (from the INx pins) to the IPROPI output being ready.

If the device is alternating between drive and slow-decay (brake) in an H-bridge PWM pattern then the low-side MOSFET sensing the current is continuously on and the sense delay time has no impact to the IPROPI output. If a command on the INx pins disables the low-side MOSFETs (according to the truth tables), the IPROPI output will disable with the input logic signal. Although the low-side MOSFETs may still conduct current as they disable according to the device slew rate (specified in the Electrical Characteristics table by t<sub>RISE</sub> time), IPROPI will not represent the current in the low-side MOSFETs during this turnoff time.

## 7.3.4.2 Current Regulation

The DRV8235 integrates current regulation using either a fixed off-time or a cycle-by-cycle PWM current regulation scheme. This allows the device to limit the output current in case of a motor stall, high torque, or other high current load events autonomously. The current regulation scheme is selectable by the REG\_CTRL bit in I<sup>2</sup>C.

The internal current regulation can be disabled by tying IPROPI to GND and setting the VREF pin voltage greater than GND if current feedback is not required. Additionally, current regulation can also be disabled by setting IMODE to 00b as explained below. If current feedback is required and current regulation is not required, set  $V_{VREF}$  and  $R_{IPROPI}$  such that  $V_{IPROPI}$  never reaches the  $V_{VREF}$  threshold. For proper operation of the current

regulation circuit, V<sub>VREF</sub> must be within the range of the VREF pin voltage specified in the Recommended Operating Conditions table.

| Bit* | Current Regulation Mode |

|------|-------------------------|

| 00b  | Fixed Off-Time          |

| 01b  | Cycle-By-Cycle          |

#### Table 7-6. REG\_CTRL Functions

Note

\*Additional REG\_CTRL options 10b and 11b allow selection between motor voltage or speed regulation described in Section 7.3.6.2.1.

The current regulation threshold ( $I_{TRIP}$ ) is set through a combination of the VREF voltage ( $V_{VREF}$ ) and IPROPI output resistor ( $R_{IPROPI}$ ). This is done by comparing the voltage drop across the external  $R_{IPROPI}$  resistor to  $V_{VREF}$  with an internal comparator.

$I_{TRIP}$  (A) x  $A_{IPROPI}$  ( $\mu$ A/A) =  $V_{VREF}$  (V) /  $R_{IPROPI}$  ( $\Omega$ )

(3)

For example, if  $V_{VREF}$  = 3.3 V,  $R_{IPROPI}$  = 1100  $\Omega$  and  $A_{IPROPI}$  = 1500  $\mu$ A/A, then  $I_{TRIP}$  will be approximately 2 A.

$V_{VREF}$  must be lower than  $V_{VM}$  by at least 1.25 V. The maximum recommended value of  $V_{VREF}$  is 3.3 V. If INT\_VREF bit is set to 1b,  $V_{VREF}$  is internally selected with a fixed value of 3 V.

The  $I_{TRIP}$  comparator has both a blanking time ( $t_{BLANK}$ ) and a deglitch time ( $t_{DEG}$ ). The internal blanking time helps to prevent voltage and current transients during output switching from affecting the current regulation. These transients may be caused by a capacitor inside the motor or motor terminals. The internal deglitch time ensures that transient conditions do not prematurely trigger the current regulation. In certain cases where the transient conditions are longer than the deglitch time, placing a 10-nF capacitor on the IPROPI pin, close to the device, helps filter the transients on IPROPI output so current regulation does not prematurely trigger. The capacitor value can be modified as needed, however large capacitor values may slow down the response time of the current regulation circuit.

The IMODE bits determine the behavior of current regulation for the motor driver.

- When IMODE is 00b, current regulation is disabled.

- When IMODE is 01b, the device performs current regulation only during the t<sub>INRUSH</sub> time when stall detection is enabled.

- When IMODE is 10b, current regulation is enabled at all times.

The following table summarizes the IMODE bit settings.

| IMODE EN_STALL Description |    | Description                                        |

|----------------------------|----|----------------------------------------------------|

| 00b                        | X  | No current regulation at any time                  |

| 01b                        | Ob | Current regulation at all times                    |

|                            | 1b | Current regulation during t <sub>INRUSH</sub> only |

| 1Xb                        | X  | Current regulation at all times                    |

## 7.3.4.2.1 Fixed Off-Time Current Regulation

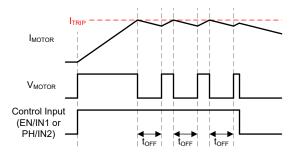

Figure 7-5. Fixed Off-Time Current Regulation

In the fixed off-time mode, the H-bridge enters a brake/low-side slow decay state (both low-side MOSFETs ON) for  $t_{OFF}$  duration after  $I_{OUT}$  exceeds  $I_{TRIP}$ . After  $t_{OFF}$  the outputs are re-enabled according to the control inputs unless  $I_{OUT}$  is still greater than  $I_{TRIP}$ . If  $I_{OUT}$  is still greater than  $I_{TRIP}$ , the H-bridge will enter another period of brake/low-side slow decay for  $t_{OFF}$ . If the state of the EN/IN1 or PH/IN2 control pin inputs or I2C\_EN\_IN1 or I2C\_PH\_IN2 bits changes during the  $t_{OFF}$  time, the remainder of the  $t_{OFF}$  time is ignored, and the outputs will again follow the inputs.

The fixed off-time mode allows for a simple current regulation scheme independent of the external controller. Fixed off-time mode will support 100% duty cycle current regulation since the H-bridge automatically enables after the  $t_{OFF}$  period and does not require a new control input edge on the control input pins or bits to reset the outputs.

## 7.3.4.2.2 Cycle-By-Cycle Current Regulation

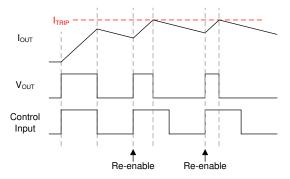

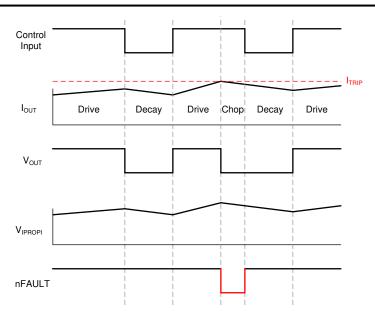

In cycle-by-cycle mode, the H-bridge enters a brake, low-side slow decay state (both low-side MOSFETs ON) after  $I_{OUT}$  exceeds  $I_{TRIP}$  until the next control input edge on either the EN/IN1 or PH/IN2 pins or 0 to 1 transitions on the I2C\_EN\_IN1 or I2C\_PH\_IN2 bits. This allows for additional control of the current regulation by the external controller. This is shown in the diagram below. Cycle-by-cycle mode will not support 100% duty cycle current regulation as a new control input edge is required to reset the outputs after the brake, low-side slow decay state has been entered.

Figure 7-6. Cycle-By-Cycle Current Regulation

In cycle-by-cycle mode, the device can indicate whenever the H-bridge enters internal current regulation by pulling the nFAULT pin low. This can be used to determine when the device outputs will differ from the control inputs or the load has reached the  $I_{TRIP}$  threshold. This behavior is controlled by the CBC\_REP bit. This is shown in the following diagram. In cycle-by-cycle mode, if the CBC\_REP bit is 1b, nFAULT will be pulled low when the H-bridge enters internal current regulation and nFAULT will be released whenever the next control input edge is received by the device and the outputs are reset.

Figure 7-7. Cycle-By-Cycle Current Regulation, CBC\_REP = 1b

No device functionality is affected when the nFAULT pin is pulled low for the current regulation indicator. The nFAULT pin is only used as an indicator and the device will continue normal operation. To distinguish a device fault from the current regulation indicator, the nFAULT pin can be compared with the control inputs. The current regulation indicator can only assert when the control inputs are commanding a forward or reverse drive state. If the nFAULT pin is pulled low and the control inputs are commanding the high-Z or slow-decay states, then a device fault has occurred.

## 7.3.5 Stall Detection

The DRV8235 integrates a stall detection feature. The principle of the stall detection scheme relies on the fact that motor current increases during stall conditions. The DRV8235 compares the voltage on the IPROPI pin to the voltage on the VREF pin or 3 V to determine whether a motor stall condition has occurred. The setting is deterimed by the INT\_VREF register. Table 7-8 shows the configurable options for INT\_VREF. The following paragraphs describe how to configure the I<sup>2</sup>C registers for the desired stall detection response.

| Bit | Description                               |  |  |

|-----|-------------------------------------------|--|--|

| Ob  | V <sub>VREF</sub> not fixed               |  |  |

| 1b  | V <sub>VREF</sub> fixed internally at 3 V |  |  |

## Table 7-8. Settings for INT\_VREF

The STALL bit in status register changes to 1b when a motor stall is detected. The EN\_STALL bit is used to enable or disable stall detection. The following table summarizes the EN\_STALL bit settings.

| Table 7-9. EN_STALL configuration |                                                                                                                   |  |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| EN_STALL Description              |                                                                                                                   |  |  |  |

| Ob                                | Stall detection disabled. If IMODE = 01b, current regulation occurs at all times when $V_{IPROPI} \ge V_{VREF}$ . |  |  |  |

| 1b                                | Stall detection enabled.                                                                                          |  |  |  |

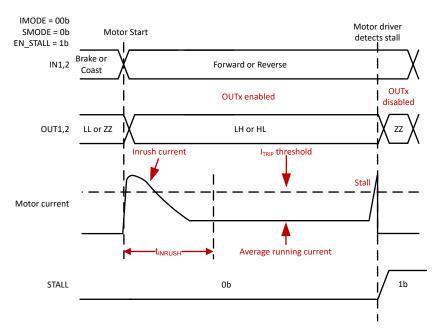

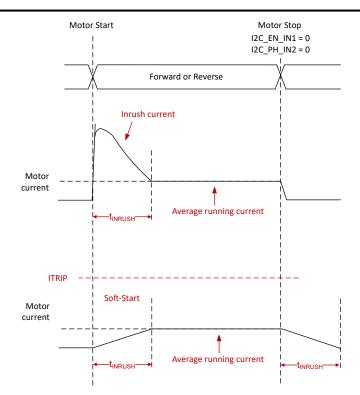

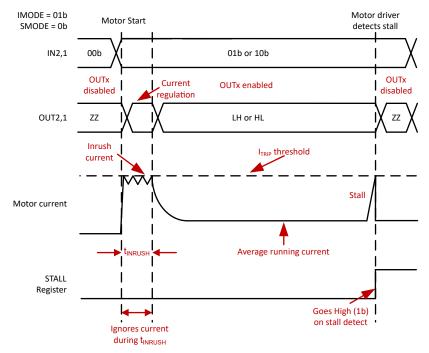

The IPROPI pin provides the current sense signal to the stall detection module. The VREF pin sets the  $I_{TRIP}$  current level at which a stall condition is detected. As shown in Table 7-8,  $V_{VREF}$  is internally fixed at 3 V when INT\_VREF = 1b. When  $V_{IPROPI} \ge V_{VREF}$ , it implies  $I_{OUT} \ge I_{TRIP}$ . The device detects a stall condition here. Stall detection is blanked for a period of time,  $t_{INRUSH}$ , to avoid false detection due to high inrush currents during motor startup. The IPROPI and VREF pins also support current regulation, as described earlier.

Copyright © 2024 Texas Instruments Incorporated

The TINRUSH[15:0] bits set the period of time the stall detection logic will ignore the inrush current during motor startup ( $t_{INRUSH}$ ). After  $t_{INRUSH}$  time expires, the DRV8235 indicates a stall condition the next instant  $V_{IPROPI}$  is greater than or equal to  $V_{VREF}$ .

When voltage or speed soft-start is disabled, the  $t_{INRUSH}$  time directly reflects the setting of the TINRUSH bits. The  $t_{INRUSH}$  can be set to a value between 5 ms (corresponding to 0000h) and 6.7 s (corresponding to FFFFh), with a default value of 1 s. Each increment of LSB corresponds to 102.4 µs of the inrush time.

When voltage or speed soft-start is enabled, target motor voltage or speed is soft-started and soft-stopped for the duration of  $t_{INRUSH}$  time. The TINRUSH bits should be setup such that the  $t_{INRUSH}$  = TINRUSH bit setting x WSET\_VSET. For example, if WSET\_VSET = 10 and intended inrush time is 1 s, then TINRUSH bit setting should correspond to 100 ms.

The following conditions cause the stall detection scheme to ignore the inrush current for t<sub>INRUSH</sub> time -

- Power-up of the DRV8235

- Recovering from faults

- · After device exits from sleep mode

- After recovering from stall, as explained in Table 7-10

The SMODE bit programs the device's response to a stall condition. When SMODE = 0b, the outputs disable, and the STALL bit becomes 1b. When SMODE = 1b, the STALL bit becomes 1b, but the outputs continue to drive current into the motor. Table 7-10 summarizes the SMODE bit settings.

| SMODE | Description                                                                          | Recovery from Stall Condition                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Ob    | Latched disable with indication: the OUTx pins disable and the STALL bit becomes 1b. | A clear fault must be issued by writing 1b to the CLR_FLT bit. STALL bit changes to 0b after a clear fault is issued. After waking up from stall, the stall detection scheme ignores the inrush current for $t_{INRUSH}$ time as described earlier. After $t_{INRUSH}$ time, if motor current is still higher than $I_{TRIP}$ , a stall condition is detected again. |  |  |

| 1b    | Indication only: the OUTx pins remain active and the STALL bit becomes 1b.           | A clear fault must be issued by writing 1b to the CLR_FLT bit to make STALL bit 0b. After $t_{\rm INRUSH}$ time, if motor current is still higher than $I_{\rm TRIP}$ , a stall condition is detected again.                                                                                                                                                         |  |  |

#### Table 7-10. SMODE configuration

The **IMODE** bits determine the behavior of current regulation in the motor driver. Table 7-7 summarizes the IMODE pin settings. For more details on current regulation, see Section 7.3.4.2.

The STALL\_REP bit determines whether stall is reported on nFAULT pin. When STALL\_REP bit is 1b, nFAULT is pulled low whenever stall is detected and STALL bit is 1b. If STALL\_REP bit is 0b, stall is not reported on nFAULT output.

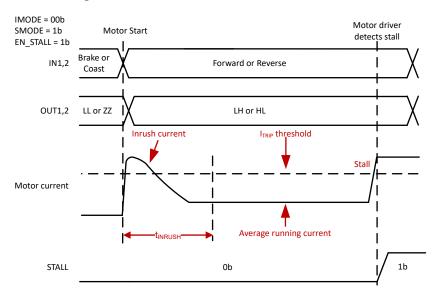

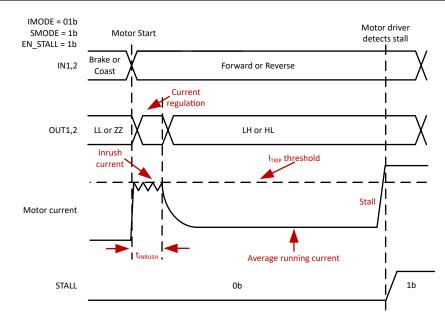

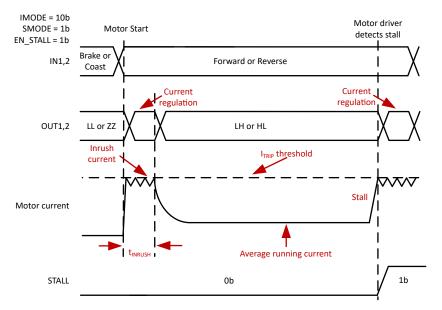

The following diagrams show example timing diagrams for different configurations of the hardware stall detection feature.

Figure 7-8. Stall Detection with Latched Disable

Figure 7-9. Stall Detection with STALL indication only

Figure 7-10. Stall Detection with current regulation during inrush

Figure 7-11. Stall Detection with current regulation

## 7.3.6 Motor Voltage and Speed Regulation

The DRV8235 provides the ability to regulate the voltage applied to the motor winding or to regulate the speed of the motor. This feature allows constant motor speed to be maintained even when operating from a varying supply voltage such as a discharging battery. The DRV8235 uses a pulse-width modulation (PWM) technique instead of a linear circuit to minimize current consumption and maximize battery life.

The intended voltage or speed can be programmed by the WSET\_VSET bits. Refer to Section 7.3.6.2.1 for further explanation.

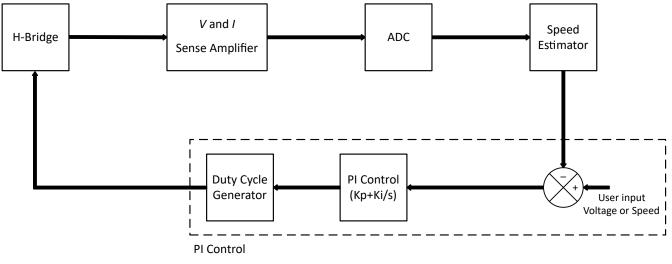

Four ranges of motor speed can be selected using the W\_SCALE bits to support low, moderate and high speed applications. The speed regulation loop compares the motor speed estimated by the speed estimator with the user definded target speed. The following section describes the internal bridge control logic taking voltage regulation as an example, but is also applicable for speed regulation.

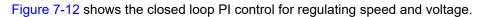

Figure 7-12. Speed and Voltage Regulation with PI Control

| Note                                                         |

|--------------------------------------------------------------|

| Please note that the sampling frequency of the ADC is 80kHz. |

# 7.3.6.1 Internal Bridge Control

For voltage regulation, an internal circuit monitors the voltage difference between the output pins. This voltage difference is integrated over time to get an average DC voltage value. The time depends on the cut-off frequency of the output filter which can be set by the OUT\_FLT register. For best results, choose a cut-off frequency equal to a value at least 20 times lower than the PWM frequency. Eg, if you PWM at 20kHz, OUT\_FLT=11b (1000Hz) is sufficient.

The DC voltage value is compared to the target motor voltage programmed by the I<sup>2</sup>C register, WSET\_VSET.

When speed/voltage regulation mode is active, an internal bridge control scheme is employed. DUTY\_CTRL must be set to 0b. The duty cycle cannot be manually programmed by the user.

- If the averaged output voltage is lower than VSET, the duty cycle of the internal bridge control output is increased.

- If the averaged output voltage is higher than VSET, the duty cycle of the internal bridge control output is decreased.

- During PWM regulation, the H-bridge is enabled to drive current through the motor winding during the PWM on time. The current flow direction depends on the EN/IN1 and PH/IN2 polarity.

- During the PWM off time, winding current is recirculated by enabling both of the low-side FETs in the bridge.

- If the programmed output voltage (VSET) is greater than the VM supply voltage, the device operates at 100% duty cycle and the voltage regulation feature is disabled. In this mode, the device behaves like a conventional H-bridge driver.

#### Note

- 1. During Speed/Voltage regulation, the duty cycle can be read from the DUTY\_READ register

- PWM\_FREQ sets the PWM frequency for internal PWM generation. Variation around the value of PWM\_FREQ is ±30%.

## Table 7-11. PWM\_FREQ Settings

| Bit | Value  |

|-----|--------|

| Ob  | 50 kHz |

| 1b  | 25 kHz |

#### Note

In voltage regulation mode, the motor speed can vary slightly because the voltage drop across the motor coil resistance introduces a small error. The speed regulation mode eliminates this error by directly regulating the target motor speed. To enable speed regulation, the REG\_CTRL bit must be set to 10b.

#### Note

When Speed/Voltage regulation is inactive, the user can still PWM internally. To do this, set DUTY\_CTRL to 1b and program the duty cycle value into PROG\_DUTY. Please note that in this case, I2C\_BC is used to decide if the information about the direction or rotation (Forward/Reverse/Coast/Brake/Sleep) is extracted:

- 1. Externally, from the EN/IN1 and PH/IN2 pins; I2C\_BC=0b), or

- 2. Internally (from the I2C\_EN\_IN1 and I2C\_PH\_IN2 bits; I2C\_BC=1b)

Please note that the setting for PMODE does not matter in this case.

As an example, if the settings in Table 7-12 are followed, the device PWMs at 50kHz with approximately 50% duty cycle in the forward direction.

| Table 7-12. Example settings |  |  |  |  |

|------------------------------|--|--|--|--|

| Value                        |  |  |  |  |

| 1b                           |  |  |  |  |

| 1b                           |  |  |  |  |

| 1b                           |  |  |  |  |

| Ob                           |  |  |  |  |

| 011111b                      |  |  |  |  |

| 1b                           |  |  |  |  |

| Ob                           |  |  |  |  |

|                              |  |  |  |  |

# 7.3.6.2 Setting Speed/Voltage Regulation Parameters

For obtaining an accurate output from speed and voltage regulation, the following parameters need to be set (for an in-depth explanation, refer to Section 8).

## 7.3.6.2.1 Speed and Voltage Set

Denoted by WSET\_VSET, this parameter helps set the target speed or motor voltage, based on the REG\_CTRL register setting.

When REG\_CTRL is set to 10b, the speed regulation mode is enabled. WSET\_VSET is an 8-bit register and can be set to a value between 00h (corresponds to 0 rad/s) and FFh (corresponds to the maximum speed allowable by W\_SCALE). The speed control loop matches the value of the SPEED register to the target speed set by WSET\_VSET. Please note that the maximum value of the SPEED register is 255.

When REG\_CTRL is set to 11b, the motor voltage regulation mode is enabled. The motor voltage in this case can be set to a value between 0 for 0V and 255 for approximately 42.67V drive output voltage. Please note that the maximum value of WSET\_VSET is 255. Each bit corresponds to approximately a 0.167mV resolution of the

output voltage setting. Setting WSET\_VSET to 255 sets the target voltage to approximately 42.7V. The formula to calculate the decimal value is represented by the equation:

Register Setting Value = Desired Target Voltage

$$\times \left(\frac{255}{42.67}\right)$$

(4)

For example, if desired target voltage is 5V, Register Setting Value = 5\*(255/42.67) = 29.88. Hence, setting a value of 30 (or 1Eh) outputs approximately 5V.

#### Note

- 1. In practice, the driver's Over Voltage Protection shuts the device down before 42.67V.

- 2. The maximum voltage for VM under Section 6.3 is 38V.

- a. Recommended to set the target voltage below 38V for better accuracy.

- 3. To set the target voltage to 38V, set WSET\_VSET to 227.

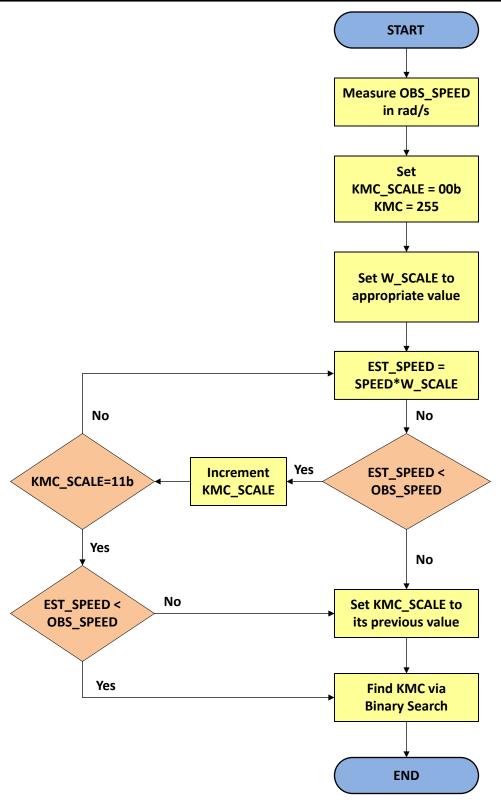

## 7.3.6.2.2 Speed Scaling Factor

Denoted by W\_SCALE, this is a scaling factor which helps in setting the target ripple speed when speed regulation mode is enabled. Settings for W\_SCALE are shown below. This register also sets the maximum value of ripple speed under each setting of W\_SCALE.

| Bit | W_SCALE | Maximum Ripple Speed |  |  |  |  |

|-----|---------|----------------------|--|--|--|--|

| 00b | 16      | 4080 rad/s           |  |  |  |  |

| 01b | 32      | 8160 rad/s           |  |  |  |  |

| 10b | 64      | 16320 rad/s          |  |  |  |  |

| 11b | 128     | 32640 rad/s          |  |  |  |  |

| Table | 7-13  | Settings | for W | SCALE |

|-------|-------|----------|-------|-------|

| Table | 1-10. | ocungs   |       | UUALL |

Example setting for W\_SCALE: If SPEED register = 15, W\_SCALE = 01b, then the actual ripple speed = 15\*32=480 rad/s.

## Note

Explanation for Maximum Ripple Speed: W\_SCALE inadvertently sets the upper limit for the target ripple speed under that setting of W\_SCALE. For example, if W\_SCALE = 00b, then the maximum ripple speed under this setting = 255\*16 rad/s = 4080 rad/s. Hence, the maximum target speed achievable under this setting is 4080 rad/s. Furthermore, under this setting of W\_SCALE, FFh corresponds to 4080 rad/s for WSET\_VSET when speed regulation mode is activated (REG\_CTRL=10b).

## 7.3.6.2.2.1 Target Speed Setting Example

To set a target speed in rpm, you need to know the following information:

- Gear ratio of the system, GR

- Number of current ripples per motor revolution, N<sub>R</sub>. This can be found by taking the lowest common multiple, LCM, of the number of brushes (N<sub>B</sub>) and the number of commutator segments (N<sub>C</sub>). LCM can easily be calculated using an online calculator.

- Choose an appropriate W\_SCALE value.

As an example, if desired target speed is 10000rpm, WSET\_VSET value can be calculated using the following equation :

WSET\_VSET =

$$\frac{\text{rpm}}{\text{W} \text{ SCALE}} \times \frac{2\pi}{60} \times \text{N}_{\text{R}} \times \text{Gear Ratio}$$

Assuming:

(5)

25

Denoted by INV\_R, this is the equivalent of the conductance (inverse of resistance) of the motor scaled by a scaling factor, INV\_R\_SCALE. Scaling allows a wide range of motor resistance values to be accepted using the combination of INV\_R and INV\_R\_SCALE.

## 7.3.6.2.4 Motor Resistance Inverse Scale

Denoted by INV\_R\_SCALE, this is the scaling factor for the inverse of motor resistance (INV\_R). Since the inverse of a motor resistance is generally not an integer, the value must be rounded off to the nearest integer. Settings are described in Table 7-14.

| Table 7-14. Settings for INV_R_SCALE |      |  |  |  |  |

|--------------------------------------|------|--|--|--|--|

| Bit Value of INV_R_SCALE             |      |  |  |  |  |

| 00b                                  | 2    |  |  |  |  |

| 01b                                  | 64   |  |  |  |  |

| 10b                                  | 1024 |  |  |  |  |

| 11b                                  | 8192 |  |  |  |  |

INV\_R is represented by the equation:

$$INV_R = \frac{1}{Motor Resistance} \times INV_R_SCALE$$

Please note that the maximum value of INV\_R is 255. Please refer to Section 9.2.3.1.1 for an example on how to select the appropriate INV\_R\_SCALE for a given value of motor resistance.

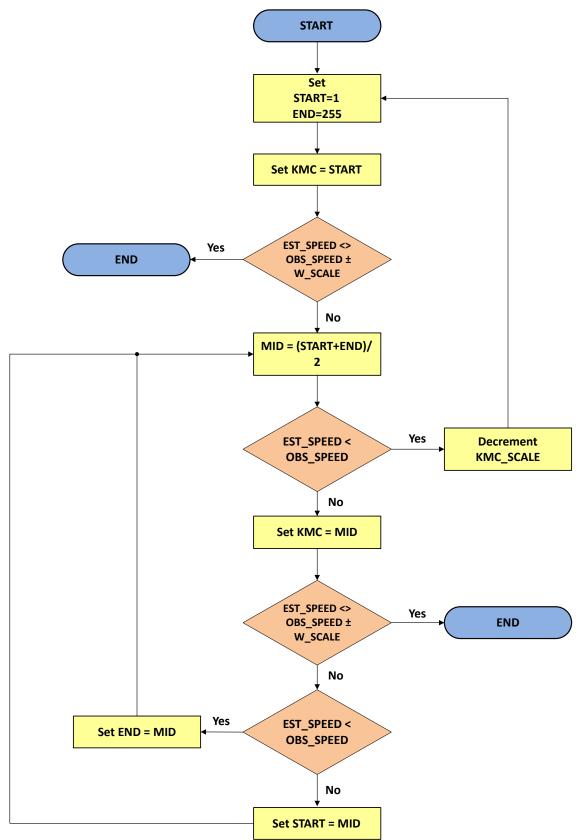

# 7.3.6.2.5 KMC Scaling Factor

Denoted by KMC\_SCALE, this is a scaling factor for the parameter KMC. KMC is represented by the following equation:

$$KMC = \frac{K_V}{N_R} \times KMC\_SCALE$$

(8)

Where,  $K_V$  is the motor back emf constant and  $N_R$  is the number of ripples per revolution.  $N_R$  is calculated by taking the LCM (Least Common Multiple) of the number of brushes,  $N_B$ , and the number of commutators,  $N_C$ :

$$N_{\rm R} = \rm LCM(N_{\rm B}, N_{\rm C}) \tag{9}$$

Please note that LCM can be easily calculated by using any online LCM calculator.

Tuning KMC appropriately is critical for the speed and voltage regulation algorithm to perform accurately. Scaling is done because the value of motor back emf constant is generally small. Scaling allows integer values to be written on to registers.

Gear ratio = 50:1

W\_SCALE = 00b (16 rad/s)

WSET\_VSET =  $\frac{10000 \text{rpm}}{16} \times \frac{2\pi}{60} \times 6 \times \frac{1}{50} = 7.86$

N<sub>R</sub>=6

Copyright © 2024 Texas Instruments Incorporated

(7)

| Table 7-15. Settings for KMC_SCALE |                      |  |  |  |  |

|------------------------------------|----------------------|--|--|--|--|

| Bit                                | Value of KMC_SCALE   |  |  |  |  |

| 00b                                | 24 x 2 <sup>8</sup>  |  |  |  |  |

| 01b                                | 24 x 2 <sup>9</sup>  |  |  |  |  |

| 10b                                | 24 x 2 <sup>12</sup> |  |  |  |  |

| 11b                                | 24 x 2 <sup>13</sup> |  |  |  |  |

.....

#### 7.3.6.2.6 KMC

This register is a motor constant representing a proportional value of the motor back emf constant. See KMC Tuning for a detailed tuning procedure.

#### 7.3.6.2.7 VSNS\_SEL

This parameter is used to select the motor voltage output filtering method (analog or digital) during PWM. The analog filter (0b) filters out the noise based on the voltage difference between the output pins. The digital filter (1b) multiplies the PWM duty cycle with VM to render an average output voltage. Settings are shown in Table 7-16. When analog filter is selected, the cut-off frequency can be selected using the OUT FLT register. Recommended setting is the analog filter (0b).

| Table 7-16. Settings for VSNS_SEL |                       |  |  |  |

|-----------------------------------|-----------------------|--|--|--|

| Bit Description                   |                       |  |  |  |

| Ob                                | Analog Output Filter  |  |  |  |

| 1b                                | Digital Output Filter |  |  |  |

## 7.3.6.3 Soft-Start and Soft-Stop

The DRV8235 integrates a soft-start and stop feature to safeguard the device from high inrush currents during start up. This feature can be activated by setting the EN SS bit to 1b when the REG CTRL register is set to 10b (Speed Regulation) or 11b (Voltage Regulation). If speed or voltage regulation modes are inactive, the EN SS bit has no influence on the device performance.

Soft-start comes into effect during motor start up. The motor current is slowly ramped up to the current value corresponding to the target speed over the duration of t<sub>INRUSH</sub> time. The inrush time t<sub>INRUSH</sub> can be set by the user via the 16-bit TINRUSH register. During this time t<sub>INRUSH</sub>, the FETs are internally PWMed with a duty cycle generated using the PI control loop.

Soft-stop results in a slow ramp down of motor current in time t<sub>INRUSH</sub>. This can be triggered by the following methods: