**DRV7308** SLVSGJ9 – MAY 2024

# DRV7308 Three Phase 650V, 5A, GaN Intelligent Power Module

#### 1 Features

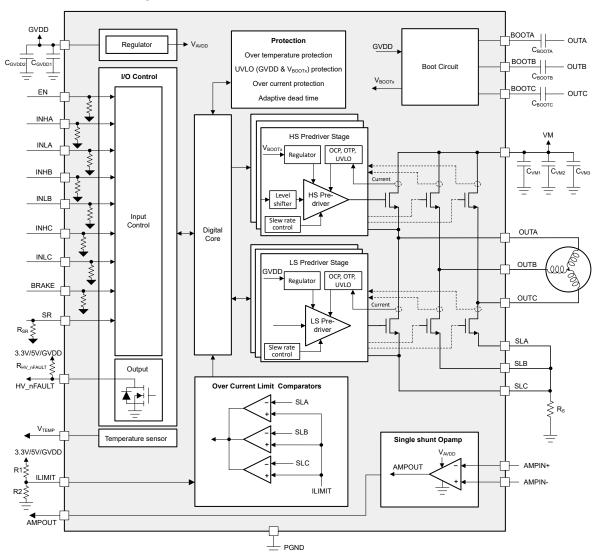

- Three-phase PWM motor driver with integrated 650V enhancement mode GaNFETs

- · Up to 450V operating voltage

- 650V absolute maximum voltage

- High output current capability: 5A Peak current

- Low conduction loss: Low on-state resistance per GaN FET: 205mΩ R<sub>DS(ON)</sub> at TA = 25°C

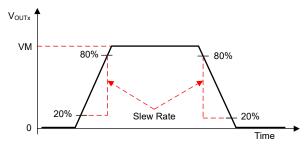

- Low switching loss: Zero reverse recovery, low output capacitance, slew rate control

- Low distortion: Ultra low propagation delay < 135ns, Ultra low adaptive dead time < 200ns</li>

- Integrated gate drives with slew rate control of phase node voltage

- Slew rate options from 5V/ns to 40V/ns

- 500ns minimum low side on time support with integrated fast bootstrap GaN rectifier

- Low-side GaN FET open source pins to support 1or 2- or 3-shunt current sensing

- Supports up to 60kHz hard switching

- Integrates a 11MHz, 15V/µs amplifier for single shunt current sensing

- Supports 3.3V and 5V logic inputs

- Integrated BRAKE functionality to turn on all low side GaN FETs together

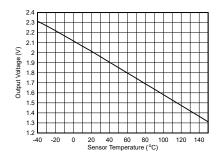

- Integrated temperature sensor

- >1.6mm clearance between OUTx and OUTx, VM and OUTx and OUTx and PGND.

- 2mm clearance between VM and PGND

- Integrated protection features

- GVDD and bootstrap under voltage lockout

- Over current protection for each GaN FET

- Over temperature protection

- PWM input dead time

- Current limit protection using integrated comparators for all three phases

- Fault condition indication pin (HV nFAULT)

- Appliances and HVAC pumps and fans

- Dishwasher

- Small home appliances

- · Residential air conditioners

- Cooker hood

- · Brushless-DC motor modules

## 3 Description

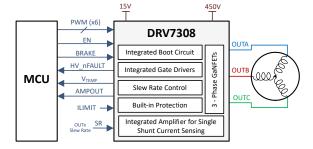

The DRV7308 is a three-phase intelligent power module (IPM) that consists of  $205m\Omega$ , 650V e-mode Gallium-Nitride (GaN) for driving three-phase BLDC/PMSM motors up to 450V DC rails. The applications include field-oriented control (FOC), sinusoidal current control, and trapezoidal (six step) current control of BLDC motors. The device helps to achieve more than 99% efficiency for a 3-phase modulated, FOC-driven, 250W motor drive application in a QFN 12mm x 12mm package at 20kHz switching frequency, eliminating the need for heat sink. The device helps to achieve ultra quiet operation, with very low dead time. The integrated bootstrap rectifier with bootstrap current limit, eliminates the need for an external bootstrap diode.

#### Note

For safety, TI recommends the use of isolated test equipment with overvoltage and overcurrent protection. TI recommends using a safety enclosure when operating the device.

### **Package Information**

| PART NUMBER | PACKAGE (1)    | PACKAGE SIZE (2)  |

|-------------|----------------|-------------------|

| DRV7308     | REN (VQFN, 65) | 12.00mm x 12.00mm |

- For more information, see the Mechanical, Packaging, and Orderable Information.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

## 2 Applications

Refrigerator & freezer

**Simplified Schematic**

# **Table of Contents**

| 1 Features1                         | 12.1 Overview                           | 11               |

|-------------------------------------|-----------------------------------------|------------------|

| 2 Applications1                     |                                         |                  |

| 3 Description1                      |                                         |                  |

| 4 Pin Configuration and Functions3  |                                         | 16               |

| 5 Absolute Maximum Ratings5         | 13 Layout                               | 19               |

| 6 ESD Ratings5                      |                                         | 19               |

| 7 Recommended Operating Conditions5 |                                         | 19               |

| 8 Thermal Information6              |                                         | 19               |

| 9 Electrical Characteristics6       | 15 Mechanical, Packaging, and Orderable |                  |

| 10 Timing Diagrams 10               | Information                             | 20               |

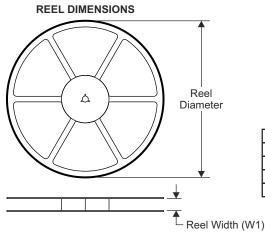

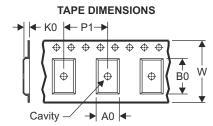

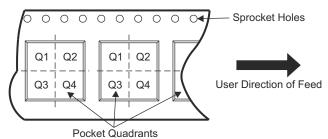

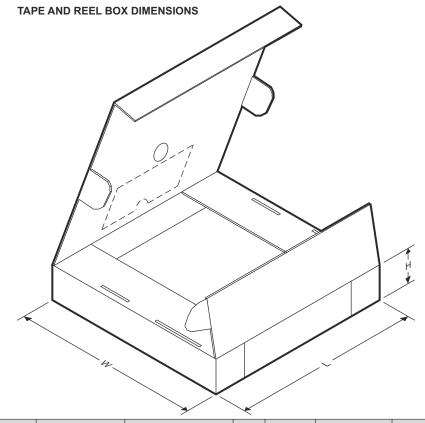

| 11 Typical Characteristics10        | 15.1 Tape and Reel Information          | <mark>2</mark> 0 |

| 12 Detailed Description11           | ·                                       |                  |

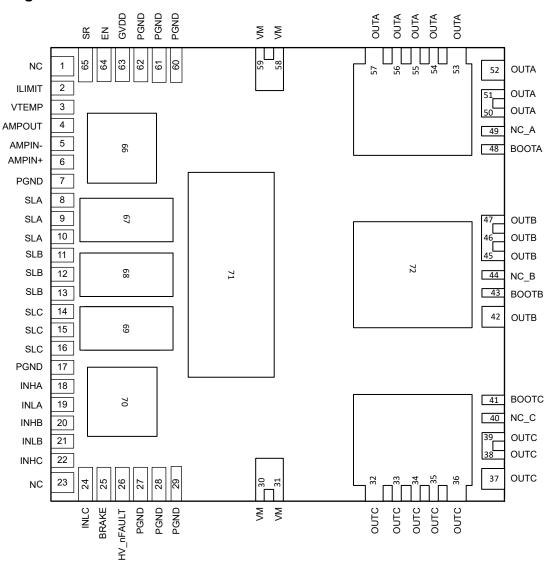

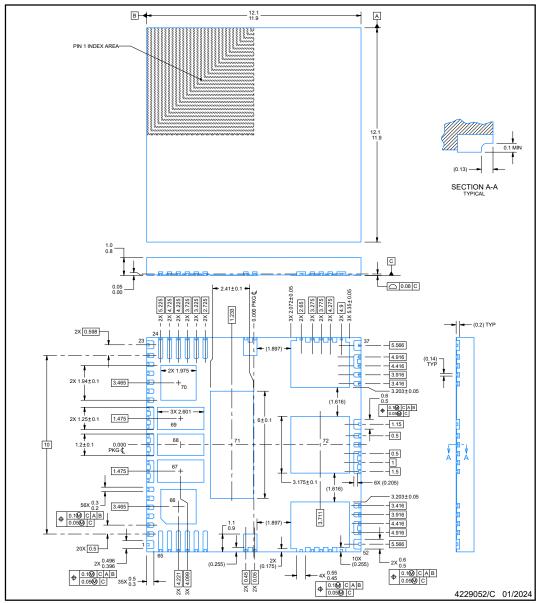

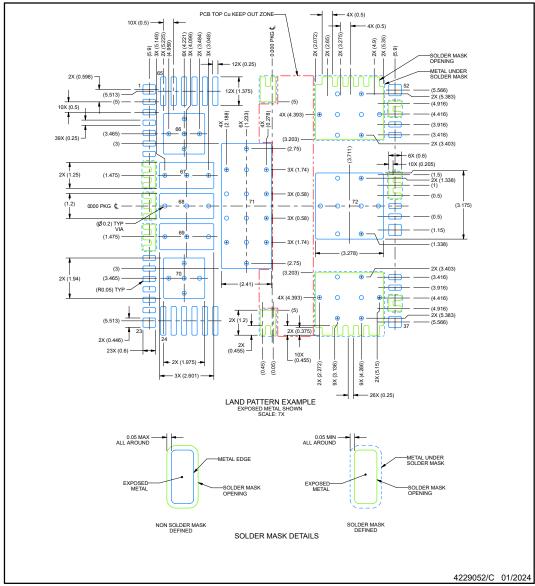

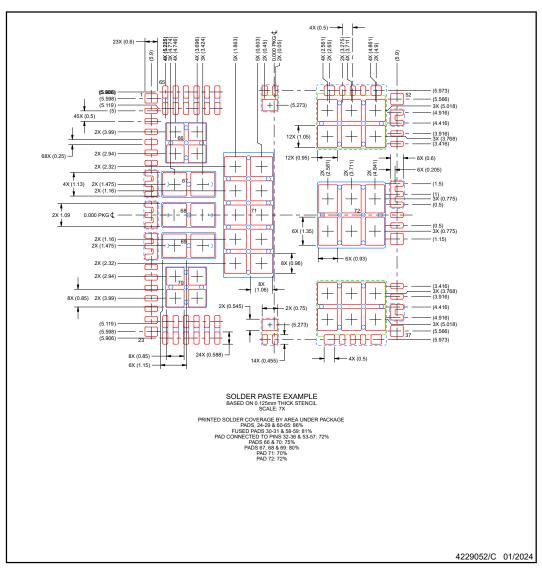

# **4 Pin Configuration and Functions**

Figure 4-1. DRV7308 VQFN With Exposed Thermal Pad Top View

### Table 4-1. Pin Functions

| PI        | IN                                            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                        |  |  |

|-----------|-----------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.                                           | I IPE               | DESCRIPTION                                                                                                                                                                        |  |  |

| AMPIN-    | 5                                             | ı                   | Inverting input of the operational amplifier                                                                                                                                       |  |  |

| AMPIN+    | 6                                             | ı                   | Non-inverting input of the operational amplifier                                                                                                                                   |  |  |

| AMPOUT    | 4                                             | 0                   | Output terminal of the operational amplifier                                                                                                                                       |  |  |

| воота     | 48                                            | Р                   | Bootstrap supply for phase A; bypass to OUTA with a GVDD rated capacitor                                                                                                           |  |  |

| воотв     | 43                                            | Р                   | Bootstrap supply for phase B; bypass to OUTB with a GVDD rated capacitor                                                                                                           |  |  |

| воотс     | 41                                            | Р                   | Bootstrap supply for phase C; bypass to OUTC with a GVDD rated capacitor                                                                                                           |  |  |

| BRAKE     | 25                                            | I                   | Motor Brake signal. Logic high on the pin turns on all the low side GaNFETs and turns off all the high side GaNFETs                                                                |  |  |

| EN        | 64                                            | I                   | Driver enable pin. When this pin is logic low the device goes to shutdown mode and all the GaN FETs are turned off. A 20µs to 40µs low pulse can be used to reset fault conditions |  |  |

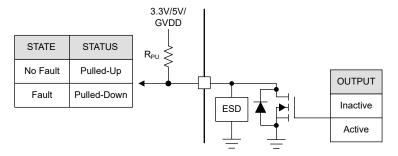

| HV_nFAULT | 26                                            | 0                   | Fault indication pin. Pulled logic-low on fault condition; open-drain output requires an external pullup                                                                           |  |  |

| ILIMIT    | 2                                             | I                   | Reference voltage for over current limit for internal comparator                                                                                                                   |  |  |

| INHA      | 18                                            | I                   | High-side driver control input for OUTA. This pin controls the output of the high-side GaNFET                                                                                      |  |  |

| INHB      | 20                                            | I                   | High-side driver control input for OUTB. This pin controls the output of the high-side GaNFET                                                                                      |  |  |

| INHC      | 22                                            | I                   | High-side driver control input for OUTC. This pin controls the output of the high-side GaNFET                                                                                      |  |  |

| INLA      | 19                                            | I                   | Low-side driver control input for OUTA. This pin controls the output of the Low-side GaNFET                                                                                        |  |  |

| INLB      | 21                                            | I                   | Low-side driver control input for OUTB. This pin controls the output of the Low-side GaNFET                                                                                        |  |  |

| INLC      | 24                                            | I                   | Low-side driver control input for OUTC. This pin controls the output of the Low-side GaNFET                                                                                        |  |  |

| NC        | 1, 23                                         |                     | No connect, can be connected to PGND                                                                                                                                               |  |  |

| NC_A      | 49                                            | ı                   | Can be connected to OUTA                                                                                                                                                           |  |  |

| NC_B      | 44                                            | ı                   | Can be connected to OUTB                                                                                                                                                           |  |  |

| NC_C      | 40                                            | ı                   | Can be connected to OUTC                                                                                                                                                           |  |  |

| OUTA      | 50-57                                         | Р                   | Half bridge output A                                                                                                                                                               |  |  |

| OUTB      | 42, 45-47, 72                                 | Р                   | Half bridge output B                                                                                                                                                               |  |  |

| OUTC      | 32-39                                         | Р                   | Half bridge output C                                                                                                                                                               |  |  |

| PGND      | 7, 17,<br>27,28,29,<br>60,61,62,66,<br>70, 71 | G                   | Device power and signal ground. Connect to system ground                                                                                                                           |  |  |

| SLA       | 8, 9, 10, 67                                  | Р                   | Phase A half bridge low side source                                                                                                                                                |  |  |

| SLB       | 11, 12, 13, 68                                | Р                   | Phase B half bridge low side source                                                                                                                                                |  |  |

| SLC       | 14, 15, 16, 69                                | Р                   | Phase C half bridge low side source                                                                                                                                                |  |  |

| SR        | 65                                            | I                   | OUTx voltage slew rate control. Connect a resistor between SR pin and PGND or SR pin to GVDD to configure the slew rate                                                            |  |  |

| GVDD      | 63                                            | Р                   | Low voltage power supply; bypass to PGND with one $1\mu F$ , GVDD rated ceramic capacitor plus one bulk capacitor rated for GVDD                                                   |  |  |

| VM        | 30, 31, 58, 59                                | Р                   | Power supply. Connect to motor supply voltage; bypass to PGND with a 0.1µF capacitor plus one bulk capacitor rated for VM                                                          |  |  |

| VTEMP     | 3                                             | 0                   | Temperature Sensor Output                                                                                                                                                          |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

Submit Document Feedback

# 5 Absolute Maximum Ratings

over operating temperature range (unless otherwise noted)(2)

|                                                              | MIN  | MAX                    | UNIT |

|--------------------------------------------------------------|------|------------------------|------|

| Drain-source blocking voltage (FET off) (V <sub>DS</sub> )   |      | 650                    | V    |

| DC voltage applied between VM and PGND                       |      | 450                    | V    |

| Drain DC current (I <sub>DC</sub> ) @ TJ = 150°C             |      | 4                      | Α    |

| Phase node pin voltage referred to PGND (OUTA, OUTB, OUTC)   | -10  | 650                    | V    |

| BOOTx pin voltage referred to OUTx (BOOTA, BOOTB, BOOTC) (1) | -0.5 | 20                     | V    |

| Pin voltage - GVDD to PGND (1)                               | -0.5 | 20                     | V    |

| Pin voltage - INx, EN, BRAKE, HV_nFAULT to PGND (1)          | -0.5 | 20                     | V    |

| Pin voltage - AMPIN+, AMPIN-, AMPOUT, ILIMIT, SR to PGND     | -0.5 | V <sub>GVDD</sub> +0.3 | V    |

| Operational amlifier output current (AMPOUT)                 |      | 20                     | mA   |

| Operating ambiient temperature                               | -40  | 125                    | °C   |

| Operating junction temperature (T <sub>J</sub> )             | -40  | 150                    | °C   |

| Storage temperature (T <sub>stg</sub> )                      | -55  | 150                    | °C   |

- (1) For PDRV7308 devices limit the voltage to less than 16V

- (2) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# **6 ESD Ratings**

|                    |                                                               |                                                                       | VALUE | UNIT |

|--------------------|---------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic<br>discharge (All<br>other pins -<br>pin names) | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | ٧    |

|                    | Electrostatic                                                 | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±1000 |      |

| V <sub>(ESD)</sub> | discharge<br>(VM, OUTx,<br>BOOT, NCx)                         | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **7 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                   |                                           |                       | MIN  | NOM | MAX  | UNIT |

|-------------------|-------------------------------------------|-----------------------|------|-----|------|------|

| V <sub>VM</sub>   | DC power supply voltage                   | VM                    | 0    |     | 450  | V    |

| V <sub>GVDD</sub> | Gate driver supply voltage (PDRV7308) (1) | GVDD                  | 10.8 |     | 15   | V    |

| f <sub>PWM</sub>  | PWM frequency                             | OUTA, OUTB, OUTC      |      | 20  | 60   | kHz  |

| V <sub>IN</sub>   | Logic Input Voltage                       | INHx, INLx, EN, BRAKE | -0.1 |     | 5    | V    |

| V <sub>OD</sub>   | Open drain pull up voltage                | HV_nFAULT             | -0.1 |     | 5    | V    |

| I <sub>OD</sub>   | Open drain output sink current            | HV_nFAULT             | 0    |     | 5    | mA   |

| V <sub>SR</sub>   | Slew rate pin voltage                     | SR                    |      |     | GVDD | V    |

| V <sub>SLx</sub>  | SLx pin voltage                           | SLA, SLB, SLC         | -1   |     | 1    | V    |

# 7 Recommended Operating Conditions (continued)

over operating temperature range (unless otherwise noted)

|                     |                                              |                | MIN  | NOM MAX | UNIT |

|---------------------|----------------------------------------------|----------------|------|---------|------|

| V <sub>AMPINx</sub> | Amplifier input pin voltage                  | AMPIN+, AMPIN- | -0.1 | 5       | V    |

| V <sub>ILIMIT</sub> | Over current protection reference            | ILIMIT         | 0.1  | 2       | V    |

| T <sub>ON_MIN</sub> | Minimum low side on time @ Fsw = 20kHz/16kHz |                | 0.5  |         | μs   |

| T <sub>A</sub>      |                                              |                | -40  | 100     | °C   |

| TJ                  |                                              |                | -40  | 125     | °C   |

<sup>(1)</sup> Recommended maximum voltage at GVDD pin of PDRV7308 is 15V

# **8 Thermal Information**

|                       |                                                         | DEVICE     |      |

|-----------------------|---------------------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                           | REN (VQFN) | UNIT |

|                       |                                                         | 40 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance                  | 21.2       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance               | 5.5        | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance                    | 6.0        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter              | 4.0        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter            | 5.8        | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance per GaNFET | 1          | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 9 Electrical Characteristics

$T_J = -40$ °C to 150°C,  $V_{GVDD} = 15$ V, EN = High (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{GVDD} = 15$ V

|                     | PARAMETER                                                             | TEST CONDITIONS                                                            | MIN TY | P MAX  | UNIT |

|---------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|--------|--------|------|

| GaN POW             | ER TRANSISTOR                                                         |                                                                            |        |        |      |

| R <sub>DS(ON)</sub> | GaN transistor on resistance                                          | V <sub>GVDD</sub> = 15V, I <sub>OUTx</sub> = 1A,T <sub>J</sub> = 25°C,     | 20     | )5 320 | mΩ   |

| R <sub>DS(ON)</sub> | GaN transistor on resistance                                          | V <sub>GVDD</sub> = 15V, I <sub>OUTx</sub> = 1A, T <sub>J</sub> = 150°C,   | 37     | 70     | mΩ   |

| V <sub>SD</sub>     | Third-quadrant mode source-drain voltage                              | INx = 0V, ISD = 0.1A, T <sub>J</sub> = 25°C                                | 1      | .5     | V    |

| V <sub>SD</sub>     | Third-quadrant mode source-drain voltage                              | INx = 0V, ISD = 4A, T <sub>J</sub> = 25°C                                  | 2      | .8     | V    |

| Q <sub>RR</sub>     | Reverse recovery charge                                               | $V_R = 300 \text{ V}, I_{SD} = 4 \text{ A}, dI_{SD}/dt = 0.2 \text{ A/ns}$ |        | 0      | nC   |

| SWITCHIN            | IG CHARACTERISTICS                                                    |                                                                            |        |        |      |

| SR                  | Phase pin slew rate switching low to high (Rising from 20 % to 80 %)  | V <sub>VM</sub> = 300V, SR setting = 0                                     |        | 5      | V/ns |

| SR                  | Phase pin slew rate switching high to low (Falling from 80 % to 20 %) | V <sub>VM</sub> = 300V, SR setting = 0                                     |        | 5      | V/ns |

| SR                  | Phase pin slew rate switching low to high (Rising from 20 % to 80 %)  | V <sub>VM</sub> = 300V, SR setting = 1                                     | ,      | 10     | V/ns |

| SR                  | Phase pin slew rate switching high to low (Falling from 80 % to 20 %) | V <sub>VM</sub> = 300V, SR setting = 1                                     | ,      | 10     | V/ns |

| SR                  | Phase pin slew rate switching low to high (Rising from 20 % to 80 %)  | V <sub>VM</sub> = 300V, SR setting = 2                                     | 2      | 20     | V/ns |

| SR                  | Phase pin slew rate switching high to low (Falling from 80 % to 20 %) | V <sub>VM</sub> = 300V, SR setting = 2                                     | 2      | 20     | V/ns |

# 9 Electrical Characteristics (continued)

$T_J$  = -40°C to 150°C,  $V_{GVDD}$  = 15V, EN = High (unless otherwise noted). Typical limits apply for  $T_A$  = 25°C,  $V_{GVDD}$  = 15V

| 15 10 0                      | PARAMETER                                                                          | TEST CONDITIONS                                                                                                                  | MIN TYP | MAX | UNIT |

|------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| OD                           | Phase pin slew rate switching low to high                                          |                                                                                                                                  |         |     | \//  |

| SR                           | (Rising from 20 % to 80 %)                                                         | V <sub>VM</sub> = 300V, SR setting = 3                                                                                           | 40      |     | V/ns |

| SR                           | Phase pin slew rate switching high to low (Falling from 80 % to 20 %)              | V <sub>VM</sub> = 300V, SR setting = 3                                                                                           | 40      |     | V/ns |

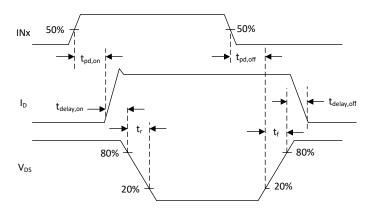

| t <sub>pd,on</sub>           | Propagation delay, turn on                                                         | $V_{INHx}$ , $V_{INLx}$ = logic low to high, $V_{VM}$ = 300V, $I_D$ = 4A, SR = 0                                                 |         | 125 | ns   |

| t <sub>delay,on</sub>        | Turn on delay time                                                                 | $V_{INHx}$ , $V_{INLx}$ = logic low to high, $V_{VM}$ = 300V, $I_D$ = 4A, SR = 0                                                 | 75      |     | ns   |

| t <sub>pd,off</sub>          | Propagation delay, turn off                                                        | $V_{INHx}$ , $V_{INLx}$ = logic high to low, $V_{VM}$ = 300V, $I_D$ = 4A, SR = 0                                                 |         | 135 | ns   |

| t <sub>delay,off</sub>       | Turn off delay time                                                                | $V_{INHx}$ , $V_{INLx}$ = logic high to low, $V_{VM}$ = 300V, $I_D$ = 4A, SR = 0                                                 | 75      |     | ns   |

| t <sub>DEAD</sub>            | Output dead time (high to low)                                                     | V <sub>VM</sub> = 300V, I <sub>OUTx</sub> = 4A, Current going out of phase node (OUTx)                                           | 40      |     | ns   |

| t <sub>DEAD</sub>            | Output dead time (high to low)                                                     | $V_{VM}$ = 300V, $I_{OUTx}$ = 4A, Current going in to phase node (OUTx), SR = 0                                                  | 100     |     | ns   |

| t <sub>DEAD</sub>            | Output dead time (high to low)                                                     | $V_{VM}$ = 300V, $I_{OUTx}$ = 4A, Current going in to phase node (OUTx), SR = 1 or 2 or 3                                        | 100     |     | ns   |

| t <sub>DEAD</sub>            | Output dead time (low to high)                                                     | $V_{VM}$ = 300V, $I_{OUTx}$ = 4A, Current going in to phase node (OUTx)                                                          | 40      |     | ns   |

| t <sub>MIN_PULSE</sub>       | Minimum input pulse width changing the output low-high-low                         | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V                                                                                  | 50      |     | ns   |

| t <sub>MIN_PULSE</sub>       | Minimum input pulse width changing the output high-low-high                        | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V                                                                                  | 50      |     | ns   |

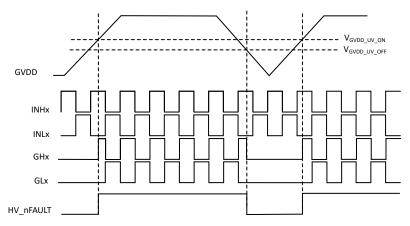

| t <sub>start</sub>           | Start up time                                                                      | V <sub>GVDD</sub> > V <sub>GVDD_UV_ON</sub> . EN = low to high,<br>INLx = 1, low side GaNFET turns ON                            |         | 2   | ms   |

| t <sub>off</sub>             | Device turn off time - to sleep                                                    | $V_{GVDD} > V_{GVDD\_UV\_ON}$ . EN = high to low                                                                                 | 40      | 80  | us   |

| tclr_flt                     | Time to clear any latched fault using EN                                           | EN = low pulse witdth                                                                                                            | 20      | 40  | us   |

| t <sub>off</sub>             | Device turn off time- gate driver off                                              | V <sub>GVDD</sub> > V <sub>GVDD_UV_ON</sub> . EN = high to low, INLx = 1, low side GaNFET turns OFF                              |         | 500 | ns   |

| <b>GVDD POW</b>              | ER SUPPLY                                                                          |                                                                                                                                  |         | '   |      |

| $I_{\text{GVDD,Q}}$          | GVDD operating curent, driver enabled, no switching                                | EN = High, V <sub>VM</sub> = 300V, V <sub>GVDD</sub> = 15V,<br>INx = 0                                                           | 4       |     | mA   |

| I <sub>GVDD,3SW</sub>        | GVDD average operating curent, driver enabled, GaN switching, No load at OUTx pins | EN = High, Fsw = $20kHz$ , 3-half bridge<br>switching at 50% complimentary PWM,<br>$V_{VM} = 300V$ , $V_{GVDD} = 15V$ , SR = $0$ | 6       |     | mA   |

| V <sub>GVDD_UV_O</sub>       | GVDD undervoltage turn on threshold                                                | GVDD rising                                                                                                                      |         | 10  | V    |

| V <sub>GVDD_UV_O</sub>       | GVDD undervoltage turn off threshold                                               | GVDD falling                                                                                                                     | 9       |     | V    |

| V <sub>GVDD_UV_H</sub><br>ys | GVDD undervoltge detection hysterisis                                              | GVDD rising to falling threshold                                                                                                 | 500     |     | mV   |

| t <sub>UVLO_GVDD</sub>       | GVDD undervoltage deglitch time                                                    |                                                                                                                                  |         | 20  | μs   |

| BOOTSTRA                     | P POWER SUPPLY                                                                     |                                                                                                                                  |         | l   |      |

| R <sub>DS_BST</sub>          | Bootsrtap rectifier on resistance                                                  | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V                                                                                  |         | 30  | Ω    |

| I <sub>LMT_BST</sub>         | Bootstrap rectifier current limit                                                  | EN = High, $V_{GVDD}$ = 15V, $V_{VM}$ = 300V, INLx = High, INHx = Low, $V_{BOOTx}$ - $V_{OUTx}$ = 12V                            | 150     | 250 | mA   |

| I <sub>BST_PK</sub>          | Bootstrap rectifier peak transient current                                         | EN = High, $V_{GVDD}$ = 15V, $V_{VM}$ = 300V,<br>INLx = High, INHx = Low, $V_{BOOTx}$ - $V_{OUTx}$<br>= 0 V                      | 350     |     | mA   |

# 9 Electrical Characteristics (continued)

$T_J = -40$ °C to 150°C,  $V_{GVDD} = 15$ V, EN = High (unless otherwise noted). Typical limits apply for  $T_A = 25$ °C,  $V_{GVDD} = 15$ V

| J .0 3                  | PARAMETER                                       | nless otherwise noted). Typical limits a                                                | MIN    | TYP  | MAX         | UNIT |

|-------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|--------|------|-------------|------|

|                         | PANAMETER                                       | EN = High, INHx = Low, INLx = Low,                                                      | IVIIIA | 111  | WAA         | ONIT |

| I <sub>BST_Q</sub>      | Bootstrap quiescent current                     | $V_{GVDD} = 15V$ , $V_{BOOTx} - V_{OUTx} = 12V$                                         |        | 100  |             | μA   |

| I <sub>BST_Q</sub>      | Bootstrap quiescent current                     | EN = High, INHx = High, INLx = Low,<br>$V_{GVDD}$ = 15V, $V_{BOOTx}$ - $V_{OUTx}$ = 12V |        | 350  |             | μΑ   |

| V <sub>BST_UV_ON</sub>  | Bootstrap supply undervoltage -turn on          |                                                                                         |        |      | 9           | V    |

| V <sub>BST_UV_OFF</sub> | Bootstrap supply undervoltage -turn off         |                                                                                         | 8      |      |             | V    |

| V <sub>BST_UV_HYS</sub> | Bootstrap supply undervoltage -hysterisis       |                                                                                         |        | 500  |             | mV   |

| t <sub>BST_UV</sub>     | Bootstrap supply undervoltage deglitch time     |                                                                                         |        |      | 20          | μs   |

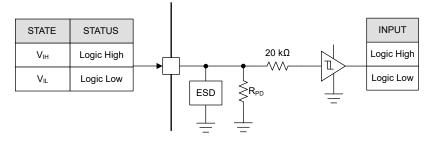

| LOGIC-LEVE              | EL INPUTS (EN, INHx, INLx, BRAKE)               | 1                                                                                       |        |      | · · · · · · |      |

| V <sub>IL</sub>         | Input logic low voltage                         | INHx, INLx, BRAKE, EN                                                                   |        |      | 0.8         | V    |

| V <sub>IH</sub>         | Input logic high voltage                        | INHx, INLx, BRAKE, EN                                                                   | 2.2    |      |             | V    |

| V <sub>HYS</sub>        | Input logic hysteresis                          | INHx, INLx, BRAKE, EN                                                                   |        | 400  |             | mV   |

| I <sub>IL</sub>         | Input logic low current (INHx, INLx, BRAKE, EN) | V <sub>I</sub> = 0 V                                                                    | -1     |      | 1           | μA   |

| I <sub>IL</sub>         | Input logic low current (BRAKE, EN)             | V <sub>1</sub> = 0 V                                                                    | -1     |      | 1           | μA   |

| R <sub>PD</sub>         | Input pulldown resistance                       | INHx, INLx, EN                                                                          | 70     | 100  | 130         | kΩ   |

| R <sub>PD</sub>         | Input pulldown resistance                       | BRAKE                                                                                   | 15     | 20   | 25          | kΩ   |

| t <sub>deg</sub>        | Input logic deglitch time                       | INHx, INLx                                                                              | 25     |      | 50          | ns   |

| t <sub>deg</sub>        | Input logic deglitch time                       | EN                                                                                      | 150    |      | 400         | ns   |

| t <sub>deq</sub>        | Input logic deglitch time                       | BRAKE                                                                                   | 1200   |      | 2000        | ns   |

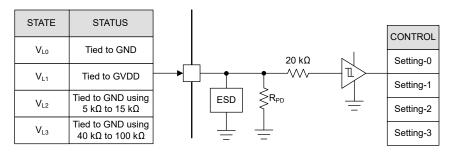

|                         | EL INPUT (SR)                                   |                                                                                         |        |      |             |      |

| R <sub>L1</sub>         | SR setting = 0                                  | Tied to PGND                                                                            | 0      |      | 1           | kΩ   |

| R <sub>L2</sub>         | SR setting = 1                                  | Tied to GVDD                                                                            | 0      |      | 1           | kΩ   |

| R <sub>L3</sub>         | SR setting =2                                   | R tied to PGND (R = $5 \text{ k}\Omega$ to $15 \text{ k}\Omega$ )                       | 5      |      | 15          | kΩ   |

| R <sub>L4</sub>         | SR setting = 3                                  | R tied to PGND (R = 40 k $\Omega$ to 100 k $\Omega$ )                                   | 40     |      | 100         | kΩ   |

|                         | N OUTPUTS (HV_nFAULT)                           |                                                                                         |        |      |             |      |

| V <sub>OL</sub>         | Output logic low voltage                        | I <sub>OD</sub> = 5 mA                                                                  |        |      | 0.4         | V    |

| I <sub>ОН</sub>         | Output logic high current                       | V <sub>OD</sub> = 5 V                                                                   | -1     |      | 1           | μA   |

| C <sub>OD</sub>         | Output capacitance                              |                                                                                         |        |      | 30          | pF   |

|                         | RIVER PROTECTION                                |                                                                                         |        |      |             |      |

| I <sub>OCP_GaN</sub>    | Overcurrent detection threshold                 | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V, T <sub>J</sub> =25°C                   | 7.5    |      |             | Α    |

| I <sub>OCP GaN</sub>    | Overcurrent detection threshold                 | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V, T <sub>J</sub> =125°C                  | 5      |      |             | Α    |

| I <sub>OCP GaN BT</sub> | Blanking time (including deglitch)              | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V                                         |        | 150  |             | ns   |

| I <sub>OCP GaN PD</sub> | Propagation delay (to FET turn off)             | V <sub>GVDD</sub> = 15V, V <sub>VM</sub> = 300V                                         |        | 50   |             | ns   |

| T <sub>SD_RISE</sub>    | Thermal shutdown rising                         | Die temperature (T <sub>J</sub> )                                                       | 145    | 165  | 185         | °C   |

| T <sub>SD_FALL</sub>    | Thermal shutdown falling                        | Die temperature (T <sub>J</sub> )                                                       | 125    | 145  | 165         | °C   |

| T <sub>SD HYST</sub>    | Thermal shutdown hysteresis                     | Die temperature (T <sub>J</sub> )                                                       |        | 20   |             | °C   |

|                         | IMIT COMPARATOR                                 | 1                                                                                       | 1      |      |             |      |

| I <sub>b</sub>          | Input bias current (ILIMIT)                     | V <sub>ILIMIT</sub> = 0.5V                                                              |        |      | 1           | μA   |

| V <sub>off</sub>        | Input voltage offset                            |                                                                                         |        | ±2.5 |             | mV   |

| V <sub>ILIMIT_DIS</sub> | ILIMIT to disable threshold minimum voltage     |                                                                                         | 2.2    |      | 2.5         | V    |

| V <sub>ILIMIT</sub>     | Voltage range at ILIMIT                         |                                                                                         |        |      | 2           | V    |

| ILIIVII I               |                                                 |                                                                                         |        |      | -           |      |

Submit Document Feedback

# 9 Electrical Characteristics (continued)

$T_J = -40^{\circ}\text{C}$  to 150°C,  $V_{GVDD} = 15\text{V}$ , EN = High (unless otherwise noted). Typical limits apply for  $T_A = 25^{\circ}\text{C}$ ,  $V_{GVDD} = 15\text{V}$

|                       | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CONDITIONS                                                              | MIN  | TYP  | MAX | UNIT  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|-----|-------|

| t <sub>blank</sub>    | Over current detection blanking on all SLx inputs, from any INHx/INLx turn on/off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                              | 400  |      | 620 | ns    |

| t <sub>deglitch</sub> | Overcurrent detection de-glitch time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              | 190  |      | 330 | ns    |

| t <sub>filter</sub>   | Input RC filter time (SLx)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>SLx</sub> = 0 to 1V step, VILIMIT = 0.63V                             | 250  |      | 450 | ns    |

| t <sub>filter</sub>   | Input RC filter time (ILIMIT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>ILIMIT</sub> = 1 to 0V step, V <sub>SLx</sub> = 0.37V                 | 600  | 1000 |     | ns    |

| t <sub>pd_OFF</sub>   | Over current detection to all GaN turn off delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>ILIMIT</sub> = 0.63V, V <sub>SLx</sub> = 0 to 1V step, INx = constant |      |      | 1.2 | μs    |

| t <sub>pd_FAULT</sub> | Over current detection to HV_nFAULT pin report delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>ILIMIT</sub> = 0.63V, V <sub>SLx</sub> = 0 to 1V step, INx = constant |      |      | 1   | μs    |

| t <sub>F_CLR</sub>    | Fault clear time after over current detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              | 40   |      | 65  | μs    |

| OPERATIO              | NAL AMPLIFIER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                              |      |      |     |       |

| V <sub>LINEAR</sub>   | Output voltage swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R <sub>L</sub> = 10k to GND                                                  | 0.02 |      | 4.9 | V     |

| GBW                   | Gain bandwidth product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RL= 10k, G = +1                                                              |      | 11   |     | MHz   |

| V <sub>SR_opamp</sub> | Output voltage slew rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RL= 10k, G = +1                                                              |      | 15   |     | V/µs  |

| t <sub>set</sub>      | Settling time to ±1%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-V step , G = +1, CL = 130 pF, RL = 10k                                     |      | 0.4  |     | μs    |

| A <sub>OL</sub>       | Open-loop voltage gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $0.04~V < VAMPOUT < 4.8~V,~RL = 10~k\Omega$ to GND                           |      | 106  |     | dB    |

| φ <sub>m</sub>        | Phase margin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | G = +1, RL = 10k                                                             |      | 60   |     | 0     |

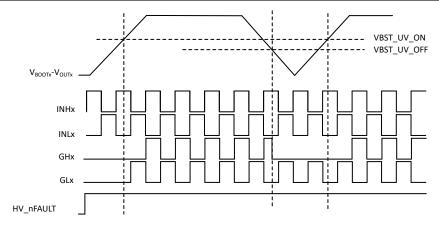

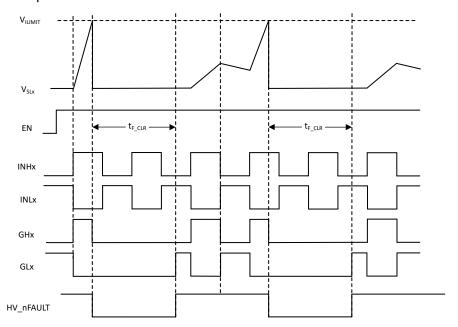

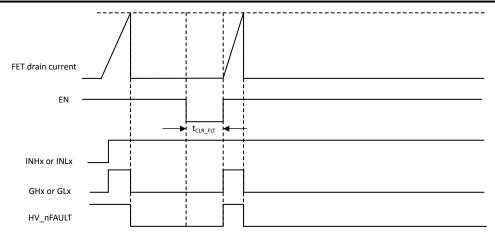

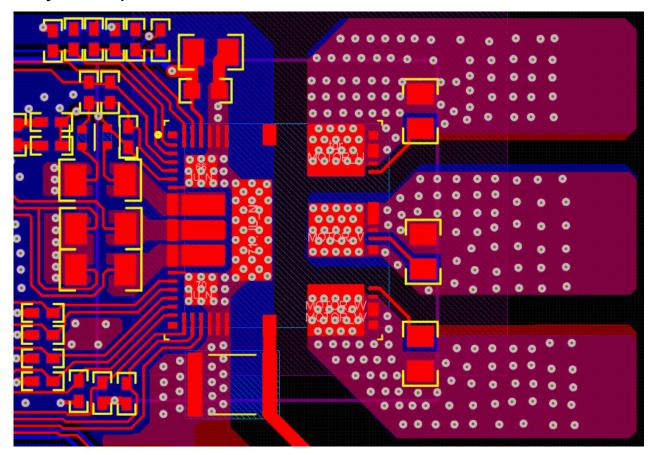

| V <sub>COM</sub>      | Common mode input range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                              | 0    |      | 5   | V     |