# DP83TC818S-Q1 Precise and Secure 100BASE-T1 Automotive Ethernet with AVB Clock Generation, IEEE802.1AE MACsec, IEEE802.1AS and TC10 Sleep-Wake

### 1 Features

- Synchronized Audio Clock Generation

- I2S & TDMx SCLK/FSYNC clock generation

- Configurable FSYNC, SCLK, MCLK frequencies

- Automatic Phase Adjustment through IEEE1722 CRF decode

- IEEE 802.1AE MACsec

- MACsec frame expansion: Inbuilt buffering and flow control support to handle 12 byte IPG ethernet frames

- Authentication, encryption at line rate

- Cipher suites: GCM-AES-XPN-128/256, GCM-AES-128/256

- Secure Channel: Total 16 SAK enabling 8 Tx/Rx SC with SAK Auto rollover support

- Ingress/Egress classification for Ethertype, VLAN, DMAC: up to 8 parallel rules

- Window replay protection

- IEEE 802.1AS time synchronization

- Highly accurate 1pps signal < ±15 ns</li>

- Precise time stamping for MACsec encoded PTP packets

- Multiple IOs for event capture and trigger

- Robust EMC Performance

- IEC62228-5, OA EMC compliant

- SAE J2962-3 EMC compliant

- 39dBm DPI Immunity with ±5% assymetry

- <4dBµV radiated emissions in GPS and</li> Glonass bands

- Stripline Emissions: Class-II compliant

- TC-10 compliant

- − < 18µA sleep current</p>

- Fast wake from sleep by retaining PHY configuration during sleep (optional)

- MAC Interfaces: MII, RMII Master, RGMII, SGMII

- Footprint compatible with TI's 1000BASE-T1 PHY

- Single board design for 100BASE-T1 and 1000BASE-T1 with required BOM change

- Diagnostic tool kit

- Signal Quality Indication (SQI) & Time Domain Reflectometry (TDR)

- Voltage, Temperature & ESD sensors

- PPM monitor: Provides external clock ppm drift (up to ±100 ppb accuracy)

- AEC-Q100 qualified for Automotive Applications:

- Temperature Grade 1: -40°C to +125 °C

- IEC61000-4-2 ESD level 4 MDI: ±8kV CD

### 2 Applications

- Infotainment & Cluster

- AVB Audio/Video

- **Body Electronics & Lighting**

- Body Control Module

- Zone Control Module

- **Telematics**

### 3 Description

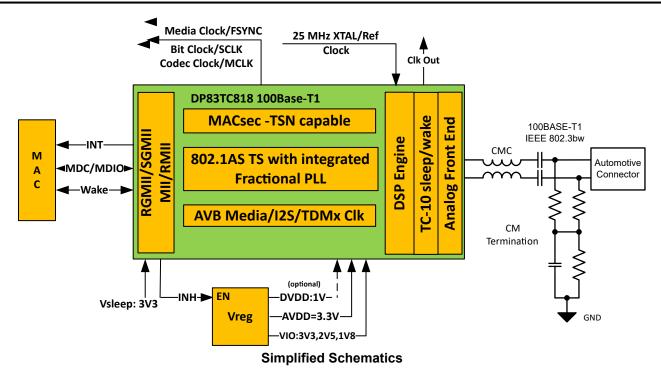

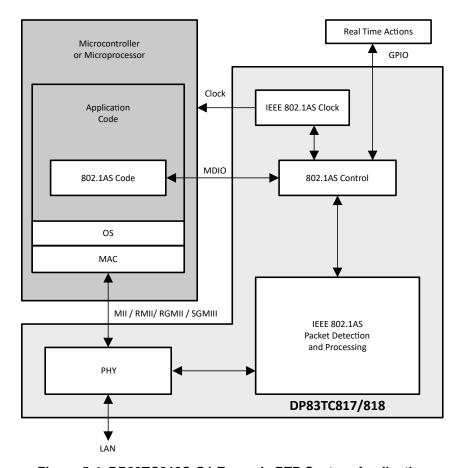

The DP83TC818S-Q1 is an IEEE 802.3bw and Open Alliance (OA) compliant automotive qualified 100Base-T1 Ethernet physical layer transceiver. The device provides all physical layer functions needed to transmit and receive data over unshielded/shielded single twisted-pair cables with xMII interface flexibility and TC10 Sleep-Wake functionality.

The DP83TC818S-Q1 integrates IEEE802.1AS / IEEE1588v2 hardware time stamping & fractional PLL, enabling highly accurate time synchronization. The fractional PLL enables frequency and phase synchronization of the wall clock (eliminating the need for external VCXO) and generation of a wide range of time synchronized frequencies needed for audio and other ADAS applications. The PHY also integrates IEEE 1722 CRF decode to generate Media clock and Bit Clock for AVB & other audio applications.

The DP83TC818S-Q1 integrates IEEE 802.1AE line rate security with authentication and optional encryption support to secure communication over the network. The DP83TC818S-Q1 supports up to 16 secure association (SA) channels with automatic SAK rollover and extended packet numbering support. DP83TC818S-Q1 offers ingress classification to filter the unwanted packets & supports WAN MACsec for end-to-end security.

The DP83TC818S-Q1 is footprint compatible to TI's 100BASE-T1 PHYs and 1000BASE-T1 PHYs enabling design scalability with a single board for different speeds and features.

#### **Device Information**

| PART NUMBER   | PACKAGE (1) | BODY SIZE (NOM) (2) |  |  |

|---------------|-------------|---------------------|--|--|

| DP83TC818S-Q1 | VQFN (36)   | 6.00mm × 6.00mm     |  |  |

- For all available packages, see Mechanical, Packaging and Orderable Information.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

## **4 Device Comparison Table**

| PART<br>NUMBER | TC10 SUPPORT | MACsec SUPPORT | 802.1AS SUPPORT | AVB CLOCK<br>GENERATION<br>SUPPORT | FOOTPRINT<br>COMPATIBLE |

|----------------|--------------|----------------|-----------------|------------------------------------|-------------------------|

| DP83TC812x-Q1  | Yes          | No             | No              | No                                 | Yes                     |

| DP83TC814x-Q1  | No           | No             | No              | No                                 | Yes                     |

| DP83TC817S-Q1  | Yes          | Yes            | Yes             | No                                 | Yes                     |

| DP83TC818S-Q1  | Yes          | Yes            | Yes             | Yes                                | Yes                     |

### **5 Application Information**

### 5.1 MAC Security

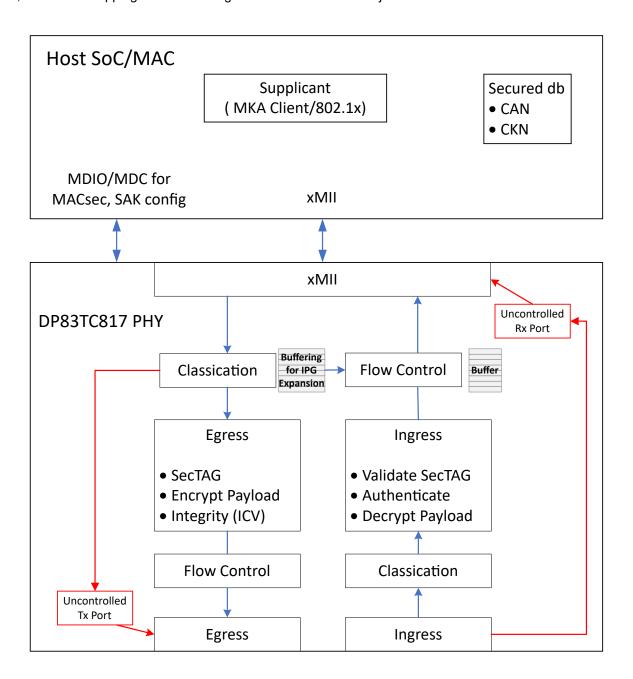

DP83TC818S-Q1 integrates MAC Security, or MACsec (IEEE 802.1AE) hardware engine to perform line-rate security (encryption and authentication) on both egress and ingress data paths. IEEE802.1AE is a Layer 2 network security protocol that prevents a range of attacks including: denial of service, intrusion, man-in-the-middle, and eavesdropping. The block diagram below shows the major MACsec blocks within the PHY.

Figure 5-1. MACsec Block Diagram

#### 5.2 TC10 Sleep Wake-up

DP83TC818S-Q1 is a 100BASE-T1 Ethernet PHY with TC-10 power saving feature with the following features.

- Open Alliance TC10 compliant

- Sleep request feature to shut down Ethernet network to save power

- 8µA (Typical, 27 °C), 20µA (Maximum, 125 °C) sleep current

- · Wake forwarding feature for Ethernet network wake-up

- Fast Wake-up

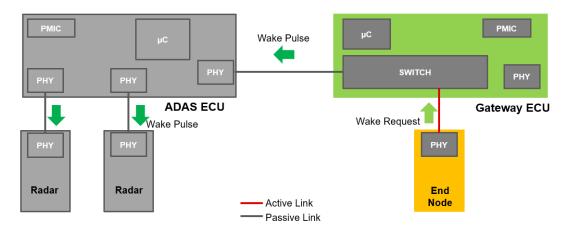

This block diagram shows an example of how TC10 can be implemented in an automotive system. First, the wake up request originates over active link and then the wake up pulse is forwarded over passive link. The wake up request and pulses are exchanged over the Ethernet cable without needing dedicated wake up wire.

Figure 5-2. TC10 ADAS System Use Case Example

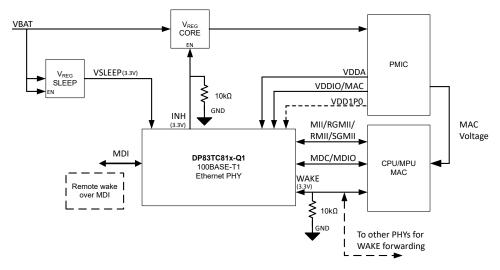

This block diagram shows the system level integration of DP83TC818S-Q1 to support the TC10 sleep/wake-up feature.

Figure 5-3. System Block Diagram

### 5.3 Time Syncronization

The DP83TC818S-Q1 integrates IEEE 1588v2/802.1AS timestamping and other additional hardware engines to offer highly accurate synchronization with synchronization jitter of  $< \pm 15$ ns (with options to reduce to  $\pm 1$ ns for point-to-point connections) and synchronization offset of  $\pm 30$ ns.

The DP83TC818S-Q1 is also capable of providing a high quality time synchronized clock signal to achieve system level synchronization for ADAS sensor data synchronisation, Corner RADAR Chirp synchronisation, 1 pps signal for LiDAR, V2X, etc.

Figure 5-4. DP83TC818S-Q1 Example PTP System Application

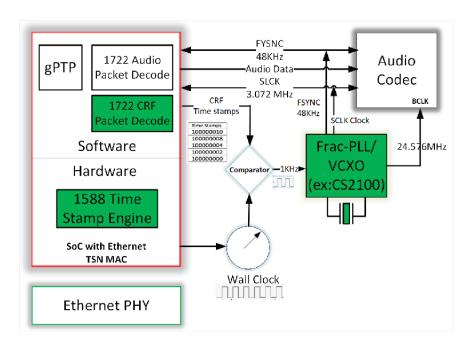

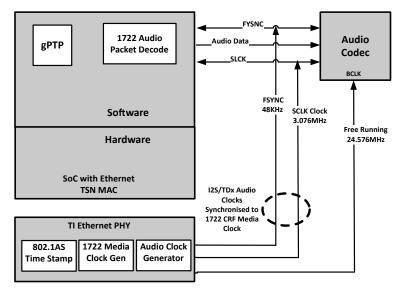

### 5.4 Integrated Audio Over Ethernet

DP83TC818S-Q1 offers audio clocking solutions for AVB (Audio Video Bridging) and other Audio transports protocols (IES676, IEEE 1733 RTP, Dante) by:

- Generating IEEE 1722 Media Clock with embedded CRF packet decode

- · Synchronised clocks (FSYNC, BCLK, MCLK) for Audio interface I2S and TDMx.

Figure 5-5. Typical Audio Over Ethernet Architecture

Figure 5-6. Audio Over Ethernet Architecture with DP83TC818S-Q1

### 5.5 DP83TC818EVM-MC and Software Support

#### DP83TC818EVM-MC

The DP83TC818EVM-MCsupports 100-Mbps speed and is IEEE 802.3bw compliant. This evaluation board is a media converter from 100Base-TX to 100Base-T1. There is an onboard MSP430F5529 for MDIO/MDC register access with the USB2MDIO and DIEP graphical user interface tools. DP83867 is provided for copper (100BASE-TX) support using RGMII MAC interface.

Figure 5-7. DP83TC818EVM-MC

#### Features:

- TC10 Support

- · Jumpers to customize PHY strap settings

- Option to supply external reference clock

- · Additional test points for debug

- Status LEDs

- Link

- Link + Activity

- Power-On

- EVM User's Guide for reference

#### New DIEP Debug Interface Experience

DIEP offers all your Ethernet PHY debug needs in one place including MDIO bus serial management, device control registers, access to both extended registers and standard registers, and the ability to save data read and run script text files.

- NEW restructured navigation and register display

- NEW improved text script execution

Debug Interface for Ethernet PHY's (DIEP)

### 6 Device and Documentation Support

#### **Note**

TI is transitioning to use more inclusive terminology. Some language may be different than what you would expect to see for certain technology areas.

### 6.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### **6.2 Support Resources**

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### **6.3 Community Resources**

#### 6.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

### 6.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 6.6 Glossary

TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

## 7 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## 7.1 Package Option Addendum

## 7.1.1 Packaging Information

| Orderable Device | Status <sup>1</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>2</sup> | Lead/Ball<br>Finish <sup>4</sup> | MSL Peak Temp <sup>3</sup> | Op Temp (°C) | Device Marking <sup>5 6</sup> |

|------------------|---------------------|-----------------|--------------------|------|----------------|-----------------------|----------------------------------|----------------------------|--------------|-------------------------------|

| DP83TC818SRHATQ1 | EARLY<br>SAMPLE     | VQFN            | RHA                | 36   | 250            | RoHS & Green          | NIPDAU                           | Level-3-260C-168 HR        | 40 to 125    | TBD                           |

| DP83TC818SRHARQ1 | EARLY<br>SAMPLE     | VQFN            | RHA                | 36   | 2500           | RoHS & Green          | NIPDAU                           | Level-3-260C-168 HR        | 40 to 125    | TBD                           |

Submit Document Feedback

11

www.ti.com 23-May-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

| DP83TC818SRHARQ1      | Active | Production    | VQFN (RHA)   36 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | 818S             |

| DP83TC818SRHARQ1.A    | Active | Production    | VQFN (RHA)   36 | 2500   LARGE T&R      | Yes  | NIPDAU                        | Level-3-260C-168 HR        | -40 to 125   | 818S             |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

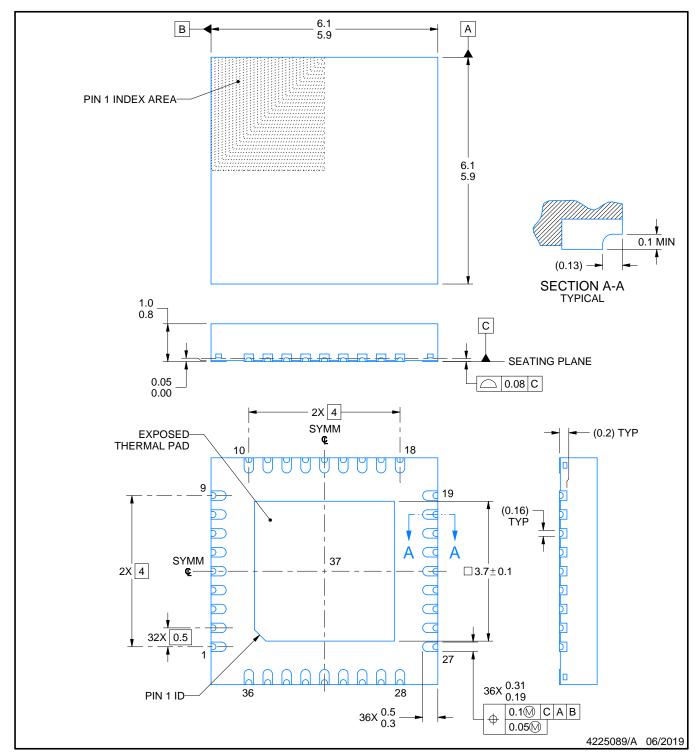

6 x 6, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

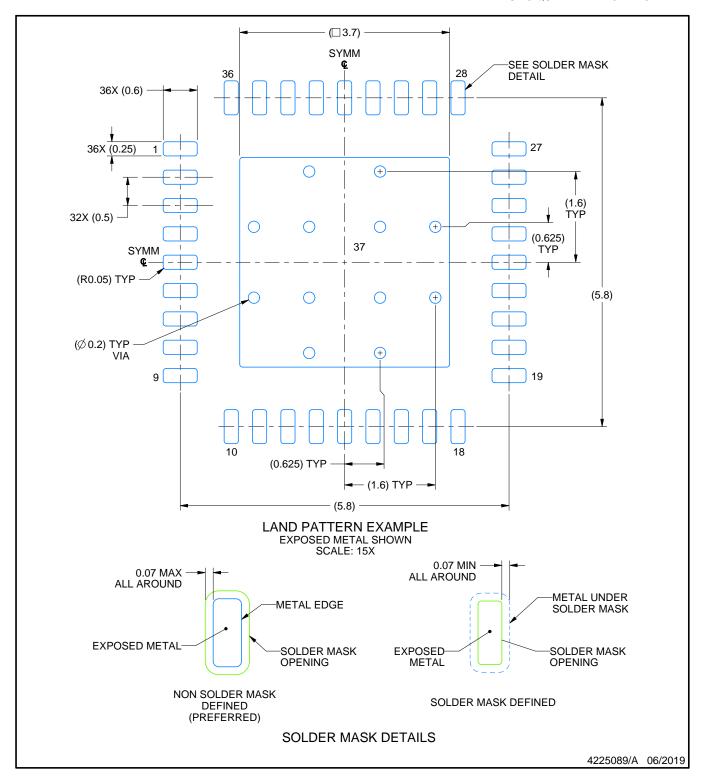

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

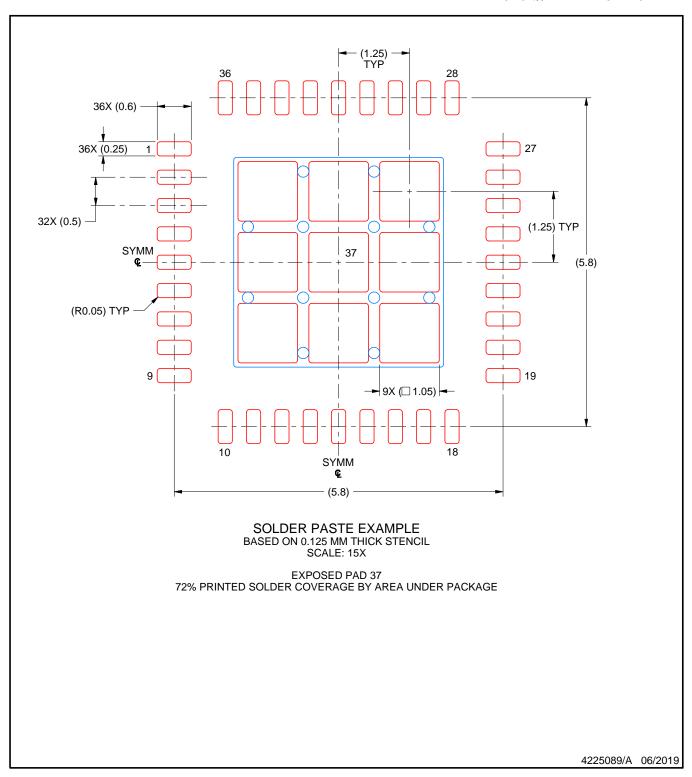

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated