# DP83TC815-Q1 100Base-T1 Automotive Ethernet PHY Transceiver With IEEE802.1AS and TC10 Sleep-Wake

#### 1 Features

- IEEE802.3bw compliant 100BASE-T1 PHY

- AEC-Q100 qualified for automotive applications:

- Temperature grade 1: –40°C to +125°C, T<sub>A</sub>

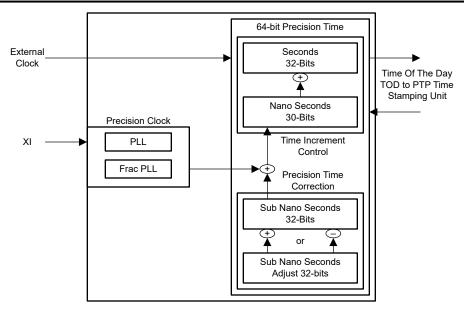

- IEEE 802.1AS time synchronization

- Highly accurate 1pps signal

- Synchronization jitter: < ±15ns (options to reduce to ±1ns)

- Synchronization offset: < ±30ns

- Multiple IOs for event capture and trigger

- OA TC-10 compliant sleep, wake up

- Robust EMC performance

- IEC62228-5, OA EMC compliant

- IEC61000-4-2 ESD level 4 MDI: ±8kV CD

- SAE J2962-3 EMC compliant

- 39dBm DPI immunity with ±5% asymmetry

- < 4dBµV radiated emissions in GPS and glonass bands

- Stripline emissions: class-II compliant

- MAC Interfaces: MII, RMII, RGMII, SGMII

- Footprint compatible with TI's 100BASE-T1, 1000BASE-T1 PHY - with BOM options

- 48V ready: VBAT transients to MDI up to +/- 70V

- Diagnostic tool kit

- Signal quality indication (SQI) and time domain reflectometry (TDR)

- Voltage, temperature, and ESD sensors

- PPM monitor: provides external clock ppm drift (up to ±100ppb accuracy)

- Single 3.3V supply capability

### 2 Applications

- **ADAS**

- Radar synchronization

- Body electronics and lighting

- Body control module

- Zone control module

- **Telematics**

### 3 Description

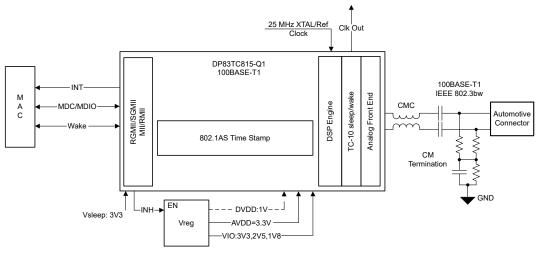

The DP83TC815-Q1 is an IEEE 802.3bw and Open Alliance (OA) compliant automotive qualified 100Base-T1 Ethernet physical layer transceiver. The device provides all physical layer functions needed to transmit and receive data over unshielded, shielded single twisted-pair cables with xMII interface flexibility.

The DP83TC815-Q1 integrates IEEE802.1AS / IEEE1588v2 to enable highly accurate synchronization and hardware time stamping for timesensitive, real-time controlled applications.

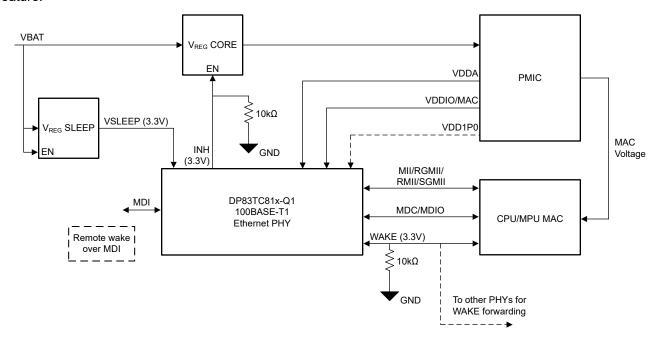

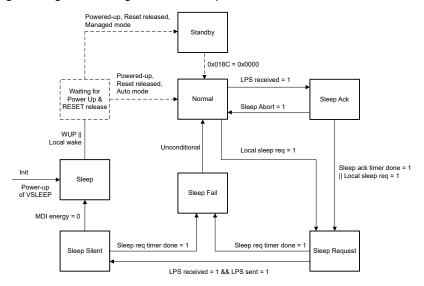

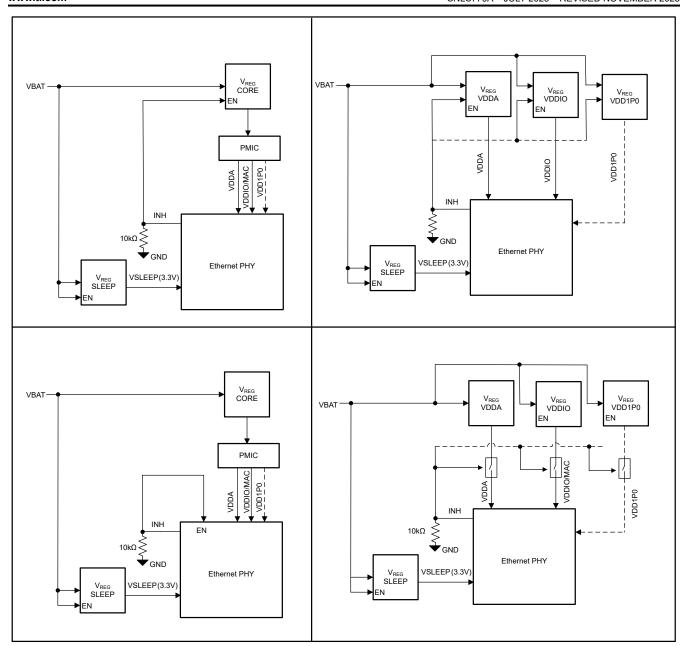

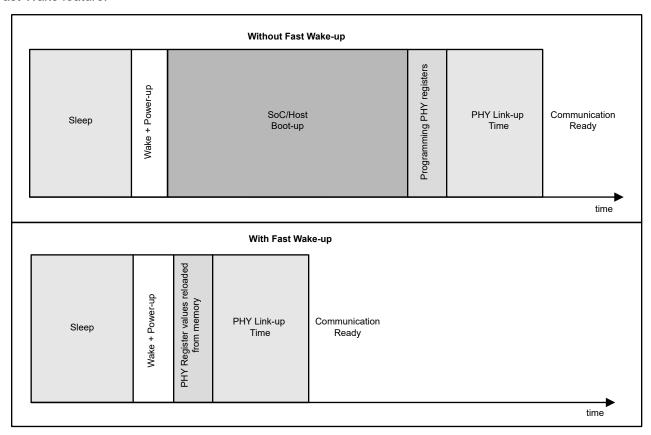

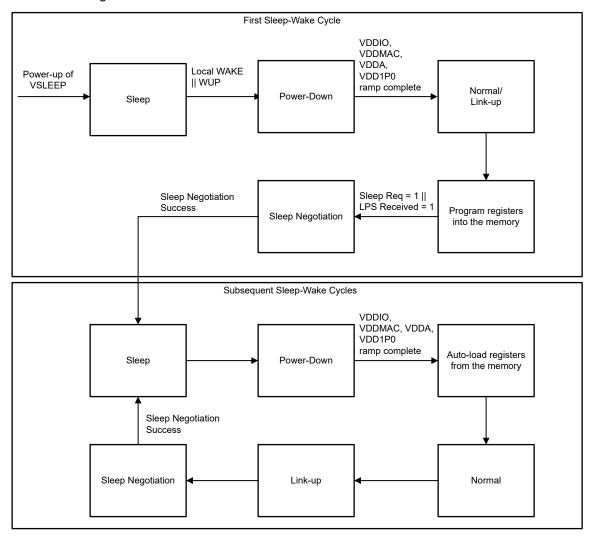

The DP83TC815-Q1 supports OA TC-10 low power sleep feature with wake forwarding for reduced system power consumption when communication is not required.

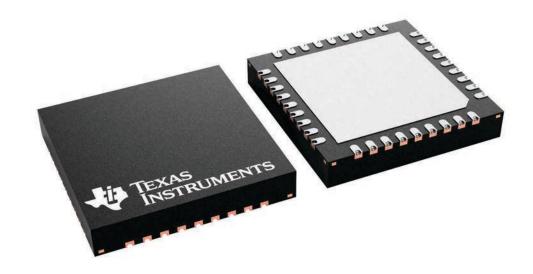

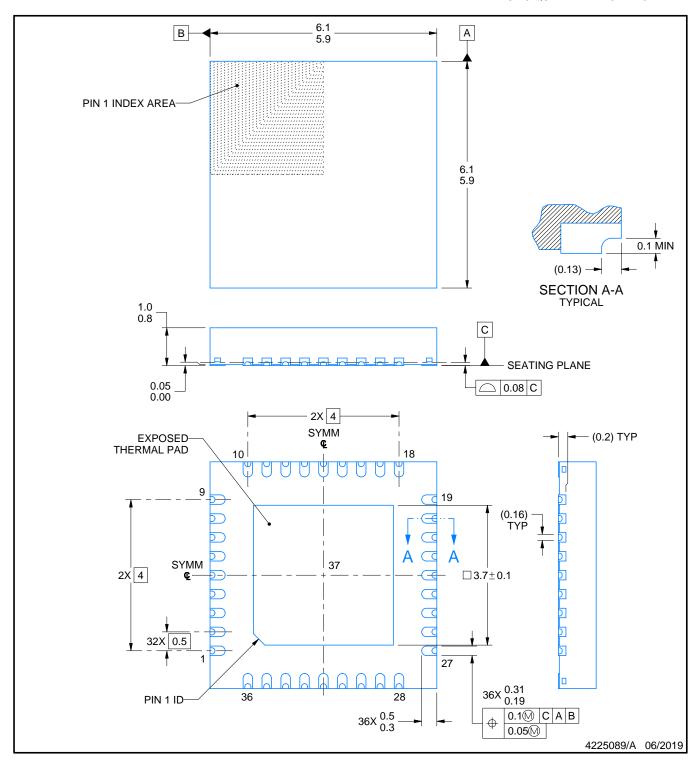

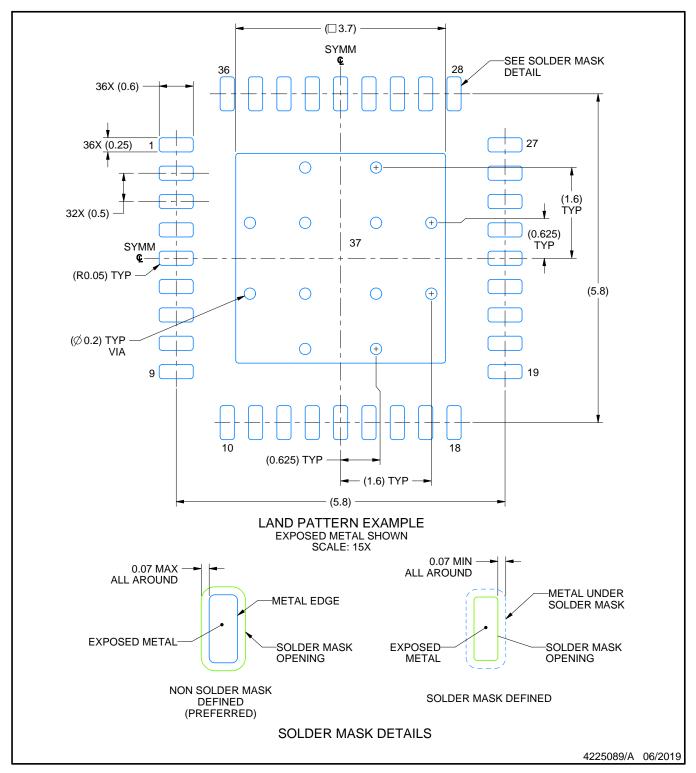

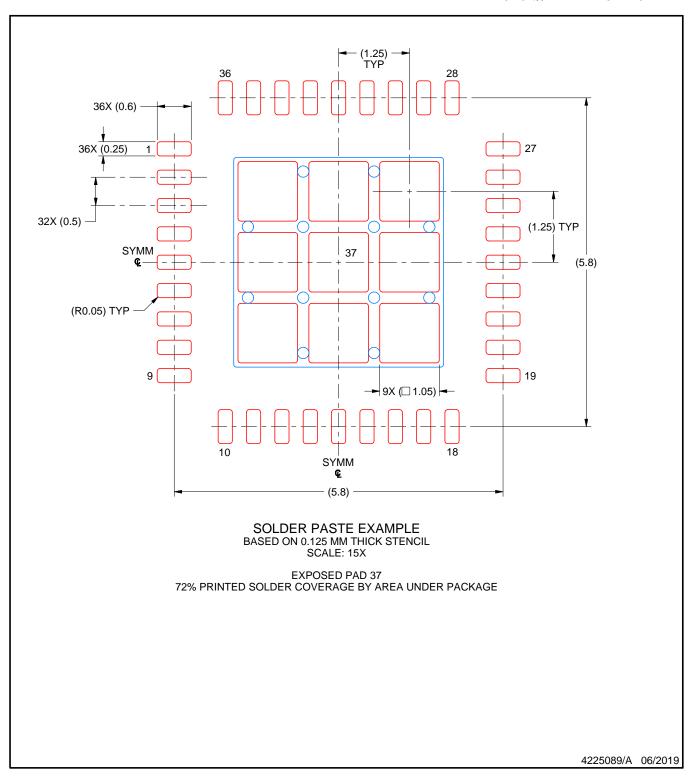

#### Package Information

| _ |              |                        |                             |

|---|--------------|------------------------|-----------------------------|

|   | PART NUMBER  | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|   | DP83TC815-Q1 | RHA (VQFN, 36)         | 6.00mm × 6.00mm             |

- (1) For more information, see Section 12.

- (2)The package size (length × width) is a nominal value and includes pins, where applicable.

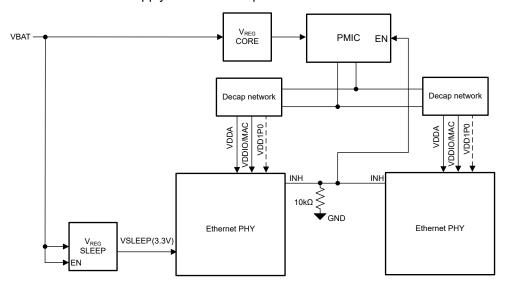

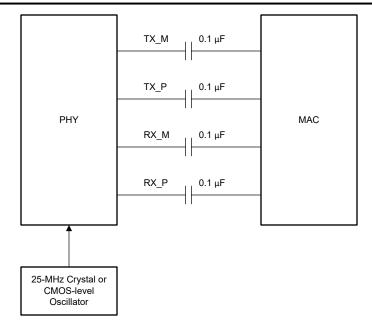

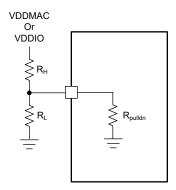

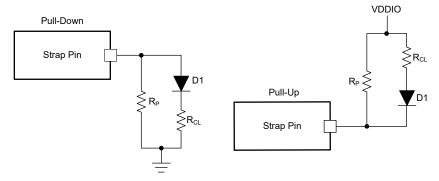

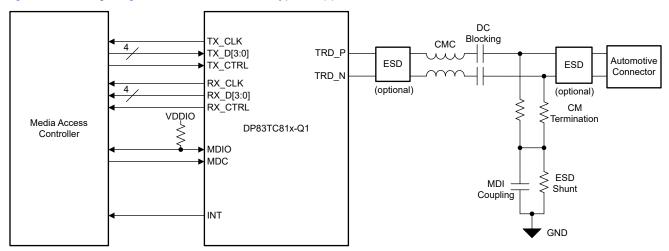

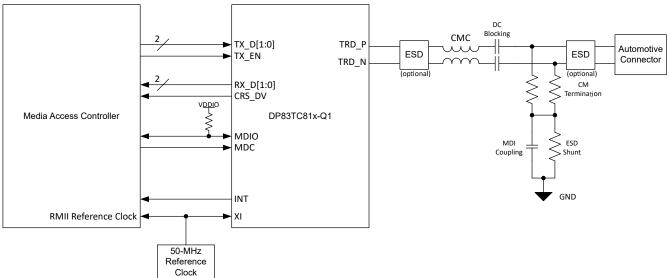

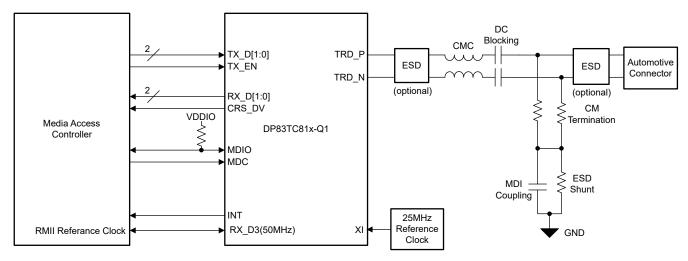

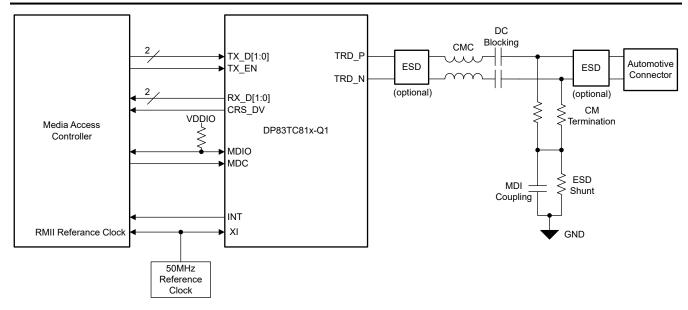

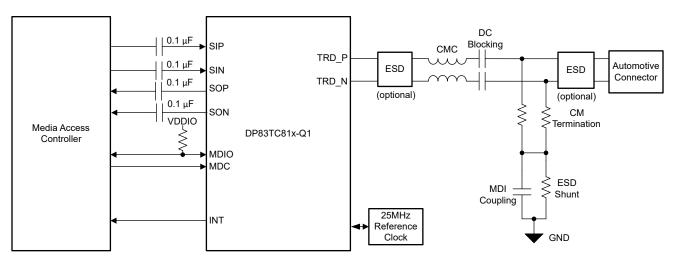

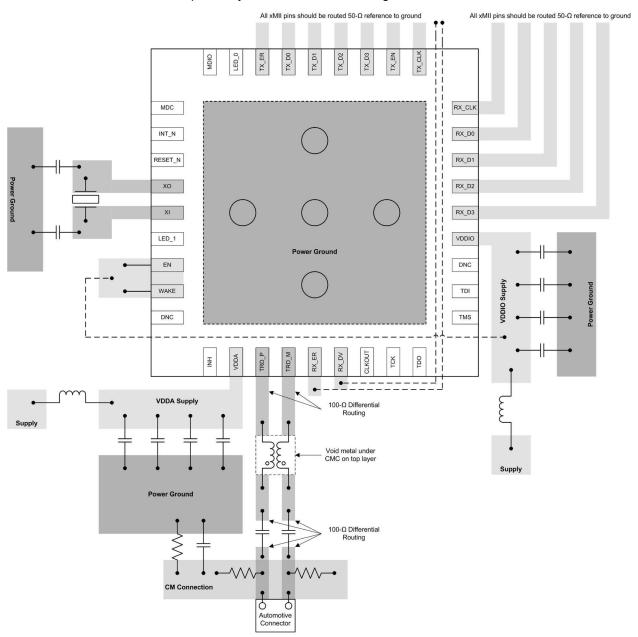

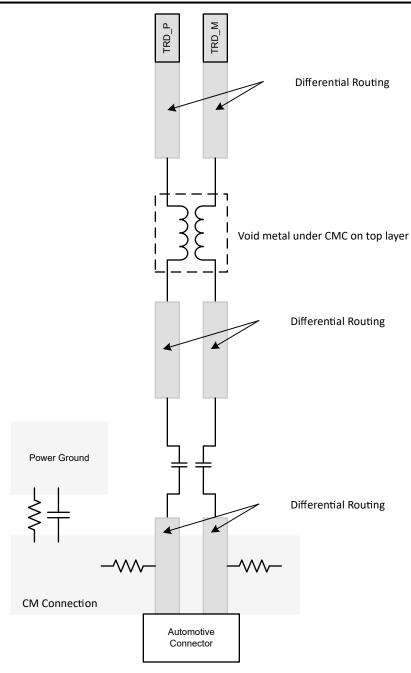

Simplified Schematics

## **Table of Contents**

| 1 Features                           | 1               | 7.4 Device Functional Modes                    | 67          |

|--------------------------------------|-----------------|------------------------------------------------|-------------|

| 2 Applications                       | 1               | 7.5 Programming                                |             |

| 3 Description                        |                 | 8 Register Maps                                |             |

| 4 Device Comparison Table            | 3               | 8.1 Register Access Summary                    | 82          |

| 5 Pin Configuration and Functions    | 4               | 8.2 DP83TC815 Registers                        | 83          |

| 5.1 Pin Power Domain                 | 8               | 9 Application and Implementation               | 156         |

| 5.2 Pin States                       | 9               | 9.1 Application Information                    | 156         |

| 5.3 Pin Multiplexing                 | 14              | 9.2 Typical Applications                       | 156         |

| 6 Specifications                     | 15              | 9.3 Power Supply Recommendations               | 161         |

| 6.1 Absolute Maximum Ratings         | 15              | 9.4 Layout                                     | 164         |

| 6.2 ESD Ratings                      | 15              | 10 Device and Documentation Support            | 168         |

| 6.3 Recommended Operating Conditions | 15              | 10.1 Device Support                            | 168         |

| 6.4 Thermal Information              | 16              | 10.2 Receiving Notification of Documentation L | Jpdates 168 |

| 6.5 Electrical Characteristics       | 16              | 10.3 Support Resources                         | 168         |

| 6.6 Timing Requirements              | <mark>21</mark> | 10.4 Trademarks                                | 168         |

| 6.7 Timing Diagrams                  | <mark>24</mark> | 10.5 Electrostatic Discharge Caution           | 168         |

| 6.8 Typical Characteristics          | 31              | 10.6 Glossary                                  | 168         |

| 7 Detailed Description               | <mark>32</mark> | 11 Revision History                            | 168         |

| 7.1 Overview                         | 32              | 12 Mechanical, Packaging, and Orderable        |             |

| 7.2 Functional Block Diagram         | 33              | Information                                    | 169         |

| 7.3 Feature Description              | 34              |                                                |             |

# **4 Device Comparison Table**

| PART NUMBER   | TC10? | MACsec? | 802.1AS? | AVB CLOCKS? | FOOTPRINT<br>COMPATIBLE? |

|---------------|-------|---------|----------|-------------|--------------------------|

| DP83TC812x-Q1 | Yes   | No      | No       | No          | Yes                      |

| DP83TC814x-Q1 | No    | No      | No       | No          | Yes                      |

| DP83TC815-Q1  | Yes   | No      | Yes      | No          | Yes                      |

| DP83TC816-Q1  | Yes   | No      | Yes      | Yes         | Yes                      |

| DP83TC817S-Q1 | Yes   | Yes     | Yes      | No          | Yes                      |

| DP83TC818S-Q1 | Yes   | Yes     | Yes      | Yes         | Yes                      |

# **5 Pin Configuration and Functions**

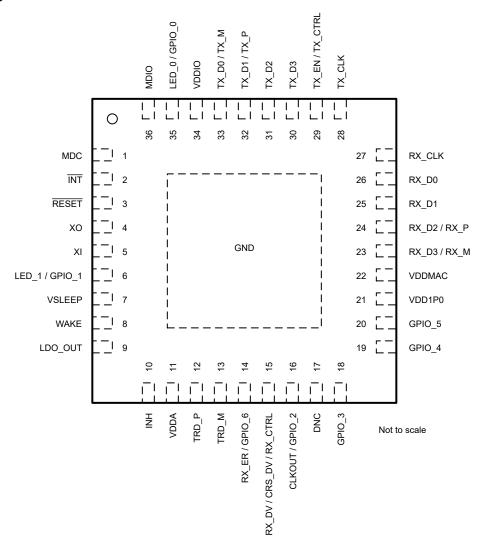

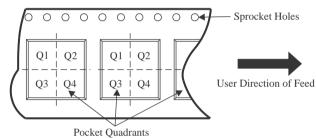

Figure 5-1. DP83TC815-Q1 RHA Package 36-Pin VQFN Top View

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

## **Table 5-1. Pin Functions**

| PIN                            |        | (4)                  | Table 5-1. Fill FullCuons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|--------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME <sup>(2)</sup>            | NO.    | STATE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MAC INTERF                     | ACE    |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RX_CLK                         | 27     | S, PD, O             | Receive Clock: In MII and RGMII modes, the receive clock provides a 25MHz reference clock.  Unused in RMII and SGMII modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RX_D0                          | 26     |                      | Receive Data: Symbols received on the cable are decoded and transmitted out of these pins synchronous to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RX_D1                          | 25     |                      | rising edge of RX_CLK. They contain valid data when RX_DV is asserted. A data nibble, RX_D[3:0], is transmitted                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RX_D2 /<br>RX_P                | 24     | S, PD, O             | in MII and RGMII modes. 2 bits; RX_D[1:0], are transmitted in RMII mode.  If the PHY is bootstrapped to RMII Leader mode, a 50MHz clock reference is automatically outputted on RX_D3.                                                                                                                                                                                                                                                                                                                                                                                                      |

| RX_D3 /<br>RX_M                | 23     |                      | This clock must be fed to the MAC.  RX_M / RX_P: Differential SGMII Data Output. These pins transmit data from the PHY to the MAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RX_DV /<br>CRS_DV /<br>RX_CTRL | 15     | S, PD, O             | Receive Data Valid: This pin indicates when valid data is presented on RX_D[3:0] for MII mode.  Carrier Sense Data Valid: This pin combines carrier sense and data valid into an asynchronous signal. When CRS_DV is asserted, data is presented on RX_D[1:0] in RMII mode.  RGMII Receive Control: Receive control combines receive data valid indication and receive error indication into a single signal. RX_DV is presented on the rising edge of RX_CLK and RX_ER is presented on the falling edge of RX_CLK.  Unused in SGMII mode                                                   |

| RX_ER /<br>GPIO_6              | 14     | S, PD, O             | Receive Error: In MII and RMII modes, this pin indicates a receive error symbol has been detected within a received packet. In MII mode, RX_ER is asserted high synchronously to the rising edge of RX_CLK. In RMII mode, RX_ER is asserted high synchronously to the rising edge of the reference clock. This pin is optional in MII or RMII because the PHY automatically corrupts data on a receive error.  Unused in RGMII and SGMII modes This pin can be used as GPIO_6.                                                                                                              |

| TX_CLK                         | 28     | PD, I, O             | Transmit Clock: In MII mode, the transmit clock is a 25MHz output (50 ohm Driver). In RGMII mode, this clock is sourced from the MAC layer to the PHY. A 25MHz clock must be provided in RGMII mode to meet the RGMII timing requirements mentioned in <i>Timing Requirements</i> .  Unused in RMII and SGMII modes                                                                                                                                                                                                                                                                         |

| TX_D0 /                        | 33     |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TX_M TX_D1 / TX_P              | 32     | PD, I                | Transmit Data: In MII and RGMII modes, the transmit data nibble, TX_D[3:0], is received from the MAC prior to the rising edge of TX_CLK. In RMII mode, TX_D[1:0] is received from the MAC prior to the rising edge of the reference                                                                                                                                                                                                                                                                                                                                                         |

| TX_D2                          | 31     |                      | clock. TX_D[3:2] are not used in RMII mode.  TX_M / TX_P: Differential SGMII Data Input. These pins receive data that is transmitted from the MAC to the PHY.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX_D3                          | 33     |                      | TA_M7 TA_1 . Billiotential committee input. These pins receive data that is dansmitted from the first to the TTT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TX_EN /<br>TX_CTRL             | 29     | PD, I                | Transmit Enable: In MII mode, transmit enable is presented prior to the rising edge of the transmit clock. TX_EN indicates the presence of valid data inputs on TX_D[3:0]. In RMII Leader mode, transmit enable is presented prior to the rising edge of RX_D3. TX_EN indicates the presence of valid data inputs on TX_D[1:0].  RGMII Transmit Control: Transmit control combines transmit enable and transmit error indication into a single signal. TX_EN is presented prior to the rising edge of TX_CLK; TX_ER is presented prior to the falling edge of TX_CLK.  Unused in SGMII mode |

| SERIAL MAN                     | AGEMEN | TINTERFACE           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MDC                            | 1      | I                    | Management Data Clock: Synchronous clock to the MDIO serial management input and output data. This clock can be asynchronous to the MAC transmit and receive clocks. The maximum clock rate is 20MHz. There is no minimum clock rate.                                                                                                                                                                                                                                                                                                                                                       |

| MDIO                           | 36     | OD, IO               | Management Data Input/Output: Bidirectional management data signal that can be sourced by the management station or the PHY. This pin requires a pullup resistor. In systems with multiple PHYs using same MDIO-MDC bus, a single pull-up resistor must be used on MDIO line.  Recommended to use a resistor between 2.2kΩ and 9kΩ.  MDIO/MDC Access is required to pass Open Alliance Compliance. See Section 7.3.8.                                                                                                                                                                       |

#### **Table 5-1. Pin Functions (continued)**

| PIN                   | 1            |                      | Table 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------|--------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME <sup>(2)</sup>   | NO.          | STATE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTROL IN            | <br> TERFACE |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| INH                   | 10           | O, OD                | <b>INH:</b> Active-HIGH output. This pin is Hi-Z when the PHY is in TC-10 SLEEP. This pin is HIGH for all other PHY states. External pull down resistor in the range of $2k\Omega - 10k\Omega$ must be used when implementing TC-10 circuit. If multiple devices are sharing INH pin, then a single pull down resistor must be used.                                                                                                                                                                                                                                                                                                                                               |

| ĪNT                   | 2            | PU, OD, IO           | Interrupt: Active-LOW output, asserts LOW when an interrupt condition occurs. This pin has a weak internal pullup. Register access is necessary to enable various interrupt triggers. Once an interrupt event flag is set, register access is required to clear the interrupt event. This pin can be configured as an Active-HIGH output using register 0x0011. Interrupt status from Reg 12-13 is recommended to be read only when INT_N is LOW. This pin can also operate as Power-Down control where asserting this pin low would put the PHY in power down mode and asserting high would put the PHY in normal mode. This feature can also be enabled through register 0x0011. |

| RESET                 | 3            | PU, I                | Reset: Active-LOW input, which initializes or reinitializes the PHY. Asserting this pin LOW for at least 1µs forces a reset process to occur. All internal registers reinitialize to the default states as specified for each bit in the Register Maps section. All bootstrap pins are resampled upon deassertion of reset.                                                                                                                                                                                                                                                                                                                                                        |

| WAKE                  | 8            | PD, I/O              | <b>WAKE:</b> Input/Output pin which is Active-HIGH input by default. As input, this pin wakes the PHY from TC-10 SLEEP. Asserting this pin HIGH at power-up brings the PHY out of SLEEP. External $10k\Omega$ pull down resistor can be used when implementing TC-10 circuit to prevent accidental wake-up. This pin can be directly tied to VSLEEP or it can be pulled to VSLEEP through a resistor to wake the device. This pin also supports wake forwarding feature where a WAKE pulse generated by the PHY is then used to wake up other PHYs in the same system.                                                                                                             |

| CLOCK INTE            | RFACE        |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ΧI                    | 5            | 1                    | Reference Clock Input (RMII): Reference clock 25MHz crystal or oscillator in RMII Leader mode.  Reference Clock Input (Other MAC Interfaces): Reference clock 25MHz crystal or oscillator input. The device supports either an external crystal resonator connected across pins XI and XO, or an external CMOS-level oscillator connected to pin XI only and XO left floating. This pin can also accept clock input from other devices like Ethernet MAC or another Ethernet PHY in daisy-chain operations.  If using a crystal, connect a 100Ω resistor in series with the XI pin                                                                                                 |

| хо                    | 4            | 0                    | Reference Clock Output: XO pin is used for crystal only. This pin must be left floating when a CMOS-level oscillator is connected to XI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| LED/GPIO IN           | ITERFACE     |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT /<br>GPIO_2    | 16           | Ю                    | Clock Output: 25MHz reference clock. This pin can also be used as LED or GPIO via Strap/Register selection.  Program register<0x045F>=0x000F and register<0x0453>=0x0003 to disable switching on clkout pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO_3 <sup>(3)</sup> | 18           | PD, IO               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GPIO_4                | 19           | S, PD, IO            | General Purpose IO pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPIO_5                | 20           | PD, IO               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LED_0 /<br>GPIO_0     | 35           | S, PD, IO            | <b>LED_0:</b> Link Status LED. This pin can also be used as LED or clock output through Register selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| LED_1 /<br>GPIO_1     | 6            | S, PD, IO            | <b>LED_1:</b> Link Status and BLINK for TX/RX Activity. This pin can also be used as LED or clock output via Strap/Register selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MEDIUM DEI            | PENDENT      | INTERFACE            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRD_M                 | 13           | IO                   | Differential Transmit and Receive: Bidirectional differential signaling configured for 100BASE-T1 operation, IEEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRD_P                 | 12           |                      | 802.3bw compliant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| POWER COM             | NECTION      | IS                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| GND                   | GND          | GROUND               | Ground: This must always be connected to power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

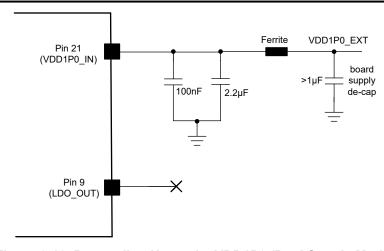

| LDO_OUT               | 9            | SUPPLY               | 1.0V LDO Out: 1.0V Internal LDO Regulator Output 1.0V is generated internally from 3.3V VDDA Core supply. Connect to VDD1P0 (Pin 21) for Single Supply Mode. Leave floating for Dual Supply Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| L                     | 1            |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

### **Table 5-1. Pin Functions (continued)**

| PIN                 |       | STATE <sup>(1)</sup> | DESCRIPTION                                                                                                   |  |

|---------------------|-------|----------------------|---------------------------------------------------------------------------------------------------------------|--|

| NAME <sup>(2)</sup> | NO.   | SIAIE                | DESCRIPTION                                                                                                   |  |

|                     |       |                      | VDD1P0 Supply: 1.0V                                                                                           |  |

| VDD1P0              | 21    | SUPPLY               | Connect to LDO_OUT (Pin 9) for Single Supply Mode.                                                            |  |

| VDDIFU              | 21    | SOFFLI               | Connect to external regulator for Dual Supply Mode.                                                           |  |

|                     |       |                      | In Dual Supply Mode, recommend using ferrite bead and 2.2μF and 0.1μF ceramic decoupling capacitors.          |  |

| VDDA                | 44    | SUPPLY               | Core Supply: 3.3V                                                                                             |  |

| VDDA                | 11    | SUPPLY               | Recommend using 0.47µF and 0.01µF ceramic decoupling capacitors; optional ferrite bead can be used.           |  |

| VDDIO               | 24    | SUPPLY               | IO Supply: 1.8V, 2.5V, or 3.3V                                                                                |  |

| VDDIO               | 34    | SUPPLY               | Recommend using ferrite bead, 0.47μF and 0.01μF ceramic decoupling capacitors.                                |  |

|                     |       |                      | Optional MAC Interface Supply: 1.8V, 2.5V, or 3.3V                                                            |  |

|                     |       |                      | Optional separate supply for MAC interface pins. This pin supplies power to the MAC interface pins and can be |  |

| VDDMAC              | 22    | SUPPLY               | kept at a different voltage level as compared to other IO pins. Recommend using 0.47μF, and 0.01μF ceramic    |  |

| VDDIVIAC            | 22    | SUPPLY               | decoupling capacitors and ferrite bead. When separate VDDMAC is not required in the system then it must be    |  |

|                     |       |                      | connected to VDDIO. When connecting to VDDIO, 0.47µF on the VDDIO can be removed. 0.47µF must still be        |  |

|                     |       |                      | connected close to VDDMAC. In this case, one common ferrite bead can be used between VDDIO and VDDMAC.        |  |

| VSLEEP              | 7     | SUPPLY               | VSLEEP Supply: 3.3V                                                                                           |  |

| VOLEEP              | '     | SUPPLY               | Recommend using 0.1μF ceramic decoupling capacitors.                                                          |  |

| DO NOT CON          | INECT |                      |                                                                                                               |  |

| DNC                 | 17    | _                    | DNC: Do not connect (leave floating)                                                                          |  |

(1) Pin Type:

I = Input

O = Output

IO = Input/Output

OD = Open Drain

PD = Internal pulldown

PU = Internal pullup

S = Bootstrap configuration pin (all configuration pins have weak internal pullups or pulldowns)

(2) When pins are unused, follow the recommended connection requirements provided in the table above. If pins do not have required termination, the pins can be left floating.

Product Folder Links: DP83TC815-Q1

(3) Do not drive the GPIO\_3 HIGH before power-up.

## 5.1 Pin Power Domain

Table 5-2. Pin Domain

| PIN NO | PIN NAME             | VOLTAGE DOMAIN |

|--------|----------------------|----------------|

| 1      | MDC                  | VDDIO          |

| 2      | INT_N                | VDDIO          |

| 3      | RESET_N              | VDDIO          |

| 4      | XO                   | VDDIO          |

| 5      | XI                   | VDDIO          |

| 6      | LED_1/GPIO_1         | VDDIO          |

| 8      | WAKE                 | VSLEEP         |

| 10     | INH                  | VSLEEP         |

| 12     | TRD_P                | VDDA           |

| 13     | TRD_M                | VDDA           |

| 14     | RX_ER / GPIO_6       | VDDMAC         |

| 15     | RX_DV/CRS_DV/RX_CTRL | VDDMAC         |

| 16     | CLKOUT/GPIO_2        | VDDMAC         |

| 18     | GPIO_3               | VDDMAC         |

| 19     | GPIO_4               | VDDMAC         |

| 20     | GPIO_5               | VDDMAC         |

| 23     | RX_D3/RX_M           | VDDMAC         |

| 24     | RX_D2/RX_P           | VDDMAC         |

| 25     | RX_D1                | VDDMAC         |

| 26     | RX_D0                | VDDMAC         |

| 27     | RX_CLK               | VDDMAC         |

| 28     | TX_CLK               | VDDMAC         |

| 29     | TX_EN/TX_CTRL        | VDDMAC         |

| 30     | TX_D3                | VDDMAC         |

| 31     | TX_D2                | VDDMAC         |

| 32     | TX_D1/TX_P           | VDDMAC         |

| 33     | TX_D0/TX_M           | VDDMAC         |

| 35     | LED_0/GPIO_0         | VDDIO          |

| 36     | MDIO                 | VDDIO          |

Copyright © 2025 Texas Instruments Incorporated Product Folder Links: *DP83TC815-Q1*

## 5.2 Pin States

Table 5-3. Pin States - POWER-UP / RESET

|        |             | Die 5-5. Fill States - FOV | POWER-UP / RESET |                    |

|--------|-------------|----------------------------|------------------|--------------------|

| PIN NO | PIN<br>NAME | PIN STATE (1)              | PULL TYPE        | PULL VALUE<br>(kΩ) |

| 1      | MDC         | I                          | none             | none               |

| 2      | ĪNT         | OD, O                      | PU               | 9                  |

| 3      | RESET       | I                          | PU               | 9                  |

| 4      | XO          | 0                          | none             | none               |

| 5      | XI          | I                          | none             | none               |

| 6      | LED_1       | I                          | PD               | 9                  |

| 7      | VSLEEP      | SUPPLY                     | none             | none               |

| 8      | WAKE        | I/O                        | PD               | 455                |

| 9      | LDO_OUT     | 0                          | none             | none               |

| 10     | INH         | OD, O                      | none             | none               |

| 11     | VDDA        | SUPPLY                     | none             | none               |

| 12     | TRD_P       | 10                         | none             | none               |

| 13     | TRD_M       | 10                         | none             | none               |

| 14     | RX_ER       | l                          | PD               | 6                  |

| 15     | RX_DV       | 1                          | PD               | 6                  |

| 16     | CLKOUT      | 0                          | none             | none               |

| 17     | DNC         | FLOAT                      | none             | none               |

| 18     | GPIO_3      | l                          | PD               | 9                  |

| 19     | GPIO_4      | l                          | PD               | 9                  |

| 20     | GPIO_5      | l                          | PD               | 9                  |

| 21     | VDD1P0      | SUPPLY                     | none             | none               |

| 22     | VDDMAC      | SUPPLY                     | none             | none               |

| 23     | RX_D3       | l                          | PD               | 9                  |

| 24     | RX_D2       | l                          | PD               | 9                  |

| 25     | RX_D1       | l                          | PD               | 9                  |

| 26     | RX_D0       | l                          | PD               | 9                  |

| 27     | RX_CLK      | I                          | PD               | 9                  |

| 28     | TX_CLK      | I                          | none             | none               |

| 29     | TX_EN       | I                          | none             | none               |

| 30     | TX_D3       | I                          | none             | none               |

| 31     | TX_D2       | I                          | none             | none               |

| 32     | TX_D1       | I                          | none             | none               |

| 33     | TX_D0       | I                          | none             | none               |

| 34     | VDDIO       | SUPPLY                     | none             | none               |

| 35     | LED_0       | I                          | PD               | 9                  |

| 36     | MDIO        | OD, IO                     | none             | none               |

|        |             | 1                          | 1                | 1                  |

#### Table 5-4. Pin States - TC10 SLEEP

|        |             | Table 5-4. Pin States - | TC10 SLEEP (All Supplies Or | n)                 |

|--------|-------------|-------------------------|-----------------------------|--------------------|

| PIN NO | PIN<br>NAME | PIN STATE (1)           | PULL TYPE                   | PULL VALUE<br>(kΩ) |

| 1      | MDC         | I                       | none                        | none               |

| 2      | ĪNT         | OD, O                   | PU                          | 9                  |

| 3      | RESET       | I                       | PU                          | 9                  |

| 4      | XO          | 0                       | none                        | none               |

| 5      | XI          | I                       | none                        | none               |

| 6      | LED_1 (1)   | 1                       | PD                          | 9                  |

| 7      | VSLEEP      | SUPPLY                  | none                        | none               |

| 8      | WAKE        | I/O                     | PD                          | 455                |

| 9      | LDO_OUT     | 0                       | none                        | none               |

| 10     | INH         | OD, O                   | none                        | none               |

| 11     | VDDA        | SUPPLY                  | none                        | none               |

| 12     | TRD_P       | 10                      | none                        | none               |

| 13     | TRD_M       | IO                      | none                        | none               |

| 14     | RX_ER       | I                       | PD                          | 6                  |

| 15     | RX_DV       | I                       | PD                          | 6                  |

| 16     | CLKOUT (2)  | 0                       | none                        | none               |

| 17     | DNC         | FLOAT                   | none                        | none               |

| 18     | GPIO_3      | I                       | PD                          | 9                  |

| 19     | GPIO_4      | I                       | PD                          | 9                  |

| 20     | GPIO_5      | I                       | PD                          | 9                  |

| 21     | VDD1P0      | SUPPLY                  | none                        | none               |

| 22     | VDDMAC      | SUPPLY                  | none                        | none               |

| 23     | RX_D3       | I                       | PD                          | 9                  |

| 24     | RX_D2       | I                       | PD                          | 9                  |

| 25     | RX_D1       | I                       | PD                          | 9                  |

| 26     | RX_D0       | 1                       | PD                          | 9                  |

| 27     | RX_CLK      | I                       | PD                          | 9                  |

| 28     | TX_CLK      | I                       | none                        | none               |

| 29     | TX_EN       | I                       | none                        | none               |

| 30     | TX_D3       | I                       | none                        | none               |

| 31     | TX_D2       | I                       | none                        | none               |

| 32     | TX_D1       | I                       | none                        | none               |

| 33     | TX_D0       | I                       | none                        | none               |

| 34     | VDDIO       | SUPPLY                  | none                        | none               |

| 35     | LED_0       | I                       | PD                          | 9                  |

| 36     | MDIO        | OD, IO                  | none                        | none               |

|        |             |                         | 1                           | 1                  |

<sup>(1)</sup> If LED\_1 is configured as CLKOUT, the TC10 Sleep IO state becomes: Output with no pull resistors (2) If CLKOUT is configured as LED\_1, the TC10 Sleep IO state becomes: Input,  $9k\Omega$  pull down

## Table 5-5. Pin States - MAC ISOLATE and IEEE PWDN

|        |             | 14510 0 0     | MAC ISOLATE | 117 (0 1002) (12 | and IEEE PVVL | IEEE PWDN |                 |

|--------|-------------|---------------|-------------|------------------|---------------|-----------|-----------------|

| PIN NO | PIN<br>NAME | PIN STATE (1) | PULL TYPE   | PULL VALUE (kΩ)  | PIN STATE (1) | PULL TYPE | PULL VALUE (kΩ) |

| 1      | MDC         | I             | none        | none             | I             | none      | none            |

| 2      | ĪNT         | OD, O         | PU          | 9                | OD, O         | PU        | 9               |

| 3      | RESET       | I             | PU          | 9                | I             | PU        | 9               |

| 4      | XO          | 0             | none        | none             | 0             | none      | none            |

| 5      | ΧI          | I             | none        | none             | I             | none      | none            |

| 6      | LED_1       | 0             | none        | none             | 0             | none      | none            |

| 7      | VSLEEP      | SUPPLY        | none        | none             | SUPPLY        | none      | none            |

| 8      | WAKE        | IO            | PD          | 455              | Ю             | PD        | 455             |

| 9      | LDO_OUT     | 0             | none        | none             | 0             | none      | none            |

| 10     | INH         | OD, O         | none        | none             | OD, O         | none      | none            |

| 11     | VDDA        | SUPPLY        | none        | none             | SUPPLY        | none      | none            |

| 12     | TRD_P       | 10            | none        | none             | Ю             | none      | none            |

| 13     | TRD_M       | 10            | none        | none             | IO            | none      | none            |

| 14     | RX_ER       | I             | PD          | 6                | I             | PD        | 6               |

| 15     | RX_DV       | I             | PD          | 6                | 0             | none      | none            |

| 16     | CLKOUT      | 0             | none        | none             | 0             | none      | none            |

| 17     | DNC         | FLOAT         | none        | none             | FLOAT         | none      | none            |

| 18     | GPIO_3      | I             | PD          | 9                | I             | PD        | 9               |

| 19     | GPIO_4      | I             | PD          | 9                | I             | PD        | 9               |

| 20     | GPIO_5      | I             | PD          | 9                | I             | PD        | 9               |

| 21     | VDD1P0      | SUPPLY        | none        | none             | SUPPLY        | none      | none            |

| 22     | VDDMAC      | SUPPLY        | none        | none             | SUPPLY        | none      | none            |

| 23     | RX_D3       | I             | PD          | 9                | 0             | none      | none            |

| 24     | RX_D2       | I             | PD          | 9                | 0             | none      | none            |

| 25     | RX_D1       | I             | PD          | 9                | 0             | none      | none            |

| 26     | RX_D0       | I             | PD          | 9                | 0             | none      | none            |

| 27     | RX_CLK      | I             | PD          | 9                | 0             | none      | none            |

| 28     | TX_CLK      | I             | PD          | 9                | I             | none      | none            |

| 29     | TX_EN       | I             | PD          | 9                | I             | none      | none            |

| 30     | TX_D3       | I             | PD          | 9                | I             | none      | none            |

| 31     | TX_D2       | I             | PD          | 9                | I             | none      | none            |

| 32     | TX_D1       | I             | PD          | 9                | I             | none      | none            |

| 33     | TX_D0       | I             | PD          | 9                | I             | none      | none            |

| 34     | VDDIO       | SUPPLY        | none        | none             | SUPPLY        | none      | none            |

| 35     | LED_0       | 0             | none        | none             | 0             | none      | none            |

| 36     | MDIO        | OD, IO        | none        | none             | OD, IO        | none      | none            |

#### Table 5-6. Pin States - MII and RGMII

|        |             |               | MII       | States - Will an |               | RGMII     |                 |  |

|--------|-------------|---------------|-----------|------------------|---------------|-----------|-----------------|--|

| PIN NO | PIN<br>NAME | PIN STATE (1) | PULL TYPE | PULL VALUE (kΩ)  | PIN STATE (1) | PULL TYPE | PULL VALUE (kΩ) |  |

| 1      | MDC         | I             | none      | none             | I             | none      | none            |  |

| 2      | ĪNT         | OD, O         | PU        | 9                | OD, O         | PU        | 9               |  |

| 3      | RESET       | I             | PU        | 9                | I             | PU        | 9               |  |

| 4      | XO          | 0             | none      | none             | 0             | none      | none            |  |

| 5      | ΧI          | I             | none      | none             | I             | none      | none            |  |

| 6      | LED_1       | 0             | none      | none             | 0             | none      | none            |  |

| 7      | VSLEEP      | SUPPLY        | none      | none             | SUPPLY        | none      | none            |  |

| 8      | WAKE        | Ю             | PD        | 455              | Ю             | PD        | 455             |  |

| 9      | LDO_OUT     | 0             | none      | none             | 0             | none      | none            |  |

| 10     | INH         | OD, O         | none      | none             | OD, O         | none      | none            |  |

| 11     | VDDA        | SUPPLY        | none      | none             | SUPPLY        | none      | none            |  |

| 12     | TRD_P       | IO            | none      | none             | IO            | none      | none            |  |

| 13     | TRD_M       | IO            | none      | none             | Ю             | none      | none            |  |

| 14     | RX_ER       | 0             | none      | none             | I             | PD        | 6               |  |

| 15     | RX_DV       | 0             | none      | none             | 0             | none      | none            |  |

| 16     | CLKOUT      | 0             | none      | none             | 0             | none      | none            |  |

| 17     | DNC         | FLOAT         | none      | none             | FLOAT         | none      | none            |  |

| 18     | GPIO_3      | I             | PD        | 9                | I             | PD        | 9               |  |

| 19     | GPIO_4      | I             | PD        | 9                | I             | PD        | 9               |  |

| 20     | GPIO_5      | I             | PD        | 9                | I             | PD        | 9               |  |

| 21     | VDD1P0      | SUPPLY        | none      | none             | SUPPLY        | none      | none            |  |

| 22     | VDDMAC      | SUPPLY        | none      | none             | SUPPLY        | none      | none            |  |

| 23     | RX_D3       | 0             | none      | none             | 0             | none      | none            |  |

| 24     | RX_D2       | 0             | none      | none             | 0             | none      | none            |  |

| 25     | RX_D1       | 0             | none      | none             | 0             | none      | none            |  |

| 26     | RX_D0       | 0             | none      | none             | 0             | none      | none            |  |

| 27     | RX_CLK      | 0             | none      | none             | 0             | none      | none            |  |

| 28     | TX_CLK      | 0             | none      | none             | I             | none      | none            |  |

| 29     | TX_EN       | I             | none      | none             | I             | none      | none            |  |

| 30     | TX_D3       | I             | none      | none             | I             | none      | none            |  |

| 31     | TX_D2       | I             | none      | none             | I             | none      | none            |  |

| 32     | TX_D1       | I             | none      | none             | I             | none      | none            |  |

| 33     | TX_D0       | I             | none      | none             | I             | none      | none            |  |

| 34     | VDDIO       | SUPPLY        | none      | none             | SUPPLY        | none      | none            |  |

| 35     | LED_0       | 0             | none      | none             | 0             | none      | none            |  |

| 36     | MDIO        | OD, IO        | none      | none             | OD, IO        | none      | none            |  |

#### Table 5-7. Pin States - SGMII

|        | PIN     | SGMII         |           |                    |  |  |

|--------|---------|---------------|-----------|--------------------|--|--|

| PIN NO | NAME    | PIN STATE (1) | PULL TYPE | PULL VALUE<br>(kΩ) |  |  |

| 1      | MDC     | I             | none      | none               |  |  |

| 2      | ĪNT     | OD, O         | PU        | 9                  |  |  |

| 3      | RESET   | I             | PU        | 9                  |  |  |

| 4      | XO      | 0             | none      | none               |  |  |

| 5      | XI      | I             | none      | none               |  |  |

| 6      | LED_1   | 0             | none      | none               |  |  |

| 7      | VSLEEP  | SUPPLY        | none      | none               |  |  |

| 8      | WAKE    | 10            | PD        | 455                |  |  |

| 9      | LDO_OUT | 0             | none      | none               |  |  |

| 10     | INH     | OD, O         | none      | none               |  |  |

| 11     | VDDA    | SUPPLY        | none      | none               |  |  |

| 12     | TRD_P   | 10            | none      | none               |  |  |

| 13     | TRD_M   | 10            | none      | none               |  |  |

| 14     | RX_ER   | I             | PD        | 6                  |  |  |

| 15     | RX_DV   | I             | PD        | 6                  |  |  |

| 16     | CLKOUT  | 0             | none      | none               |  |  |

| 17     | DNC     | FLOAT         | none      | none               |  |  |

| 18     | GPIO_3  | I             | PD        | 9                  |  |  |

| 19     | GPIO_4  | I             | PD        | 9                  |  |  |

| 20     | GPIO_5  | 1             | PD        | 9                  |  |  |

| 21     | VDD1P0  | SUPPLY        | none      | none               |  |  |

| 22     | VDDMAC  | SUPPLY        | none      | none               |  |  |

| 23     | RX_D3   | 0             | none      | none               |  |  |

| 24     | RX_D2   | 0             | none      | none               |  |  |

| 25     | RX_D1   | I             | PD        | 9                  |  |  |

| 26     | RX_D0   | I             | PD        | 9                  |  |  |

| 27     | RX_CLK  | I             | PD        | 9                  |  |  |

| 28     | TX_CLK  | I             | none      | none               |  |  |

| 29     | TX_EN   | I             | none      | none               |  |  |

| 30     | TX_D3   | I             | none      | none               |  |  |

| 31     | TX_D2   | I             | none      | none               |  |  |

| 32     | TX_D1   | I             | none      | none               |  |  |

| 33     | TX_D0   | I             | none      | none               |  |  |

| 34     | VDDIO   | SUPPLY        | none      | none               |  |  |

| 35     | LED_0   | 0             | none      | none               |  |  |

| 36     | MDIO    | OD, IO        | none      | none               |  |  |

(1) Type: I = Input O = Output IO = Input/Output

OD = Open Drain

PD = Internal pulldown

PU = Internal pullup

### 5.3 Pin Multiplexing

Following table provides details of the different functions available on GPIO pins.

**LED:** Pin configured as LED indication.

**CLKOUT:** Pin configured as a clock output signal

Event Triggers/Capture: Pin configured to capture and trigger 802.1AS Time stamp generated events

PTP Interrupt: Pin configured to output 802.1AS/PTP specific interrupts

**50/25MHz PTP Input:** 50/25MHz Reference Clock for PTP

Sync Clock: Programmable Frequency Clock synchronous to PTP wall clock

**PPM Monitor:** Pin configured for external clock input to monitor PPM w.r.t internal clocks

Table 5-8. Pin Multiplexing

| FIELD           | PIN | Default | LED | CLKOUT 25MHz | Event Trigger /<br>Capture |

|-----------------|-----|---------|-----|--------------|----------------------------|

| LED_0 / GPIO_0  | 35  | LED_0   | Yes |              | Yes                        |

| LED_1 / GPIO_1  | 6   | LED_1   | Yes | Yes          | Yes                        |

| CLKOUT / GPIO_2 | 16  | CLKOUT  | Yes | Yes          | Yes                        |

| GPIO_3          | 18  | GPIO_3  |     |              | Yes                        |

| GPIO_4          | 19  | GPIO_4  |     |              | Yes                        |

| GPIO_5          | 20  | GPIO_5  |     |              | Yes                        |

| RX_ER / GPIO_6  | 14  | RX_ER   |     |              | Yes                        |

Table 5-9. Pin Multiplexing - PTP, Interrupts

|                 |     |                    | ,              |               |

|-----------------|-----|--------------------|----------------|---------------|

| FIELD           | PIN | 50/25MHz PTP Input | PTP Sync Clock | PTP Interrupt |

| LED_0 / GPIO_0  | 35  | Yes                |                | Yes           |

| LED_1 / GPIO_1  | 6   |                    |                | Yes           |

| CLKOUT / GPIO_2 | 16  |                    | Yes            | Yes           |

| GPIO_3          | 18  |                    | Yes            | Yes           |

| GPIO_4          | 19  |                    | Yes            | Yes           |

| GPIO_5          | 20  | Yes                |                | Yes           |

| RX_ER / GPIO_6  | 14  |                    |                | Yes           |

## **6 Specifications**

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                   |                                                                                                         | MIN  | TYP MAX      | UNIT                                  |

|-------------------|---------------------------------------------------------------------------------------------------------|------|--------------|---------------------------------------|

| Input Voltage     | VDDA                                                                                                    | -0.3 | 4            | V                                     |

| Input Voltage     | VDD1P0                                                                                                  | -0.3 | 1.4          | V                                     |

| Input Voltage     | VDDIO (3.3V)                                                                                            | -0.3 | 4            | V                                     |

| Input Voltage     | VDDIO(2.5V)                                                                                             | -0.3 | 4            | V                                     |

| Input Voltage     | VDDIO(1.8V)                                                                                             | -0.3 | 4            | V                                     |

| Input Voltage     | VSLEEP                                                                                                  | -0.3 | 4            | V                                     |

| Pins              | MDI (TRD_M, TRD_P)                                                                                      | -0.3 | 4            | V                                     |

| Input Voltage     | MDC, RESET, XI, LED_1, RX_ER, RX_CTRL, CLKOUT, RX_D[3:0], TX_CLK, TX_CTRL, TX_D[3:0], LED_0, MDIO, GPIO | -0.3 | VDDIO + 0.3  | V                                     |

| Pins              | MDIO, MDC, GPIO, XI, XO, INT, RESET, CLKOUT                                                             | -0.3 | VDDIO + 0.3  | V                                     |

| Output<br>Voltage | INH                                                                                                     | -0.3 | VSLEEP + 0.3 | V                                     |

| Input Voltage     | WAKE                                                                                                    | -0.3 | VSLEEP + 0.3 | · · · · · · · · · · · · · · · · · · · |

| Output<br>Voltage | INT, LED_1, RX_CTRL, CLKOUT, RX_D[3:0], RX_CLK, LED_0, MDIO, GPIO                                       | -0.3 | 4            | V                                     |

| TJ                | Junction temperature                                                                                    | -40  | 150          | °C                                    |

| T <sub>stg</sub>  | Storage temperature                                                                                     | -65  | 150          | °C                                    |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

#### 6.2 ESD Ratings

|                    |                             |                                              |                   | VALUE          | UNIT |

|--------------------|-----------------------------|----------------------------------------------|-------------------|----------------|------|

|                    | Human body model (HBM), per | All pins                                     | ±2000             |                |      |

|                    |                             | AEC Q100-002 <sup>(1)</sup>                  | TRD_N, TRD_P pins | ±8000          |      |

| V <sub>(ESD)</sub> | Electrostatic discharge     | Charged device model (CDM), per AEC Q100-011 | All pins          | ±500           | V    |

|                    |                             | IEC 61000-4-2 contact discharge              | TRD_N, TRD_P pins | ±2000<br>±8000 |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing must be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                   |                                   | MIN    | NOM | MAX    | UNIT |

|-------------------|-----------------------------------|--------|-----|--------|------|

|                   | IO Supply Voltage, 1.8V operation | 1.665  | 1.8 | 1.935  |      |

| VDDIO /<br>VDDMAC | IO Supply Voltage, 2.5V operation | 2.3125 | 2.5 | 2.6875 | V    |

|                   | IO Supply Voltage, 3.3V operation | 3.0525 | 3.3 | 3.5475 |      |

| VDDA              | Core Supply Voltage, 3.3V         | 2.97   | 3.3 | 3.63   | V    |

| VDD1P0            | Core Digital External Supply 1V   | 0.95   | 1.0 | 1.1    | V    |

| VSLEEP            | Sleep Supply Voltage, 3.3V        | 2.97   | 3.3 | 3.63   | V    |

| T <sub>A</sub>    | Ambient temperature               | -40    |     | 125    | °C   |

Copyright © 2025 Texas Instruments Incorporated

#### **6.4 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | RHA (VQFN)<br>36 PINS | UNIT |

|-----------------------|----------------------------------------------|-----------------------|------|

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 30.7                  | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 21.6                  | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 13.1                  | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3                   | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 11.9                  | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.8                   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

#### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                     | TEST CONDITIONS                   | MIN             | TYP MAX         | UNIT                                  |

|-----------------------|-----------------------------------------------|-----------------------------------|-----------------|-----------------|---------------------------------------|

| 100BASE-T1            | PMA CONFORMANCE                               | 1                                 |                 |                 | <b>'</b>                              |

| V <sub>OD-MDI</sub>   | Output Differential Voltage                   | $R_{L(diff)} = 100\Omega$         |                 | 2.2             | V                                     |

| R <sub>MDI-Diff</sub> | Integrated Differential<br>Output Termination | TRD_P and TRD_M                   |                 | 100             | Ω                                     |

| BOOTSTRAF             | P DC CHARACTERISTICS (2                       | 2 Level)                          |                 |                 |                                       |

| V <sub>MODE1</sub>    | Mode 1 Strap Voltage<br>Range                 | VDDIO = 3.3V ±7.5%, 2-level strap | 0               | 0.8             | V                                     |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 3.3V ±7.5%, 2-level strap | 2               | VDDIO           | V                                     |

| $V_{MODE1}$           | Mode 1 Strap Voltage<br>Range                 | VDDIO = 2.5V ±7.5%, 2-level strap | 0               | 0.7             | V                                     |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 2.5V ±7.5%, 2-level strap | 1.7             | VDDIO           | V                                     |

| V <sub>MODE1</sub>    | Mode 1 Strap Voltage<br>Range                 | VDDIO = 1.8V ±7.5%, 2-level strap | 0               | 0.35 x<br>VDDIO |                                       |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 1.8V ±7.5%, 2-level strap | 0.65 x<br>VDDIO | VDDIO           | V                                     |

| BOOTSTRAF             | P DC CHARACTERISTICS (3                       | Level)                            | 1               |                 |                                       |

| V <sub>MODE1</sub>    | Mode 1 Strap Voltage<br>Range                 | VDDIO = 3.3V ±7.5%, 3-level strap | 0               | 0.18 x<br>VDDIO |                                       |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 3.3V ±7.5%, 3-level strap | 0.22 x<br>VDDIO | 0.42 x<br>VDDIO | · · · · · · · · · · · · · · · · · · · |

| V <sub>MODE3</sub>    | Mode 3 Strap Voltage<br>Range                 | VDDIO = 3.3V ±7.5%, 3-level strap | 0.46 x<br>VDDIO | VDDIO           | V                                     |

| V <sub>MODE1</sub>    | Mode 1 Strap Voltage<br>Range                 | VDDIO = 2.5V ±7.5%, 3-level strap | 0               | 0.25 x<br>VDDIO |                                       |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 2.5V ±7.5%, 3-level strap | 0.29 x<br>VDDIO | 0.56 x<br>VDDIO | V                                     |

| V <sub>MODE3</sub>    | Mode 3 Strap Voltage<br>Range                 | VDDIO = 2.5V ±7.5%, 3-level strap | 0.65 x<br>VDDIO | VDDIO           | V                                     |

| V <sub>MODE1</sub>    | Mode 1 Strap Voltage<br>Range                 | VDDIO = 1.8V ±7.5%, 3-level strap | 0               | 0.35 x<br>VDDIO | · · · · · · · · · · · · · · · · · · · |

| V <sub>MODE2</sub>    | Mode 2 Strap Voltage<br>Range                 | VDDIO = 1.8V ±7.5%, 3-level strap | 0.40 x<br>VDDIO | 0.75 x<br>VDDIO | V                                     |

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                    | TEST CONDITIONS                                | MIN             | TYP | MAX            | UNIT |

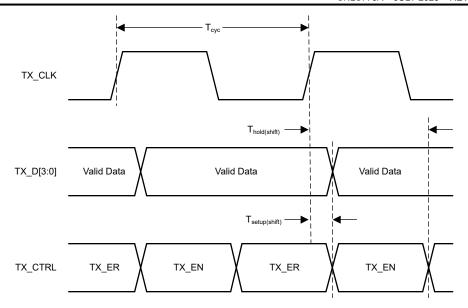

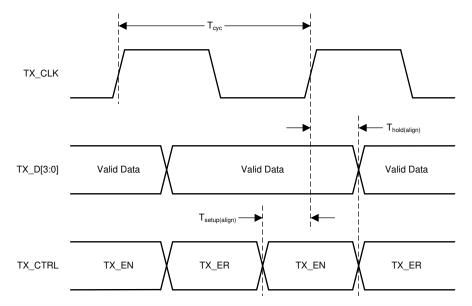

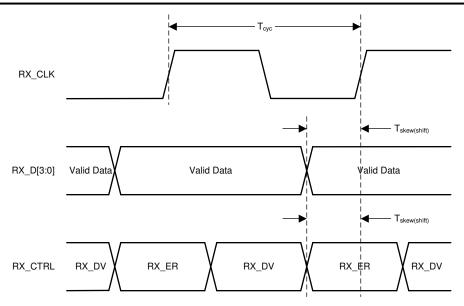

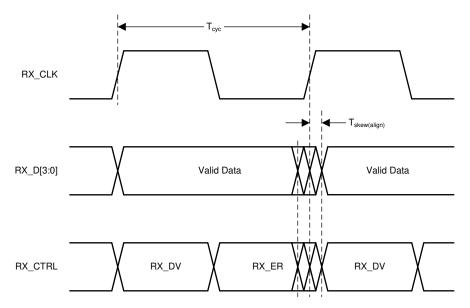

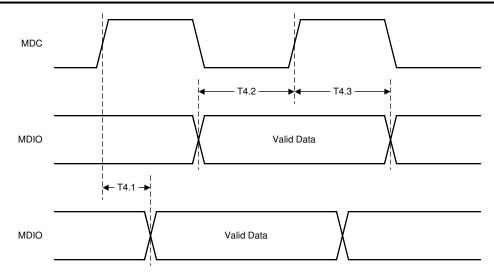

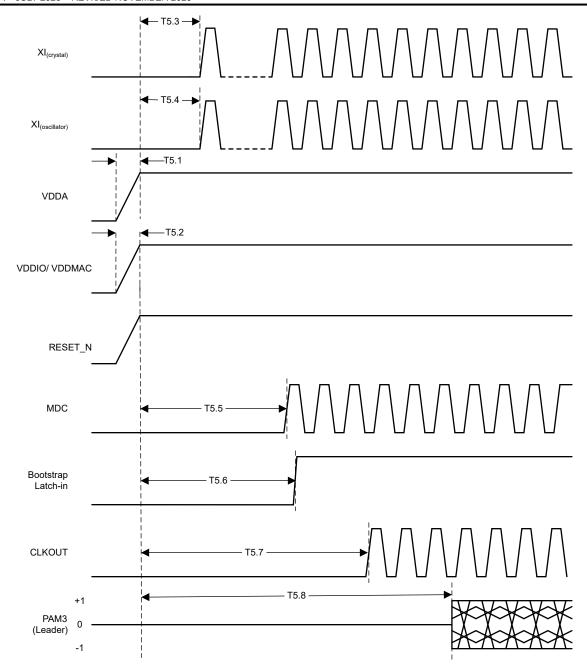

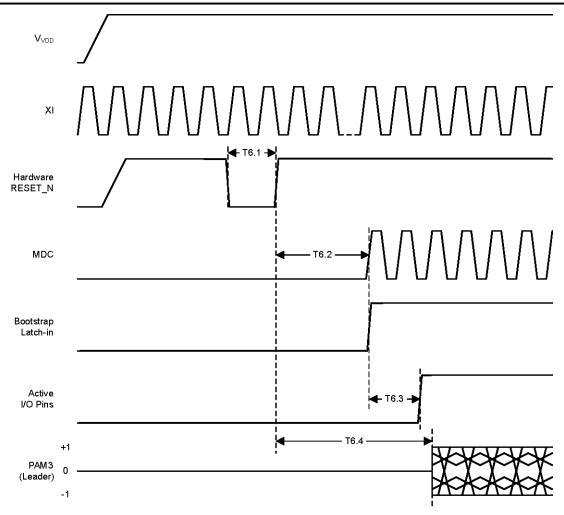

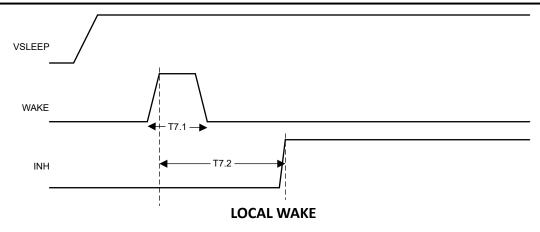

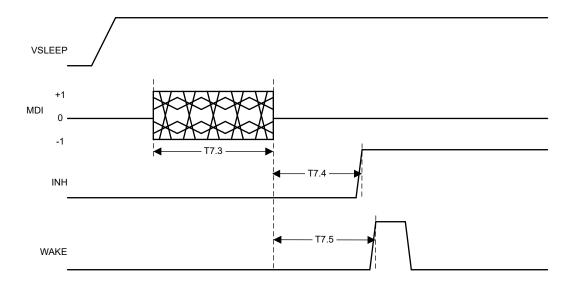

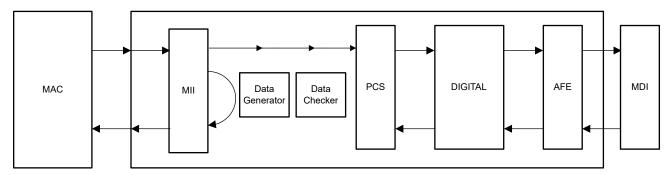

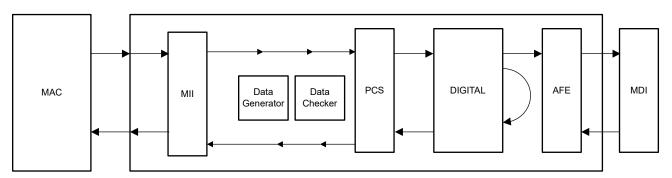

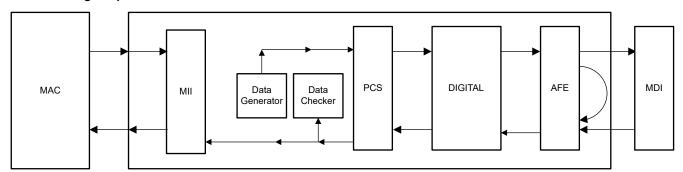

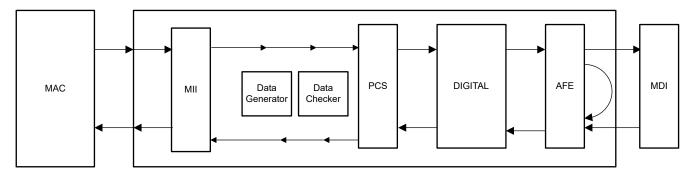

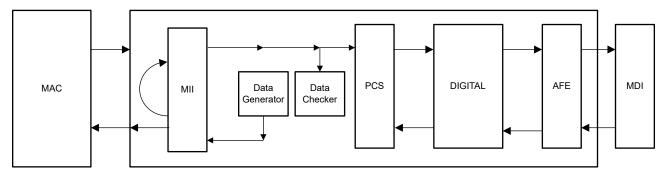

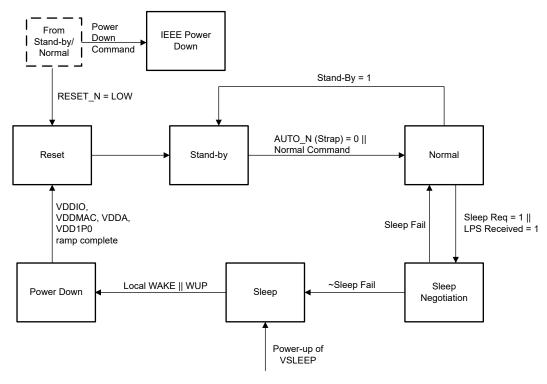

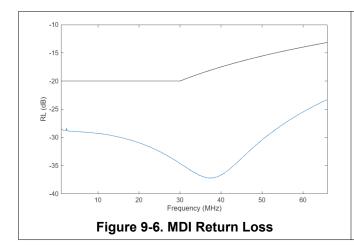

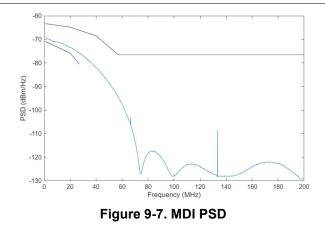

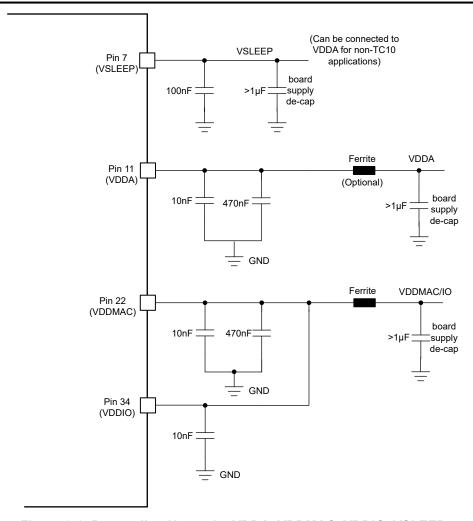

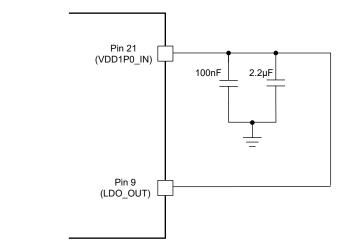

|---------------------|----------------------------------------------|------------------------------------------------|-----------------|-----|----------------|------|