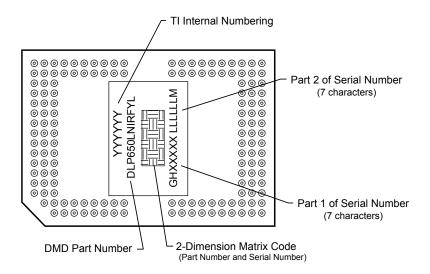

**DLP650LNIR**

DLPS136-NOVEMBER 2018

# DLP650LNIR 0.65 NIR WXGA S450 DMD

#### 1 Features

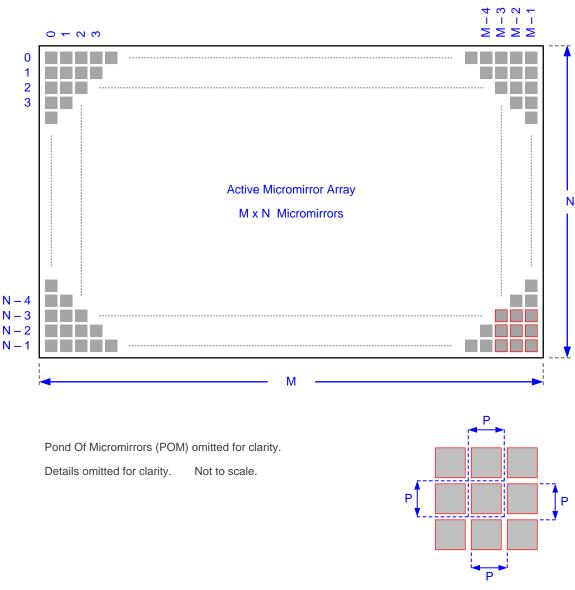

- 1280 x 800 (WXGA) Array with >1 Million Micromirrors

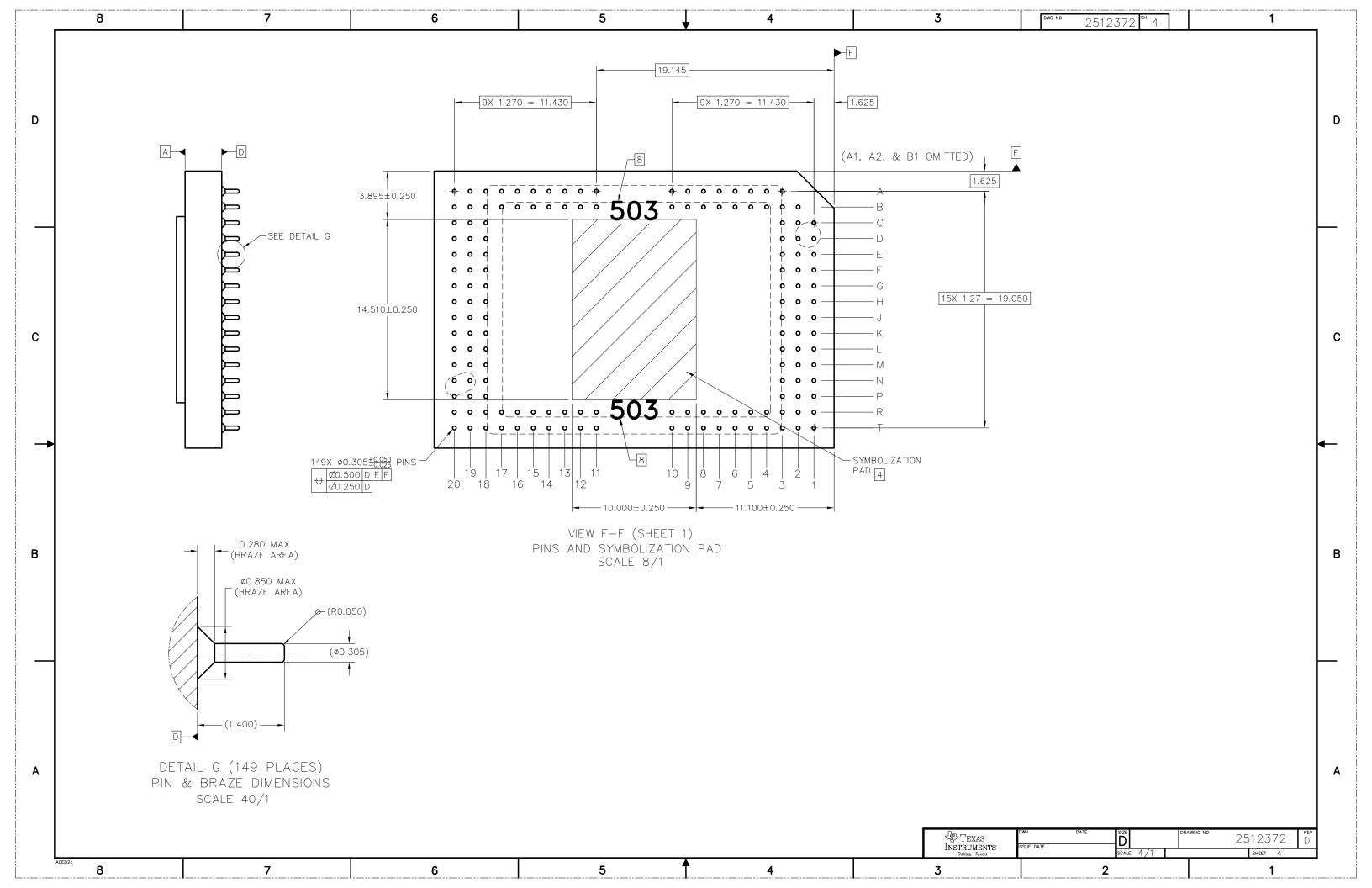

- 10.8 µm Micromirror Pitch

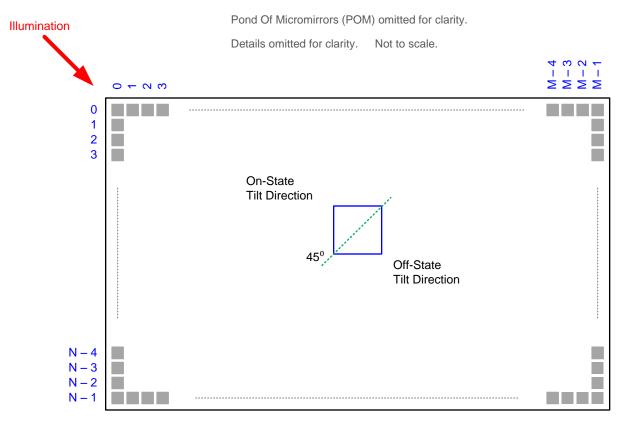

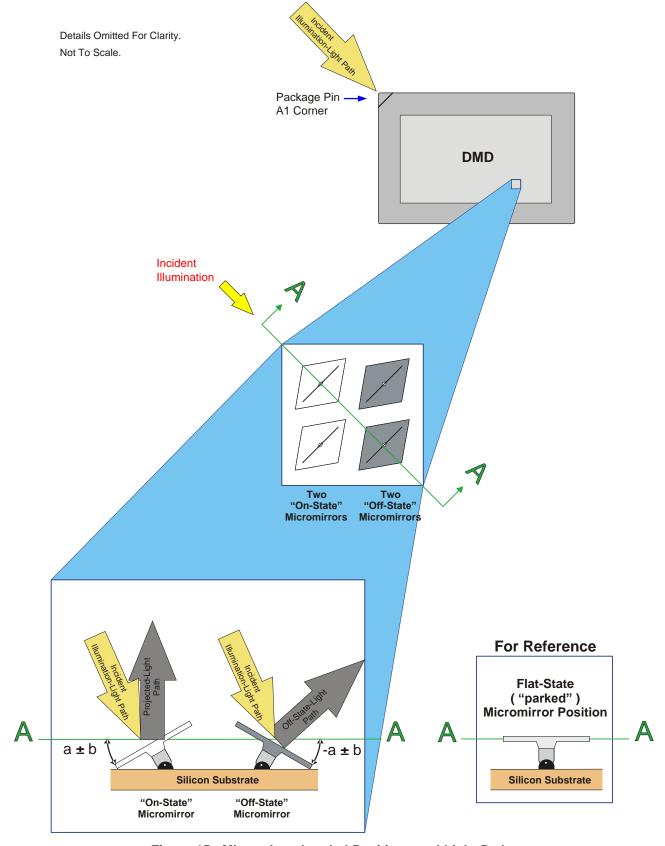

- ±12° Micromirror Tilt Angle (Relative to Flat State)

- 0.65-Inch Diagonal Array Designed for Corner Illumination

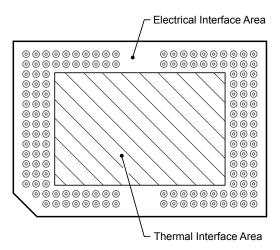

- 0.5 °C/W Thermal Resistance High Efficiency Package

- Efficient Steering of NIR Light (800 nm to 2000 nm)

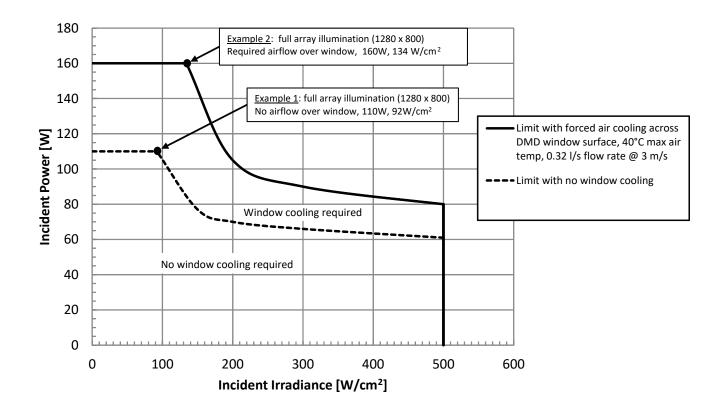

- Up to 160-W Incident on DMD

- Window Transmission Efficiency >98% (950 nm to 1150 nm, Single Pass, Two Window Surfaces)

- Window Transmission Efficiency >93% (850 nm to 2000 nm, Single Pass, Two Window Surfaces)

- Polarization Independent Aluminum Micromirrors

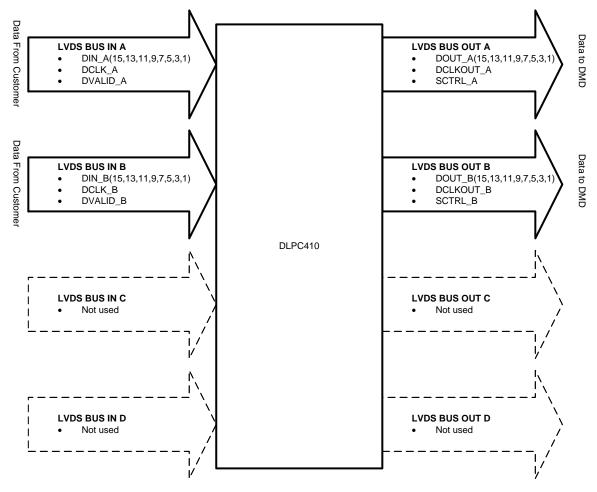

- 16-Bit, 2xLVDS, 400-MHz Input Data Bus

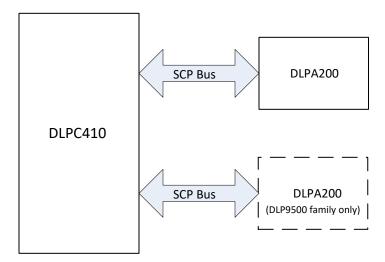

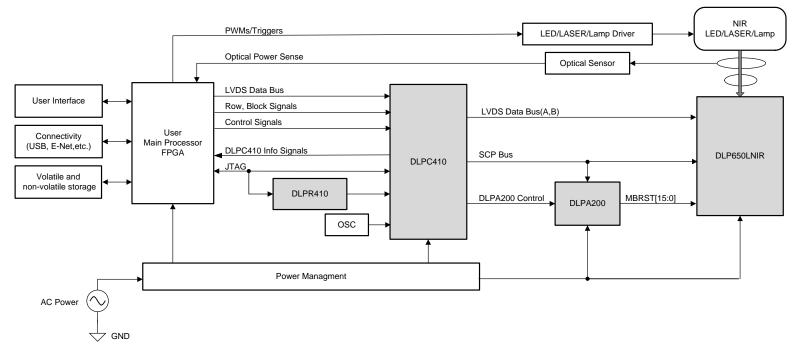

- Dedicated DLPC410 Controller, DLPR410 PROM, and DLPA200 Micromirror Driver for Reliable High Speed Operation

- Binary Pattern Rates up to 12,500 Hz

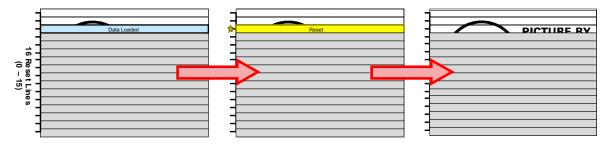

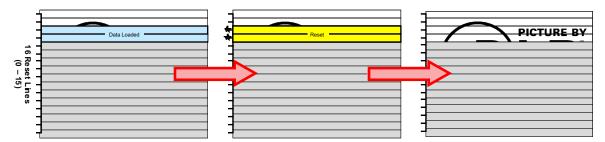

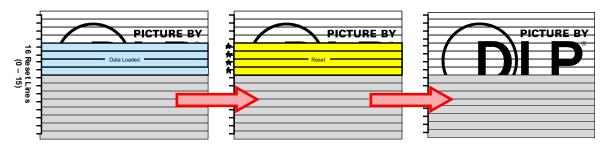

- Global, Single, Dual, and Quad Block Mirror Clocking Pulse (Reset) Operational Modes

# 2 Applications

- 3D Printing, Selective Laser Sintering (SLS)

- Dynamic Grayscale Laser Marking and Coding

- Industrial Printing, Flexographic Printing, Digital Platemaking

- Repair and Ablation

- Spectroscopy

- 3D Machine vision and 3D Biometrics

- Infrared Scene Projection

- Hyperspectral Imaging

- Optical Switching

# 3 Description

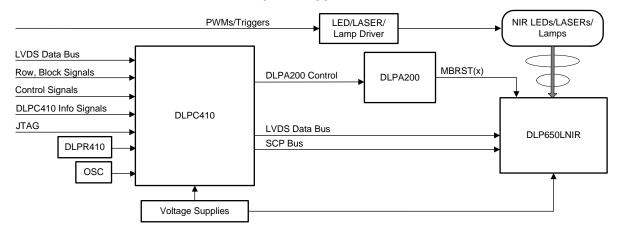

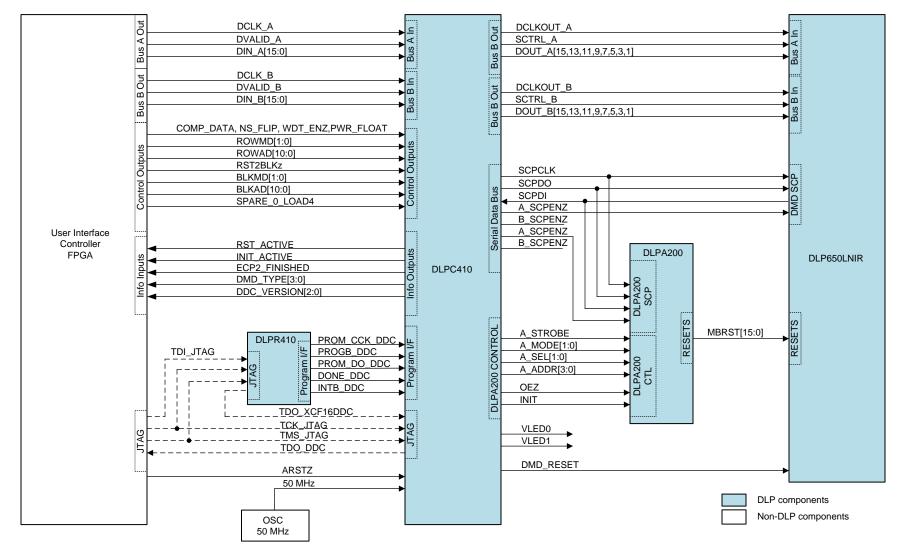

The DLP650LNIR digital micromirror device (DMD) operates as a spatial light modulator (SLM) to steer near-infrared (NIR) light and generate high speed patterns for advanced imaging in industrial equipment. The thermally efficient package allows customers to combine the DMD with high-power NIR laser illumination for dynamic digital printing, sintering and marking solutions. The DLP650LNIR, DLPC410, DLPR410 and DLPA200 chipset provides 1-bit pattern rates up to 12,500 Hz with pixel-accurate control so engineers can design more innovative and precise optical systems than traditional steering lasers allow.

#### Device Information<sup>(1)</sup>

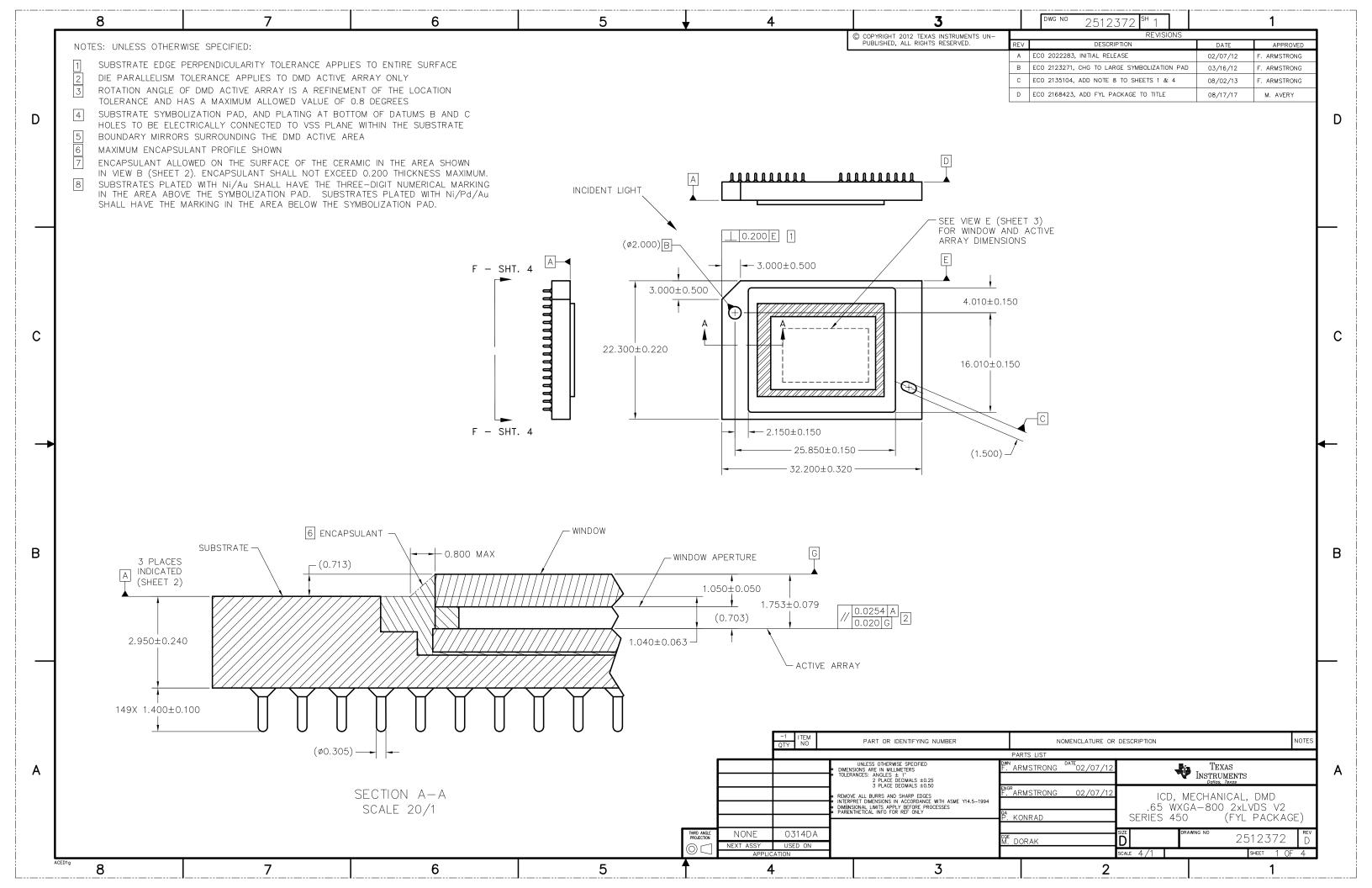

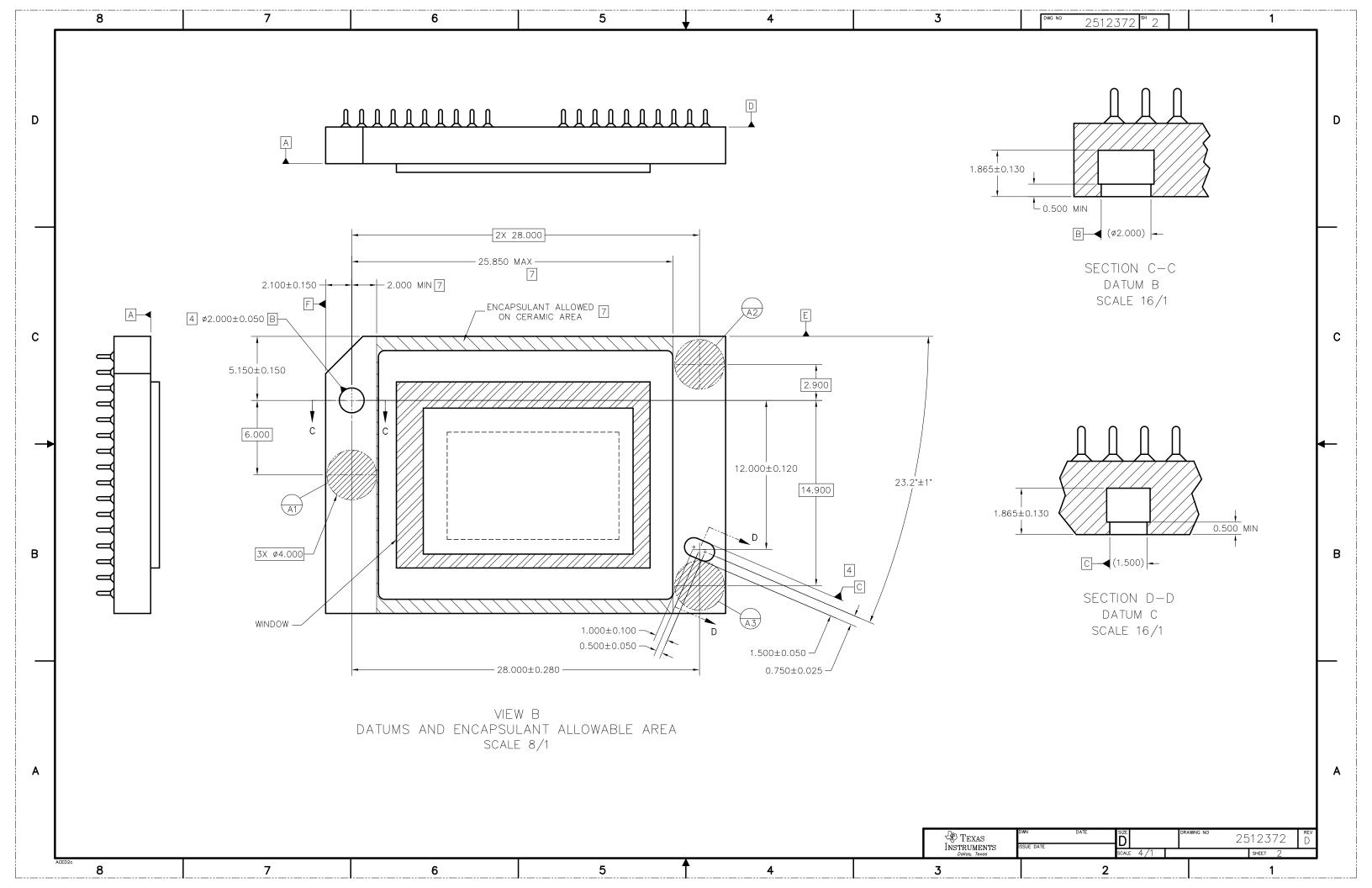

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| DLP650LNIR  | FYL (149) | 22.30 mm × 32.20 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

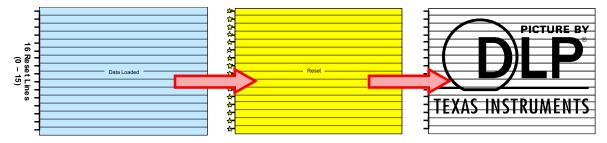

#### Simplified Application

DLPS136 – NOVEMBER 2018 www.ti.com

# **Table of Contents**

| 1 | Features 1                                        |    | 7.5 Feature Description                                       | 31   |

|---|---------------------------------------------------|----|---------------------------------------------------------------|------|

| 2 | Applications                                      |    | 7.6 Optical Interface and System Image Quality Considerations | 3′   |

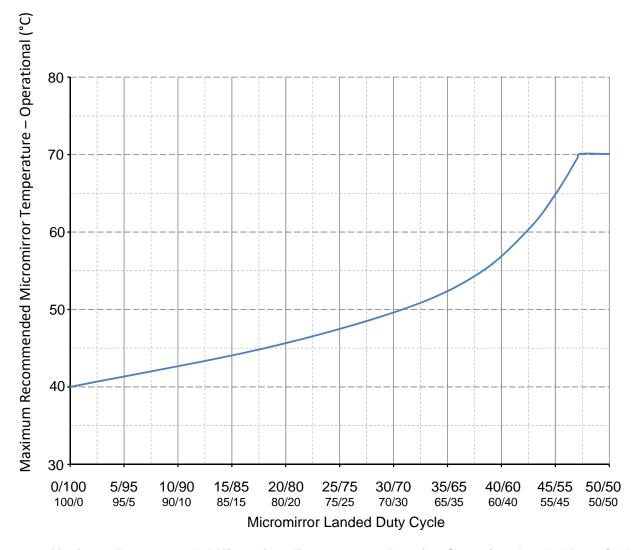

| 3 | Description                                       |    | 7.7 Micromirror Temperature Calculations                      |      |

| 4 | Revision History                                  |    | 7.8 Micromirror Landed-On/Landed-Off Duty Cycle               | 35   |

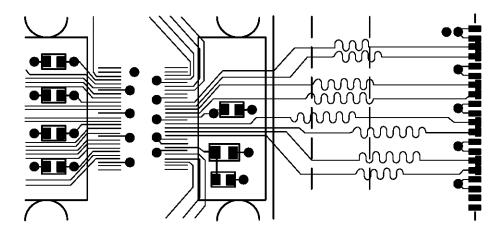

| 5 | Pin Configuration and Functions 3                 | 8  | Application and Implementation                                | . 37 |

| 6 | Specifications 8                                  |    | 8.1 Application Information                                   |      |

|   | 6.1 Absolute Maximum Ratings 8                    |    | 8.2 Typical Application                                       |      |

|   | 6.2 Storage Conditions9                           | 9  | Power Supply Recommendations                                  |      |

|   | 6.3 ESD Ratings9                                  | 10 | Layout                                                        |      |

|   | 6.4 Recommended Operating Conditions9             |    | 10.1 Layout Guidelines                                        |      |

|   | 6.5 Thermal Information                           |    | 10.2 Layout Example                                           |      |

|   | 6.6 Electrical Characteristics                    | 11 | Device and Documentation Support                              |      |

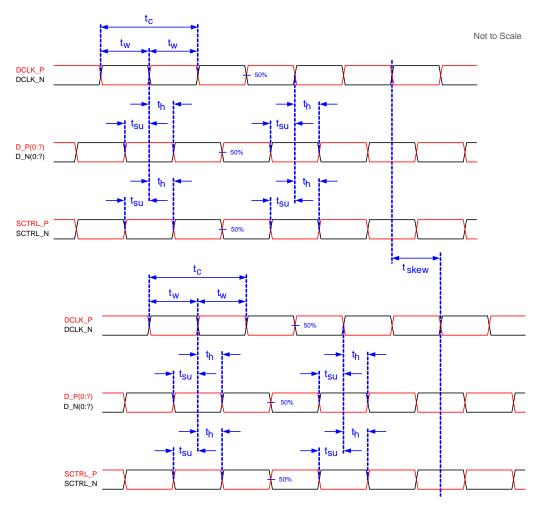

|   | 6.7 Timing Requirements                           |    |                                                               |      |

|   | 6.8 System Mounting Interface Loads 16            |    | 11.1 Device Support                                           |      |

|   | 6.9 Micromirror Array Physical Characteristics 18 |    | 11.2 Documentation Support                                    |      |

|   | 6.10 Micromirror Array Optical Characteristics 19 |    | 11.3 Related Links                                            |      |

|   | 6.11 Window Characteristics20                     |    | 11.4 Receiving Notification of Documentation Update           |      |

|   | 6.12 Chipset Component Usage Specification 20     |    | 11.5 Community Resources                                      | 45   |

| 7 | Detailed Description21                            |    | 11.6 Trademarks                                               | 45   |

| • | 7.1 Overview                                      |    | 11.7 Electrostatic Discharge Caution                          | 45   |

|   | 7.2 System Functional Block Diagram               |    | 11.8 Glossary                                                 | 45   |

|   | 7.3 Feature Description                           | 12 | Mechanical, Packaging, and Orderable                          |      |

|   | ·                                                 |    | Information                                                   | . 46 |

|   | 7.4 Device Operational Modes                      |    |                                                               |      |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| November 2018 | *        | Initial release. |

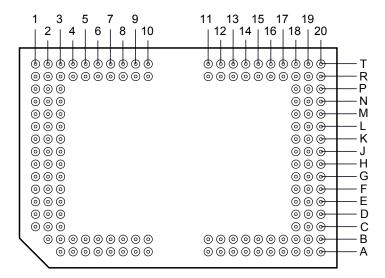

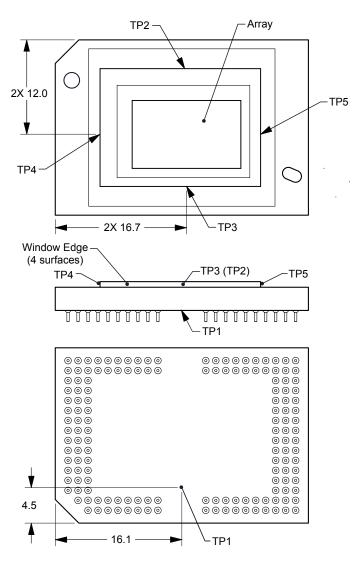

# 5 Pin Configuration and Functions

# TEXAS INSTRUMENTS

## **Pin Functions**

|                     |       | riii i            | runctions |                     |                                       |  |  |  |

|---------------------|-------|-------------------|-----------|---------------------|---------------------------------------|--|--|--|

| PIN                 | NO    | NET LENGTH (mils) | SIGNAL    | TYPE <sup>(1)</sup> | DESCRIPTION                           |  |  |  |

| NAME                | NO.   | (111113)          |           |                     |                                       |  |  |  |

| DATA INPUTS         |       |                   |           |                     | I                                     |  |  |  |

| D_AN(1)             | G20   | 711.64            |           |                     |                                       |  |  |  |

| D_AN(3)             | H19   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(5)             | F18   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(7)             | E18   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(9)             | C20   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(11)            | B18   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(13)            | A20   | 711.60            |           |                     |                                       |  |  |  |

| D_AN(15)            | B19   | 711.58            | LVDS      | 1                   | LVDS pair for Data Bus A              |  |  |  |

| D_AP(1)             | H20   | 711.66            |           |                     | EVBO pair for Bata Bas /              |  |  |  |

| D_AP(3)             | G19   | 711.61            |           |                     |                                       |  |  |  |

| D_AP(5)             | G18   | 711.59            |           |                     |                                       |  |  |  |

| D_AP(7)             | D18   | 711.60            |           |                     |                                       |  |  |  |

| D_AP(9)             | D20   | 711.59            |           |                     |                                       |  |  |  |

| D_AP(11)            | A18   | 711.58            |           |                     |                                       |  |  |  |

| D_AP(13)            | B20   | 711.59            |           |                     |                                       |  |  |  |

| D_AP(15)            | A19   | 711.59            |           |                     |                                       |  |  |  |

| D_BN(1)             | K20   | 711.61            |           |                     |                                       |  |  |  |

| D_BN(3)             | J19   | 711.59            |           |                     |                                       |  |  |  |

| D_BN(5)             | L18   | 711.59            |           |                     |                                       |  |  |  |

| D_BN(7)             | M18   | 711.6             |           |                     |                                       |  |  |  |

| D_BN(9)             | P20   | 711.6             |           |                     |                                       |  |  |  |

| D_BN(11)            | R18   | 711.59            |           |                     |                                       |  |  |  |

| D_BN(13)            | T20   | 711.59            |           |                     |                                       |  |  |  |

| D_BN(15)            | R19   | 711.59            |           |                     |                                       |  |  |  |

| D_BP(1)             | J20   | 711.61            | LVDS      | I                   | LVDS pair for Data Bus B              |  |  |  |

| D_BP(3)             | K19   | 711.6             |           |                     |                                       |  |  |  |

| D_BP(5)             | K18   | 711.58            |           |                     |                                       |  |  |  |

| D_BP(7)             | N18   | 711.58            |           |                     |                                       |  |  |  |

| D_BP(9)             | N20   | 711.6             |           |                     |                                       |  |  |  |

| D_BP(11)            | T18   | 711.61            |           |                     |                                       |  |  |  |

| D_BP(13)            | R20   | 711.59            |           |                     |                                       |  |  |  |

| D_BP(15)            | T19   | 711.6             |           |                     |                                       |  |  |  |

| DCLK_AN             | D19   | 711.59            |           |                     |                                       |  |  |  |

| DCLK_AP             | E19   | 711.59            | 1         | I                   | LVDS pair for Data Clock A            |  |  |  |

| DCLK_BN             | N19   | 711.6             |           |                     |                                       |  |  |  |

| DCLK_BP             | M19   | 711.61            | 1         | I                   | LVDS pair for Data Clock B            |  |  |  |

| DATA CONTROL INPUTS |       | 1.51              | 1         | <u> </u>            | 1                                     |  |  |  |

| SCTRL_AN            | F20   | 711.62            |           |                     |                                       |  |  |  |

| SCTRL_AP            | E20   | 711.6             | 1         | I                   | LVDS pair for Serial Control (Sync) A |  |  |  |

| SCTRL_BN            | L20   | 711.59            |           |                     |                                       |  |  |  |

| SCTRL_BP            | M20   | 711.59            | 1         | I                   | LVDS pair for Serial Control (Sync) B |  |  |  |

| 33.1KL_DI           | IVIZU | 7.11.00           |           |                     | <u> </u>                              |  |  |  |

<sup>(1)</sup> I = Input, O = Output, G = Ground, A = Analog, P = Power, NC = No Connect.

# Pin Functions (continued)

| PIN                             |                                                          | NET I ENOTE:      |        |                     |                                                                                                                                   |

|---------------------------------|----------------------------------------------------------|-------------------|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME                            | NO.                                                      | NET LENGTH (mils) | SIGNAL | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                       |

| MICROMIRROR BIAS RESET IN       | -                                                        | . ,               |        |                     |                                                                                                                                   |

| MBRST(0)                        | C3                                                       | 507.20            |        |                     |                                                                                                                                   |

| MBRST(1)                        | D2                                                       | 576.83            |        |                     |                                                                                                                                   |

| MBRST(2)                        | D3                                                       | 545.78            |        |                     |                                                                                                                                   |

| MBRST(3)                        | E2                                                       | 636.33            | _      |                     |                                                                                                                                   |

| MBRST(4)                        | G3                                                       | 618.42            | _      |                     |                                                                                                                                   |

| MBRST(5)                        | E1                                                       | 738.25            |        |                     |                                                                                                                                   |

| MBRST(6)                        | G2                                                       | 718.82            |        |                     | Non-logic commetible Missonium Disc                                                                                               |

| MBRST(7)                        | G1                                                       | 777.04            | _      |                     | Non–logic compatible Micromirror Bias<br>Reset signals. Connected directly to the                                                 |

| MBRST(8)                        | N3                                                       | 543.29            |        | I                   | array of pixel micromirrors. Used to hold or                                                                                      |

| MBRST(9)                        | M2                                                       | 612.93            |        |                     | release the micromirrors. Bond Pads connect to an internal pull–down resistor.                                                    |

| MBRST(10)                       | M3                                                       | 580.97            |        |                     | р                                                                                                                                 |

| MBRST(11)                       | L2                                                       | 672.43            |        |                     |                                                                                                                                   |

| MBRST(12)                       | J3                                                       | 653.61            |        |                     |                                                                                                                                   |

| MBRST(13)                       | L1                                                       | 764.00            |        |                     |                                                                                                                                   |

| MBRST(14)                       | J2                                                       | 764.37            |        |                     |                                                                                                                                   |

| MBRST(15)                       | J1                                                       | 813.14            |        |                     |                                                                                                                                   |

| SCP CONTROL                     | JI                                                       | 013.14            |        |                     |                                                                                                                                   |

| SCF CONTROL                     |                                                          |                   |        |                     | Serial Communications Port Clock. Bond                                                                                            |

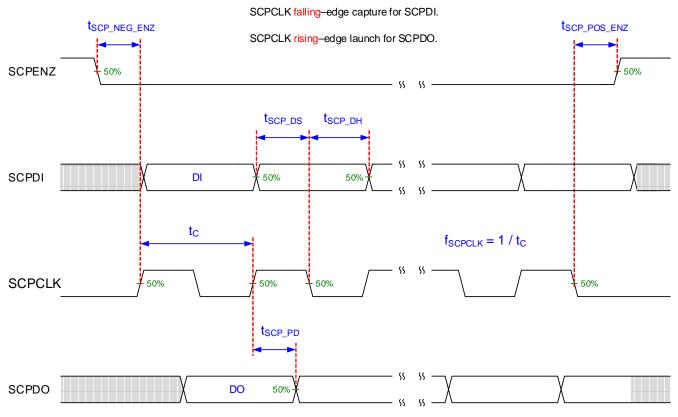

| SCPCLK                          | A8                                                       |                   |        | I                   | Pad connects to an internal pulldown circuit.                                                                                     |

| SCPDI                           | A5                                                       |                   |        | I                   | Serial Communications Port Data. Bond Pad connects to an internal pulldown circuit.                                               |

| SCPENZ                          | В7                                                       |                   |        | I                   | Active low serial communications port enable. Bond pad connects to an internal pulldown circuit.                                  |

| SCPDO                           | A9                                                       |                   |        | 0                   | Serial communications port output.                                                                                                |

| OTHER SIGNALS                   |                                                          |                   |        | !                   |                                                                                                                                   |

| EVCC                            | А3                                                       |                   |        | Р                   | Do Not Connect on the DLP system board.                                                                                           |

| MODE_A                          | A4                                                       | 415.1             |        | I                   | Data Bus Width Select. Bond Pad connects to an internal pull-down circuit, but for this DMD the PCB also ties this signal to GND. |

| PWRDNZ                          | В9                                                       | 110.38            |        | I                   | Active Low Device Reset. Bond Pad connects to an internal pull–down circuit.                                                      |

| POWER                           |                                                          |                   |        | 1                   | 1                                                                                                                                 |

| V <sub>CC</sub> <sup>(2)</sup>  | B11,<br>B12,<br>B13,<br>B16,<br>R12,<br>R13,<br>R16, R17 |                   |        | Р                   | Power supply for low voltage CMOS logic.<br>Power supply for normal high voltage at<br>micromirror address electrodes.            |

| V <sub>CCI</sub> <sup>(2)</sup> | A12,<br>A14,<br>A16,<br>T12,<br>T14, T16                 |                   |        | Р                   | Power supply for low voltage CMOS LVDS interface.                                                                                 |

| V <sub>CC2</sub> <sup>(2)</sup> | C1, D1,<br>M1, N1                                        |                   |        | Р                   | Power supply for high voltage CMOS logic.<br>Power supply for stepped high voltage at<br>micromirror address electrodes.          |

(2) Power supply pins required for all DMD operating modes are  $V_{SS}$ ,  $V_{CC}$ ,  $V_{CCI}$ ,  $V_{CC2}$ .

# Pin Functions (continued)

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |                                                                                                                                                                                                        | Pin Function |        | iniucu,             |                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|---------------------|--------------------------------------------|

| AB   AB   AB   AB   AB   AB   AB   AB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PIN                                     | NO                                                                                                                                                                                                     | NET LENGTH   | SIGNAL | TYPE <sup>(1)</sup> | DESCRIPTION                                |

| A13, A15, A17, B4, B6, B8, B15, B17, C2, C18, C19, F1, F2, F19, H1, H2, H3, H18, B18, B17, T2, H3, H18, B18, B19, B19, B17, C2, C18, C19, F1, F2, F19, H1, H2, H3, H18, B19, B19, R4, R9, R14, R15, T7, T13, T15, T17,   | NAME                                    |                                                                                                                                                                                                        | (IIIIIS)     |        |                     |                                            |

| RESERVED_FC         R7         40.64         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_FD         R8         94.37         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_PFE         T8         50.74         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_STM         B6         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_TP0         R10         93.3         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_TP0         R10         93.3         I         Do not connect on the DLP system board.           RESERVED_TP1         T11         263.74         I         Do not connect on the DLP system board.           RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | V <sub>SS</sub> (Ground) <sup>(3)</sup> | A13,<br>A15,<br>A17, B4,<br>B5, B8,<br>B14,<br>B15,<br>B17, C2,<br>C18,<br>C19, F1,<br>F2, F19,<br>H1, H2,<br>H3, H18,<br>J18, K1,<br>K2, L19,<br>N2, P18,<br>P19, R4,<br>R9, R14,<br>R15, T7,<br>T13, |              |        | Р                   | Common Return for all power.               |

| RESERVED_FD R8 94.37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RESERVED SIGNALS                        | 1                                                                                                                                                                                                      |              | l      |                     |                                            |

| RESERVED_FF         R8         94.37         I         Bond Pad connects to an internal pull-down circuit.           RESERVED_FFE         T8         50.74         I         Connect to ground on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_STM         B6         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_TP0         R10         93.3         I         Do not connect on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_TP1         T11         263.74         I         Do not connect on the DLP system board.           RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_TS         B10         145.42         O         Do not connect on the DLP system board.           RESERVED_A(1)         T3         T4         NC         Do not connect on the DLP system board.           RESERVED_A(2)         R3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RESERVED_FC                             | R7                                                                                                                                                                                                     | 40.64        |        | ı                   | Bond Pad connects to an internal pull-down |

| RESERVED_PFE         T8         50.74         I         board. Bond Pad connects to an internal pull-down circuit.           RESERVED_STM         B6         I         Connect to GND on the DLP system board. Bond Pad connects to an internal pull-down circuit.           RESERVED_TP0         R10         93.3         I         Do not connect on the DLP system board.           RESERVED_TP1         T11         263.74         I         Do not connect on the DLP system board.           RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RA1         T9         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_A(0)         T2         RESERVED_A(1)         T3           RESERVED_A(2)         R3         RESERVED_A(2)         R3           RESERVED_M(0)         R2         NC         Do not connect on the DLP system board.           RESERVED_S(0)         T1         NC         Do not connect on the DLP system board. <td>RESERVED_FD</td> <td>R8</td> <td>94.37</td> <td></td> <td>I</td> <td>Bond Pad connects to an internal pull-down</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RESERVED_FD                             | R8                                                                                                                                                                                                     | 94.37        |        | I                   | Bond Pad connects to an internal pull-down |

| RESERVED_STM         B6         I         Bond Pad connects to an internal pull-down circuit.           RESERVED_TPO         R10         93.3         I         Do not connect on the DLP system board.           RESERVED_TP1         T11         263.74         I         Do not connect on the DLP system board.           RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RA1         T9         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_A(0)         T2         T2 <td< td=""><td>RESERVED_PFE</td><td>Т8</td><td>50.74</td><td></td><td>I</td><td>board. Bond Pad connects to an internal</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RESERVED_PFE                            | Т8                                                                                                                                                                                                     | 50.74        |        | I                   | board. Bond Pad connects to an internal    |

| RESERVED_TP1         T11         263.74         I         Do not connect on the DLP system board.           RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RA1         T9         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_TS         B10         145.42         O         Do not connect on the DLP system board.           RESERVED_A(0)         T2         RESERVED_A(1)         T3           RESERVED_A(2)         R3         RESERVED_A(2)         R3           RESERVED_A(3)         T4         NC         Do not connect on the DLP system board.           RESERVED_M(0)         R2         NC         Do not connect on the DLP system board.           RESERVED_S(0)         T1         NC         Do not connect on the DLP system board.           RESERVED_S(1)         R1         NC         Do not connect on the DLP system board.           RESERVED_IRQZ         T6         NC <td>RESERVED_STM</td> <td>В6</td> <td></td> <td></td> <td>I</td> <td>Bond Pad connects to an internal pull-down</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RESERVED_STM                            | В6                                                                                                                                                                                                     |              |        | I                   | Bond Pad connects to an internal pull-down |

| RESERVED_TP2         R11         281.47         I         Do not connect on the DLP system board.           RESERVED_BA         T10         148.85         O         Do not connect on the DLP system board.           RESERVED_BB         A10         105.28         O         Do not connect on the DLP system board.           RESERVED_RA1         T9         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_TS         B10         145.42         O         Do not connect on the DLP system board.           RESERVED_A(0)         T2         T2         T2         T3         T4         T4 <td>RESERVED_TP0</td> <td>R10</td> <td>93.3</td> <td></td> <td>I</td> <td>Do not connect on the DLP system board.</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RESERVED_TP0                            | R10                                                                                                                                                                                                    | 93.3         |        | I                   | Do not connect on the DLP system board.    |

| RESERVED_BA RESERVED_BB A10 105.28 O Do not connect on the DLP system board.  RESERVED_RA1 T9 O Do not connect on the DLP system board.  RESERVED_RB1 A7 O Do not connect on the DLP system board.  RESERVED_TS B10 145.42 O Do not connect on the DLP system board.  RESERVED_A(0) T2 RESERVED_A(1) RESERVED_A(2) R3 RESERVED_A(3) T4 RESERVED_M(0) R2 RESERVED_M(0) R2 RESERVED_M(1) R1 RESERVED_S(0) R1 RESERVED_S(0) R1 RESERVED_S(0) R1 RESERVED_S(0) R1 R1 RESERVED_S(1) R2 RESERVED_IRQZ R5 R6 R6 R6 DO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RESERVED_TP1                            | T11                                                                                                                                                                                                    | 263.74       |        | I                   | Do not connect on the DLP system board.    |

| RESERVED_BB A10 105.28 O Do not connect on the DLP system board.  RESERVED_RA1 T9 O Do not connect on the DLP system board.  RESERVED_RB1 A7 O Do not connect on the DLP system board.  RESERVED_TS B10 145.42 O Do not connect on the DLP system board.  RESERVED_A(0) T2 RESERVED_A(1) T3 RESERVED_A(2) R3 RESERVED_A(3) T4 RESERVED_M(0) R2 NC Do not connect on the DLP system board.  RESERVED_M(1) P1 NC Do not connect on the DLP system board.  RESERVED_S(0) T1 NC Do not connect on the DLP system board.  RESERVED_S(1) R1 NC Do not connect on the DLP system board.  RESERVED_IRQZ T6 NC Do not connect on the DLP system board.  RESERVED_RSTZ R6 NC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RESERVED_TP2                            | R11                                                                                                                                                                                                    | 281.47       |        | -                   | Do not connect on the DLP system board.    |

| RESERVED_RA1         T9         O         Do not connect on the DLP system board.           RESERVED_RB1         A7         O         Do not connect on the DLP system board.           RESERVED_TS         B10         145.42         O         Do not connect on the DLP system board.           RESERVED_A(0)         T2         RESERVED_A(1)         T3           RESERVED_A(2)         R3         RESERVED_A(3)         T4           RESERVED_M(0)         R2         NC         Do not connect on the DLP system board.           RESERVED_M(1)         P1         NC         Do not connect on the DLP system board.           RESERVED_S(0)         T1         NC         Do not connect on the DLP system board.           RESERVED_S(1)         R1         NC         Do not connect on the DLP system board.           RESERVED_IRQZ         T6         NC         Do not connect on the DLP system board.           RESERVED_OEZ         R5         NC         Do not connect on the DLP system board.           RESERVED_RSTZ         R6         NC         Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         | T10                                                                                                                                                                                                    | 148.85       |        |                     | •                                          |

| RESERVED_RB1 A7 O Do not connect on the DLP system board.  RESERVED_A(0) T2 RESERVED_A(1) T3 RESERVED_A(2) R3 RESERVED_A(3) T4 RESERVED_M(0) R2 RESERVED_M(0) R2 RESERVED_S(0) T1 RESERVED_S(0) T1 RESERVED_S(1) R1 RESERVED_S(1) R1 RESERVED_S(1) R1 RESERVED_IRQZ RESERVED_IRQZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RD DO not connect on the DLP system board. RESERVED_S(0) Do not connect on the DLP system board. RESERVED_RSTZ  | _                                       |                                                                                                                                                                                                        | 105.28       |        |                     |                                            |

| RESERVED_A(0) RESERVED_A(1) RESERVED_A(2) RESERVED_A(2) RESERVED_A(3) RESERVED_M(0) RESERVED_M(0) RESERVED_M(1) RESERVED_S(0) RESERVED_S(0) RESERVED_S(0) RESERVED_S(1) RESERVED_S(1) RESERVED_IRQZ RESERVED_IRQZ RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_RESERVED_ |                                         |                                                                                                                                                                                                        |              |        | -                   |                                            |

| RESERVED_A(0) RESERVED_A(1) RESERVED_A(2) RESERVED_A(3) RESERVED_M(0) RESERVED_M(0) RESERVED_M(1) RESERVED_S(0) RESERVED_S(0) RESERVED_S(1) RESERVED_IRQZ RESERVED_IRQZ RESERVED_OEZ RESERVED_OEZ RESERVED_RSTZ RESE |                                         |                                                                                                                                                                                                        |              |        |                     | ·                                          |

| RESERVED_A(1) RESERVED_A(2) RESERVED_A(3) RESERVED_M(0) RESERVED_M(1) RESERVED_S(0) RESERVED_S(1) RESERVED_S(1) RESERVED_IRQZ RESERVED_IRQZ RESERVED_OEZ RESERVED_OEZ RESERVED_RSTZ RESE |                                         |                                                                                                                                                                                                        | 145.42       |        | 0                   | Do not connect on the DLP system board.    |

| RESERVED_A(2) RESERVED_A(3) RESERVED_M(0) RESERVED_M(1) RESERVED_S(0) RESERVED_S(1) RESERVED_IRQZ RESERVED_IRQZ RESERVED_OEZ RESERVED_OEZ RESERVED_RSTZ RESE | . ,                                     |                                                                                                                                                                                                        |              |        |                     |                                            |

| RESERVED_A(3)  RESERVED_M(0)  RESERVED_M(1)  RESERVED_S(0)  RESERVED_S(1)  RESERVED_IRQZ  RESERVED_IRQZ  RESERVED_OEZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_RSTZ  RESERVED_NC  RE |                                         |                                                                                                                                                                                                        |              |        | NC                  | Do not connect on the DLP system board.    |

| RESERVED_M(0) RESERVED_M(1) RESERVED_S(0) RESERVED_S(1) RESERVED_IRQZ RESERVED_OEZ RESERVED_OEZ RESERVED_OEZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_RSTZ RESERVED_NC Do not connect on the DLP system board. NC Do not connect on the DLP system board. NC Do not connect on the DLP system board. NC Do not connect on the DLP system board. NC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | · ·                                     |                                                                                                                                                                                                        |              |        |                     |                                            |

| RESERVED_M(1)  RESERVED_S(0)  T1  NC  Do not connect on the DLP system board.  NC  RESERVED_S(1)  R1  NC  Do not connect on the DLP system board.  NC  RESERVED_IRQZ  T6  NC  Do not connect on the DLP system board.  NC  RESERVED_OEZ  R5  NC  Do not connect on the DLP system board.  NC  RESERVED_RSTZ  R6  NC  Do not connect on the DLP system board.  NC  Do not connect on the DLP system board.  NC  Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ·                                       |                                                                                                                                                                                                        |              |        | NC                  | Do not connect on the DLD quotem heard     |

| RESERVED_S(0)  RESERVED_S(1)  RESERVED_IRQZ  RESERVED_OEZ  RESERVED_RSTZ  RSTZ  RSTZ |                                         |                                                                                                                                                                                                        |              |        |                     |                                            |

| RESERVED_S(1) R1 NC Do not connect on the DLP system board.  RESERVED_IRQZ T6 NC Do not connect on the DLP system board.  RESERVED_OEZ R5 NC Do not connect on the DLP system board.  RESERVED_RSTZ R6 NC Do not connect on the DLP system board.  RC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . ,                                     |                                                                                                                                                                                                        |              |        |                     | ·                                          |

| RESERVED_IRQZ T6 NC Do not connect on the DLP system board.  RESERVED_OEZ R5 NC Do not connect on the DLP system board.  RESERVED_RSTZ R6 NC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . ,                                     |                                                                                                                                                                                                        |              |        |                     | ·                                          |

| RESERVED_OEZ R5 NC Do not connect on the DLP system board. RESERVED_RSTZ R6 NC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | · ·                                     |                                                                                                                                                                                                        |              |        |                     | ·                                          |

| RESERVED_RSTZ R6 NC Do not connect on the DLP system board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |                                                                                                                                                                                                        |              |        |                     | ·                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                                                        |              |        |                     | ·                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                                                                                                                                                                                                        |              |        |                     |                                            |

<sup>(3)</sup>  $V_{SS}$  must be connected for proper DMD operation.

# Pin Functions (continued)

| PIN          |                   | NET LENGTH | SIGNAL | TYPE <sup>(1)</sup> | DESCRIPTION                             |

|--------------|-------------------|------------|--------|---------------------|-----------------------------------------|

| NAME         | NO.               | (mils)     | SIGNAL | I TPE\/             | DESCRIPTION                             |

| RESERVED_STR | T5                |            |        | NC                  | Do not connect on the DLP system board. |

| RESERVED_VB  | E3, F3,<br>K3, L3 |            |        | NC                  | Do not connect on the DLP system board. |

| RESERVED_VR  | B2, B3,<br>P2, P3 |            |        | NC                  | Do not connect on the DLP system board. |

# **STRUMENTS**

## **Specifications**

#### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). (1)

|                                    |                                                                                                    | MIN  | MAX                   | UNIT |

|------------------------------------|----------------------------------------------------------------------------------------------------|------|-----------------------|------|

| SUPPLY VOLTAGES                    |                                                                                                    |      |                       |      |