# DDS39RF10 and DDS39RFS10, 10.24GSPS to 20.48GSPS Dual and Single Channel, Multi-Nyquist Direct Digital Synthesizer (DDS)

#### 1 Features

- 16-bit, 10.24 to 20.48GSPS, multi-Nyquist DAC

- Maximum input data rate:

- 16-bit, single channel complex I/Q: 775MSPS

- 16-bit, dual channel complex I/Q: 388MSPS

- Output bandwidth (-3dB): 12GHz

- Performance at f<sub>OUT</sub> = 2.997GHz, DES2XL mode, DEM/Dither off

- Noise floor (small signal): -153dBFS/Hz

- SFDR (-0.1dBFS): 76dBc

- IMD3 (-7dBFS each tone): -71dBc

- Additive phase noise, 10kHz offset: -138dBc/Hz

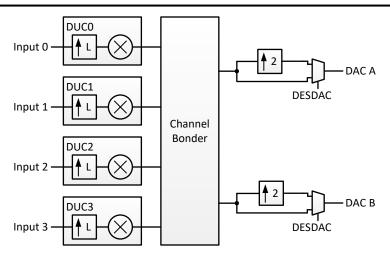

- Four Integrated digital up-converters (DUC)

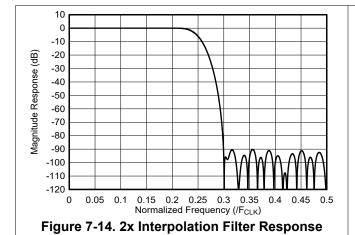

- Interpolation: 4x, 6x, 8x, 12x ... 256x

- Complex baseband DUC for I/Q output

- Complex to real up conversion for dual channel direct RF sampling

- 64-bit frequency resolution NCOs

- Fast reconfiguration interface for fast frequency hopping

- 4-bit data with 200MHz clock

- 60ns reconfiguration (32-bit frequency)

- Any frequency hopping with phase coherence

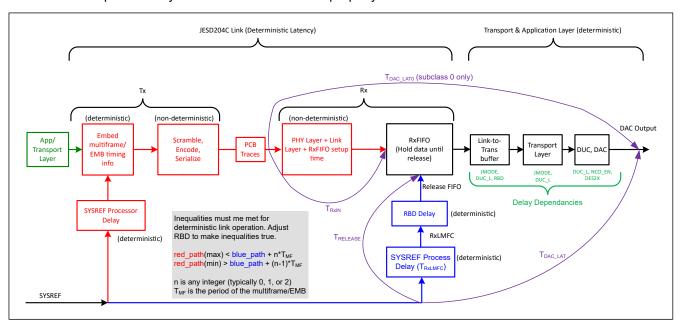

- JESD204C Interface

- Up to 2 Lanes at up to 12.8Gbps

- Class C-S, subclass-1 Compatible

- Internal AC coupling capacitors

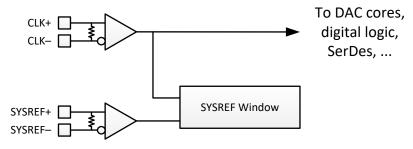

- SYSREF Windowing for automatic SYSREF timing calibration

# 2 Applications

- Satellite communications (SATCOM)

- Phased array antenna systems

- Synthetic aperture radar (SAR) exciter

- Wireless communications testers

- Arbitrary waveform generator (AWG)

- Agile, low phase noise LO generation

#### 3 Description

DDS39RF10 and 'RFS10 are a family of dual and single channel direct digital synthesizers with 16-bit resolution digital-to-analog converters (DAC). The high sampling rate, output frequency range, 64-bit NCO frequency resolution and any frequency hopping with phase coherence makes the device capable of arbitrary waveform generation (AWG) and direct digital synthesis (DDS).

The devices can also be used as interpolating DACs for narrowband direct RF sampling or complex baseband signal generation. The maximum input data rate is 775MSPS for a single channel or 388MSPS for two channels. The devices can generate signals of up to 620MHz signal bandwidth (16-bit input resolution) at carrier frequencies exceeding 10GHz enabling direct sampling through C-band and into X-band.

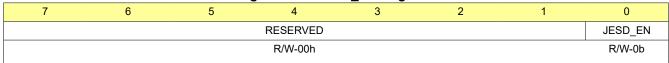

A JESD204B and JESD204C compatible serial interface has 2 receiver pairs capable of up to 12.8Gbps each. The interface is JESD204B and JESD204C subclass-1 compliant for deterministic latency and multi-device synchronization through the use of SYSREF.

#### **Package Information**

| PART NUMBER             | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------------------|------------------------|-----------------------------|

| DDS39RF10<br>DDS39RFS10 | FCBGA (256)            | 17mm x 17mm,<br>1mm pitch   |

- For more information, see Section 11.

- The package size (length × width) is a nominal value and (2) includes pins, where applicable.

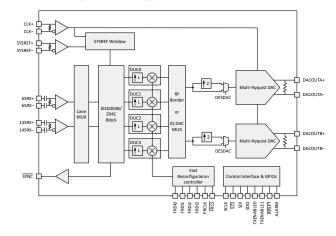

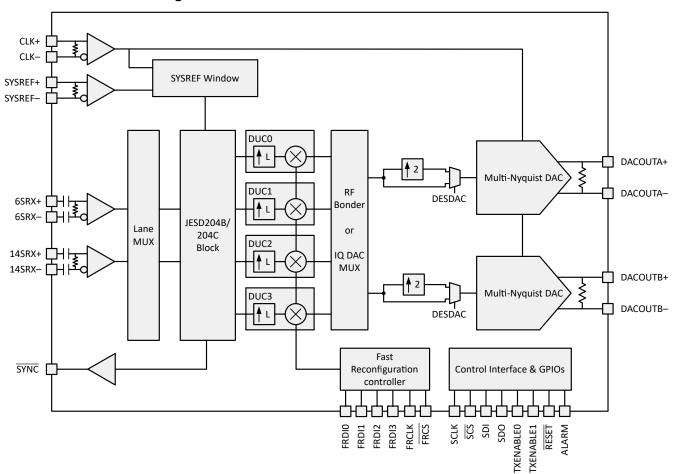

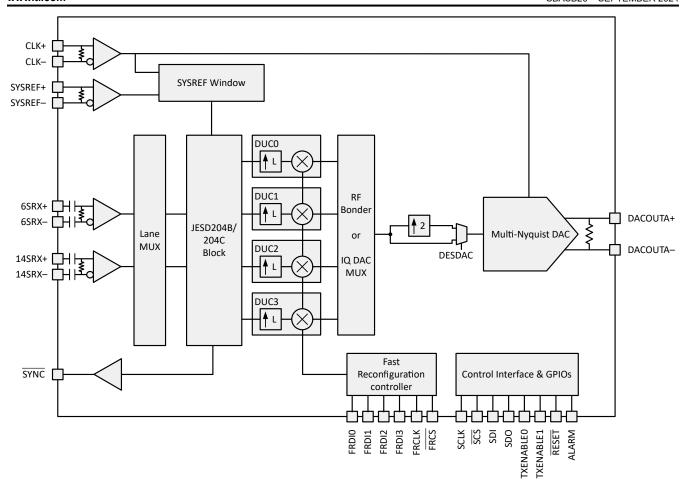

**Block Diagram (Dual Channel Devices)**

# **Table of Contents**

| 1 Features1                                           | 7 Detailed Description4                                |

|-------------------------------------------------------|--------------------------------------------------------|

| 2 Applications1                                       | 7.1 Overview4                                          |

| 3 Description1                                        | 7.2 Functional Block Diagrams4                         |

| 4 Device Comparison2                                  | 7.3 Feature Description4                               |

| 5 Pin Configuration and Functions3                    | 7.4 Device Functional Modes7                           |

| 6 Specifications7                                     | 7.5 Programming7                                       |

| 6.1 Absolute Maximum Ratings7                         | 8 Application and Implementation13                     |

| 6.2 ESD Ratings                                       | 8.1 Application Information                            |

| 6.3 Recommended Operating Conditions8                 | 8.2 Typical Application14                              |

| 6.4 Thermal Information8                              | 8.3 Power Supply Recommendations15                     |

| 6.5 Electrical Characteristics - DC Specifications9   | 8.4 Layout                                             |

| 6.6 Electrical Characteristics - AC Specifications 11 | 9 Device and Documentation Support16                   |

| 6.7 Electrical Characteristics - Power Consumption23  | 9.1 Receiving Notification of Documentation Updates 16 |

| 6.8 Timing Requirements26                             | 9.2 Support Resources16                                |

| 6.9 Switching Characteristics27                       | 9.3 Trademarks16                                       |

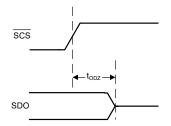

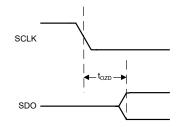

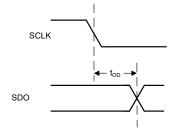

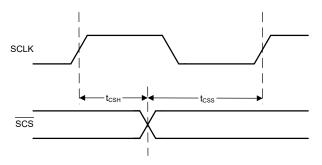

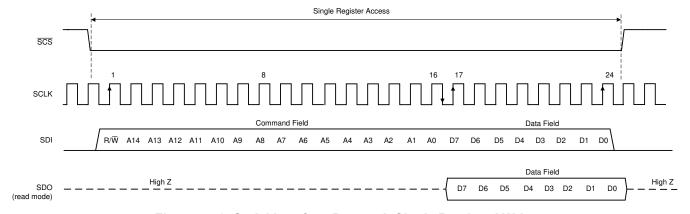

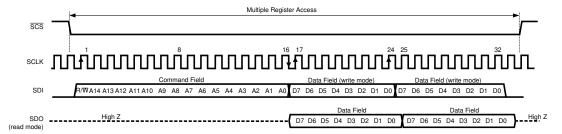

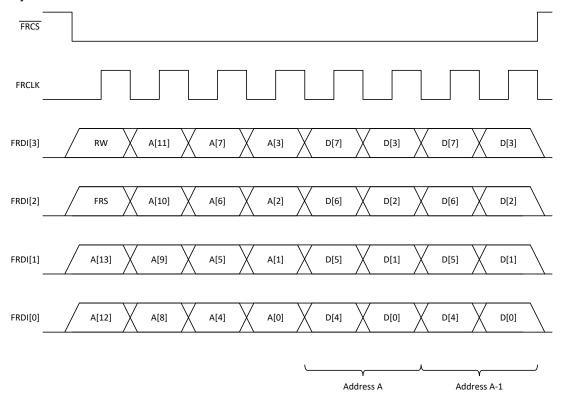

| 6.10 SPI and FRI Timing Diagrams29                    | 9.4 Electrostatic Discharge Caution16                  |

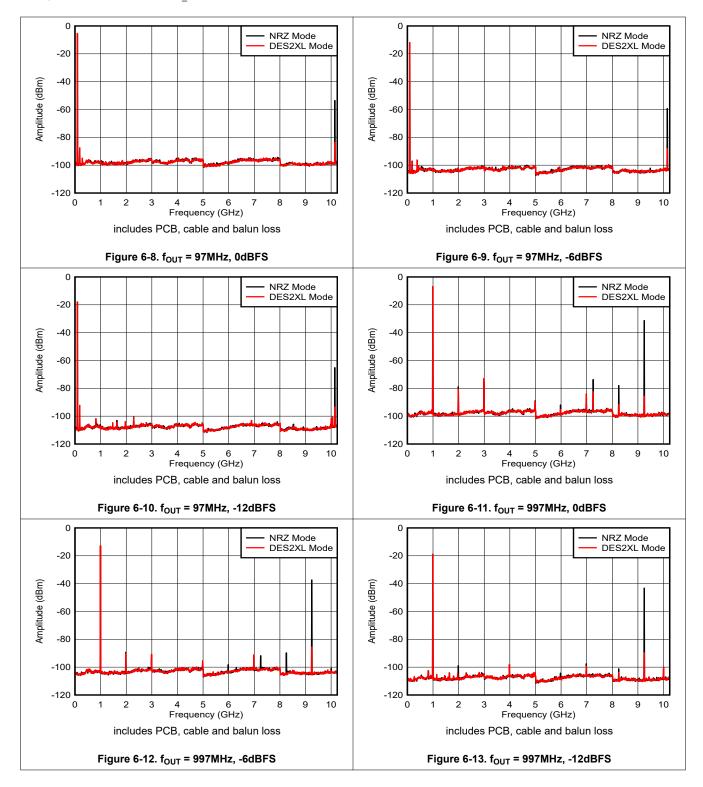

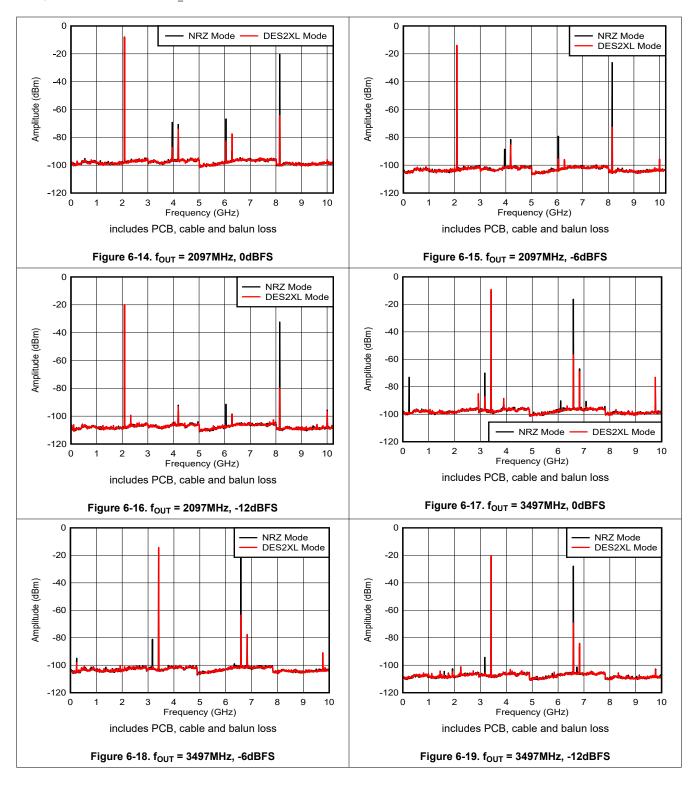

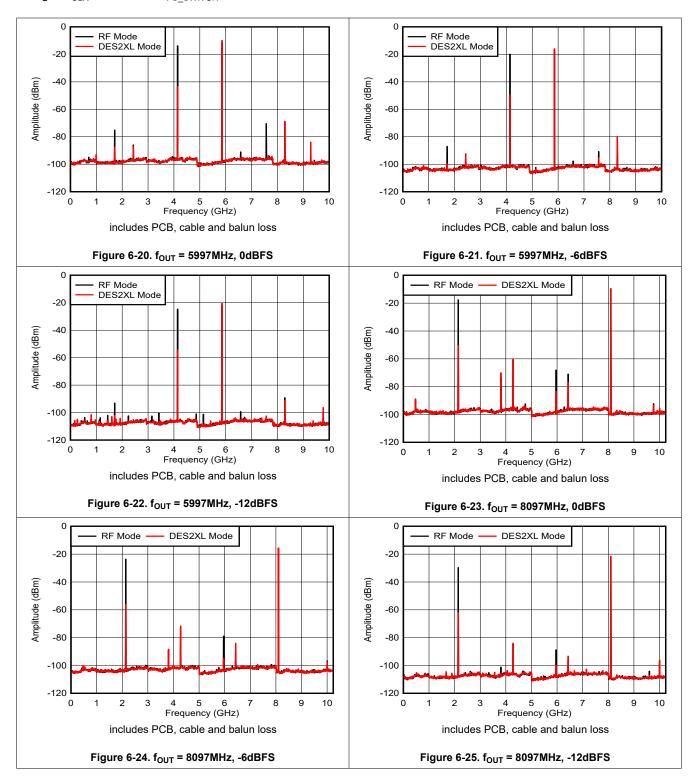

| 6.11 Typical Characteristics: Single Tone Spectra31   | 9.5 Glossary16                                         |

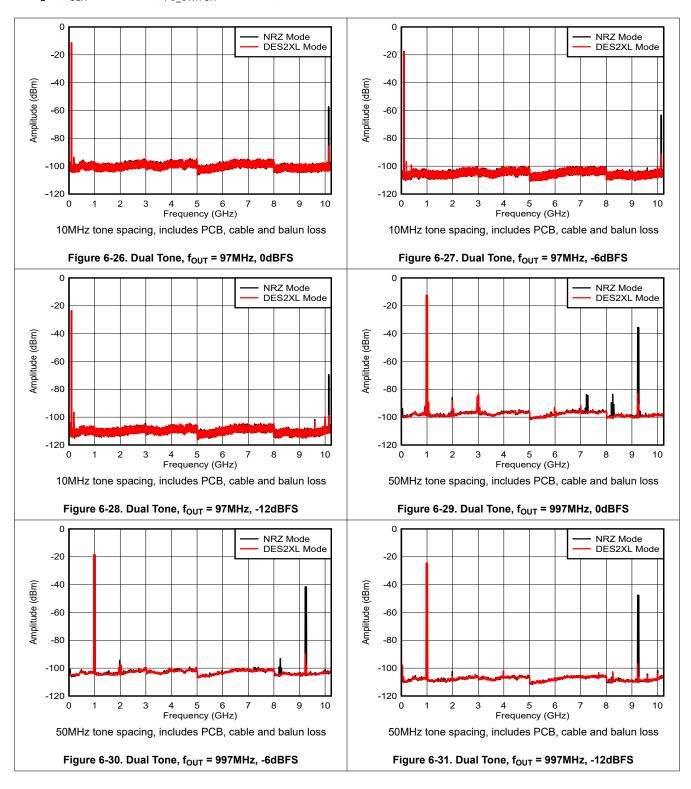

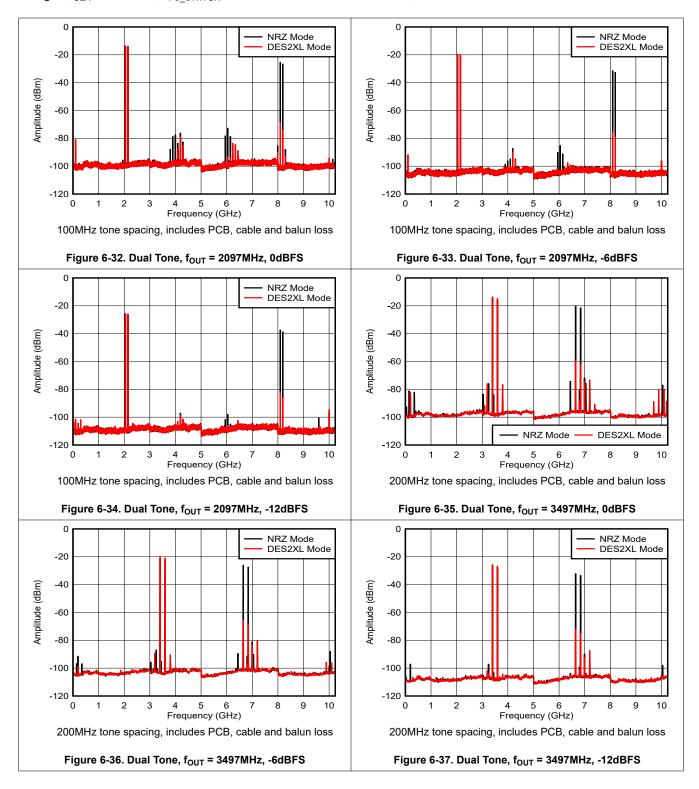

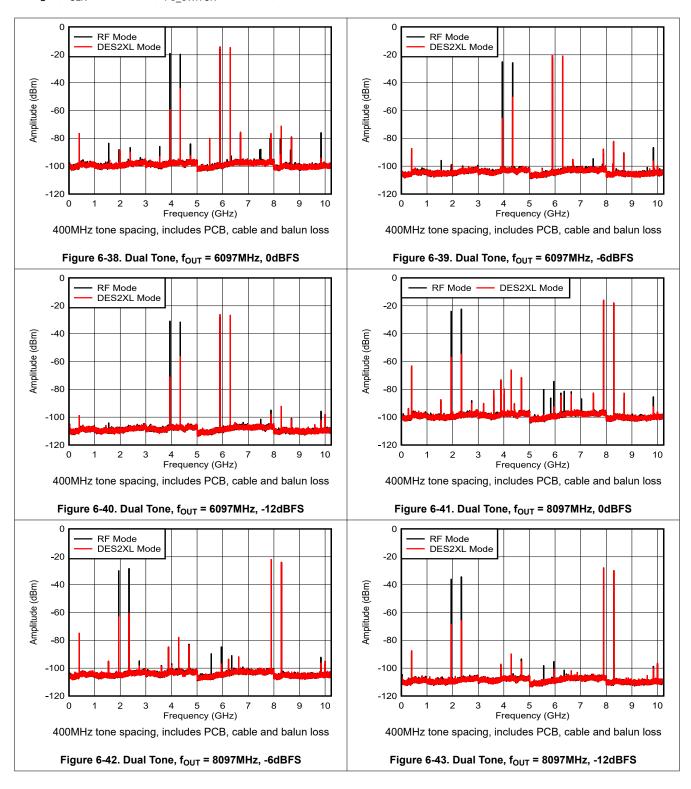

| 6.12 Typical Characteristics: Dual Tone Spectra34     | 10 Revision History16                                  |

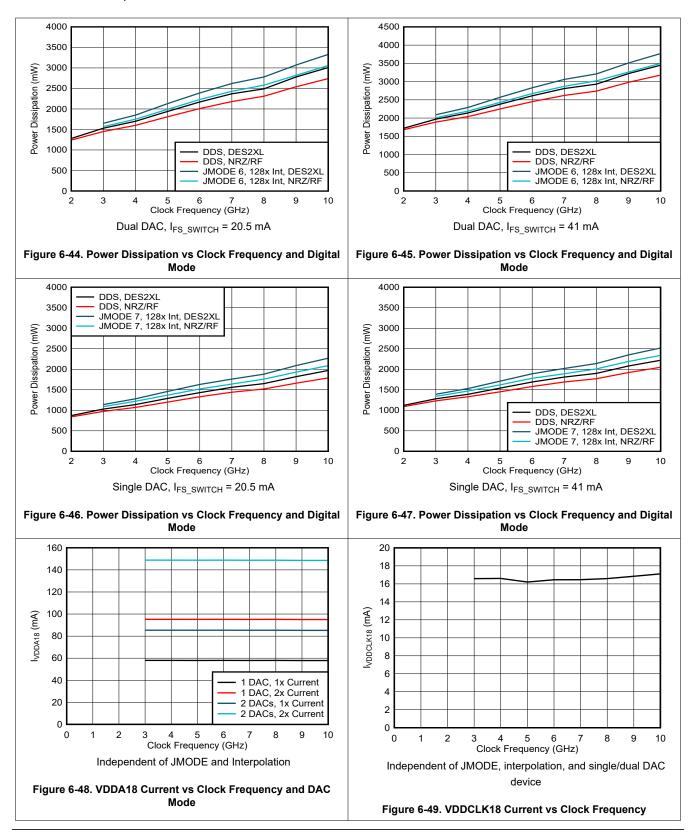

| 6.13 Typical Characteristics: Power Dissipation and   | 11 Mechanical, Packaging, and Orderable                |

| Supply Currents37                                     | Information16                                          |

|                                                       |                                                        |

# **4 Device Comparison**

| Davi Numbar    | ber # Channels Maximum Sample Rate |                     | Radiation | IEOD Interfere |                    |

|----------------|------------------------------------|---------------------|-----------|----------------|--------------------|

| Part Number    | # Channels                         | (Single, Dual Edge) | SEL/SEFI  | TID            | JESD Interface     |

| DAC39RF10      | 2                                  | 10.24, 20.48GSPS    | NA        | NA             | Yes                |

| DAC39RFS10     | 1                                  | 10.24, 20.48GSPS    | NA        | NA             | Yes                |

| DAC39RF12      | 2                                  | 12, 24GSPS          | NA        | NA             | Yes                |

| DAC39RFS12     | 1                                  | 12, 24GSPS          | NA        | NA             | Yes                |

| DAC39RF10-EP   | 2                                  | 10.4, 20.8GSPS      | NA        | NA             | Yes                |

| DAC39RFS10-EP  | 1                                  | 10.4, 20.8GSPS      | NA        | NA             | Yes                |

| DAC39RF10-SP   | 2                                  | 10.4, 20.8GSPS      | 120MeV    | 300krad        | Yes                |

| DAC39RFS10-SP  | 1                                  | 10.4, 20.8GSPS      | 120MeV    | 300krad        | Yes                |

| DAC39RF10-SEP  | 2                                  | 10.4, 20.8GSPS      | 43MeV     | 30krad         | Yes                |

| DAC39RFS10-SEP | 1                                  | 10.4, 20.8GSPS      | 43MeV     | 30krad         | Yes                |

| DDS39RF12      | 2                                  | 12, 24GSPS          | NA        | NA             | 2 lanes only       |

| DDS39RFS12     | 1                                  | 12, 24GSPS          | NA        | NA             | 2 lanes only       |

| DDS39RF10      | 2                                  | 10.24, 20.48GSPS    | NA        | NA             | 2 lanes only       |

| DDS39RFS10     | 1                                  | 10.24, 20.48GSPS    | NA        | NA             | 2 lanes only       |

| DAC39RF10EF    | 2                                  | 10.24, 20.48GSPS    | NA        | NA             | Input rate limited |

| DAC39RFS10EF   | 1                                  | 10.24, 20.48GSPS    | NA        | NA             | Input rate limited |

# 5 Pin Configuration and Functions

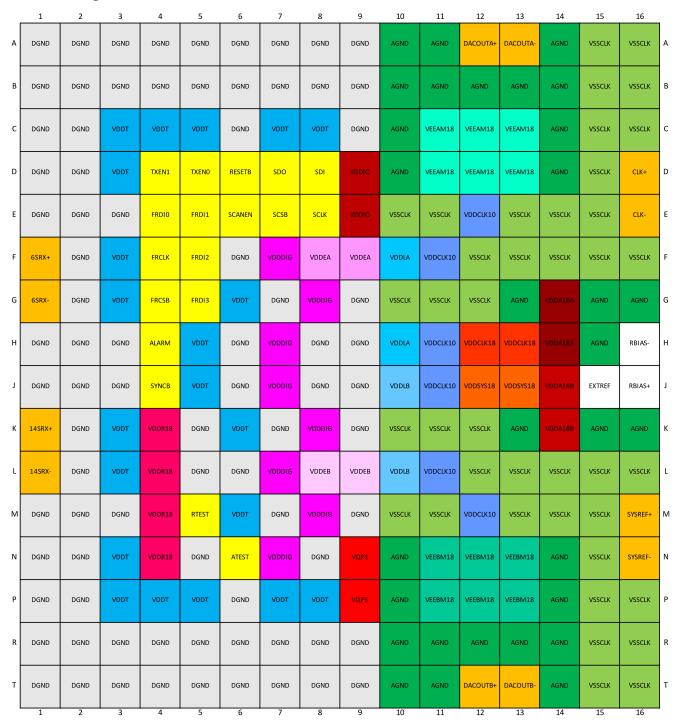

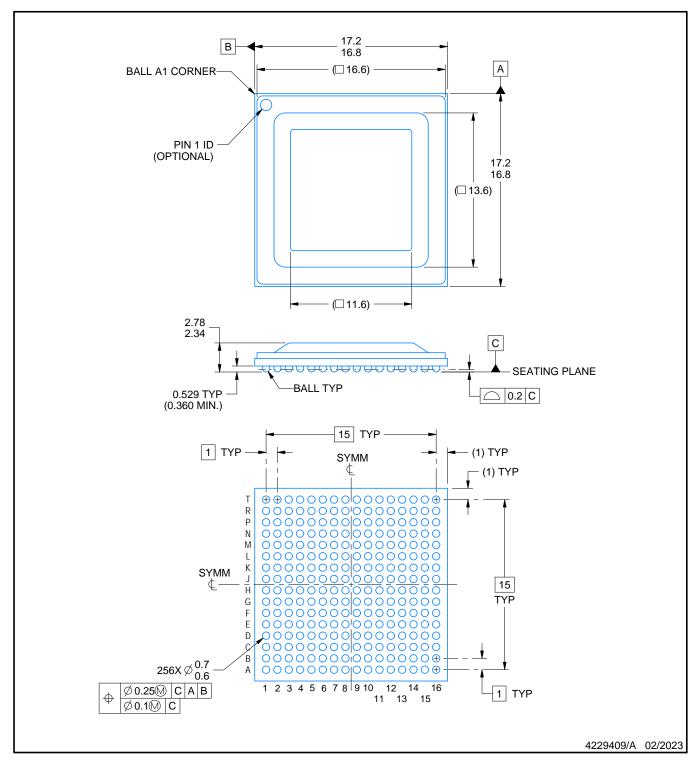

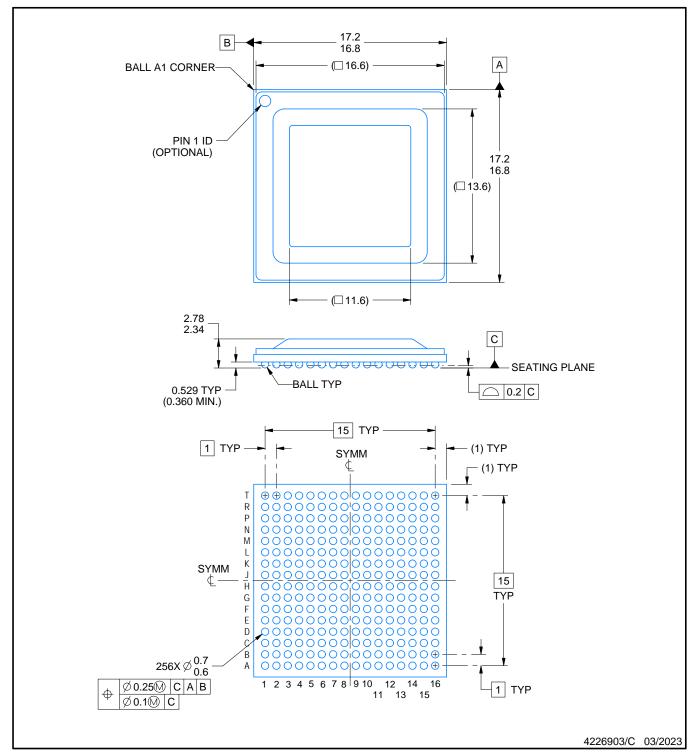

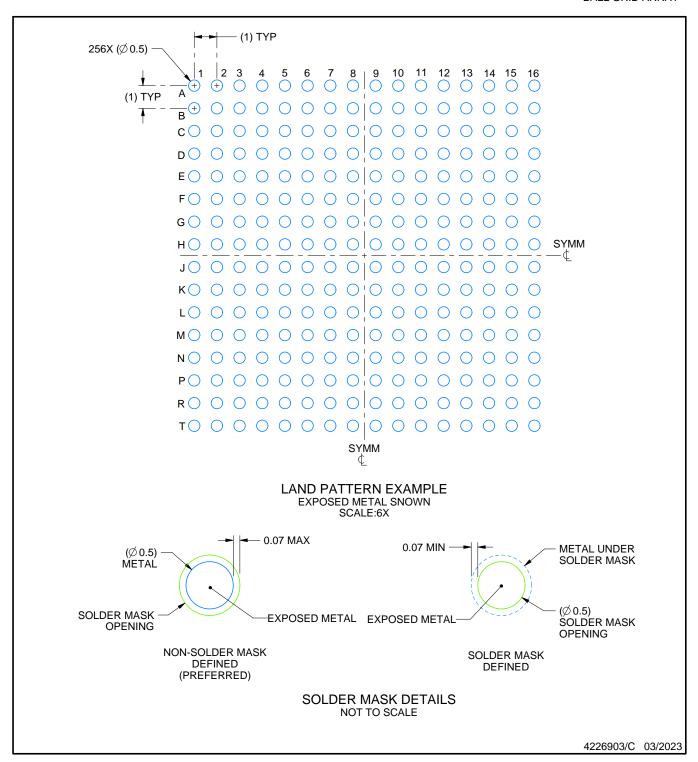

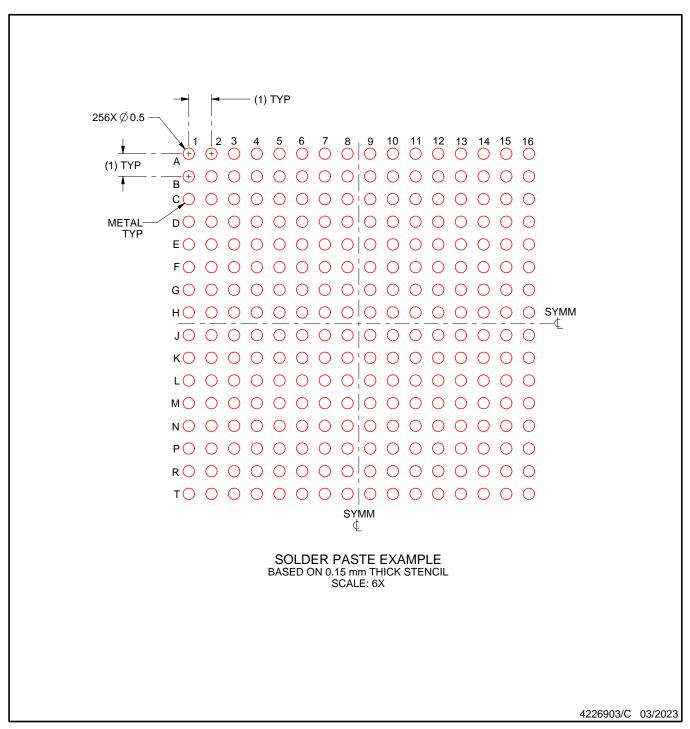

Figure 5-1. FCBGA Package, 256-Ball Flip Chip BGA with 1mm pitch (Top View)

# **Table 5-1. Pin Functions**

|                  | PIN             |       | Table 5-1. Fill FullCuons                                                                                                                                                                      |

|------------------|-----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             | NO.             | TYPE  | DESCRIPTION                                                                                                                                                                                    |

| DAC Outputs      |                 |       |                                                                                                                                                                                                |

| DACOUTA-         | A13             | 0     | DAC channel A analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                       |

| DACOUTA+         | A12             | 0     | DAC channel A analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                       |

| DACOUTB-         | T13             | 0     | DAC channel B analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. <i>Not available in single channel devices</i> .      |

| DACOUTB+         | T12             | 0     | DAC channel B analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance. <i>Not available in single channel devices</i> .      |

| Differential Clo | ck and SYSREF I | nputs |                                                                                                                                                                                                |

| CLK-             | E16             | 1     | Device clock input negative terminal. There is an internal $100\Omega$ differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source. |

| CLK+             | D16             | 1     | Device clock input positive terminal. There is an internal $100\Omega$ differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source. |

| SYSREF-          | N16             | 1     | Differential JESD204C SYSREF input negative terminal. There is an internal $100\Omega$ differential termination between SYSREF+ and SYSREF                                                     |

| SYSREF+          | M16             | ı     | Differential JESD204C SYSREF input negative terminal. There is an internal $100\Omega$ differential termination between SYSREF+ and SYSREF                                                     |

| SerDes Interfa   | ce              |       |                                                                                                                                                                                                |

| 6SRX-            | G1              | ı     | Serdes Lane 6 negative input. Includes in package AC-coupling series capacitor and $100\Omega$ internal termination to 6SRX+.                                                                  |

| 6SRX+            | F1              | ı     | Serdes Lane 6 positive input. Includes in package AC-coupling series capacitor and $100\Omega$ internal termination to 6SRX                                                                    |

| 14SRX-           | L1              | ı     | Serdes Lane 14 negative input. Includes in package AC-coupling series capacitor and $100\Omega$ internal termination to 14SRX+.                                                                |

| 14SRX+           | K1              | I     | Serdes Lane 14 positive input. Includes in package AC-coupling series capacitor and $100\Omega$ internal termination to 14SRX                                                                  |

| GPIO Function    | s               |       |                                                                                                                                                                                                |

| ALARM            | H4              | 0     | ALARM pin is asserted when an internal unmasked alarm is detected. Alarm mask is set by ALM_MASK register.                                                                                     |

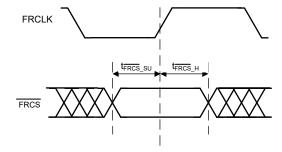

| FRCLK            | F4              | I     | Fast reconfiguration interface clock.                                                                                                                                                          |

| FRCS             | G4              | I     | Fast reconfiguration interface chip select. Internal pullup.                                                                                                                                   |

| FRDI0            | E4              | I     | Fast reconfiguration interface data bit 0.                                                                                                                                                     |

| FRDI1            | E5              | I     | Fast reconfiguration interface data bit 1.                                                                                                                                                     |

| FRDI2            | F5              | I     | Fast reconfiguration interface data bit 2.                                                                                                                                                     |

| FRDI3            | G5              | I     | Fast reconfiguration interface data bit 3.                                                                                                                                                     |

| RESET            | D6              | I     | Device reset input, active low. Must be toggled after power up. Internal pullup.                                                                                                               |

| SCANEN           | E6              | I     | TI use only, can be left unconnected. Internal pulldown.                                                                                                                                       |

| SCLK             | E8              | I     | Serial programming interface (SPI) clock input.                                                                                                                                                |

| SCS              | E7              | I     | Serial programming interface (SPI) device select input, active low. Internal pullup.                                                                                                           |

| SDI              | D8              | ı     | Serial programming interface (SPI) data input.                                                                                                                                                 |

| SDO              | D7              | 0     | Serial programming interface (SPI) data output. High impedance when not reading out SPI data.                                                                                                  |

| SYNC             | J4              | 0     | JESD204C SYNC output, active low.                                                                                                                                                              |

#### Table 5-1. Pin Functions (continued)

| PIN             |                                                                            | TVDE | DECORPTION .                                                                                                                                                                                                                                                                                                |  |  |

|-----------------|----------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NO.                                                                        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                 |  |  |

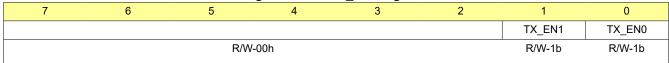

| TXEN0           | D5                                                                         | I    | Transmit enable for channel A active high input. This pin must be enabled using register USE_TX_EN0. The DAC output is forced to midcode (0x0000 in 2's complement) when transmission is disabled. Internal pullup.                                                                                         |  |  |

| TXEN1           | D4                                                                         | I    | Transmit enable for channel B active high input. This pin must be enabled using register USE_TX_EN1. The DAC output is forced to midcode (0x0000 in 2's complement) when transmission is disabled. Internal pullup.                                                                                         |  |  |

| Analog function | าร                                                                         |      |                                                                                                                                                                                                                                                                                                             |  |  |

| ATEST           | N6                                                                         | 0    | Analog test pin for TI use. Should be left disconnected.                                                                                                                                                                                                                                                    |  |  |

| EXTREF          | J15                                                                        | I/O  | Reference voltage output or input, determined by the EXTREF_EN register field. If the internal reference is used, the ball should be tied through 0.1uF to AGND.                                                                                                                                            |  |  |

| RBIAS-          | H16                                                                        | 0    | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS+.                                                                                                                                                                                                                    |  |  |

| RBIAS+          | J16                                                                        | 0    | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS                                                                                                                                                                                                                      |  |  |

| RTEST           | M5                                                                         | 0    | TI use only. Tie to AGND.                                                                                                                                                                                                                                                                                   |  |  |

| Power Supplies  | S                                                                          |      |                                                                                                                                                                                                                                                                                                             |  |  |

| VDDA18A         | G14 H14                                                                    | I    | 1.8V supply voltage for DAC channel A. Can be combined with VDDA18B, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                  |  |  |

| VDDA18B         | J14 K14                                                                    | 1    | 1.8V supply voltage for DAC channel B. Can be combined with VDDA18A, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                                                  |  |  |

| VDDCLK10        | F11 H11 J11 L11<br>E12 M12                                                 | 1    | 1V supply voltage for internal sampling clock distribution path. Noise or spurs on this s may degrade phase noise performance. Recommended to separate from VDDDIG and VDDA for best performance.                                                                                                           |  |  |

| VDDCLK18        | H12 H13                                                                    | 1    | 1.8V supply voltage for clock (CLK+/–) input buffer. Noise or spurs on this supply may degrade phase noise performance.                                                                                                                                                                                     |  |  |

| VDDDIG          | F7 H7 J7 L7 N7<br>G8 K8 M8                                                 | I    | 1V supply voltage for digital block. Recommended to separate from VDDA and VDDCLK for best performance.                                                                                                                                                                                                     |  |  |

| VDDEA           | F8 F9                                                                      | ı    | 1V supply voltage for channel A DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEB.                                                                                                                                                                          |  |  |

| VDDEB           | L8 L9                                                                      | I    | 1V supply voltage for channel B DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEA.                                                                                                                                                                          |  |  |

| VDDIO           | D9 E9                                                                      | I    | 1.8V supply for CMOS input and output terminals.                                                                                                                                                                                                                                                            |  |  |

| VDDLA           | F10 H10                                                                    | I    | 1V supply for DAC analog latch for channel A. Separate from VDDLB for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                        |  |  |

| VDDLB           | J10 L10                                                                    | ı    | 1V supply for DAC analog latch for channel B. Separate from VDDLA for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                        |  |  |

| VDDR18          | K4 L4 M4 N4                                                                | ļ    | 1.8V Supply voltage for SerDes receivers.                                                                                                                                                                                                                                                                   |  |  |

| VDDSYS18        | J12 J13                                                                    | I    | 1.8V supply voltage for SYSREF (SYSREF+/–) input buffer. Can be combined with VDDCLK18 when SYSREF is disabled during normal operation. This supply should be separate from VDDCLK18 when SYSREF is run continuously during operation to avoid noise and spur coupling and reduced phase noise performance. |  |  |

| VDDT            | C3 D3 F3 G3 K3<br>L3 N3 P3 C4 P4<br>C5 H5 J5 P5 G6<br>K6 M6 C7 P7 C8<br>P8 | I    | 1V Supply voltage for SerDes termination.                                                                                                                                                                                                                                                                   |  |  |

| VEEAM18         | C11 D11 C12 D12<br>C13 D13                                                 | I    | -1.8V supply voltage for DAC current source bias for channel A. Can be combined with VEEBM18, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                         |  |  |

| VEEBM18         | N11 P11 N12 P12<br>N13 P13                                                 | I    | -1.8V supply voltage for DAC current source bias for channel B. Can be combined with VEEAM18, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                         |  |  |

| VQPS            | N9 P9                                                                      | I    | TI use only. Can be tied to DGND during normal operation.                                                                                                                                                                                                                                                   |  |  |

| Grounds         |                                                                            |      |                                                                                                                                                                                                                                                                                                             |  |  |

#### **Table 5-1. Pin Functions (continued)**

|        | PIN                                                                                                                                                                                                                                                |      | Properties      |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|

| NAME   | NO.                                                                                                                                                                                                                                                | TYPE | DESCRIPTION     |

| AGND   | A10 B10 C10 D10<br>N10 P10 R10<br>T10 A11 B11 R11<br>T11 B12 R12 B13<br>G13 K13 R13<br>A14 B14 C14 D14<br>N14 P14 R14 T14<br>G15 H15 K15<br>G16 K16                                                                                                | -    | Analog ground.  |

| DGND   | A1 B1 C1 D1 E1 H1 J1 M1 N1 P1 R1 T1 A2 B2 C2 D2 E2 F2 G2 H2 J2 K2 L2 M2 N2 P2 R2 T2 A3 B3 E3 H3 J3 M3 R3 T3 A4 B4 R4 T4 A5 B5 K5 L5 N5 R5 T5 A6 B6 C6 F6 H6 J6 L6 P6 R6 T6 A7 B7 G7 K7 M7 R7 T7 A8 B8 H8 J8 N8 R8 T8 A9 B9 C9 G9 H9 J9 K9 M9 R9 T9 | -    | Digital ground. |

| VSSCLK | E10 G10 K10<br>M10 E11 G11 K11<br>M11 F12 G12 K12<br>L12 E13 F13 L13<br>M13 E14 F14 L14<br>M14 A15 B15<br>C15 D15 E15 F15<br>L15 M15 N15 P15<br>R15 T15 A16 B16<br>C16 F16 L16 P16<br>R16 T16                                                      | -    | Clock ground.   |

# **6 Specifications**

#### **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER                                                                                                                                                                                                                                                                  | TEST CONDITIONS                                             | MIN  | MAX                                                                                                                                                                                  | UNIT |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

|                                                                                                                                                                                                                                                                            | Supply voltage range, VDDA18A, VDDA18B <sup>(2)</sup>       | -0.3 | 2.45                                                                                                                                                                                 | V    |  |

|                                                                                                                                                                                                                                                                            | Supply voltage range, VEEAM18, VEEBM18 <sup>(2)</sup>       | -2.0 | 0.3                                                                                                                                                                                  | V    |  |

|                                                                                                                                                                                                                                                                            | Supply voltage range, VDDCLK18, VDDSYS18 <sup>(3)</sup>     | -0.3 | 2.45                                                                                                                                                                                 | V    |  |

| Supply voltage range                                                                                                                                                                                                                                                       | Supply voltage range, VDDLB, VDDLA, VDDCLK10 <sup>(3)</sup> | -0.3 | 1.3                                                                                                                                                                                  | V    |  |

|                                                                                                                                                                                                                                                                            | Supply voltage range, VDDA18A, VDDA18B <sup>(2)</sup>       | V    |                                                                                                                                                                                      |      |  |

| upply voltage range  oltage between any combination of GND, DGND and VSSCLK  oltage applied to input pins  oltage at output pins  eak input current (any input)  eak total input current (sum of absort including power supply current a ACOUTB—)  unction temperature, TJ |                                                             | -0.3 | 1.3                                                                                                                                                                                  | V    |  |

| Voltage between any combination of AGND, DGND and VSSCLK                                                                                                                                                                                                                   |                                                             | -0.1 | 0.1                                                                                                                                                                                  | V    |  |

|                                                                                                                                                                                                                                                                            | 6SRX-/+, 14SRX-/+ AC Voltage 1.6                            |      |                                                                                                                                                                                      |      |  |

| Voltage applied to input pins                                                                                                                                                                                                                                              | 6SRX-/+, 14SRX-/+ AC Voltage                                |      | 1.6                                                                                                                                                                                  | V    |  |

|                                                                                                                                                                                                                                                                            | 6SRX-/+, 14SRX-/+ DC Voltage to GND                         | -5   | 5                                                                                                                                                                                    |      |  |

|                                                                                                                                                                                                                                                                            |                                                             | -0.3 | VDDIO+0.3                                                                                                                                                                            |      |  |

|                                                                                                                                                                                                                                                                            | EXTREF <sup>(2)</sup>                                       | -0.3 | 0.3 2.45 2.0 0.3 0.3 2.45 0.3 1.3 0.3 2.45 0.3 1.3 0.1 0.1 0.1 0.3 VDDCLK18+0.3 1.6 -5 5 0.3 VDDO+0.3 0.3 VDDA18A + 0.3 0.3 VDDA18B + 0.5 0.5 VDDA18B + 0.3 0.5 VDDIO+0.3 -20 20 30  |      |  |

|                                                                                                                                                                                                                                                                            | DACOUTA+, DACOUTA-(2)                                       | -0.3 | 0.3 2.45 1.3 2.45 1.3 0.1 VDDCLK18+0.3 1.6 5 VDDIO+0.3 VDDA18A + 0.5 VDDA18B + 0.5 VDDA18B + 0.3 |      |  |

| /oltage at output pins                                                                                                                                                                                                                                                     | DACOUTB+, DACOUTB-(2)                                       | -0.3 | VDDA18B + 0.5                                                                                                                                                                        | V    |  |

| voltage at output pins                                                                                                                                                                                                                                                     | ATEST, RBIAS-/+ <sup>(2)</sup>                              | -0.5 | 1.6 -5 5 -0.3 VDDIO+0.3 -0.3 VDDA18A + 0.3 -0.3 VDDA18A + 0.5 -0.3 VDDA18B + 0.5 -0.5 VDDA18B + 0.3 -0.5 VDDIO + 0.3                                                                 | V    |  |

|                                                                                                                                                                                                                                                                            | SDI, SDO, ALARM <sup>(4)</sup>                              | -0.5 | VDDIO + 0.3                                                                                                                                                                          |      |  |

| Peak input current (any input)                                                                                                                                                                                                                                             |                                                             | -20  | 20                                                                                                                                                                                   | mA   |  |

| Peak total input current (sum of absolute value of all currents forced in or out, ot including power supply current and DACOUTA+, DACOUTA-, DACOUTB+ and DACOUTB-)                                                                                                         |                                                             | 30   | mA                                                                                                                                                                                   |      |  |

| Junction temperature, T <sub>J</sub>                                                                                                                                                                                                                                       |                                                             |      | 150                                                                                                                                                                                  | °C   |  |

| Storage temperature, T <sub>stg</sub>                                                                                                                                                                                                                                      |                                                             | -65  | 150                                                                                                                                                                                  | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                                            |                         |                                                                                     | VALUE | UNIT |

|--------------------------------------------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Electrostatio discharge | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | 1000  | V    |

|                                            | Electrostatic discharge | Charged device model (CDM), per ANSI/<br>ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | 250   | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> Measured to AGND.

<sup>(3)</sup> Measured to VSSCLK.

<sup>(4)</sup> Measured to DGND.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                   |                                         |                                                | MIN   | NOM  | MAX   | UNIT                  |

|-------------------|-----------------------------------------|------------------------------------------------|-------|------|-------|-----------------------|

|                   |                                         | VDDA18A, VDDA18B <sup>(1)</sup>                | 1.71  | 1.8  | 1.89  | V                     |

|                   |                                         | VEEAM18, VEEBM18 <sup>(1)</sup>                | -1.89 | -1.8 | -1.71 | V                     |

|                   |                                         | VDDCLK18, VDDSYS18, VDDR18 <sup>(2)</sup>      | 1.71  | 1.8  | 1.89  | V                     |

| Supply volta      | age range                               | VDDLB, VDDLA, VDDCLK10(2)                      | 0.95  | 1    | 1.05  | V                     |

|                   |                                         | VDDIO <sup>(3)</sup>                           | 1.71  | 1.8  | 1.89  | V                     |

|                   |                                         | VQPS <sup>(3)</sup>                            | 0     | 0    | 1.89  | V                     |

|                   |                                         | VDDDIG, VDDEB, VDDEA, VDDT(3)                  | 0.95  | 1    | 1.05  | V                     |

| V <sub>CMI</sub>  | Input common mode voltage               | CLK+, CLK-(2) (4)                              |       | 0.4  |       | V                     |

| V <sub>CMI</sub>  | Input common mode voltage               | SYSREF+, SYSREF-(2) (4)                        | 0     | 0.4  | 1.0   | V                     |

|                   |                                         | SYSREF+ to SYSREF-                             | 800   | 1000 | 2000  | mV <sub>PP-DIFF</sub> |

|                   | Input differential peak to peak voltage | CLK+ to CLK-, f <sub>CLK</sub> < 5GHz          | 800   | 1000 | 1400  | mV <sub>PP-DIFF</sub> |

| V <sub>ID</sub>   | Input differential peak-to-peak voltage | CLK+ to CLK-, 5GHz < f <sub>CLK</sub> < 7.5GHz | 800   | 1000 | 1800  | mV <sub>PP-DIFF</sub> |

|                   |                                         | CLK+ to CLK-, f <sub>CLK</sub> > 7.5GHz        | 800   | 1000 | 2000  | $mV_{PP\text{-DIFF}}$ |

| DC <sub>MIN</sub> | CLK+/- duty cycle minimum               |                                                |       | 45   |       | %                     |

| DC <sub>MAX</sub> | CLK+/– duty cycle maximum               | CLK+/– duty cycle maximum                      |       | 55   |       | %                     |

Measured to AGND. (1)

#### **6.4 Thermal Information**

|                       | THERMAL METRIC <sup>(1)</sup>                | 17mmx17mm FC-BGA | UNIT |

|-----------------------|----------------------------------------------|------------------|------|

|                       | THERMAL METRIC                               | 256 PINS         | UNIT |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 15.8             | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.9              | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.2              | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4              | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 4.2              | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: DDS39RF10 DDS39RFS10

<sup>(2)</sup> Measured to VSSCLK.

<sup>(3)</sup> Measured to DGND.

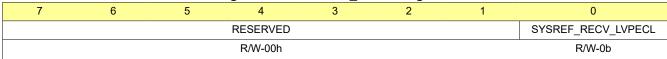

SYSREF+/- termination has two options. In option 1 the inputs are weakly self-biased to the optimal common mode voltage, which is appropriate for AC coupling. In option 2, each input terminal is connected through 500hms to ground, which is appropriate to level shift from a higher common mode voltage.

# 6.5 Electrical Characteristics - DC Specifications

Typical values at  $T_A$  = +25°C, minimum and maximum values over operating free-air temperature range, typical supply voltages, 2 channels, DDS Mode,  $F_{CLK}$  = 10.24 GHz,  $F_{OUT}$  = 2997 MHz, NRZ mode,  $I_{FSSWITCH}$  = 20.5 mA, unless otherwise noted.

|                         | PARAMETER                                                    | TEST CONDITIONS                                                                                                               | MIN                 | TYP MAX                | UNIT            |

|-------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-----------------|

| DC ACCURA               | ACY                                                          |                                                                                                                               |                     |                        |                 |

| BITS                    | DAC core resolution                                          |                                                                                                                               | 16                  |                        | bits            |

| DNL                     | Differential nonlinearity                                    |                                                                                                                               |                     | ±2.2                   | LSB             |

| INL                     | Integral nonlinearity                                        |                                                                                                                               |                     | ±9                     | LSB             |

| DAC ANALO               | OG OUTPUT (DACOUTA+, DACOUTA-,                               | DACOUTB+, DACOUTB-)                                                                                                           |                     |                        |                 |

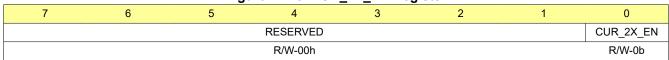

|                         |                                                              | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B= 0xF and FINE_CUR_A / FINE_CUR_B = default, CUR_2X_EN = 1  |                     | 41                     |                 |

|                         | Switched full people output averent                          | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B= 0xF and FINE_CUR_A / FINE_CUR_B = default                 |                     | 20.5                   | m A             |

| I <sub>FS_</sub> SWITCH | Switched full scale output current                           | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0x0 and FINE_CUR_A / FINE_CUR_B = default, CUR_2X_EN = 1 |                     | 11                     | mA              |

|                         |                                                              | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0x0 and FINE_CUR_A / FINE_CUR_B = default                |                     | 5.5                    |                 |

| I <sub>STATIC</sub>     | Static output current per pin                                | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = default                |                     | 4.8                    | mA              |

|                         |                                                              | 3.6-kΩ resistor from RBIAS+                                                                                                   | -8.6                |                        | uA/°C           |

| I <sub>FSDRIFT</sub>    | Full scale output current temperature drift                  | to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = default                                            |                     | -0.3                   | PPM/°C          |

| I <sub>FSERROR</sub>    | Full scale current error                                     | 3.6-kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = default                |                     | ±0.1                   | %               |

| I <sub>MIDOFFERR</sub>  | Mid Code Offset Error                                        | Mid Code offset                                                                                                               |                     | ±0.02                  | %FSR            |

| V <sub>COMP</sub>       | Output compliance voltage range                              | Measured from DACOUTA+,<br>DACOUTA-, DACOUTB+ or<br>DACOUTB- to AGND                                                          | VDDA18<br>A/B - 0.5 | VDDA18<br>A/B +<br>0.5 | V               |

| C <sub>OUT</sub>        | Output capacitance                                           | Single-ended capacitance to ground                                                                                            |                     | 0.25                   | pF              |

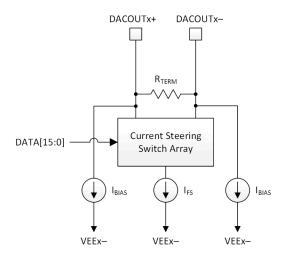

| R <sub>TERM</sub>       | Output differential termination resistance                   |                                                                                                                               |                     | 102                    | Ω               |

| R <sub>TERMDRIFT</sub>  | Output differential termination resistance temperature coeff |                                                                                                                               |                     | -9.6<br>-42            | mΩ/°C<br>PPM/°C |

| CLOCK AND               | O SYSREF INPUTS (CLK+, CLK-, SYSR                            | EF+, SYSREF-)                                                                                                                 |                     |                        |                 |

| R <sub>T</sub>          | Internal differential termination resistar                   | · · · · · · · · · · · · · · · · · · ·                                                                                         |                     | 100                    | Ω               |

| C <sub>IN</sub>         | Internal differential input capacitance                      |                                                                                                                               | +                   | 0.5                    | pF              |

# 6.5 Electrical Characteristics - DC Specifications (continued)

Typical values at  $T_A$  = +25°C, minimum and maximum values over operating free-air temperature range, typical supply voltages, 2 channels, DDS Mode,  $F_{CLK}$  = 10.24 GHz,  $F_{OUT}$  = 2997 MHz, NRZ mode,  $I_{FSSWITCH}$  = 20.5 mA, unless otherwise noted.

|                        | PARAMETER                                               | TEST CONDITIONS                                                                           | MIN                  | TYP MAX              | UNIT     |

|------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------|----------------------|----------|

| REFERENCI              | E VOLTAGE                                               |                                                                                           |                      |                      |          |

| V <sub>REF</sub>       | Reference output voltage                                |                                                                                           |                      | 0.9                  | V        |

| V <sub>REF-DRIFT</sub> | Absolute Value of Reference output vol                  | tage drift over temperature                                                               |                      | 45                   | ppm/°C   |

| I <sub>REF</sub>       | Maximum reference output current sou internal reference | aximum reference output current sourcing capability for EXTREF ball with ternal reference |                      |                      |          |

| JESD204C S             | SERDES INTERFACE ( 6SRX+/-, 14SRX                       | +/-)                                                                                      |                      |                      |          |

| V <sub>SRDIFF</sub>    | SerDes Receiver Input Amplitude                         |                                                                                           | 50                   | 1200                 | mVppdiff |

| V <sub>SRCOM</sub>     | SerDes Input Common Mode                                |                                                                                           | Interna              | I AC coupled         |          |

| Z <sub>SRdiff</sub>    | SerDes Internal Differential<br>Termination             |                                                                                           |                      | 100                  | Ω        |

| CMOS INTE              | RFACE (ALARM, SCLK, SCS, SDI, SDO                       | , RESET, FRDI[0:3], FRCLK, FRCS, SY                                                       | NC, TXENA            | BLE[0:1])            |          |

| I <sub>IH</sub>        | High level input current (with pulldowns)               | SCANEN <sup>(1)</sup>                                                                     |                      | 200                  | uA       |

| I <sub>IH</sub>        | High level input current (without pulldowns)            | SCS, RESET, FRCS,<br>TXEN[0:1], FRDI[0:3], FRCLK,<br>SDI, SCLK <sup>(1)</sup>             |                      | 2                    | uA       |

| I <sub>IL</sub>        | Low level input current (with pullups)                  | SCS, RESET, FRCS, TXEN[0:1] <sup>(1)</sup>                                                | -200                 |                      | uA       |

| I <sub>IL</sub>        | Low level input current (without pullups)               | SCANEN, FRDI[0:3], FRCLK, SDI, SCLK <sup>(1)</sup>                                        | -3                   |                      | uA       |

| Cı                     | Input capacitance                                       | Input capacitance                                                                         |                      | 3                    | pF       |

| V <sub>IH</sub>        | High level input voltage                                | SCLK, SCS, SDI, RESET, FRDI[0:3],                                                         | 0.7 x<br>VDDIO1<br>8 |                      | V        |

| V <sub>IL</sub>        | Low level input voltage                                 | FRCLK, FRCS, SCANEN, TXEN[0:1]                                                            |                      | 0.3 x<br>VDDIO1<br>8 | V        |

| V <sub>OH</sub>        | High level output voltage                               | ALARM, SDO, SYNC, I <sub>LOAD</sub> = -400 uA                                             | 1.55                 | -                    | V        |

| V <sub>OL</sub>        | Low level output voltage                                | ALARM, SDO, SYNC, I <sub>LOAD</sub> = 400 uA                                              |                      | 0.2                  | V        |

| TEMPERATI              | URE SENSOR                                              |                                                                                           |                      |                      | •        |

| Res                    | Resolution                                              |                                                                                           |                      | 1                    | °C/LSB   |

| Range                  | Digital Range                                           |                                                                                           | -50                  | 150                  | °C       |

| T <sub>ERROR</sub>     | Temperature Error                                       | TA = 25°C, device powered down except for temperature sensor and SPI interface            |                      | ±5                   | °C       |

<sup>(1)</sup> With no IO supply voltage offset in connecting device.

Submit Document Feedback

Copyright © 2025 Texas Instruments Incorporated

## 6.6 Electrical Characteristics - AC Specifications

|                       | PARAMETER                                                                                                                | TEST CONDITIONS                                                                                           | MIN | TYP   | MAX   | UNIT |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-------|-------|------|

| MODE INDEPE           | NDENT PARAMETERS                                                                                                         |                                                                                                           |     |       |       |      |

| F <sub>CLK</sub>      | DAC clock rate                                                                                                           |                                                                                                           | 0.8 |       | 10.24 | GHz  |

| BW                    | Analog output bandwidth (–3 dB)                                                                                          | Excluding sinx/x response. Useable bandwidth may exceed the –3 dB point. I <sub>FS_SWITCH</sub> = 20.5 mA |     | 12.15 |       | GHz  |

| DVV                   | Arialog output bandwidth (–3 db)                                                                                         | Excluding sinx/x response. Useable bandwidth may exceed the –3 dB point. I <sub>FS_SWITCH</sub> = 41 mA   |     | 11.95 |       | GHZ  |

|                       |                                                                                                                          | f <sub>OUT</sub> = 97 MHz, NRZ mode                                                                       |     | 101   |       | dBc  |

|                       | Isolation between channel A (DACOUTA+/–) and channel B (DACOUTB+/-), f <sub>OUT</sub> = -25 MHz offset on victim channel | f <sub>OUT</sub> = 1897 MHz, NRZ mode                                                                     |     | 97    |       | dBc  |

| Crosstalk             |                                                                                                                          | f <sub>OUT</sub> = 3897 MHz, NRZ mode                                                                     |     | 91    |       | dBc  |

|                       |                                                                                                                          | f <sub>OUT</sub> = 5897 MHz, RF mode                                                                      |     | 84    |       | dBc  |

|                       |                                                                                                                          | f <sub>OUT</sub> = 7897 MHz, RF mode                                                                      |     | 74    |       | dBc  |

| DAC OUTPUT            | TIME DOMAIN CHARACTERISTICS                                                                                              |                                                                                                           |     |       |       |      |

| t <sub>RISE</sub>     | 10% to 90% <sup>(1)</sup>                                                                                                | JMODE 6, 1x Interpolation                                                                                 |     | 42    |       | ps   |

| t <sub>FALL</sub>     | 90% to 10% <sup>(1)</sup>                                                                                                | JMODE 6, 1x Interpolation                                                                                 |     | 42    |       | ps   |

|                       |                                                                                                                          | NRZ Mode, f <sub>OUT</sub> = DC (mid-code),<br>DEM/Dither off                                             |     | 55    |       | dBc  |

| f <sub>CLK</sub> DC   | Relative to fullscale sinewave at 1                                                                                      | NRZ Mode, f <sub>OUT</sub> = DC (mid-code),<br>DEM/Dither on                                              |     | 56    |       | dBc  |

| Feedthrough           | GHz                                                                                                                      | DES2XL Mode, f <sub>OUT</sub> = DC (mid-code), DEM/Dither off                                             |     | 56    |       | dBc  |

|                       |                                                                                                                          | DES2XL Mode, f <sub>OUT</sub> = DC (mid-code), DEM/Dither on                                              |     | 56    |       | dBc  |

| 2*f <sub>CLK</sub> DC | Relative to fullscale sinewave at 1                                                                                      | DES2XL Mode, f <sub>OUT</sub> = DC (mid-code), DEM/Dither off                                             |     | 56    |       | dBc  |

| Feedthrough           | GHz                                                                                                                      | DES2XL Mode, f <sub>OUT</sub> = DC (mid-<br>code), DEM/Dither on                                          |     | 57    |       | dBc  |

|            | PARAMETER                                                                            | TEST CONDITIONS             | MIN TYP | MAX | UNIT |

|------------|--------------------------------------------------------------------------------------|-----------------------------|---------|-----|------|

| 10.24 GSPS | , DUAL or SINGLE CHANNEL MODE, DDS                                                   | Mode, NRZ MODE              |         |     |      |

|            |                                                                                      | f <sub>OUT</sub> = 97 MHz   | 1.0     |     | dBm  |

|            |                                                                                      | f <sub>OUT</sub> = 997 MHz  | 0.6     |     | dBm  |

|            | Output power into $100\Omega$ load, I <sub>FS</sub> SWITCH = $20.5 \text{ mA}^{(2)}$ | f <sub>OUT</sub> = 1997 MHz | -0.3    |     | dBm  |

|            | load, IFS_SWITCH = 20.5 IIIA                                                         | f <sub>OUT</sub> = 2997 MHz | -0.9    |     | dBm  |

| 5          |                                                                                      | f <sub>OUT</sub> = 3997 MHz | -2.9    |     | dBm  |

| Роит       |                                                                                      | f <sub>OUT</sub> = 97 MHz   | 7.0     |     | dBm  |

|            |                                                                                      | f <sub>OUT</sub> = 997 MHz  | 6.5     |     | dBm  |

|            | Output power into $100\Omega$ load, $I_{FS \text{ SWITCH}} = 41 \text{ mA}^{(2)}$    | f <sub>OUT</sub> = 1997 MHz | 5.5     |     | dBm  |

|            | load, IFS_SWITCH 41 III/V                                                            | f <sub>OUT</sub> = 2997 MHz | 4.9     |     | dBm  |

|            |                                                                                      | f <sub>OUT</sub> = 3997 MHz | 2.9     |     | dBm  |

|            |                                                                                      | f <sub>OUT</sub> = 97 MHz   | 78      |     | dBc  |

|            | Spurious free dynamic range (SFDR)                                                   | f <sub>OUT</sub> = 997 MHz  | 67      |     | dBc  |

|            | across 0 - F <sub>DAC</sub> /2, I <sub>FS_SWITCH</sub> = 20.5                        | f <sub>OUT</sub> = 1997 MHz | 62      |     | dBc  |

|            | mA                                                                                   | f <sub>OUT</sub> = 2997 MHz | 59      |     | dBc  |

| SFDR       |                                                                                      | f <sub>OUT</sub> = 3997 MHz | 63      |     | dBc  |

| SFUR       |                                                                                      | f <sub>OUT</sub> = 97 MHz   | 71      |     | dBc  |

|            | Spurious free dynamic range (SFDR)                                                   | f <sub>OUT</sub> = 997 MHz  | 51      |     | dBc  |

|            | across 0 - F <sub>DAC</sub> /2, I <sub>FS_SWITCH</sub> = 41                          | f <sub>OUT</sub> = 1997 MHz | 48      |     | dBc  |

|            | mA                                                                                   | f <sub>OUT</sub> = 2997 MHz | 48      |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 3997 MHz | 52      |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 97 MHz   | -78     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 997 MHz  | -79     |     | dBc  |

|            | Second harmonic (HD2), 0 - F <sub>DAC</sub> /<br>2, I <sub>FS SWITCH</sub> = 20.5 mA | f <sub>OUT</sub> = 1997 MHz | -65     |     | dBc  |

|            | -, .F3_3WITCH                                                                        | f <sub>OUT</sub> = 2997 MHz | -59     |     | dBc  |

| HD2        |                                                                                      | f <sub>OUT</sub> = 3997 MHz | -63     |     | dBc  |

| IDZ        |                                                                                      | f <sub>OUT</sub> = 97 MHz   | -72     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 997 MHz  | -74     |     | dBc  |

|            | Second harmonic (HD2), 0 - F <sub>DAC</sub> /<br>2, I <sub>FS_SWITCH</sub> = 41 mA   | f <sub>OUT</sub> = 1997 MHz | -62     |     | dBc  |

|            | 7 10_0W11011                                                                         | f <sub>OUT</sub> = 2997 MHz | -61     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 3997 MHz | -62     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 97 MHz   | -91     |     | dBc  |

|            | Third harmonia (UD2) 0 F                                                             | f <sub>OUT</sub> = 997 MHz  | -68     |     | dBc  |

| HD3        | Third harmonic (HD3), 0 - F <sub>DAC</sub> /<br>2, I <sub>FS_SWITCH</sub> = 20.5 mA  | f <sub>OUT</sub> = 1997 MHz | -62     |     | dBc  |

|            | , 10_0W1011 ====                                                                     | f <sub>OUT</sub> = 2997 MHz | -62     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 3997 MHz | -78     |     | dBc  |

| טטו        |                                                                                      | f <sub>OUT</sub> = 97 MHz   | -73     |     | dBc  |

|            | Third become aris (UDO) O. 5                                                         | f <sub>OUT</sub> = 997 MHz  | -55     |     | dBc  |

|            | Third harmonic (HD3), 0 - F <sub>DAC</sub> /<br>2, I <sub>FS SWITCH</sub> = 41 mA    | f <sub>OUT</sub> = 1997 MHz | -52     |     | dBc  |

|            | 10_5WIIGH                                                                            | f <sub>OUT</sub> = 2997 MHz | -48     |     | dBc  |

|            |                                                                                      | f <sub>OUT</sub> = 3997 MHz | -53     |     | dBc  |

|                        | PARAMETER                                                                                                | TEST CONDITIONS                                                  | MIN | TYP  | MAX | UNIT   |

|------------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----|------|-----|--------|

|                        |                                                                                                          | f <sub>OUT</sub> = 97 MHz                                        |     | 94   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 997 MHz                                       |     | 87   |     | dBc    |

|                        | non-HD2/3 SFDR, I <sub>FS_SWITCH</sub> = 20.5 mA                                                         | f <sub>OUT</sub> = 1997 MHz                                      |     | 92   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 2997 MHz                                      |     | 89   |     | dBc    |

| YEDD                   |                                                                                                          | f <sub>OUT</sub> = 3997 MHz                                      |     | 87   |     | dBc    |

| FDR <sub>NONHD23</sub> |                                                                                                          | f <sub>OUT</sub> = 97 MHz                                        |     | 88   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 997 MHz                                       |     | 72   |     | dBc    |

|                        | non-HD2/3 SFDR, I <sub>FS_SWITCH</sub> = 41<br>mA                                                        | f <sub>OUT</sub> = 1997 MHz                                      |     | 76   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 2997 MHz                                      |     | 72   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 3997 MHz                                      |     | 67   |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 97 +/- 10 MHz, -7dBFS/tone                    |     | -100 |     | dBc    |

|                        | Third-order two tone intermodulation distortion, I <sub>FS_SWITCH</sub> = 20.5 mA                        | f <sub>OUT</sub> = 997 +/- 10 MHz, -7dBFS/tone                   |     | -74  |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 1997 +/- 10 MHz, -7dBFS/tone                  |     | -76  |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 2997 +/- 10 MHz, -7dBFS/tone                  |     | -70  |     | dBc    |

| AD2                    |                                                                                                          | f <sub>OUT</sub> = 3997 +/- 10 MHz, -7dBFS/tone                  |     | -65  |     | dBc    |

| MD3                    |                                                                                                          | f <sub>OUT</sub> = 97 +/- 10 MHz, -7dBFS/tone                    |     | -88  |     | dBc    |

|                        | Third-order two tone intermodulation distortion, I <sub>FS_SWITCH</sub> = 41 mA                          | f <sub>OUT</sub> = 997 +/- 10 MHz, -7dBFS/tone                   |     | -61  |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 1997 +/- 10 MHz, -7dBFS/tone                  |     | -58  |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 2997 +/- 10 MHz, -7dBFS/tone                  |     | -52  |     | dBc    |

|                        |                                                                                                          | f <sub>OUT</sub> = 3997 +/- 10 MHz, -7dBFS/tone                  |     | -55  |     | dBc    |

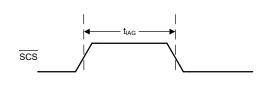

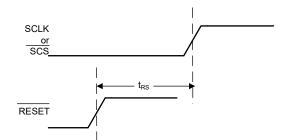

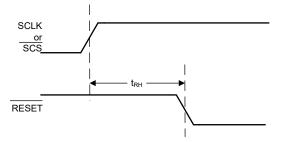

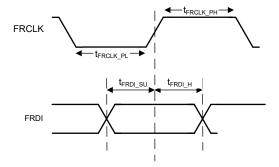

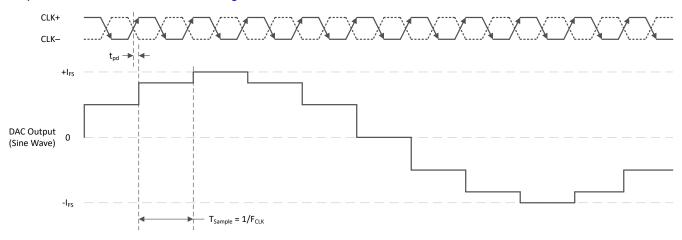

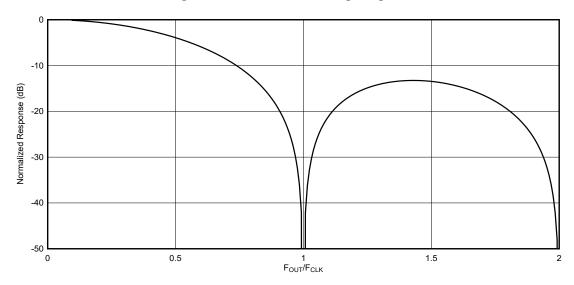

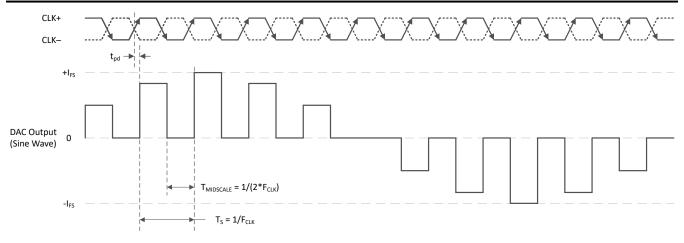

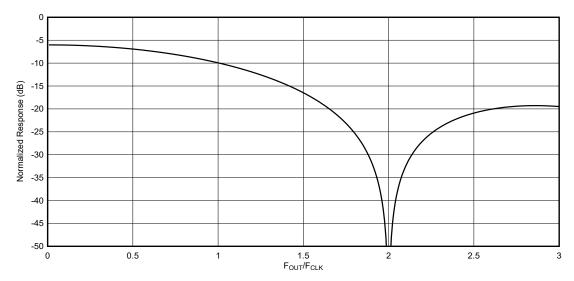

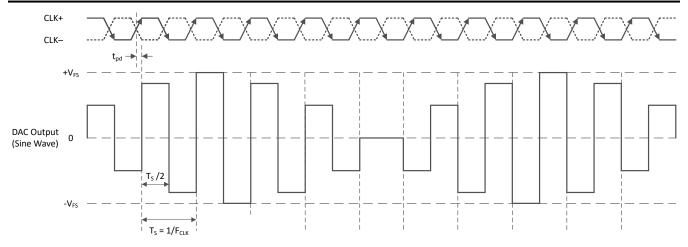

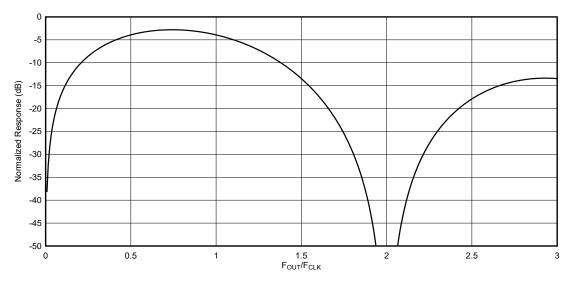

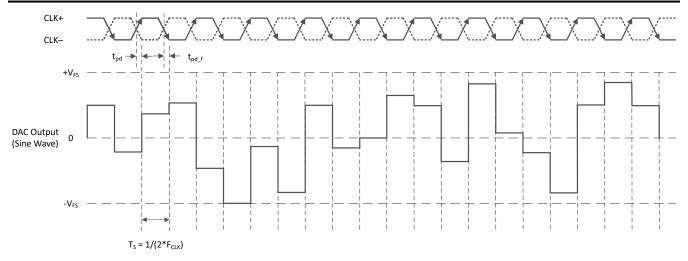

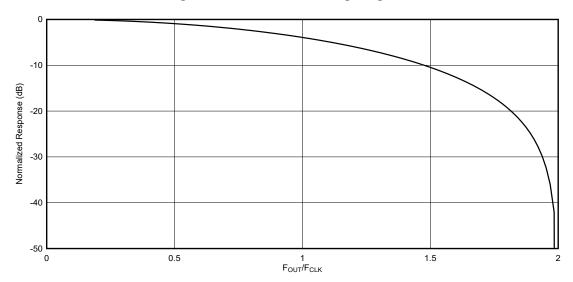

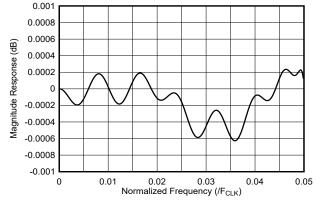

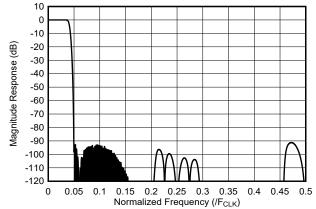

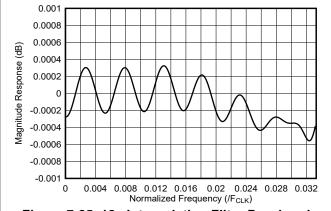

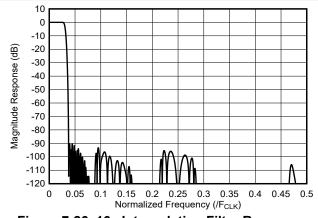

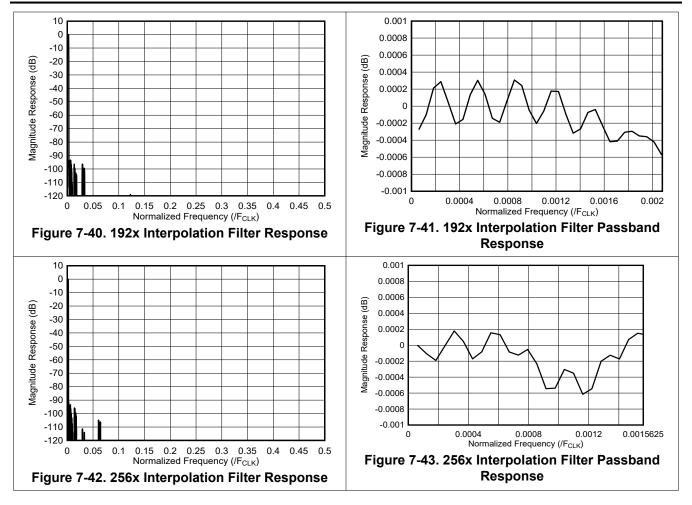

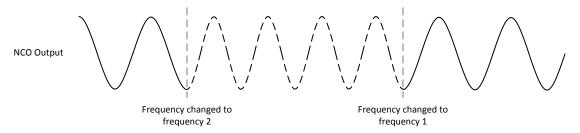

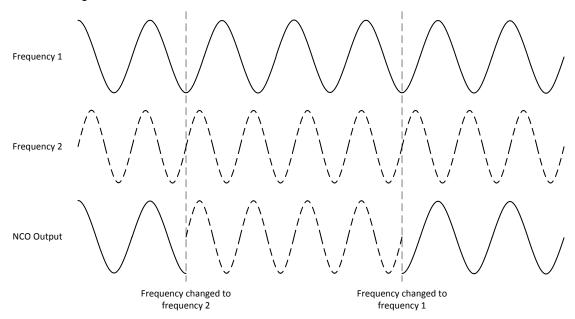

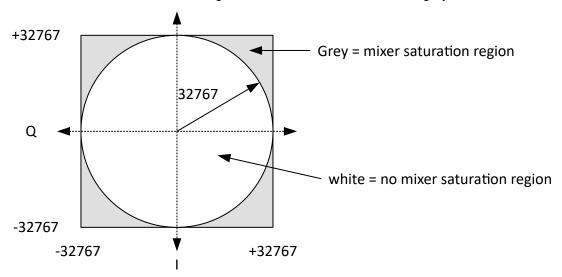

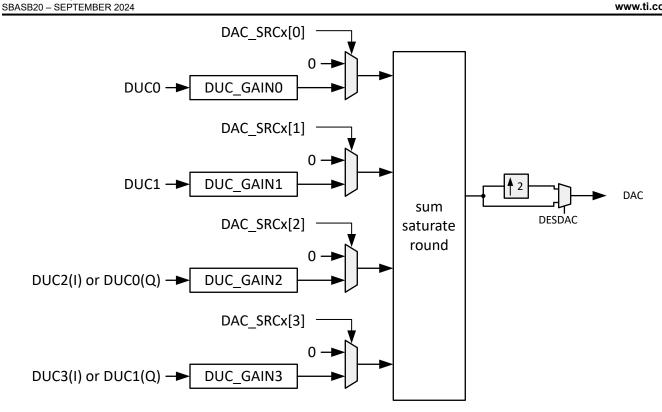

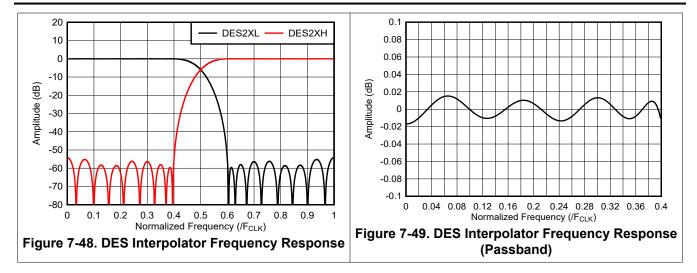

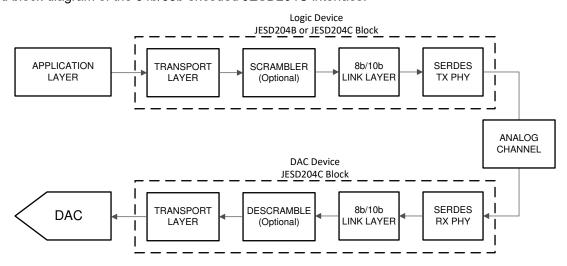

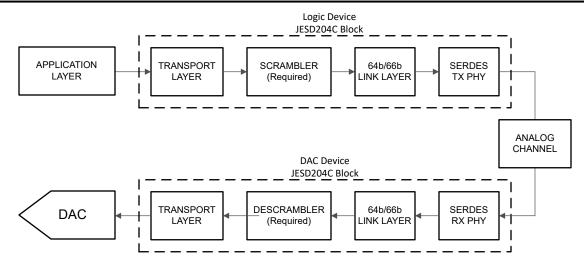

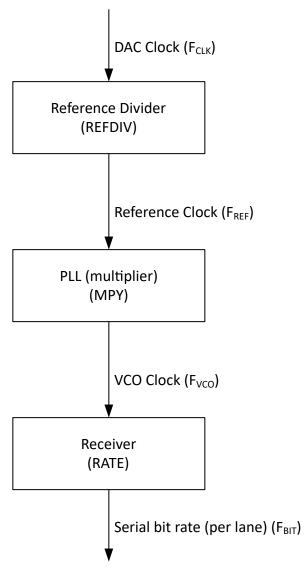

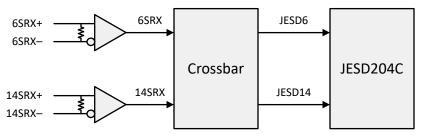

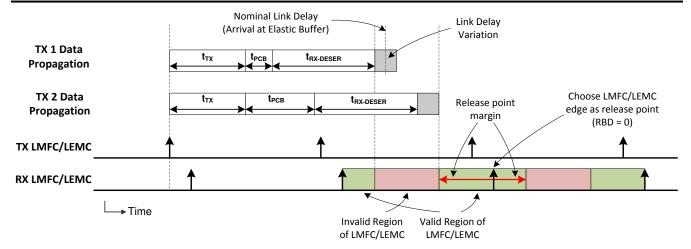

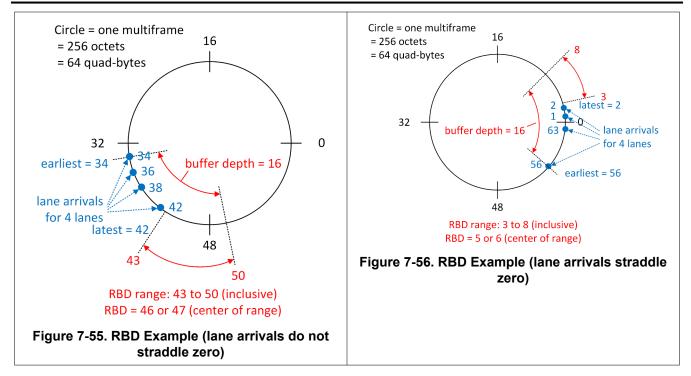

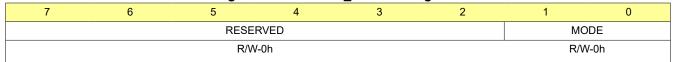

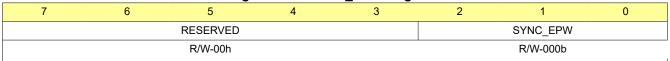

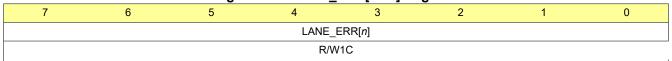

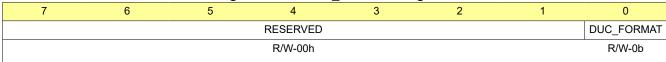

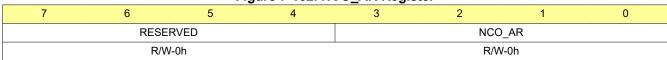

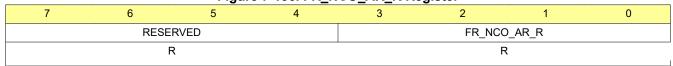

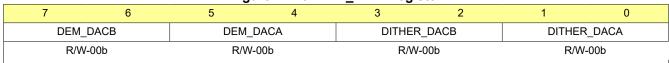

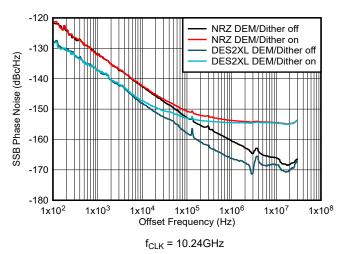

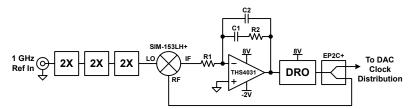

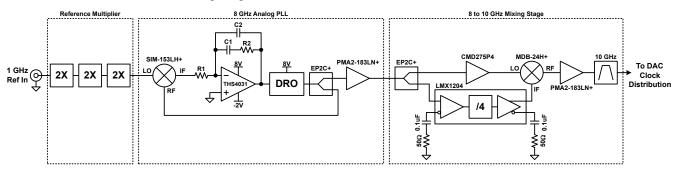

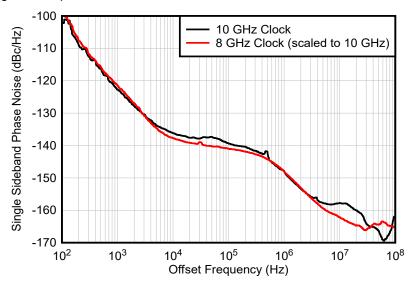

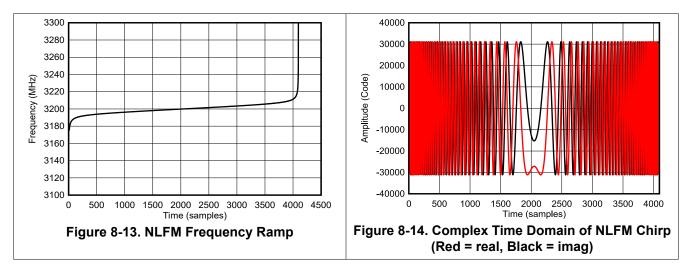

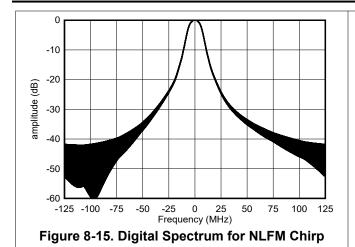

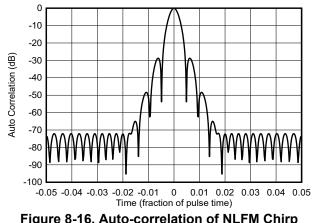

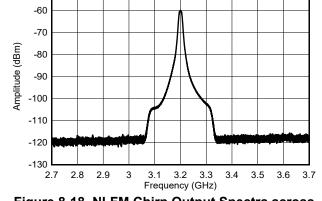

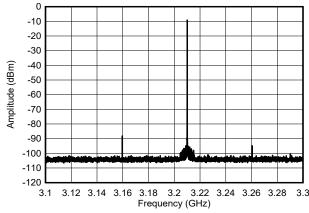

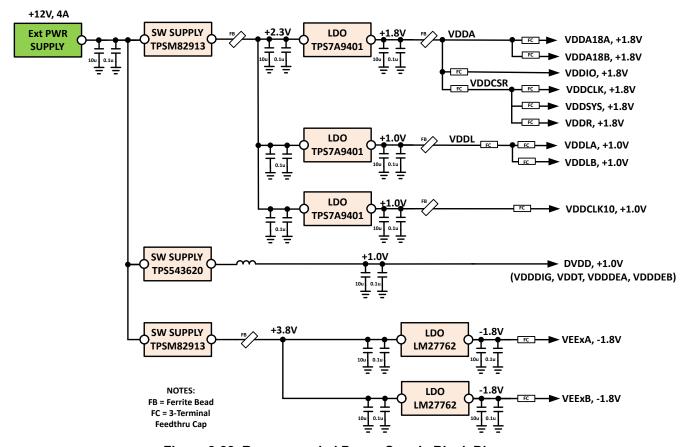

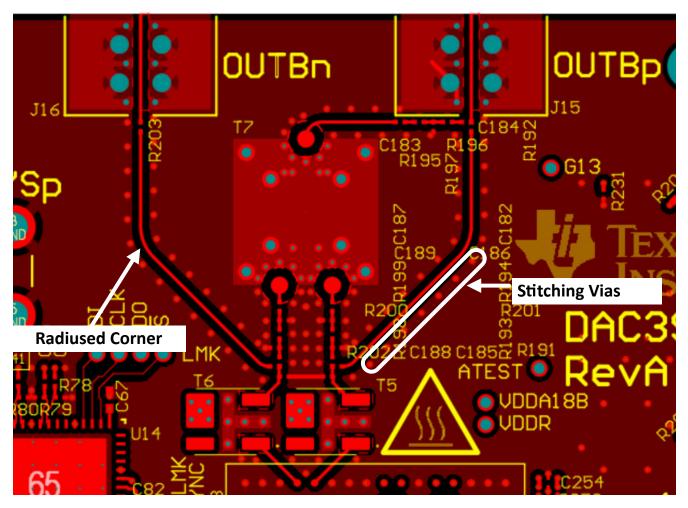

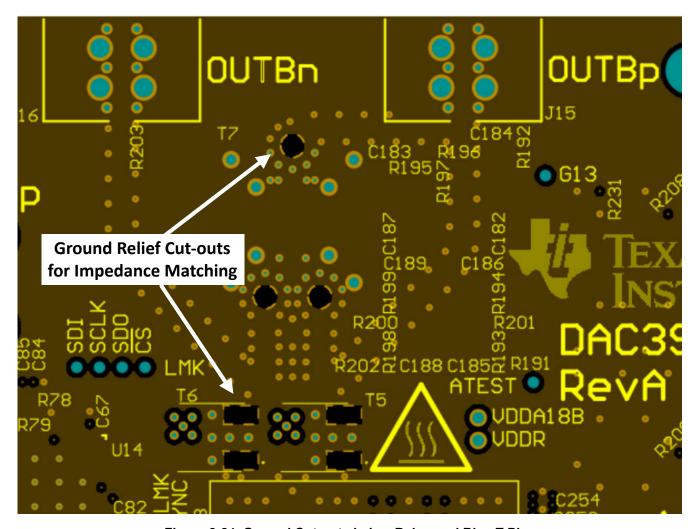

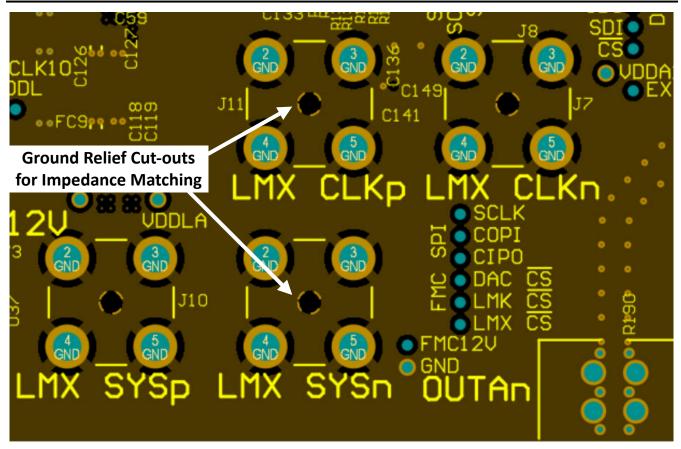

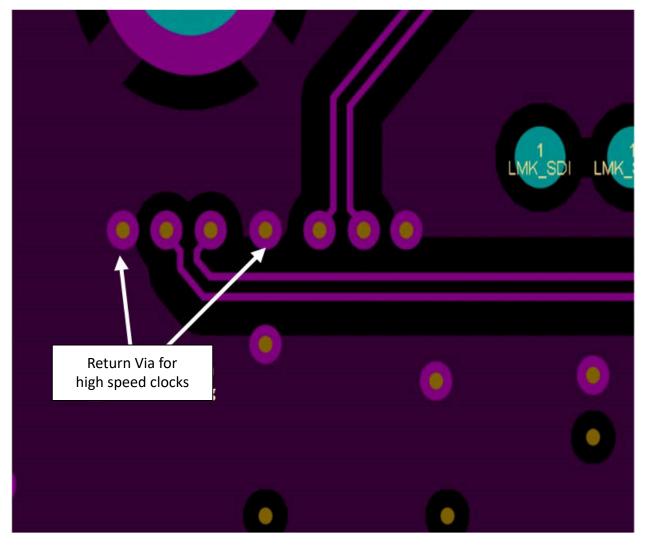

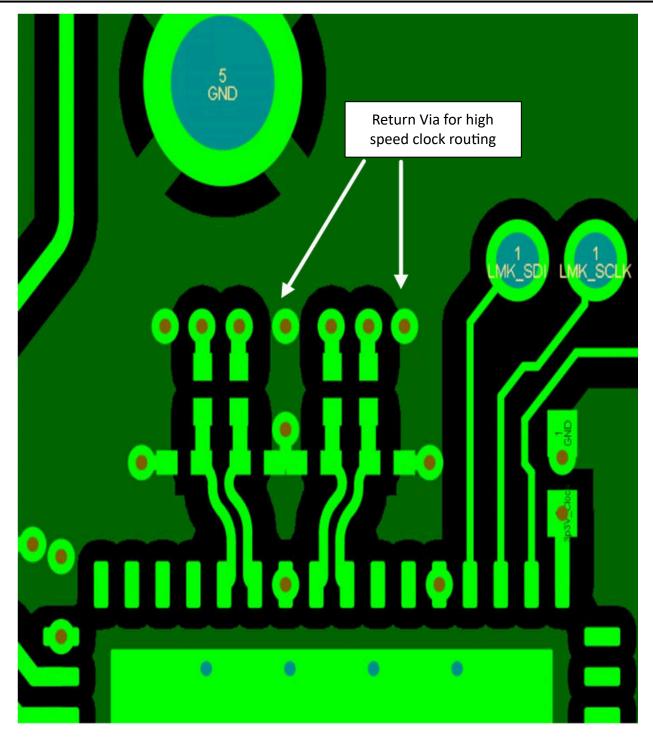

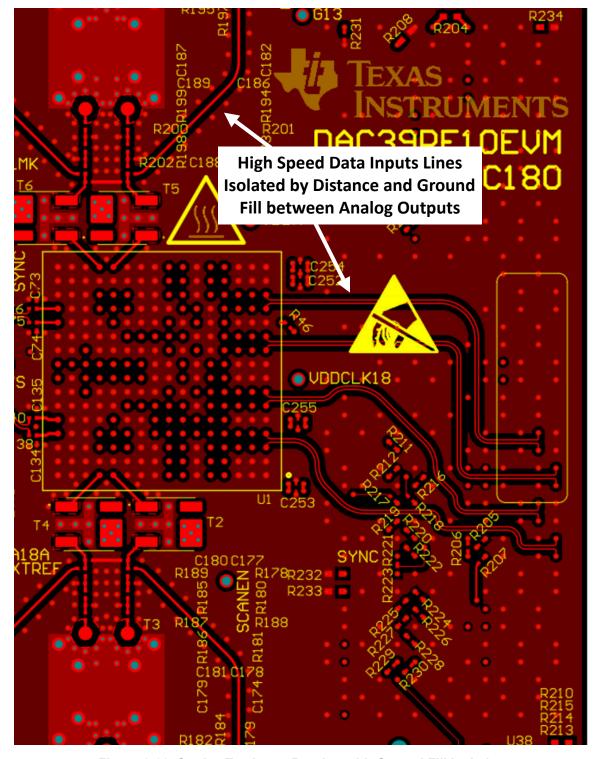

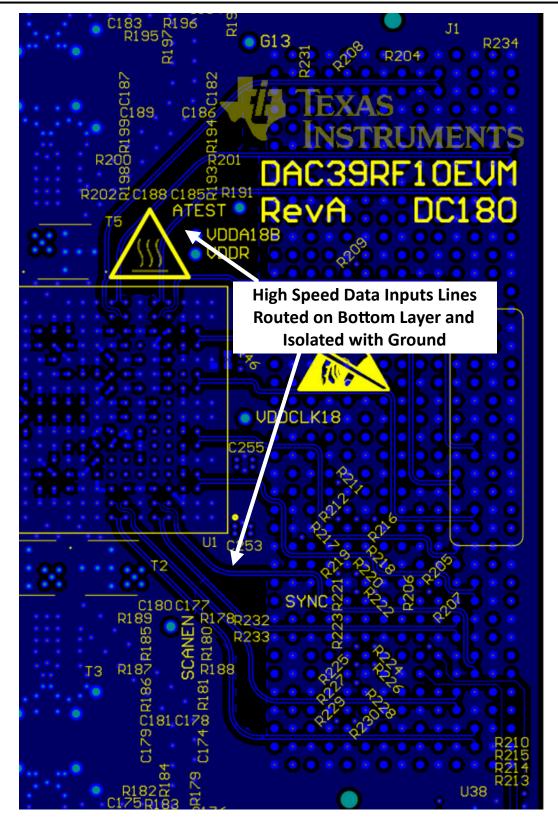

|                        |                                                                                                          | f <sub>OUT</sub> = 97 MHz, 70-MHz offset from f <sub>OUT</sub>   |     | -158 |     | dBc/Hz |