# DAC80516 16-Channel, 16-Bit, Voltage-Output DAC With Internal Reference

#### 1 Features

- Performance:

- INL: ±2LSB maximum at 16-bit resolution

- TUE: ±0.15% of FSR maximum

- Integrated 2.5V precision internal reference

- Initial accuracy: ±2.5mV maximum

- Drift: 5ppm/°C typical

- High drive capability: 50mA with 0.5V from supply

- Flexible configuration options

- User selectable gain: 2 ×, 1 ×

- Reset to zero scale

- Clear output function

- Wide operating range:

- Power supply: 2.7V to 5.5V

- Temperature range: -40°C to +125°C

- SPI and I<sup>2</sup>C interfaces: 1.7V to 5.5V operation

- SPI: 4-wire interface

- I<sup>2</sup>C: Four target addresses

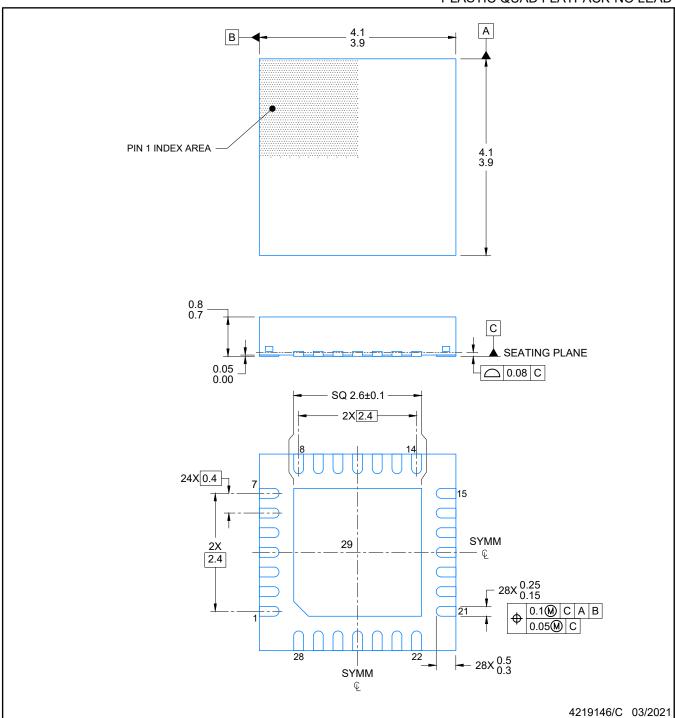

- Small package:

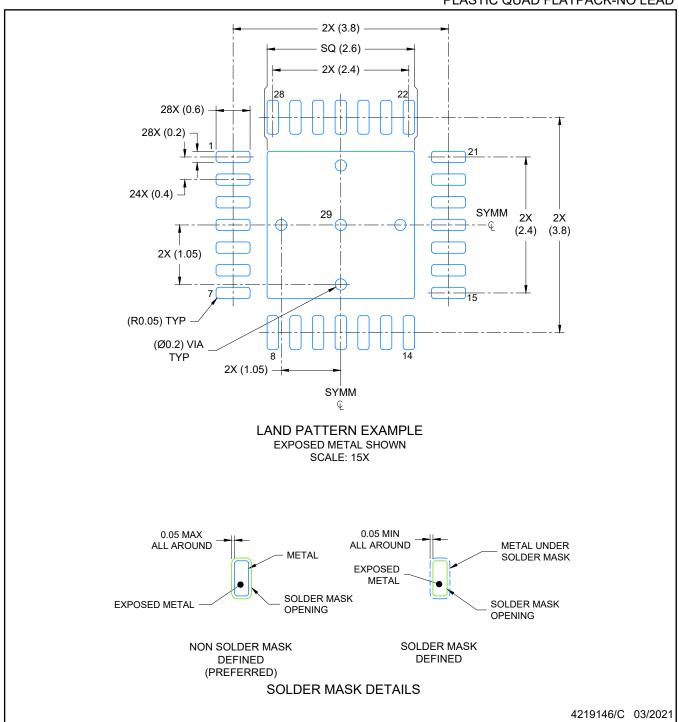

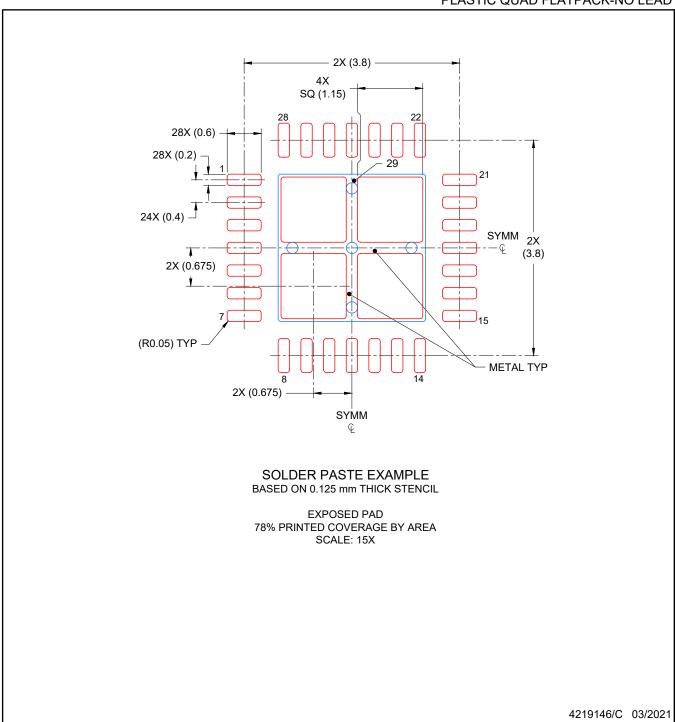

- 4mm × 4mm, 28-pin WQFN

# 2 Applications

- Optical modules

- Inter-DC interconnect

- Analog output module

# 3 Description

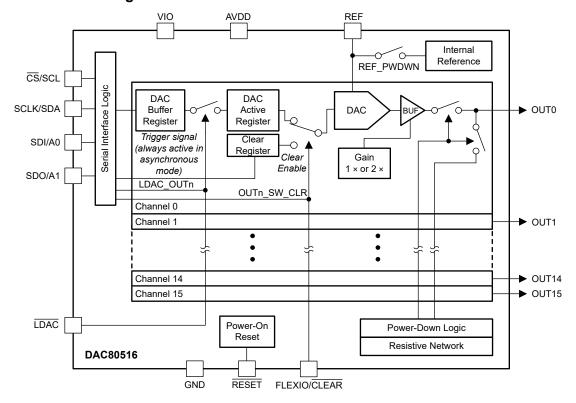

The 16-bit DAC80516 is a low-power, 16-channel, buffered voltage-output digital-to-analog converter (DAC). The DAC80516 includes a 2.5V, 5ppm/°C internal reference, eliminating the need for an external precision reference in most applications. A user selectable gain configuration can be used to provide full-scale output voltages of 2.5V or 5V. The DAC80516 operates from a single power supply.

Communication to the DAC80516 is performed through an SPI- and I<sup>2</sup>C-supported serial interface, operating at clock rates of up to 50MHz (during SPI writes to the device). The VIO pin enables serial interface operation from 1.7V to 5.5V. The DAC80516 flexible interface enables operation with a wide range of industry-standard microprocessors and microcontrollers.

The DAC80516 is characterized for operation over the temperature range of -40°C to +125°C and available in a small WQFN package.

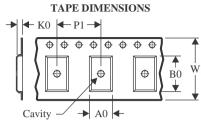

Package Information

|             | •                      |                             |

|-------------|------------------------|-----------------------------|

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

| DAC80516    | RUY (WQFN, 28)         | 4mm × 4mm                   |

- For more information, see Section 11.

- The package size (length × width) is a nominal value and includes pins, where applicable.

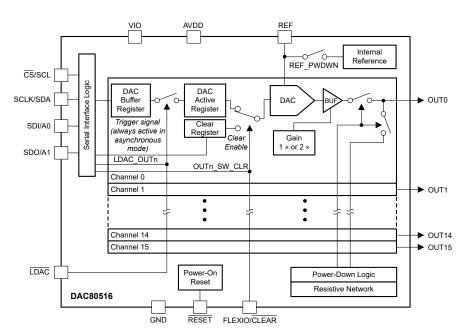

**Functional Block Diagram**

# **Table of Contents**

| 1 Features1                                                | 6.4 Device Functional Modes2                         |

|------------------------------------------------------------|------------------------------------------------------|

| 2 Applications1                                            | 6.5 Programming2                                     |

| 3 Description1                                             | 7 Register Map2                                      |

| 4 Pin Configuration and Functions2                         | 7.1 DAC80516 Registers3                              |

| 5 Specifications4                                          | 8 Application and Implementation5                    |

| 5.1 Absolute Maximum Ratings4                              | 8.1 Application Information5                         |

| 5.2 ESD Ratings4                                           | 8.2 Typical Application5                             |

| 5.3 Recommended Operating Conditions4                      | 8.3 Initialization Setup6                            |

| 5.4 Thermal Information4                                   | 8.4 Power Supply Recommendations6                    |

| 5.5 Electrical Characteristics5                            | 8.5 Layout6                                          |

| 5.6 Timing Requirements - I <sup>2</sup> C Standard Mode7  | 9 Device and Documentation Support6                  |

| 5.7 Timing Requirements - I <sup>2</sup> C Fast Mode7      | 9.1 Documentation Support6                           |

| 5.8 Timing Requirements - I <sup>2</sup> C Fast Mode Plus7 | 9.2 Receiving Notification of Documentation Updates6 |

| 5.9 Timing Requirements - SPI8                             | 9.3 Support Resources6                               |

| 5.10 Switching Characteristics8                            | 9.4 Trademarks6                                      |

| 5.11 Timing Diagrams9                                      | 9.5 Electrostatic Discharge Caution6                 |

| 5.12 Typical Characteristics10                             | 9.6 Glossary6                                        |

| 6 Detailed Description19                                   | 10 Revision History6                                 |

| 6.1 Overview19                                             | 11 Mechanical, Packaging, and Orderable              |

| 6.2 Functional Block Diagram19                             | Information6                                         |

| 6.3 Feature Description20                                  |                                                      |

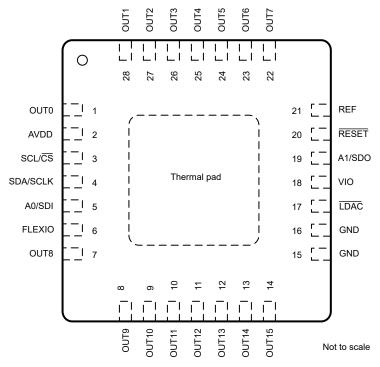

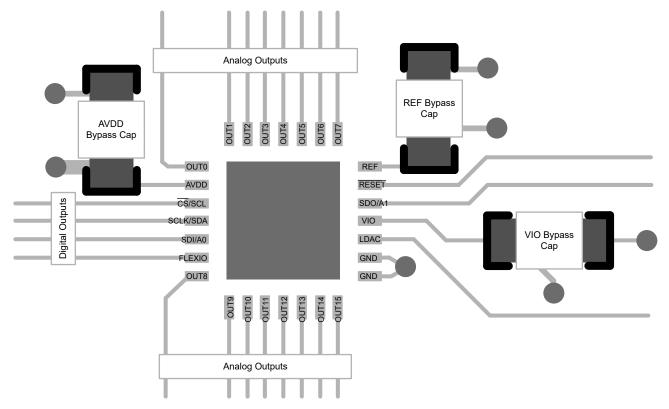

# **4 Pin Configuration and Functions**

Figure 4-1. RUY Package, 28-Pin WQFN (Top View)

## **Table 4-1. Pin Functions**

|     | PIN      |                  | Table 4-1. Pin Functions                                                                                                                                                                  |

|-----|----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME     | TYPE             | DESCRIPTION                                                                                                                                                                               |

| 1   | OUT0     | Output           | DAC output channel 0                                                                                                                                                                      |

| 2   | AVDD     | Power            | Analog power supply                                                                                                                                                                       |

| _   | 7.022    |                  | l <sup>2</sup> C: Clock input.                                                                                                                                                            |

| 3   | SCL/CS   | Input            | SPI: Active-low serial data enable. This input is the frame synchronization signal for the serial data. When                                                                              |

|     |          | ·                | the signal goes low, this pin enables the serial interface input shift register.                                                                                                          |

| 4   | SDA/SCLK | Input/           | I <sup>2</sup> C: Bidirectional data line                                                                                                                                                 |

| 4   | SDA/SCLK | Output           | SPI: Clock input                                                                                                                                                                          |

| 5   | A0/SDI   | lanut            | I <sup>2</sup> C: Target address selector                                                                                                                                                 |

| 5   | AU/SDI   | Input            | SPI: Data input. Data are clocked into the input shift register on each falling edge of the SCLK pin.                                                                                     |

| 6   | FLEXIO   | Input/<br>Output | FLEXIO pin, including GPIO and CLEAR pin functionality                                                                                                                                    |

| 7   | OUT8     | Output           | DAC output channel 8                                                                                                                                                                      |

| 8   | OUT9     | Output           | DAC output channel 9                                                                                                                                                                      |

| 9   | OUT10    | Output           | DAC output channel 10                                                                                                                                                                     |

| 10  | OUT11    | Output           | DAC output channel 11                                                                                                                                                                     |

| 11  | OUT12    | Output           | DAC output channel 12                                                                                                                                                                     |

| 12  | OUT13    | Output           | DAC output channel 13                                                                                                                                                                     |

| 13  | OUT14    | Output           | DAC output channel 14                                                                                                                                                                     |

| 14  | OUT15    | Output           | DAC output channel 15                                                                                                                                                                     |

| 15  | GND      | Power            | Ground reference point for all circuitry on the device                                                                                                                                    |

| 16  | GND      | Power            | Ground reference point for all circuitry on the device                                                                                                                                    |

| 17  | LDAC     | Input            | Active-low DAC synchronization signal. A high-to-low transition on the $\overline{\text{LDAC}}$ pin simultaneously updates the outputs configured in synchronous mode                     |

| 18  | VIO      | Power            | IO supply voltage. This pin sets the I/O operating voltage for the device.                                                                                                                |

|     |          | Innut/           | I <sup>2</sup> C: Target address selector.                                                                                                                                                |

| 19  | A1/SDO   | Input/<br>Output | SPI: Data output. Data are clocked out of the input shift register on either rising or falling edges of the SCLK pin as specified by the FSDO bit.                                        |

| 20  | RESET    | Input            | Active low reset input, logic low on this pin causes the device to initiate a reset event                                                                                                 |

| 21  | REF      | Input/<br>Output | DAC voltage reference input/output. This pin acts as input pin REFIN by default (with internal reference disabled). If internal reference is enabled, this pin acts as output pin REFOUT. |

| 22  | OUT7     | Output           | DAC output channel 7                                                                                                                                                                      |

| 23  | OUT6     | Output           | DAC output channel 6                                                                                                                                                                      |

| 24  | OUT5     | Output           | DAC output channel 5                                                                                                                                                                      |

| 25  | OUT4     | Output           | DAC output channel 4                                                                                                                                                                      |

| 26  | OUT3     | Output           | DAC output channel 3                                                                                                                                                                      |

| 27  | OUT2     | Output           | DAC output channel 2                                                                                                                                                                      |

| 28  | OUT1     | Output           | DAC output channel 1                                                                                                                                                                      |

# **5 Specifications**

## 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                                | MIN  | MAX                    | UNIT |

|------------------|------------------------------------------------|------|------------------------|------|

| $AV_{DD}$        | Analog supply voltage, AV <sub>DD</sub> to GND | -0.3 | 6                      | V    |

| V <sub>IO</sub>  | Digital supply voltage, V <sub>IO</sub> to GND | -0.3 | $AV_DD$                | V    |

|                  | Analog output (OUT) pin voltage                | -0.3 | AV <sub>DD</sub> + 0.3 | V    |

|                  | Reference pin voltage                          | -0.3 | AV <sub>DD</sub> + 0.3 | V    |

|                  | Serial interface pin voltage                   | -0.3 | V <sub>IO</sub> + 0.3  | V    |

| TJ               | Operating junction temperature                 | -40  | 150                    | °C   |

| T <sub>stg</sub> | Storage temperature                            | -60  | 150                    | °C   |

<sup>(1)</sup> Operation outside the *Absolute Maximum Ratings* may cause permanent device damage. *Absolute Maximum Ratings* do not imply functional operation of the device at these or any other conditions beyond those listed under *Recommended Operating Conditions*. If used outside the *Recommended Operating Conditions* but within the *Absolute Maximum Ratings*, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|                    |                          |                                                                                 | VALUE | UNIT |

|--------------------|--------------------------|---------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatic discharge  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2500 | V    |

| V <sub>(ESD)</sub> | Liectrostatic discriarge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

#### **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                 |                                                | MIN | NOM MAX         | UNIT |

|-----------------|------------------------------------------------|-----|-----------------|------|

| $AV_{DD}$       | Analog supply voltage, AV <sub>DD</sub> to GND | 2.7 | 5.5             | V    |

| V <sub>IO</sub> | IO supply voltage, V <sub>IO</sub> to GND      | 1.7 | $AV_DD$         | V    |

|                 | Serial interface input voltage to GND          | 0   | V <sub>IO</sub> | V    |

| T <sub>J</sub>  | Operating junction temperature                 | -40 | 125             | °C   |

#### **5.4 Thermal Information**

|                       |                                              | DAC80516   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC(1)                            | RUY (WQFN) | UNIT |

|                       |                                              | 28 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 39.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 24.8       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 15.9       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.3        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 15.9       | °C/W |

| $R_{\theta JC(bot)}$  | Junction-to-case (bottom) thermal resistance | 2.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **5.5 Electrical Characteristics**

at  $T_J = -40^{\circ}$ C to +125°C,  $AV_{DD} = 2.7V$  to 5.5V,  $V_{IO} = 1.7V$  to  $AV_{DD}$ ,  $V_{REFIN} = 2.4V$  to 5.5V, DAC outputs unloaded, and digital inputs at  $V_{IO}$  or GND (unless otherwise noted)

|            | PARAMETER                       | TEST CONDITIONS                                             | MIN | TYP   | MAX                  | UNIT          |

|------------|---------------------------------|-------------------------------------------------------------|-----|-------|----------------------|---------------|

| Resolution |                                 |                                                             |     |       |                      |               |

|            | Resolution                      |                                                             | 16  |       |                      | Bits          |

| INL        | Relative accuracy               |                                                             |     | ±1    | ±2                   | LSB           |

| DNL        | Differential nonlinearity       |                                                             | -1  | ±0.6  | 1                    | LSB           |

| TUE        | Total unadjusted error          | DAC output range = 0V to 5V                                 |     | ±0.04 | ±0.15                | %FSR          |

|            | Offset error                    | Gain = 1 or 2                                               |     | ±0.75 | ±3                   | mV            |

|            | Zero-scale error                | DAC register loaded with all zeroes                         | 0   | 0.5   | 3                    | mV            |

|            | Full-scale error                |                                                             |     | ±0.04 | ±0.15                | %FSR          |

|            | Gain error                      | Gain = 1 or 2                                               |     | ±0.04 | ±0.15                | %FSR          |

|            | Offset error drift              |                                                             |     | ±3    |                      | μV/°C         |

|            | Zero-scale error drift          |                                                             |     | ±2    |                      | μV/°C         |

|            | Full-scale error drift          |                                                             |     | ±3    |                      | ppm<br>FSR/°C |

|            | Gain error drift                |                                                             |     | ±2    |                      | ppm<br>FSR/°C |

|            | Output voltage drift over time  |                                                             |     | 20    |                      | ppm FSI       |

| OUTPL      | JT CHARACTERISTICS              |                                                             |     |       |                      |               |

|            | Output valtage(2)               | Gain = 2                                                    | 0   |       | 2 × V <sub>REF</sub> | V             |

|            | Output voltage(=)               | Gain = 1                                                    | 0   |       | $V_{REF}$            |               |

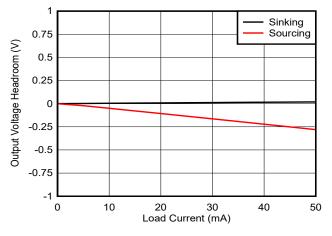

|            | Output voltage headroom         |                                                             | 0.5 |       |                      | V             |

|            | Load current                    |                                                             |     | 50    |                      | mA            |

|            |                                 | Full-scale output shorted to GND                            |     | 75    |                      | ^             |

|            | Short-circuit current(*)        | Zero-scale output shorted to V <sub>DD</sub>                |     | 75    |                      | - mA          |

|            | Capacitive load <sup>(4)</sup>  | R <sub>LOAD</sub> = open                                    | 0   |       | 2                    | nF            |

|            | DC systematics and areas        | DAC output at AV <sub>DD</sub> /2                           |     | 0.08  |                      | _             |

|            | DC output impedance             | DAC output at AV <sub>DD</sub> or GND                       |     | 10    |                      | Ω             |

| DYNAI      | MIC PERFORMANCE                 |                                                             |     |       |                      |               |

|            | Output voltage settling time    | time to $\pm 2$ LSB, AV <sub>DD</sub> = 5.5V,               |     | 6     |                      | μs            |

|            | Slew rate                       | AV <sub>DD</sub> = 5.5V, V <sub>REFIN</sub> = 2.5V          |     | 1.7   |                      | V/µs          |

|            | Power-on glitch magnitude       | DAC code = zero scale                                       |     | 25    |                      | mV            |

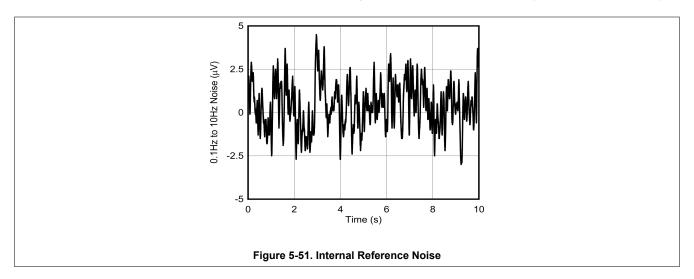

|            | Output noise                    | 0.1Hz to 10Hz, DAC code = midscale                          |     | 12    |                      | μVpp          |

|            | Output noise density            |                                                             |     | 65    |                      | nV/Hz         |

|            | AC PSRR                         | amplitude 200mVpp superimposed on                           |     | 80    |                      | dB            |

|            | DC PSRR                         | DAC code = midscale, AV <sub>DD</sub> = 5V ±0.5V            |     | 0.02  |                      | mV/V          |

|            | Code change glitch impulse      | 1LSB change around major carrier                            |     | 1     |                      | nV-s          |

|            | Channel-to-channel ac crosstalk | DAC code = zero scale, full-scale swing on adjacent channel |     | 1     |                      | nV-s          |

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

#### 5.5 Electrical Characteristics (continued)

at  $T_J = -40^{\circ}$ C to +125°C,  $AV_{DD} = 2.7V$  to 5.5V,  $V_{IO} = 1.7V$  to  $AV_{DD}$ ,  $V_{REFIN} = 2.4V$  to 5.5V, DAC outputs unloaded, and digital inputs at  $V_{IO}$  or GND (unless otherwise noted)

|                     | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TEST CONDITIONS                                                                                     | MIN                   | TYP | MAX                   | UNIT   |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|--------|

|                     | Channel to channel do crosstalk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Measured channel at zero scale, adjacent channel at full scale                                      |                       | 12  |                       | μV     |

|                     | Channel-to-channel dc crosstalk  Digital feedthrough  Power-up time(5)  L REFERENCE INPUT  Reference input voltage range  Reference input current  Reference input impedance  Reference input capacitance  L REFERENCE  Reference output voltage range  Reference output voltage range  Reference output drift  Reference output impedance  Reference output noise  Reference output noise  Reference load current  Reference load regulation  Reference line regulation  NPUTS AND OUTPUTS  High-level input voltage, V <sub>IL</sub> Input current  Input pin capacitance  High-level output voltage, V <sub>OL</sub> Coutput pin capacitance | Measured channel at zero scale, all other channels at full scale                                    |                       | 12  |                       | μν     |

|                     | Digital feedthrough                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DAC code = midscale, f <sub>SCLK</sub> = 1MHz                                                       |                       | 0.1 |                       | nV-s   |

|                     | Power-up time <sup>(5)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Time for DAC channels to power on and output 0V after $A_{VDD}$ ramps to 2.4V, $V_{REFIN} = 2.5V$ . |                       | 120 |                       | μs     |

| EXTERN              | AL REFERENCE INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                       |     |                       |        |

| $V_{REFIN}$         | Reference input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Gain = 1                                                                                            | 1                     |     | $V_{DD}$              | V      |

| V REFIN             | Treference input voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Gain = 2                                                                                            | 1                     |     | $AV_{DD}/2$           | V      |

|                     | Reference input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $V_{REFIN} = 2.5V$                                                                                  |                       | 85  |                       | μΑ     |

|                     | Reference input impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                     |                       | 25  | 30                    | kΩ     |

|                     | Reference input capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                     |                       | 5   |                       | pF     |

| INTERNA             | AL REFERENCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                     |                       |     |                       |        |

| V <sub>REFOUT</sub> | Reference output voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T <sub>J</sub> = 25°C                                                                               | 2.4975                |     | 2.5025                | V      |

|                     | Reference output drift                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |                       | 5   | 10                    | ppm/°C |

|                     | Reference output impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                     |                       | 0.2 |                       | Ω      |

|                     | Reference output noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.1Hz to 10Hz                                                                                       |                       | 10  |                       | μVрр   |

|                     | Reference output noise density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10kHz, reference load = 10nF                                                                        |                       | 125 |                       | nV/Hz  |

|                     | Reference load current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     | -4                    |     | 10                    | mA     |

|                     | Reference load regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Source and sink                                                                                     |                       | 175 |                       | μV/mA  |

|                     | Reference line regulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                     |                       | 500 |                       | μV/V   |

| DIGITAL             | INPUTS AND OUTPUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                     |                       |     |                       |        |

| V <sub>IH</sub>     | High-level input voltage, V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AV <sub>DD</sub> = 2.7V to 5.5V                                                                     | 0.7 × V <sub>IO</sub> |     |                       | V      |

| V <sub>IL</sub>     | Low-level input voltage, V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | AV <sub>DD</sub> = 2.7V to 5.5V                                                                     |                       |     | 0.3 × V <sub>IO</sub> | V      |

|                     | Input current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                     |                       | ±2  |                       | μΑ     |

|                     | Input pin capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                     |                       | 8   |                       | pF     |

| V <sub>OH</sub>     | High-level output voltage, V <sub>OH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I <sub>OH</sub> = 0.2mA                                                                             | V <sub>IO</sub> - 0.2 |     |                       | V      |

| V <sub>OL</sub>     | Low-level output voltage, V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>OL</sub> = 0.2mA                                                                             |                       |     | 0.4                   | V      |

|                     | Output pin capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |                       | 4   |                       | pF     |

| POWER               | REQUIREMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                     |                       |     |                       |        |

| I                   | AV cumply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Active mode, internal reference enabled, DAC code = full-scale, SPI static                          |                       | 8.5 | 13                    | mA     |

| I <sub>AVDD</sub>   | AV <sub>DD</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Active mode, internal reference disabled, DAC code = full-scale, SPI static                         |                       | 8   | 12.5                  | ША     |

|                     | AV <sub>DD</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power-down mode                                                                                     |                       | 10  | 20                    | μΑ     |

| I <sub>VIO</sub>    | V <sub>IO</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                     |                       | 0.1 | 1                     | μA     |

- (1) End point fit between codes 256 to 65280

- (2) When using an external reference  $V_{REF} = V_{REFIN}$ . Otherwise,  $V_{REF} = 2.5V$  (internal reference voltage)

- (3) Temporary overload condition protection. Junction temperature can be exceeded during current limit. Operation at temperatures greater than the specified maximum junction temperature can impair device reliability.

- (4) Specified by design and characterization, not production tested.

- (5) For a further period of time equal to approximately 5ms, SPI or I2C communication to the device is blocked while the device loads internal calibration coefficients from memory. Any digital communication during this timeframe is ignored.

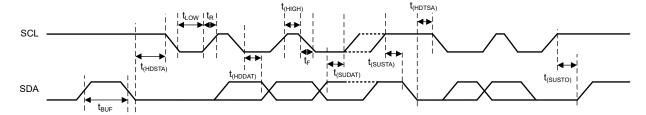

# 5.6 Timing Requirements - I<sup>2</sup>C Standard Mode

at  $T_J = -40$ °C to +125°C,  $AV_{DD} = 2.7V$  to 5.5V,  $V_{IO} = 1.7V$  to  $AV_{DD}$ ,  $V_{REFIN} = 2.4V$  to 5.5V, and digital inputs at  $V_{IO}$  or GND

|                     | 7 DD 7 TO DD TALLING                            |      | <u> </u> |      |

|---------------------|-------------------------------------------------|------|----------|------|

|                     |                                                 | MIN  | NOM MAX  | UNIT |

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 100      | kHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 4.7  |          | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 4    |          | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 4.7  |          | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 4    |          | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |          | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 250  |          | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 4700 |          | ns   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 4000 |          | ns   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 300      | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 1000     | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 3.45     | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 3.45     | μs   |

# 5.7 Timing Requirements - I<sup>2</sup>C Fast Mode

at  $T_{L} = -40^{\circ}$ C to +125°C, AV<sub>DD</sub> = 2.7V to 5.5V,  $V_{IO} = 1.7$ V to AV<sub>DD</sub>,  $V_{REFIN} = 2.4$ V to 5.5V, and digital inputs at  $V_{IO}$  or GND

|                     |                                                 | MIN  | NOM MAX | UNIT |

|---------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 400     | kHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 1.3  |         | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 0.6  |         | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 0.6  |         | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 0.6  |         | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 100  |         | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 1300 |         | ns   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 600  |         | ns   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 300     | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 300     | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 0.9     | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 0.9     | μs   |

# 5.8 Timing Requirements - I<sup>2</sup>C Fast Mode Plus

at  $T_J = -40$ °C to +125°C,  $AV_{DD} = 2.7V$  to 5.5V,  $V_{IO} = 1.7V$  to  $AV_{DD}$ ,  $V_{REFIN} = 2.4V$  to 5.5V, and digital inputs at  $V_{IO}$  or GND

|                     |                                                 | MIN  | NOM MAX | UNIT |

|---------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 1       | MHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 0.5  |         | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 0.26 |         | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 0.26 |         | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 0.26 |         | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 50   |         | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 0.5  |         | μs   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 0.26 |         | μs   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 120     | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 120     | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 0.45    | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 0.45    | μs   |

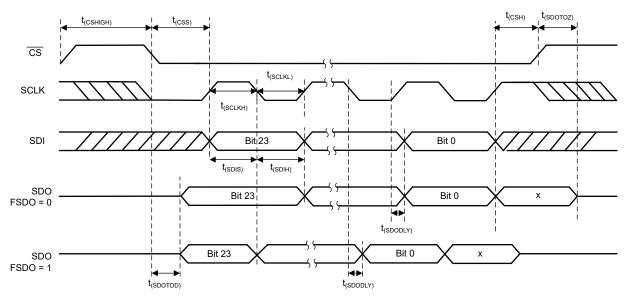

## 5.9 Timing Requirements - SPI

at  $T_J = -40$ °C to +125°C,  $AV_{DD} = 2.7V$  to 5.5V,  $V_{IO} = 1.7V$  to  $AV_{DD}$ ,  $V_{REFIN} = 2.4V$  to 5.5V, and digital inputs at  $V_{IO}$  or GND

|                       |                                             | MIN | NOM | MAX | UNIT |

|-----------------------|---------------------------------------------|-----|-----|-----|------|

| SPI TIMIN             | G REQUIREMENTS, FSDO = 0                    | 1   |     |     |      |

| f <sub>(SCLK)</sub>   | SCLK frequency                              |     |     | 20  | MHz  |

| t <sub>(SCLKH)</sub>  | SCLK high time                              | 20  |     |     | ns   |

| t <sub>(SCLKL)</sub>  | SCLK low time                               | 23  |     |     | ns   |

| t <sub>(SDIS)</sub>   | SDI setup time                              | 5   |     |     | ns   |

| t <sub>(SDIH)</sub>   | SDI hold time                               | 8   |     |     | ns   |

| t <sub>(SDOTOZ)</sub> | SDO active output to tri-state output delay | 0   |     | 17  | ns   |

| t <sub>(SDOEN)</sub>  | SDO tri-state output to active output delay | 0   |     | 21  | ns   |

| t <sub>(SDOTOD)</sub> | SDO output delay                            | 2   |     | 23  | ns   |

| t <sub>(CSS)</sub>    | CS setup time                               | 15  |     |     | ns   |

| t <sub>(CSH)</sub>    | CS hold time                                | 15  |     |     | ns   |

| t <sub>(CSHIGH)</sub> | CS high time                                | 15  |     |     | ns   |

| SPI TIMIN             | G REQUIREMENTS, FSDO = 1                    |     |     |     |      |

| f <sub>(SCLK)</sub>   | SCLK frequency (1)                          |     |     | 30  | MHz  |

| t <sub>(SCLKH)</sub>  | SCLK high time                              | 14  |     |     | ns   |

| t <sub>(SCLKL)</sub>  | SCLK low time                               | 16  |     |     | ns   |

| t <sub>(SDIS)</sub>   | SDI setup time                              | 5   |     |     | ns   |

| t <sub>(SDIH)</sub>   | SDI hold time                               | 8   |     |     | ns   |

| t <sub>(SDOTOZ)</sub> | SDO active output to tri-state output delay | 0   |     | 17  | ns   |

| t <sub>(SDOEN)</sub>  | SDO tri-state output to active output delay | 0   |     | 21  | ns   |

| t <sub>(SDOTOD)</sub> | SDO output delay                            | 2.5 |     | 30  | ns   |

| t <sub>(CSS)</sub>    | CS setup time                               | 15  |     |     | ns   |

| t <sub>(CSH)</sub>    | CS hold time                                | 15  |     |     | ns   |

| t(CSHIGH)             | CS high time                                | 15  |     |     | ns   |

<sup>(1)</sup> Write operations to the device can be performed at frequencies up to 50MHz.

## **5.10 Switching Characteristics**

at  $T_J$  =  $-40^{\circ}$ C to +125°C,  $AV_{DD}$  = 2.7V to 5.5V,  $V_{IO}$  = 1.7V to  $AV_{DD}$ ,  $V_{REFIN}$  = 2.4V to 5.5V, DAC outputs unloaded, and digital inputs at  $V_{IO}$  or GND

|                       | PARAMETER               | TEST CONDITIONS                                                   | MIN | TYP | MAX | UNIT |  |  |  |  |  |  |

|-----------------------|-------------------------|-------------------------------------------------------------------|-----|-----|-----|------|--|--|--|--|--|--|

| RESET CHARACTERISTICS |                         |                                                                   |     |     |     |      |  |  |  |  |  |  |

| t <sub>AMCRDY</sub>   | Device ready wait time  | Time for valid serial interface access, measured from reset event |     |     | 10  | ms   |  |  |  |  |  |  |

| t <sub>RESET</sub>    | RESET pulse duration    |                                                                   | 20  |     |     | ns   |  |  |  |  |  |  |

| DAC CHARA             | CTERISTICS              |                                                                   |     |     |     |      |  |  |  |  |  |  |

| t <sub>DACCLR</sub>   | DAC clear response time | Time for DAC to begin code change after CLEAR trigger             |     | 50  |     | ns   |  |  |  |  |  |  |

| t <sub>CLRWDTH</sub>  | CLEAR pulse duration    |                                                                   | 100 |     |     | ns   |  |  |  |  |  |  |

| t <sub>LDACWDTH</sub> | LDAC pulse duration     |                                                                   | 100 |     |     | ns   |  |  |  |  |  |  |

# **5.11 Timing Diagrams**

Figure 5-1. I<sup>2</sup>C Timing Diagram

Figure 5-2. SPI Timing Diagram

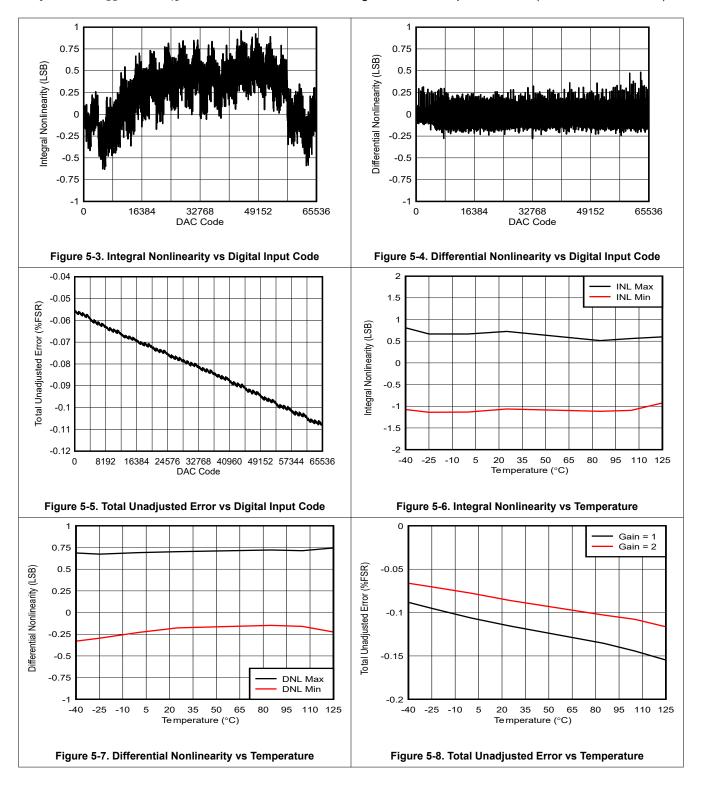

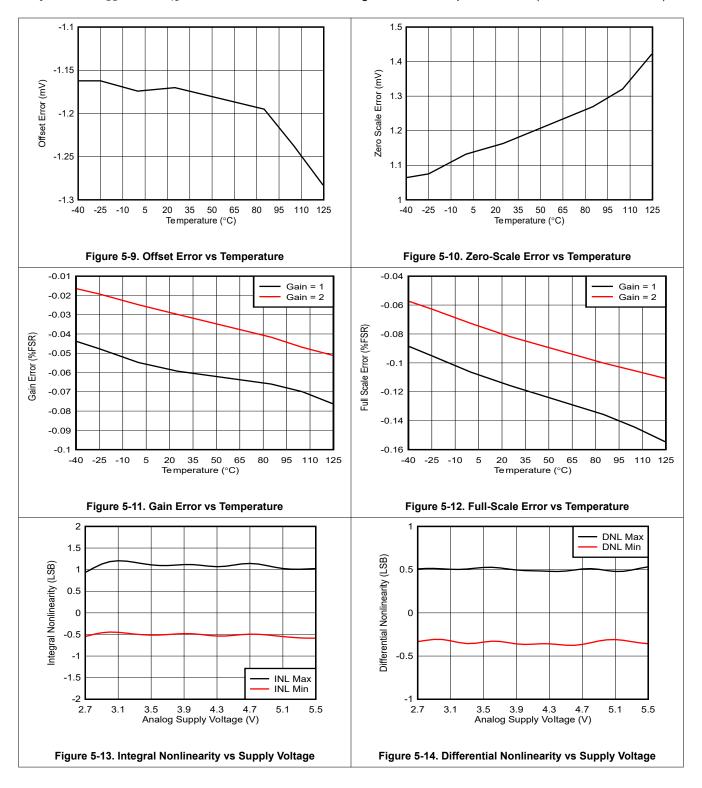

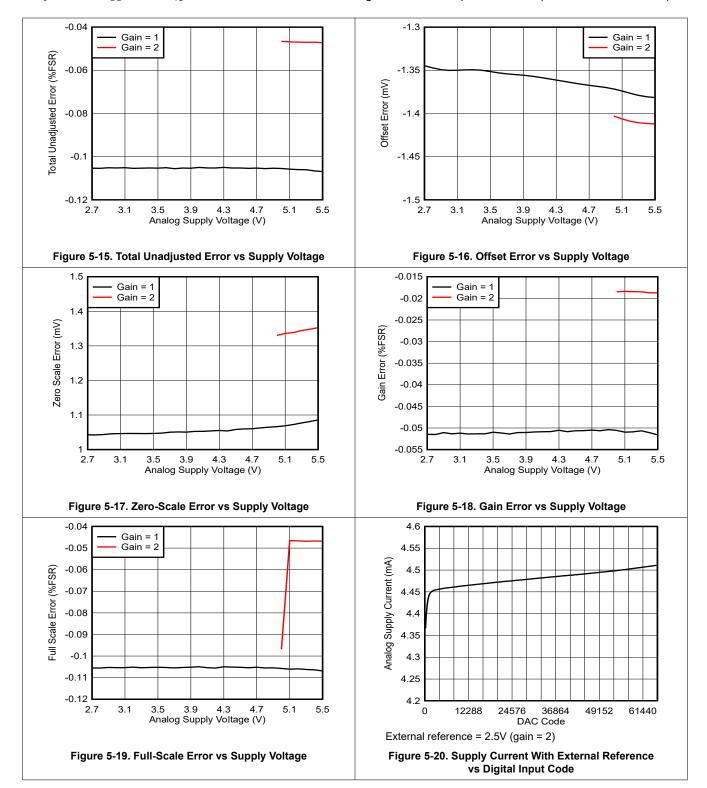

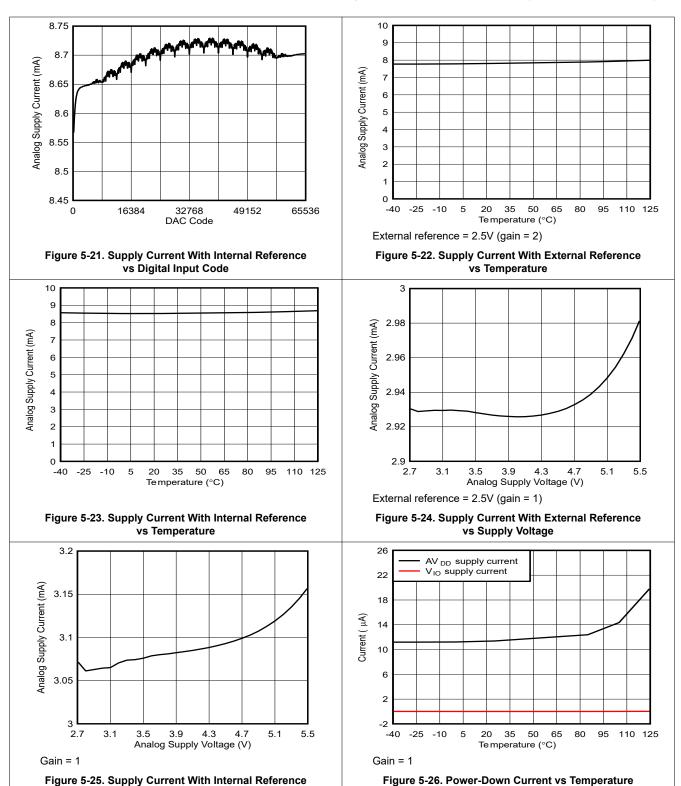

#### **5.12 Typical Characteristics**

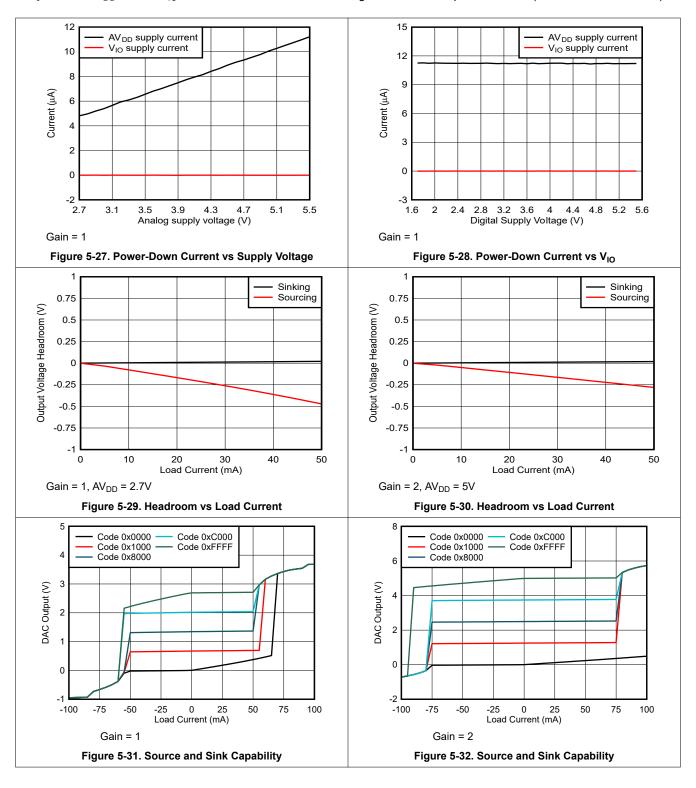

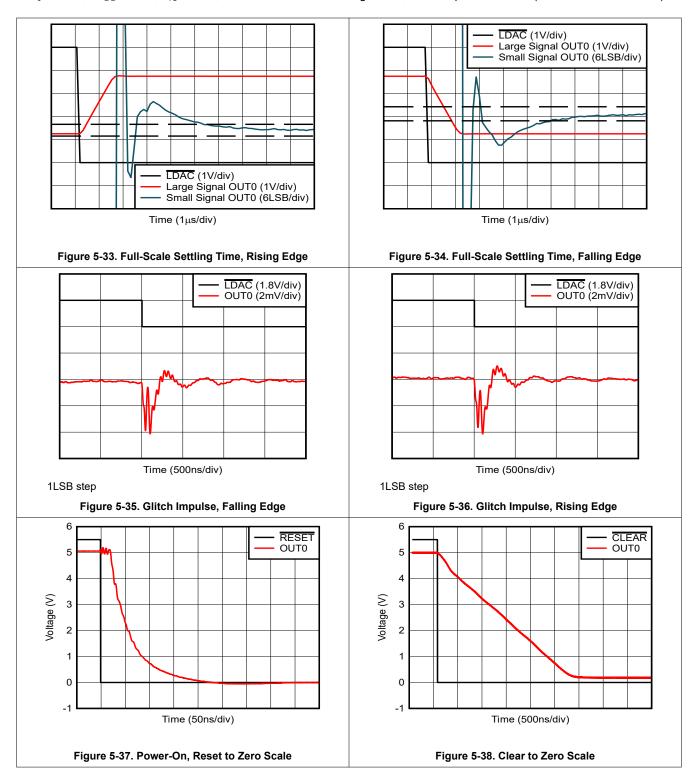

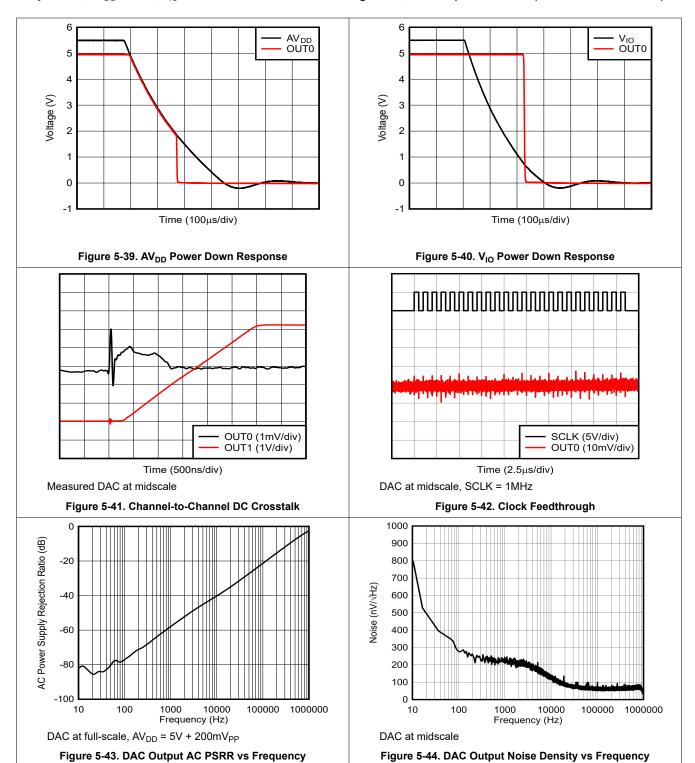

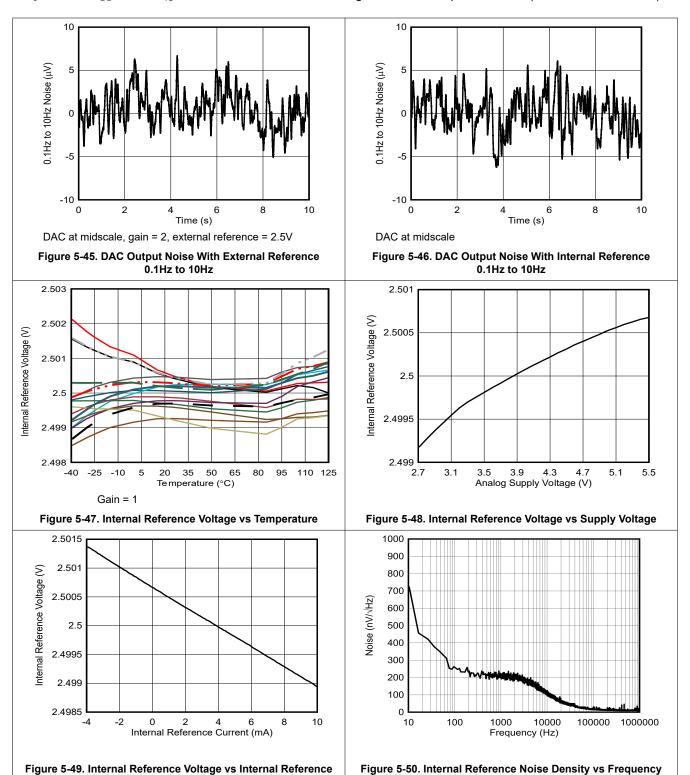

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Submit Document Feedback

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Copyright © 2024 Texas Instruments Incorporated

Submit Document Feedback

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Submit Document Feedback

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

vs Supply Voltage

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Submit Document Feedback

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Submit Document Feedback

at T<sub>J</sub> = 25°C, AV<sub>DD</sub> = 5.5V, V<sub>IO</sub> = 5.5V, internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

Current

at  $T_J = 25$ °C,  $AV_{DD} = 5.5V$ ,  $V_{IO} = 5.5V$ , internal reference = 2.5V, gain = 2, DAC outputs unloaded (unless otherwise noted)

# **6 Detailed Description**

#### 6.1 Overview

The DAC80516 is a low-power, sixteen-channel, buffered voltage-output digital-to-analog converter (DAC) with 16-bit resolution. The DAC80516 includes a 2.5V internal reference and provides user-selectable gain configuration through software, which can be used to set the full-scale output voltage range for groups of four DACs at a time (see also Section 6.3.1.1). The device operates from a single 2.7V to 5.5V supply. Communication to the DAC80516 is performed through a serial interface that supports SPI and I<sup>2</sup>C communication.

The DAC80516 incorporates a power-on-reset circuit that powers up and maintains the DAC outputs at zero scale until a valid code is written to the device.

A clear pin enables a simultaneous update of multiple DAC channels to specified clear values.

#### 6.2 Functional Block Diagram

#### **6.3 Feature Description**

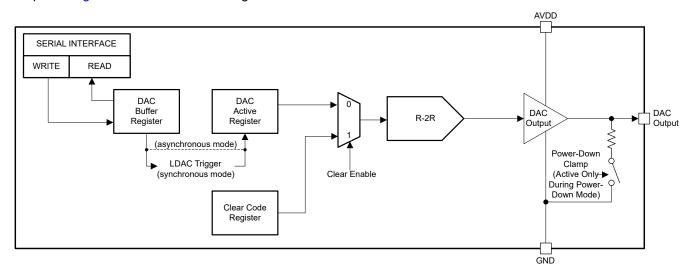

#### 6.3.1 Digital-to-Analog Converter (DAC) Architecture

Each output channel in the DAC80516 consists of an R-2R ladder architecture followed by an output buffer amplifier. Figure 6-1 shows a block diagram of the DAC architecture.

Figure 6-1. DAC80516 DAC Block Diagram

After a reset event, all the DAC registers are set to code 0x0000, the DAC output amplifiers are powered down, and the DAC outputs are clamped to GND. Each DAC output can be independently enabled or disabled through software by writing to the appropriate bit of the PWDWN register. When disabled, the DAC output is clamped to ground via a pull-down resistor.

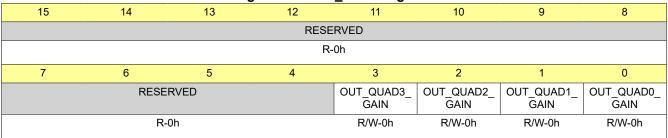

#### 6.3.1.1 DAC Register Structure

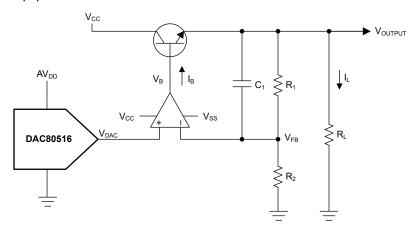

The DAC produces output voltages proportional to a 16-bit input data code. Input data are written to the DAC data register in straight binary format for all output ranges. By writing to the DAC\_GAIN register, the user can configure the maximum full-scale DAC output voltage as either 1 ×  $V_{REF}$  or 2 ×  $V_{REF}$  (maximum of 5V), where  $V_{REF}$  is the internal or external reference input voltage. Section 7.1.5 shows that the gain settings can be configured for QUAD0 (OUT0 through OUT3), QUAD1 (OUT4 through OUT7), QUAD2 (OUT8 through OUT11) and QUAD3 (OUT12 through OUT15); all DAC channels in a QUAD group share the same gain settings.

Data written to the DAC data registers are initially stored in the DAC buffer registers. The transfer of data from the DAC buffer registers to the DAC active registers can be configured to happen immediately (asynchronous mode) or initiated by a DAC trigger signal (synchronous mode). When the DAC active registers are updated, the DAC output channels change to the new values.

By setting the corresponding BCAST\_EN bits in the DAC\_BCAST\_EN register, each DAC can be configured to operate in broadcast mode. When a value is written to the BCAST\_DAC\_DATA register, this value is automatically stored in the buffer and active data registers of all DACs operating in broadcast mode.

Additionally, each DAC has a short circuit detection circuit. The DAC\_STATUS register indicates which DAC channels are presently in short-circuit condition. A global status bit (GDAC\_SC\_STS, in the STATUS register) is the logical OR of all the DAC\_STATUS bits, which can be used to determine if there is at least one channel in the short circuit condition.

## 6.3.1.1.1 DAC Synchronous Operation

The update mode for each DAC channel is determined by the DAC synchronous setting, configured for each DAC by writing to the SYNC\_EN register. In asynchronous mode, a write to the DAC buffer data register results in an immediate update of the DAC active registers on a  $\overline{CS}$  rising edge. In synchronous mode, writing to the DAC buffer data register does not automatically update the DAC active register. Instead, the update occurs only after a DAC trigger signal is generated. A DAC trigger signal can be generated by pulling the  $\overline{LDAC}$  pin low, which updates the active registers of all DAC output channels operating in synchronous mode simultaneously. The  $\overline{LDAC}$  pin does not affect the active registers of channels already configured as asynchronous in the SYNC\_EN register; however all other channels (configured as synchronous in the SYNC\_EN register) operate in asynchronous mode as long as the  $\overline{LDAC}$  pin is held at logic low. A DAC trigger can also be generated through software, by writing to the appropriate LDAC\_OUTn bit in the TRIGGER register. A software trigger updates the active registers of two DAC channels at a time; each bit in the TRIGGER register corresponds to a pair of output channels, and setting a bit to 1 updates both corresponding channels simultaneously.

#### 6.3.1.1.2 DAC Buffer Amplifier

The DAC output buffer amplifiers are capable of rail-to-rail operation, featuring low noise and low drift voltage output. The amplifier outputs are available at the DAC output pins. The maximum DAC output voltage range is limited by the AV<sub>DD</sub> supply.

The high output current of the device provides good slewing characteristics even with large capacitive loads. To estimate the positive and negative slew rates for large capacitive loads, divide the source and sink short-circuit current value by the capacitor.

#### 6.3.1.1.3 DAC Transfer Function

The DAC transfer function is given by Equation 1.

$$V_{DAC} = \left(\frac{DACIN}{2^{16}}\right) \times FSR \tag{1}$$

where

- DACIN = decimal equivalent of the binary code loaded to the DAC register. DACIN range = 0 to 2<sup>16</sup> 1.

- FSR = DAC full-scale output for the selected output range. FSR is 2.5V for the 0V to 2.5V range, and 5V for the 0V to 5V range.

The DAC output spans the voltage ranges shown in Table 6-1.

Table 6-1. DAC Data Format

| DAC DATA            | REGISTER | DAC OUTPUT     | VOLTAGE (V)      |

|---------------------|----------|----------------|------------------|

| BINARY              | HEX      | 0V TO 5V RANGE | 0V TO 2.5V RANGE |

| 0000 0000 0000 0000 | 0000     | 0              | 0                |

| 0000 0000 0000 0001 | 0001     | 0.000076       | 0.000038         |

| 1000 0000 0000 0000 | 8000     | 2.5            | 1.25             |

| 1111 1111 1111 1110 | FFFE     | 4.999847       | 2.499924         |

| 1111 1111 1111 1111 | FFFF     | 4.999924       | 2.499962         |

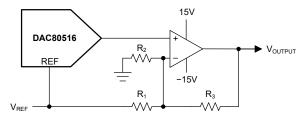

#### 6.3.2 Internal Reference

The DAC80516 includes a 2.5V precision band-gap reference enabled by default. Operation from an external reference is supported by disabling the internal reference, by writing to the REF\_PWDWN bit in the GEN CONFIG register. The internal reference is externally available at the REF pin.

A minimum 150nF capacitor is recommended between the reference output and GND for noise filtering.

#### 6.3.3 Power-On Reset (POR)

The DAC80516 provides a power-on reset (POR) function. After start-up, when the  $AV_{DD}$  and  $V_{IO}$  supplies have been established, a POR is issued to so that the device initializes correctly (see also Section 8.3). The DAC80516 requires 5ms to 10ms to initialize the serial interface after a POR; therefore, wait at least 10ms after start-up to communicate with the device.

During operation, the following three conditions can trigger a reset:

- 1. AV<sub>DD</sub> or V<sub>IO</sub> decrease to less than the recommended minimum operating value (by at least 200mV)

- 2. A value of 0xA (hexadecimal) is written to the SOFT\_RST field in the TRIGGER register

- 3. The RESET pin of the device is pulled to logic 0, for at least 20ns. As long as the pin is held at logic 0, the device remains in a powered-down state until the pin is set to logic 1 (at which time, the device performs initialization of the serial interface again).

#### **6.4 Device Functional Modes**

#### 6.4.1 Clear Mode

Each DAC can be set to enter a clear state using either hardware or software. When a DAC enters the clear state, the DAC is loaded with the data stored in the corresponding CLEAR\_CODE register (code 0 by default) and the output is set to the corresponding voltage level.

The DAC buffer and active registers do not change when the DACs enter the clear state, which enables the DAC to return to the operating point prior to the clear event. The DAC buffer and active registers can also be updated while the DAC is in clear state, thus allowing the DAC to output a new value upon return to normal operation. When the DAC exits the clear state, the DAC is immediately loaded with the data in the active register, and the DAC output channel is set back to the corresponding level to restore operation.

By writing to the appropriate bits in the CLEAR register, each DAC can be programmed to enter or exit the clear state. Each DAC can also be forced to enter a clear state through the FLEXIO pin, when configured as an active-low CLEAR pin. This configuration is done by setting the FLEXIO\_FUNC bit in the GEN\_CONFIG register (by default, this bit is 0, and FLEXIO acts as a general purpose input-output pin). By default, each DAC output is automatically cleared when the CLEAR pin is asserted to a logic-low level, unless the appropriate bit in the CLEAR\_PIN\_MASK register is set. After the DAC leaves the clear state, the DAC is reloaded with the contents of the active register and the DAC output channel updates accordingly.

The device also allows user to set a common clear code for each DAC, which can be done by writing to the BCAST\_CLR\_DATA register. The value stored in this register is written to the CLEAR\_CODE registers of all DACs operating in broadcast mode (determined by the appropriate bit setting in the BCAST\_EN register), which can be used to clear multiple DACs channels to the same code simultaneously.

If a DAC channel is in a power-down state for any reason, any clear commands are ignored on the DAC until the channel exits the power-down state.

#### 6.5 Programming

The device communicates with the system controller through a serial interface, which supports either an  $I^2C$ -compatible two-wire bus, or an SPI-compatible bus. The device includes a robust mechanism that detects between an SPI-compatible or  $I^2C$ -compatible controller, and automatically configures the interface accordingly. The interface detection mechanism operates at start-up, thus preventing protocol change during normal operation.

The register map addresses range from 0x00 to 0x32, enabling access of bits within each respective register (see Section 7 for additional details).

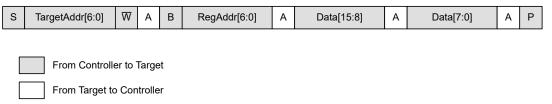

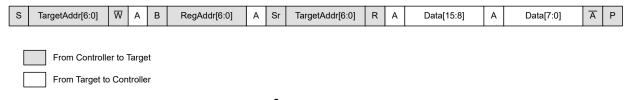

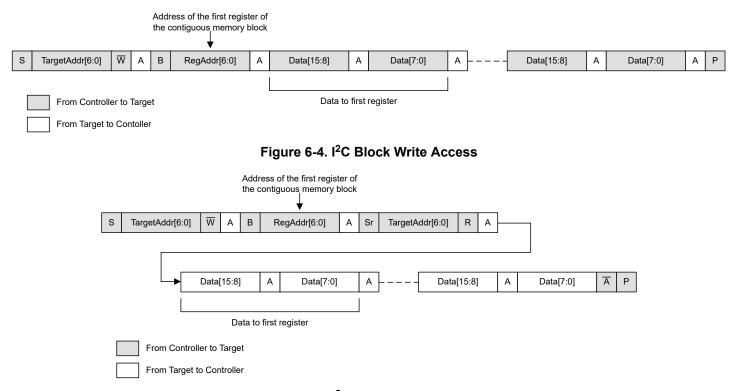

#### 6.5.1 I<sup>2</sup>C Serial Interface

In I<sup>2</sup>C mode, the device operates only as a target device on the two-wire bus. Connections to either bus are made using the open-drain I/O lines, SDA and SCL. The SDA and SCL pins feature integrated spike suppression filters and Schmitt triggers to minimize the effects of input spikes and bus noise. The device supports the transmission protocol for fast mode as well as fast mode plus. All data bytes are transmitted MSB first.

#### 6.5.1.1 I<sup>2</sup>C Bus Overview

The device is I<sup>2</sup>C compatible. In I<sup>2</sup>C protocol, the device that initiates the transfer is called a *controller*, and a device controlled by the controller is called a *target*. The bus must be controlled by a controller device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions.

To address a specific device, a START condition is initiated. A START condition is indicated by pulling the data line (SDA) from a high-to-low logic level while SCL is high. All targets on the bus receive the target address byte, with the last bit indicating whether a read or write operation is intended. During the ninth clock pulse, the target being addressed responds to the controller by generating an acknowledge bit and pulling SDA low.

Data transfer is then initiated and sent over eight clock pulses followed by an acknowledge bit. During data transfer, SDA must remain stable while SCL is high because any change in SDA while SCL is high is interpreted as a control signal.

After all data have been transferred, the controller generates a STOP condition. A STOP condition is indicated by pulling SDA from low to high, while SCL is high.

#### 6.5.1.2 I<sup>2</sup>C Bus Definitions

The device is  $I^2C$ -compatible and the bus definitions are listed in Table 6-2.

# Table 6-2. I<sup>2</sup>C Symbol Set

| CONDITION              | SYMBOL         | SOURCE            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                     |

|------------------------|----------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START                  | S              | Controller        | Begins all bus transactions. A change in the state of the SDA line, from high to low, while the SCL line is high, defines a START condition. Each data transfer initiates with a START condition                                                                                                                                                |

| STOP                   | Р              | Controller        | Terminates all transactions and resets bus. A change in the state of the SDA line from low to high while the SCL line is high defines a STOP condition. Each data transfer terminates with a repeated START or STOP condition.                                                                                                                  |