DAC63204, DAC53204, DAC43204

SLASEX3A - MARCH 2021 - REVISED DECEMBER 2021

# DACx3204 12-Bit, 10-Bit, and 8-Bit, Quad Voltage and Current Output Smart DACs With Auto-Detected I<sup>2</sup>C, PMBus<sup>™</sup>, or SPI Interface

### 1 Features

- Programmable voltage or current outputs with flexible configuration:

- Voltage outputs:

- 1 LSB INL and DNL (10-bit and 8-bit)

- Gains of 1x, 1.5x, 2x, 3x, and 4x

- Current outputs:

- 1 LSB INL and DNL (8-bit)

- ±25 μA, ±50 μA, ±125 μA, ±250 μA output range options

- Programmable comparator mode for all channels

- High-impedance output when VDD is off

- High-impedance and resistive pulldown powerdown modes

- 50-MHz SPI-compatible interface

- Automatically detected I<sup>2</sup>C, PMBus<sup>™</sup>, or SPI interface

- 1.62-V V<sub>IH</sub> with V<sub>DD</sub> = 5.5 V

- General-purpose input/output (GPIO) configurable as multiple functions

- Predefined waveform generation: sine wave, triangular, sawtooth

- User-programmable nonvolatile memory (NVM)

- Internal, external, or power-supply as reference

- Wide operating range:

- Power supply: 1.8 V to 5.5 V

- Temperature range: –40°C to +125°C

- Tiny package: 16-pin WQFN (3 mm × 3 mm)

# 2 Applications

- Rack server

- Optical module

- Inter-DC interconnect (metro)

- High performance computing

- Standard notebook PC

## 3 Description

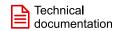

The 12-bit DAC63204, 10-bit DAC53204, and 8-bit DAC43204 (DACx3204) are a pin-compatible family of quad-channel, buffered, voltage-output and currentoutput smart digital-to-analog converters (DACs). These DACx3204 support Hi-Z power-down mode and Hi-Z output during power-off condition. The DAC outputs provide a force-sense option for use as a programmable comparator and current sink. The multifunction GPIO, function generation, and NVM enable these smart DACs for processorless applications and design reuse. These devices automatically detect I<sup>2</sup>C, PMBus, and SPI interfaces and contain an internal reference.

The feature set combined with the tiny package and low power make these smart DACs an excellent choice for applications such as voltage margining and scaling, dc set-point for biasing and calibration, and waveform generation.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |  |  |

|-------------|------------------------|-------------------|--|--|

| DACx3204    | WQFN (16)              | 3.00 mm x 3.00 mm |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

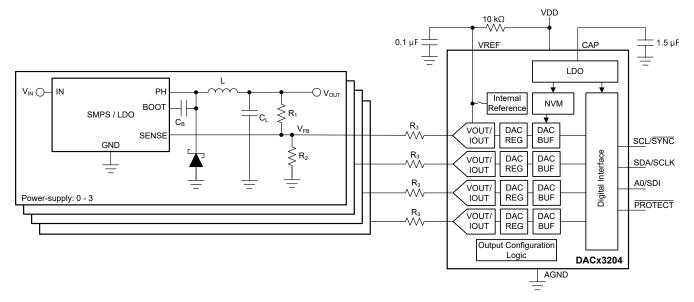

Voltage Margining and Scaling Using the DACx3204

## **Table of Contents**

| 1 Features1                                                 | 6.19 Typical Characteristics: Comparator              | .23  |

|-------------------------------------------------------------|-------------------------------------------------------|------|

| 2 Applications1                                             | 6.20 Typical Characteristics: General                 | . 24 |

| B Description1                                              | 7 Detailed Description                                | . 25 |

| 4 Revision History2                                         | 7.1 Overview                                          | .25  |

| 5 Pin Configuration and Functions3                          | 7.2 Functional Block Diagram                          | .25  |

| Specifications4                                             | 7.3 Feature Description                               | 26   |

| 6.1 Absolute Maximum Ratings4                               | 7.4 Device Functional Modes                           | 28   |

| 6.2 ESD Ratings4                                            | 7.5 Programming                                       | . 44 |

| 6.3 Recommended Operating Conditions4                       | 7.6 Register Map                                      | 52   |

| 6.4 Thermal Information4                                    | 8 Application and Implementation                      |      |

| 6.5 Electrical Characteristics: Voltage Output5             | 8.1 Application Information                           | . 70 |

| 6.6 Electrical Characteristics: Current Output7             | 8.2 Typical Application                               | . 70 |

| 6.7 Electrical Characteristics: Comparator Mode8            | 9 Power Supply Recommendations                        |      |

| 6.8 Electrical Characteristics: General9                    | 10 Layout                                             |      |

| 6.9 Timing Requirements: I <sup>2</sup> C Standard Mode10   | 10.1 Layout Guidelines                                | . 73 |

| 6.10 Timing Requirements: I <sup>2</sup> C Fast Mode10      | 10.2 Layout Example                                   | . 73 |

| 6.11 Timing Requirements: I <sup>2</sup> C Fast Mode Plus10 | 11 Device and Documentation Support                   | 74   |

| 6.12 Timing Requirements: SPI Write Operation 11            | 11.1 Documentation Support                            | . 74 |

| 6.13 Timing Requirements: SPI Read and Daisy                | 11.2 Receiving Notification of Documentation Updates. | .74  |

| Chain Operation (FSDO = 0)11                                | 11.3 Support Resources                                | . 74 |

| 6.14 Timing Requirements: SPI Read and Daisy                | 11.4 Trademarks                                       | . 74 |

| Chain Operation (FSDO = 1)11                                | 11.5 Electrostatic Discharge Caution                  | . 74 |

| 6.15 Timing Requirements: GPIO12                            | 11.6 Glossary                                         | . 74 |

| 6.16 Timing Diagrams12                                      | 12 Mechanical, Packaging, and Orderable               |      |

| 6.17 Typical Characteristics: Voltage Output14              | Information                                           | . 74 |

| 6.18 Typical Characteristics: Current Output19              |                                                       |      |

|                                                             |                                                       |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Revision \* (April 2021) to Revision A (December 2021)

Page

• Changed DACx3204 devices from advanced information (preview) to production data (active)......1

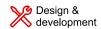

# **5 Pin Configuration and Functions**

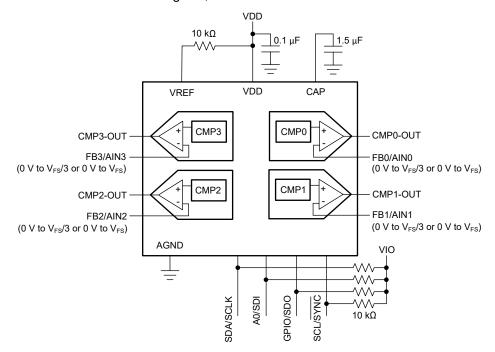

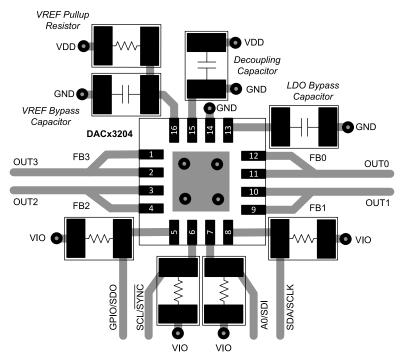

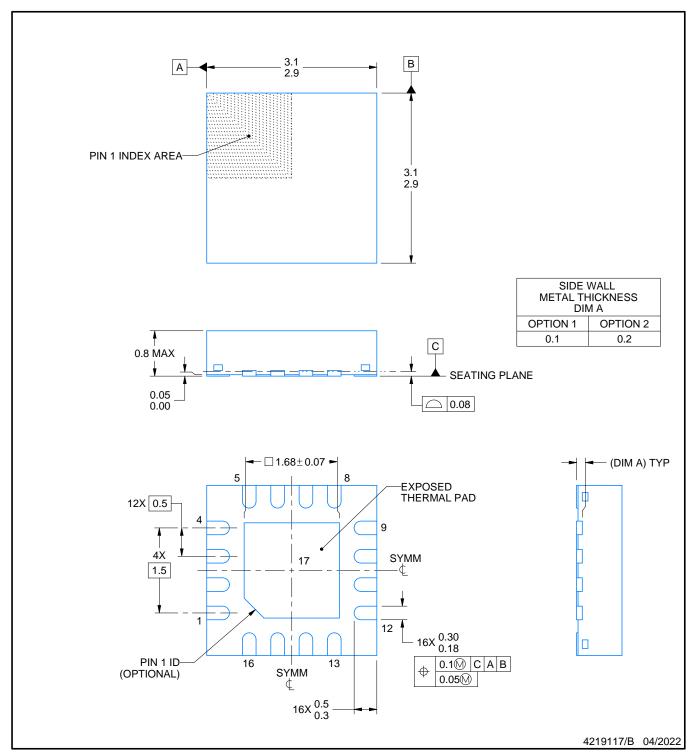

Figure 5-1. RTE Package, 16-pin WQFN, Top View

**Table 5-1. Pin Functions**

|     | PIN         | TVDE         | DECORPORTION                                                                                                                                                                                                                                                                                |

|-----|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME TYPE   |              | DESCRIPTION                                                                                                                                                                                                                                                                                 |

| 1   | FB3         | Input        | Voltage feedback pin for channel 3. In voltage-output mode, connect to OUT3 for closed-loop amplifier output. In current-output mode, keep the FB3 pin unconnected to minimize leakage current.                                                                                             |

| 2   | OUT3        | Output       | Analog output voltage from DAC channel 3.                                                                                                                                                                                                                                                   |

| 3   | OUT2        | Output       | Analog output voltage from DAC channel 2.                                                                                                                                                                                                                                                   |

| 4   | FB2         | Input        | Voltage feedback pin for channel 2. In voltage-output mode, connect to OUT2 for closed-loop amplifier output. In current-output mode, keep the FB2 pin unconnected to minimize leakage current.                                                                                             |

| 5   | GPIO/SDO    | Input/Output | General-purpose input/output configurable as LDAC, PD, PROTECT, RESET, SDO, and STATUS. For STATUS and SDO, connect the pin to the IO voltage with an external pullup resistor. If unused, connect the GPIO pin to VDD or AGND using an external resistor. This pin can ramp up before VDD. |

| 6   | SCL/SYNC    | Output       | I <sup>2</sup> C serial interface clock or SPI chip select input. This pin must be connected to the IO voltage using an external pullup resistor. This pin can ramp up before VDD.                                                                                                          |

| 7   | A0/SDI      | Input        | Address configuration pin for I <sup>2</sup> C or serial data input for SPI. For A0, connect this pin to VDD, AGND, SDA, or SCL for address configuration (Section 7.5.2.2.1). For SDI, this pin need not be pulled up or pulled down. This pin can ramp up before VDD.                     |

| 8   | SDA/SCLK    | Input/Output | Bidirectional I <sup>2</sup> C serial data bus or SPI clock input. This pin must be connected to the IO voltage using an external pullup resistor in the I <sup>2</sup> C mode. This pin can ramp up before VDD.                                                                            |

| 9   | FB1         | Input        | Voltage feedback pin for channel 1. In voltage-output mode, connect to OUT1 for closed-loop amplifier output. In current-output mode, keep the FB1 pin unconnected to minimize leakage current.                                                                                             |

| 10  | OUT1        | Output       | Analog output voltage from DAC channel 1.                                                                                                                                                                                                                                                   |

| 11  | OUT0        | Output       | Analog output voltage from DAC channel 0.                                                                                                                                                                                                                                                   |

| 12  | FB0         | Input        | Voltage feedback pin for channel 0. In voltage-output mode, connect to OUT0 for closed-loop amplifier output. In current-output mode, keep the FB0 pin unconnected to minimize leakage current.                                                                                             |

| 13  | CAP         | Power        | External bypass capacitor for the internal LDO. Connect a capacitor (approximately 1.5 μF) between CAP and AGND.                                                                                                                                                                            |

| 14  | AGND        | Ground       | Ground reference point for all circuitry on the device.                                                                                                                                                                                                                                     |

| 15  | VDD         | Power        | Supply voltage.                                                                                                                                                                                                                                                                             |

| 16  | VREF        | Power        | External reference input. Connect a capacitor (approximately 0.1 µF) between VREF and AGND. Use a pullup resistor to VDD when the external reference is not used. This pin must not ramp up before VDD. In case an external reference is used, make sure the reference ramps up after VDD.  |

| _   | Thermal Pad | Ground       | Connect the thermal pad to AGND.                                                                                                                                                                                                                                                            |

## **6 Specifications**

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                  |                                                          | MIN  | MAX                   | UNIT |

|------------------|----------------------------------------------------------|------|-----------------------|------|

| $V_{DD}$         | Supply voltage, V <sub>DD</sub> to A <sub>GND</sub>      | -0.3 | 6                     | V    |

|                  | Digital inputs to A <sub>GND</sub>                       | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | CAP to A <sub>GND</sub>                                  | -0.3 | 1.65                  | V    |

|                  | V <sub>FBX</sub> to A <sub>GND</sub>                     | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | V <sub>OUTX</sub> to A <sub>GND</sub>                    | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>REF</sub> | External reference, V <sub>REF</sub> to A <sub>GND</sub> | -0.3 | V <sub>DD</sub> + 0.3 | V    |

|                  | Current into any pin except the OUTx pins                | -10  | 10                    | mA   |

| TJ               | Junction temperature                                     | -40  | 150                   | °C   |

| T <sub>stg</sub> | Storage temperature                                      | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

## 6.2 ESD Ratings

|                    |               |                                                                                 | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | ±2000 | \/   |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | ±500  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                                             | MIN  | NOM MAX  | UNIT |

|------------------|-------------------------------------------------------------|------|----------|------|

| $V_{DD}$         | Positive supply voltage to ground (A <sub>GND</sub> )       | 1.7  | 5.5      | V    |

| $V_{REF}$        | External reference to ground (A <sub>GND</sub> )            | 1.7  | $V_{DD}$ | V    |

| V <sub>IH</sub>  | Digital input high voltage, 1.7 V < V <sub>DD</sub> ≤ 5.5 V | 1.62 |          | V    |

| V <sub>IL</sub>  | Digital input low voltage                                   |      | 0.4      | V    |

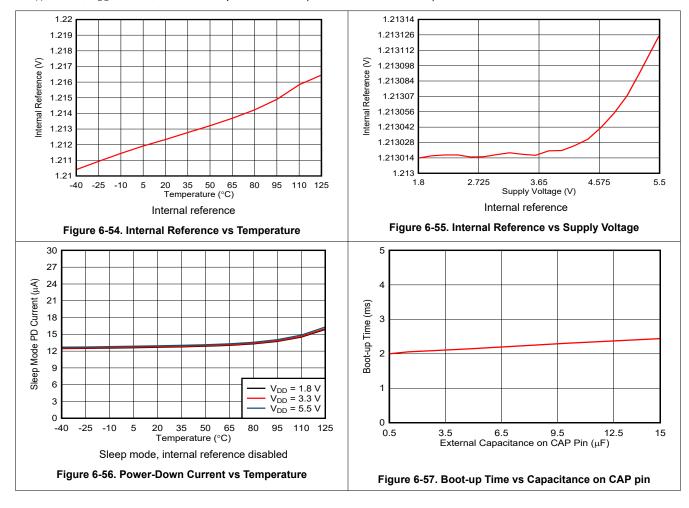

| C <sub>CAP</sub> | External capacitor on CAP pin                               | 0.5  | 15       | μF   |

| T <sub>A</sub>   | Ambient temperature                                         | -40  | 125      | °C   |

### 6.4 Thermal Information

|                        |                                              | DACx3204   |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RTE (WQFN) | UNIT |

|                        |                                              | 16 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 49         | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 50         | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 24.1       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 1.1        | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 24.1       | °C/W |

| R <sub>θJC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 8.7        | °C/W |

<sup>(1)</sup> For information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.5 Electrical Characteristics: Voltage Output

all minimum/maximum specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C and typical specifications at  $T_A$  = 25°C, 1.7 V ≤  $V_{DD}$  ≤ 5.5 V, DAC reference tied to VDD, gain = 1x, DAC output pin (OUT) loaded with resistive load ( $R_L$  = 5 k $\Omega$  to AGND) and capacitive load ( $R_L$  = 200 pF to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|      | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                           | MIN   | TYP     | MAX      | UNIT     |

|------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|----------|----------|

| STAT | TIC PERFORMANCE                                         |                                                                                                                                                                           |       |         |          |          |

|      |                                                         | DAC63204                                                                                                                                                                  | 12    |         |          |          |

|      | Resolution                                              | DAC53204                                                                                                                                                                  | 10    |         |          | Bits     |

|      |                                                         | DAC43204                                                                                                                                                                  | 8     |         |          |          |

|      |                                                         | DAC63204                                                                                                                                                                  | -4    |         | 4        |          |

| NL   | Integral nonlinearity <sup>(1)</sup>                    | DAC53204, DAC43204                                                                                                                                                        | -1    |         | 1        | LSB      |

| DNL  | Differential nonlinearity <sup>(1)</sup>                |                                                                                                                                                                           | -1    |         | 1        | LSB      |

|      |                                                         | Code 0d into DAC, external reference, V <sub>DD</sub> = 5.5 V                                                                                                             |       | 6       | 12       |          |

|      | Zero-code error <sup>(4)</sup>                          | Code 0d into DAC, internal V <sub>REF</sub> , gain = 4x,<br>V <sub>DD</sub> = 5.5 V                                                                                       |       | 6       | 15       | mV       |

|      | Zero-code error temperature coefficient <sup>(4)</sup>  | Code 0d into DAC                                                                                                                                                          |       | ±10     |          | μV/°C    |

|      | Offset error <sup>(4)</sup> (6)                         | $1.7~\text{V} \leq \text{V}_{\text{DD}} < 2.7~\text{V}$ , FBx pin shorted to OUTx, DAC code: 32d for 12-bit resolution, 8d for 10-bit resolution, 2d for 8-bit resolution | -0.75 | 0.3     | 0.75     | %FSR     |

|      | Oliset ellol VVV                                        | 2.7 V ≤ V <sub>DD</sub> ≤ 5.5 V, FBx pin shorted to OUTx,<br>DAC code: 32d for 12-bit resolution, 8d for 10-bit<br>resolution, 2d for 8-bit resolution                    | -0.5  | 0.25    | 0.5      | /0F3IX   |

|      | Offset-error temperature coefficient <sup>(4)</sup>     | FBx pin shorted to OUTx, DAC code: 32d for 12-bit resolution, 8d for 10-bit resolution, 2d for 8-bit resolution                                                           |       | ±0.0003 |          | %FSR/°C  |

|      | Gain error <sup>(4)</sup>                               | Between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution, 2d to 254d for 8-bit resolution                                           | -0.5  | 0.25    | 0.5      | %FSR     |

|      | Gain-error temperature coefficient <sup>(4)</sup>       | Between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution, 2d to 254d for 8-bit resolution                                           |       | ±0.0008 |          | %FSR/°C  |

|      | Full-scale error <sup>(4)</sup> (6)                     | 1.7 V ≤ V <sub>DD</sub> < 2.7 V, DAC at full-scale                                                                                                                        | -1    |         | 1        | %FSR     |

|      | Full-scale effort (*/ (*)                               | 2.7 V ≤ V <sub>DD</sub> ≤ 5.5 V, DAC at full-scale                                                                                                                        | -0.5  |         | 0.5      | 70 F S K |

|      | Full-scale-error temperature coefficient <sup>(4)</sup> | DAC at full-scale                                                                                                                                                         |       | ±0.0008 |          | %FSR/°C  |

| DUT  | PUT                                                     |                                                                                                                                                                           |       |         |          |          |

|      | Output voltage                                          | Reference tied to V <sub>DD</sub>                                                                                                                                         | 0     |         | $V_{DD}$ | V        |

| շլ   | Capacitive load <sup>(2)</sup>                          | R <sub>L</sub> = infinite, phase margin = 30°                                                                                                                             |       |         | 200      |          |

| ·L   | Capacitive load                                         | Phase margin = 30°                                                                                                                                                        |       |         | 1000     | pF       |

|      |                                                         | $V_{DD}$ = 1.7 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                         |       | 15      |          |          |

|      | Short-circuit current                                   | $V_{DD}$ = 2.7 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                         |       | 50      |          | mA       |

|      |                                                         | $V_{DD}$ = 5.5 V, full-scale output shorted to $A_{GND}$ or zero-scale output shorted to $V_{DD}$                                                                         |       | 60      |          |          |

# 6.5 Electrical Characteristics: Voltage Output (continued)

all minimum/maximum specifications at  $T_A = -40^{\circ}\text{C}$  to +125°C and typical specifications at  $T_A = 25^{\circ}\text{C}$ , 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, DAC reference tied to VDD, gain = 1x, DAC output pin (OUT) loaded with resistive load ( $R_L = 5 \text{ k}\Omega$  to AGND) and capacitive load ( $C_L = 200 \text{ pF}$  to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|                 | PARAMETER                                          | TEST CONDITIONS                                                                                                                                                                                                                   | MIN | TYP  | MAX | UNIT               |

|-----------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------------------|

|                 |                                                    | To V <sub>DD</sub> (DAC output unloaded, internal reference = 1.21 V), V <sub>DD</sub> ≥ 1.21 V × gain + 0.2 V                                                                                                                    | 0.2 |      |     | V                  |

|                 | Output-voltage headroom <sup>(2)</sup>             | To $V_{DD}$ and $A_{GND}$ (DAC output unloaded, external reference at $V_{DD}$ , gain = 1x, the VREF pin is not shorted to VDD)                                                                                                   | 0.8 |      |     |                    |

|                 |                                                    | To $V_{DD}$ and $A_{GND}$ ( $I_{LOAD}$ = 10 mA at $V_{DD}$ = 5.5 V, $I_{LOAD}$ = 3 mA at $V_{DD}$ = 2.7 V, $I_{LOAD}$ = 1 mA at $V_{DD}$ = 1.8 V), external reference at $V_{DD}$ , gain = 1x, the VREF pin is not shorted to VDD | 10  |      |     | %FSR               |

| Z <sub>O</sub>  | V <sub>FB</sub> dc output impedance <sup>(3)</sup> | DAC output enabled, internal reference (gain = 1.5x or 2x) or external reference at $V_{DD}$ (gain = 1x), the VREF pin is not shorted to VDD                                                                                      | 400 | 500  | 600 | kΩ                 |

|                 |                                                    | DAC output enabled, internal V <sub>REF</sub> , gain = 3x or 4x                                                                                                                                                                   | 325 | 400  | 485 |                    |

|                 | Power supply rejection ratio (dc)                  | Internal $V_{REF}$ , gain = 2x, DAC at midscale, $V_{DD}$ = 5 V ±10%                                                                                                                                                              |     | 0.25 |     | mV/V               |

| DYN             | AMIC PERFORMANCE                                   |                                                                                                                                                                                                                                   |     |      |     |                    |

|                 | Output valtage cettling time                       | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, V <sub>DD</sub> = 5.5 V                                                                                                                                                 |     | 20   |     |                    |

| sett            | Output voltage settling time                       | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 10%FSR, V <sub>DD</sub> = 5.5 V, internal V <sub>REF</sub> , gain = 4x                                                                                                          |     | 25   |     | μs                 |

|                 | Slew rate                                          | V <sub>DD</sub> = 5.5 V                                                                                                                                                                                                           |     | 0.3  |     | V/µs               |

|                 | Power-on glitch magnitude                          | At startup (DAC output disabled)                                                                                                                                                                                                  |     | 75   |     | mV                 |

|                 | Fower-on gillon magnitude                          | At startup (DAC output disabled), $R_L = 100 \text{ k}\Omega$                                                                                                                                                                     |     | 200  |     | IIIV               |

|                 | Output-enable glitch magnitude                     | DAC output disabled to enabled (DAC registers at zero scale), $R_L$ = 100 $k\Omega$                                                                                                                                               |     | 250  |     | mV                 |

|                 | Output poigo voltago (poak to                      | f = 0.1 Hz to 10 Hz, DAC at midscale, V <sub>DD</sub> = 5.5 V                                                                                                                                                                     |     | 50   |     |                    |

| V <sub>n</sub>  | Output noise voltage (peak to peak)                | Internal $V_{REF}$ , gain = 4x, f = 0.1 Hz to 10 Hz, DAC at midscale, $V_{DD}$ = 5.5 V                                                                                                                                            |     | 90   |     | $\mu V_{PP}$       |

|                 |                                                    | f = 1 kHz, DAC at midscale, V <sub>DD</sub> = 5.5 V                                                                                                                                                                               |     | 0.35 |     |                    |

|                 | Output noise density                               | Internal V <sub>REF,</sub> gain = 4x, f = 1 kHz, DAC at midscale, V <sub>DD</sub> = 5.5 V                                                                                                                                         |     | 0.9  |     | μV/√ <del>Hz</del> |

|                 | Power supply rejection ratio (ac) <sup>(3)</sup>   | Internal V <sub>REF</sub> , gain = 4x, 200-mV 50-Hz or 60-Hz sine wave superimposed on power supply voltage, DAC at midscale                                                                                                      |     | -68  |     | dB                 |

|                 | Code change glitch impulse                         | ±1 LSB change around midscale (including feedthrough)                                                                                                                                                                             |     | 10   |     | nV-s               |

|                 | Code change glitch impulse magnitude               | ±1 LSB change around midscale (including feedthrough)                                                                                                                                                                             |     | 15   |     | mV                 |

| POW             | /ER                                                |                                                                                                                                                                                                                                   |     |      |     |                    |

| I <sub>DD</sub> | Current flowing into VDD <sup>(4)</sup> (5)        | Normal operation, DACs at full scale, digital pins static, external reference at V <sub>DD</sub> but the VREF pin is not shorted to VDD                                                                                           |     | 150  |     | μΑ/ch              |

<sup>(1)</sup> Measured with DAC output unloaded. For external reference and internal reference V<sub>DD</sub> ≥ 1.21 x gain + 0.2 V, between end-point codes: 32d to 4064d for 12-bit resolution, 8d to 1016d for 10-bit resolution, 2d to 254d for 8-bit resolution.

<sup>(2)</sup> Specified by design and characterization, not production tested.

<sup>(3)</sup> Specified with 200-mV headroom with respect to reference value when internal reference is used.

<sup>(4)</sup> Measured with DAC output unloaded.

<sup>(5)</sup> The total power consumption is calculated by I<sub>DD</sub> x (total number of channels powered on) + (sleep-mode current).

<sup>(6)</sup> When a DAC channel is configured in IOUT mode for long term and then switched to VOUT mode, the VOUT mode can show parametric drift.

## **6.6 Electrical Characteristics: Current Output**

all minimum/maximum specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C and typical specifications at  $T_A$  = 25°C, 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, ±250 $\mu$ A output range, and digital inputs at VDD or AGND (unless otherwise noted)

|                   | PARAMETER                                           | TEST CONDITIONS                                                                                                                              | MIN | TYP  | MAX | UNIT               |

|-------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------------------|

| STAT              | IC PERFORMANCE                                      |                                                                                                                                              |     |      |     |                    |

|                   | Resolution                                          |                                                                                                                                              | 8   |      |     | Bits               |

| INL               | Integral nonlinearity                               | DAC codes between 0d and 255d                                                                                                                | -1  |      | 1   | LSB                |

| DNL               | Differential nonlinearity                           | DAC codes between 0d and 255d                                                                                                                | -1  |      | 1   | LSB                |

|                   | Offset error                                        | DAC at midscale                                                                                                                              |     | ±1   |     | %FSR               |

|                   | Gain error                                          | DAC codes between 0d and 255d                                                                                                                |     | ±1.3 |     | %FSR               |

| OUTI              | PUT                                                 |                                                                                                                                              |     |      |     |                    |

|                   | Output compliance voltage <sup>(1)</sup>            | To V <sub>DD</sub> and A <sub>GND</sub>                                                                                                      | 400 |      |     | mV                 |

| Zo                | I <sub>OUT</sub> dc output impedance <sup>(2)</sup> | DAC at midscale, DAC output kept at V <sub>DD</sub> /2                                                                                       | 60  |      |     | ΜΩ                 |

|                   | Power supply rejection ratio (dc)                   | DAC at midscale, all bipolar ranges, V <sub>DD</sub> changed from 4.5V to 5.5V                                                               |     | 0.23 |     | LSB/V              |

| DYN               | AMIC PERFORMANCE                                    |                                                                                                                                              |     |      |     |                    |

| t <sub>sett</sub> | Output current settling time                        | 1/4 to 3/4 scale and 3/4 to 1/4 scale settling to 1 LSB at 8-bit resolution, $V_{DD}$ = 5.5 V, common-mode voltage at OUTx pin is $V_{DD}/2$ |     | 60   |     | μs                 |

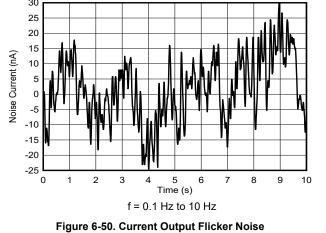

| V <sub>n</sub>    | Output noise current (peak to peak)                 | 0.1 Hz to 10 Hz, DAC at midscale,<br>V <sub>DD</sub> = 5.5 V, ±250-μA output range                                                           |     | 150  |     | nA <sub>PP</sub>   |

|                   | Output noise density                                | f = 1 kHz, DAC at midscale,<br>V <sub>DD</sub> = 5.5 V, ±250-μA output range                                                                 |     | 1    |     | nA/√ <del>Hz</del> |

|                   | Power supply rejection ratio (ac) <sup>(3)</sup>    | ±250 μA output range, 200-mV 50-Hz or 60-Hz sine wave superimposed on power-supply voltage, DAC at midscale                                  |     | 0.65 |     | LSB/V              |

| POW               | ER                                                  |                                                                                                                                              |     |      |     |                    |

|                   |                                                     | Normal operation, DACs at full scale, ±25-µA output range, digital pins static                                                               |     | 42   | 50  |                    |

| l                 | Current flowing into VDD <sup>(3)</sup> (4)         | Normal operation, DACs at full scale, ±50-μA output range, digital pins static                                                               |     | 56   | 70  | μΑ/ch              |

| I <sub>DD</sub>   |                                                     | Normal operation, DACs at full scale, ±125-μA output range, digital pins static                                                              |     | 98   | 120 | μΑ/ση              |

|                   |                                                     | Normal operation, DACs at full scale, ±250-μA output range, digital pins static                                                              |     | 167  | 200 |                    |

<sup>(1)</sup> Measured between DAC codes 0d and 255d.

<sup>(2)</sup> Specified by design and characterization, not production tested.

<sup>(3)</sup> The current flowing into  $V_{DD}$  does not account for the load current sourced or sinked on the OUTx pins. The VREF pin is connected to  $V_{DD}$ .

<sup>(4)</sup> The total power consumption is calculated by I<sub>DD</sub> x (total number of channels powered on) + (sleep-mode current).

# 6.7 Electrical Characteristics: Comparator Mode

all minimum/maximum specifications at  $T_A$  = -40°C to +125°C and typical specifications at  $T_A$  = 25°C, 1.7 V ≤  $V_{DD}$  ≤ 5.5 V, DAC reference tied to VDD, gain = 1x in voltage output mode, DAC output pin (OUT) loaded with resistive load ( $R_L$  = 5 k $\Omega$  to AGND) and capacitive load ( $R_L$  = 200 pF to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|                   | PARAMETER                              | TEST CONDITIONS                                                                                                                                                                                                                                                                                                      | MIN | TYP | MAX                           | UNIT |

|-------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------------|------|

| STAT              | IC PERFORMANCE                         |                                                                                                                                                                                                                                                                                                                      | 1   |     |                               |      |

|                   | Offset error <sup>(1)</sup> (2)        | 1.7 V ≤ V <sub>DD</sub> ≤ 5.5 V, DAC at midscale, comparator input at Hi-Z, and DAC operating with external reference                                                                                                                                                                                                | -5  | 0   | 5                             | mV   |

|                   | Offset error time drift <sup>(1)</sup> | $V_{DD}$ = 5.5 V, external reference, $T_A$ = 125°C, FBx in Hi-Z mode, DAC at full scale and $V_{FB}$ at 0 V or DAC at zero scale and $V_{FB}$ at 1.84 V, drift specified for 10 years of continuous operation                                                                                                       |     | 4   |                               | mV   |

| OUT               | PUT                                    |                                                                                                                                                                                                                                                                                                                      |     |     |                               |      |

|                   | Input voltage                          | VREF connected to VDD, FBx resistor network connected to ground                                                                                                                                                                                                                                                      | 0   |     | V <sub>DD</sub>               | V    |

|                   | Input voltage                          | VREF connected to VDD, FBx resistor network disconnected from ground                                                                                                                                                                                                                                                 | 0   |     | V <sub>DD</sub> (1/3 – 1/100) | V    |

| V <sub>OL</sub>   | Logic low output voltage               | I <sub>LOAD</sub> = 100 μA, output in open-drain mode                                                                                                                                                                                                                                                                |     | 0.1 |                               | V    |

| DYN               | AMIC PERFORMANCE                       |                                                                                                                                                                                                                                                                                                                      |     |     |                               |      |

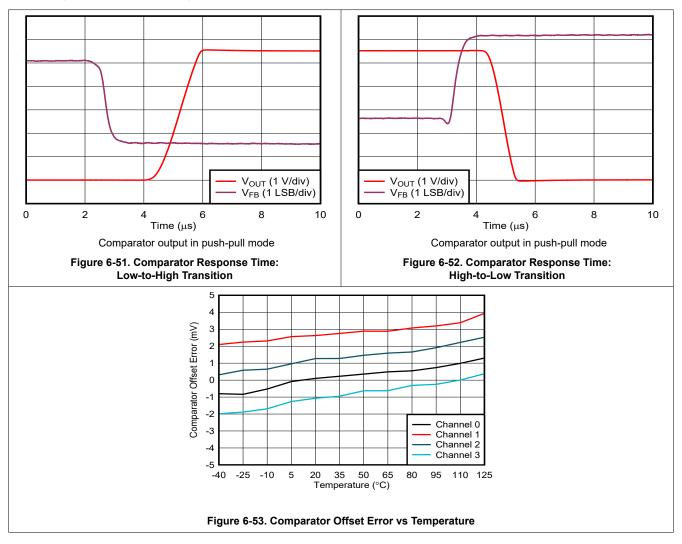

| t <sub>resp</sub> | Output response time                   | DAC at midscale with 10-bit resolution, FBx input at Hi-Z, and transition step at FBx node is ( $V_{DAC}-2$ LSB) to ( $V_{DAC}+2$ LSB), transition time measured between 10% and 90% of output, output current of 100 $\mu$ A, comparator output configured in push-pull mode, load capacitor at DAC output is 25 pF |     | 10  |                               | μs   |

<sup>(1)</sup> Specified by design and characterization, not production tested.

<sup>(2)</sup> This specification does not include the total unadjusted error (TUE) of the DAC.

## 6.8 Electrical Characteristics: General

all minimum/maximum specifications at  $T_A$  =  $-40^{\circ}$ C to +125°C and typical specifications at  $T_A$  = 25°C, 1.7 V ≤  $V_{DD}$  ≤ 5.5 V, DAC reference tied to VDD, gain = 1x in voltage output mode or  $\pm 250 \mu A$  output range in current output mode, DAC output pin (OUT) loaded with resistive load ( $R_L$  = 5 k $\Omega$  to AGND) in voltage-output mode and capacitive load ( $R_L$  = 200 pF to AGND), and digital inputs at VDD or AGND (unless otherwise noted)

|       | PARAMETER                                                   | TEST CONDITIONS                                                                                                                                     | MIN    | TYP   | MAX   | UNIT   |

|-------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|--------|

| INTE  | RNAL REFERENCE                                              |                                                                                                                                                     |        |       |       |        |

|       | Initial accuracy                                            | T <sub>A</sub> = 25°C                                                                                                                               | 1.1979 | 1.212 | 1.224 | V      |

|       | Reference output temperature coefficient <sup>(1)</sup> (2) |                                                                                                                                                     |        |       | 50    | ppm/°C |

| EXTE  | RNAL REFERENCE                                              |                                                                                                                                                     | -      |       |       |        |

|       | V <sub>REF</sub> input impedance <sup>(1) (3)</sup>         |                                                                                                                                                     |        | 192   |       | kΩ/ch  |

| EPF   | ROM                                                         |                                                                                                                                                     |        |       |       |        |

|       | Endurance <sup>(1)</sup>                                    | -40°C ≤ T <sub>A</sub> ≤ +85°C                                                                                                                      |        | 20000 |       | Cycles |

|       | Endurance                                                   | T <sub>A</sub> = 125°C                                                                                                                              |        | 1000  |       | Cycles |

|       | Data retention <sup>(1)</sup>                               | T <sub>A</sub> = 25°C                                                                                                                               | -      | 50    |       | Years  |

|       | EEPROM programming write cycle time <sup>(1)</sup>          |                                                                                                                                                     |        |       | 200   | ms     |

|       | Device boot-up time <sup>(1)</sup>                          | Time taken from power valid (V <sub>DD</sub> ≥ 1.7 V) to output valid state (output state as programmed in EEPROM), 0.5-µF capacitor on the CAP pin |        | 5     |       | ms     |

| DIGIT | TAL INPUTS                                                  |                                                                                                                                                     |        |       |       |        |

|       | Digital feedthrough                                         | Voltage output mode, DAC output static at midscale, fast mode plus, SCL toggling                                                                    |        | 20    |       | nV-s   |

|       | Pin capacitance                                             | Per pin                                                                                                                                             |        | 10    |       | pF     |

| POW   | ER-DOWN MODE                                                |                                                                                                                                                     |        |       |       |        |

|       |                                                             | DAC in sleep mode, internal reference powered down, external reference at 5.5 V                                                                     |        |       | 28    |        |

| DD    | Current flowing into VDD <sup>(1)</sup>                     | DAC in sleep mode, internal reference enabled, additional current through internal reference                                                        |        | 10    |       | μΑ     |

|       |                                                             | DAC channels enabled, internal reference enabled, additional current through internal reference per DAC channel in voltage-output mode              |        | 12.5  |       |        |

| HIGH  | -IMPEDANCE OUTPUT                                           |                                                                                                                                                     |        |       |       |        |

|       |                                                             | DAC in Hi-Z output mode, 1.7 V ≤ V <sub>DD</sub> ≤ 5.5 V                                                                                            |        | 10    |       |        |

|       | Current flouring into \/ and                                | $V_{DD}$ = 0 V, $V_{OUT}$ ≤ 1.5 V, decoupling capacitor between $V_{DD}$ and AGND = 0.1 $\mu$ F                                                     |        | 200   |       | nA     |

| LEAK  | Current flowing into $V_{OUTX}$ and $V_{FBX}$               | $V_{DD}$ = 0 V, 1.5 V < $V_{OUT}$ ≤ 5.5 V, decoupling capacitor between $V_{DD}$ and AGND = 0.1 $\mu F$                                             |        | 500   |       |        |

|       |                                                             | 100 kΩ between V <sub>DD</sub> and AGND, V <sub>OUT</sub> ≤ 1.25 V, series resistance of 10 kΩ at OUTx pin                                          |        | ±2    |       | μΑ     |

<sup>(1)</sup> Specified by design and characterization, not production tested.

<sup>(2)</sup> Measured at –40°C and +125°C and calculated the slope.

<sup>(3)</sup> Impedances for the DAC channels are connected in parallel.

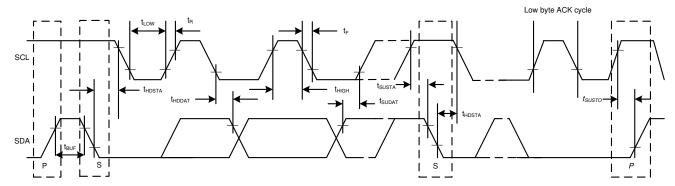

# 6.9 Timing Requirements: I<sup>2</sup>C Standard Mode

all input signals are timed from VIL to 70% of  $V_{pull-up}$ , 1.7 V  $\leq$   $V_{DD}$   $\leq$  5.5 V,  $-40^{\circ}$ C  $\leq$   $T_{A}$   $\leq$  +125 $^{\circ}$ C, and 1.7 V  $\leq$   $V_{pull-up}$   $\leq$   $V_{DD}$  V

|                     | pan ap 35                                       | MIN  | NOM MAX | UNIT |

|---------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 100     | kHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 4.7  |         | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 4    |         | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 4.7  |         | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 4    |         | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 250  |         | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 4700 |         | ns   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 4000 |         | ns   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 300     | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 1000    | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 3.45    | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 3.45    | μs   |

# 6.10 Timing Requirements: I<sup>2</sup>C Fast Mode

all input signals are timed from VIL to 70% of  $V_{\text{pull-up}}$ , 1.7 V  $\leq$   $V_{\text{DD}} \leq$  5.5 V,  $-40^{\circ}\text{C} \leq$   $T_{\text{A}} \leq$  +125°C, and 1.7 V  $\leq$   $V_{\text{pull-up}} \leq$   $V_{\text{DD}}$  V

|                     |                                                 | MIN  | NOM MAX | UNIT |

|---------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 400     | kHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 1.3  |         | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 0.6  |         | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 0.6  |         | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 0.6  |         | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 100  |         | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 1300 |         | ns   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 600  |         | ns   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 300     | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 300     | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 0.9     | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 0.9     | μs   |

## 6.11 Timing Requirements: I<sup>2</sup>C Fast Mode Plus

all input signals are timed from VIL to 70% of  $V_{pull-up}$ , 1.7  $V \le V_{DD} \le 5.5 \text{ V}$ ,  $-40^{\circ}\text{C} \le T_{A} \le +125^{\circ}\text{C}$ , and 1.7  $V \le V_{pull-up} \le V_{DD} V_{DD} \le 5.5 \text{ V}$

|                     |                                                 | MIN  | NOM MAX | UNIT |

|---------------------|-------------------------------------------------|------|---------|------|

| f <sub>SCLK</sub>   | SCL frequency                                   |      | 1       | MHz  |

| t <sub>BUF</sub>    | Bus free time between stop and start conditions | 0.5  |         | μs   |

| t <sub>HDSTA</sub>  | Hold time after repeated start                  | 0.26 |         | μs   |

| t <sub>SUSTA</sub>  | Repeated start setup time                       | 0.26 |         | μs   |

| t <sub>SUSTO</sub>  | Stop condition setup time                       | 0.26 |         | μs   |

| t <sub>HDDAT</sub>  | Data hold time                                  | 0    |         | ns   |

| t <sub>SUDAT</sub>  | Data setup time                                 | 50   |         | ns   |

| t <sub>LOW</sub>    | SCL clock low period                            | 0.5  |         | μs   |

| t <sub>HIGH</sub>   | SCL clock high period                           | 0.26 |         | μs   |

| t <sub>F</sub>      | Clock and data fall time                        |      | 120     | ns   |

| t <sub>R</sub>      | Clock and data rise time                        |      | 120     | ns   |

| t <sub>VD_DAT</sub> | Data valid time                                 |      | 0.45    | μs   |

| t <sub>VD_ACK</sub> | Data valid acknowledge time                     |      | 0.45    | μs   |

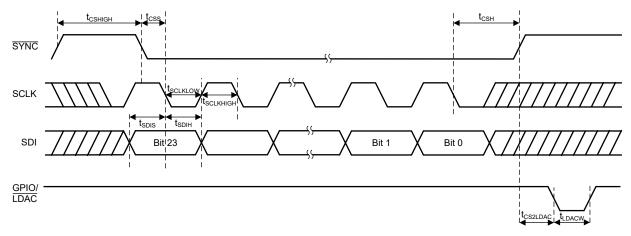

## 6.12 Timing Requirements: SPI Write Operation

all input signals are specified with  $t_r$  =  $t_f$  = 1 V/ns (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of (VIL + VIH) / 2, 1.7 V  $\leq$   $V_{IO} \leq$  5.5 V, 1.7 V  $\leq$   $V_{DD} \leq$  5.5 V, and  $-40^{\circ}$ C  $\leq$   $T_A \leq$  +125 $^{\circ}$ C

|                        |                                                  | MIN | NOM | MAX | UNIT |

|------------------------|--------------------------------------------------|-----|-----|-----|------|

| f <sub>(SCLK)</sub>    | Serial clock frequency                           |     |     | 50  | MHz  |

| t <sub>SCLKHIGH</sub>  | SCLK high time                                   | 9   |     |     | ns   |

| t <sub>SCLKLOW</sub>   | SCLK low time                                    | 9   |     |     | ns   |

| t <sub>SDIS</sub>      | SDI setup time                                   | 8   |     |     | ns   |

| t <sub>SDIH</sub>      | SDI hold time                                    | 8   |     |     | ns   |

| t <sub>CSS</sub>       | CS to SCLK falling edge setup time               | 18  |     |     | ns   |

| t <sub>CSH</sub>       | SCLK falling edge to CS rising edge              | 10  |     |     | ns   |

| t <sub>CSHIGH</sub>    | CS hight time                                    | 50  |     |     | ns   |

| t <sub>DACWAIT</sub>   | Sequential DAC update wait time for same channel | 2   |     |     | μs   |

| t <sub>BCASTWAIT</sub> | Broadcast DAC update wait time                   | 2   |     |     | μs   |

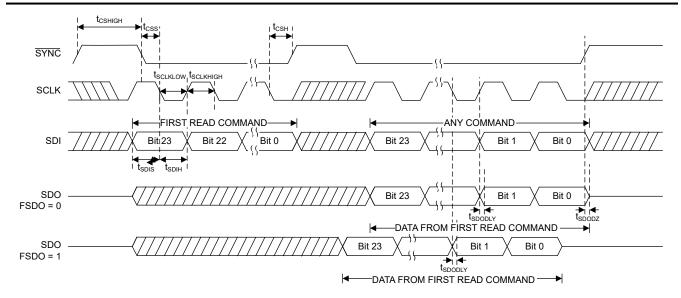

## 6.13 Timing Requirements: SPI Read and Daisy Chain Operation (FSDO = 0)

all input signals are specified with  $t_r$  =  $t_f$  = 1 V/ns (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of (VIL + VIH) / 2, 1.7 V  $\leq$   $V_{IO} \leq$  5.5 V, 1.7 V  $\leq$   $V_{DD} \leq$  5.5 V,  $-40^{\circ}$ C  $\leq$   $T_A \leq$  +125°C, and FSDO = 0

|                       |                                                                                       | MIN | NOM | MAX  | UNIT |

|-----------------------|---------------------------------------------------------------------------------------|-----|-----|------|------|

| f <sub>(SCLK)</sub>   | Serial clock frequency                                                                |     |     | 1.25 | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                                                                        | 350 |     |      | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                                                                         | 350 |     |      | ns   |

| t <sub>SDIS</sub>     | SDI setup time                                                                        | 8   |     |      | ns   |

| t <sub>SDIH</sub>     | SDI hold time                                                                         | 8   |     |      | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup time                                                  | 400 |     |      | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge                                                 | 400 |     |      | ns   |

| t <sub>CSHIGH</sub>   | SYNC hight time                                                                       | 1   |     |      | μs   |

| t <sub>SDODLY</sub>   | SCLK rising edge to SDO falling edge, I <sub>OL</sub> ≤ 5 mA, C <sub>L</sub> = 20 pF. |     |     | 300  | ns   |

### 6.14 Timing Requirements: SPI Read and Daisy Chain Operation (FSDO = 1)

all input signals are specified with  $t_r$  =  $t_f$  = 1 V/ns (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of (VIL + VIH) / 2, 1.7 V  $\leq$   $V_{IO} \leq$  5.5 V, 1.7 V  $\leq$   $V_{DD} \leq$  5.5 V,  $-40^{\circ}$ C  $\leq$   $T_A \leq$  +125°C, and FSDO = 1

|                       |                                                                         | MIN | NOM I | ИАХ | UNIT |

|-----------------------|-------------------------------------------------------------------------|-----|-------|-----|------|

| f <sub>(SCLK)</sub>   | Serial clock frequency                                                  |     |       | 2.5 | MHz  |

| t <sub>SCLKHIGH</sub> | SCLK high time                                                          | 175 |       |     | ns   |

| t <sub>SCLKLOW</sub>  | SCLK low time                                                           | 175 |       |     | ns   |

| t <sub>SDIS</sub>     | SDI setup time                                                          | 8   |       |     | ns   |

| t <sub>SDIH</sub>     | SDI hold time                                                           | 8   |       |     | ns   |

| t <sub>CSS</sub>      | SYNC to SCLK falling edge setup time                                    | 300 |       |     | ns   |

| t <sub>CSH</sub>      | SCLK falling edge to SYNC rising edge                                   | 300 |       |     | ns   |

| t <sub>CSHIGH</sub>   | SYNC hight time                                                         | 1   |       |     | μs   |

| t <sub>SDODLY</sub>   | SCLK rising edge to SDO falling edge, $I_{OL} \le 5$ mA, $C_L = 20$ pF. |     |       | 300 | ns   |

## 6.15 Timing Requirements: GPIO

all input signals are specified with  $t_r$  =  $t_f$  = 1 V/ns (10% to 90% of  $V_{IO}$ ) and timed from a voltage level of (VIL + VIH) / 2, 1.7 V  $\leq$   $V_{IO} \leq$  5.5 V, 1.7 V  $\leq$   $V_{DD} \leq$  5.5 V, and  $-40^{\circ}$ C  $\leq$   $T_A \leq$  +125 $^{\circ}$ C

|                       |                                                            | MIN | NOM | MAX | UNIT |

|-----------------------|------------------------------------------------------------|-----|-----|-----|------|

| t <sub>GPIHIGH</sub>  | GPI high time <sup>(1)</sup>                               | 2   |     |     | μs   |

| t <sub>GPILOW</sub>   | GPI low time <sup>(1)</sup>                                | 2   |     |     | μs   |

| t <sub>GPAWGD</sub>   | LDAC falling edge to DAC update delay <sup>(2)</sup>       |     |     | 2   | μs   |

| t <sub>CS2LDAC</sub>  | SYNC rising edge to LDAC falling edge                      | 1   |     |     | μs   |

| t <sub>STP2LDAC</sub> | I <sup>2</sup> C stop bit rising edge to LDAC falling edge | 1   |     |     | μs   |

| t <sub>LDACW</sub>    | LDAC low time                                              | 2   |     |     | μs   |

- (1) The SCL, SDA, A0, and A1 pins can be configured as GPIOs that perform different channel-specific or independent operations. The actual response time of the GPIO is determined by the delay provided by the configured function and the settling time of the DAC.

- (2) The GPIOs can be configured as channel-specific or global  $\overline{\text{LDAC}}$  function.

## **6.16 Timing Diagrams**

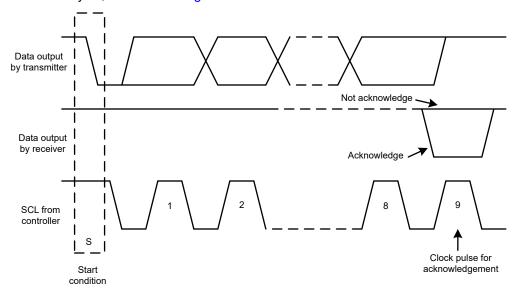

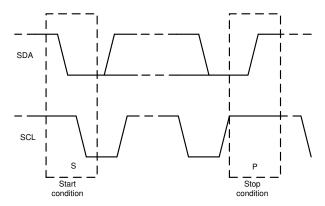

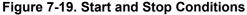

Figure 6-1. I<sup>2</sup>C Timing Diagram

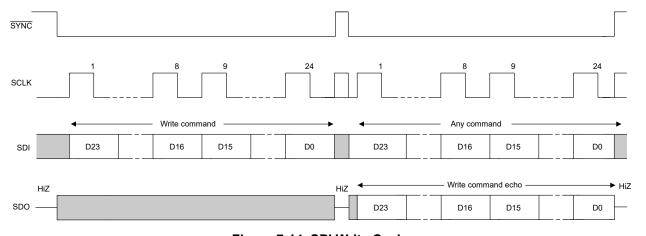

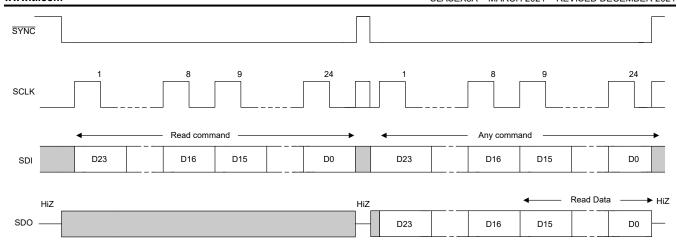

Figure 6-2. SPI Write Timing Diagram

Figure 6-3. SPI Read Timing Diagram

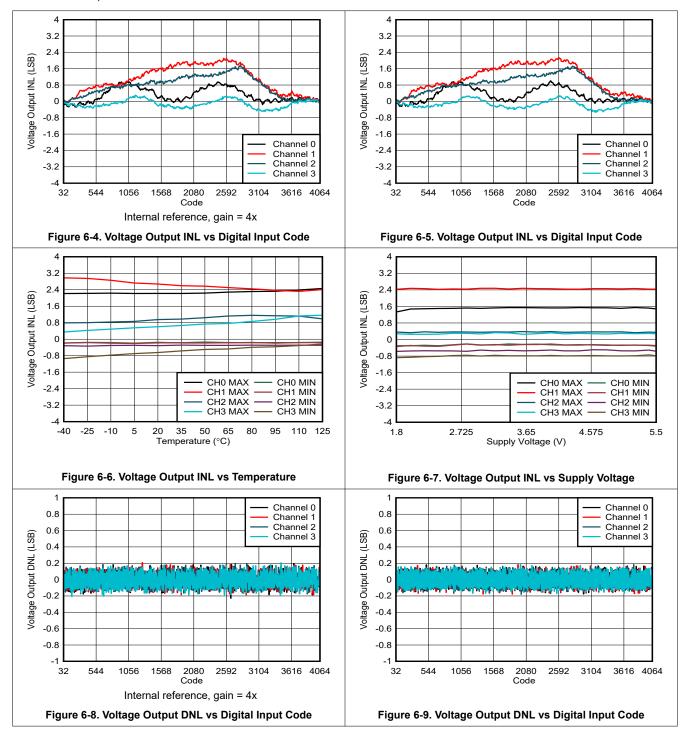

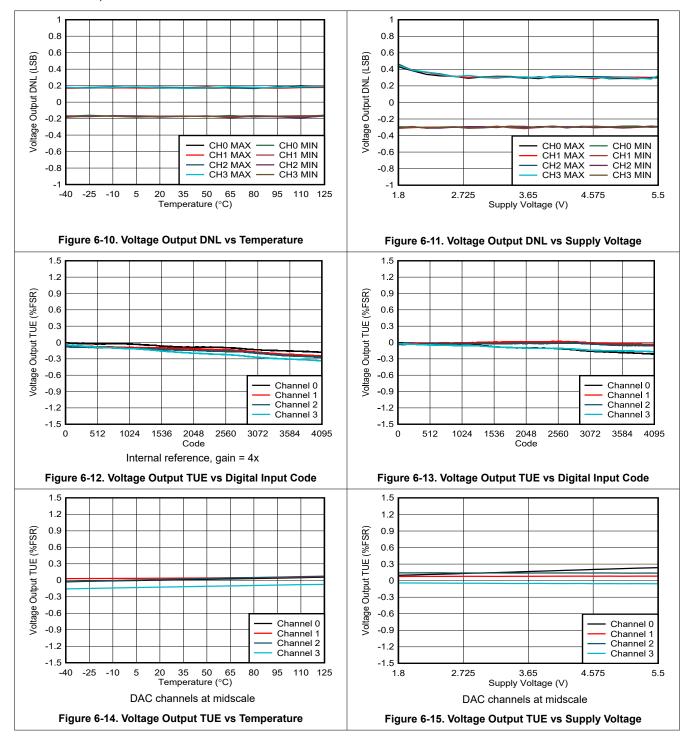

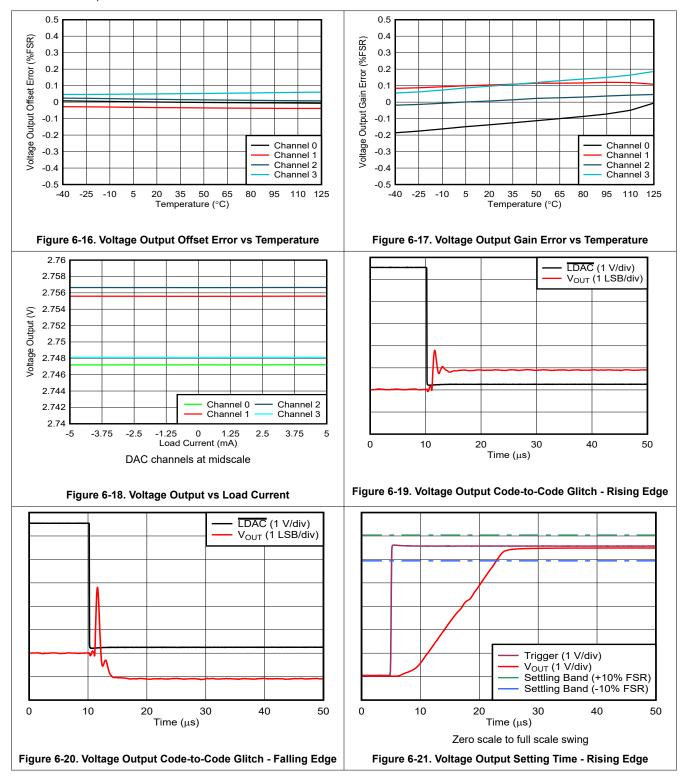

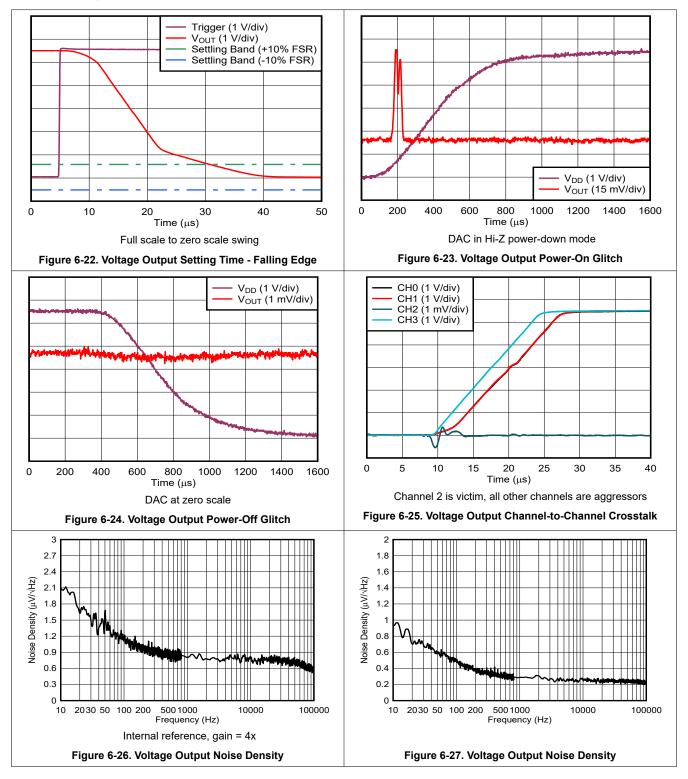

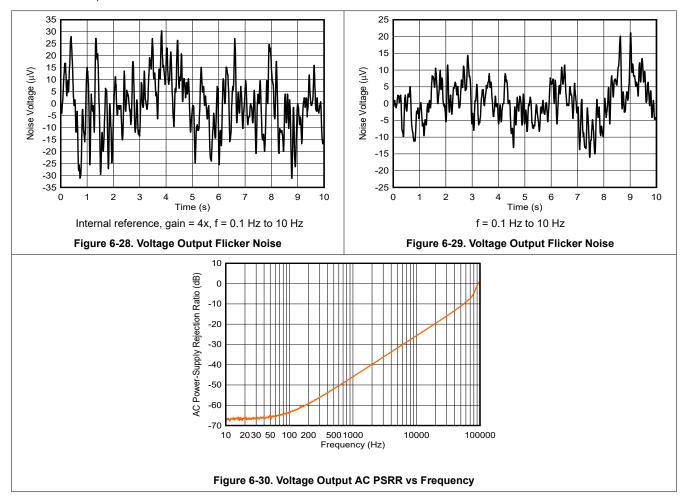

## 6.17 Typical Characteristics: Voltage Output

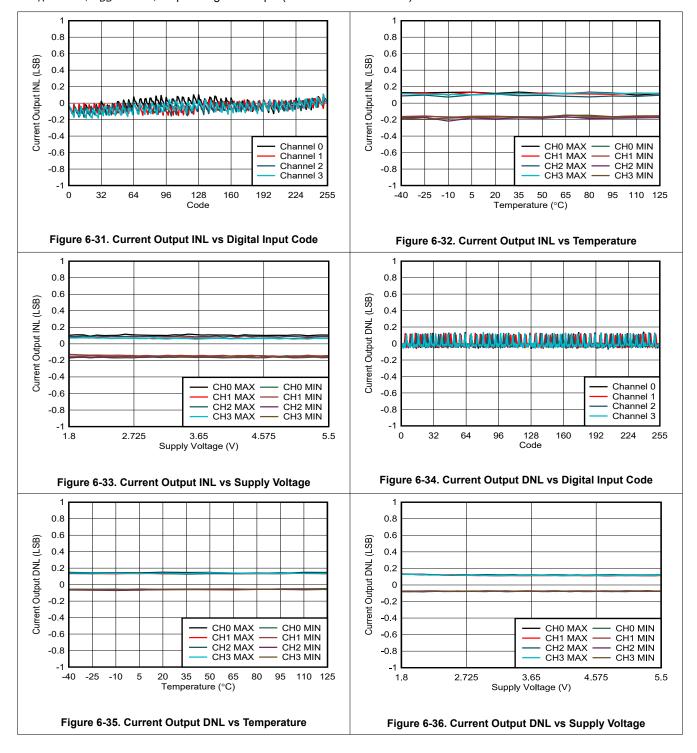

## 6.18 Typical Characteristics: Current Output

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 5.5 V, output range: ±250 µA (unless otherwise noted)

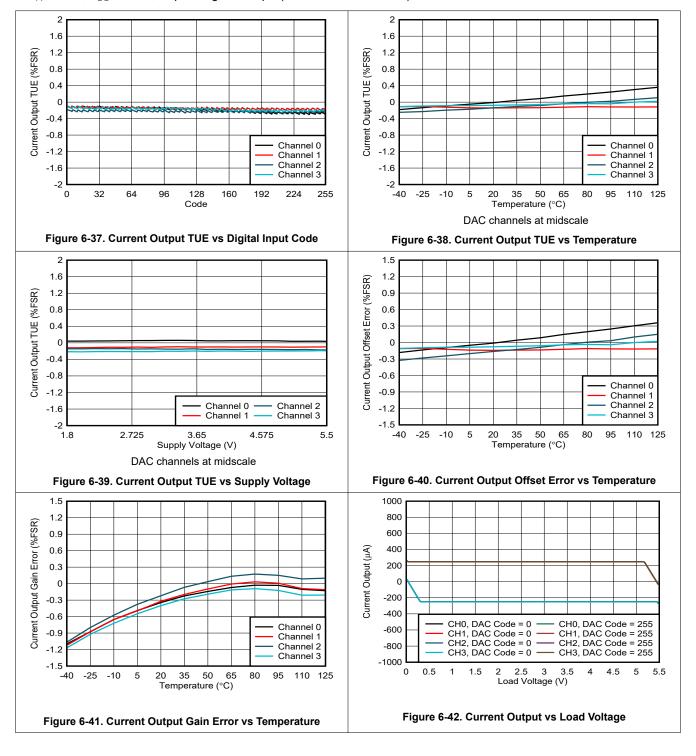

## **6.18 Typical Characteristics: Current Output (continued)**

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 5.5 V, output range: ±250 µA (unless otherwise noted)

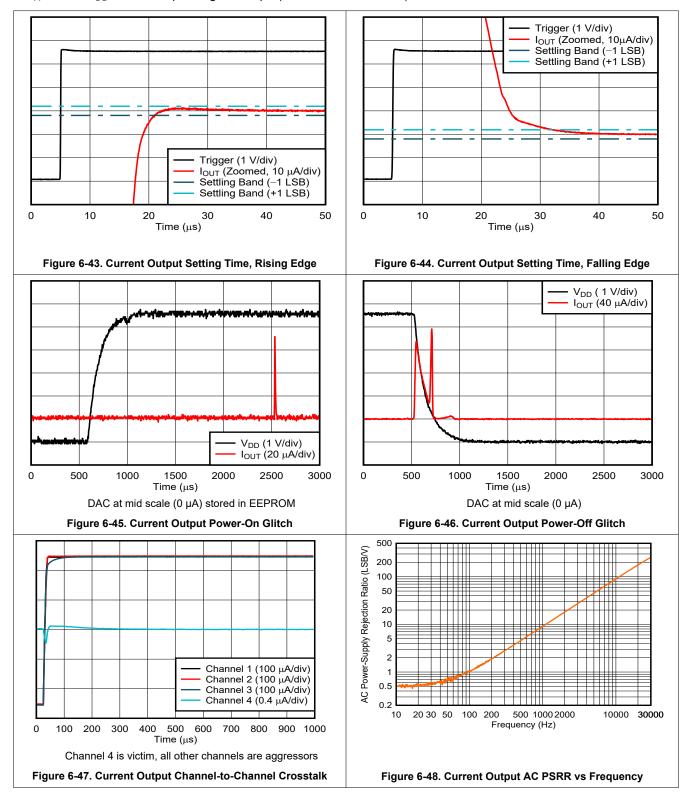

## **6.18 Typical Characteristics: Current Output (continued)**

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 5.5 V, output range: ±250 µA (unless otherwise noted)

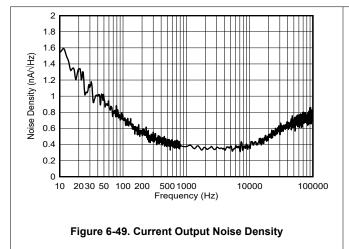

# **6.18 Typical Characteristics: Current Output (continued)**

at  $T_A$  = 25°C,  $V_{DD}$  = 5.5 V, output range: ±250  $\mu A$  (unless otherwise noted)

## 6.19 Typical Characteristics: Comparator

## 6.20 Typical Characteristics: General

at T<sub>A</sub> = 25°C, V<sub>DD</sub> = 5.5 V, and DAC outputs unloaded (unless otherwise noted)

# 7 Detailed Description

#### 7.1 Overview

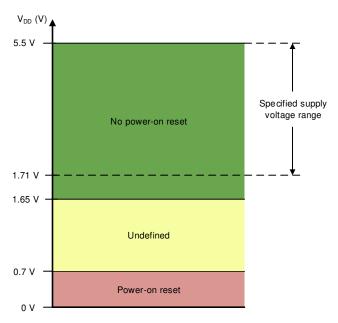

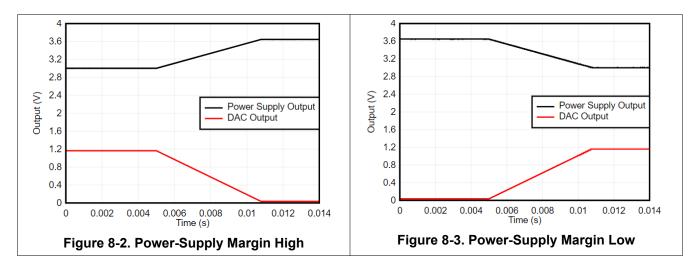

The 12-bit DAC63204,10-bit DAC53204, and 8-bit DAC43204 (DACx3204) are a pin-compatible family of quad-channel buffered voltage-output and current-output, smart digital-to-analog converters (DACs). The DAC channels are independently configurable as voltage or current output. The DAC outputs change to Hi-Z when VDD is off; a feature useful in voltage-margining applications. These smart DACs contain nonvolatile memory (NVM), an internal reference, automatically detectable I $^2$ C and SPI interface, PMBus-compatibility in I $^2$ C mode, force-sense output, and a general-purpose input. These devices support Hi-Z power-down modes by default, which can be configured to 10 k $\Omega$ -GND or 100 k $\Omega$ -GND using the NVM. The DACx3204 have a power-on-reset (POR) circuit that makes sure all the registers start with default or user-programmed settings using NVM. The DACx3204 operate with either an internal reference, external reference, or with a power supply as the reference, and provide a full-scale output of 1.8 V to 5.5 V.

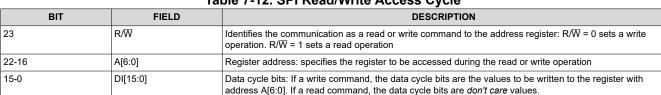

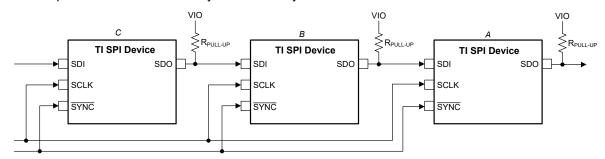

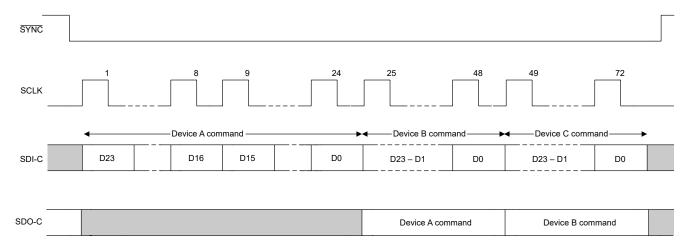

The DACx3204 devices support  $I^2C$  standard mode (100 kbps), fast mode (400 kbps), and fast mode plus (1 Mbps). The  $I^2C$  interface can be configured with four target addresses using the A0 pin. These devices also support specific PMBus commands such as *turn on/off*, *margin high or low*, and more. The SPI mode supports a 3-wire interface by default with up to 50-MHz SCLK input. The GPIO input can be configured as SDO in the NVM for SPI read capability. The GPIO input can alternatively be configurable as  $\overline{\text{LDAC}}$ ,  $\overline{\text{PD}}$ ,  $\overline{\text{STATUS}}$ ,  $\overline{\text{FAULT-DUMP}}$ ,  $\overline{\text{RESET}}$ , and  $\overline{\text{PROTECT}}$  functions.

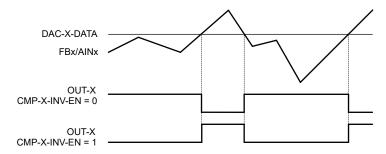

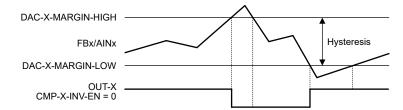

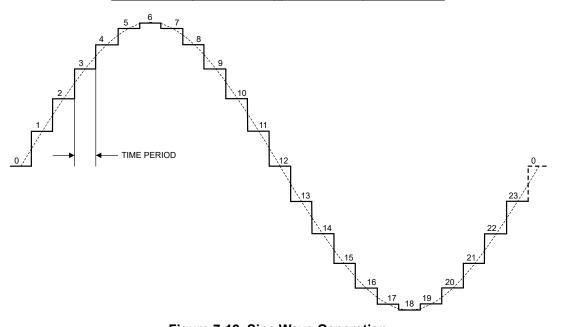

The DACx3204 also include digital slew rate control, and support standard waveform generation such as *sine and cosine*, *triangular*, and *sawtooth* waveforms. These devices can generate pulse-width modulation (PWM) output with the combination of the triangular or sawtooth waveform and the FB pin. The force-sense outputs of the DAC channels can be used as programmable comparators. The comparator mode allows programmable hysteresis, latching comparator, window comparator, and fault-dump to the NVM. These features enable the DACx3204 to go beyond the limitations of a conventional DAC that depends on a processor to function. As a result of processor-less operation and the *smart* feature set, the DACx3204 are called smart DACs.

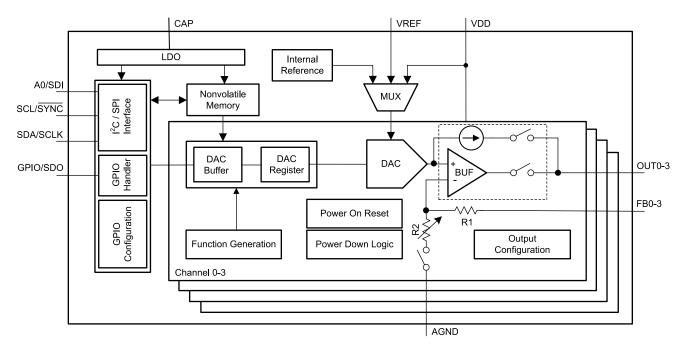

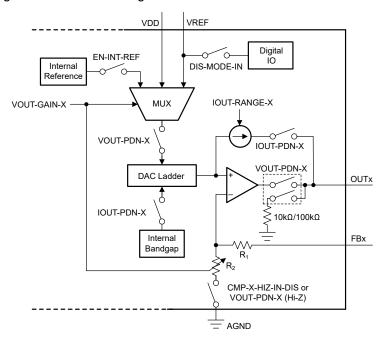

### 7.2 Functional Block Diagram

Figure 7-1. Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 Smart Digital-to-Analog Converter (DAC) Architecture

The DACx3204 devices consist of string architecture with a voltage-output amplifier and an external FB pin and voltage-to-current converter for each channel. Section 7.2 shows the DAC architecture within the block diagram, which operates from a 1.8-V to 5.5-V power supply. The DAC has an internal voltage reference of 1.21 V. There is an option to select an external reference on the VREF pin or the power supply as a reference. The voltage output mode uses one of these three reference options. The current output mode uses an internal band gap to generate the current outputs. Both the voltage- and current-output modes support multiple programmable output ranges.

The DACx3204 devices support Hi-Z output when VDD is off, maintaining very low leakage current at the output pins with up to 1.25 V of forced voltage. The DAC output pin also starts up in high-impedance mode by default, making these devices an excellent choice for voltage margining and scaling applications. To change the power-up mode to 10 k $\Omega$ -GND or 100 k $\Omega$ -GND, program the corresponding VOUT-PDN-X field in the COMMON-CONFIG register and load these bits in the device NVM.

The DACx3204 devices support an independent comparator mode for each channel. The respective FBx pins act as the inputs for the comparator. The DAC architecture supports inversion of the comparator output using register settings. The comparator outputs can be push-pull or open-drain. The comparator mode supports programmable hysteresis using *margin-high* and *margin-low* register fields, latching comparator, and window comparator. The comparator outputs are accessible internally by the device.

The DACx3204 devices include a *smart* feature set to enable processor-less operation and high-integration. The NVM enables a predictable start-up. The GPIO triggers the DAC output without the I<sup>2</sup>C interface in the absence of a processor or when the processor or software fails. The integrated functions and the FBx pin enable PWM output for control applications. The FBx pin enables this device to be used as a programmable comparator. The digital slew-rate control and the Hi-Z power-down modes enable a hassle-free voltage margining and scaling function.

#### 7.3.2 Digital Input/Output

The DACx3204 have four digital IO pins that include I<sup>2</sup>C, SPI, PMBus, and GPIO interfaces. These devices automatically detect I<sup>2</sup>C and SPI protocols at the first successful communication after power-on, and then connect to the detected interface. After an interface protocol is connected, any change in the protocol is ignored. The I<sup>2</sup>C interface uses the A0 pin to select from among four address options. The SPI interface is a 3-wire interface by default. No readback capability is available in this mode. The GPIO pin can be configured in the register map and then programmed in to the NVM as the SDO pin. The SPI readback mode is slower than the write mode. The programming interface pins are:

- I<sup>2</sup>C: SCL, SDA, A0

- SPI: SCLK, SDI, SYNC, SDO/GPIO

The GPIO can be configured as multiple functions other than SDO. These are  $\overline{\text{LDAC}}$ ,  $\overline{\text{PD}}$ ,  $\overline{\text{STATUS}}$ ,  $\overline{\text{PROTECT}}$ ,  $\overline{\text{FAULT-DUMP}}$ , and  $\overline{\text{RESET}}$ . All the digital pins are open-drain when used as outputs. Therefore, all the output pins must be pulled up to the desired IO voltage using external resistors.

## 7.3.3 Nonvolatile Memory (NVM)

The DACx3204 contain nonvolatile memory (NVM) bits. These memory bits are user programmable and erasable, and retain the set values in the absence of a power supply. All the register bits, as shown in the highlighted gray cells in Table 7-20, can be stored in the NVM by setting NVM-PROG = 1 in the COMMON-TRIGGER register. The NVM-PROG is an autoresetting bit. The default values for all the registers in the DACx3204 are loaded from NVM as soon as a POR event is issued.

The DACx3204 also implement NVM-RELOAD bit in the COMMON-TRIGGER register. Set this bit to 1 for the device to start an NVM-reload operation. After completion, the device autoresets the NVM-RELOAD bit to 0. During the NVM write or reload operation, all read/write operations to the device are blocked. Section 6.8 provides the timing specification for the NVM write cycle. The processor must wait for the specified duration before resuming any read or write operation on the SPI or I<sup>2</sup>C interface.

### 7.4 Device Functional Modes

### 7.4.1 Voltage-Output Mode

The voltage-output mode for each DAC channel can be entered by selecting the power-up option in the VOUT-PDN-X fields in the COMMON-CONFIG register and simultaneously powering down the current output option for the respective channels using the IOUT-PDN-X bits in the same register. Short the OUTx and FBx pins of respective channels externally for closed-loop amplifier output. An open FBx pin saturates the amplifier output. To achieve the desired voltage output, select the correct reference option, select the amplifier gain for the required output range, and program the DAC code in the DAC-X-DATA register of the respective channels.

## 7.4.1.1 Voltage Reference and DAC Transfer Function

There are three voltage reference options possible with the DACx3204: internal reference, external reference, and the power supply as reference, as shown in Figure 7-2. The DAC transfer function in the voltage-output and comparator modes changes based on the voltage reference selection.

Figure 7-2. Voltage Reference Selection and Power-Down Logic

#### 7.4.1.1.1 Internal Reference

The DACx3204 contain an internal reference that is disabled by default. To enable the internal reference, write 1 to bit EN-INT-REF in the COMMON-CONFIG register. The internal reference generates a fixed 1.21-V voltage (typical). Use the VOUT-GAIN-X bit in the DAC-X-VOUT-CMP-CONFIG register to achieve gains of 1.5x, 2x, 3x, or 4x for the DAC output voltage (V<sub>OUT</sub>). Equation 1 shows DAC transfer function using the internal reference.

$$V_{OUT} = \frac{DAC\_DATA}{2^{N}} \times V_{REF} \times GAIN$$

(1)

where:

- N is the resolution in bits, 8 (DAC43204), 10 (DAC53204), or 12 (DAC63204).

- DAC\_DATA is the decimal equivalent of the binary code that is loaded to the DAC-X-DATA bit in the DAC-X-DATA register. DAC\_DATA ranges from 0 to 2<sup>N</sup> – 1.

- V<sub>RFF</sub> is the internal reference voltage = 1.21 V (typical).

- GAIN = 1.5x, 2x, 3x, or 4x, based on VOUT-X-GAIN bits.

#### 7.4.1.1.2 External Reference

By default, the DACx3204 operate from an external reference input. The external reference option can also be selected by configuring the VOUT-GAIN-X field in the DAC-X-VOUT-CMP-CONFIG register appropriately. Write 1 to the DIS-MODE-IN bit in the DEVICE-MODE-CONFIG register to minimize  $I_{DD}$ . The external reference can be between 1.7 V and VDD. Equation 2 shows DAC transfer function when the external reference is used. The gain at the output stage of the DAC is always 1x in the external reference mode.

#### Note

The external reference must be less than VDD in both transient and steady-state conditions. Therefore, the external reference must ramp up after VDD and ramp down before VDD.

$$V_{OUT} = \frac{DAC\_DATA}{2N} \times V_{REF}$$

(2)

#### where:

- N is the resolution in bits, 8 (DAC43204), 10 (DAC53204), or 12 (DAC63204).

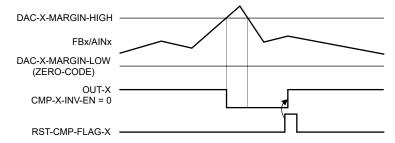

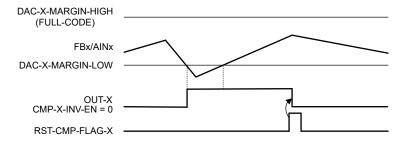

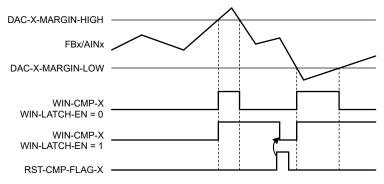

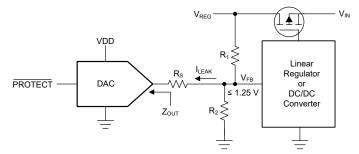

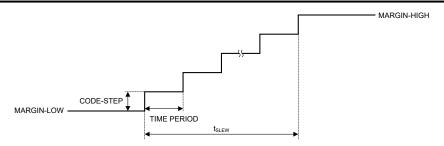

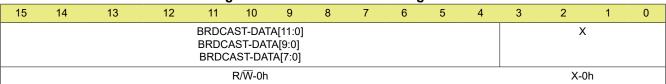

- DAC\_DATA is the decimal equivalent of the binary code that is loaded to the DAC-X-DATA field in the DAC-X-DATA register. DAC DATA ranges from 0 to 2<sup>N</sup> – 1.