**DAC60096** SBAS721A - DECEMBER 2015-REVISED JANUARY 2016

# DAC60096 96-Channel, 12-Bit, Low-Power, Serial-Input, High-Voltage **Output DAC with Conversion Trigger**

#### **Features**

- **High-Channel Count**

- 96-Channel DAC

- Specified Monotonic to 12 Bits

- Wide, Unbuffered Output Voltage Range: ±10.5 V

- Simultaneous Update of DAC Outputs

- Clear Function

- Integrated Reference Buffers: 2.5-V Input

- Dedicated A-B Trigger Pin

- Toggle Mode Enables Square-Wave Generation

- SPI™-Compatible Serial Interface

- 4-Wire Mode, 3-V to 5.5-V Operation

- Low Power: 440-mW Typical Operation

- Operating Temperature Range: -40°C to +85°C

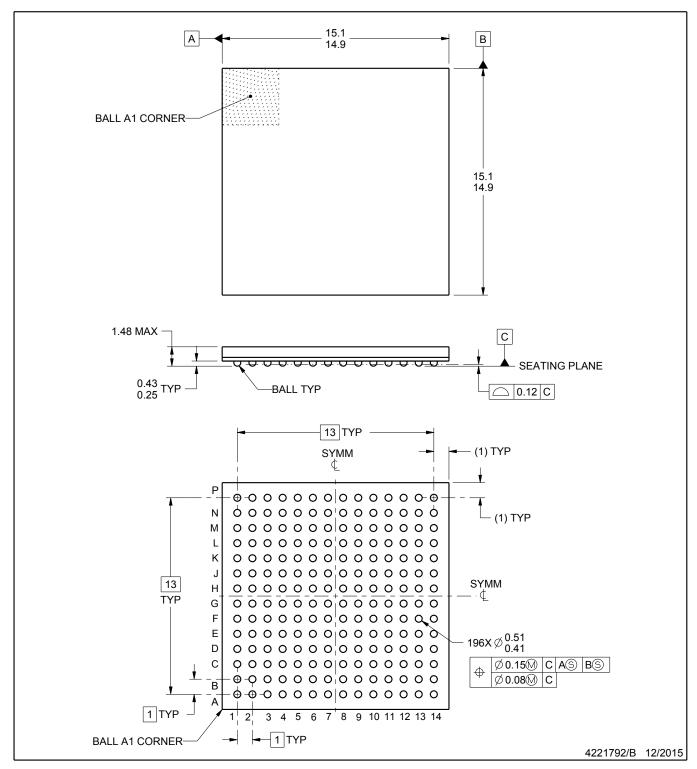

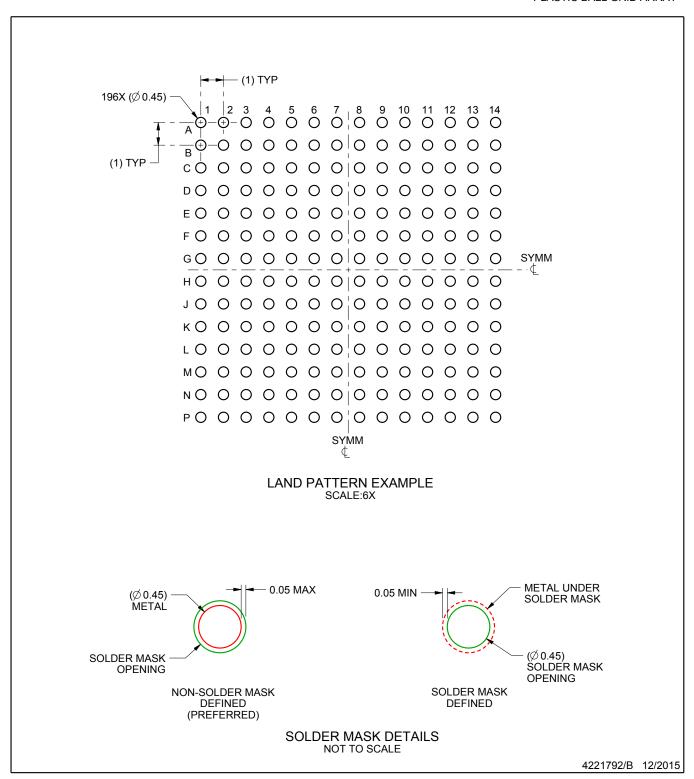

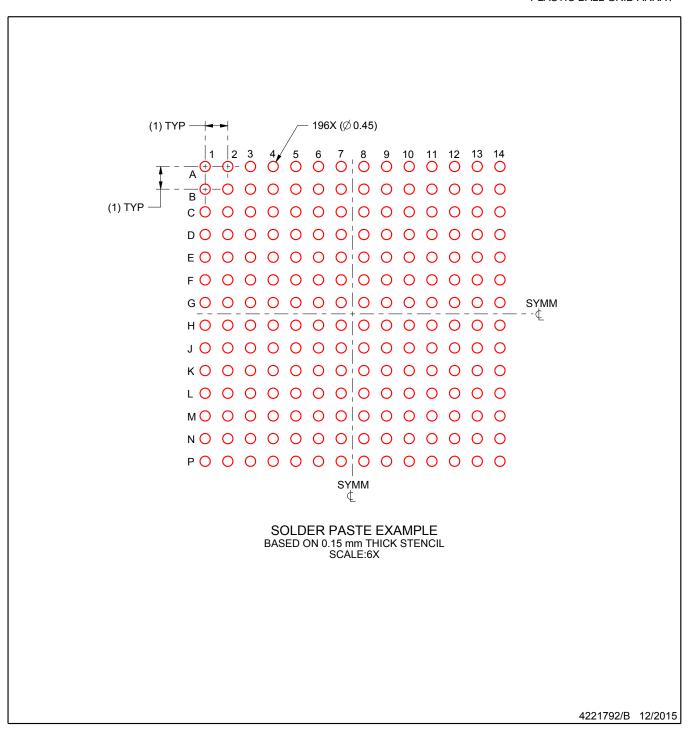

- 196-Ball, 15-mm x 15-mm NFBGA, 1-mm Pitch

# **Applications**

- **Optical Switches**

- **Optical Attenuators**

- Automatic Test Equipment (ATE)

- Instrumentation

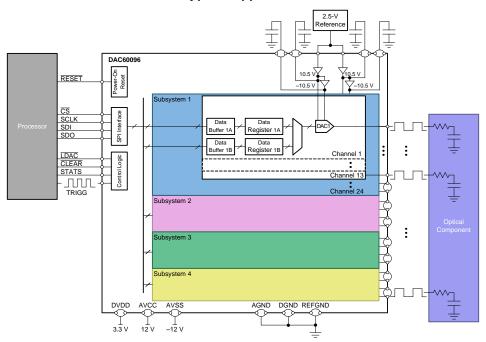

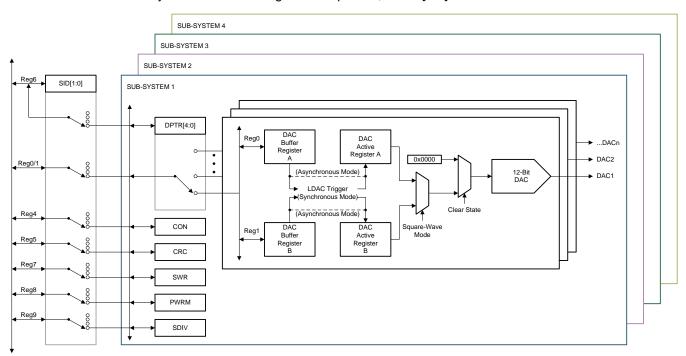

## 3 Description

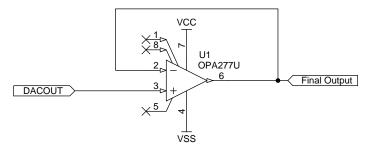

The DAC60096 is a low-power, fast-settling, 96channel, 12-bit, digital to analog converter (DAC). The device provides ±10.5-V unbuffered, bipolar voltage outputs. The DAC60096 high-channel count, low-power operation, and good linearity make it an ideal solution in systems where a very high number of precise analog outputs is required.

Communication to the device is performed through a high-speed, 4-wire, serial interface compatible with industry standard microprocessors microcontrollers.

The DAC60096 can be set up to clear or update all DACs simultaneously. In addition, a versatile external conversion trigger allows each DAC channel to operate square-wave generator as а independent amplitude control.

The DAC60096 is characterized for operation over the temperature range of -40°C to +85°C, and is available in a 196-ball, 15-mm x 15-mm, 1-mm pitch, BGA package.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| DAC60096    | NFBGA   | 15.0 mm × 15.0 mm |

(1) For all available packages, see the package option addendum at the end of the data sheet.

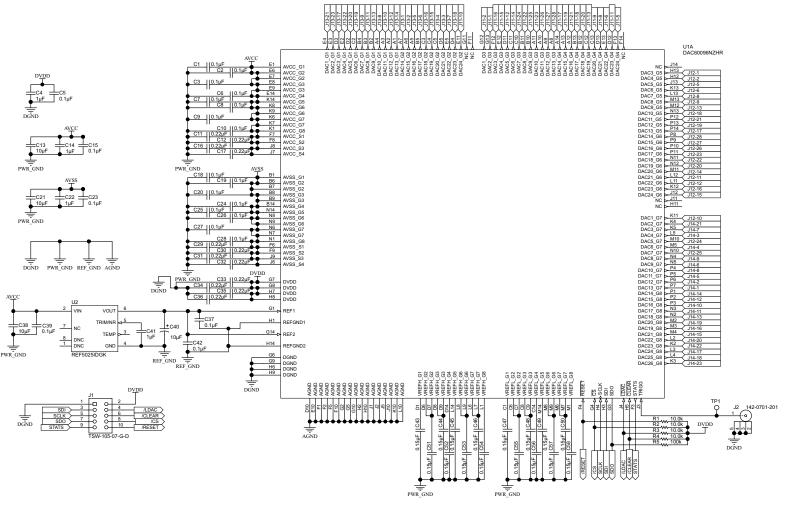

#### **Typical Application**

# **Table of Contents**

| 1 | Features 1                                           |    | 7.3 Feature Description                          | 19 |

|---|------------------------------------------------------|----|--------------------------------------------------|----|

| 2 | Applications 1                                       |    | 7.4 Device Functional Modes                      | 22 |

| 3 | Description 1                                        |    | 7.5 Programming                                  | 23 |

| 4 | Revision History2                                    |    | 7.6 Register Maps                                | 25 |

| 5 | Pin Configuration and Functions                      | 8  | Application and Implementation                   | 31 |

| 6 | Specifications6                                      |    | 8.1 Application Information                      | 31 |

| U | 6.1 Absolute Maximum Ratings                         |    | 8.2 Typical Application                          | 32 |

|   | 6.2 ESD Ratings                                      | 9  | Power Supply Recommendations                     | 36 |

|   | 6.3 Recommended Operating Conditions                 |    | 9.1 Device Reset Options                         | 36 |

|   | 6.4 Thermal Information                              | 10 | Layout                                           | 38 |

|   | 6.5 Electrical Characteristics: DAC DC               |    | 10.1 Layout Guidelines                           | 38 |

|   | 6.6 Electrical Characteristics: Square-Wave Output 8 |    | 10.2 Layout Examples                             | 38 |

|   | 6.7 Electrical Characteristics: General              | 11 | Device and Documentation Support                 | 45 |

|   | 6.8 Timing Requirements                              |    | 11.1 Documentation Support                       | 45 |

|   | 6.9 Typical Characteristics: DC Mode                 |    | 11.2 Community Resources                         | 45 |

|   | 6.10 Typical Characteristics: Toggle Mode            |    | 11.3 Trademarks                                  | 45 |

|   | 6.11 Typical Characteristics, General                |    | 11.4 Electrostatic Discharge Caution             | 45 |

| 7 | Detailed Description 18                              |    | 11.5 Glossary                                    | 45 |

| - | 7.1 Overview                                         | 12 | Mechanical, Packaging, and Orderable Information | 45 |

|   | S -                                                  |    |                                                  |    |

# 4 Revision History

| CI | hanges from Original (December 2015) to Revision A | Page |

|----|----------------------------------------------------|------|

| •  | Changed from product preview to production data    | 1    |

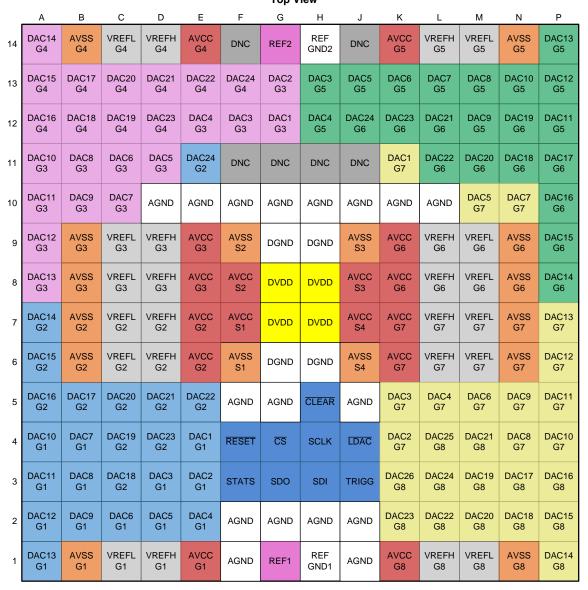

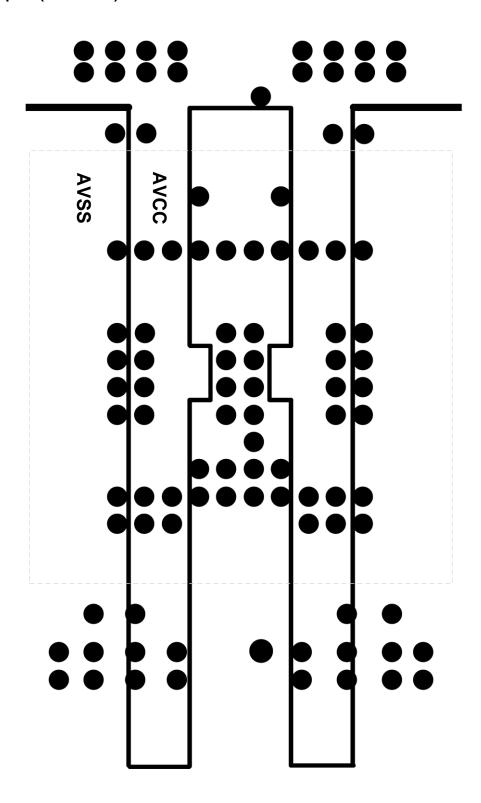

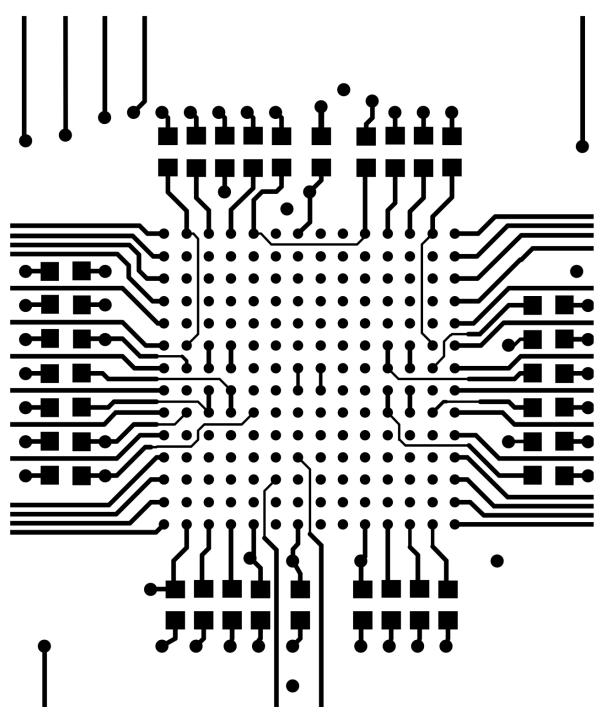

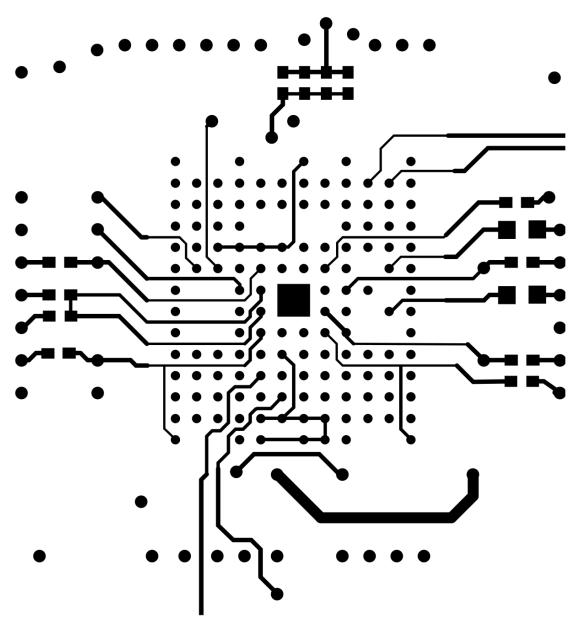

# 5 Pin Configuration and Functions

#### ZEB Package 196-Ball NFBGA Top View

Copyright © 2015–2016, Texas Instruments Incorporated

Submit Documentation Feedback

### **Pin Functions**

|               | PIN                                                                                    |      |                                                                                                                                                                                                                                                                                        |  |  |

|---------------|----------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.                                                                                    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                            |  |  |

| AGND          | D10, E10,<br>F1, F2, F5, F10,<br>G2, G5, G10, H2, H10,<br>J1, J2, J5, J10,<br>K10, L10 | GND  | Analog ground.                                                                                                                                                                                                                                                                         |  |  |

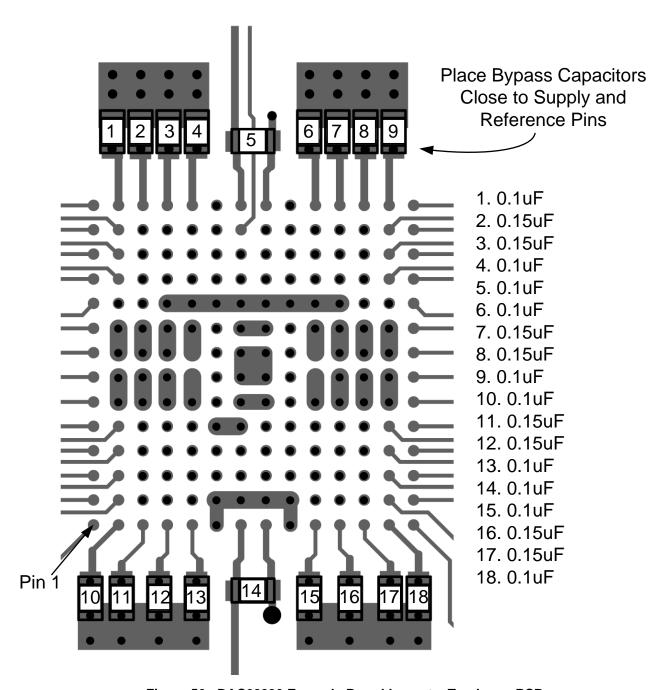

| AVCC          | E1, E6, E7, E8, E9, E14,<br>F7, F8, J7, J8,<br>K1, K6, K7, K8, K9, K14                 | PWR  | Positive analog supply voltage. (11.2 V to 12.6 V). A 100-nF bypass capacitor for each AVCC_n (n = G1, G2, G3, G4, G5, G6, G7, G8, S1, S2, S3 or S4) is required; place as close as possible to the pins.                                                                              |  |  |

| AVSS          | B1, B6, B7, B8, B9, B14,<br>F6, F9, J6, J9,<br>N1, N6, N7, N8, N9, N14                 | PWR  | Negative analog supply voltage. (-12.6V to -11.2V). A 100-nF bypass capacitor for each AVSS_n (n = G1, G2, G3, G4, G5, G6, G7, G8, S1, S2, S3 or S4) is required; place as close as possible to the pins.                                                                              |  |  |

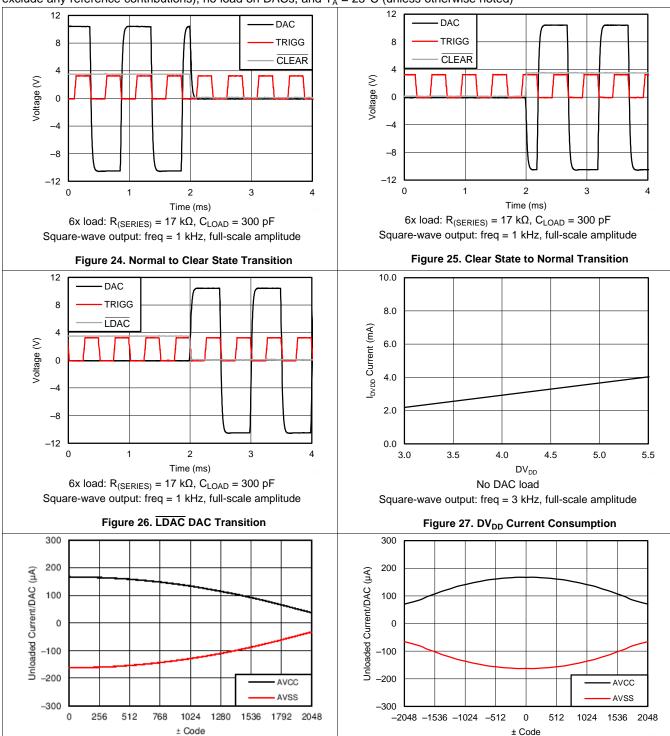

| CLEAR         | H5                                                                                     | I    | Asynchronous clear control input, active low. When CLEAR is low, all DACs are loaded with code 000h. When CLEAR is high, all DACs return to normal operation                                                                                                                           |  |  |

| <u>CS</u>     | G4                                                                                     | I    | Serial data enable, active low. This input is the frame synchronization signal for the serial data.                                                                                                                                                                                    |  |  |

| DAC[1-13]_G1  | A1, A2, A3, A4,<br>B2, B3, B4, C2, D2, D3,<br>E2, E3, E4                               | 0    | Subsystem 1 Regular DAC outputs: DAC group 1 and DAC group 2. Each DAC subsystem can be                                                                                                                                                                                                |  |  |

| DAC[14-26]_G2 | A5, A6, A7, B5,<br>C3, C4, C5,<br>D4, D5, E5, E11                                      | 0    | controlled independently through the serial interface.                                                                                                                                                                                                                                 |  |  |

| DAC[1-13]_G3  | A8, A9, A10, A11,<br>B10, B11, C10, C11,<br>D11, E12, F12, G12, G13                    | 0    | Subsystem 2 Regular DAC outputs: DAC group 3 and DAC group 4. Each DAC subsystem can be                                                                                                                                                                                                |  |  |

| DAC[14-24]_G4 | A12, A13, A14,<br>B12, B13, C12, C13,<br>D12, D13, E13, F13                            | 0    | controlled independently through the serial interface.                                                                                                                                                                                                                                 |  |  |

| DAC[3-13]_G5  | H12, H13, J13, K13, L13,<br>M12, M13, N13,<br>P12, P13, P14                            | 0    | Subsystem 3 Regular DAC outputs: DAC group 5 and DAC group 6. Each DAC subsystem can be                                                                                                                                                                                                |  |  |

| DAC[14-26]_G6 | J12, K12<br>L11, L12, M11, N11, N12,<br>P8, P9, P10, P11                               | 0    | controlled independently through the serial interface.                                                                                                                                                                                                                                 |  |  |

| DAC[1-13]_G7  | K4, K5, K11, L5,<br>M5, M10, N4, N5, N10,<br>P4, P5, P6, P7                            | 0    | Subsystem 4 Regular DAC outputs: DAC group 7 and DAC group 8. Each DAC subsystem can                                                                                                                                                                                                   |  |  |

| DAC[14-26]_G8 | K2, K3, L2, L3, L4,<br>M2, M3, M4, N2, N3,<br>P1, P2, P3                               | 0    | controlled independently through the serial interface.                                                                                                                                                                                                                                 |  |  |

| DGND          | G6, G9, H6, H9                                                                         | GND  | Digital ground. Ground reference point for all digital circuitry on the device.                                                                                                                                                                                                        |  |  |

| DNC           | F11, F14, G11<br>H11, J11, J14                                                         | _    | Reserved for factory use. For proper operation, do not connect.                                                                                                                                                                                                                        |  |  |

| DVDD          | G7, G8, H7, H8                                                                         | PWR  | Digital supply voltage. (3 V to $5.5$ V). A 100-nF bypass capacitor is required; place as close as possible to the pins.                                                                                                                                                               |  |  |

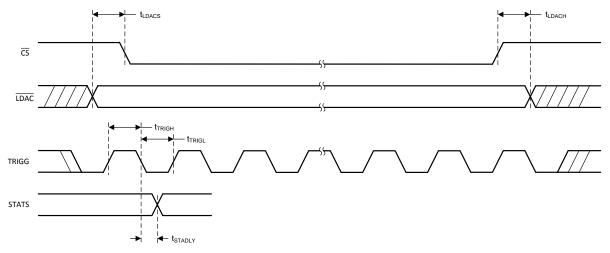

| LDAC          | J4                                                                                     | 1    | Synchronous DAC load control input, active low. When $\overline{\text{LDAC}}$ is low, the DAC outputs are updated immediately after a register write. If left high during DAC register updates, bringing $\overline{\text{LDAC}}$ low causes all DAC outputs to update simultaneously. |  |  |

| RESET         | F4                                                                                     | I    | Reset input, active low. Logic low on this pin causes the device to perform a hardware reset.                                                                                                                                                                                          |  |  |

| REFGND1       | H1                                                                                     | GND  | Reference ground. Ground reference point for REF1. REFGND1 should be star connected at the system GND source and not connected to the GND plane for best performance.                                                                                                                  |  |  |

| REFGND2       | H14                                                                                    | GND  | Reference ground. Ground reference point for REF2. REFGND2 should be star connected at the system GND source and not connected to the GND plane for best performance.                                                                                                                  |  |  |

| SCLK          | H4                                                                                     | I    | Serial interface clock.                                                                                                                                                                                                                                                                |  |  |

| SDI           | НЗ                                                                                     | I    | Serial interface data input. Data are clocked into the input shift register on each rising edge of SCLK.                                                                                                                                                                               |  |  |

| SDO           | G3                                                                                     | 0    | Serial interface data output. The SDO pin is in high impedance when $\overline{\text{CS}}$ is high. Data can be clocked out of the input shift register on either rising or falling edges of SCLK as specified by PHAINV in the CON register.                                          |  |  |

| STATS         | F3                                                                                     | 0    | DAC output status indicator. Identifies which of the two DAC data registers is active.                                                                                                                                                                                                 |  |  |

| REF1          | G1                                                                                     | I    | Input voltage reference pin 1 (2.5 V). A 100-nF bypass capacitor between this pin and REFGND1 is required.                                                                                                                                                                             |  |  |

| REF2          | G14                                                                                    | I    | Input voltage reference pin 2 (2.5 V). A 100-nF bypass capacitor between this pin and REFGND2 is required.                                                                                                                                                                             |  |  |

Submit Documentation Feedback

Copyright © 2015–2016, Texas Instruments Incorporated

# Pin Functions (continued)

|          | PIN                                                 | T)/DE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |

|----------|-----------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |                                                     | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |  |  |

| TRIGG    | J3                                                  | 1     | Trigger input signal. Enables all DAC outputs to toggle between the two DAC data registers associated with each DAC. This functionality enables the device to operate as a square-wave generator. The DAC registers are prepared for toggle mode operation on a TRIGG rising edge and the outputs are toggled on each following TRIGG falling edge. |  |  |

| VREFH    | D1, D6, D7, D8, D9, D14,<br>L1, L6, L7, L8, L9, L14 | 0     | Compensation capacitor connection for the internal 10.5 V reference voltage. A 100-nF bypass capacitor for each VREFH_n (n = G1, G2, G3, G4, G5, G6, G7 or G8) is required; place as close as possible to the pins.                                                                                                                                 |  |  |

| VREFL    | C1, C6, C7, C8, C9, C14, M1, M6, M7, M8, M9, M14    | 0     | Compensation capacitor connection for the internal -10.5 V reference voltage. A 100-nF bypass capacitor for each VREFL_n (n = G1, G2, G3, G4, G5, G6, G7 or G8) is required; place as close as possible to the pins.                                                                                                                                |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

|                |                                                              | MIN                    | MAX                    | UNIT |

|----------------|--------------------------------------------------------------|------------------------|------------------------|------|

|                | AV <sub>CC</sub> to DGND                                     | -0.3                   | 13                     |      |

| Supply voltage | AV <sub>SS</sub> to DGND                                     | -13                    | 0.3                    |      |

|                | DV <sub>DD</sub> to DGND                                     | -0.3                   | 6                      | V    |

| Supply voltage | AV <sub>CC</sub> to AV <sub>SS</sub>                         | -0.3                   | 26                     | V    |

|                | DGND to AGND                                                 | -0.3                   | 0.3                    |      |

|                | DGND to REFGND[1,2]                                          | -0.3                   | 0.3                    |      |

|                | REF1 to REFGND1                                              | -0.3                   | 6                      |      |

|                | REF2 to REFGND2                                              | -0.3                   | 6                      |      |

|                | DAC to DGND                                                  | AV <sub>SS</sub> - 0.3 | AV <sub>CC</sub> + 0.3 |      |

| Pin voltage    | CLEAR, CS, LDAC, RESET, SCLK, SDI, SDO, TRIGG, STATS to DGND | -0.3                   | DV <sub>DD</sub> + 0.3 | V    |

|                | VREFH to DGND                                                | -0.3                   | AV <sub>CC</sub> + 0.3 |      |

|                | VREFL to DGND                                                | AV <sub>SS</sub> - 0.3 | 0.3                    |      |

|                | VREFH to adjacent VREFL                                      | -0.3                   | 26                     |      |

| Temperature    | Operating, T <sub>A</sub>                                    | -40                    | 85                     |      |

|                | Junction, T <sub>J</sub>                                     | -40                    | 150                    | °C   |

|                | Storage, T <sub>stg</sub>                                    | -40                    | 150                    |      |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| .,                 | Flootrootatio diacharga | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                               | MIN   | NOM | MAX     | UNIT |

|-----------------------------------------------|-------|-----|---------|------|

| POWER SUPPLY                                  |       |     | •       |      |

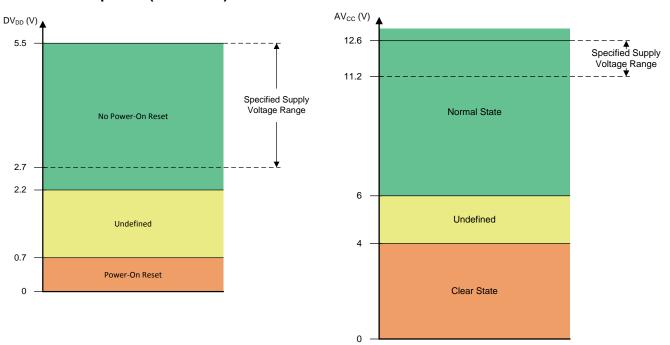

| AV <sub>CC</sub>                              | 11.2  | 12  | 12.6    | V    |

| AV <sub>SS</sub>                              | -12.6 | -12 | -11.2   | V    |

| $DV_DD$                                       | 3     | 3.3 | 5.5     | V    |

| AV <sub>CC</sub> to AV <sub>SS</sub>          | 22.4  | 24  | 25.2    | V    |

| DIGITAL INPUTS                                |       |     | ·       |      |

| Digital input voltage                         | 0     |     | $DV_DD$ | V    |

| REFERENCE INPUT                               |       |     |         |      |

| Reference input voltage, V <sub>REF</sub>     | 2.475 | 2.5 | 2.525   | V    |

| TEMPERATURE                                   |       |     |         |      |

| Operating ambient temperature, T <sub>A</sub> | -40   |     | 85      | °C   |

Copyright © 2015-2016, Texas Instruments Incorporated Product Folder Links: DAC60096

#### 6.4 Thermal Information

|                       |                                              | DAC60096    |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | ZEB (NFBGA) | UNIT |

|                       |                                              | 196 BALLS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 21.4        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 7.5         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 5.1         | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.4         | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 5.0         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

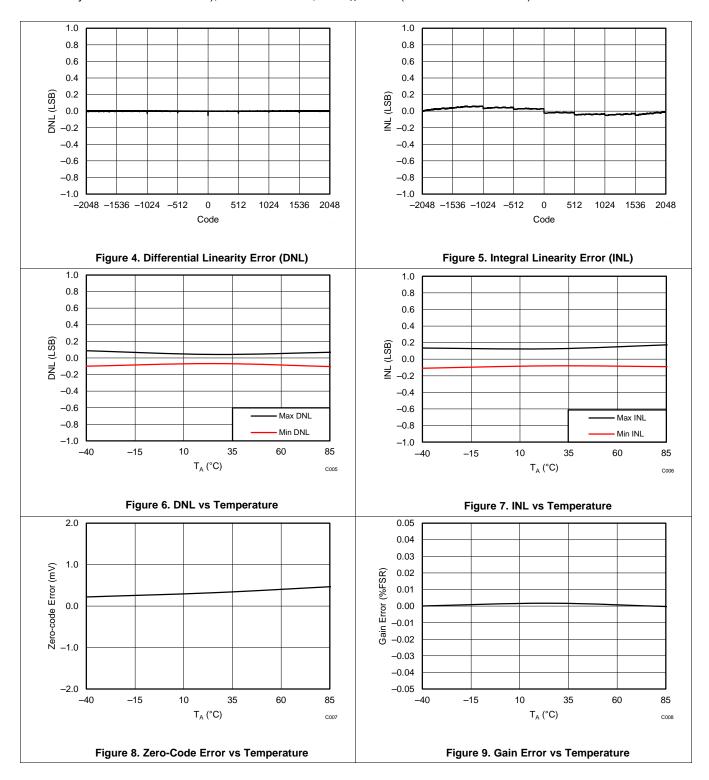

# 6.5 Electrical Characteristics: DAC DC

at AV<sub>CC</sub> = 11.2 V to 12.6 V, AV<sub>SS</sub> = -12.6 V to -11.2 V, DV<sub>DD</sub> = 3 V to 5.5 V, AGND = DGND = REFGND[1,2] = 0 V, REF1 = REF2 = 2.5 V (specifications exclude any reference contributions), no load on DACs, and  $T_A = -40$ °C to +85°C (unless otherwise noted)

|        | PARAMETER                 | TEST CONDITIONS                                                                                                                     | MIN   | TYP   | MAX   | UNIT               |

|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|

| STATIC | PERFORMANCE               |                                                                                                                                     |       |       |       |                    |

|        | Resolution                |                                                                                                                                     | 12    |       |       | Bits               |

| INL    | Relative accuracy         |                                                                                                                                     |       | ±0.15 | ±1    | LSB                |

| DNL    | Differential nonlinearity | Specified 12-bit monotonic                                                                                                          |       | ±0.1  | ±0.9  | LSB                |

|        | Gain error                | T <sub>A</sub> = 25°C                                                                                                               |       | ±0.05 | ±0.15 | %FSR               |

|        | Zero-code error           | T <sub>A</sub> = 25°C, code 000h                                                                                                    |       | ±2    | ±7    | mV                 |

|        | Gain error drift          |                                                                                                                                     |       | ±1    |       | ppm/°C             |

|        | Zero-code error drift     |                                                                                                                                     |       | ±1    |       | ppm/°C             |

| OUTPUT | CHARACTERISTICS           |                                                                                                                                     |       |       |       |                    |

|        | Output voltage            |                                                                                                                                     | -10.5 |       | 10.5  | V                  |

|        | Output impedance          |                                                                                                                                     |       | 41    |       | kΩ                 |

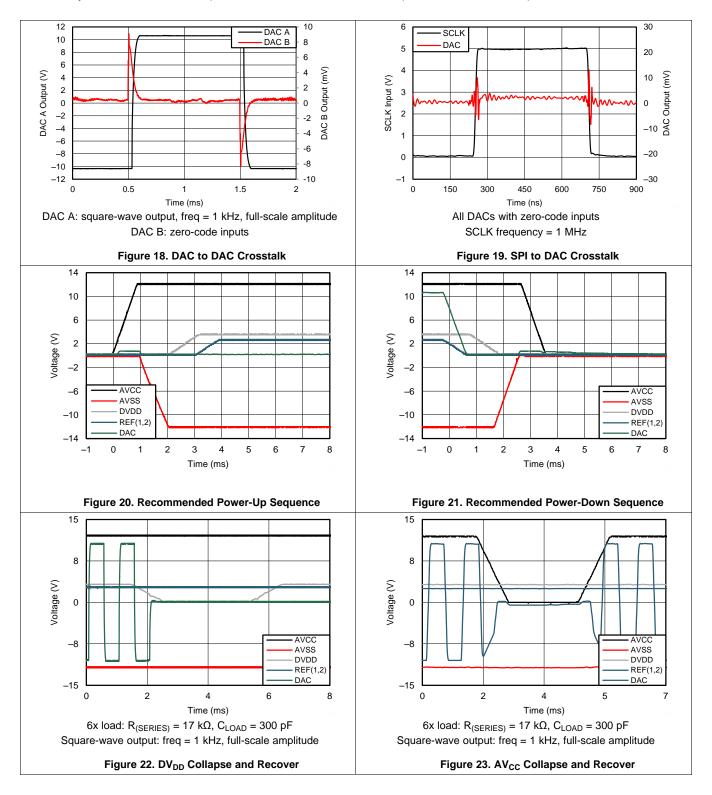

|        | DC crosstalk              | Measured channel at code 000h, all others transition from code 7FFh to 02Bh                                                         |       | 0.5   |       | LSB                |

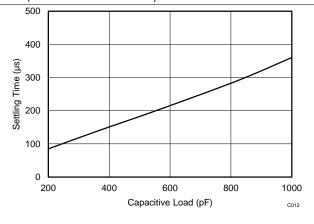

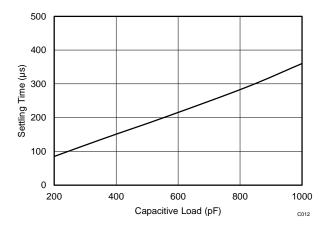

|        | Cattling time             | DAC ouput transition: code 800h to 7FFh to within 1 LSB, 6x load: $R_{(SERIES)} = 17 \text{ k}\Omega$ , $C_{LOAD} = 300 \text{ pF}$ |       | 160   |       |                    |

|        | Settling time             | DAC ouput transition: code 800h to 7FFh to within 1 LSB, 1x load: $R_{(SERIES)} = 100 \text{ k}\Omega$ , $C_{LOAD} = 50 \text{ pF}$ |       | 65    |       | μs                 |

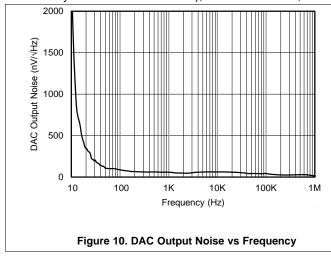

|        | Output noise              | T <sub>A</sub> = 25°C, 1 kHz, code 000h                                                                                             |       | 60    |       | nV/√ <del>Hz</del> |

### 6.6 Electrical Characteristics: Square-Wave Output

at  $AV_{CC}$  = 11.2 V to 12.6 V,  $AV_{SS}$  = -12.6 V to -11.2 V,  $DV_{DD}$  = 3 V to 5.5 V, AGND = DGND = REFGND[1,2] = 0 V, REF1 = REF2 = 2.5 V (specifications exclude any reference contributions), no load on DACs, and  $T_A$  = -40°C to +85°C (unless otherwise noted)

| PARAMETER                                            | TEST CONDITIONS                                                                                         | MIN | TYP | MAX | UNIT                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|-----|-----|----------------------|

| OAC OUTPUTS - 6x LOAD: R <sub>(SERIES)</sub> = 17 kΩ | t, C <sub>LOAD</sub> = 300 pF                                                                           |     |     |     |                      |

| Frequency                                            | For amplitude $\geq$ 9.1 V <sub>RMS</sub> , amplitude = $\pm$ 10.5 V <sub>PP</sub> , codes 7FFh to 801h |     | 3   |     | kHz                  |

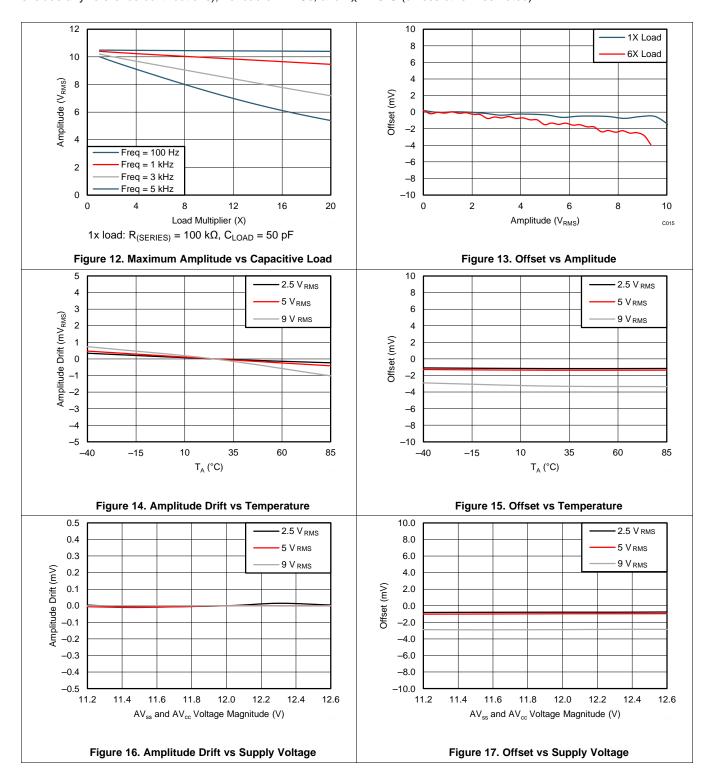

| Amalituda                                            | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | 9.1 |     |     | $V_{RMS}$            |

| Amplitude                                            | Frequency = 5 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | 8   |     |     | $V_{RMS}$            |

| Amplitude step precision                             | Frequency = 3 kHz, amplitude ≥ 1 V <sub>RMS</sub>                                                       |     |     | 6   | $mV_{RMS}$           |

| Amplitude temperature drift                          | Frequency = 3 kHz, amplitude = ±5 V <sub>PP</sub> , codes 3CFh to C31h                                  |     |     | 5   | $mV_{RMS}$           |

| Amplitude temperature drift                          | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               |     |     | 15  | $mV_{RMS}$           |

| Offertuality                                         | Frequency = 3 kHz, amplitude = ±5 V <sub>PP</sub> , codes 3CFh to C31h                                  | -10 |     | 10  | mV                   |

| Offset voltage                                       | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | -10 |     | 10  | mV                   |

| Rise and fall time                                   | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , 10% to 90%, codes 7FFh to 801h                   |     | 40  |     | μs                   |

| AC OUTPUTS - 1x LOAD: R <sub>(SERIES)</sub> = 100 k  | $\Omega$ , $C_{LOAD} = 50 \text{ pF}^{(1)}$                                                             |     |     |     |                      |

| Frequency                                            | For amplitude ≥ 9.1 V <sub>RMS</sub> , amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh and 801h          |     | 5   |     | kHz                  |

| Amplitude                                            | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | 10  |     |     | $V_{RMS}$            |

| Ampillude                                            | Frequency = 5 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | 9.5 |     |     | $V_{RMS}$            |

| Amplitude step precision                             | Frequency = 3 kHz, amplitude ≥ 1 V <sub>RMS</sub>                                                       |     |     | 7   | $mV_{RMS}$           |

| Amplitude temperature drift                          | Frequency = 3 kHz, amplitude = ±5 V <sub>PP</sub> , codes 3CFh to C31h                                  |     |     | 5   | $mV_{RMS}$           |

| Amplitude temperature drift                          | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               |     |     | 15  | ${\rm mV}_{\rm RMS}$ |

| Officet voltage                                      | Frequency = 3 kHz, amplitude = ±5 V <sub>PP</sub> , codes 3CFh to C31h                                  | -10 |     | 10  | mV                   |

| Offset voltage                                       | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> , codes 7FFh to 801h                               | -10 |     | 10  | mV                   |

| Rise and fall time                                   | Frequency = 3 kHz, amplitude = ±10.5 V <sub>PP</sub> ,<br>10% to 90%, codes 7FFh to 801h                |     | 10  |     | μs                   |

<sup>(1)</sup> Specified by design and characterization. Not tested during production.

Submit Documentation Feedback

#### 6.7 Electrical Characteristics: General

at AV<sub>CC</sub> = 11.2 V to 12.6 V, AV<sub>SS</sub> = -12.6 V to -11.2 V, DV<sub>DD</sub> = 3 V to 5.5 V, AGND = DGND = REFGND[1,2] = 0 V, REF1 = REF2 = 2.5 V (specifications exclude any reference contributions), no load on DACs, and  $T_A = -40$ °C to +85°C (unless otherwise noted)

|                     | PARAMETER                       | TEST CONDITIONS                                                | MIN                    | TYP   | MAX                  | UNIT |

|---------------------|---------------------------------|----------------------------------------------------------------|------------------------|-------|----------------------|------|

| EXTERNA             | AL REFERENCE INPUTS             |                                                                |                        |       |                      |      |

| $V_{REF}$           | Input voltage range             | REF1 and REF2 input pins                                       | 2.475                  | 2.5   | 2.525                | V    |

|                     | Reference input current         | Per input pin                                                  |                        | 1     |                      | μΑ   |

| DIGITAL             | LOGIC                           |                                                                |                        |       |                      |      |

| V <sub>IH</sub>     | High-level input voltage        |                                                                | $0.7 \times DV_{DD}$   |       |                      | V    |

| V <sub>IL</sub>     | Low-level input voltage         |                                                                |                        |       | $0.3 \times DV_{DD}$ | V    |

| V <sub>OH</sub>     | High-level output voltage       | I <sub>LOAD</sub> = 1 mA, SDO2x = 01                           | DV <sub>DD</sub> - 0.2 |       |                      | V    |

| V <sub>OL</sub>     | Low-level output voltage        | $I_{LOAD} = -1 \text{ mA}, SDO2x = 01$                         |                        |       | 0.4                  | V    |

|                     | Input capacitance               |                                                                |                        | 20    |                      | pF   |

| POWER F             | REQUIREMENTS (1)                |                                                                |                        |       |                      |      |

| I <sub>(AVCC)</sub> | AV <sub>CC</sub> supply current | 6x load:                                                       |                        | 18.1  | 25                   | mA   |

| I <sub>(AVSS)</sub> | AV <sub>SS</sub> supply current | $R_{(SERIES)} = 17 \text{ k}\Omega, C_{LOAD} = 300 \text{ pF}$ | -25                    | -18.1 |                      | mA   |

| I <sub>(DVDD)</sub> | DV <sub>DD</sub> supply current | frequency = 3 kHz 48 DAC outputs, codes 7FFh and 801h          |                        | 2     | 10                   | mA   |

|                     | Power consumption               | 48 DAC outputs, codes 117h and EE9h                            |                        | 440   |                      | mW   |

| I <sub>(AVCC)</sub> | AV <sub>CC</sub> supply current | 1x load:                                                       |                        | 17    | 22                   | mA   |

| I <sub>(AVSS)</sub> | AV <sub>SS</sub> supply current | $R_{(SERIES)} = 100 \text{ k}\Omega, C_{LOAD} = 50 \text{ pF}$ | -22                    | -17   |                      | mA   |

| I <sub>(DVDD)</sub> | DV <sub>DD</sub> supply current | frequency = 3 kHz 48 DAC outputs, codes 7FFh and 801h          |                        | 2     | 10                   | mA   |

|                     | Power consumption               | 48 DAC outputs, codes 117h and EE9h (2)                        |                        | 415   |                      | mW   |

| I <sub>(AVCC)</sub> | AV <sub>CC</sub> supply current |                                                                |                        | 25    | 30                   | mA   |

| I <sub>(AVSS)</sub> | AV <sub>SS</sub> supply current | 6x load:<br>$R_{(SERIES)} = 17 kΩ$ , $C_{LOAD} = 300 pF$       | -30                    | -25   |                      | mA   |

| I <sub>(DVDD)</sub> | DV <sub>DD</sub> supply current | frequency = 3 kHz                                              |                        | 2     | 10                   | mA   |

|                     | Power consumption               | All DAC outputs, codes 02Bh and FD5h                           |                        | 650   | 760                  | mW   |

<sup>(1)</sup> Power requirements tested unloaded during production. Load current contribution to power consumption specified by design and characterization.

<sup>(2)</sup> Specified by design and characterization. Not tested during production.

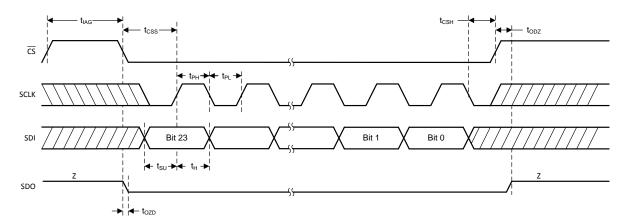

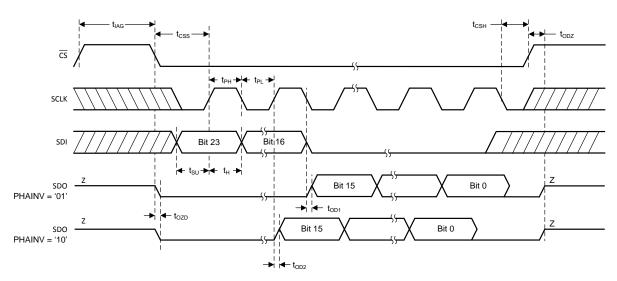

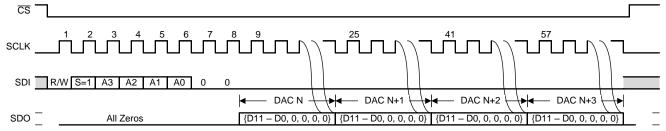

# 6.8 Timing Requirements(1)(2)

at  $AV_{CC}$  = 11.2 V to 12.6 V,  $AV_{SS}$  = -12.6 V to -11.2 V,  $DV_{DD}$  = 3 V to 5.5 V, AGND = DGND = REFGND[1,2] = 0 V, REF1 = REF2 = 2.5 V (specifications exclude any reference contributions), no load on DACs, and  $T_A$  = -40°C to +85°C (unless otherwise noted)

|                              |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MIN | NOM | MAX | UNIT |

|------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SERIAL IN                    | ITERFACE – DEFAULT MOD  | DE: SDO2X = 01, PHAINV = 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •   |     |     |      |

| ,                            | 0011/.                  | Write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     | 32  | MHz  |

| f <sub>SCLK</sub>            | SCLK frequency          | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     | 18  | MHz  |

|                              | 00114                   | Write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14  |     |     | ns   |

| t <sub>PH</sub>              | SCLK pulse width high   | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26  |     |     | ns   |

|                              | OOLK and an of the law  | Write operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14  |     |     | ns   |

| t <sub>PL</sub>              | SCLK pulse width low    | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26  |     |     | ns   |

| t <sub>SU</sub>              | SDI setup               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5   |     |     | ns   |

| t <sub>H</sub>               | SDI hold                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |     |     | ns   |

| t <sub>CSS</sub>             | CS setup                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10  |     |     | ns   |

| t <sub>CSH</sub>             | CS hold                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20  |     |     | ns   |

| t <sub>IAG</sub>             | Inter-access gap        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70  |     |     | ns   |

| t <sub>ODZ</sub>             | SDO driven to tri-state | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   |     | 20  | ns   |

| t <sub>OZD</sub>             | SDO tri-state to driven | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   |     | 20  | ns   |

| t <sub>OD1</sub>             | SDO output delay        | Read operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0   |     | 20  | ns   |

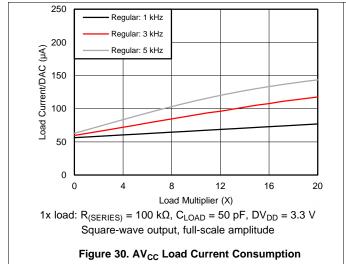

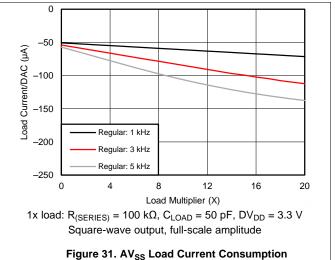

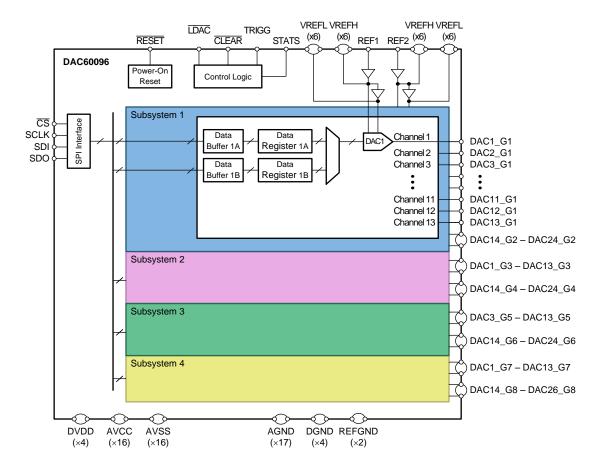

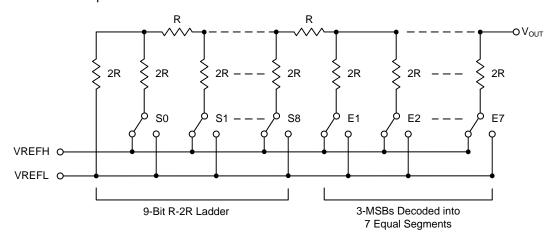

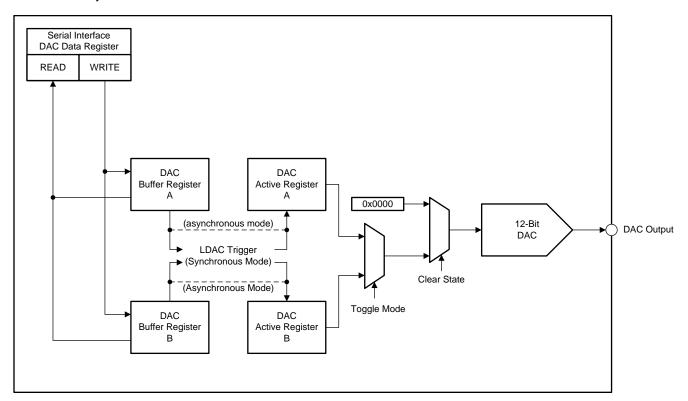

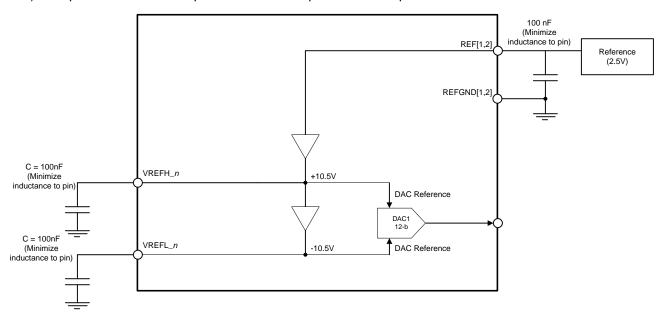

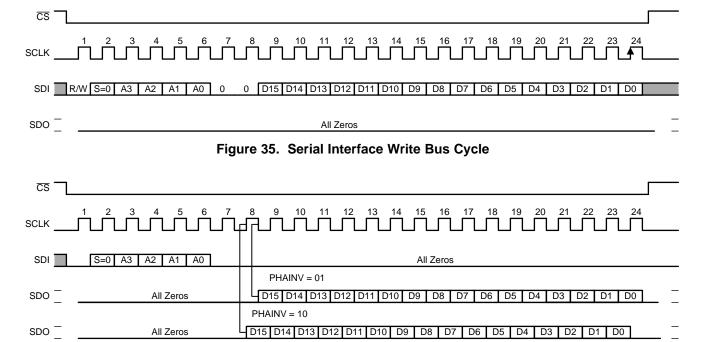

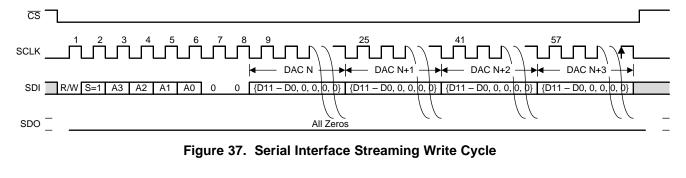

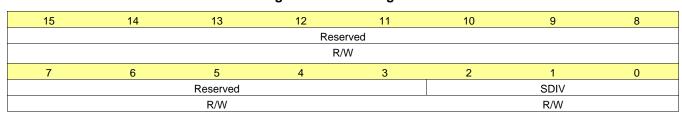

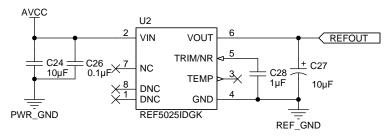

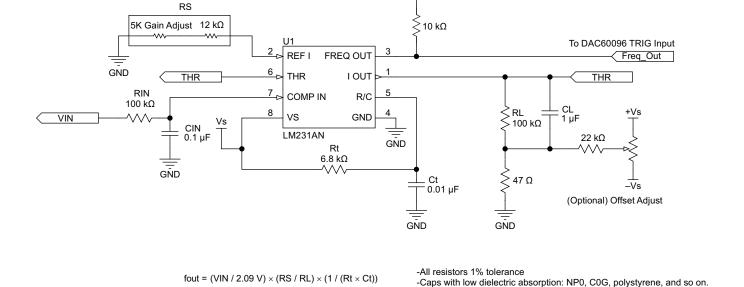

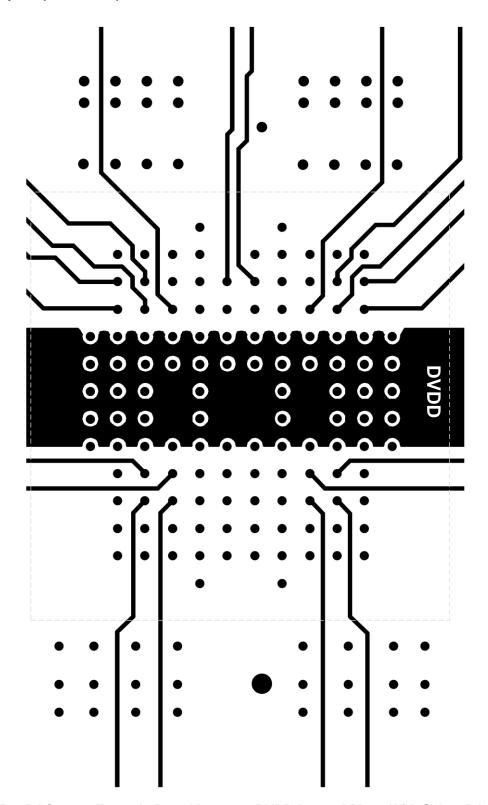

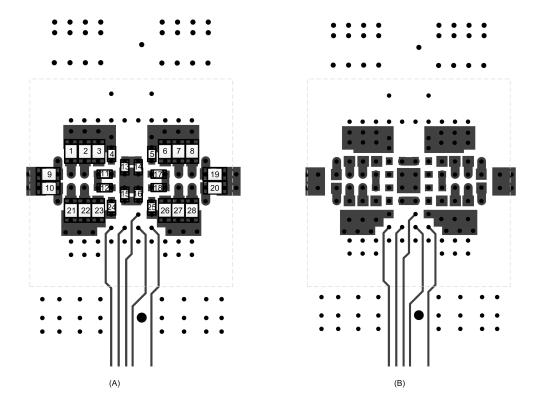

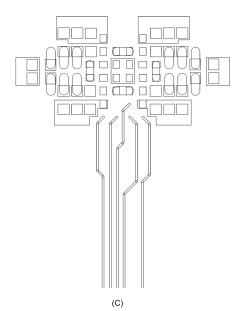

|                              | ITERFACE - FAST MODE: S | SDO2X = 10, PHAINV = 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |     |     |      |