# DAC39RF20: 22GSPS or 44GSPS, 16-bit, Single and Dual Channel, Multi-Nyquist Digital-to-Analog Converter (DAC) with JESD204C Interface

#### 1 Features

- · 16-bit Multi-Nyquist DAC core

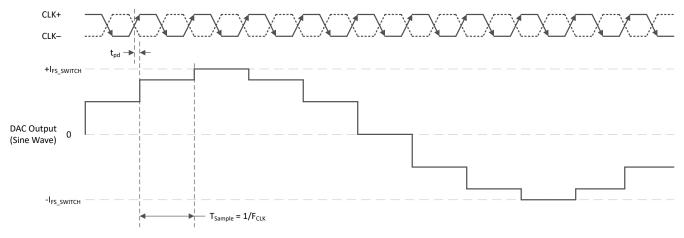

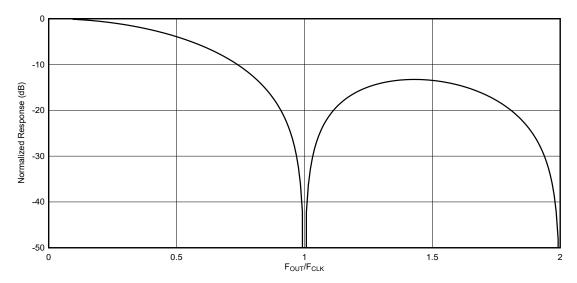

- DAC sample rate:

- NRZ, RF Modes: 22GSPS

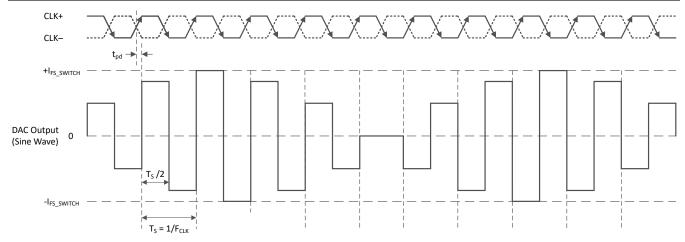

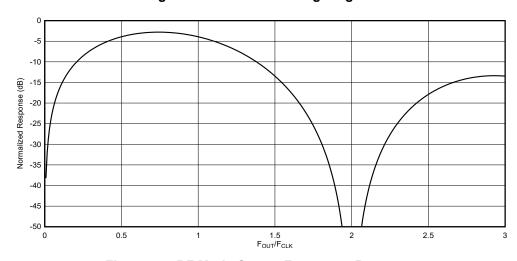

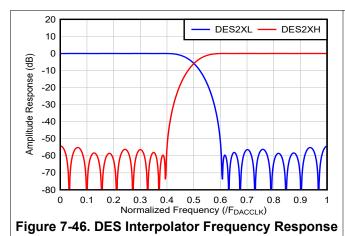

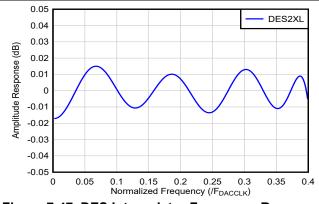

- DES2xL, DES2xH modes: 44GSPS

- Maximum input data rate:

- 12-bit, Dual channel: 21GSPS/ch

- 16-bit, Dual channel: 15.75GSPS/ch

- 16-bit, Single channel: 22GSPS

- Output frequency range: >18GHz

- Performance at f<sub>OUT</sub> = 10GHz, DES2xL mode

- Noise floor (small signal): –170dBFS/Hz

- SFDR (-0.1dBFS): -55dBc

- IMD3 (-7dBFS each tone): –60dBc

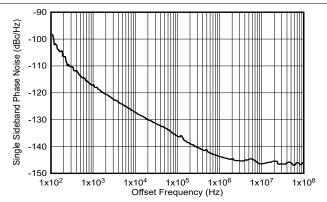

- Additive phase noise, 10kHz offset: -132dBc/Hz

- Optional PLL/VCO for DAC clock generation

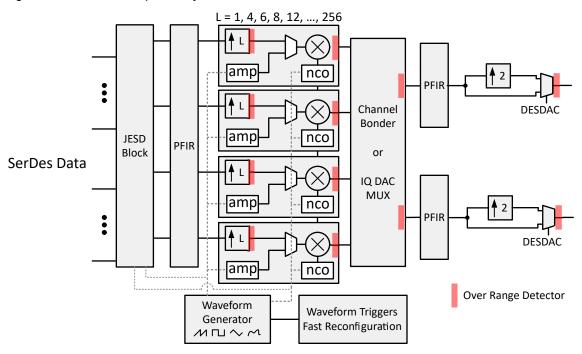

- Four integrated digital up-converters (DUC)

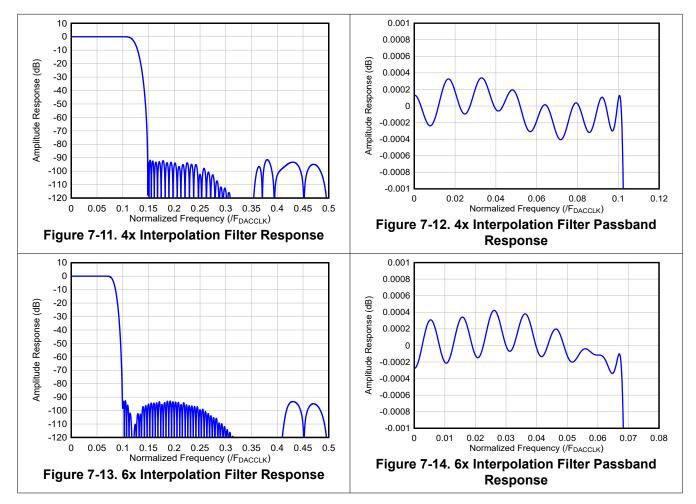

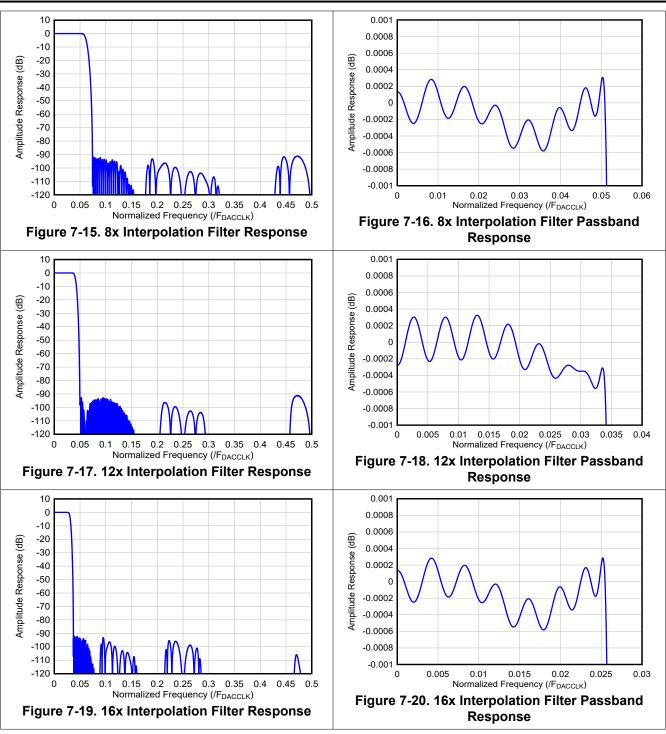

- Interpolation: 1x, 4x, 6x, 8x to 256x

- Complex baseband DUC for I/Q output

- Complex to real upconversion for direct RF sampling

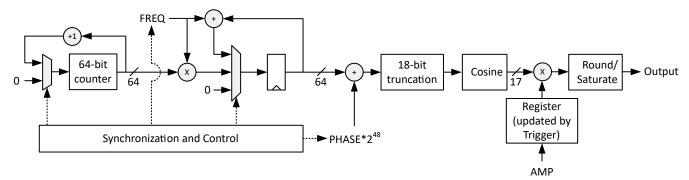

- 64-bit frequency resolution NCOs

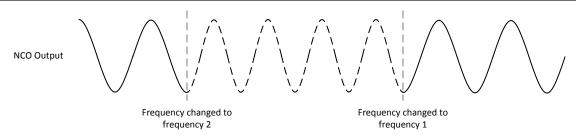

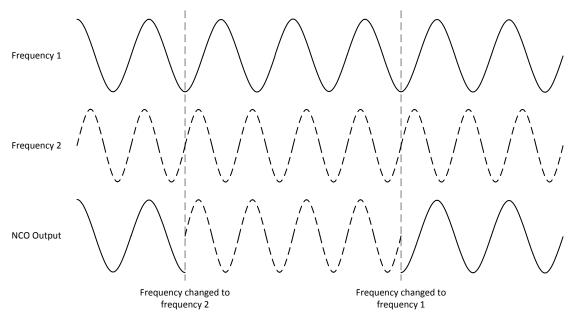

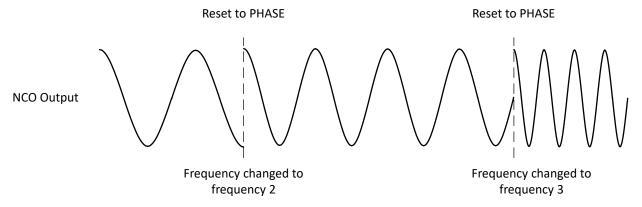

- Phase continuous, synchronous and reset options with frequency hopping

- Programmable FIR equalizer at DUC input or DAC input

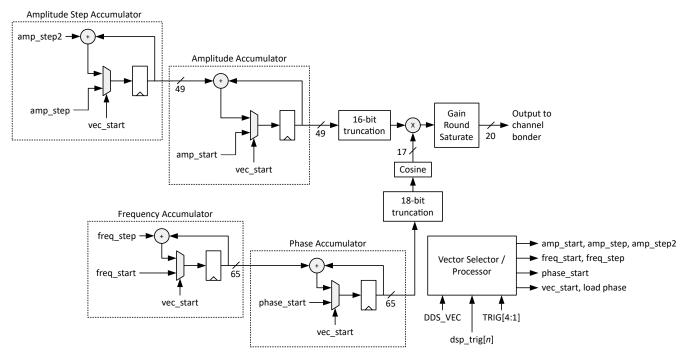

- Direct digital synthesis (DDS) functions

- Four piecewise linear waveform generators

- 16 Prestored waveforms

- · 256 Total vectors

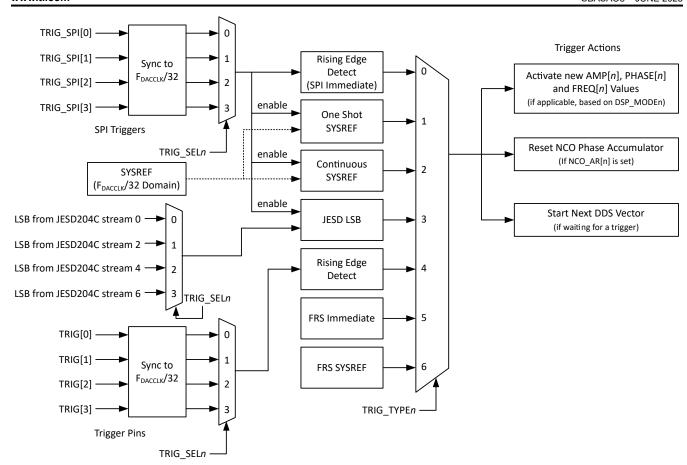

- Automatic or synchronous external triggers

- Frequency, amplitude, phase interface streaming

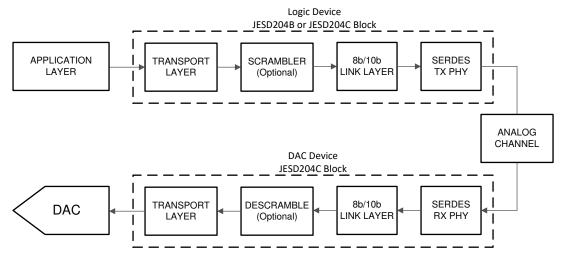

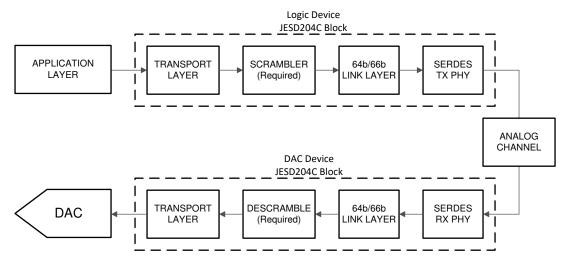

- JESD204C Interface

- 16 Lanes at up to 32.5Gbps

- Class C-S, subclass-1 compatible

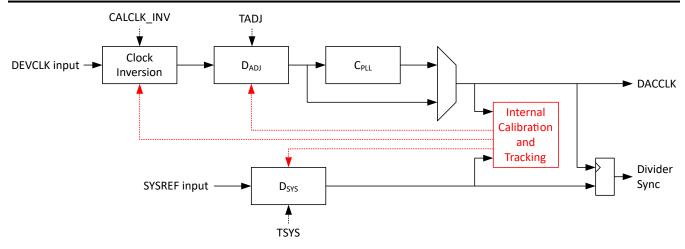

- Automatic clock and SYSREF calibration and tracking

# 2 Applications

- Satellite Communications (SATCOM)

- Phased Array Antenna Systems

- Synthetic Aperture Radar (SAR) Exciter

- Wireless Communications Testers

- Arbitrary Waveform Generator (AWG)

#### 3 Description

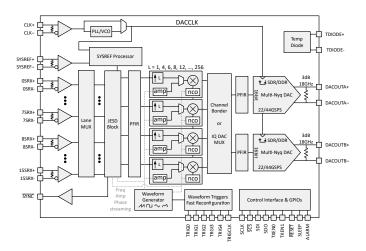

The DAC39RF20 is a single and dual channel digitalto-analog converter (DAC) with 16-bit resolution. With an external full rate clock, the devices support 22GSPS with single edge sampling modes (NRZ and RF) and 44GSPS in dual edge sampling modes (DES2XL, DES2XH). When using the internal PLL/ VCO, the devices support 17GSPS with single edge sampling modes (NRZ and RF) and 34GSPS in dual edge sampling modes (DES2XL, DES2XH). The devices can be used as noninterpolating or interpolating DACs for either direct RF sampling or complex baseband signal generation. The maximum input data rate for two channels is 21GSPS (12-bit resolution) or 15.75GSPS (16-bit resolution). The maximum rate for one channel is 22GSPS (16-bit resolution). The device can generate signals greater than 10GHz bandwidth at frequencies exceeding 20GHz, enabling direct sampling through Ku band.

#### **Package Information**

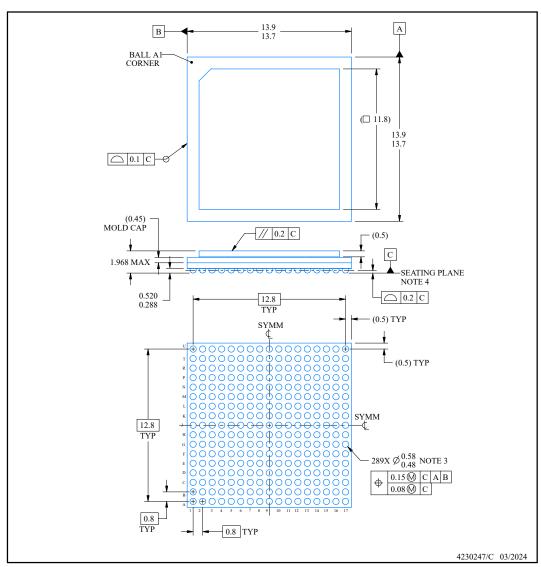

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup>     |

|-------------|------------------------|---------------------------------|

| DAC39RF20   | FCCSP (289 balls)      | 13.8mm × 13.8mm,<br>0.8mm pitch |

- (1) For more information, see Section 12.

- (2) The package size (length × width) is a nominal value and includes pins, where applicable.

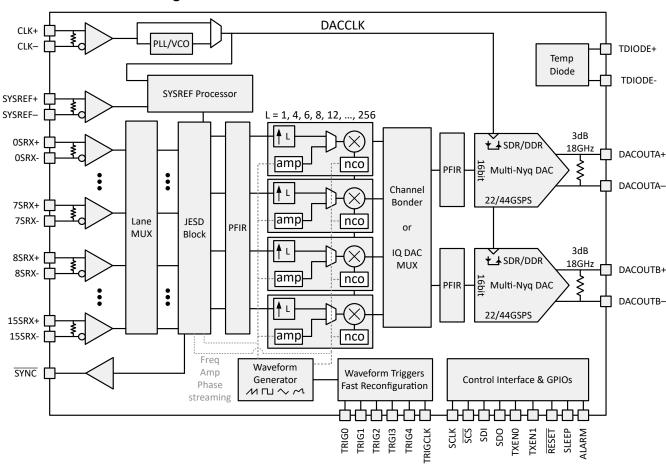

**Block Diagram**

# **4 Device Comparison**

|                                                 | Feature/Specification           | DAC39RF20 Generation 1                                                                         | DAC39RF2x Generation 2                               |

|-------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                                 | F <sub>DACCLK</sub>             | 8.125GHz ≤ F <sub>DACCLK</sub> ≤ 17GHz                                                         | 0.8GHz ≤ F <sub>DACCLK</sub> ≤ 22GHz                 |

|                                                 | PLL Output Divider              | 1x only                                                                                        | 1, 2, 4, 8 or 16x                                    |

| PLL/VCO                                         | CPLL_MPY                        | 8 to 99                                                                                        | 6 to 256                                             |

| PLL/VCO Phase Noise                             |                                 |                                                                                                | 5dB better between 100kHz≤F <sub>OFFSET</sub> ≤10MHz |

|                                                 | Multi-device<br>Synchronization | No                                                                                             | Yes                                                  |

| SYSREF Windowing for F <sub>DACCLK</sub> <10GHz |                                 | No                                                                                             | Yes                                                  |

| Timestamp Output                                |                                 | No                                                                                             | Yes                                                  |

| SPI readable temp se                            | nsor                            | No (temp diode is available)                                                                   | Yes                                                  |

| SerDes Loss of Signa                            | l Detector                      | No                                                                                             | Yes                                                  |

| Maximum SPI Clock F                             | requency                        | 15MHz                                                                                          | >50MHz (target)                                      |

| DDS Streaming Trigge                            | er                              | AMP = 0                                                                                        | AMP = 0 and PHASE[0]=1                               |

| SOFT_RESET                                      |                                 | does not properly clear registers in an address range of 0x0080 to 0x00FE. Use external RESET. | Fixed                                                |

| HD2                                             |                                 |                                                                                                | improved by 10 to 20dB                               |

Submit Document Feedback

# **Table of Contents**

| 1 Features                                         | 1  | 8.3 Register Maps                                   | 112 |

|----------------------------------------------------|----|-----------------------------------------------------|-----|

| 2 Applications                                     | 1  | 8.3.1 Standard_SPI-3.1 Registers                    | 113 |

| 3 Description                                      | 1  | 8.3.2 System Registers                              |     |

| 4 Device Comparison                                |    | 8.3.3 Trigger Registers                             |     |

| 5 Pin Configuration and Functions                  |    | 8.3.4 CPLL_AND_CLOCK Registers                      |     |

| 6 Specifications                                   | 8  | 8.3.5 SYSREF Registers                              |     |

| 6.1 Absolute Maximum Ratings                       |    | 8.3.6 JESD204C Registers                            |     |

| 6.2 ESD Ratings                                    |    | 8.3.7 JESD204C Advanced Registers                   |     |

| 6.3 Recommended Operating Conditions               |    | 8.3.8 SerDes_Equalizer Registers                    |     |

| 6.4 Thermal Information                            |    | 8.3.9 SerDes_Eye-Scan Registers                     |     |

| 6.5 Electrical Characteristics - DC Specifications |    | 8.3.10 SerDes_Lane_Status Registers                 |     |

| 6.6 Electrical Characteristics - AC Specifications |    | 8.3.11 SerDes PLL Registers                         |     |

| 6.7 Electrical Characteristics - Power Consumption |    | 8.3.12 DAC_and_Analog_Configuration Registers       |     |

| 6.8 Timing Requirements                            |    | 8.3.13 Datapath Registers                           |     |

| 6.9 Switching Characteristics                      |    | 8.3.14 NCO_and_Mixer Registers                      |     |

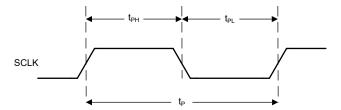

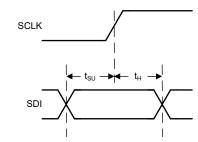

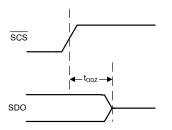

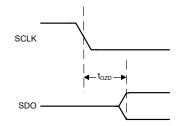

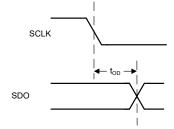

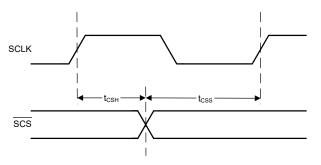

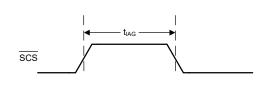

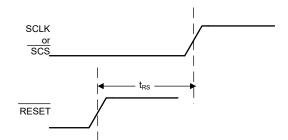

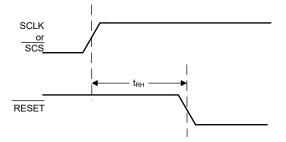

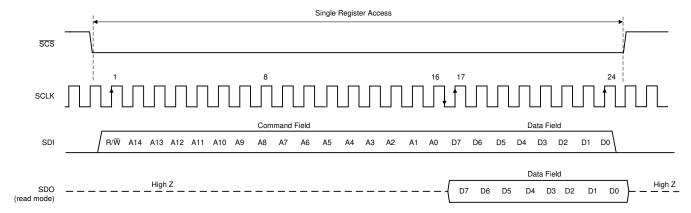

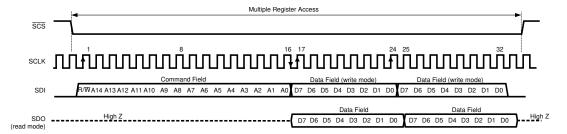

| 6.10 SPI Interface Timing Diagrams                 |    | 8.3.15 Alarm Registers                              |     |

| 7 Detailed Description                             |    | 8.3.16 Fuse_Control Registers                       |     |

| 7.1 Overview                                       |    | 8.3.17 Fuse Backed Registers                        |     |

| 7.2 Functional Block Diagram                       |    | 8.3.18 DDS_Vector_Mode Registers                    |     |

| 7.3 Feature Description                            |    | 8.3.19 Programmable_FIR Registers                   |     |

| 7.3.1 DAC Output Modes                             |    | 9 Application and Implementation                    |     |

| 7.3.2 DAC Core                                     |    | 9.1 Application Information                         |     |

| 7.3.3 DEM and Dither                               |    | 9.1.1 Startup Procedure                             |     |

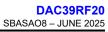

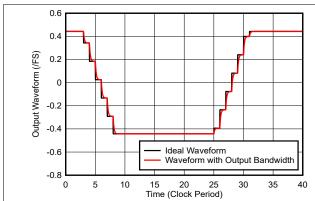

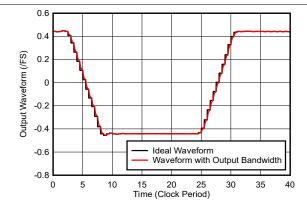

| 7.3.4 Offset Adjustment                            |    | 9.1.2 Bandwidth Optimization for Square Wave        |     |

| 7.3.5 Clocking Subsystem                           |    | Mode                                                | 221 |

| 7.3.6 Digital Signal Processing Blocks             |    | 9.2 Typical Application: Ku-Band Radar Transmitter. |     |

| 7.3.7 Serdes Physical Layer                        |    | 9.2.1 Design Requirements                           |     |

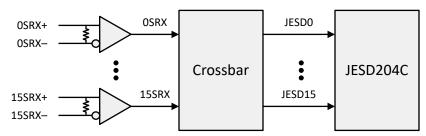

| 7.3.8 JESD204C Interface                           |    | 9.2.2 Detailed Design Procedure                     |     |

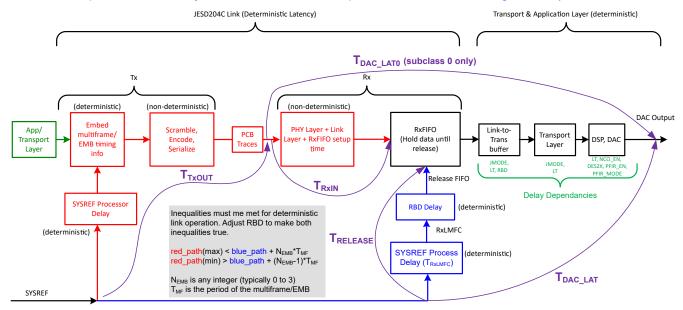

| 7.3.9 Data Path Latency                            |    | 9.2.3 Application Curves                            |     |

| 7.3.10 Multi-Device Synchronization and            |    | 9.3 Power Supply Recommendations                    |     |

| Deterministic Latency                              | 98 | 9.3.1 Power Up and Down Sequence                    |     |

| 7.3.11 Link Reset                                  |    | 9.4 Layout                                          |     |

| 7.3.12 Alarm Generation                            |    | 9.4.1 Layout Guidelines and Example                 |     |

| 7.3.13 Mute Function                               |    | 10 Device and Documentation Support                 |     |

| 7.4 Device Functional Modes                        |    | 10.1 Documentation Support                          |     |

| 7.4.1 Power Modes                                  |    | 10.1.1 Related Documentation                        |     |

| 8 Programming                                      |    | 10.2 Receiving Notification of Documentation Updat  |     |

| 8.1 Using the Standard SPI Interface               |    | 10.3 Support Resources                              |     |

| 8.1.1 SCS                                          |    | 10.4 Trademarks                                     |     |

| 8.1.2 SCLK                                         |    | 10.5 Electrostatic Discharge Caution                |     |

| 8.1.3 SDI                                          |    | 10.6 Glossary                                       |     |

| 8.1.4 SDO                                          |    | 11 Revision History                                 |     |

| 8.1.5 Serial Interface Protocol                    |    | 12 Mechanical, Packaging, and Orderable             | 00  |

| 8.1.6 Streaming Mode                               |    | Information                                         | 235 |

| 8 2 Using the East Reconfiguration Interface       |    |                                                     | 00  |

# **5 Pin Configuration and Functions**

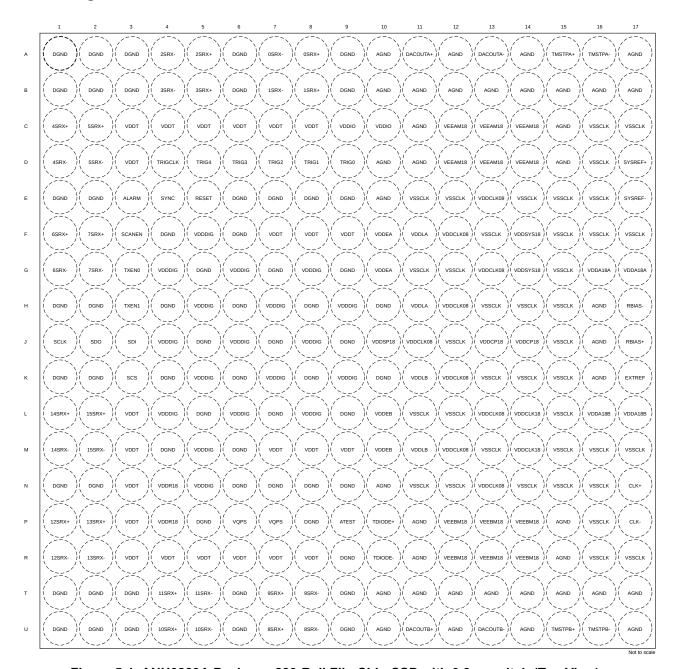

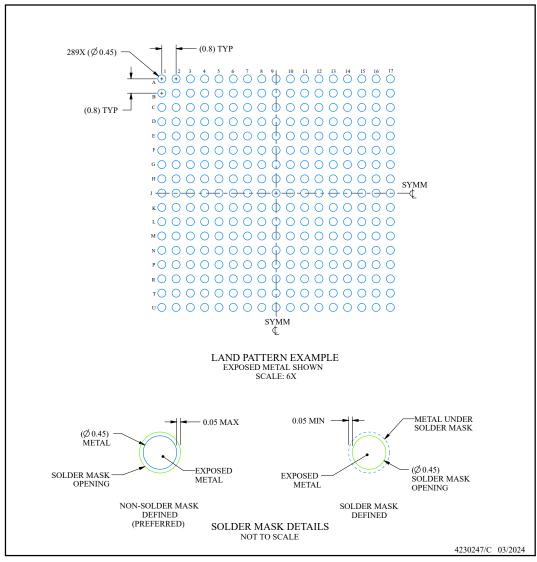

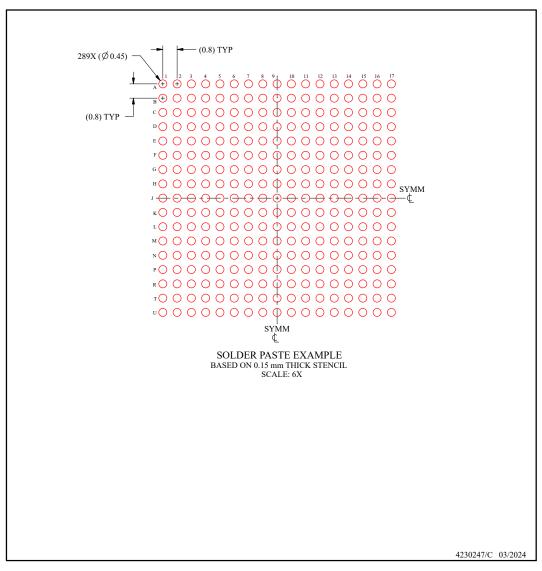

Figure 5-1. ANH0289A Package, 289-Ball Flip Chip CSP with 0.8mm pitch (Top View)

#### **Table 5-1. Pin Functions**

|                   | PIN                  |      | Table 5-1. Pin Functions                                                                                                                                                                                                                                                                                   |

|-------------------|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO                   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                |

| DAC Outputs       | NO                   |      |                                                                                                                                                                                                                                                                                                            |

| DAC Outputs       |                      |      | DAC channel A analog output negative terminal. Output voltage must comply with DAC compliance                                                                                                                                                                                                              |

| DACOUTA-          | A13                  | 0    | voltage to maintain specified performance.                                                                                                                                                                                                                                                                 |

| DACOUTA+          | A11                  | 0    | DAC channel A analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                                                                                                                                   |

| DACOUTB-          | U13                  | 0    | DAC channel B analog output negative terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                                                                                                                                   |

| DACOUTB+          | U11                  | 0    | DAC channel B analog output positive terminal. Output voltage must comply with DAC compliance voltage to maintain specified performance.                                                                                                                                                                   |

| Differential Cloc | ck and SYSREF Inputs |      |                                                                                                                                                                                                                                                                                                            |

| CLK-              | P17                  | ı    | Device clock input negative terminal. There is an internal $100\Omega$ differential termination between CLK+                                                                                                                                                                                               |

| CLN-              | PII                  | '    | and CLK This input is self-biased and should be AC coupled to the clock source.                                                                                                                                                                                                                            |

| CLK+              | N17                  | I    | Device clock input positive terminal. There is an internal $100\Omega$ differential termination between CLK+ and CLK–. This input is self-biased and should be AC coupled to the clock source.                                                                                                             |

| SYSREF-           | E17                  | I    | Differential JESD204C SYSREF input negative terminal. There is an internal $100\Omega$ differential termination between SYSREF+ and SYSREF This input is self-biased if AC coupled. If DC coupled, the input common mode must meet the $V_{\text{CMI}}$ specification in Recommended Operating Conditions. |

| SYSREF+           | D17                  | I    | Differential JESD204C SYSREF input negative terminal. There is an internal 100Ω differential termination between SYSREF+ and SYSREF–.                                                                                                                                                                      |

| SerDes Interfac   | e                    |      |                                                                                                                                                                                                                                                                                                            |

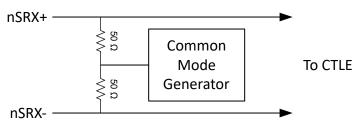

| 0SRX-             | A7                   | I    | Serdes Lane 0 negative input. Includes 100Ω internal termination to 0SRX+.                                                                                                                                                                                                                                 |

| 0SRX+             | A8                   | I    | Serdes Lane 0 positive input. Includes 100Ω internal termination to 0SRX                                                                                                                                                                                                                                   |

| 1SRX-             | B7                   | I    | Serdes Lane 1 negative input. Includes 100Ω internal termination to 1SRX+.                                                                                                                                                                                                                                 |

| 1SRX+             | B8                   | I    | Serdes Lane 1 positive input. Includes 100Ω internal termination to 1SRX                                                                                                                                                                                                                                   |

| 2SRX-             | A4                   | I    | Serdes Lane 2 negative input. Includes 100Ω internal termination to 2SRX+.                                                                                                                                                                                                                                 |

| 2SRX+             | A5                   | ı    | Serdes Lane 2 positive input. Includes 100Ω internal termination to 2SRX                                                                                                                                                                                                                                   |

| 3SRX-             | B4                   | ı    | Serdes Lane 3 negative input. Includes 100Ω internal termination to 3SRX+.                                                                                                                                                                                                                                 |

| 3SRX+             | B5                   | ı    | Serdes Lane 3 positive input. Includes 100Ω internal termination to 3SRX                                                                                                                                                                                                                                   |

| 4SRX-             | D1                   | ı    | Serdes Lane 4 negative input. Includes 100Ω internal termination to 4SRX+.                                                                                                                                                                                                                                 |

| 4SRX+             | C1                   | ı    | Serdes Lane 4 positive input. Includes 100Ω internal termination to 4SRX                                                                                                                                                                                                                                   |

| 5SRX-             | D2                   | ı    | Serdes Lane 5 negative input. Includes 100Ω internal termination to 5SRX+.                                                                                                                                                                                                                                 |

| 5SRX+             | C2                   | ı    | Serdes Lane 5 positive input. Includes 100Ω internal termination to 5SRX                                                                                                                                                                                                                                   |

| 6SRX-             | G1                   | ı    | Serdes Lane 6 negative input. Includes 100Ω internal termination to 6SRX+.                                                                                                                                                                                                                                 |

| 6SRX+             | F1                   | 1    | Serdes Lane 6 positive input. Includes 100Ω internal termination to 6SRX                                                                                                                                                                                                                                   |

| 7SRX-             | G2                   | 1    | Serdes Lane 7 negative input. Includes 100Ω internal termination to 7SRX+.                                                                                                                                                                                                                                 |

| 7SRX+             | F2                   | 1    | Serdes Lane 7 positive input. Includes 100Ω internal termination to 7SRX                                                                                                                                                                                                                                   |

| 8SRX-             | U8                   | 1    | Serdes Lane 8 negative input. Includes 100Ω internal termination to 8SRX+.                                                                                                                                                                                                                                 |

| 8SRX+             | U7                   | 1    | Serdes Lane 8 positive input. Includes 100Ω internal termination to 8SRX                                                                                                                                                                                                                                   |

| 9SRX-             | Т8                   | 1    | Serdes Lane 9 negative input. Includes 100Ω internal termination to 9SRX+.                                                                                                                                                                                                                                 |

| 9SRX+             | T7                   | 1    | Serdes Lane 9 positive input. Includes 100Ω internal termination to 9SRX                                                                                                                                                                                                                                   |

| 10SRX-            | U5                   | 1    | Serdes Lane 10 negative input. Includes 100Ω internal termination to 10SRX+.                                                                                                                                                                                                                               |

| 10SRX+            | U4                   | · ·  | Serdes Lane 10 positive input. Includes 100Ω internal termination to 10SRX                                                                                                                                                                                                                                 |

| 11SRX-            | T5                   | · ·  | Serdes Lane 11 negative input. Includes 100Ω internal termination to 11SRX+.                                                                                                                                                                                                                               |

| 11SRX+            | T4                   | · ·  | Serdes Lane 11 positive input. Includes 100Ω internal termination to 11SRX                                                                                                                                                                                                                                 |

| 12SRX-            | R1                   | i    | Serdes Lane 12 negative input. Includes 100Ω internal termination to 12SRX+.                                                                                                                                                                                                                               |

| 12SRX+            | P1                   | · ·  | Serdes Lane 12 positive input. Includes 100Ω internal termination to 12SRX                                                                                                                                                                                                                                 |

| 13SRX-            | R2                   | 1    | Serdes Lane 13 negative input. Includes 100Ω internal termination to 13SRX+.                                                                                                                                                                                                                               |

| 13SRX+            | P2                   | 1    | Serdes Lane 13 positive input. Includes 100Ω internal termination to 13SRX                                                                                                                                                                                                                                 |

| 14SRX-            | M1                   | 1    | Serdes Lane 14 negative input. Includes 100Ω internal termination to 14SRX+.                                                                                                                                                                                                                               |

| 14SRX+            | L1                   |      | Serdes Lane 14 positive input. Includes 100Ω internal termination to 145RX                                                                                                                                                                                                                                 |

| 15SRX-            | M2                   | l    | Serdes Lane 15 negative input. Includes 100Ω internal termination to 15SRX+.                                                                                                                                                                                                                               |

| 15SRX+            | L2                   | l    |                                                                                                                                                                                                                                                                                                            |

| LUORAT            | L-Z                  | _ '  | Serdes Lane 15 positive input. Includes 100Ω internal termination to 15SRX                                                                                                                                                                                                                                 |

|                 |                                                                              | Ta          | able 5-1. Pin Functions (continued)                                                                                                                                                                         |

|-----------------|------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PIN                                                                          | TYPE        | DESCRIPTION                                                                                                                                                                                                 |

| NAME            | NO                                                                           |             |                                                                                                                                                                                                             |

| GPIO Function   | ns                                                                           |             | 1                                                                                                                                                                                                           |

| ALARM           | E3                                                                           | 0           | ALARM pin is asserted when an internal unmasked alarm is detected. Alarm mask is set by ALM_MASK register. No pullup or pulldown.                                                                           |

| RESET           | E5                                                                           | I           | Device reset input, active low. Must be toggled after power up. Internal pullup.                                                                                                                            |

| SCANEN          | F3                                                                           | 1           | TI use only, can be left unconnected. Internal pulldown.                                                                                                                                                    |

| SCLK            | J1                                                                           | 1           | Serial programming interface (SPI) clock input. No pullup or pulldown.                                                                                                                                      |

| SCS             | К3                                                                           | ı           | Serial programming interface (SPI) device select input, active low. Internal pullup.                                                                                                                        |

| SDI             | J3                                                                           | ı           | Serial programming interface (SPI) data input. No pullup or pulldown.                                                                                                                                       |

| SDO             | J2                                                                           | 0           | Serial programming interface (SPI) data output. High impedance when not reading out SPI data. No pullup or pulldown.                                                                                        |

| SYNC            | E4                                                                           | I/O         | JESD204C SYNC output, active low. Pullup active when used as an input.                                                                                                                                      |

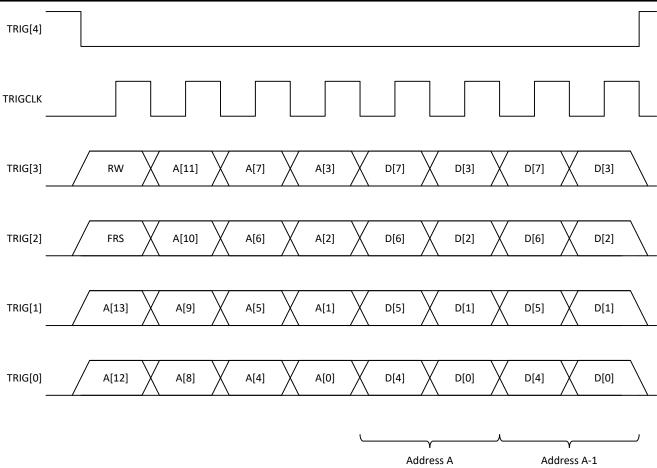

| TRIG0           | D9                                                                           | 1           | Trigger interface ball 0. Also used as data input 0 for FR Interface. Internal pulldown.                                                                                                                    |

| TRIG1           | D8                                                                           | 1           | Trigger interface ball 1. Also used as data input 1 for FR Interface. Internal pulldown.                                                                                                                    |

| TRIG2           | D7                                                                           | I           | Trigger interface ball 2. Also used as data input 2 for FR Interface. Internal pulldown.                                                                                                                    |

| TRIG3           | D6                                                                           | I           | Trigger interface ball 3. Also used as data input 3 for FR Interface. Internal pulldown.                                                                                                                    |

| TRIG4           | D5                                                                           | I           | Trigger interface ball 4. Also used as chip select input for FR Interface. Internal pulldown.                                                                                                               |

| TRIGCLK         | D4                                                                           | I/O         | Trigger interface clock. Used as an input clock for FR Interface or output clock for trigger interface. Internal pulldown.                                                                                  |

| TXEN0           | G3                                                                           | I           | Pin control for muting DAC outputs or entering APP Sleep (see TX_EN_SEL). See also Transmit Enables. Internal pullup.                                                                                       |

| TXEN1           | НЗ                                                                           | I           | Pin control for muting DAC outputs or entering APP Sleep (see TX_EN_SEL). See also Transmit Enables. Internal pullup.                                                                                       |

| Analog function | ons                                                                          |             |                                                                                                                                                                                                             |

| ATEST           | P9                                                                           | 0           | Analog test pin. Can be left disconnected if not used.                                                                                                                                                      |

| EXTREF          | K17                                                                          | I/O         | Reference voltage output or input, determined by the EXTREF_EN register field. If the internal reference is used, the ball should be tied through 0.1uF to AGND.                                            |

| RBIAS-          | H17                                                                          | 0           | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS+.                                                                                                                    |

| RBIAS+          | J17                                                                          | 0           | Full-scale output current bias is set by the resistor tied from this terminal to RBIAS                                                                                                                      |

| TDIODE+         | P10                                                                          | I           | Temperature diode positive terminal (to be sensed by an external circuit)                                                                                                                                   |

| TDIODE-         | R10                                                                          | ı           | Temperature diode negative terminal (to be sensed by an external circuit)                                                                                                                                   |

| TMSTPA+         | A15                                                                          | 0           | Reserved.                                                                                                                                                                                                   |

| TMSTPA-         | A16                                                                          | 0           | Reserved.                                                                                                                                                                                                   |

| TMSTPB+         | U15                                                                          | 0           | Reserved.                                                                                                                                                                                                   |

| TMSTPB-         | U16                                                                          | 0           | Reserved.                                                                                                                                                                                                   |

| Power Supplie   | es                                                                           |             |                                                                                                                                                                                                             |

|                 | one                                                                          | e low ESL 0 | Note .1μF decoupling capacitor per power supply pin is recommended                                                                                                                                          |

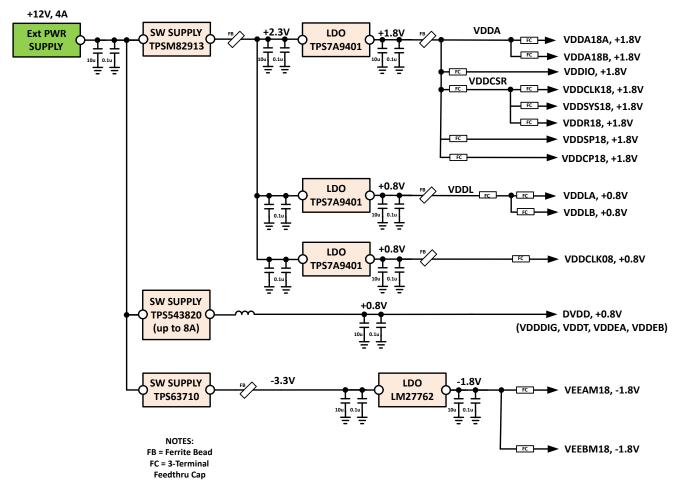

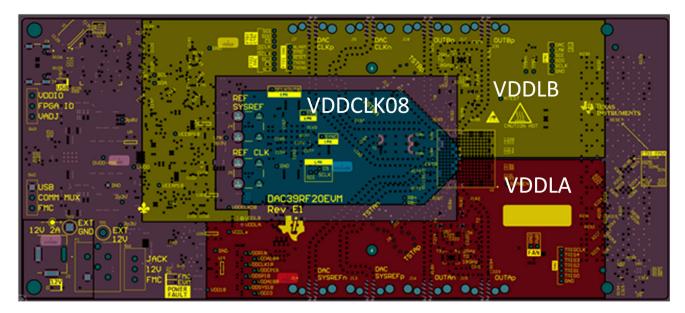

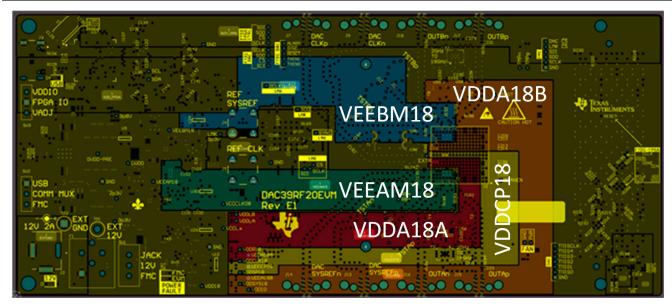

| VDDA18A         | G16, G17                                                                     | I           | 1.8V supply voltage for DAC channel A. Can be combined with VDDA18B, but may degrade channel-to-channel crosstalk (XTALK).                                                                                  |

| VDDA18B         | L16, L17                                                                     | I           | 1.8V supply voltage for DAC channel B. Can be combined with VDDA18A, but may degrade channel-to-channel crosstalk (XTALK).                                                                                  |

| VDDCLK08        | J11, F12, H12, K12,<br>M12, E13, G13, L13,<br>N13                            | I           | 0.8V supply voltage for internal sampling clock distribution path. Noise or spurs on this supply may degrade phase noise performance. Recommended to separate from VDDDIG and VDDLA/B for best performance. |

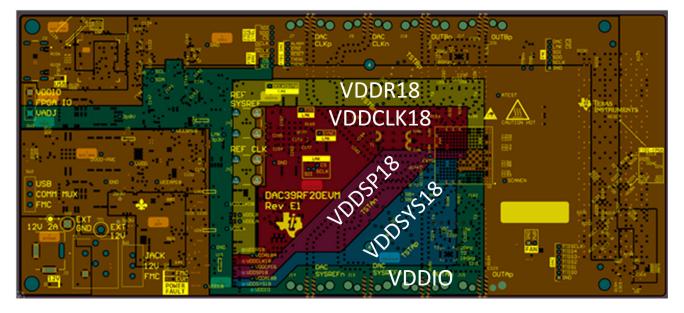

| VDDCLK18        | L14, M14                                                                     | 1           | 1.8V supply voltage for clock (CLK+/–) input buffer. Noise or spurs on this supply may degrade phase noise performance.                                                                                     |

| VDDCP18         | J13, J14                                                                     | I           | Data converter PLL 1.8V supply.                                                                                                                                                                             |

| VDDDIG          | G4, J4, L4, F5, H5, K5,<br>M5, N5, G6, J6, L6, H7,<br>K7, G8, J8, L8, H9, K9 | I           | 0.8V supply voltage for digital block. Recommended to separate from VDDLA/B and VDDCLK for bes performance.                                                                                                 |

| VDDEA           | F10, G10                                                                     | I           | 0.8V supply voltage for channel A DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEB.                                                                        |

Submit Document Feedback

#### **Table 5-1. Pin Functions (continued)**

|          | PIN                                                                                                                                                                                                                                              |      | ble 5-1. Pin Functions (continued)                                                                                                                                                                                                                                                                          |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO                                                                                                                                                                                                                                               | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                 |

| VDDEB    | L10, M10                                                                                                                                                                                                                                         | I    | 0.8V supply voltage for channel B DAC encoder. Recommended to separate from VDDDIG for best performance. Can be combined with VDDEA.                                                                                                                                                                        |

| VDDIO    | C9, C10                                                                                                                                                                                                                                          | I    | 1.8V supply for CMOS input and output terminals.                                                                                                                                                                                                                                                            |

| VDDLA    | F11, H11                                                                                                                                                                                                                                         | I    | 0.8V supply for DAC analog latch for channel A. Separate from VDDLB for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                      |

| VDDLB    | K11, M11                                                                                                                                                                                                                                         | ı    | 0.8V supply for DAC analog latch for channel B. Separate from VDDLA for best channel-to-channel crosstalk (XTALK). Must be separated from VDDDIG for best performance.                                                                                                                                      |

| VDDR18   | N4, P4                                                                                                                                                                                                                                           | I    | 1.8V Supply voltage for SerDes receivers.                                                                                                                                                                                                                                                                   |

| VDDSP18  | J10                                                                                                                                                                                                                                              | I    | Serdes PLL 1.8V supply.                                                                                                                                                                                                                                                                                     |

| VDDSYS18 | F14, G14                                                                                                                                                                                                                                         | I    | 1.8V supply voltage for SYSREF (SYSREF+/–) input buffer. Can be combined with VDDCLK18 when SYSREF is disabled during normal operation. This supply should be separate from VDDCLK18 when SYSREF is run continuously during operation to avoid noise and spur coupling and reduced phase noise performance. |

| VDDT     | C3, D3, L3, M3, N3, P3,<br>R3, C4, R4, C5, R5, C6,<br>R6, C7, F7, M7, R7, C8,<br>F8, M8, R8, F9, M9                                                                                                                                              | I    | 0.8V Supply voltage for SerDes termination.                                                                                                                                                                                                                                                                 |

| VEEAM18  | C12, D12, C13, D13,<br>C14, D14                                                                                                                                                                                                                  | 1    | -1.8V supply voltage for DAC current source bias for channel A. Can be combined with VEEBM18, but may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                         |

| VEEBM18  | P12, R12, P13, R13,<br>P14, R14                                                                                                                                                                                                                  | 1    | -1.8V supply voltage for DAC current source bias for channel B. Can be combined with VEEAM18, but<br>may degrade channel-to-channel crosstalk (XTALK).                                                                                                                                                      |

| VQPS     | P6, P7                                                                                                                                                                                                                                           | I    | TI use only. Can be tied to DGND during normal operation.                                                                                                                                                                                                                                                   |

| Grounds  |                                                                                                                                                                                                                                                  |      |                                                                                                                                                                                                                                                                                                             |

| AGND     | A10, B10, D10, E10,<br>N10, T10, U10, B11,<br>C11, D11, P11, R11,<br>T11, B12, A12, T12,<br>U12, B13, T13, A14,<br>B14, T14, U14, B15,<br>C15, D15, P15, R15,<br>T15, B16, H16, J16,<br>K16, T16, A17, B17,<br>T17, U17                          | -    | Analog ground.                                                                                                                                                                                                                                                                                              |

| DGND     | A1, B1, E1, H1, K1, N1, T1, U1, A2, B2, E2, H2, K2, N2, T2, U2, A3, B3, T3, U3, F4, H4, K4, M4, G5, J5, L5, P5, A6, B6, E6, F6, H6, K6, M6, N6, T6, U6, E7, G7, J7, L7, N7, E8, H8, K8, N8, P8, A9, B9, E9, G9, J9, L9, N9, R9, T9, U9, H10, K10 | -    | Digital ground.                                                                                                                                                                                                                                                                                             |

| VSSCLK   | E11, G11, L11, N11,<br>E12, G12, J12, L12,<br>N12, F13, H13, K13,<br>M13, E14, H14, K14,<br>N14, E15, F15, G15,<br>H15, J15, K15, L15,<br>M15, N15, C16, D16,<br>E16, F16, M16, N16,<br>P16, R16, C17, F17,<br>M17, R17                          | -    | Clock ground.                                                                                                                                                                                                                                                                                               |

# **6 Specifications**

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)

| PARAMETER                                                | TEST CONDITIONS                                                                   | MIN  | MAX            | UNIT |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------|------|----------------|------|--|

|                                                          | Supply voltage range, VDDA18A, VDDA18B <sup>(2)</sup>                             | -0.3 | 2.45           | V    |  |

|                                                          | Supply voltage range, VEEAM18, VEEBM18 <sup>(2)</sup>                             | -2.0 | 0.3            | V    |  |

|                                                          | Supply voltage range, VDDCLK18, VDDSYS18, VDDSP18, VDDCP18 <sup>(3)</sup>         | -0.3 | 2.45           | V    |  |

| Supply voltage range                                     | Supply voltage range, VDDLB, VDDLA, VDDCLK08 <sup>(3)</sup>                       | -0.3 | 1.0            | V    |  |

|                                                          | Supply voltage range, VDDIO, VQPS, VDDR18 <sup>(4)</sup>                          | -0.3 | 2.45           | V    |  |

|                                                          | Supply voltage range, VDDDIG, VDDEB, VDDEA, VDDT <sup>(4)</sup>                   | -0.3 | 1.0            | V    |  |

| Voltage between any combination of AGND, DGND and VSSCLK | Voltage between any combination of AGND, DGND and VSSCLK                          | -0.1 | 0.1            | V    |  |

| Voltage applied to input pins                            | CLK+, CLK-(3)                                                                     | -0.3 | VDDCLK18+0.3   |      |  |

|                                                          | SYSREF+, SYSREF- <sup>(3)</sup>                                                   | -0.3 | VDDSYS18+0.3   |      |  |

|                                                          | [0:15]SRX-/+ <sup>(4)</sup>                                                       | -0.3 | VDDT + 0.2     | V    |  |

|                                                          | SCLK, SCS, SDI, RESET, SYNC, SCANEN, TXEN[0:1], FRDI[0:3], FRCLK, FRCS, SYNC (4)  | -0.3 | -0.3 VDDIO+0.3 |      |  |

|                                                          | EXTREF <sup>(2)</sup>                                                             | -0.3 | VDDA18A + 0.3  |      |  |

|                                                          | DACOUTA+, DACOUTA-(2)                                                             | -0.3 | VDDA18A + 0.5  |      |  |

|                                                          | DACOUTB+, DACOUTB-(2)                                                             | -0.3 | VDDA18B + 0.5  |      |  |

| Voltage at output pins                                   | ATEST <sup>(2)</sup>                                                              | -0.3 | VDDA18B + 0.3  | V    |  |

|                                                          | RBIAS-/+(2)                                                                       | -0.3 | VDDA18A + 0.3  |      |  |

|                                                          | SDI, SDO, ALARM <sup>(4)</sup>                                                    | -0.3 | VDDIO + 0.3    |      |  |

| Peak input current (any input)                           |                                                                                   | -20  | 20             | mA   |  |

|                                                          | ute value of all currents forced in or out,<br>d DACOUTA+, DACOUTA-, DACOUTB+ and |      | 30             | mA   |  |

| Junction temperature, T <sub>J</sub>                     |                                                                                   |      | 150            | °C   |  |

| Storage temperature, T <sub>stg</sub>                    |                                                                                   | -65  | 150            | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Measured to AGND.

- (3) Measured to VSSCLK.

- (4) Measured to DGND.

#### 6.2 ESD Ratings

|        |                         |                                                                                     | VALUE | UNIT |

|--------|-------------------------|-------------------------------------------------------------------------------------|-------|------|

| V      | Electrostatic discharge | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001, all pins <sup>(1)</sup>     | 500   | V    |

| V(ESD) | Electrostatic discharge | Charged device model (CDM), per ANSI/<br>ESDA/JEDEC JS-002, all pins <sup>(2)</sup> | 250   | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Submit Document Feedback

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                    |                                              |                                                               | MIN   | NOM  | MAX                | UNIT                  |

|--------------------|----------------------------------------------|---------------------------------------------------------------|-------|------|--------------------|-----------------------|

|                    |                                              | VDDA18A, VDDA18B <sup>(1)</sup>                               | 1.71  | 1.8  | 1.89               | V                     |

|                    |                                              | VEEAM18, VEEBM18 <sup>(1)</sup>                               | -1.89 | -1.8 | -1.71              | V                     |

|                    |                                              | VDDCLK18, VDDSYS18, VDDSP18, VDDCP18 <sup>(2)</sup>           | 1.71  | 1.8  | 1.89               | V                     |

| Supply volta       | age range                                    | VDDLB, VDDLA, VDDCLK08 <sup>(2)</sup>                         | 0.76  | 0.8  | 0.84               | V                     |

|                    | V Innut common mode veltore                  | VDDIO, VDDR18 <sup>(3)</sup>                                  | 1.71  | 1.8  | 1.89               | V                     |

|                    |                                              | VQPS <sup>(3)</sup>                                           | 0     | 0    | 1.89               | V                     |

|                    |                                              | VDDDIG, VDDEB, VDDEA, VDDT <sup>(3)</sup>                     | 0.76  | 0.8  | 0.84               | V                     |

| \ /                | Input common mode voltage                    | CLK+, CLK-(2) (4)                                             |       | 0.4  |                    | V                     |

| V <sub>CMI</sub>   |                                              | SYSREF+, SYSREF-(2) (4)                                       | 0.4   | 0.5  | 0.6                | V                     |

|                    |                                              | SYSREF+ to SYSREF-                                            | 400   | 1000 | 2000               | $mV_{PP-DIFF}$        |

|                    |                                              | CLK+ to CLK-, f <sub>CLK</sub> < 3GHz <sup>(6)</sup>          | 800   | 1000 | 2000               | $mV_{PP-DIFF}$        |

| V <sub>ID</sub>    | Input differential peak-to-peak voltage      | CLK+ to CLK-, 3GHz < f <sub>CLK</sub> < 12GHz <sup>(6)</sup>  | 800   | 1000 | 1400               | mV <sub>PP-DIFF</sub> |

|                    |                                              | CLK+ to CLK-, 12GHz < f <sub>CLK</sub> < 17GHz <sup>(6)</sup> | 800   | 1000 | 1800               | $mV_PP\text{-DIFF}$   |

|                    |                                              | CLK+ to CLK-, f <sub>CLK</sub> > 17GHz <sup>(6)</sup>         | 800   | 1000 | 2000               | $mV_{PP\text{-DIFF}}$ |

| DC <sub>MIN</sub>  | DACCLK+/– duty cycle minimum                 | CLK+/- duty cycle minimum                                     |       | 45   |                    | %                     |

| DC <sub>MAX</sub>  | DACCLK+/– duty cycle maximum                 | CLK+/- duty cycle maximum                                     |       | 55   |                    | %                     |

| T <sub>A</sub>     | Operating free-air temperature               |                                                               | -40   |      | 85                 | °C                    |

| TJ                 | Recommended operating junction temp          | perature                                                      |       |      | 105 <sup>(5)</sup> | °C                    |

| T <sub>J-MAX</sub> | Maximum rated operating junction temperature | Maximum rated operating junction temperature                  | 125   |      |                    | °C                    |

- (1) Measured to AGND.

- (2) Measured to VSSCLK.

- (3) Measured to DGND.

- (4) CLK+/- and SYSREF+/- are weakly self-biased to the optimal common mode voltage. CLK+/- should always be AC coupled to the clock source. SYSREF+/- is recommended to be AC coupled to the clock source when possible.

- (5) Die is designed for Tj = 150 °C operation and for device and die metallization degradation up to 150,000POH continuous operation at Tj = 113 °C (118 °C for 100,000POH). Prolonged use above a junction temperature of Tj =105 °C may, however, increase the package failure-in-time (FIT) rate.

- (6) For optimum phase noise, the clock amplitude should be near the high end of the range.

#### **6.4 Thermal Information**

|                       | THERMAL METRIC(1)                            | 13.8mm x 13.8mm FCCSP | UNIT |

|-----------------------|----------------------------------------------|-----------------------|------|

|                       | THERMAL METRIC                               | 289 PINS              | ONIT |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 15.3                  | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 1.3                   | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 4.3                   | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.5                   | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 4.0                   | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics - DC Specifications

|                        | PARAMETER                                                    | TEST CONDITIONS                                                                                                                      | MIN | TYP       | MAX | UNIT            |

|------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----------|-----|-----------------|

| DC ACCURA              | ACY                                                          |                                                                                                                                      |     |           |     |                 |

| BITS                   | DAC core resolution                                          |                                                                                                                                      | 16  |           | 16  | bits            |

| DNL                    | Differential nonlinearity                                    |                                                                                                                                      |     | ±4        |     | LSB             |

| INL                    | Integral nonlinearity                                        |                                                                                                                                      |     | ±6        |     | LSB             |

| RT <sub>DRIFT</sub>    | Internal termination resistance drift over temperature       |                                                                                                                                      |     | .02       |     | Ω/°C            |

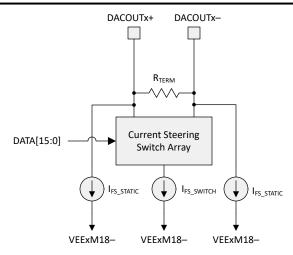

| DAC ANALO              | OG OUTPUT (DACOUTA+, DACOUTA-                                | , DACOUTB+, DACOUTB–)                                                                                                                |     |           |     |                 |

| I <sub>FS_SWITCH</sub> | Switched full scale output current                           | 3.6kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B= 0xF and FINE_CUR_A / FINE_CUR_B = 0x10 (default), Current_2x = 1  |     | 40        |     | mA              |

| ı                      | Switched full acale output current                           | 3.6kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B= 0xF and FINE_CUR_A / FINE_CUR_B = 0x10 (default), Current_2x = 0  |     | 20        |     | mΛ              |

| I <sub>FS_SWITCH</sub> | Switched full scale output current                           | 3.6kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0x0 and FINE_CUR_A / FINE_CUR_B = 0x10 (default), Current_2x = 0 |     | 2         |     | mA              |

| I <sub>STATIC</sub>    | Static output current per pin                                | 3.6kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = 0x10 (default)                 |     | 4.7       |     | mA              |

|                        |                                                              | 3.6kΩ resistor from RBIAS+                                                                                                           |     | 1         |     | uA/°C           |

| I <sub>FSDRIFT</sub>   | Full scale output current temperature drift                  | to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = 0x10 (default)                                            |     | 65        |     | PPM/°C          |

| I <sub>FSERROR</sub>   | Full scale current error                                     | 3.6kΩ resistor from RBIAS+ to RBIAS-, COARSE_CUR_A / COARSE_CUR_B = 0xF and FINE_CUR_A / FINE_CUR_B = 0x10 (default)                 |     | ±1        |     | %               |

| $V_{COMP}$             | Output compliance voltage range                              | Measured from DACOUTA+,<br>DACOUTA-, DACOUTB+ or<br>DACOUTB- to AGND                                                                 | 1.3 |           | 2.3 | ٧               |

| R <sub>TERM</sub>      | Output differential termination resistance                   |                                                                                                                                      |     | 100       |     | Ω               |

| R <sub>TERMDRIFT</sub> | Output differential termination resistance temperature coeff |                                                                                                                                      |     | -5<br>-50 |     | mΩ/°C<br>PPM/°C |

| CLOCK AND              | SYSREF INPUTS (CLK+, CLK-, SYSF                              | REF+, SYSREF-)                                                                                                                       |     |           |     |                 |

| R <sub>T</sub>         | Internal differential termination resista                    | nce                                                                                                                                  |     | 100       |     | Ω               |

| C <sub>IN</sub>        | Internal differential input capacitance                      |                                                                                                                                      |     | 0.5       |     | pF              |

| REFERENCI              | E VOLTAGE                                                    |                                                                                                                                      |     |           |     |                 |

| V <sub>REF</sub>       | Reference output voltage                                     |                                                                                                                                      |     | 0.9       |     | V               |

| V <sub>REF-DRIFT</sub> | Reference output voltage drift over ter                      | mperature                                                                                                                            |     | 45        |     | ppm/°C          |

| I <sub>REF</sub>       | Maximum reference output current so                          | urcing capability                                                                                                                    |     | 100       |     | nA              |

|                     | PARAMETER                                    | TEST CONDITIONS                                                                                                                                                                                                                                               | MIN            | TYP   | MAX            | UNIT     |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------|----------------|----------|

| JESD204C            | SERDES INTERFACE ([15:0]SRX+/-)              |                                                                                                                                                                                                                                                               |                |       |                |          |

| V <sub>SRDIFF</sub> | SerDes Receiver Input Amplitude              |                                                                                                                                                                                                                                                               | 50             |       | 1200           | mVppdiff |

| V <sub>SRCOM</sub>  | SerDes Input Common Mode <sup>(2)</sup>      |                                                                                                                                                                                                                                                               |                | 450   |                | mV       |

| Z <sub>SRdiff</sub> | SerDes Internal Differential<br>Termination  |                                                                                                                                                                                                                                                               | 80             | 100   | 120            | Ω        |

| CMOS INT            | ERFACE (SCLK, SCS, SDI, SDO, RESET           | , TRIG[0:4], TRIGCLK, SYNC, TXENABL                                                                                                                                                                                                                           | .E[0:1])       |       |                |          |

| I <sub>IH</sub>     | High level input current (with pulldowns)    | TRIG[04] <sup>(3)</sup> , TRIGCLK <sup>(3)</sup> , SCANEN <sup>(1)</sup>                                                                                                                                                                                      |                |       | 200            | uA       |

| I <sub>IH</sub>     | High level input current (without pulldowns) | SDS, RESET, SYNC, TXEN[0:1],<br>SDI, SCLK <sup>(1)</sup>                                                                                                                                                                                                      |                |       | 2              | uA       |

| I <sub>IL</sub>     | Low level input current (with pullups)       | SDS, RESET, SYNC, TXEN[0:1] <sup>(1)</sup>                                                                                                                                                                                                                    | -100           |       |                | uA       |

| I <sub>IL</sub>     | Low level input current (without pullups)    | SCANEN, SDI, SCLK <sup>(1)</sup>                                                                                                                                                                                                                              | -20            |       |                | uA       |

| Cı                  | Input capacitance                            | Input capacitance                                                                                                                                                                                                                                             |                | 3     |                | pF       |

| V <sub>IH</sub>     | High level input voltage                     | SCLK, SCS, SDI, RESET, SCANEN,<br>TXEN[0:1], SYNC, TRIG[04],                                                                                                                                                                                                  | 0.7 x<br>VDDIO |       |                | V        |

| V <sub>IL</sub>     | Low level input voltage                      | TRIGCLK                                                                                                                                                                                                                                                       |                |       | 0.3 x<br>DIO18 | V        |

| V <sub>OH</sub>     | High level output voltage                    | I <sub>LOAD</sub> = -400uA                                                                                                                                                                                                                                    | 1.55           |       |                | V        |

| V <sub>OL</sub>     | Low level output voltage                     | I <sub>LOAD</sub> = 400uA                                                                                                                                                                                                                                     |                |       | 0.2            | V        |

| TEMPERA             | TURE DIODE CHARACTERISTICS (TDIO             | DE+, TDIODE–)                                                                                                                                                                                                                                                 |                |       |                |          |

| $\Delta V_{BE}$     | Temperature diode voltage slope              | Forced forward current of 100µA.  Offset voltage (approximately 0.792V at 0°C) varies with process and must be measured for each part. Offset measurement must be done with the device unpowered or with the PD pin asserted to minimize device self-heating. |                | -1.45 |                | mV/°C    |

- 1) With no IO supply voltage offset in connecting device.

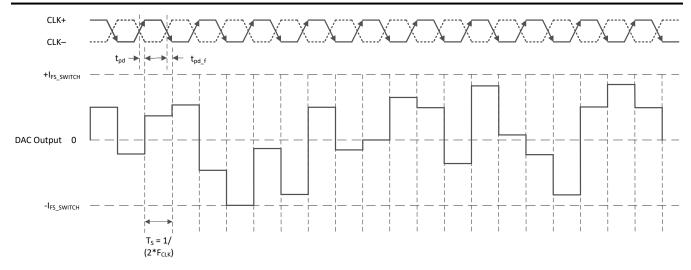

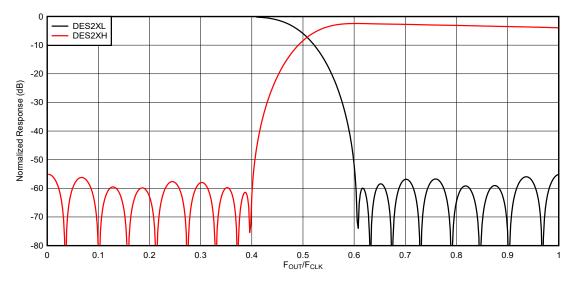

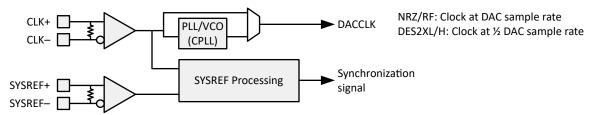

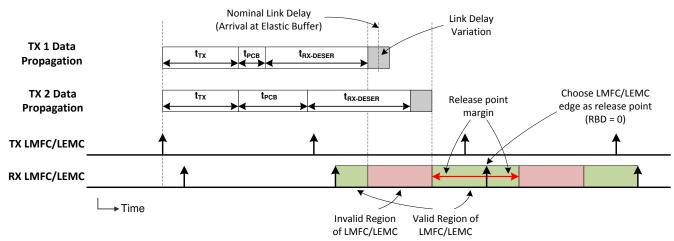

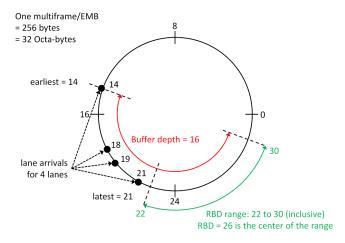

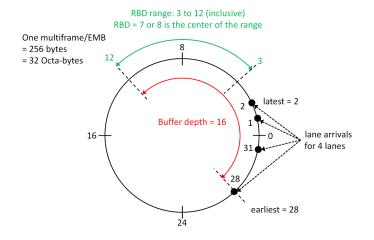

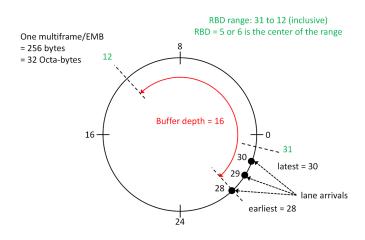

- (2) AC coupling from the Serdes transmitter is recommended.