**DAC38RF80, DAC38RF83, DAC38RF84 DAC38RF85, DAC38RF90, DAC38RF93**

SLASEA3D - DECEMBER 2016 - REVISED DECEMBER 2023

# DAC38RFxx Dual- or Single-Channel, Single-Ended or Differential Output, 14-Bit, 9-GSPS, RF-Sampling DAC With JESD204B Interface and On-Chip PLL

### 1 Features

- 14-bit resolution

- Maximum DAC sample rate: 9 GSPS

- **Key Specifications:**

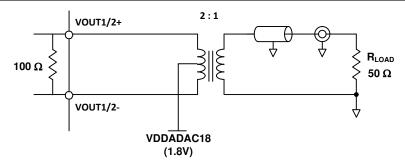

- RF full-scale output power at 2.1 GHz:

- DAC38RF80/90/84: 0 dBm

- DAC38RF83/93/85: 3 dBm (with 2:1 balun)

- Spectral performance(on-chip PLL, DIFF):

- f<sub>DAC</sub> = 5898.24 MSPS, f<sub>OUT</sub> = 2.14 GHz

- WCDMA ACLR: 75 dBc

- WCDMA alt-ACLR: 77 dBc

- f<sub>DAC</sub> = 8847.36 MSPS, f<sub>OUT</sub> = 3.7 GHz

- 20 MHz LTE ACLR: 63 dBc

- f<sub>DAC</sub> = 9 GSPS, f<sub>OUT</sub> = 1.8 GHz

- IMD3 = 70 dBc (-6 dBFS, 10-MHz tone spacing)

- NSD = -157 dBc/Hz

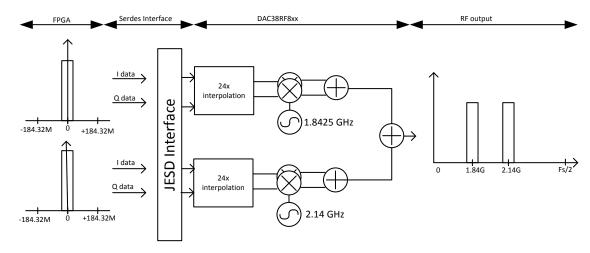

- · Dual-band digital up-converter per DAC

- 6, 8, 10, 12, 16, 18, 20 or 24x interpolation

- 4 Independent NCOs with 48-bit resolution

- JESD204B Interface, subclass 1

- Support for multichip synchronization

- Maximum lane rate: 12.5 Gbps

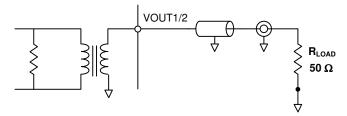

- Single-ended output with integrated balun (DAC38RF80/90/84) covering 700 MHz to 3800 MHz

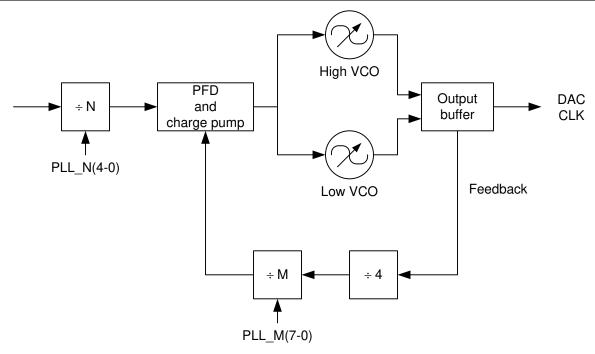

- Internal PLL and VCO with bypass

- $f_{C(VCO)} = 5.9 \text{ or } 8.9 \text{ GHz}$

- Power dissipation: 1.4 to 2.2 W/ch

- Power supplies: -1.8 V, 1 V, 1.8 V

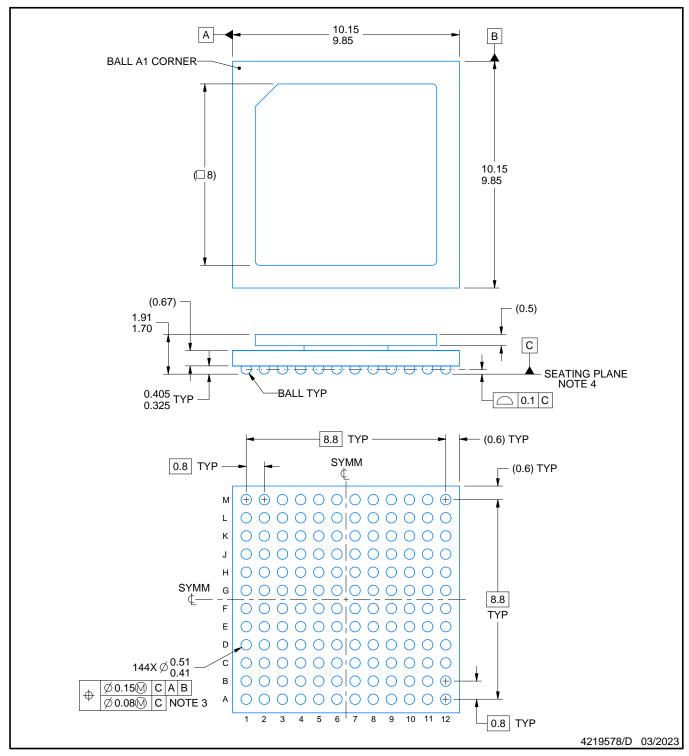

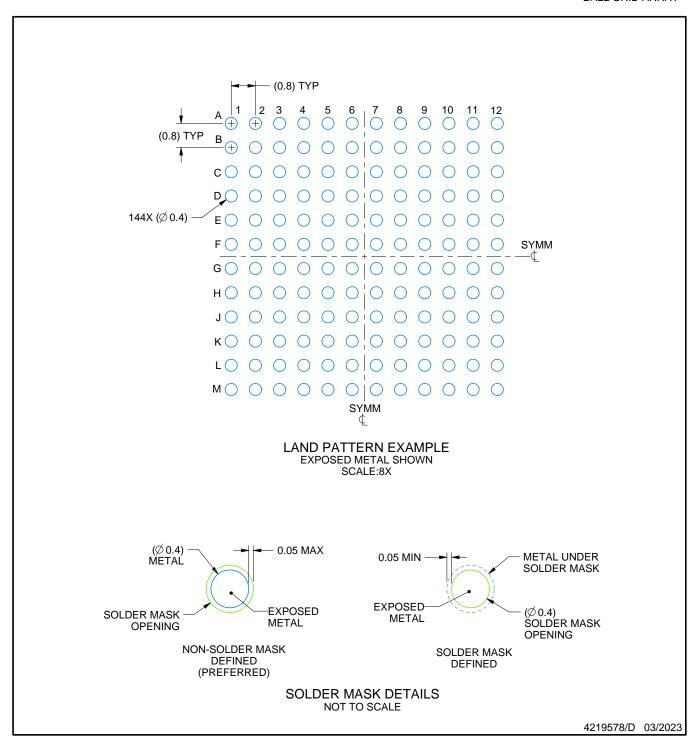

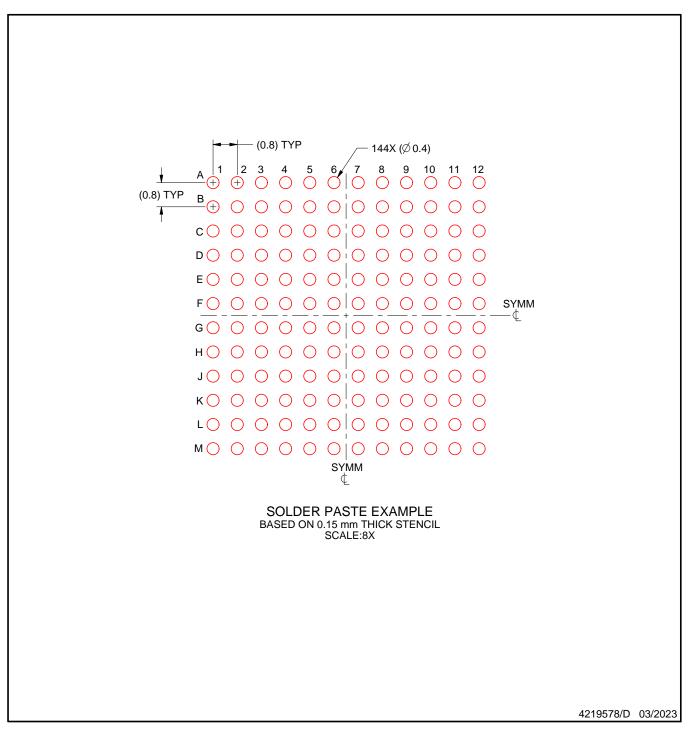

- Package: 10 x 10 mm BGA, 0.8 mm pitch, 144balls

### 2 Applications

- Wireless communications

- Communications test equipment

- Arbitrary waveform generators

- Military software defined radios

- Radar and satellite communications (SATCOM)

## 3 Description

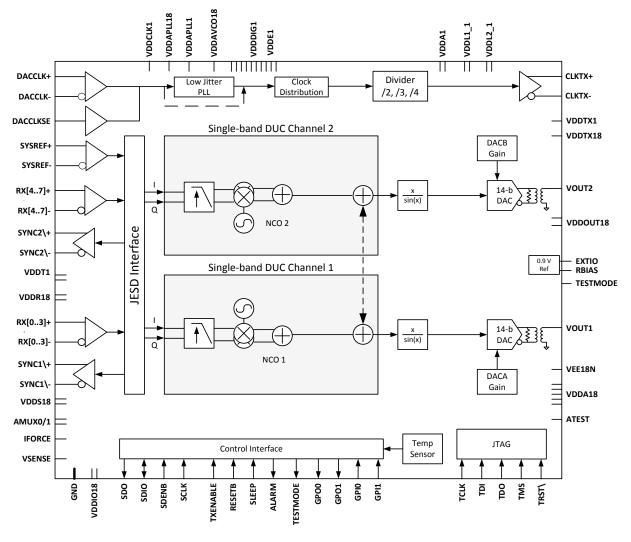

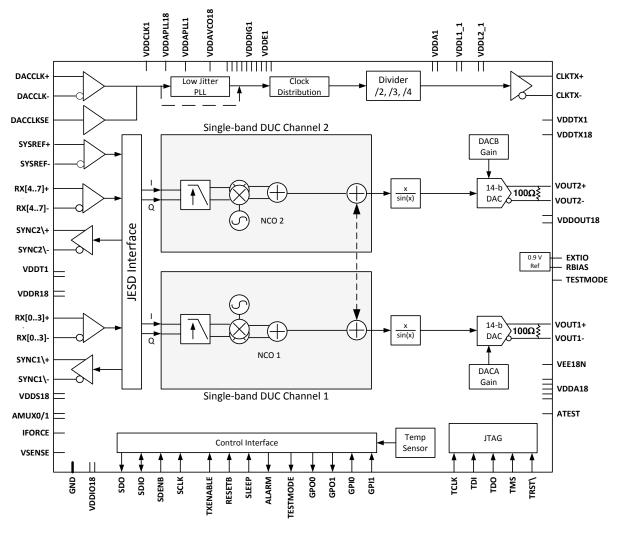

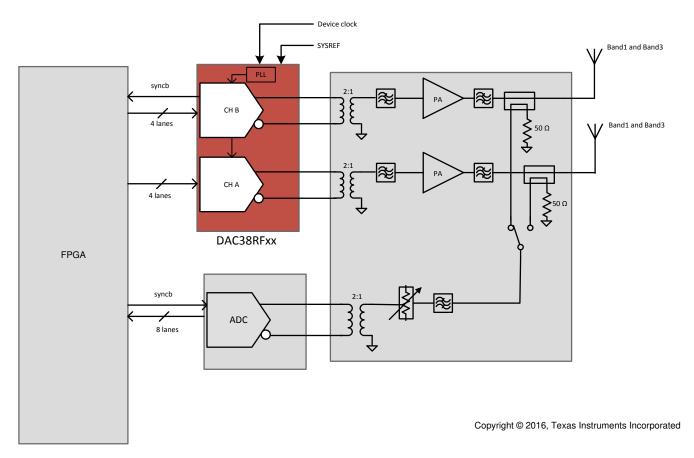

The DAC38RFxx is a family of high-performance, dual/single-channel, 14-bit, 9-GSPS, RF-sampling digital-to-analog converters (DACs) that are capable of synthesizing wideband signals from 0 to 4.5 GHz. A high dynamic range allows the DAC38RFxx family to generate signals for a wide range of applications including 3G/4G signals for wireless base-stations and radar.

The devices feature a low-power JESD204B Interface with up to 8 lanes with a maximum bit rate of 12.5 Gbps allowing an input data rate of 1.25 GSPS complex per channel. The DAC38RFxx provides two digital up-converters per channel, with multiple options for interpolation rates. A digital quadrature modulator with independent, frequency flexible NCOs are available to support multi-band operation. An optional low-iitter PLL/VCO simplifies the DAC sampling clock generation by allowing use of a lower frequency reference clock.

### **Device Information**

| PART NUMBER <sup>(1)</sup> (2) | OUTPUT TYPE  | NUMBER OF<br>CHANNELS |

|--------------------------------|--------------|-----------------------|

| DAC38RF83                      |              | 2                     |

| DAC38RF93                      | Differential | 2                     |

| DAC38RF85                      |              | 1                     |

| DAC38RF80                      |              | 2                     |

| DAC38RF90                      | Single ended | 2                     |

| DAC38RF84                      |              | 1                     |

- For all available packages, see the orderable addendum at the end of the data sheet.

- For all available device options, see the Device Comparison Table.

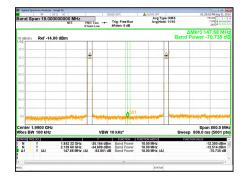

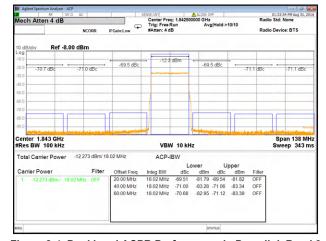

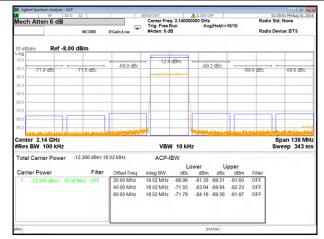

2x20-MHz LTE at 1.84 GHz and 2.14 GHz, 800 MHz Span

## **Table of Contents**

| 1 Features1                                                | 7.3 Feature Description36                               |

|------------------------------------------------------------|---------------------------------------------------------|

| 2 Applications1                                            | 7.4 Device Functional Modes73                           |

| 3 Description                                              | 7.5 Register Maps                                       |

| 4 Device Comparison3                                       | 8 Application and Implementation                        |

| 5 Pin Configuration and Functions4                         | 8.1 Application Information                             |

| 6 Specifications10                                         | 8.2 Typical Application: Multi-band Radio Frequency     |

| 6.1 Absolute Maximum Ratings10                             | Transmitter140                                          |

| 6.2 ESD Ratings10                                          | 8.3 Power Supply Recommendations142                     |

| 6.3 Recommended Operating Conditions10                     | 8.4 Layout143                                           |

| 6.4 Thermal Information11                                  | 9 Device and Documentation Support147                   |

| 6.5 Electrical Characteristics - DC Specifications 11      | 9.1 Receiving Notification of Documentation Updates 147 |

| 6.6 Electrical Characteristics - Digital Specifications 14 | 9.2 Support Resources147                                |

| 6.7 Electrical Characteristics - AC Specifications 17      | 9.3 Trademarks                                          |

| 6.8 PLL/VCO Electrical Characteristics                     | 9.4 Electrostatic Discharge Caution147                  |

| 6.9 Timing Requirements21                                  | 9.5 Glossary147                                         |

| 6.10 Typical Characteristics22                             | 10 Revision History147                                  |

| 7 Detailed Description30                                   | 11 Mechanical, Packaging, and Orderable                 |

| 7.1 Overview30                                             | Information151                                          |

| 7.2 Functional Block Diagrams                              |                                                         |

## **4 Device Comparison**

**Table 4-1. Device Comparison**

| Device    | No. of<br>Channels | Output       | Interpolation | VCO Center<br>Frequency            |

|-----------|--------------------|--------------|---------------|------------------------------------|

| DAC38RF83 | 2                  |              | 6-24          | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

| DAC38RF93 | 2                  | Differential | 12-24         | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

| DAC38RF85 | 1                  |              | 6-24          | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

| DAC38RF80 | 2                  |              | 6-24          | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

| DAC38RF90 | 2                  | Single ended | 12-24         | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

| DAC38RF84 | 1                  |              | 6-24          | VCO0 = 5.9 GHz,<br>VCO1 = 8.85 GHz |

## **5 Pin Configuration and Functions**

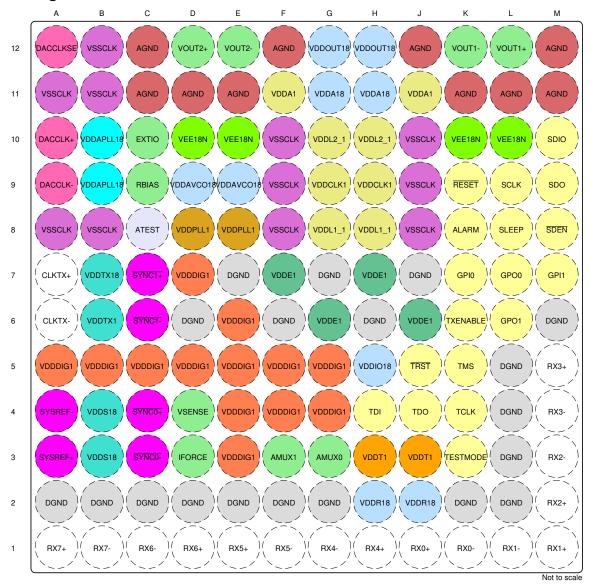

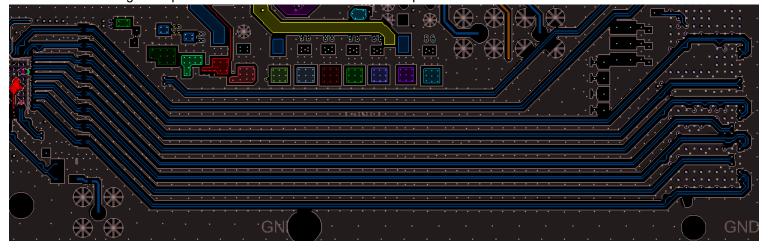

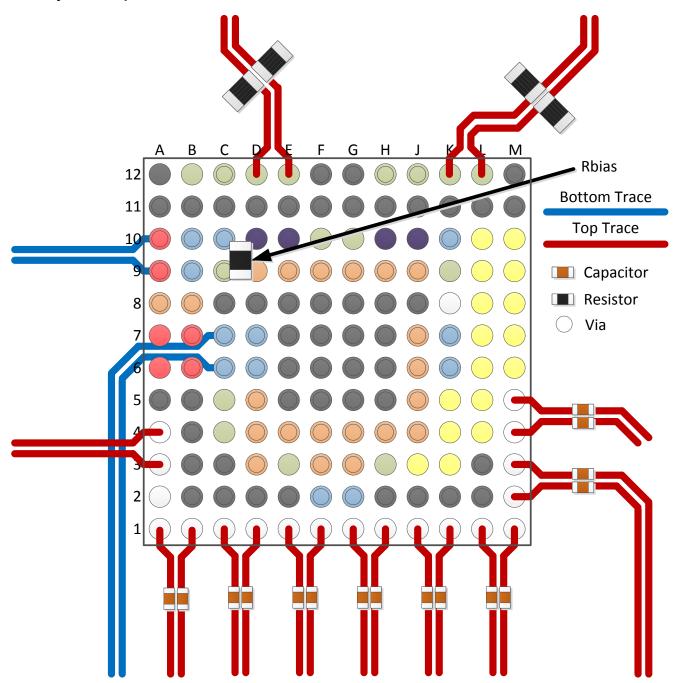

Figure 5-1. DAC38RF83, DAC38RF93, DAC38RF85 AAV Package 144-Pin (FCBGA) 144-Pin FCBGA Top View

### Pin Functions - DAC38RF83, DAC38RF93, DAC38RF85

| PIN    |                                                        | I/O | DESCRIPTION                                                                                                                                      |  |

|--------|--------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME   | NO.                                                    | 1/0 | DESCRIPTION                                                                                                                                      |  |

| AGND   | C11, C12, D11, E11,<br>F12, J12, K11, L11, M11,<br>M12 | -   | Analog ground.                                                                                                                                   |  |

| ALARM  | K8                                                     | 0   | CMOS output for ALARM condition. Default polarity is active low, but can be changed to active high through RESET_CONFIG alm_out_pol control bit. |  |

| AMUX0  | G3                                                     | 0   | Analog test pin for SerDes, Lane 0 to Lane 3. Can be left floating.                                                                              |  |

| AMUX1  | F3                                                     | 0   | Analog test pin for SerDes, Lane 4 to Lane 7. Can be left floating.                                                                              |  |

| ATEST  | C8                                                     | 0   | Analog test pin for DAC, references and PLL. Can be left floating.                                                                               |  |

| CLKTX+ | A7                                                     | 0   | Divided output clock, internal 100 $\Omega$ differential termination, self-biased, positive terminal.                                            |  |

| CLKTX- | A6                                                     | 0   | Divided output clock, internal 100 $\Omega$ differential termination, self-biased, negative terminal.                                            |  |

## Pin Functions - DAC38RF83, DAC38RF93, DAC38RF85 (continued)

| NAME       NO.       DESCRIPTION         DACCLK+       A10       I Device clock, internal 100 Ω differential termination, self-biased, positive terminal.         DACCLK-       A9       I Device clock, internal 100 Ω differential termination, self-biased, negative terminal.         DACCLKSE       A12       I Single ended device clock optional input. Can be left floating if not used. internal 50         DGND       A2, B2, C2, D2, D6, E2, E7, F6, G2, G7, H6, J7, K2, L2, L3, L4, L5, M6       - Digital ground.         EXTIO       C10       I/O Requires a 0.1 μF decoupling capacitor to AGND.         GPI0       K7       - Factory use only. User should GND.         CDI1       M7 | Ω termination.          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| DACCLK-  A9  I Device clock, internal 100 Ω differential termination, self-biased, negative terminal.  DACCLKSE  A12  I Single ended device clock optional input. Can be left floating if not used. internal 50  A2, B2, C2, D2, D6, E2, E7, F2, F6, G2, G7, H6, J7, K2, L2, L3, L4, L5, M6  EXTIO  C10  I/O Requires a 0.1 μF decoupling capacitor to AGND.  GPI0  K7  - Factory use only. User should GND.                                                                                                                                                                                                                                                                                            | Ω termination.          |

| DACCLKSE  A12  I Single ended device clock optional input. Can be left floating if not used. internal 50  A2, B2, C2, D2, D6, E2, E7, F2, F6, G2, G7, H6, J7, K2, L2, L3, L4, L5, M6  EXTIO  C10  I/O Requires a 0.1 μF decoupling capacitor to AGND.  GPI0  K7  - Factory use only. User should GND.                                                                                                                                                                                                                                                                                                                                                                                                   | Ω termination.          |

| A2, B2, C2, D2, D6, E2, E7, F2, F6, G2, G7, H6, J7, K2, L2, L3, L4, L5, M6  EXTIO  C10  I/O  Requires a 0.1 μF decoupling capacitor to AGND.  GPI0  K7  - Factory use only. User should GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Ω termination.          |

| DGND         E7, F2, F6, G2, G7, H6, J7, K2, L2, L3, L4, L5, M6         -         Digital ground.           EXTIO         C10         I/O         Requires a 0.1 μF decoupling capacitor to AGND.           GPI0         K7         -         Factory use only. User should GND.                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |

| GPI0 K7 - Factory use only. User should GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |

| CDI4 M7 Footoming only Hope should CND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| GPI1 M7 - Factory use only. User should GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| GPO0 L7 O Used for CMOS SYNC0\ signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| GPO1 L6 O Used for CMOS SYNC1\ signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |

| IFORCE D3 O Test pin for on chip parametrics. Can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                         |

| RBIAS  C9  Full-scale output current bias. Change the full-scale output current through DACFS (8.5.72). Expected to be 3.6 kΩ to GND for 40 mA full scale output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | in register DACFS       |

| RESET K9 I Active low input for chip RESET, which resets all the programming registers to their pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | default state. Internal |

| RX0+ J1 I CML SerDes interface lane 0 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX0- K1 I CML SerDes interface lane 0 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX1+ M1 I CML SerDes interface lane 1 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX1- L1 I CML SerDes interface lane 1 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX2+ M2 I CML SerDes interface lane 2 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX2- M3 I CML SerDes interface lane 2 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX3+ M5 I CML SerDes interface lane 3 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX3- M4 I CML SerDes interface lane 3 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX4+ H1 I CML SerDes interface lane 4 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX4- G1 I CML SerDes interface lane 4 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX5+ E1 I CML SerDes interface lane 5 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX5- F1 I CML SerDes interface lane 5 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX6+ D1 I CML SerDes interface lane 6 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX6- C1 I CML SerDes interface lane 6 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX7+ A1 I CML SerDes interface lane 7 input, positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| RX7- B1 I CML SerDes interface lane 7 input, negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

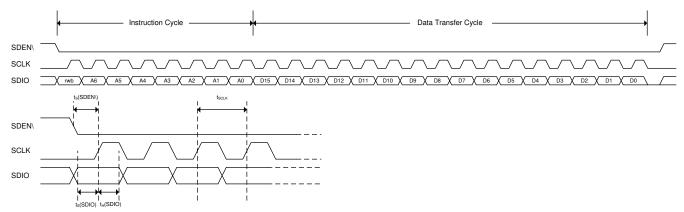

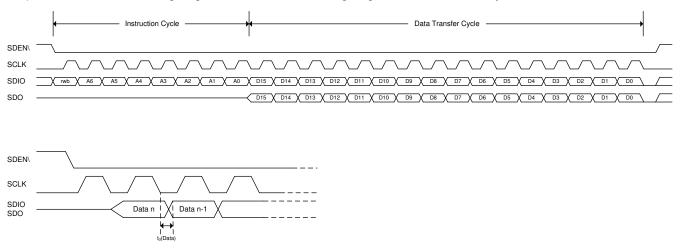

| SCLK L9 I Serial interface clock. Internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                         |

| SDEN M8 I Active low serial data enable, always an input to the DAC38RFxx. Internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| SDIO M10 I/O Serial interface data. Bi-directional in 3-pin mode (default) and uni-directional input of pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-pin mode. Internal    |

| SDO M9 O Uni-directional serial interface data output in 4-pin mode. The SDO pin is tri-stated i (default).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | in 3-pin interface mode |

| SLEEP L8 I Active high asynchronous hardware power-down input. Internal pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |

| SYNC0+ C4 O Synchronization request to transmitter for JESD204B link 0, LVDS positive output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| SYNCO- C3 O Synchronization request to transmitter for JESD204B link 0, LVDS negative output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| SYNC1+ C7 O Synchronization request to transmitter for JESD204B link 1, LVDS positive output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| SYNC1- C6 O Synchronization request to transmitter for JESD204B link 1, LVDS negative output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| SYSREF+ A3 LVPECL SYSREF positive input, internal 100 Ω differential termination, self biased. pair is captured with the rising edge of DACCLKP/N. It is used for multiple DAC syn                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |

| SYSREF- A4 I LVPECL SYSREF negative input, self biased, internal 100 $\Omega$ differential termination description)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . (See the SYSREF+      |

| TCLK K4 I JTAG test clock. Internal pull-down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

| TDI H4 I JTAG test data in. Internal pull-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |

| TDO J4 O JTAG test data out. Internal pull-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                         |

### Pin Functions - DAC38RF83, DAC38RF93, DAC38RF85 (continued)

| PIN       |                                                          |     | PERCENTION                                                                                                                                                                                                                                                                                                                                   |  |  |

|-----------|----------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME      | NO.                                                      | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |  |  |

| TESTMODE  | К3                                                       | -   | This pin is used for factory testing. Recommended to connect to ground for normal operation.                                                                                                                                                                                                                                                 |  |  |

| TMS       | K5                                                       | I   | JTAG test mode select. Internal pull-up                                                                                                                                                                                                                                                                                                      |  |  |

| TRST      | J5                                                       | I   | JTAG test reset. Internal pull-up. Must be connected to ground if not used                                                                                                                                                                                                                                                                   |  |  |

| TXENABLE  | K6                                                       | I   | Transmit enable active high input. Internal pull-down. This pin is ORed with spi_txenable bit in JESD_FIFO register to enable analog output data transmission. To enable analog output data transmission, pull the CMOS TXENABLE pin to high. To disable analog output, pull CMOS TXENABLE pin to low. The DAC output is forced to midscale. |  |  |

| VDDA1     | F11, J11                                                 | I   | Analog 1 V supply voltage. Must be separated from VDDDIG1 supply for best performance.                                                                                                                                                                                                                                                       |  |  |

| VDDA18    | G11, H11                                                 | I   | Analog 1.8 V supply voltage. (1.8 V)                                                                                                                                                                                                                                                                                                         |  |  |

| VDDPLL1   | D8, E8                                                   | I   | Analog 1 V supply for PLL.                                                                                                                                                                                                                                                                                                                   |  |  |

| VDDAPLL18 | B9, B10                                                  | I   | PLL analog supply voltage. (1.8 V)                                                                                                                                                                                                                                                                                                           |  |  |

| VDDAVCO18 | D9, E9                                                   | I   | Analog supply voltage for VCO (1.8 V)                                                                                                                                                                                                                                                                                                        |  |  |

| VDDCLK1   | G9, H9                                                   | I   | Internal clock buffer supply voltage (1 V). It is recommended to isolate this supply from VDDDIG1 and VDDA1.                                                                                                                                                                                                                                 |  |  |

| VDDL1_1   | G8, H8                                                   | I   | DAC core supply voltage. (1 V)                                                                                                                                                                                                                                                                                                               |  |  |

| VDDL2_1   | G10, H10                                                 | I   | DAC core supply voltage. (1 V)                                                                                                                                                                                                                                                                                                               |  |  |

| VDDDIG1   | A5, B5, C5, D5, D7, E3,<br>E4, E5, E6, F4, F5, G4,<br>G5 | I   | Digital supply voltage. (1 V). It is recommended to isolate this supply from VDDCLK1 and VDDA1.                                                                                                                                                                                                                                              |  |  |

| VDDE1     | F7, H7, G6, J6                                           | I   | Digital Encoder supply voltage (1 V). Must be separated from VDDDIG1 supply for best performance.                                                                                                                                                                                                                                            |  |  |

| VDDIO18   | H5                                                       | I   | Supply voltage for all digital I/O and CMOS I/O (1.8 V).                                                                                                                                                                                                                                                                                     |  |  |

| VDDOUT18  | G12, H12                                                 | I   | DAC output supply. (1.8 V)                                                                                                                                                                                                                                                                                                                   |  |  |

| VDDR18    | H2, J2                                                   | I   | Supply voltage for SerDes. (1.8 V)                                                                                                                                                                                                                                                                                                           |  |  |

| VDDS18    | B3, B4                                                   | I   | Supply voltage for LVDS SYNC0+/- and SYNC1+/- (1.8 V)                                                                                                                                                                                                                                                                                        |  |  |

| VDDT1     | H3, J3                                                   | I   | Supply voltage for SerDes termination. (1 V)                                                                                                                                                                                                                                                                                                 |  |  |

| VDDTX1    | B6                                                       | I   | Supply voltage for divided clock output. (1 V)                                                                                                                                                                                                                                                                                               |  |  |

| VDDTX18   | B7                                                       | I   | Supply voltage for divided clock output . (1.8 V)                                                                                                                                                                                                                                                                                            |  |  |

| VEE18N    | D10, E10, K10, L10                                       | I   | Analog supply voltage. (-1.8 V)                                                                                                                                                                                                                                                                                                              |  |  |

| VOUT1+    | L12                                                      | 0   | DAC channel 1 output.                                                                                                                                                                                                                                                                                                                        |  |  |

| VOUT1-    | K12                                                      | 0   | DAC channel 1 complementary output.                                                                                                                                                                                                                                                                                                          |  |  |

| VOUT2+    | D12                                                      | 0   | DAC channel 2 output. Leave pin floating in DAC38RF85                                                                                                                                                                                                                                                                                        |  |  |

| VOUT2-    | E12                                                      | 0   | DAC channel 2 complementary output. Leave pin floating in DAC38RF85                                                                                                                                                                                                                                                                          |  |  |

| VSENSE    | D4                                                       | 0   | Test pin for on chip parametrics. Can be left floating.                                                                                                                                                                                                                                                                                      |  |  |

| VSSCLK    | A8, A11, B8, B11, B12,<br>F8, F9, F10, J8, J9, J10       | -   | Clock ground.                                                                                                                                                                                                                                                                                                                                |  |  |

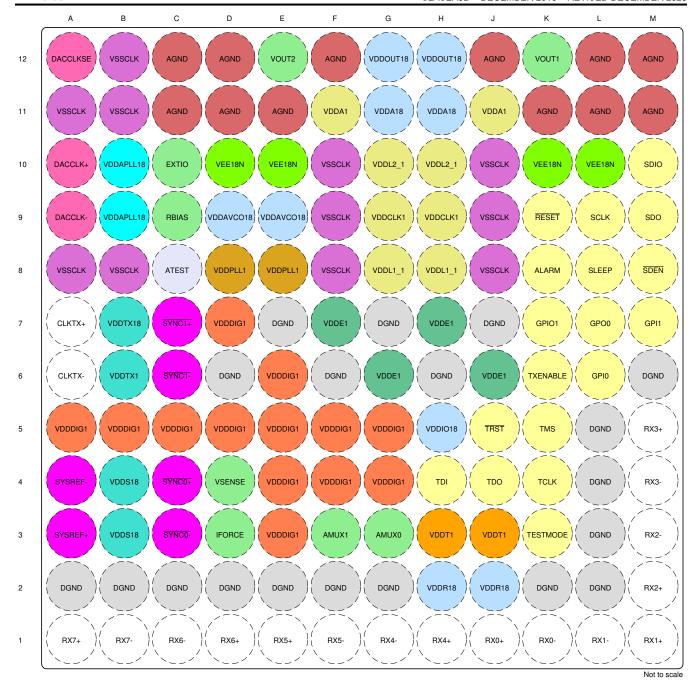

Figure 5-2. DAC38RF80, DAC38RF84, DAC38RF90 AAV Package 144-Pin (FCBGA) 144-Pin FCBGA Top View

#### Pin Functions - DAC38RF80, DAC38RF90, DAC38RF84

|       | PIN                                                              | I/O | DESCRIPTION                                                                                                                                      |  |  |  |

|-------|------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME  | NO.                                                              | 1/0 | DESCRIPTION                                                                                                                                      |  |  |  |

| AGND  | C11, C12, D11, E11,<br>F12, J12, K11, L11, M11,<br>M12, D12, L12 | -   | Analog ground.                                                                                                                                   |  |  |  |

| ALARM | K8                                                               | 0   | CMOS output for ALARM condition. Default polarity is active low, but can be changed to active high through RESET_CONFIG alm_out_pol control bit. |  |  |  |

| AMUX0 | G3                                                               | 0   | Analog test pin for SerDes, Lane 0 to Lane 3. Can be left floating.                                                                              |  |  |  |

| AMUX1 | F3                                                               | 0   | Analog test pin for SerDes, Lane 4 to Lane 7. Can be left floating.                                                                              |  |  |  |

### Pin Functions - DAC38RF80, DAC38RF90, DAC38RF84 (continued)

| NO.   NO.   NO.   Arabid test pin for DAC, references and PLL. Can be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                                               | 10113 | DAC36KF60, DAC36KF90, DAC36KF64 (CONtinued)                                                                                                                                                                        |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ATEST C8 O Analog test pin for DAC, references and PLL. Can be left floating.  CIKITX* A7 O Divided output coloc, internal 100 D differential termination, self-biased, positive terminal.  DACCLK* A10 I Device clock, informal 100 D differential termination, self-biased, positive terminal.  DACCLK* A10 I Device clock, informal 100 D differential termination, self-biased, positive terminal.  DACCLK* A2 I Device clock, informal 100 D differential termination, self-biased, positive terminal.  DACCLKSE A12 I Single ended device clock optional input. Can be left floating if not used internal 50 D termination.  A2, 18, 12, 12, 10, 10, 15, 16, 17, 17, 17, 17, 17, 17, 18, 18, 19, 11, 15, 11, 11, 11, 11, 11, 11, 11, 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NAME    | PIN                                                                           | I/O   | DESCRIPTION                                                                                                                                                                                                        |  |  |  |

| CLKTX+ A7 O Divided output clock, internal 100 Ω differential termination, self-biased, positive terminal.  CLKTX- A6 O Divided output clock, internal 100 Ω differential termination, self-biased, negative terminal.  DACCLK- A10 I Device clock, internal 100 Ω differential termination, self-biased, negative terminal.  DACCLK- A9 I Device clock, internal 100 Ω differential termination, self-biased, negative terminal.  DACCLK- A9 I Device clock, internal 100 Ω differential termination, self-biased, negative terminal.  Single ended device clock optional input. Can be left floating if not used, internal 50 Ω termination of the property |         |                                                                               | 0     | Analog test pin for DAC references and PLL Can be left floating                                                                                                                                                    |  |  |  |

| CLKTX A6 O Divided output clock, informal 100 Ω differential termination, self-biased, negative terminal.  DACCLK A70 I Device clock, internal 100 Ω differential termination, self-biased, positive terminal.  DACCLKSE A12 I DACCLKSE A12 I Single ended device clock optional input. Can be left floating if not used, internal 50 Ω termination  A2, B2, C2, D2, D2, E2, C7, F2, F6, C2, C7, FM, L1, L5, L5, L1, L5, L1, L5, L5, L5, L5, L5, L5, L5, L5, L5, L5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                                                                               |       |                                                                                                                                                                                                                    |  |  |  |

| DACCLK A10  I Device clock, internal 100 Ω differential termination, self-biased, positive terminal.  DACCLKS A2  I Self-color (A) Help of the Color (A)  |         |                                                                               |       | 1 1                                                                                                                                                                                                                |  |  |  |

| DACCLK  A  B  DACCLKSE  A  A  A  A  A  A  B  DACCLKSE  A  A  A  A  A  A  B  DACCLKSE  A  A  B  A  C  DACCLKSE  A  A  B  A  C  DACCLKSE  A  A  B  A  C  A  C  C  C  C  C  C  C  C  C  C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                                               |       |                                                                                                                                                                                                                    |  |  |  |

| DACCLKSE A12 I Single ended device clock optional input. Can be left floating if not used. Internal 50 Ω termination  A2, B2, C2, D2, D6, E2, F7, P7, P6, C2, G7, P16, J7, P62, L2, L3, L4, L5, L5, L4, L5, L5, L4, L5, L5, L5, L5, L5, L5, L5, L5, L5, L5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                                               |       |                                                                                                                                                                                                                    |  |  |  |

| DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                                               |       |                                                                                                                                                                                                                    |  |  |  |

| GP10 L6 Factory use only. User should GND.  GP11 M7 Factory use only. User should GND.  GP11 M7 Lose for CMDS SYNC01 signal.  GP00 L7 Used for CMDS SYNC01 signal.  GP101 K7 Used for CMDS SYNC01 signal.  GP102 Test pin for on chip parametrics. Can be left floating.  RBIAS C9 I/O Fill-scale output current his Change the full-scale output current through DACFS in register DACFS (8.5-72). Expected to be 3.6 k0 to GND for 40 mA full scale output.  RESET K9 I Active low input for chip RESET, which resets all the programming registers to their default state. Inter publishy.  RX0+ J1 I CML SerDes interface lane 0 input, positive  RX0- K1 I CML SerDes interface lane 0 input, positive  RX1+ M1 I CML SerDes interface lane 1 input, positive  RX1+ L1 I CML SerDes interface lane 1 input, positive  RX2+ M2 I CML SerDes interface lane 2 input, positive  RX2+ M3 I CML SerDes interface lane 2 input, positive  RX3+ M6 I CML SerDes interface lane 2 input, positive  RX3+ M6 I CML SerDes interface lane 2 input, positive  RX3- M4 I CML SerDes interface lane 3 input, positive  RX4+ H1 I CML SerDes interface lane 3 input, positive  RX4+ H1 I CML SerDes interface lane 4 input, positive  RX5- F1 I CML SerDes interface lane 6 input, positive  RX5- F1 I CML SerDes interface lane 6 input, positive  RX6- F1 I CML SerDes interface lane 6 input, positive  RX7- B1 CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane 6 input, positive  RX7- B1 I CML SerDes interface lane |         | A2, B2, C2, D2, D6, E2,<br>E7, F2, F6, G2, G7, H6,<br>J7, K2, L2, L3, L4, L5, |       |                                                                                                                                                                                                                    |  |  |  |

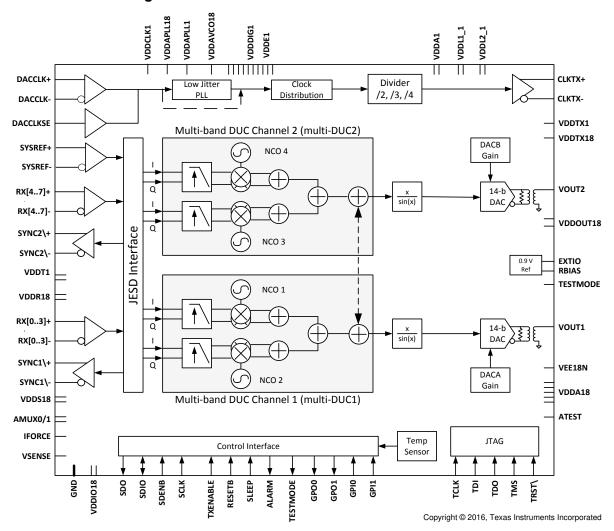

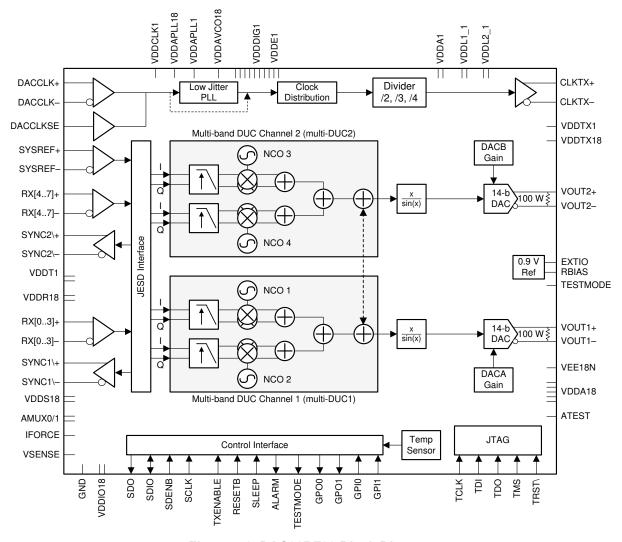

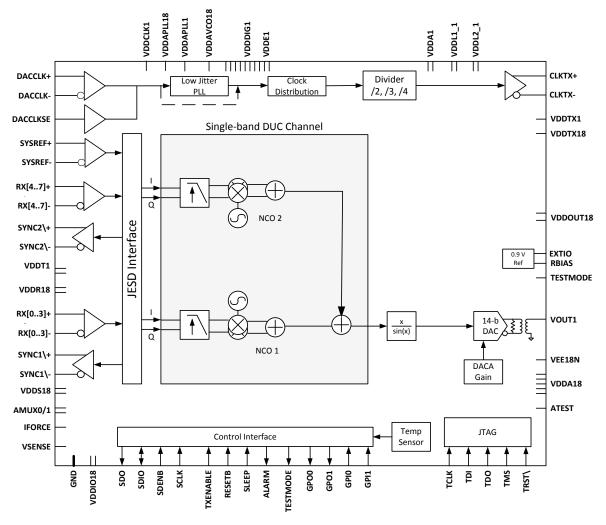

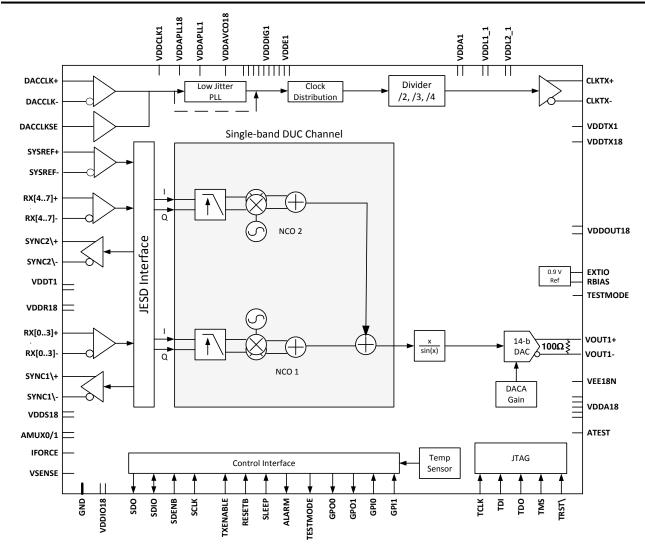

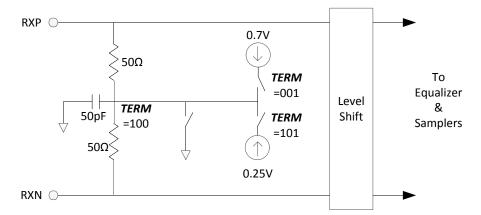

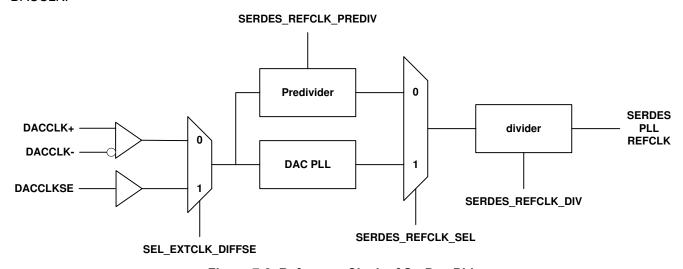

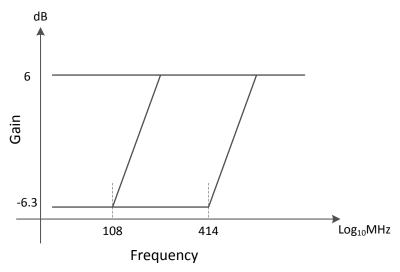

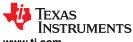

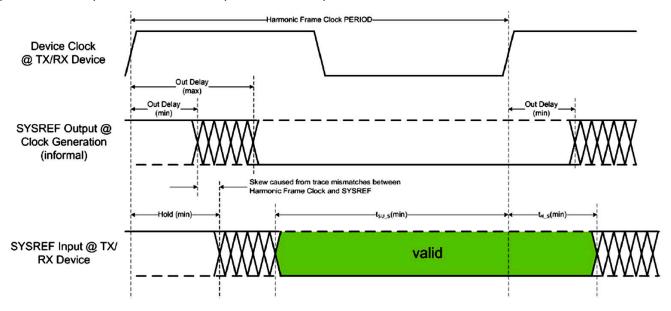

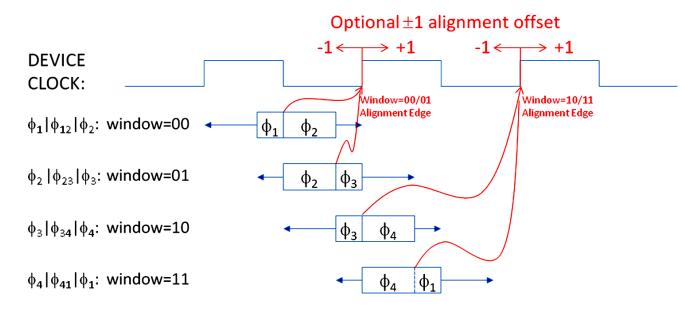

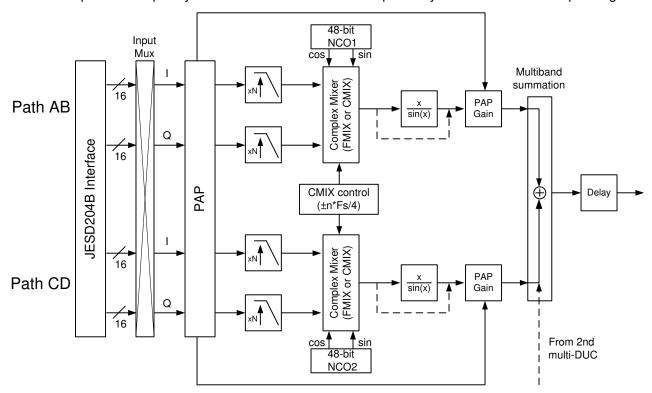

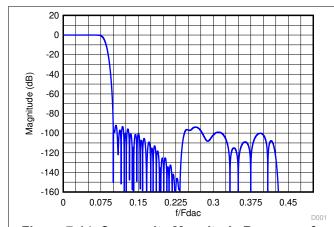

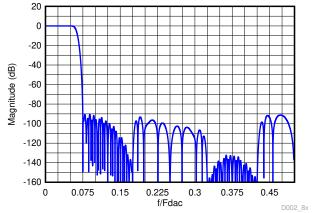

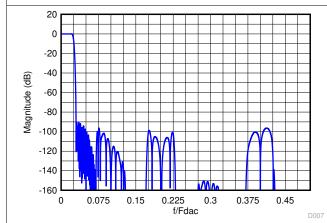

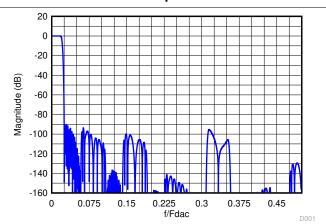

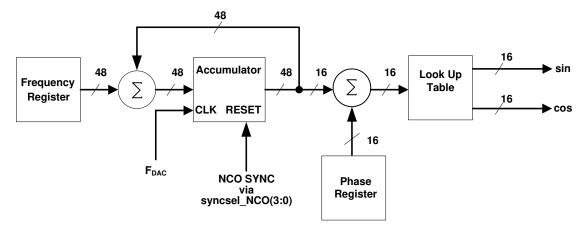

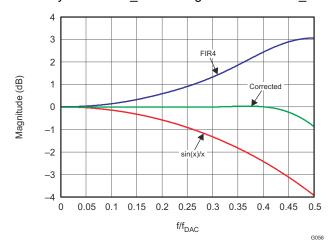

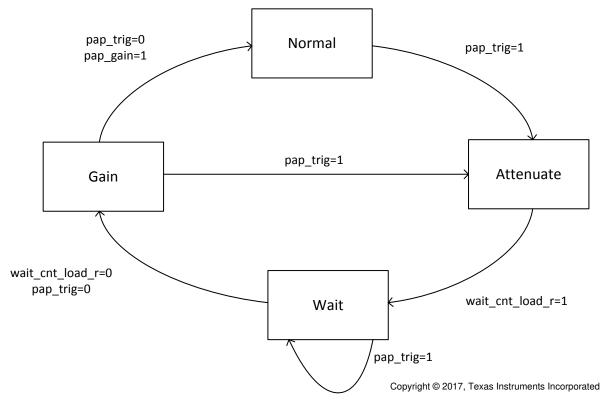

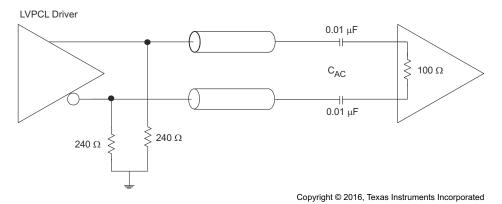

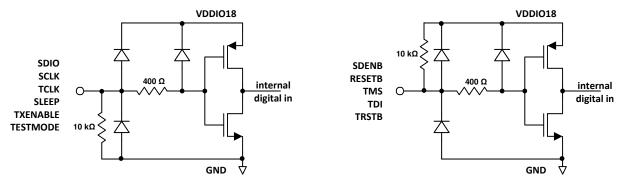

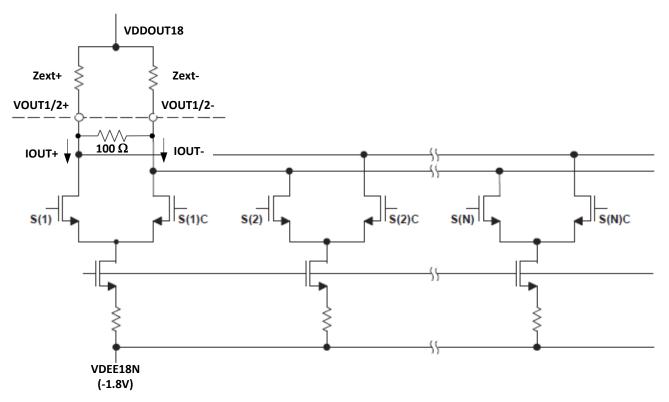

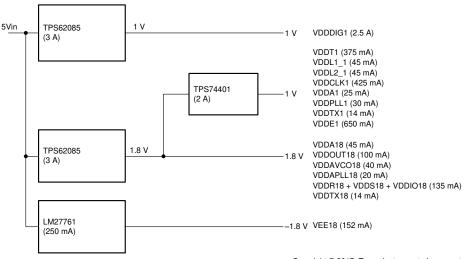

| GPI0 M7 Factory use only. User should GND. GPO0 L7 Used for CMOS SYNC01 signal. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D3 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGURE D4 Test pin for on chip parametrics. Can be left floating. FIGUR D4 Test pin for on chip parametrics. Can be left floating. FIGUR D4 Test pin for on chip parametrics. Can be left floating. FIGUR D4 Test pin for floatin | EXTIO   | C10                                                                           |       | Requires a 0.1 µF decoupling capacitor to AGND.                                                                                                                                                                    |  |  |  |