www.ti.com

SCAS858C - JUNE 2008-REVISED JANUARY 2012

# Ten Output High Performance Clock Synchronizer, Jitter Cleaner, and Clock Distributor

Check for Samples: CDCE72010

#### **FEATURES**

- High Performance LVPECL, LVDS, LVCMOS PLL Clock Synchronizer

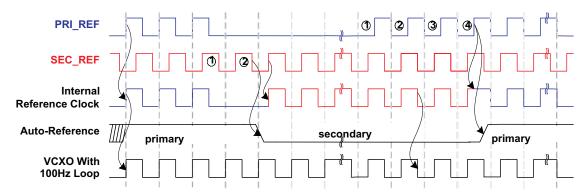

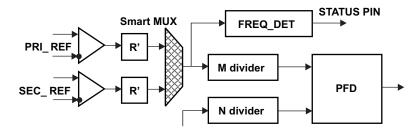

- Two Reference Clock Inputs (Primary and Secondary Clock) for Redundancy Support with Manual or Automatic Selection

- Accepts Two Differential Input (LVPECL or LVDS) References up to 500MHz (or Two LVCMOS Inputs up to 250MHz) as PLL Reference

- VCXO\_IN Clock is Synchronized to One of Two Reference Clocks

- VCXO\_IN Frequencies up to 1.5GHz (LVPECL) 800MHz for LVDS and 250MHz for LVCMOS Level Signaling

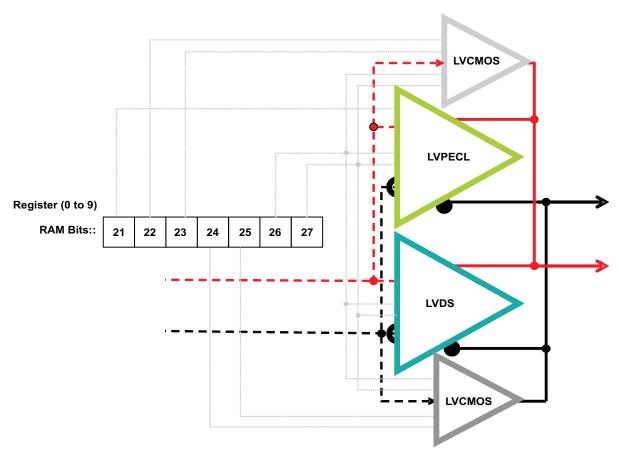

- Outputs Can be a Combination of LVPECL, LVDS, and LVCMOS (Up to 10 Differential LVPECL or LVDS Outputs or up to 20 LVCMOS Outputs), Output 9 can be Converted to an Auxiliary Input as a 2nd VC(X)O.

- Output Divider is Selectable to Divide by 1, 2, 3, 4, 5, 6, 8, 10, 12, 16, 18, 20, 24, 28, 30, 32, 36, 40, 42, 48, 50, 56, 60, 64, 70, or 80 On Each Output Individually up to Eight Dividers. (Except for Output 0 and 9, Output 0 Follows Output 1 Divider and Output 9 Follows Output 8 Divider)

- SPI Controllable Device Setting

- Individual Output Enable Control via SPI Interface

- Integrated On-Chip Non-Volatile Memory (EEPROM) to Store Settings without the Need to Apply High Voltage to the Device

- Optional Configuration Pins to Select Between Two Default Settings Stored in EEPROM

- Efficient Jitter Cleaning from Low PLL Loop Bandwidth

- Very Low Phase Noise PLL Core

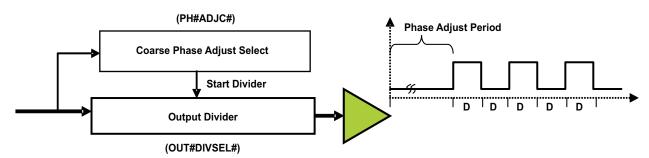

- Programmable Phase Offset (Input Reference to Outputs)

- Wide Charge-Pump Current Range From 200µA to 3mA

- Presets Charge-Pump to V<sub>CC\_CP</sub>/2 for Fast Center-Frequency Setting of VC(X)O, Controlled Via the SPI Bus

- SERDES Startup Mode (Depending on VCXO Range)

- Auxiliary Input: Output 9 can Serve as 2nd VCXO Input to Drive All Outputs or to Serve as PLL Feedback Signal

- RESET or HOLD Input Pin to Serve as Reset or Hold Functions

- REFERENCE SELECT for Manual Select Between Primary and Secondary Reference Clocks

- POWER DOWN (PD) to Put Device in Standby Mode

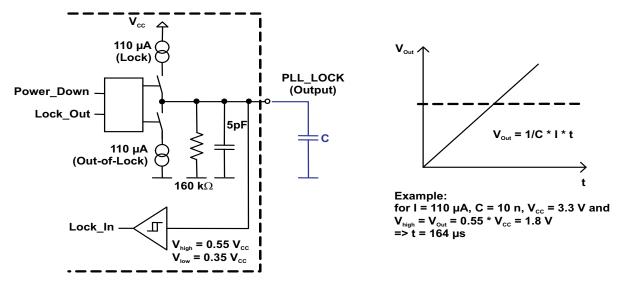

- Analog and Digital PLL Lock Indicator

- Internally Generated VBB Bias Voltages for Single-Ended Input Signals

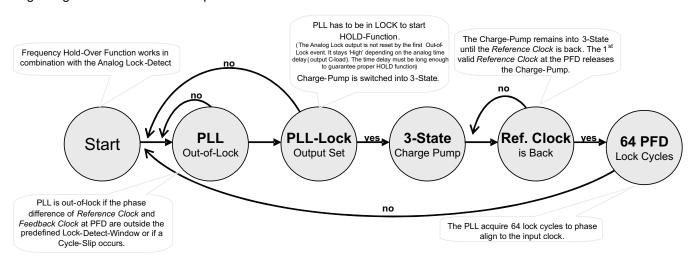

- Frequency Hold-Over Mode Activated by HOLD Pin or SPI Bus to Improve Fail-Safe Operation

- Input to All Outputs Skew Control

- Individual Skew Control for Each Output with Each Output Divider

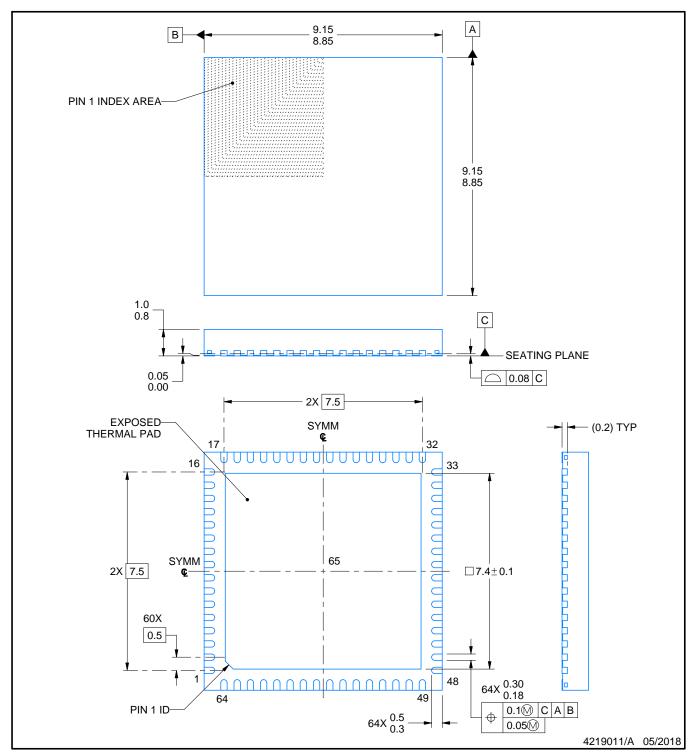

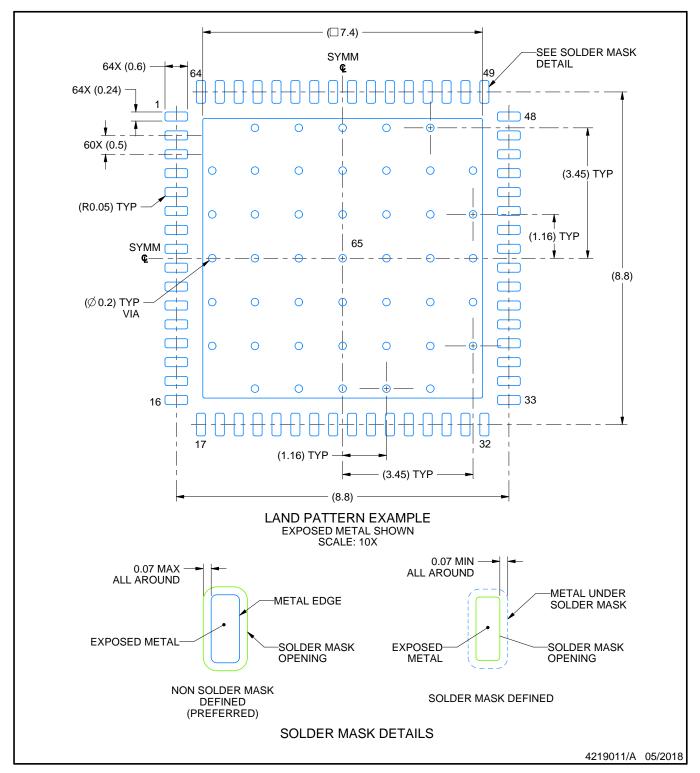

- Packaged in a QFN-64 Package

- ESD Protection Exceeds 2kV HBM

- Industrial Temperature Range of –40°C to 85°

#### **APPLICATIONS**

- Low Jitter Clock Driver for High-End Telecom and Wireless Applications

- High Precision Test Equipment

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

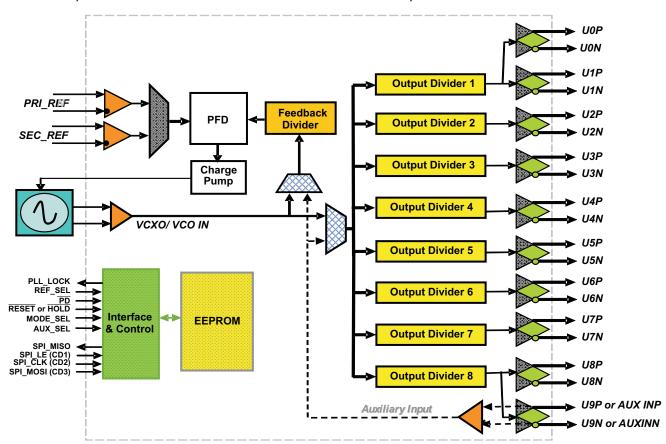

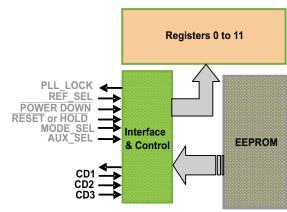

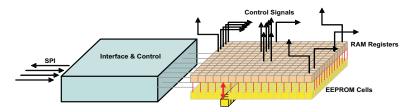

#### **DESCRIPTION**

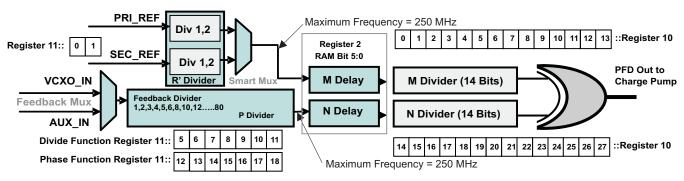

The CDCE72010 is a high-performance, low phase noise, and low skew clock synchronizer that synchronizes a VCXO (Voltage Controlled Crystal Oscillator) or VCO (Voltage Controlled Oscillator) frequency to one of two reference clocks. The clock path is fully programmable providing the user with a high degree of flexibility. The following relationship applies to the dividers:

Frequency (VCXO\_IN or AUX\_IN) / Frequency (PRI\_REF or SEC\_REF) = (P\*N)/(R\*M)

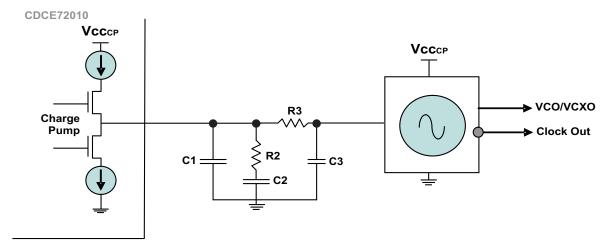

The VC(X)O\_IN clock operates up to 1.5GHz through the selection of external VC(X)O and loop filter components. The PLL loop bandwidth and damping factor can be adjusted to meet different system requirements.

The CDCE72010 can lock to one of two reference clock inputs (PRI\_REF and SEC\_REF) and supports frequency hold-over mode for fail-safe and system redundancy. The outputs of the CDCE72010 are user definable and can be any combination of up to 10 LVPECL/LVDS outputs or up to 20 LVCMOS outputs. The built-in synchronization latches ensure that all outputs are synchronized for very low output skew.

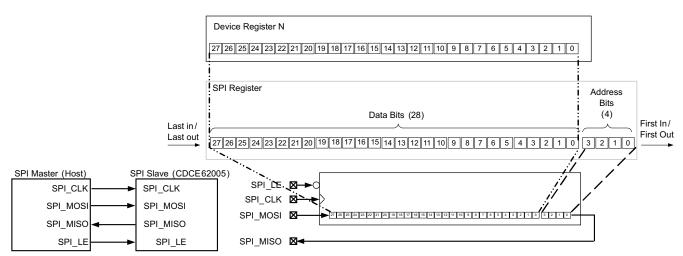

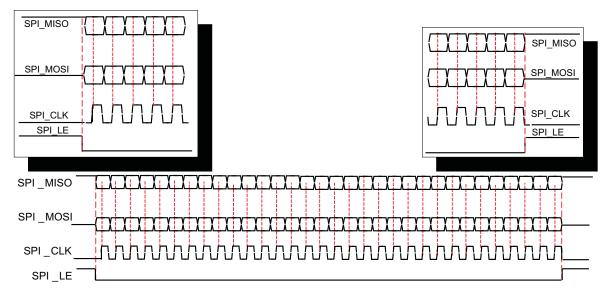

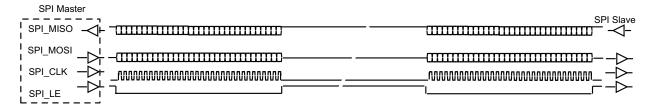

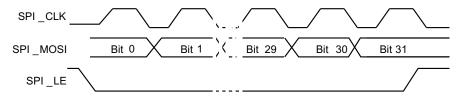

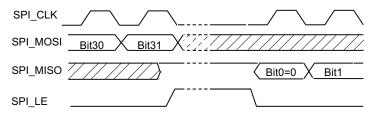

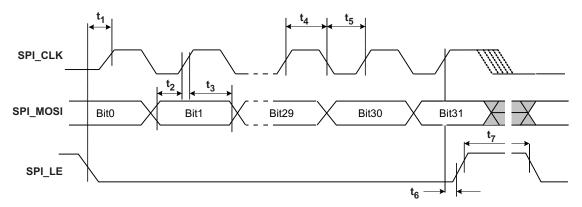

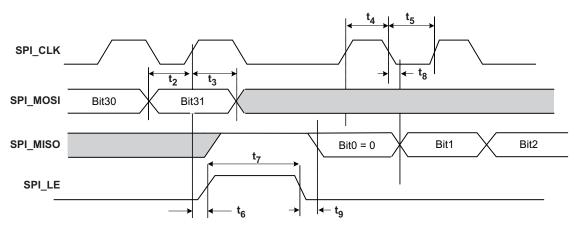

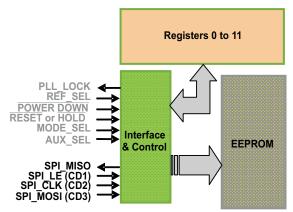

All device settings, including output signaling, divider value selection, input selection, and many more, are programmable with the SPI (4-wire Serial Peripheral Interface). The SPI allows individual control of the device settings.

The device operates in a 3.3V environment and is characterized for operation from -40°C to +85°C.

Figure 1. High Level Block Diagram of the CDCE72010

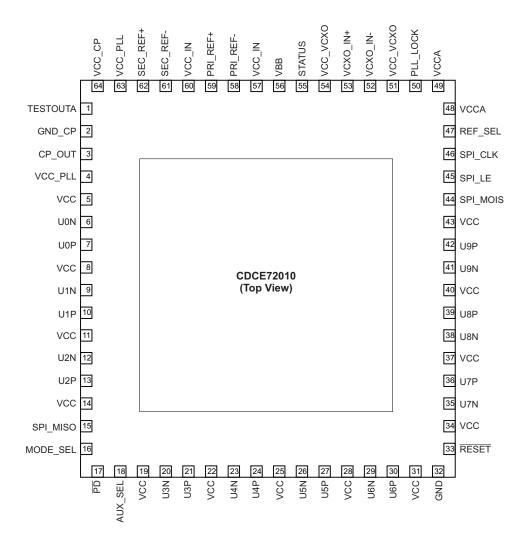

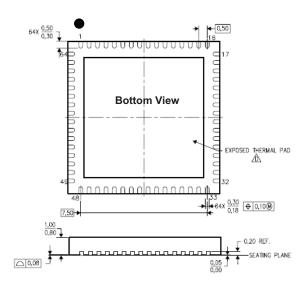

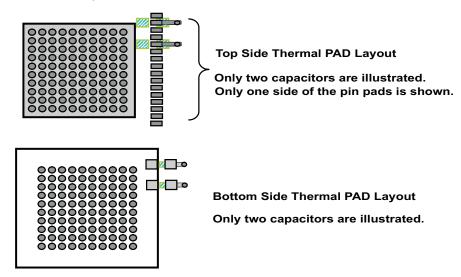

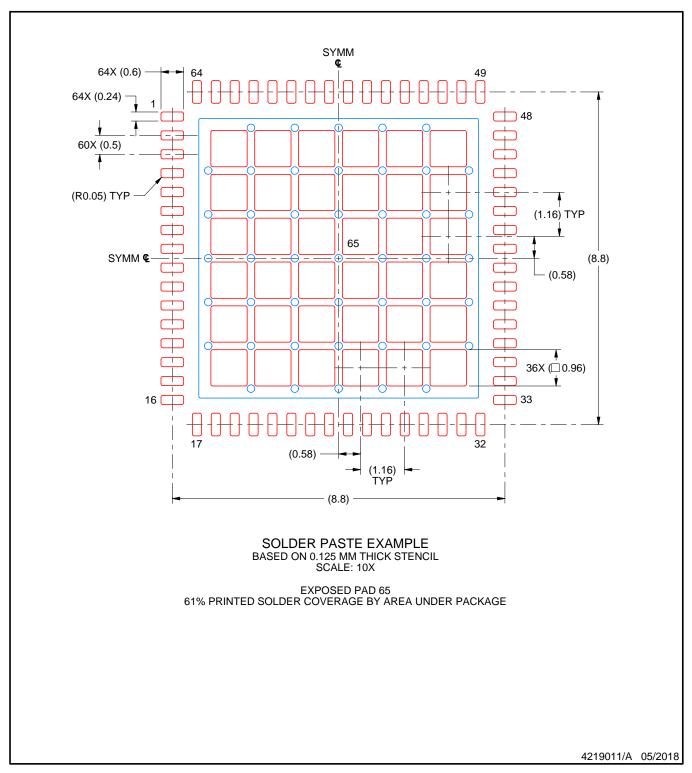

#### **PACKAGE**

The CDCE72010 is available in a 64-pin lead-free "green" plastic quad flatpack package with enhanced bottom thermal pad for heat dissipation. The Texas Instruments package designator is RGC (S-PQFP-N64).

#### **PIN FUNCTIONS**

|                    | PIN                                                        | 1/0          | DECODIDATION (1)                                                                                                                                                                          |

|--------------------|------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.                                                        | I/O          | DESCRIPTION <sup>(1)</sup>                                                                                                                                                                |

| vcc                | 5, 8, 11, 14, 19<br>22, 25, 28, 31<br>34, 37, 40 and<br>43 | Power        | 3.3V supply for the output buffers. (2)                                                                                                                                                   |

| VCC_PLL            | 4, 63                                                      | A.<br>Power  | 3.3V PLL supply voltage for the PLL circuitry.                                                                                                                                            |

| VCC_IN             | 57, 60                                                     | A.<br>Power  | 3.3V reference input buffers and circuitry supply voltage.                                                                                                                                |

| vcc_vcxo           | 51, 54                                                     | A.<br>Power  | 3.3V VCXO input buffer and circuitry supply voltage.                                                                                                                                      |

| GND                | 32                                                         | Ground       | Ground connected to thermal pad internally.                                                                                                                                               |

| GND                | PAD                                                        | Ground       | Ground on thermal pad. See layout recommendations.                                                                                                                                        |

| VCCA               | 48, 49                                                     | A.<br>Power  | 3.3V for internal analog circuitry power supply                                                                                                                                           |

| GND_CP             | 2                                                          | A.<br>Ground | Analog ground for charge pump                                                                                                                                                             |

| VCC_CP             | 64                                                         | A.<br>Power  | Charge pump power supply pin used to have the same supply as the external VCO/VCXO. It can be set from 2.3V to 3.6V.                                                                      |

| SPI_MISO           | 15                                                         | 0            | 3-State LVCMOS output is enabled when SPI_LE is asserted low. It is the serial data output to the SPI bus interface.                                                                      |

| SPI_LE<br>or CD1   | 45                                                         | I            | LVCMOS input, control latch enable for the Serial Programmable Interface (SPI), with hysteresis in SPI mode.  In configuration default mode this pin becomes CD1.                         |

| SPI_CLK<br>or CD2  | 46                                                         | I            | LVCMOS input, serial control clock input for the SPI bus interface, with hysteresis. <i>In configuration default mode this pin becomes CD2.</i>                                           |

| SPI_MOSI<br>or CD3 | 44                                                         | ı            | LVCMOS input, master out slave in as a serial control data input to CDCE72010 for the SPI bus interface. In configuration default mode this pin becomes CD3 and it should be tied to GND. |

<sup>(1)</sup> It is recommended to use supply filter to each VCC supply domain independently.

<sup>(2)</sup> Pin 5 and 8, pin 28 and 31, pin 40 and 43, pin 51 and 54, pin 4 and 63 and pin 60 and 57 are internally connected.

# PIN FUNCTIONS (continued)

| PI                                                                                              | N                                                                                   | 1/0 | DESCRIPTION <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                            | NO.                                                                                 | 1/0 | DESCRIPTION */                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MODE_SEL                                                                                        | 16                                                                                  | I   | SPI MODE = H; when driven high or left unconnected, it defaults to SPI bus interface mode.  CD (Configuration Default) MODE = L; If tied low the device goes into configuration default mode which is configured by CD1, CD2, CD3, and AUX_SEL. In configuration default mode the device loads various configuration defaults from the EEPROM into memory at start-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AUX_SEL                                                                                         | 18                                                                                  | I   | This pin is used in CD mode only. If set to "1" or left unconnected, it disables output 9 and enables the AUXILIARY input to drive all outputs from output0 to output8 depending on the EEPROM configuration. If driven low in CD mode, it enables output 9 and makes all outputs driven by the VCXO Input depending on the internal EEPROM configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| REF_SEL                                                                                         | 47                                                                                  | I   | If Auto Reference Select mode is OFF, this pin acts as an External Input Reference Select Pin; The REF_SEL signal selects one of two input clocks: REF_SEL [1]: PRI_REF is selected; REF_SEL [0]: SEC_REF is selected; The input has an internal 150-k $\Omega$ pull-up resistor and if left unconnected it will default to logic level "1". If Auto Reference Select mode in ON, this pin not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PD                                                                                              | 17                                                                                  | I   | This pin is active low and can be activated externally or by the corresponding bit in the SPI register (in case of logic high, the SPI setting is valid). This pin switches the device into powerdown mode The input has an internal 150-k $\Omega$ pull-up resistor and if left unconnected it will default to logic level "1".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RESET or<br>HOLD                                                                                | 33                                                                                  | I   | This LVCMOS input can be programmed (SPI) to act as $\overline{\text{HOLD}}$ or $\overline{\text{RESET}}$ . $\overline{\text{RESET}}$ is the default function. This pin is active low and can be activated external or via the corresponding bit in the SPI register. In the case of $\overline{\text{RESET}}$ , the CP (Charge Pump) is switched to 3-state and all counters are reset to zero. The LVPECL outputs are static low (N) and high (P) respectively, and the LVCMOS outputs are all low or high if inverted. In the case of $\overline{\text{HOLD}}$ , the CP (Charge Pump) is switched into 3-state mode only. After $\overline{\text{HOLD}}$ is released and with the next valid reference clock cycle, the charge pump is switched back into normal operation (CP stays in 3-state as long as no reference clock is valid). During $\overline{\text{HOLD}}$ , all outputs are at normal operation. This mode allows external control of "frequency hold-over" mode. The input has an internal 150-k $\Omega$ pull-up resistor. |

| VCXO_IN+                                                                                        | 53                                                                                  | - 1 | VCXO input (+) for LVPECL+, LVDS+, and LVCMOS level inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCXO_IN-                                                                                        | 52                                                                                  | 1   | Complementary VCXO input for LVPECL-, LVDS- inputs. In the case of a LVCMOS level input on VCXO IN+, ground this pin through 1k resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| PRI_REF+                                                                                        | 59                                                                                  | I   | Universal input buffer (LVPECL, LVDS, LVCMOS) positive input for the Primary Reference Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PRI_REF-                                                                                        | 58                                                                                  | 1   | Universal input buffer (LVPECL, LVDS) negative input for the Primary Reference Clock. In the case of LVCMOS signaling, ground this pin through 1k resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SEC_REF+                                                                                        | 62                                                                                  | 1   | Universal input buffer (LVPECL, LVDS, LVCMOS) positive input for the Secondary Reference Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SEC_REF-                                                                                        | 61                                                                                  | 1   | Universal input buffer (LVPECL, LVDS,) negative input for the Secondary Reference Clock. In the case of LVCMOS signaling, ground this pin through 1k resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TESTOUTA                                                                                        | 1                                                                                   | Α   | Analog Test Point for TI internal testing. Connect a $1k\Omega$ pull-down resistor or leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| STATUS                                                                                          | 55                                                                                  | 0   | LVCMOS output for TI internal testing. Leave unconnected unless it is configured as the IREF_CP pin. In this case it should be connected to a $12$ -k $\Omega$ resistor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CP_OUT                                                                                          | 3                                                                                   | AO  | Charge pump output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VBB                                                                                             | 56                                                                                  | AO  | Internal voltage bias analog output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

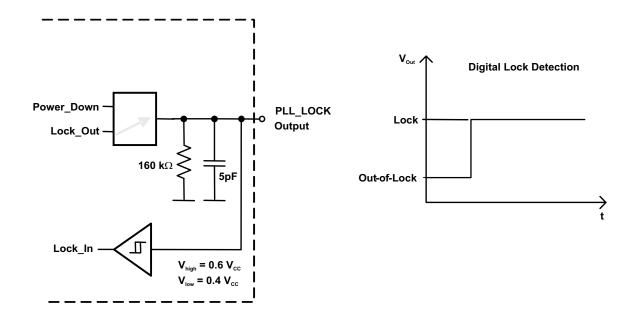

| PLL_LOCK                                                                                        | 50                                                                                  | AO  | LVCMOS output for PLL_LOCK information. This pin is set high if the PLL is in lock. This output can be programmed to be a digital lock detect or analog lock detect (see description of Analog Lock).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| U0P:U0N<br>U1P:U1N<br>U2P:U2N<br>U3P:U3N<br>U4P:U4N<br>U5P:U5N<br>U6P:U6N<br>U7P:U7N<br>U8P:U8N | 7, 6<br>10, 9<br>13, 12<br>21, 20<br>24, 23<br>27, 26<br>30, 29<br>36, 35<br>39, 38 | 0   | The outputs of the CDCE72010 are user definable and can be any combination of up to 9 LVPECL outputs, 9 LVDS outputs, or up to 18 LVCMOS outputs. The outputs are selectable via the SPI interface. The power-up setting is EEPROM configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### PIN FUNCTIONS (continued)

|                  | PIN NAME NO. |     | DESCRIPTION <sup>(1)</sup>                                                                                                                                                                                                                    |

|------------------|--------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME             |              |     | DESCRIPTION                                                                                                                                                                                                                                   |

| U9P or<br>AUXINP | 42           | I/O | Positive universal output buffer 9 can be 3-stated and used as a positive universal auxiliary input buffer (It requires external termination). The auxiliary input signal can be routed to drive the outputs or the feedback loop to the PLL. |

| U9N or<br>AUXINN | 41           | I/O | Negative universal output buffer 9 can be 3-stated and used as a negative universal auxiliary input buffer (It requires external termination). The auxiliary input signal can be routed to drive the outputs or the feedback loop to the PLL. |

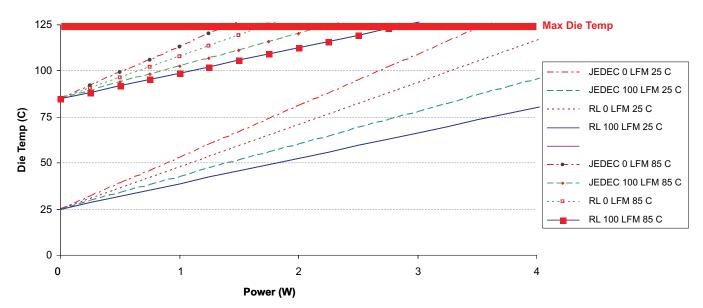

# PACKAGE THERMAL RESISTANCE FOR QFN (RGZ) PACKAGE<sup>(1)</sup> (2)

| AIRFLOW<br>(LFM) |                                         | θ <sub>JP</sub> (°C/W) <sup>(3)</sup> | θ <sub>JA</sub> (°C/W) |

|------------------|-----------------------------------------|---------------------------------------|------------------------|

| 0                | JEDEC compliant board (6×6 VIAs on PAD) | 1.5                                   | 28                     |

| 100              | JEDEC compliant board (6×6 VIAs on PAD) | 1.5                                   | 17.6                   |

| 0                | Recommended layout (10×10 VIAs on PAD)  | 1.5                                   | 22.8                   |

| 100              | Recommended layout (10×10 VIAs on PAD)  | 1.5                                   | 13.8                   |

- (1) The package thermal impedance is calculated in accordance with JESD 51 and JEDEC2S2P (high-k board).

- (2) Connected to GND with 9 thermal vias (0.3 mm diameter).

- (3)  $\theta_{JP}$  (Junction Pad) is used for the QFN package, because the main heat flow is from the junction to the GND-pad of the QFN.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

|                                                               |                                          |                                      | MIN  | MAX                   | UNIT |

|---------------------------------------------------------------|------------------------------------------|--------------------------------------|------|-----------------------|------|

| V <sub>CC</sub> ,<br>AV <sub>CC</sub> ,<br>V <sub>CC_CP</sub> | Supply voltage range <sup>(1)</sup>      |                                      | -0.5 | 4.6                   | V    |

| VI                                                            | Input voltage range (2)                  |                                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |

| Vo                                                            | Output voltage range <sup>(2)</sup>      |                                      | -0.5 | V <sub>CC</sub> + 0.5 | V    |

|                                                               | Input current                            | $V_1 < 0, V_1 > V_{CC}$              |      | ±20                   | mA   |

|                                                               | Output current for LVPECL/LVCMOS Outputs | 0 < V <sub>O</sub> < V <sub>CC</sub> |      | ±50                   | mA   |

| TJ                                                            | Junction temperature                     |                                      |      | 125                   | °C   |

| T <sub>stg</sub>                                              | Storage temperature range                |                                      | -65  | 150                   | °C   |

(1) All supply voltages have to be supplied simultaneously.

(2) The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

# **RECOMMENDED OPERATING CONDITIONS**

for the CDCE72010 device for under the specified industrial temperature range of -40°C to 85°C

|                                                                                             |                                                               |                                                                                                                                              | MIN                 | NOM                                                                                                                                            | MAX                      | UNIT |

|---------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|

| Power Supp                                                                                  | oly                                                           |                                                                                                                                              |                     |                                                                                                                                                |                          |      |

| V <sub>CC</sub>                                                                             | Supply voltage                                                |                                                                                                                                              | 3                   | 3.3                                                                                                                                            | 3.6                      | V    |

| V <sub>CC_PLL</sub> ,<br>V <sub>CC_IN</sub> ,<br>V <sub>CC_VCXO</sub> ,<br>V <sub>CCA</sub> | Analog supply voltage                                         |                                                                                                                                              | 3                   | 3.3                                                                                                                                            | 3.6                      |      |

| V <sub>CC_CP</sub>                                                                          |                                                               |                                                                                                                                              | 2.3                 |                                                                                                                                                | $V_{CC}$                 | V    |

| P <sub>LVPECL</sub>                                                                         | REF at 30.72MHz VCXO at<br>491.52MHz Outputs are<br>LVPECL-HS | Divider 1 set to divide by 8 (DCR 30%) Divider 2 set to divide by 4 (DCR 30%) Divider 3 set to divide by 2 (DCR 30%) Divider 4 set to divide |                     | 2.9                                                                                                                                            |                          | W    |

| P <sub>LVDS</sub>                                                                           | REF at 30.72MHz VCXO at 491.52MHz Outputs are LVDS-HS         | by 2 (DCR 30%) Divider 5 set to divide by 1 (DCR 30%) Divider 6 set to divide by 1 (DCR 0%) Divider 7 set to divide by 1 (DCR 0%)            |                     | 2.0                                                                                                                                            |                          | W    |

| P <sub>LVCMOS</sub>                                                                         | REF at 30.72MHz VCXO at 122.88MHz Outputs are LVCMOS          | Divider 8 set to divide by 1 (DCR 0%) DCR: Divider Current Reduction Setting                                                                 |                     | 2.2                                                                                                                                            |                          | W    |

| P <sub>OFF</sub>                                                                            | REF at 30.72MHz VCXO at 491.52MHz                             | Dividers are disabled. Outputs are disabled.                                                                                                 |                     | 775                                                                                                                                            |                          | mW   |

| P <sub>PD</sub>                                                                             |                                                               | Device is powered down                                                                                                                       |                     | 3 3.3 3.6 3 3.3 3.6 2.3 V <sub>CC</sub> 2.9 2.0 2.2 775 30 0.1 1.3 1.0 V <sub>CC</sub> 0.3 7 0 0.3 V <sub>CC</sub> (CC V <sub>CC</sub> -1.2 20 |                          | mW   |

| Typical Oper                                                                                | rating Conditions at $V_{CC}$ = 3.3V and 25°                  | C unless otherwise specified.                                                                                                                |                     |                                                                                                                                                |                          |      |

| Differential                                                                                | Input Mode (PRI_REF, SEC_REF, VC                              | XO_IN and AUX_IN)                                                                                                                            |                     |                                                                                                                                                |                          |      |

| $V_{IN}$                                                                                    | Differential input amplitude                                  | $(V_{INP} - V_{INN})$                                                                                                                        | 0.1                 |                                                                                                                                                | 1.3                      | V    |

| V <sub>ICM</sub>                                                                            | Common-mode input voltage                                     |                                                                                                                                              | 1.0                 |                                                                                                                                                | V <sub>CC</sub> -<br>0.3 | V    |

| I <sub>IH</sub>                                                                             | Differential input current high ( No internal termination)    | $V_{I} = V_{CC}, V_{CC} = 3.6 \text{ V}$                                                                                                     |                     |                                                                                                                                                | 20                       | μΑ   |

| I <sub>IL</sub>                                                                             | Differential input current low( No internal termination)      | V <sub>I</sub> = 0 V, V <sub>CC</sub> = 3.6 V                                                                                                | -20                 |                                                                                                                                                | 20                       | μΑ   |

|                                                                                             | Input capacitance on PRI_REF, SE                              | C_REF and VCXO_REF                                                                                                                           |                     | 3                                                                                                                                              |                          | pF   |

|                                                                                             | Input capacitance on AUX_IN                                   |                                                                                                                                              |                     | 7                                                                                                                                              |                          | pF   |

| LVCMOS In                                                                                   | put Mode (SPI_CLK, SPI_MOSI, SPI_                             | LE, PD, RESET, REF_SEL, MODE_SEL)                                                                                                            |                     |                                                                                                                                                |                          |      |

| $V_{IL}$                                                                                    | Low-level input voltage LVCMOS                                |                                                                                                                                              | 0                   |                                                                                                                                                | $0.3\ V_{CC}$            | V    |

| V <sub>IH</sub>                                                                             | High-level input voltage LVCMOS                               | ,                                                                                                                                            | 0.7 V <sub>CC</sub> |                                                                                                                                                | V <sub>CC</sub>          | V    |

| V <sub>IK</sub>                                                                             | LVCMOS input clamp voltage                                    | $V_{CC} = 3 \text{ V, II} = -18 \text{ mA}$                                                                                                  |                     |                                                                                                                                                | -1.2                     | V    |

| I <sub>IH</sub>                                                                             | LVCMOS input current                                          | $V_I = V_{CC}$ , $V_{CC} = 3.6 \text{ V}$                                                                                                    |                     |                                                                                                                                                | 20                       | μΑ   |

| I <sub>IL</sub>                                                                             | LVCMOS input                                                  | $V_{I} = 0 \text{ V}, V_{CC} = 3.6 \text{ V}$                                                                                                | -10                 |                                                                                                                                                | -40                      | μΑ   |

| C <sub>I</sub>                                                                              | Input capacitance (LVCMOS signals)                            | V <sub>I</sub> = 0 V or V <sub>CC</sub>                                                                                                      |                     | 3                                                                                                                                              |                          | pF   |

### **TIMING REQUIREMENTS**

over recommended ranges of supply voltage, load, and operating free-air temperature (1) (2)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PARAMETER                                                                                                                         | MIN | TYP MAX | UNIT |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|---------|------|

| PRI_REF/SEC_REF    f_REF - Single   For single-ended inputs (LVCMOS) on PRI_REF and SEC_REF   250     For differential inputs (LVDS and LVPECL) on PRI_REF and SEC_REF   500     SEC_REF (R divider set to DIV2)   500     Duty Cycle   Duty cycle of PRI_REF or SEC_REF   40%   60%     t_slew   Input signal slew rate   1     VCXO_IN, AUX_IN     F_REF - Single   For single-ended inputs (LVCMOS)   250     f_REF - Diff   For differential inputs (LVDS and LVPECL)   1500     Duty Cycle   Duty cycle of PRI_REF or SEC_REF   40%   60%     t_slew   Input signal slew rate   1     PD, RESET, Hold, REF SEL |                                                                                                                                   |     |         |      |

| f <sub>REF</sub> - Single                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | For single-ended inputs ( LVCMOS) on PRI_REF and SEC_REF                                                                          |     | 250     | MHz  |

| f <sub>REF - Diff</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SEC_REF                                                                                                                           |     | 500     | MHz  |

| Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Duty cycle of PRI_REF or SEC_REF                                                                                                  | 40% | 60%     |      |

| t <sub>slew</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input signal slew rate                                                                                                            | 1   |         | V/ns |

| VCXO_IN, AU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | X_IN                                                                                                                              |     |         |      |

| f <sub>REF - Single</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | For single-ended inputs ( LVCMOS)                                                                                                 |     | 250     | MHz  |

| f <sub>REF - Diff</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | For differential inputs (LVDS and LVPECL)                                                                                         |     | 1500    | MHz  |

| Duty Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Duty cycle of PRI_REF or SEC_REF                                                                                                  | 40% | 60%     |      |

| t <sub>slew</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Input signal slew rate                                                                                                            | 1   |         | V/ns |

| PD, RESET, H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lold, REF_SEL                                                                                                                     |     |         |      |

| t <sub>r</sub> /t <sub>f</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Rise and fall time of the $\overline{PD}$ , $\overline{RESET}$ , $\overline{Hold}$ , REF_SEL signal from 20% to 80% of the signal |     | 4       | ns   |

<sup>(1)</sup> From 250MHz to 500MHz is achieved by setting the divide by 2 in the R-divdier

<sup>(2)</sup> If the feedback clock (derived from the VCXO input) is less than 2MHz, the device stays in normal operation mode but the frequency detection circuitry resets the STATUS\_VCXO signal and PLL\_LOCK signal to low. Both status signals are no longer relevant. This affects the HOLD-Over-Function as well as the PLL\_LOCK signal is no longer valid.

#### **AC/DC CHARACTERISTICS**

|                    | PARAMETER                                                                                  | TEST                                                 | CONDITIONS                           | MIN                  | TYP <sup>(1)</sup> | MAX | UNIT   |

|--------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------|----------------------|--------------------|-----|--------|

| SPI Output         | (MISO) / PLL_LOCK                                                                          | I                                                    |                                      |                      |                    |     |        |

| I <sub>OH</sub>    | High-level output current                                                                  | V <sub>CC</sub> = 3.3 V                              | V <sub>O</sub> = 1.65 V              |                      | -30                |     | mA     |

| I <sub>OL</sub>    | Low-level output current                                                                   | V <sub>CC</sub> = 3.3 V                              | V <sub>O</sub> = 1.65 V              |                      | 33                 |     | mA     |

| V <sub>OH</sub>    | High-level output voltage for LVCMOS outputs                                               | V <sub>CC</sub> = 3 V                                | I <sub>OH</sub> = -100 μA            | V <sub>CC</sub> -0.5 |                    |     | V      |

| V <sub>OL</sub>    | Low-level output voltage for LVCMOS outputs                                                | V <sub>CC</sub> = 3 V                                | I <sub>OL</sub> = 100 μA             |                      |                    | 0.3 | V      |

| Co                 | Output capacitance on MISO                                                                 | V <sub>CC</sub> = 3.3 V; VO =                        | 0 V or V <sub>CC</sub>               |                      | 3                  |     | pF     |

| I <sub>OZH</sub>   | 2 state output ourrant                                                                     | $V_{O} = V_{CC}$                                     |                                      |                      | 5                  |     | μA     |

| l <sub>OZL</sub>   | 3-state output current                                                                     | $V_O = V_{CC}$<br>$V_O = 0 V$                        |                                      |                      | <b>-</b> 5         |     | μΑ     |

| EEPROM             |                                                                                            |                                                      |                                      |                      |                    |     |        |

| EEcyc              | Programming cycle of EEPROM                                                                |                                                      |                                      | 100                  | 1000               |     | Cycles |

| EEret              | Data retention                                                                             |                                                      |                                      | 10                   |                    |     | Years  |

| VBB                | <u> </u>                                                                                   |                                                      |                                      |                      |                    |     |        |

| VBB                | VCXO termination voltage<br>depends on the settings<br>of the VCXO/AUX_IN<br>input buffers | IBB = $-0.2$ mA<br>Depending on the = 25 Ω           | setting, Output impedance            | 0.9                  |                    | 1.9 | V      |

| Input Buffe        | ers Internal Termination Res                                                               | istors (VCXO_IN,F                                    | PRI_REF and SEC_REF)                 |                      |                    |     |        |

|                    | Termination resistance <sup>(2)</sup>                                                      | Single ended                                         |                                      |                      | 53                 |     | Ω      |

| Phase Dete         | ector                                                                                      |                                                      |                                      |                      |                    |     |        |

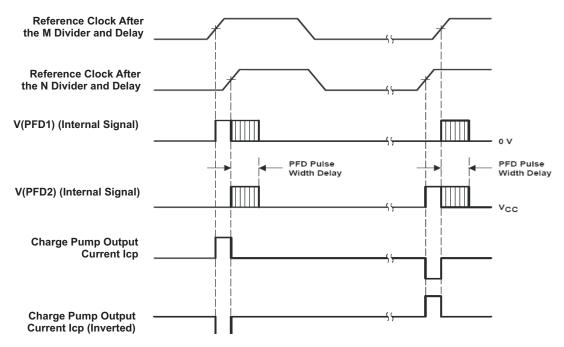

| f <sub>CPmax</sub> | Maximum charge pump frequency                                                              | Default PFD pulse                                    | width delay                          |                      |                    | 100 | MHz    |

| Charge Pu          | mp                                                                                         |                                                      |                                      |                      |                    |     |        |

| ICP3St             | Charge pump 3-state current                                                                | 0.5 V < VCP < V <sub>C</sub>                         | <sub>C_CP</sub> – 0.5 V              |                      | 15                 |     | nA     |

| ICPA               | ICP absolute accuracy                                                                      | $V_{CP} = 0.5 V_{CC\_CP};$                           | internal reference resistor          |                      | 20%                |     |        |

| ICPA               | ICP absolute accuracy                                                                      | $VCP = 0.5 V_{CC\_CP}$ 12kΩ (1%)                     | ; external reference resistor        |                      | 5%                 |     |        |

| ICPM               | Sink/source current matching                                                               | 0.5 V < VCP < V <sub>C</sub> settings                | <sub>C_CP</sub> - 0.5 V, SPI default |                      | %4                 |     |        |

| IVCPM              | ICP vs VCP matching                                                                        | 0.5 V < VCP < V <sub>C</sub>                         | <sub>C_CP</sub> – 0.5 V              |                      | 6%                 |     |        |

| $V_{I\_REF\_CP}$   | Voltage on STATUS PIN when configured as I_REF_CP                                          | 12-kΩ resitor to G (External current p pump current) | ND path for accurate charge          |                      | 1.24               |     | V      |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 3.3 V,  $T_A$  = 25°C. (2) Termination resistor can vary by 20%.

over the specified industrial temperature range of -40°C to 85°C

|                                  | PARAMETER                                               | TEST C                                                            | ONDITIONS                 | MIN                   | TYP <sup>(1)</sup> | MAX | UNIT |

|----------------------------------|---------------------------------------------------------|-------------------------------------------------------------------|---------------------------|-----------------------|--------------------|-----|------|

| LVCMOS O                         | utput                                                   |                                                                   |                           |                       |                    |     |      |

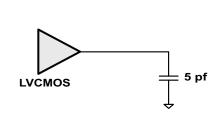

| f <sub>clk</sub>                 | Output frequency (see Figure 2)                         | Load = 5 pF to GND                                                |                           |                       |                    | 250 | MHz  |

| V <sub>OH</sub>                  | High-level output voltage for LVCMOS outputs            | V <sub>CC</sub> = min to max                                      | I <sub>OH</sub> = -100 μA | V <sub>CC</sub> - 0.5 |                    |     | V    |

| $V_{OL}$                         | Low-level output voltage for LVCMOS outputs             | V <sub>CC</sub> = min to max                                      | I <sub>OL</sub> =100 μA   |                       |                    | 0.3 | V    |

| I <sub>OH</sub>                  | High-level output current                               | V <sub>CC</sub> = 3.3 V                                           | V <sub>O</sub> = 1.65 V   |                       | -30                |     | mA   |

| l <sub>OL</sub>                  | Low-level output current                                | $V_{CC} = 3.3 \text{ V},$                                         | V <sub>O</sub> = 1.65 V   |                       | 33                 |     | mΑ   |

| t <sub>pho</sub>                 | Phase offset without using available delay adjustment   | VCXO at 491.52MHz<br>16 and reference at<br>delays are fixed to o | •                         | 13                    |                    | ns  |      |

| t <sub>pd(LH)</sub> /<br>tpd(HL) | Propagation delay from VCXO_IN to Outputs               | Crosspoint to V <sub>CC</sub> /2,                                 | load = 5 pF               |                       | 3.3                |     | ns   |

|                                  | Skew, output-to-output<br>LVCMOS single-ended<br>output | Divide by 1 for all dividers                                      |                           |                       | 75                 |     |      |

| t <sub>sk(o)</sub>               |                                                         | Divide by 16 for all dividers                                     |                           | 75                    |                    | ps  |      |

| -5K(U)                           |                                                         | Divide by 1 for divide all other dividers                         | er 1 and divide by 16 for |                       | 1400               |     | ,,,  |

| Co                               | Output capacitance on Y0 to Y8                          | $V_{CC} = 3.3 \text{ V}; V_{O} = 0$                               | V or V <sub>CC</sub>      |                       | 5                  |     | pF   |

| Co                               | Output capacitance on Y9                                | $V_{CC} = 3.3 \text{ V}; V_{O} = 0$                               | V or V <sub>CC</sub>      |                       | 5                  |     | pF   |

| I <sub>OZH</sub>                 | 3-state LVCMOS output current                           | $V_O = V_{CC}$                                                    |                           |                       | 5                  |     | μΑ   |

| I <sub>OZL</sub>                 | 3-state LVCMOS output current                           | V <sub>O</sub> = 0V                                               |                           |                       | <b>–</b> 5         |     | μΑ   |

| I <sub>OPDH</sub>                | Power-down output current                               | $V_O = V_{CC}$                                                    |                           |                       |                    | 25  | μΑ   |

| I <sub>OPDL</sub>                | Power-down output current                               | V <sub>O</sub> = 0V                                               |                           |                       |                    | 5   | μΑ   |

| Duty cycle                       | LVCMOS                                                  | With 50% / 50% duty clock                                         | cycle of the VCXO input   | 45%                   |                    | 55% |      |

| t <sub>slew-rate</sub>           | Output rise/fall slew rate                              |                                                                   |                           | 3.6                   |                    | 5.2 | V/ns |

<sup>(1)</sup> All typical values are at  $V_{CC}$  = 3.3 V,  $T_A$  = 25°C.

Product Folder Link(s): CDCE72010

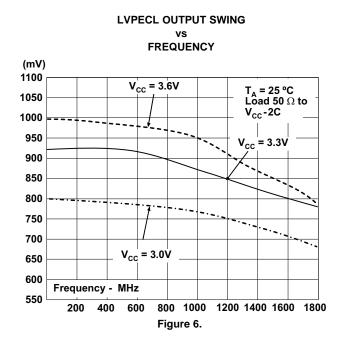

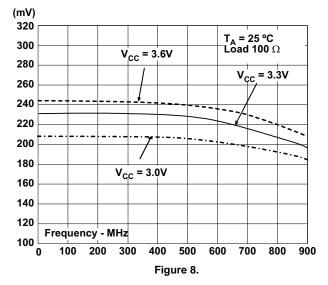

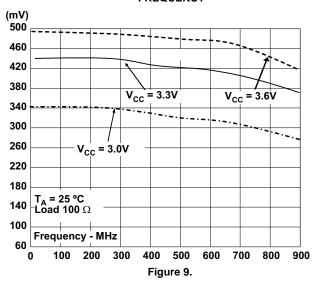

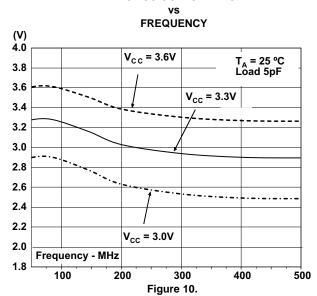

|                                 | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TEST CONDITIONS                                                                                                        | MIN | TYP <sup>(1)</sup> | MAX | UNIT |