# BUF802 Wide-Bandwidth, 2.3nV/ $\sqrt{Hz}$ , High-Input Impedance Buffer

### 1 Features

- Large-signal bandwidth (1V<sub>PP</sub>): 3.1GHz

- Slew rate: 7000V/µs

- Input voltage noise: 2.3nV/√Hz

- 1% settling time: 0.7ns

- Input-impedance: 50GΩ || 2.4pF

- Capable of driving 50Ω load

- Adjustable quiescent current for power and performance trade-off

- Integrated input and output clamp with fast overdrive recovery

- Voltage supply: ±4.5V to ±6.5V

# **2** Applications

- Oscilloscope front-end

- · High-frequency data acquisition

- High input-impedance and high slew rate T&M systems

- Oscilloscope encoder and front-end add-on cards

- Active probes

- Nondestructive testing (NDT)

#### **3 Description**

The BUF802 device is an open-loop, unity gain buffer with a JFET input stage that offers lownoise, high-impedance buffering for data acquisition system (DAQ) front ends. The BUF802 supports dc-to-3.1GHz of bandwidth while offering excellent distortion and noise performance across the frequency range.

The BUF802 can be used in a composite loop with a precision amplifier in applications where higher precision performance is required. The BUF802 uses a remarkable architecture to simplify the design of high-precision, wide-bandwidth composite loops.

The BUF802 features an adjustable quiescent current pin that enables designers to trade bandwidth and distortion for a lower quiescent current. This feature makes the device an excellent choice across a widefrequency range. The BUF802 has integrated input and output clamps to protect the device and the subsequent signal-chain from overdrive voltages.

#### Device Information

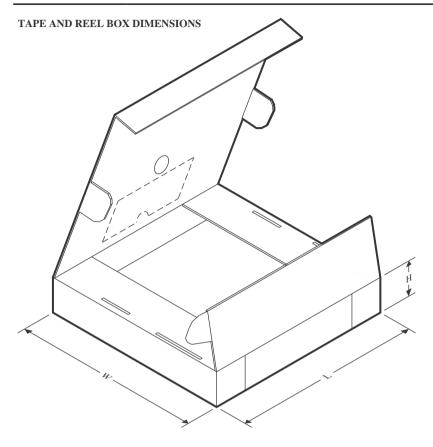

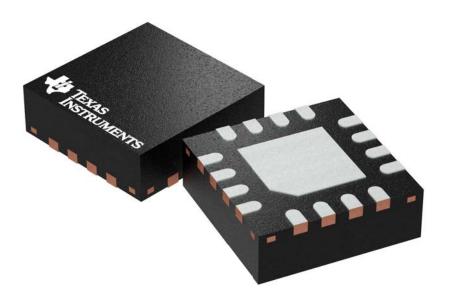

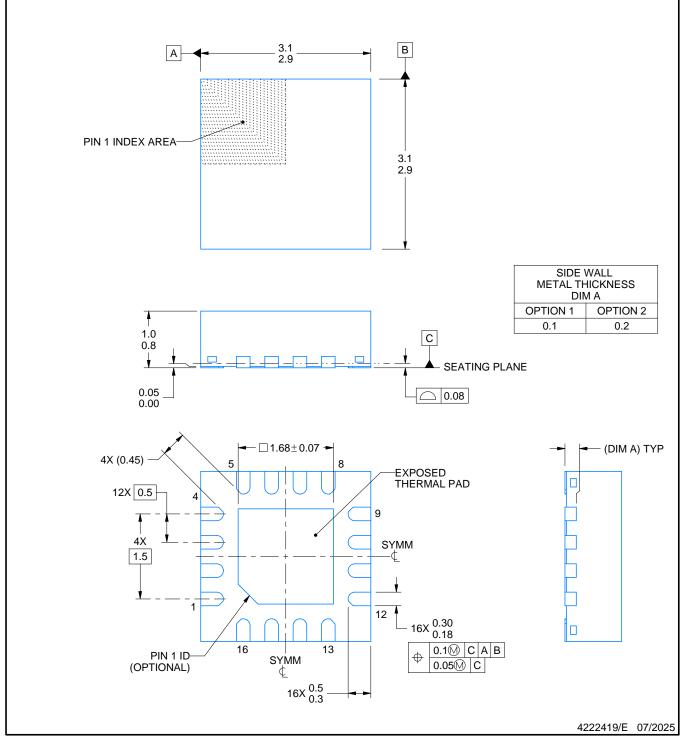

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| BUF802      | RGT (VQFN, 16)         | 3mm × 3mm                   |

(1) For more information, see Section 11.

(2) The package size (length × width) is a nominal value and includes pins, where applicable.

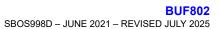

**Transient Response**

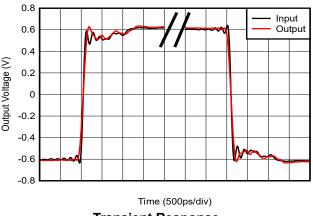

Impedance Transformation Circuit Using the BUF802

# **Table of Contents**

| 1 Features                                           | 1    |

|------------------------------------------------------|------|

| 2 Applications                                       | 1    |

| 3 Description                                        | 1    |

| 4 Pin Configuration and Functions                    | 3    |

| 5 Specifications                                     | 4    |

| 5.1 Absolute Maximum Ratings                         | 4    |

| 5.2 ESD Ratings                                      |      |

| 5.3 Recommended Operating Conditions                 |      |

| 5.4 Thermal Information                              | 4    |

| 5.5 Electrical Characteristics Wide Bandwidth Mode   | 5    |

| 5.6 Electrical Characteristics Low Quiescent Current |      |

| Mode                                                 | 7    |

| 5.7 Typical Characteristics                          | 8    |

| 6 Parameter Measurement Information                  | . 14 |

| 7 Detailed Description                               | 15   |

| 7.1 Overview                                         | . 15 |

| 7.2 Functional Block Diagram                         |      |

| -                                                    |      |

| 7.3 Feature Description                             | 16   |

|-----------------------------------------------------|------|

| 7.4 Device Functional Modes                         | 19   |

| 8 Application and Implementation                    | . 22 |

| 8.1 Application Information                         | . 22 |

| 8.2 Typical Applications                            |      |

| 8.3 Power Supply Recommendations                    | 28   |

| 8.4 Layout                                          | . 28 |

| 9 Device and Documentation Support                  | 31   |

| 9.1 Documentation Support                           | . 31 |

| 9.2 Receiving Notification of Documentation Updates | 31   |

| 9.3 Support Resources                               | . 31 |

| 9.4 Trademarks                                      | 31   |

| 9.5 Electrostatic Discharge Caution                 | 31   |

| 9.6 Glossary                                        |      |

| 10 Revision History                                 | . 31 |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 32 |

|                                                     |      |

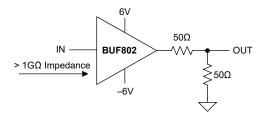

# **4** Pin Configuration and Functions

#### Figure 4-1. RGT Package, 16-Pin VQFN (Top View and Bottom View)

| Р                               | NIN       | TYPE <sup>(1)</sup>                                       | OPERATING | DESCRIPTION                                                                                              |  |

|---------------------------------|-----------|-----------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------|--|

| NAME                            | NO.       | <b>TYPE</b> <sup>(1)</sup> <b>MODE</b> <sup>(2) (3)</sup> |           | DESCRIPTION                                                                                              |  |

| Aux_Bias                        | 6         | Р                                                         | CL        | Connect to $V_{S-}$ to enable control of OUT through the In_Aux                                          |  |

| CLH                             | 15        | I                                                         | BF, CL    | Input pin for setting positive clamp voltage                                                             |  |

| CLL                             | 14        | I                                                         | BF, CL    | Input pin for setting negative clamp voltage                                                             |  |

| IN                              | 2         | I                                                         | BF, CL    | Signal input                                                                                             |  |

| In_Aux                          | 4         | I                                                         | CL        | Auxiliary input for controlling OUT through an external amplifier                                        |  |

| In_Bias                         | 3         | I                                                         | CL        | JFET biasing pin                                                                                         |  |

| NC                              | 16, 13, 9 | NC                                                        |           | Do not connect                                                                                           |  |

| OUT                             | 11        | 0                                                         | BF, CL    | Signal output                                                                                            |  |

| R_Bias                          | 7         | I                                                         | BF, CL    | Output-stage bias-current setting pin                                                                    |  |

| V <sub>S+</sub>                 | 1         | Р                                                         | BF, CL    | Positive power supply connection for the input stage                                                     |  |

| V <sub>S-</sub>                 | 5, 8      | Р                                                         | BF, CL    | Negative power supply connection for the input stage; pin 5 and pin 8 are internally shorted             |  |

| V <sub>SO+</sub> <sup>(4)</sup> | 12        | Р                                                         | BF, CL    | Positive power supply connection for the output stage                                                    |  |

| V <sub>SO-</sub> <sup>(4)</sup> | 10        | Р                                                         | BF, CL    | Negative power supply connection for the output stag                                                     |  |

| Thermal Pad                     |           | _                                                         | _         | The thermal pad is electrically isolated from the die and pins; connect the thermal pad to any potential |  |

Table 4-1. Pin Functions

(1) I = input, O= output, P= power, NC = no connect.

(2) See Section 7.4 for more information on *Buffer Mode (BF)* and *Composite Loop Mode (CL)* functional modes.

(3) Use pins specified as CL only when operating in Composite Loop Mode, and float these pins when operating in Buffer Mode.

(4) Tie V<sub>SO</sub> and V<sub>S</sub> to the same potential because these pins are internally connected to the other through back-to-back diodes.

# **5** Specifications

#### 5.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                                     | MIN                      | MAX                | UNIT |

|------------------|---------------------------------------------------------------------|--------------------------|--------------------|------|

| Vs               | Input stage supply voltage, $V_S = (V_{S+}) - (V_{S-})^{(2)}$       |                          | 14                 | V    |

| V <sub>SO</sub>  | Output stage supply voltage, $V_{SO} = (V_{SO+}) - (V_{SO-})^{(2)}$ |                          | 14                 | V    |

| IN               | Input voltage                                                       | (V <sub>S-</sub> ) – 0.5 | (V <sub>S+</sub> ) | V    |

| CLH              | Positive clamp voltage                                              | Mid-supply               | V <sub>S+</sub>    | V    |

| CLL              | Negative clamp voltage                                              | V <sub>S-</sub>          | Mid-supply         | V    |

|                  | Input clamp diode                                                   |                          | 100                | mA   |

| TJ               | Junction temperature                                                |                          | 150                | °C   |

| T <sub>stg</sub> | Storage temperature                                                 | -65                      | 150                | °C   |

(1) Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

(2) Tie  $V_{SO}$  and  $V_S$  to the same potential.  $V_{SO}$  and  $V_S$  are internally connected together through back-to-back diodes.

# 5.2 ESD Ratings

|                    |                        |                                                                       | VALUE | UNIT |

|--------------------|------------------------|-----------------------------------------------------------------------|-------|------|

| V                  |                        | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±1000 | V    |

| V <sub>(ESD)</sub> | Liechostatic discharge | Charged device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### **5.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                   |                       | MIN  | NOM | MAX  | UNIT |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------|------|-----|------|------|

| $\sum_{i=1}^{n} \sum_{j=1}^{n} \frac{1}{2} \sum_{i=1}^{n} \frac{1}{2} \sum_{j=1}^{n} \frac{1}{2} \sum_{i=1}^{n} $ |                                                   | Dual-supply voltage   | ±4.5 | ±5  | ±6.5 | V    |

| Vs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Supply voltage, $V_S = (V_{S+}) - (V_{S-})^{(1)}$ | Single-supply voltage | 9    | 10  | 13   | v    |

| T <sub>A</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ambient temperature                               |                       | -40  | 25  | 85   | °C   |

(1) The BUF802 can be used with any possible combination of  $V_{S+}$  and  $V_{S-}$ , but do not exceed the *Recommended Operating Conditions*.

#### **5.4 Thermal Information**

|                       |                                              | BUF802     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGT (VQFN) | UNIT |

|                       |                                              | 16 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 53         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 61         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 27         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 2.7        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 27         | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 13         | °C/W |

(1) For information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 5.5 Electrical Characteristics Wide Bandwidth Mode

at T<sub>A</sub> = 25°C, V<sub>S</sub> = ±6 V, R<sub>L</sub> = 100  $\Omega$  || 400 fF, R<sub>S</sub> = 25  $\Omega$ , V<sub>OCM</sub> = 0 V (mid-supply), CLH and CLL tied to V<sub>S+</sub> and V<sub>S-</sub> respectively, R\_Bias = 17.8 k $\Omega$ , and wide bandwidth mode (unless otherwise noted)

| PARAMETER            |                                      | TEST CONDITIONS                                                         |                                         | MIN  | TYP     | MAX   | UNIT   |  |

|----------------------|--------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|------|---------|-------|--------|--|

| AC PERFC             | DRMANCE                              |                                                                         |                                         |      |         |       |        |  |

| SSBW                 | Small-signal bandwidth               | V <sub>OUT</sub> = 100 mV <sub>PP</sub>                                 | V <sub>OUT</sub> = 100 mV <sub>PP</sub> |      | 3.1     |       | GHz    |  |

|                      |                                      | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                    |                                         |      | 3.1     |       |        |  |

| LSBW                 | Large-signal bandwidth               | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                    |                                         |      | 1.6     |       | GHz    |  |

|                      | Bandwidth for 0.1-dB flatness        | V <sub>OUT</sub> = 1 V <sub>PP.</sub> R <sub>L</sub> = 100 Ω            | 2                                       |      | 0.6     |       | GHz    |  |

|                      | Bandwidth for -1-dB flatness         | V <sub>OUT</sub> = 1 V <sub>PP</sub> , R <sub>L</sub> = 100 Ω           | 2                                       |      | 1.8     |       | GHz    |  |

|                      | Bandwidth for -2-dB flatness         | $V_{OUT}$ = 1 $V_{PP}$ , $R_{L}$ = 50 Ω                                 |                                         |      | 2.4     |       | GHz    |  |

| SR                   | Slew rate                            | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sle                      | ew rate = 13000 V/µs                    |      | 7000    |       | V/µs   |  |

|                      | V <sub>OUT</sub> = 1.2-V step (10% t | to 90%)                                                                 |                                         | 0.16 |         |       |        |  |

|                      | Rise and fall time                   | V <sub>OUT</sub> = 0.25-V step (10%                                     | to 90%)                                 |      | 0.15    |       | ns     |  |

|                      | Settling time to 0.1%                | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sle                      | ew rate = 13000 V/µs                    |      | 1.3     |       | ns     |  |

|                      | Settling time to 1%                  | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sle                      | ew rate = 13000 V/µs                    |      | 0.7     |       | ns     |  |

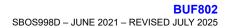

|                      |                                      | 1/f corner                                                              |                                         |      | 18      |       | kHz    |  |

| e <sub>n</sub>       | Voltage noise                        | f = 100 MHz in BF mode and CL mode                                      |                                         |      | 2.3     |       | nV/√Hz |  |

| i <sub>n</sub>       | Current noise                        | f = 10 kHz                                                              |                                         |      | 1.5     |       | fA/√Hz |  |

|                      | Harmonic distortion                  | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                    | f = 500 MHz                             |      | -68/-58 |       |        |  |

|                      |                                      | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                    | f = 1 GHz                               |      | -55/-59 |       | dBc    |  |

| HD2/HD3              |                                      |                                                                         | f = 2 GHz                               |      | -45/-49 |       |        |  |

|                      |                                      |                                                                         | f = 2 GHz, $R_L$ = 50 $\Omega$          |      | -43/-41 |       |        |  |

| DC PERFC             | ORMANCE                              |                                                                         |                                         |      |         |       |        |  |

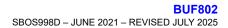

| V                    | Input offect veltage                 | V <sub>OUT</sub> – V <sub>IN</sub>                                      |                                         |      | -600    | -800  | mV     |  |

| V <sub>OS</sub>      | Input offset voltage                 | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                  |                                         |      |         | -900  | mv     |  |

| dV <sub>OS</sub> /dT | Input offset voltage drift           | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                           |                                         |      | ±700    | ±1330 | µV/°C  |  |

|                      | Innut higg ourrant                   |                                                                         |                                         | 3    |         | 25    | ~^     |  |

| IB                   | Input bias current                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                           |                                         |      | 220     | рА    |        |  |

| 1                    | Auxiliary input bias current         |                                                                         |                                         |      | 44      | 140   |        |  |

| I <sub>AB</sub>      | Auxiliary input bias current         | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                           |                                         |      |         | 200   | μA     |  |

|                      |                                      |                                                                         | R <sub>L</sub> = 200 Ω                  | 0.97 | 0.978   | 0.99  | - V/V  |  |

|                      |                                      | V <sub>OUT</sub> = ± 0.5 V                                              | R <sub>L</sub> = 100 Ω                  | 0.96 | 0.971   | 0.98  |        |  |

| C                    | DC agin                              |                                                                         | R <sub>L</sub> = 50 Ω                   | 0.95 | 0.961   | 0.97  |        |  |

| G                    | DC gain                              |                                                                         | R <sub>L</sub> = 200 Ω                  | 0.97 |         | 0.99  |        |  |

|                      |                                      | $V_{OUT} = \pm 0.5 V,$<br>$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | R <sub>L</sub> = 100 Ω                  | 0.96 |         | 0.98  |        |  |

|                      |                                      |                                                                         | R <sub>L</sub> = 50 Ω                   | 0.94 |         | 0.97  |        |  |

# 5.5 Electrical Characteristics Wide Bandwidth Mode (continued)

at T<sub>A</sub> = 25°C, V<sub>S</sub> = ±6 V, R<sub>L</sub> = 100  $\Omega$  || 400 fF, R<sub>S</sub> = 25  $\Omega$ , V<sub>OCM</sub> = 0 V (mid-supply), CLH and CLL tied to V<sub>S+</sub> and V<sub>S-</sub> respectively, R\_Bias = 17.8 k $\Omega$ , and wide bandwidth mode (unless otherwise noted)

| PARAMETER           |                                        | TEST CONDITIONS                                                          |                                               | MIN                   | TYP                 | MAX                       | UNIT            |

|---------------------|----------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|-----------------------|---------------------|---------------------------|-----------------|

| INPUT               |                                        |                                                                          |                                               |                       |                     |                           |                 |

| Z <sub>IN</sub>     | Input impedance                        | f = 100 MHz                                                              |                                               | 50    2.4             |                     |                           | GΩ∥pF           |

|                     | Input clamp current rating             | Continuous current rating                                                |                                               |                       | 100                 |                           | mA              |

| V <sub>CLH</sub>    | High side clamp voltage <sup>(1)</sup> |                                                                          |                                               | 0                     |                     | V <sub>S+</sub>           | V               |

| V <sub>CLL</sub>    | Low side clamp voltage <sup>(1)</sup>  |                                                                          |                                               |                       |                     | 0                         | V               |

|                     | CLH clamping time                      | Time taken to clamp V <sub>OUT</sub> to                                  | V <sub>CLH</sub> during overdrive             |                       | 0.2                 |                           |                 |

|                     | CLL clamping time                      | Time taken to clamp V <sub>OUT</sub> to                                  | V <sub>CLL</sub> during overdrive             |                       | 0.2                 |                           | ns              |

|                     |                                        |                                                                          | f = 500 MHz                                   |                       | 4.5                 |                           |                 |

|                     | Input voltage                          | THD = -40 dBc                                                            | f = 1 GHz                                     |                       | 2.1                 |                           | V <sub>PP</sub> |

|                     |                                        |                                                                          | f = 2 GHz                                     |                       | 1.2                 |                           |                 |

| OUTPUT              |                                        | 1                                                                        |                                               |                       |                     |                           |                 |

|                     |                                        | T <sub>A</sub> = 25°C                                                    |                                               | V <sub>S+</sub> – 1.9 |                     | V <sub>S</sub> - +<br>3.4 |                 |

| Output swing        |                                        | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                   |                                               | V <sub>S+</sub> - 2.0 |                     | V <sub>S</sub> -+<br>3.4  | V               |

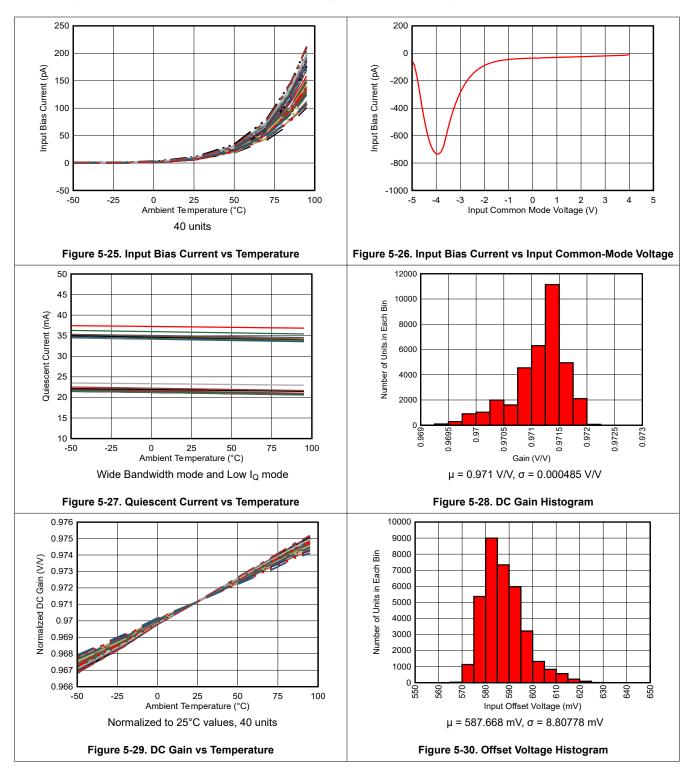

| Zo                  | Output impedance                       | f = 100 MHz                                                              |                                               |                       | 1.2                 |                           | Ω               |

| AUXILIAR            |                                        |                                                                          |                                               |                       |                     |                           |                 |

| 0                   |                                        | At low frequency (V <sub>IN</sub> is left floating)                      |                                               | 6.15                  |                     | 20                        | V/V             |

| G <sub>AUX</sub>    | V <sub>OUT</sub> / In_Aux gain         | At crossover frequency (V <sub>IN</sub> shorted to GND)                  |                                               | 0.18                  | 0.26                |                           |                 |

|                     | Default voltage at In_Aux              | Driving In_Aux to default vo<br>results in V <sub>OUT</sub> = mid-supply |                                               | V <sub>S-</sub> +2.3  | V <sub>S-</sub> + 3 | V <sub>S-</sub> + 3.8     | V               |

|                     | In_Aux input voltage                   | At crossover frequency                                                   |                                               | V <sub>S-</sub> +1.0  |                     | V <sub>S-</sub> + 5.0     | V               |

| G <sub>AUX</sub> BW | V <sub>OUT</sub> / In_Aux bandwidth    |                                                                          |                                               |                       | 800                 |                           | MHz             |

|                     | RHF                                    | Resistance between In_Bias to JFET source                                |                                               |                       | 100                 |                           | kΩ              |

| POWER S             | UPPLY                                  |                                                                          |                                               |                       |                     |                           |                 |

|                     |                                        |                                                                          |                                               |                       | 34                  | 37                        |                 |

| l <sub>Q</sub>      | Quiescent current                      | I <sub>OUT</sub> = 0 mA<br>(R_bias = 17.8 kΩ)                            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                       | 35.5                |                           | mA              |

|                     |                                        |                                                                          | CL Mode enabled                               |                       | 36                  | 40                        |                 |

| PSRR                | Dower ounply rejection refin           | PSRR at 100 kHz on V <sub>S+</sub>                                       |                                               |                       | 49                  |                           | dB              |

| FORK                | Power-supply rejection ratio           | PSRR at 100 kHz on V <sub>S-</sub>                                       |                                               |                       | 38                  |                           | uв              |

(1) The 0-V limits are for bipolar and balanced power supplies. For other supply configurations mid-supply sets the minimum limit for V<sub>CLH</sub> and maximum limit for V<sub>CLL</sub>.

#### 5.6 Electrical Characteristics Low Quiescent Current Mode

at T<sub>A</sub> = 25°C, V<sub>S</sub> = ±6 V, R<sub>L</sub> = 100  $\Omega$  || 400 fF, R<sub>S</sub> = 25  $\Omega$ , V<sub>OCM</sub> = 0 V (mid-supply), CLH and CLL tied to V<sub>S+</sub> and V<sub>S-</sub> respectively, R\_Bias = 35.7 k $\Omega$ , and low quiescent current mode (unless otherwise specified)

| PARAMETER      |                               | TEST CONDITION                                                                |                                               | MIN     | TYP     | MAX  | UNIT   |

|----------------|-------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|---------|---------|------|--------|

| AC PERF        | ORMANCE                       |                                                                               | I.                                            |         |         |      |        |

| SSBW           | Small-signal bandwidth        | V <sub>OUT</sub> = 100 mV <sub>PP</sub>                                       | V <sub>OUT</sub> = 100 mV <sub>PP</sub>       |         | 2.6     |      | GHz    |

|                |                               | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                          |                                               |         | 2       |      |        |

| LSBW           | Large-signal bandwidth        | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                          |                                               |         | 0.7     |      | GHz    |

|                | Bandwidth for 0.1 dB flatness | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                          |                                               |         | 0.45    |      | GHz    |

|                | Bandwidth for –1 dB flatness  | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                          |                                               |         | 1.4     |      | GHz    |

| SR             | Slew rate                     | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sl                             | ew rate = 13000 V/µs                          |         | 5500    |      | V/µs   |

|                | Rise and fall time            | V <sub>OUT</sub> = 1.2-V step (10%                                            | to 90%)                                       |         | 0.3     |      |        |

|                |                               | V <sub>OUT</sub> = 0.25-V step (10%                                           | 5 to 90%)                                     |         | 0.16    |      | ns     |

|                | Settling time to 0.1%         | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sl                             | ew rate = 13000 V/µs                          |         | 1.4     |      |        |

|                | Settling time to 1%           | V <sub>OUT</sub> = 1.2-V step, V <sub>IN</sub> sl                             | ew rate = 13000 V/µs                          |         | 0.8     |      | ns     |

| _              |                               | . 1/f corner                                                                  |                                               | 10      |         |      | kHz    |

| e <sub>n</sub> | Voltage noise                 | f = 100 MHz 2.2                                                               |                                               |         | nV/√Hz  |      |        |

| i <sub>n</sub> | Current noise                 | f = 10 kHz                                                                    |                                               |         | 1.5     |      | fA/√Hz |

|                |                               | V <sub>OUT</sub> = 2 V <sub>PP</sub>                                          | f = 500 MHz                                   | -35/-32 |         |      |        |

| HD2/HD3        | Harmonic distortion           |                                                                               | f = 100 MHz                                   |         | -80/-77 |      | dBc    |

|                |                               | V <sub>OUT</sub> = 1 V <sub>PP</sub>                                          | f = 500 MHz                                   | -56/-54 |         |      |        |

| DC PERFO       | ORMANCE                       |                                                                               |                                               |         |         |      |        |

|                |                               | V <sub>OUT</sub> = ±0.5 V                                                     | R <sub>L</sub> = 200 Ω                        | 0.96    | 0.975   | 0.99 |        |

| 0              | DO main                       |                                                                               | R <sub>L</sub> = 100 Ω                        | 0.95    | 0.963   | 0.98 |        |

| G              | DC gain                       | V <sub>OUT</sub> = ±0.5 V,                                                    | R <sub>L</sub> = 200 Ω                        | 0.96    |         | 0.99 | V/V    |

|                |                               | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                 | R <sub>L</sub> = 100 Ω                        | 0.95    |         | 0.98 |        |

| INPUT          |                               |                                                                               |                                               |         |         |      |        |

|                | CLH clamping time             | Time taken to clamp V <sub>OU</sub>                                           | T to V <sub>CLH</sub> during overdrive        |         | 0.3     |      |        |

|                | CLL clamping time             | Time taken to clamp V <sub>OUT</sub> to V <sub>CLL</sub> during overdrive 0.7 |                                               |         | ns      |      |        |

| OUTPUT         | 1                             | 1                                                                             |                                               |         |         |      | 1      |

| Z <sub>O</sub> | Output impedance              | f = 100 MHz                                                                   |                                               |         | 1.2     |      | Ω      |

| POWER S        | UPPLY                         | 1                                                                             |                                               |         |         |      |        |

|                | Oniversity of the             | I <sub>OUT</sub> = 0 mA                                                       |                                               |         | 21      | 24   |        |

| l <sub>Q</sub> | Quiescent current             | (R_bias = 35.7 kΩ)                                                            | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |         | 22      |      | mA     |

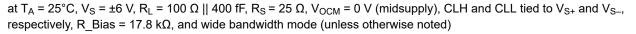

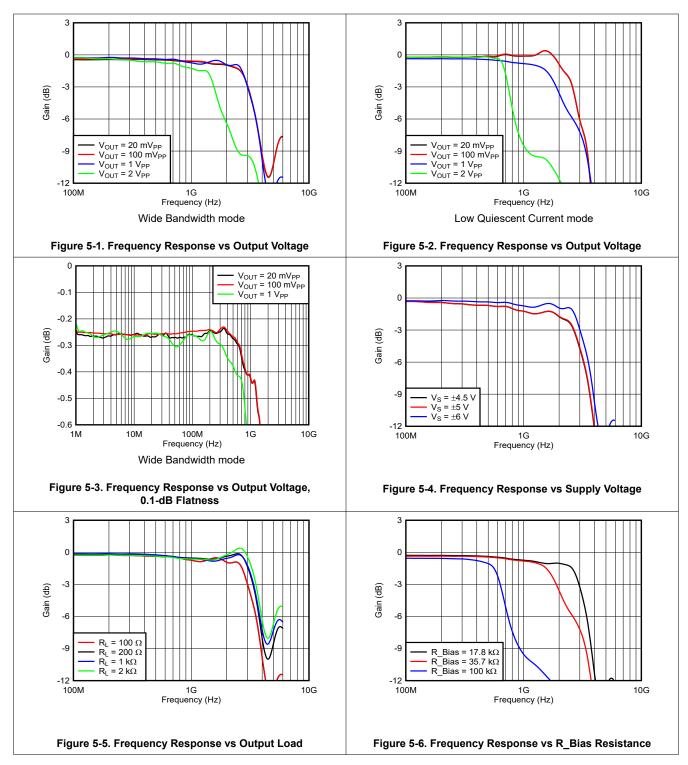

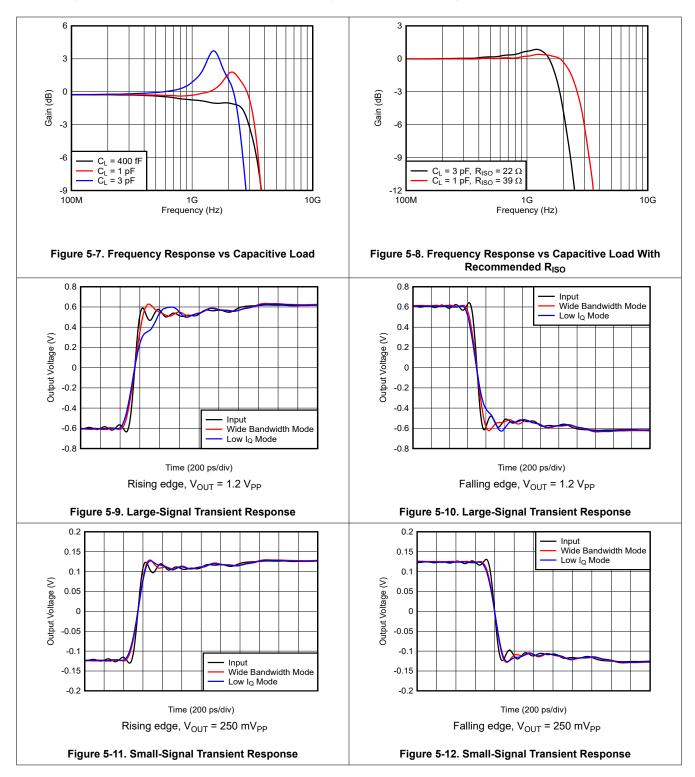

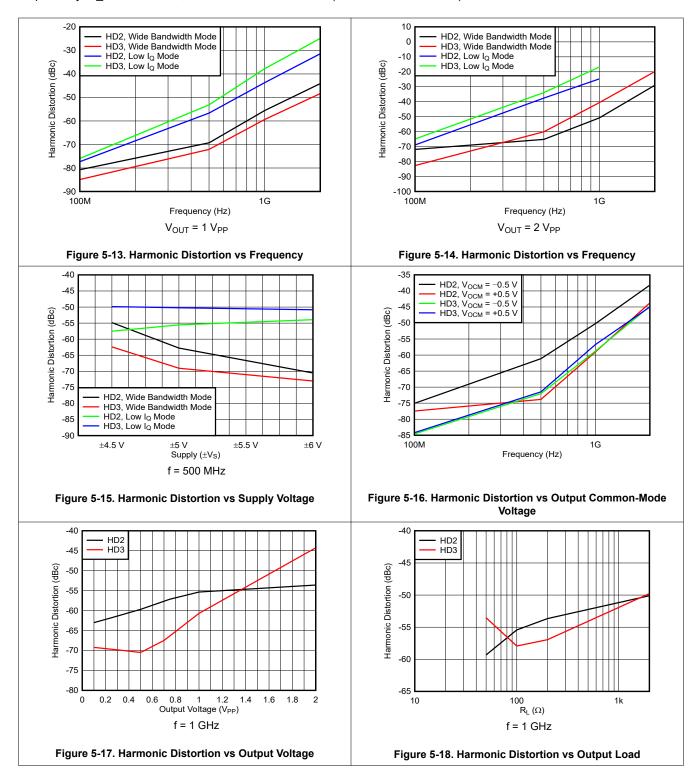

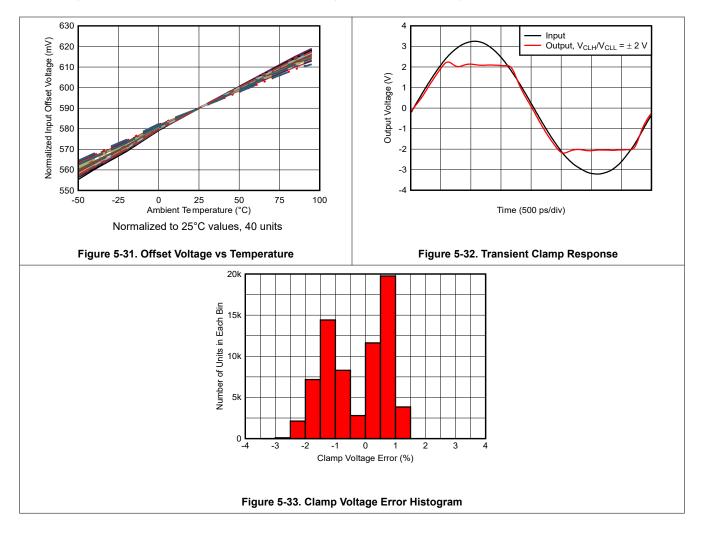

#### **5.7 Typical Characteristics**

# **6** Parameter Measurement Information

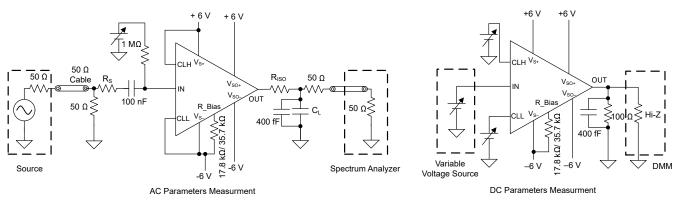

Figure 6-1 through Figure 6-3 show the various test setup configurations for the BUF802.

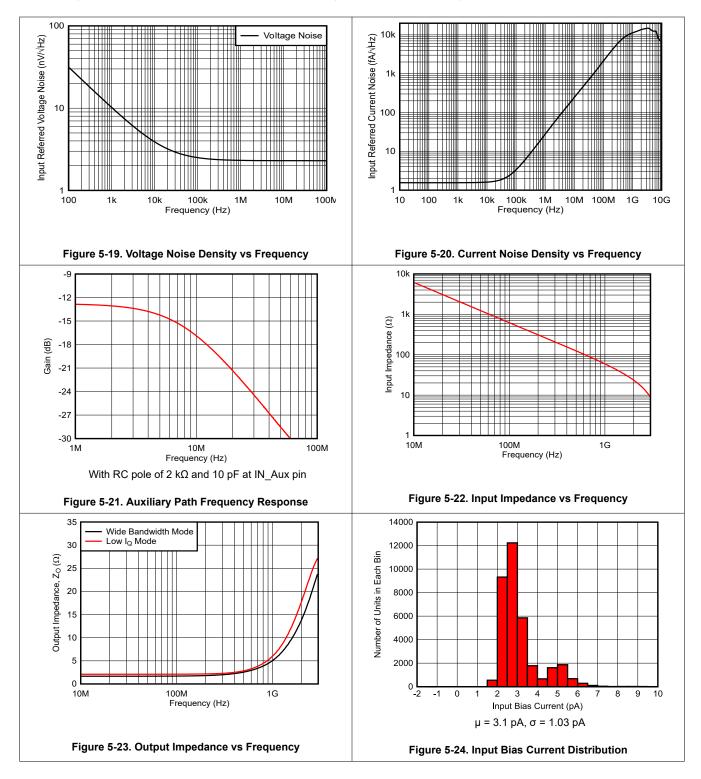

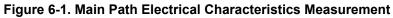

Figure 6-2 shows the two inputs for BUF802 (IN and In\_Aux) which control the output. The IN pin controls the output of BUF802 through the Main Path, whereas the In\_Aux pin controls the output through the Auxiliary Path. Either the Main Path or the Auxiliary Path, can be used to steer the output. The electrical characteristics of the Main Path and the Auxiliary Path is specified in Section 5.7.

# 7 Detailed Description

#### 7.1 Overview

The BUF802 device is a high input-impedance, open-loop buffer used in signal acquisition front-end applications. The BUF802 is used as a standalone buffer in *Buffer Mode (BF Mode)*, or in a composite loop with a precision amplifier in *Composite Loop Mode (CL Mode)* to achieve dc precision and a wide, large-signal bandwidth. The low output impedance and high output current drive strength enables the BUF802 to drive loads as large as 50  $\Omega$ . The BUF802 comes with adjustable quiescent current to customize system level power and performance trade-offs.

#### 7.2 Functional Block Diagram

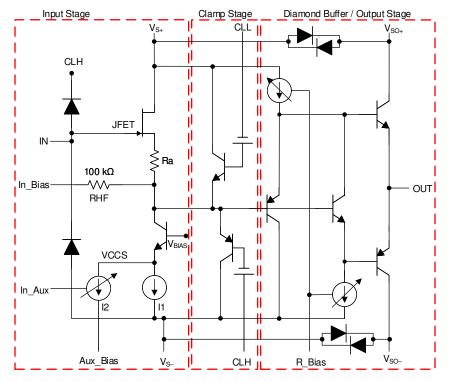

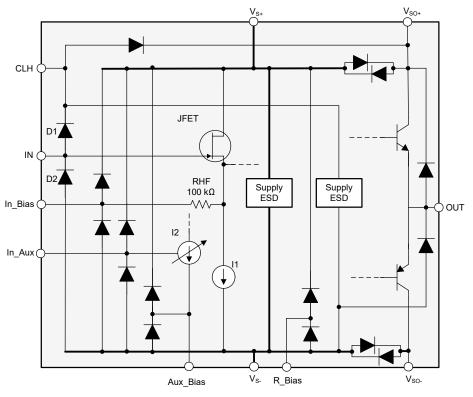

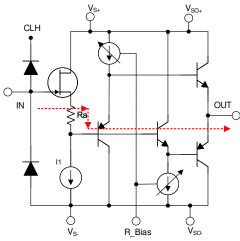

The functional block diagram shows an overview of the internal structure of the BUF802. The internal schematic of the BUF802 is divided into the following three parts:

- **Input Stage**: consists of a low-noise JFET with biasing circuitry. The input stage is configurable in two modes: *BF Mode* and *CL Mode*. Choosing one of the two modes affects the circuit operation of the input stage. The clamp and output stage operation are unaffected by the mode selection. Section 7.4 describes the two modes in greater detail.

- **Clamp Stage**: provides the following functions:

- 1. Protects the input of the BUF802 against large input signal transients through diode clamps to  $V_{S-}$  and CLH respectively.

- 2. Prevents the output voltage of the BUF802 from exceeding the voltage at the CLH and CLL.

- **Output Stage**: tracks the JFET source voltage and is optimized to drive 50-Ω and 100-Ω loads while maintaining signal fidelity.

# 7.3 Feature Description

7.3.1 Input and Output Overvoltage Clamp

#### Figure 7-1. Internal Input and Output Overvoltage Clamp

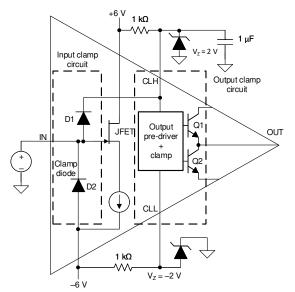

The BUF802 device integrates an input and output clamp circuit. The input clamp protects the BUF802 from large input transients and the output clamp protects the subsequent stages from being overdriven.

#### Input Clamp Circuit:

- Figure 7-1 shows the input of the BUF802 tied to pins CLH and V<sub>S-</sub> through two internal clamp diodes, D1 and D2. The diodes are rated for 100 mA of continuous current but withstand much higher transient currents. If the JFET input voltage exceeds the voltage at CLH or V<sub>S-</sub>, the diodes get forward biased, clamping the JFET to CLH and V<sub>S-</sub>. A 1-μF capacitor connected in parallel to the zener diode helps in transient absorption traveling through the D1 diode.

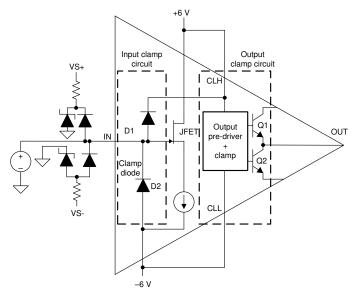

- Figure 7-2 shows how the external clamping diodes is used in cases where the 100-mA current rating of D1 and D2 is insufficient. When using external clamping, disable the internal protection of the BUF802 by connecting CLH and CLL to  $V_{S+}$  and  $V_{S-}$ .

Figure 7-2. External Input Clamp Circuit

#### Output Clamp Circuit:

- The output protection circuit prevents the stages following the BUF802 from being overdriven. This circuit also helps the BUF802 recover rapidly from a saturated state resulting from an input- or output-overdrive condition. In a typical data-acquisition system, the BUF802 is followed by a variable gain amplifier (VGA). High-speed VGAs are typically designed on 5-V processes, making the device susceptible to potential damage from the 12-V BUF802. The voltage applied to the CLH and CLL pins dictate the maximum output swing of the BUF802.

- Figure 7-2 shows that the internal clamps are disabled by connecting CLH and CLL to  $V_{S+}$  and  $V_{S-}$ , respectively. When the clamps are disabled, the maximum output swing is limited by the output swing specification described in Section 5.5. Section 5.7 shows the response time and accuracy of the output clamp.

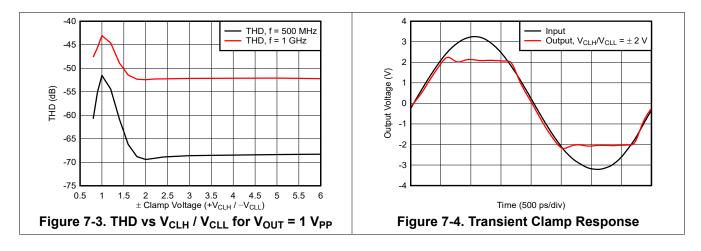

- The output THD of the BUF802 degrades when V<sub>CLH</sub> and V<sub>CLL</sub> are set close to the expected V<sub>OUT</sub> peak value. To prevent signal degradation, maintain at least a 1.5-V difference between the expected peak output voltage and the clamp voltage applied at the CLH and CLL pins. Figure 7-3 shows the relation between the absolute clamp voltage value and THD for a 1 V<sub>PP</sub> output.

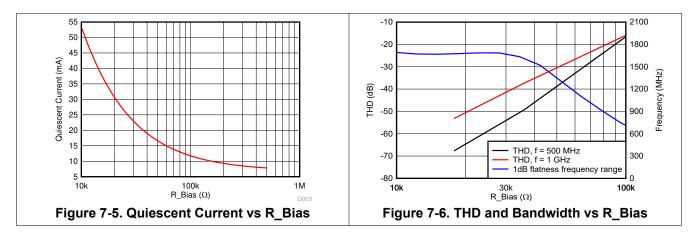

#### 7.3.2 Adjustable Quiescent Current

The BUF802 includes an adjustable quiescent current feature to allow the system designer to trade off the current consumed versus the distortion performance obtained. Section 7.2 shows to connect a resistor between R\_Bias and  $V_{S_{-}}$  to set the bias point operating current of the output stages. Figure 7-5 shows the quiescent current variation as a function of R\_Bias value.

Figure 7-6 shows that changing the resistor between R\_Bias and  $V_{S_{-}}$  primarily affects the THD of the output signal. Section 5.5 and Section 5.6 specify the ac and dc parameters of the BUF802 at two different R\_Bias values. The dc parameters are independent of the quiescent current setting.

#### 7.3.3 ESD Structure

Figure 7-7 shows the internal ESD structure of the BUF802.  $V_{SO}$  and  $V_S$  supply pins are internally shorted to each other through back-to-back diodes. See also Section 8.3. The input ESD diodes D1 and D2 are optimized to carry 100 mA of continuous current while the remaining ESD diodes are rated for 10 mA.

### 7.4 Device Functional Modes

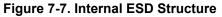

Figure 7-8. Main Path and Auxiliary Path

The BUF802 is designed to operate in two modes: *Buffer Mode (BF Mode)* and *Composite Loop Mode (CL Mode)*.

In *BF Mode*, the BUF802 uses the JFET, output driver and bipolar transistors in the Main Path to reproduce the signal, applied on IN, at the output of the BUF802. Figure 7-8 shows the Main Path and the Auxiliary Path of the BUF802. The BUF802 operates from dc to high-frequency, and is therefore usable as a standalone buffer. When used in *BF Mode*, only the Main Path of the BUF802 is used.

In *CL Mode*, the BUF802 uses the Auxiliary signal path and the Main Path to control the output voltage. As the name suggests in the *Composite Loop Mode*, the BUF802 is used in a composite loop with a precision amplifier to achieve dc precision and a wide, large-signal bandwidth simultaneously. The composite loop splits the applied signal to low-frequency and high-frequency components and passes the signal over to different circuits with an appropriate transfer function. The low-frequency and high-frequency signal components then recombine inside the BUF802 and are reproduced at the OUT pin.

#### 7.4.1 Buffer Mode (BF Mode)

Figure 7-9. Internal Schematic – BF Mode

The wide large-signal bandwidth and fast slew rate of the BUF802 coupled with Hi-Z input are useful in a variety of high-frequency signal chain applications. Figure 7-9 shows that the BUF802 uses the Main Path and operates the JFET and transistors as source follower and emitter followers to reproduce signal applied on IN, at the output of BUF802. The pins associated with only *CL Mode* (Pin No. 6, 4, and 3) are left floating while operating in *BF Mode*.

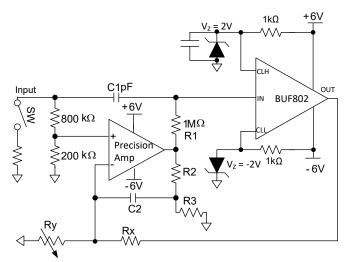

Figure 7-10. Composite Loop Using *BF Mode*

Figure 7-10 shows how the BUF802 is also used in a composite loop while being operated in *BF Mode*. The operation of BUF802 in Figure 7-10 is still called *BF Mode* because the signal is being transferred through the Main Path only. The Auxiliary path and the pins associated with the Auxiliary path and *CL Mode* are kept disabled. The low-frequency and high-frequency signal components are combined externally through the discrete components R1 and C1 before being applied at the IN pin.

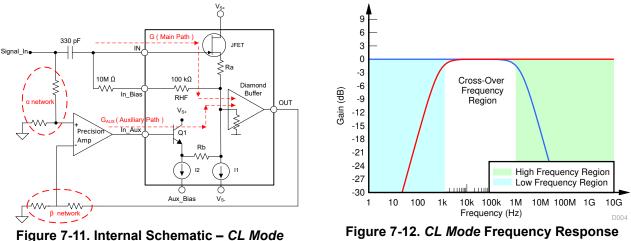

#### 7.4.2 Composite Loop Mode (CL Mode)

Figure 7-12. CL Mode Frequency Response

The 330-pF input series capacitor shown in Figure 7-11 splits the- input signal into low-frequency and highfrequency components. These signals are applied to In Aux and IN, respectively. The IN pin controls the output of BUF802 through the Main Path, whereas the In Aux pin controls the output through the Auxiliary Path.

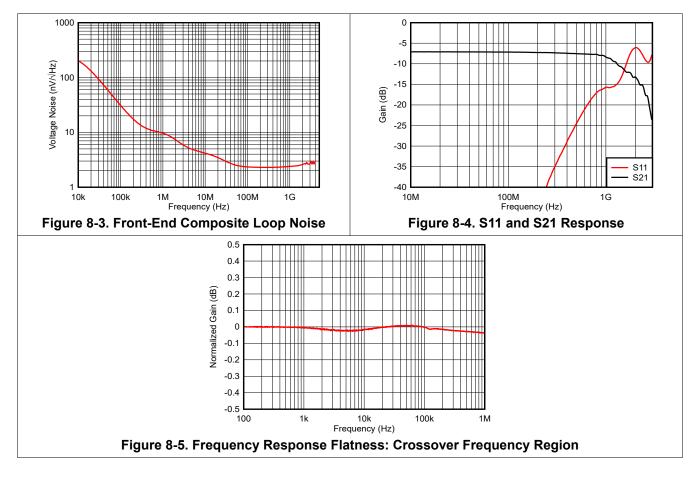

The transfer function of the composite loop in *CL Mode* can be split into the following 3 frequency regions:

- 1. Low Frequency Region: The gain of the composite loop in the low-frequency region is  $\alpha/\beta$  (determined by  $\alpha$  and  $\beta$  network). In the low-frequency region the 330 pF input capacitor presents a high-impedance in the Main Path, causing the signal to flow through the precision amplifier and the In Aux pin. This region spans from DC to  $f_{LF}$ .  $f_{LF}$  is the pole resulting from the gain bandwidth of the precision amplifier, the Auxiliary Path bandwidth, and parasitic capacitance of the components along the path.

- 2. High Frequency Region: In the high-frequency region, the precision amplifier and the Auxiliary Path run out of bandwidth. The net gain of the composite loop in this region is determined solely by the Main Path gain of the BUF802, which is denoted by G. This region spans from the pole created at f<sub>HF</sub> till the LSBW of the BUF802. The f<sub>HF</sub> is the pole resulting from the 330 pF series capacitor and the 10 M $\Omega$  resistor on the In Bias pin.

- 3. Crossover Frequency Region: the Main Path and Auxiliary Path work in conjunction to determine the gain in the crossover region. To maintain a flat frequency response in this region, the following conditions have to be met:

- a.  $\alpha/\beta = G$

- b. High frequency response pole  $f_{HF}$  << Low frequency pole  $f_{IF}$

A detailed analysis of discrete component selection to achieve a flat frequency response is discussed further in Section 8.1.

# **8** Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

#### 8.1 Application Information

The BUF802 offers a wide large-signal bandwidth, high-slew rate along with high-input impedance making this device an excellent choice for data acquisition systems. In applications where dc precision is not needed, or in cases where the input is ac coupled, the BUF802 is usable as a standalone input buffer in *BF Mode*. In case the precision required is greater than that offered by the BUF802, operate the BUF802 in *CL Mode* with a precision amplifier in a composite loop.

#### 8.2 Typical Applications

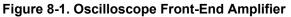

#### 8.2.1 Oscilloscope Front-End Amplifier Design

#### 8.2.1.1 Design Requirements

The following table shows the target specification for a 1-GHz oscilloscope front-end and precision amplifier.

| SPECIFICATION                                    | VALUE                       |  |  |

|--------------------------------------------------|-----------------------------|--|--|

| Input impedance                                  | 1 ΜΩ / 50 Ω                 |  |  |

| S parameters (f = 1 GHz)                         | S11 = -15 dB, S21 = -1.5 dB |  |  |

| Offset drift                                     | 1 μV/°C, maximum            |  |  |

| Noise at highest resolution (50- $\Omega$ input) | 80 μV <sub>RMS</sub>        |  |  |

#### 8.2.1.2 Detailed Design Procedure

- **Input Impedance**: The JFET-input stage of the BUF802 offers gigohms of input impedance, and therefore, enables the front-end to be terminated with a 1-M $\Omega$  resistor without affecting performance. A 50- $\Omega$  resistance can also be switched in offering matched termination for high-frequency signals. The BUF802 enables the designer to use both 1-M $\Omega$  and 50- $\Omega$  termination in the same signal chain.

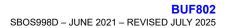

- **Noise**: The total noise of the front-end amplifier is the function of the voltage and current noise of the BUF802, OPA140, and the resistors thermal noise. The dominant noise source, however, is contributed by the voltage noise of the BUF802 as a result of the noise presence across the complete bandwidth. Thus, the total RMS noise of the front-end amplifier is approximately equal to the voltage noise of BUF802 over 1 GHz.

The specified input-referred voltage noise of the BUF802 (see Section 5.5) is 2.3 nV/ $\sqrt{Hz}$ . The total input referred RMS noise in a bandwidth of 1 GHz is given by the following equation:

$En_{RMS} = 2.3 \text{ nV}/\sqrt{Hz} \times \sqrt{(1 \text{ GHz} \times 1.22)} = 80 \mu V_{RMS}.$

(1)

(2)

(3)

1.22 = Brickwall correction factor. See TI Precision Labs – Op Amps: Noise – Spectral Density for detailed calculations.

Figure 8-3 shows the total input-referred spot noise as a function of frequency. Assuming the oscilloscope has eight divisions on the screen and a highest resolution of 1 mV, the full-scale reading is 8 mV<sub>PP</sub> or 2.82 mV<sub>RMS</sub>. Thus, the SNR of the front-end amplifier stage at the highest-resolution setting is:

$20 \times \log (2.82 \text{ mV}_{\text{RMS}} / 80 \mu \text{V}_{\text{RMS}}) = 31 \text{ dB}.$

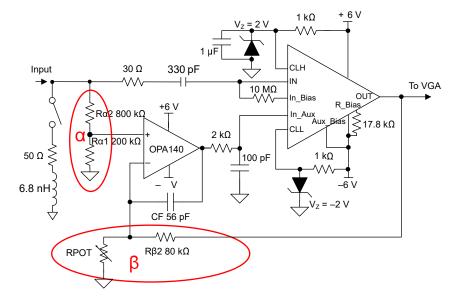

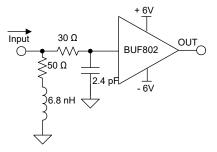

**S11 Optimization**: The front-end amplifier circuit requires a exact 50- $\Omega$  termination to achieve the required S11 parameter of –15 dB across the frequency. Although mounting an exact 50- $\Omega$  resistance at the input of the front-end composite loop circuit is possible, the parasitic capacitance of the BUF802 appears in parallel to this 50- $\Omega$  resistance, resulting in a net-imperfect termination.

The parasitic input capacitance of BUF802 (IN pin) is 2.4 pF. At 1 GHz, this parasitic capacitance reduces to an impedance of 66.3  $\Omega$ . Thus, the net input impedance as seen by the signal at the input is as follows:

66.3  $\Omega \parallel$  50  $\Omega$  = 28.5  $\Omega$

This result is an imperfect termination for the  $50-\Omega$  source, resulting in a poor S11. The addition of a  $30-\Omega$  resistance in series with the input trace, and a 6.8-nH inductor in series with the onboard  $50-\Omega$  termination help isolate the input parasitic capacitance. This configuration also helps maintain the net input impedance at  $50 \Omega$ . Figure 8-4 shows the S11 response of this modified circuit.

Figure 8-2. Net Input Impedance

(5)

• Uniform Gain Across Frequency: The front-end amplifier circuit is designed with BUF802 and OPA140 connected in a composite loop. The loop splits the input signal into low- and high-frequency components, taking both components to the output through two different circuits (transfer functions) and recombining them to reproduce a net output signal. The end goal is to achieve a smooth transition between the two circuits and maintain a flat frequency response from dc until the frequency of interest.

*CL Mode* of the BUF802 simplifies this design for achieving a flat frequency response from dc until the frequency of interest (1 GHz in this case). To achieve a flat response, meet the following two conditions:

1. High-frequency response pole  $f_{HF}$  << low frequency pole  $f_{LF}$

2.  $\alpha/\beta = G$

where  $\alpha$  is the input attenuation factor,  $\beta$  is the inverse of the noninverting gain of the precision amplifier and G is the dc gain of the main path of the BUF802. G varies from device-to-device; therefore, trim either  $\alpha$  or  $\beta$  to achieve a flat frequency response. In Figure 8-1, trim  $\beta$  using the RPOT.

G is the typical value, (G = 0.971 V/V) from Section 5.5 and  $\alpha$  is 1/5 (200 k $\Omega$  / (200 k $\Omega$  + 800 k $\Omega$ )); therefore, trim RPOT so that  $\beta \approx 1/5$ .

For the  $\beta$  network, use resistors that are an order of magnitude of resistance lower than the resistors used in the  $\alpha$  network. Therefore,  $\beta$  resistor values of 80 k $\Omega$  and  $\approx$  20 k $\Omega$  are chosen.

$f_{HF}$  is the pole resulting from the 330-pF series capacitor and the 10-M $\Omega$  resistor on the In\_Bias pin. Reduction in value of 10-M $\Omega$  helps with the reduction of overdrive recovery time of the composite loop, but increases the  $f_{HF}$  pole frequency.

$$f_{HF} = 1 / (2 \times pi \times R \times C) = 1 / (2 \times 3.14 \times 10 \text{ M}\Omega \times 330 \text{ pF}) = 48 \text{ Hz}$$

(4)

$f_{LF}$  is the pole resulting from the gain bandwidth of the precision amplifier (OPA140), the auxiliary path bandwidth and other parasitic capacitance of the resistor network.

$$f_{LF1}$$

of precision amplifier = GBW ×  $G_{AUX}$  ×  $\beta$  = 440 kHz

where

- GBW is the gain bandwidth product of the precision amplifier (OPA140) = 11 MHz

- $G_{AUX}$  is the gain from In\_Aux to OUT = 0.2 V/V

- $-1/\beta$  is the external noninverting gain set for the precision amplifier = 5 V/V

The common mode input capacitor of the precision amplifier ( $C_{INPA}$ ) forms a pole with the R $\alpha$ 2 resulting in pole frequency of:

$$f_{LF2}$$

of R $\alpha$ 2 and C<sub>INPA</sub> of amplifier = 1 / (2 × pi × R $\alpha$ 2 × C<sub>INPA</sub>) = 28.4 kHz (6)

Since  $f_{LF2} < f_{LF1}$ ,  $f_{LF2}$  is to be considered as the dominant pole for the auxiliary path bandwidth. Based on the above value of  $f_{HF}$  and  $f_{LF2}$ , the required condition of  $f_{HF} << f_{LF2}$  is met.

CF, connected across the precision amplifier, is required to compensate for the parasitic capacitance and to make the overall poles and zeros cancel each other. Use the following equation to find the value of CF:

$$CF = C_{INPA} \times ((G \times R_{\alpha 2} / R_{\beta 2}) - 1)).$$

(7)

where

- C<sub>INPA</sub> is the common-mode input capacitance of the precision amplifier, the OPA140 in this case

- G is the typical value, (G = 0.971 V/V) from Section 5.5

Plugging in the value of these components arrives approximately to CF = 61 pF, rounding off to nearest standard capacitor CF = 56 pF. In the final system, based on the quality of the flat-band response needed, CF is able to be trimmed along with RPOT in the final production flow.

#### 8.2.1.3 Application Curves

# 8.2.2 Transforming a Wide-Bandwidth, 50- $\Omega$ Input Signal Chain to High-Input Impedance

#### 8.2.2.1 Detailed Design Procedure

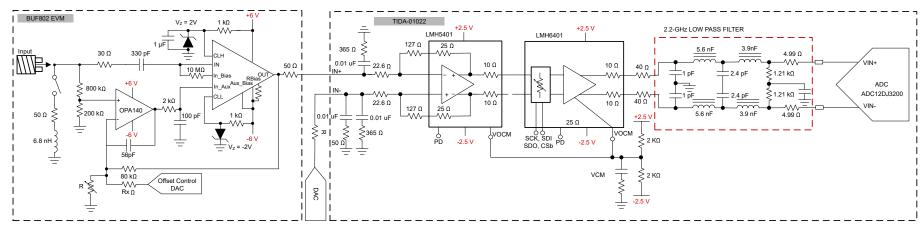

TIDA-01022 reference design primarily focuses on a multichannel high-speed analog front-end, which is typically used in end equipment, such as a digital storage oscilloscope (DSO), wireless communication test equipment (WCTE), and radars. A 50- $\Omega$  input data-acquisition (DAQ) signal chain, such as the TIDA-01022, is convertible into a high-input impedance DAQ system by inserting the BUF802 at the front.

TIDA-01022 features the following:

- The LMH5401 is a high-performance, differential amplifier with a usable bandwidth from dc to 2 GHz. The device is used as single-to-differential conversion amplifier in this signal chain. The device offers excellent linearity performance at a fixed 12-dB gain.

- The LMH6401LMH6401 is a wideband digitally controlled variable-gain, differential in and differential out, amplifier. The noise and distortion performance are optimized to drive ultra-wideband analog-to-digital converters (ADCs). The device offers dc to 4.5-GHz bandwidth with a gain range from –6 dB to 26 dB in 1-dB steps. The gain is controlled using a standard serial peripheral interface (SPI).

- The ADC12DJ5200RF is a 12-bit, gigasample ADC that directly samples input frequencies from dc to greater than 10 GHz. The ADC12DJ5200RF is configurable as a dual-channel, 5.2-GSPS ADC or single-channel, 10.4-GSPS ADC.

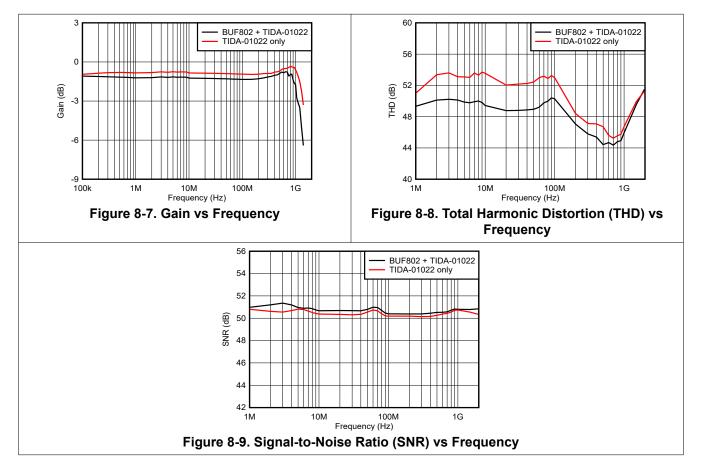

The BUF802 along with offering high-input impedance and low-noise for the front-end amplifier, holds capability of driving matched loads of 50  $\Omega$ , making this device easy to retrofit with predesigned analog front-end signal chains. Figure 8-7 to Figure 8-9 shows the comparison of native performance of the TI design TIDA-01022 and performance achieved post addition of the BUF802 at the front-end. Adding the BUF802 at the input of TIDA-01022 translates the original 50- $\Omega$  input impedance TI design to a high-input impedance DAQ signal chain. Figure 8-6 shows a simplified schematic of the BUF802 + TIDA-01022.

#### 8.2.2.2 Application Curves

#### 8.3 Power Supply Recommendations

The BUF802 is intended to operate with supplies ranging from  $\pm 4.5$  V to  $\pm 6.5$  V. The BUF802 operates on either single-sided supplies or split supplies. When using split supplies, the supplies are symmetrically balanced around GND or asymmetric. For best ac performance, center the input and output signal around the mid-supply.

Minimize the distance between the power-supply pins and decoupling capacitors. Place the high-frequency capacitors (< 0.1  $\mu$ F) close to the supply-pins, and on the same side of the PCB as the BUF802. Place larger capacitors (> 1  $\mu$ F) further away from the device. Section 8.4 has additional details on decoupling capacitor layout and routing.

The BUF802 has two sets of supply pins:

- V<sub>S+</sub> and V<sub>S-</sub>

- $V_{SO^+}$  and  $V_{SO}$

The separation of the input- and output-stage supply pins minimizes spurious crosstalk and maximizes transient decoupling between the two stages. Section 7.2 shows how both sets of supply pins are internally connected through back-to-back diodes. Therefore, connect the supply pins for the input and output stages to the same potential. Maintain separate and individual decoupling capacitors for all the supply pins; see also Section 8.4.

#### 8.4 Layout

#### 8.4.1 Layout Guidelines

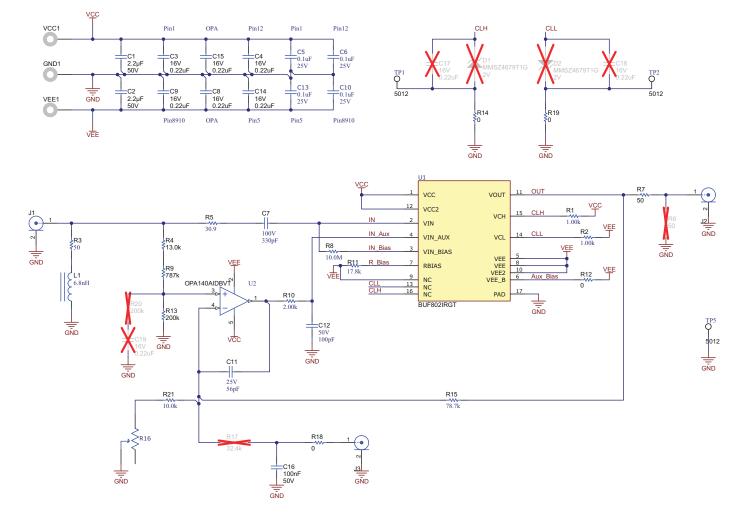

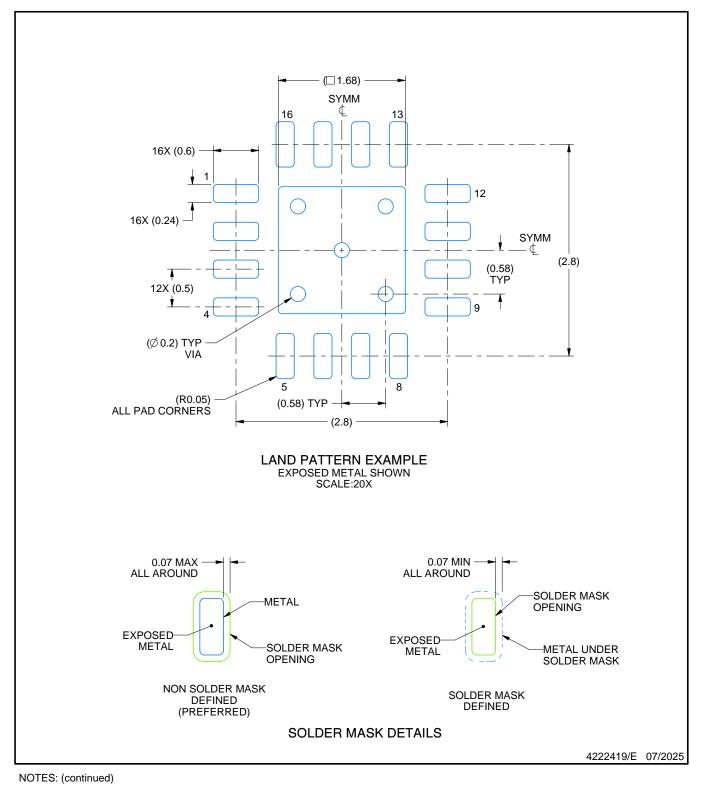

Achieving optimized performance with the BUF802 requires careful attention to board layout, parasitics, and passive component selection. Consider the following:

- **Peaking in the S21 transfer function**: keeping the trace length minimum is of prime importance to prevent peaking in the S21 transfer function of the BUF802. The trace inductance can form a resonant circuit with the input capacitance of the BUF802, causing peaking in the S21 response. Add a small resistor (R5 in Figure 8-10) in series with the dc blocking capacitor to dampen the LC resonance created by the trace inductance and the input capacitance of the BUF802. Choose series capacitors (C7 in Figure 8-10) with low equivalent series inductance (ESL) to minimize total inductance.

- Power-supply bypass capacitors: mount the power-supply bypass capacitors as close to the supply pins as possible and on the same side of the PCB as the BUF802. As shown in Figure 8-10, choose low-inductance LICC capacitors (C5, C6, C13, and C10) to minimize high-frequency impedance between the BUF802 and the bypass capacitors. Use multiple vias between the bypass capacitor and GND to reduce series inductance. As shown in Figure 8-10, also use multiple vias to GND on the 50-Ω input termination resistor (R3). Connect the bypass and termination vias to a solid GND plane.

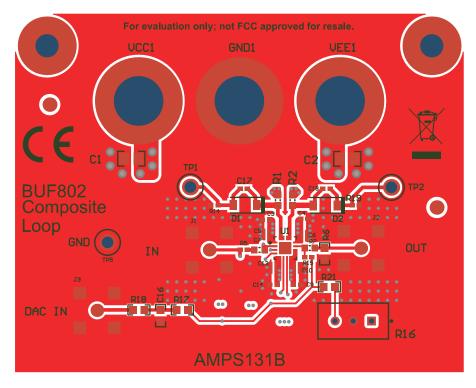

- **High precision signal path**: consisting of the precision op amp along with discrete components, the signal path can be adjusted and moved around to give precedence to the two previous points. In the Figure 8-12, the precision components are placed on the opposite side of the PCB as the BUF802.

- **Thermal pad**: thermally conductive but electrically insulated to the die. This configuration gives the circuit designer flexibility in connecting the thermal pad to any voltage. Choose a power or ground plane with the highest thermal mass for effective heat dissipation.

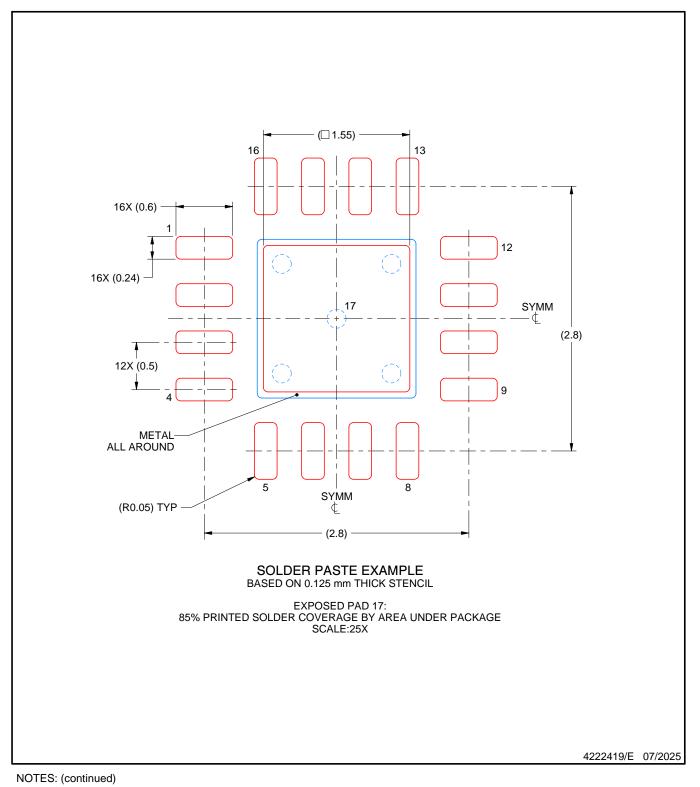

#### 8.4.2 Layout Example

Figure 8-10. Layout Example: Schematic for Layout Reference

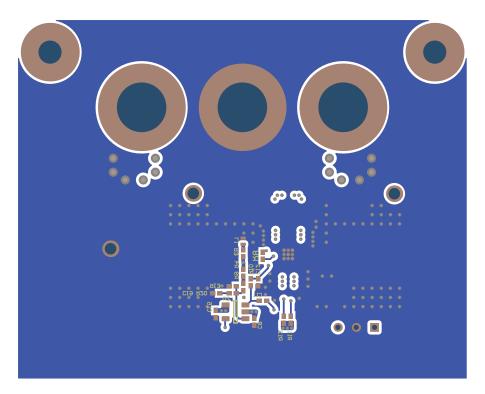

Figure 8-11. Layout Example: Top Layer

Figure 8-12. Layout Example: Bottom Layer

# 9 Device and Documentation Support

#### 9.1 Documentation Support

#### 9.1.1 Related Documentation

For related documentation, see the following:

• Texas Instruments, Flexible 3.2-GSPS multi-channel AFE reference design for DSOs, radar and 5G wireless test systems reference design

#### 9.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Notifications* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 9.3 Support Resources

TI E2E<sup>™</sup> support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 9.4 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

#### 9.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 9.6 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

### 10 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision C (March 2022) to Revision D (July 2025)                                                  | Page            |

|---|----------------------------------------------------------------------------------------------------------------|-----------------|

| • | Deleted maximum dVS/dT for supply turn-on and turn-off from Absolute Maximum Ratings                           | 4               |

| • | Changed current noise unit from pA/VHz to fA/VHz in both <i>Electrical Characteristics</i>                     | 5               |

| • | Moved V <sub>CLH</sub> and V <sub>CLL</sub> to symbol column and expanded text for clarity                     | <mark>5</mark>  |

| • | Deleted across temperature data from G <sub>AUX</sub>                                                          | 5               |

| • | Changed "to" to "/" in G <sub>AUX</sub> parameter name for clarity                                             | 5               |

| • | Added new row to G <sub>AUX</sub> for low frequency region                                                     |                 |

| • | Added crossover text to G <sub>AUX</sub>                                                                       | <mark>5</mark>  |

| • | Added test condition to In_Aux input voltage for clarity                                                       |                 |

| • | and a second |                 |

|   | Updated G <sub>AUX</sub> BW to a ratio for clarity                                                             |                 |

| • | Moved operating voltage to Recommended Operating Conditions                                                    | 5               |

| • | Updated voltage noise and current noise density vs frequency plots in Typical Characteristics                  | <mark>8</mark>  |

| • | Changed unit for current noise density vs frequency plot in Typical Characteristics                            | <mark>8</mark>  |

| • | Updated Detailed Design Procedure to reflect pole frequencies more accurately, to use G value from             |                 |

|   | Electrical Characteristics: Wide Bandwidth Mode, and to clarify CF value                                       | <mark>23</mark> |

|   |                                                                                                                |                 |

| С | Changes from Revision B (February 2022) to Revision C (March 2022) |   |  |  |  |  |

|---|--------------------------------------------------------------------|---|--|--|--|--|

| • | Relaxed DC Gain specifications                                     | 5 |  |  |  |  |

| • | Relaxed DC Gain specifications                                     |   |  |  |  |  |

| С | Changes from Revision A (December 2021) to Revision B (February 2022) |    |  |  |

|---|-----------------------------------------------------------------------|----|--|--|