# BQ79600-Q1 Automotive SPI/UART Communication Interface Functional-Safety **Compliant With Automatic Host Wakeup**

### 1 Features

- Qualified for automotive applications

- AEC-Q100 Qualified with the following results:

- Device temperature grade 1: –40°C to +125°C ambient operating temperature range

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- **Functional Safety-Compliant**

- Developed for functional safety applications

- Documentation available to aid ISO 26262 system design

- Safety Manual

- · Functional Safety Analysis Report

- Systematic capability up to ASIL-D

- Hardware capability up to ASIL-D

- Automatic wake up of BMS/BMU system when fault is detected in ring architecture

- Support supply from 4.75-V to 40-V

- UART/SPI Host interface

- Compatible with 3.3-V/5-V logic

- Isolated differential daisy chain

- Support ring architecture with one device

- Support transformer/ capacitor isolation

- Designed for BCI/EMI/EMC robustness

- Supports BQ7961X-Q1 family, BQ7965X, BQ7963X and future products

# 2 Applications

- Battery management system (BMS)

- Other HEV/EV

- Fuel cell

- Energy storage

# 3 Description

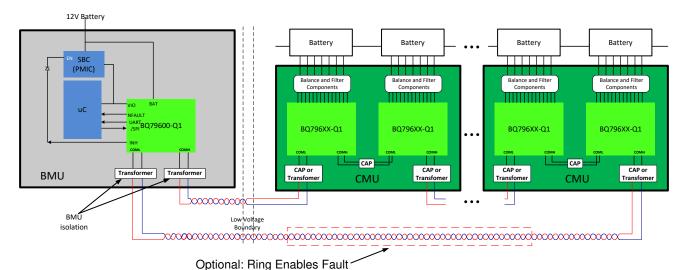

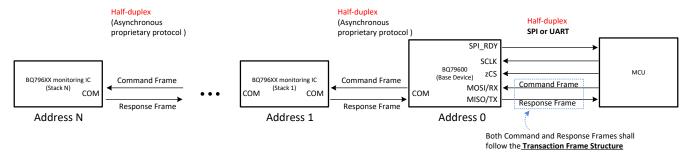

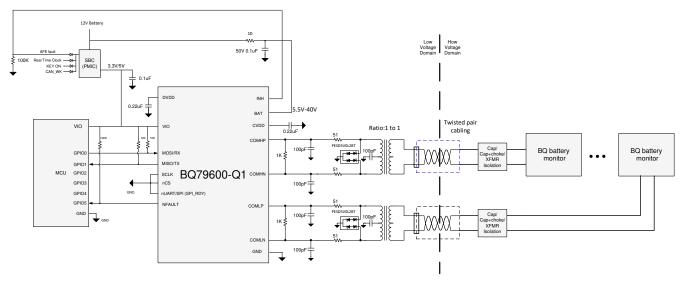

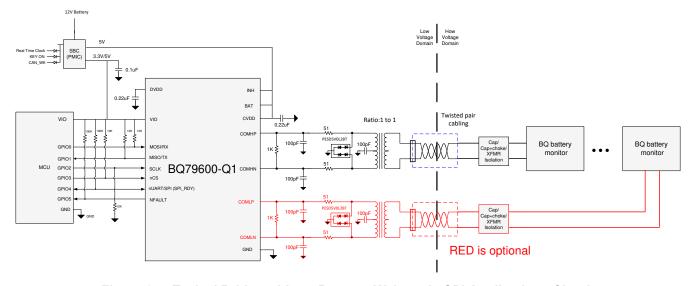

The BQ79600-Q1 is a communication (bridge) IC designed to interface between a microcontroller (MCU) and TI battery monitoring ICs, for example the BQ7961X-Q1. The information from the MCU is translated by the device to signals recognized by Tl's battery management daisy chain protocol, and transmitted out. And signals from daisy chain are decoded to bit stream and then sent back to MCU.

When the MCU and PMIC are in SHUTDOWN/ SLEEP, the BQ79600-Q1 can wake them up if any unmasked fault is detected when using ring architecture.

#### **Device Information**

| PART NUMBER(1) | PACKAGE        | BODY SIZE (NOM) |

|----------------|----------------|-----------------|

| BQ79600-Q1     | TSSOP (16-pin) | 6.6 mm × 5.1 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

**Simplified System Diagram**

and Reverse Wakeup Feature

# **Table of Contents**

| 1 Features                           | 1 7.5 Register Maps3                                      |

|--------------------------------------|-----------------------------------------------------------|

| 2 Applications                       | 1 8 Application and Implementation5                       |

| 3 Description                        |                                                           |

| 4 Revision History                   |                                                           |

| 5 Pin Configuration and Functions    |                                                           |

| Pin Functions                        |                                                           |

| 6 Specifications                     |                                                           |

| 6.1 Absolute Maximum Ratings         |                                                           |

| 6.2 ESD Ratings                      |                                                           |

| 6.3 Recommended Operating Conditions |                                                           |

| 6.4 Thermal Information              |                                                           |

| 6.5 Electrical Characteristics       | 5 11.3 Receiving Notification of Documentation Updates 63 |

| 6.6 Timing Requirements              | 6 11.4 Support Resources6                                 |

| 6.7 Typical Characteristics          |                                                           |

| 7 Detailed Description               | 10 11.6 Electrostatic Discharge Caution63                 |

| 7.1 Overview                         | 10 11.7 Glossary63                                        |

| 7.2 Functional Block Diagram         | 10 12 Mechanical, Packaging, and Orderable                |

| 7.3 Feature Description              |                                                           |

| 7.4 Device Functional Modes          | 36                                                        |

|                                      |                                                           |

|                                      |                                                           |

# **4 Revision History**

| C | hanges from Revision * (November 2019) to Revision A (June 2020) | Pag |

|---|------------------------------------------------------------------|-----|

| • | Changed from Advance Information to Production Data              |     |

# **5 Pin Configuration and Functions**

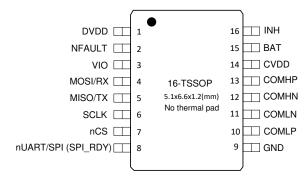

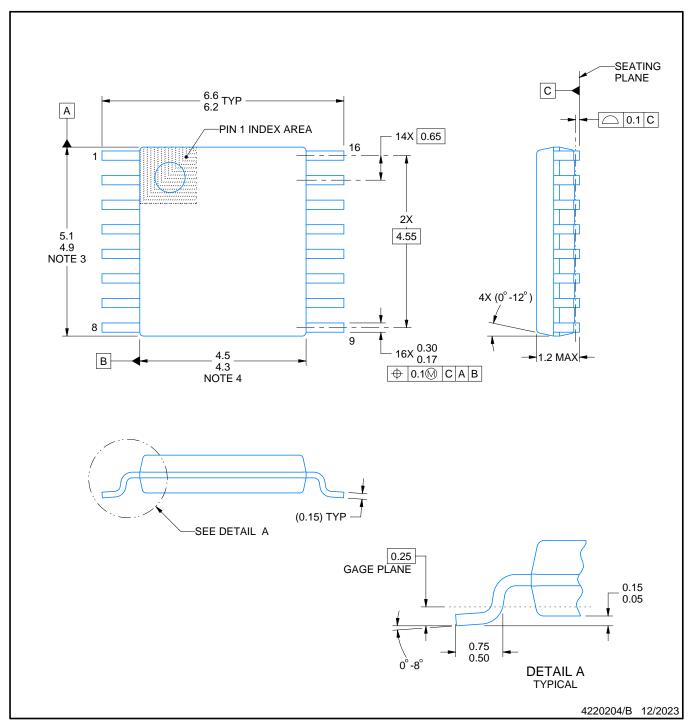

Figure 5-1. PW Package 16-Pin TSSOP Top View

# **Pin Functions**

| PII                    | N   | T) (D=(1)           | DECODED :                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|------------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                   | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| VIO                    | 3   | Р                   | Power supply input for UART/SPI input/output pins. Decouple with a 0.1µF capacitor to GND. VIO should be powered before SCLK, nCS, RX/MOSI, TX/MISO, NFAULT, nUART/SPI (SPI_RDY) is driven.                                                                                                                                                                                                                                                                                  |  |

| SCLK                   | 6   | DI                  | SPI clock input. If SPI interface is used, this pin is connected to SPI master controller. Connect to GND with a 10-100kohm pull-down resistor. If not used, connect to GND.                                                                                                                                                                                                                                                                                                 |  |

| nCS                    | 7   | DI                  | Active low chip select pin for SPI interface. Connect to VIO with 10-100kohm pull-up resistor in SPI mode. Cannot hardwire to GND in SPI mode. Connect to GND in UART mode.                                                                                                                                                                                                                                                                                                  |  |

| RX/MOSI                | 4   | DI                  | UART receiver input or SPI master out slave in. Connect to VIO with a 10-100kohm pull-up resistor. Don't leave it unconnected.                                                                                                                                                                                                                                                                                                                                               |  |

| TX/MISO                | 5   | DO                  | UART transmitter output or SPI master in slave out. Pull up to VIO with a 10-100kohm pull-up resistor at MCU side. MISO pin drives high in SPI idle mode, cannot directly support SPI multidrop, if multidrop is needed, add a tri-state buffer between BQ79600-Q1 and MCU.                                                                                                                                                                                                  |  |

| NFAULT                 | 2   | DO                  | Fault indication output. Open drain active low. Pull up to VIO with 100kohm resistor. Connect NFAULT to host MCU GPIO. If not used, connect to GND.                                                                                                                                                                                                                                                                                                                          |  |

| nUART/SPI<br>(SPI_RDY) | 8   | DI/O                | If used as UART mode, connect this pin to GND. If used as SPI mode, connect to VIO through 10-100kohm pull up resistor and connect this pin to MCU GPIO. This pin is used as an input pin to select SPI or UART interface before device finishes wakeup/reset initialization (SPI communication is ready). If SPI mode is selected, SPI_RDY has to be used by host to decide if read/write can be initiated or needing further wait. Refer to Section 7.3.2.1.2.2.1 details. |  |

| DVDD                   | 1   | Р                   | 1.8V regulated output. DVDD supplies the internal digital circuits. Bypass DVDD with a $0.22\mu F$ (recommended) or a $0.47\mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                          |  |

| GND                    | 9   | Р                   | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| CVDD                   | 14  | Р                   | Dedicated 5V supply used for the daisy chain communications. Decouple with a 0.22µF (recommended) or a 0.47µF to GND.                                                                                                                                                                                                                                                                                                                                                        |  |

| COMHN                  | 12  | AC-I/O              | This is an AC coupled bi-directional I/O pin for daisy chain (VIF) communication. Do not apply                                                                                                                                                                                                                                                                                                                                                                               |  |

| СОМНР                  | 13  | AC-I/O              | external DC voltage to this pin. Shall connect to COMLN/P of adjacent device through proper isolation, see Section 7.3.2.1.1. Leave unconnected if (Ring Architecture) not used.                                                                                                                                                                                                                                                                                             |  |

| COMLN                  | 11  | AC-I/O              | This is an AC coupled bi-directional I/O pin for daisy chain (VIF) communication. Do not apply                                                                                                                                                                                                                                                                                                                                                                               |  |

| COMLP                  | 10  | AC-I/O              | external DC voltage to this pin. Shall connect to COMHN/P of adjacent device through proper isolation, see Section 7.3.2.1.1. Leave unconnected if (Ring Architecture) not used.                                                                                                                                                                                                                                                                                             |  |

| INH                    | 16  | HV-O                | ibit pin (PMOS open drain) to control system voltage regulators, connect 100kohm resistor GND. If reverse wake up feature is not used, connect this pin to BAT pin. Don't leave this pin ting.                                                                                                                                                                                                                                                                               |  |

| BAT                    | 15  | HV-P                | Battery supply Input. Supply internal LDOs and wakeup circuit. Connect to external supply through 10ohm resistor. Bypass to GND with 0.1µF.                                                                                                                                                                                                                                                                                                                                  |  |

<sup>(1)</sup> DI = digital input, DO = digital output, HV = high voltage

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

| ·                |                                                                | MIN  | MAX     | UNIT |

|------------------|----------------------------------------------------------------|------|---------|------|

|                  | BAT to GND                                                     | -0.3 | 40      | V    |

|                  | INH to GND (INH is lower than BAT)                             | -0.3 | 40      | V    |

|                  | VIO, CVDD to GND                                               | -0.3 | 5.5     | V    |

| Input Voltage    | DVDD to GND                                                    | -0.3 | 1.98    | V    |

| put romago       | MISO/TX, MOSI/RX, nCS, SCLK, NFAULT, nUART/SPI(SPI_RDY) to GND | -0.3 | VIO+0.3 | V    |

|                  | COMHP, COMHN, COMLP, COMLN to GND                              | -10  | 10      | V    |

|                  | COMHP to COMHN, COMLP to COMLN                                 | -6.5 | 6.5     | V    |

| INH current      |                                                                |      | 4       | mA   |

| I/O current      | MISO/TX current (100pF load, VIO=5V, 10ns transition-time)     |      | 8       | mA   |

| T <sub>A</sub>   | Ambient temperature                                            | -40  | 125     | °C   |

| TJ               | Junction temperature                                           | -40  | 150     | °C   |

| T <sub>stg</sub> | Storage temperature                                            | -65  | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                                                                                                                                                                                                          |  |                              | VALUE | UNIT |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------|-------|------|

|                    | V <sub>(ESD)</sub> Electrostatic discharge Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> Charged device model (CDM), per AEC Q100-0019 Charged device model (CDM), per AEC Q100-019 Other pins |  | ±2000                        |       |      |

| V <sub>(ESD)</sub> |                                                                                                                                                                                                          |  | Corner pins (1, 8, 9 and 16) | ±750  | V    |

|                    |                                                                                                                                                                                                          |  | Other pins                   | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                        |                                                                                 | MIN   | TYP MAX | UNIT |

|------------------------|---------------------------------------------------------------------------------|-------|---------|------|

| V <sub>BAT, INH</sub>  | BAT, INH (INH is equal to or lower than BAT) (Powered by 12V Battery)           | 5.5   | 24      | V    |

| V <sub>VIO_RANGE</sub> | VIO input (applies to nCS, MOSI/RX, MISO/TX, SLCK, nUART/SPI (SPI_RDY), NFAULT) | 3.135 | 5.25    | V    |

| I <sub>MISO/TX</sub>   | MISO/TX current                                                                 |       | 3       | mA   |

| I <sub>INH</sub>       | INH output current                                                              |       | 2       | mA   |

| T <sub>A</sub>         | Operation temperature                                                           | -40   | 125     | °C   |

# **6.4 Thermal Information**

|                       |                                            | BQ79600-Q1 |      |

|-----------------------|--------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>              | PW(TSSOP)  | UNIT |

|                       |                                            | 16 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance     | 102        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance  | 28.9       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance       | 49         | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter | 14         | °C/W |

Product Folder Links: BQ79600-Q1

|             |                                              | 16 PINS   |      |

|-------------|----------------------------------------------|-----------|------|

|             | THERMAL METRIC <sup>(1)</sup>                | PW(TSSOP) | UNIT |

|             |                                              | 16 PINS   |      |

| $\Psi_{JB}$ | Junction-to-board characterization parameter | 48.2      | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

# **6.5 Electrical Characteristics**

VIO = 3.3V, over operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                                                                    | TEST CONDITIONS                                                                                                     | MIN  | TYP  | MAX  | UNIT |

|------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OPERATI                      | ON VOLTAGE                                                                   |                                                                                                                     |      |      |      |      |

| V <sub>BAT</sub>             |                                                                              | When reverse wakeup feature is used, BAT pin is powered by "12V battery"                                            | 5.5  |      | 24   | V    |

| $V_{BAT}$                    |                                                                              | When reverse wakeup feature is not used, BAT/CVDD are powered by regulated 5V                                       | 4.75 |      | 5.25 | V    |

| THERMA                       | L SHUTDOWN                                                                   |                                                                                                                     |      |      |      |      |

| T <sub>SHUT_R</sub>          | Thermal shutdown (rising direction)                                          | DieTemp sensor                                                                                                      | 126  | 138  | 150  | °C   |

| T <sub>SHUT_F</sub>          | Thermal shutdown (falling direction)                                         | DieTemp sensor                                                                                                      | 116  |      | 141  | °C   |

| SUPPLY (                     | CURRENTS                                                                     |                                                                                                                     |      |      |      |      |

| I <sub>SHDN_1</sub>          | Supply current in SHUTDOWN mode device powered by regulated 5V supply        | VBAT shorted to CVDD, both equal to 5V, measured through GND pin                                                    |      |      | 7    | μΑ   |

| I <sub>SHDN_2</sub>          | Supply current in SHUTDOWN mode powered by "12V" battery directly            | VBAT= 17V, CVDD self powered, measured through GND pin                                                              |      |      | 9    | μΑ   |

| I <sub>VALIDATE</sub>        | Supply current in VALIDATE mode                                              | Current on BAT pin                                                                                                  |      |      | 168  | μA   |

| I <sub>SLP(IDLE)</sub>       | Baseline supply current in SLEEP mode                                        | Current on BAT pin, no fault, COMH and COML RX disabled, no HB TX                                                   |      |      | 110  | μΑ   |

| I <sub>SLP_RX_O</sub>        | Additional supply current to SLEEP mode base line                            | When COML OR COMH RX is on                                                                                          |      | 35   |      | μΑ   |

| I <sub>SLP_TX_O</sub>        | Additional supply current to SLEEP mode base line                            | When COML or COMH tone transmiter is on (HB tone)                                                                   |      |      | 8    | μΑ   |

| I <sub>ACT(IDLE)</sub>       | Baseline supply current in ACTIVE mode                                       | Current on BAT pin, no fault, no communication, Tone RX/TX is off                                                   |      | 3    | 4    | mA   |

| I <sub>СОМТ</sub>            | Additional average current for one of BQ79600 daisy chain transmitters is on | Average current into VBAT when BQ79600 transmits 14 bytes of data (brdcast write 8 bytes of 0x00 into address 0X1B) |      | 10   |      | mA   |

| Supplies                     | (AVAO_REF, always on internal supply)                                        |                                                                                                                     |      |      |      |      |

| V <sub>AVAORE</sub><br>G     | AVAOREG voltage                                                              | VBAT > min VBAT                                                                                                     |      | 2.45 |      | V    |

| V <sub>AVDDREF</sub>         | AVDDREF OV threshold                                                         | VBAT > min VBAT, hys = 130mV                                                                                        | 2.8  |      | 3.1  | V    |

| Supplies                     | (CVDD)                                                                       |                                                                                                                     |      |      |      |      |

| V <sub>CVDD</sub>            | CVDD output voltage                                                          | No external load, C <sub>SUPPLIES</sub> = 0.22μF,<br>ACTIVE mode                                                    | 4.9  | 5    | 5.1  | V    |

| V <sub>CVDD_O</sub>          | CVDD OV rising threshold                                                     | Hys = 140mV                                                                                                         | 5.3  | 5.5  | 5.65 | V    |

| V <sub>CVDD_U</sub><br>v_f   | CVDD UV falling threshold                                                    |                                                                                                                     | 4.35 | 4.5  | 4.65 | V    |

| V <sub>CVDD_U</sub><br>v_r   | CVDD UV rising threshold                                                     |                                                                                                                     | 4.45 | 4.6  | 4.75 | V    |

| V <sub>CVDD_ILI</sub><br>MIT | CVDD current limit                                                           |                                                                                                                     | 53   | ,    | 81   | mA   |

| C <sub>CVDD</sub>            | Capacitance range on CVDD pin                                                | Not capacitor value                                                                                                 | 0.1  |      | 0.8  | μF   |

VIO = 3.3V, over operating free-air temperature range (unless otherwise noted)

|                              | PARAMETER                                                                                | TEST CONDITIONS                                                  | MIN                        | TYP | MAX                        | UNIT |

|------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|-----|----------------------------|------|

| Supplies                     | (DVDD)                                                                                   |                                                                  |                            |     |                            |      |

| $V_{DVDD}$                   | DVDD output voltage                                                                      | No external load, C <sub>SUPPLIES</sub> = 0.22μF,<br>ACTIVE mode | 1.75                       | 1.8 | 1.85                       | V    |

| V <sub>DVDD_O</sub>          | DVDD OV rising threshold                                                                 | Hys = 65mV                                                       | 1.9                        |     | 2.1                        | V    |

| V <sub>DVDD_U</sub><br>v_f   | DVDD UV falling threshold                                                                |                                                                  | 1.63                       |     | 1.69                       | V    |

| V <sub>DVDD_U</sub><br>v_r   | DVDD UV rising threshold                                                                 |                                                                  | 1.68                       |     | 1.75                       | V    |

| V <sub>DVDD_ILI</sub><br>MIT | DVDD current limit                                                                       |                                                                  | 20                         |     | 57                         | mA   |

| D <sub>DVDD</sub>            | Load capacitance on DVDD pin                                                             | Not capacitor value                                              | 0.1                        |     | 0.8                        | μF   |

| SNIFF DE                     | TECTOR                                                                                   |                                                                  |                            |     |                            |      |

| V <sub>VAL_THR</sub>         | Sniffer detector threshold, rising swing on COMHP has to be larger than value            | Sniffer is enabled, and device is in SHUTDOWN mode               | 3.2                        |     | 3.6                        | V    |

| INH Drive                    | er                                                                                       |                                                                  |                            |     |                            |      |

| V <sub>DROP_IN</sub>         | When INH is pulled up, voltage drop from BAT to INH                                      | I <sub>INH</sub> = -0.5mA                                        |                            | 0.5 | 1                          | V    |

| V <sub>INH_DET</sub>         | Threshold to set [INH_STAT] to '1'                                                       |                                                                  | 2.2                        |     |                            | V    |

| Referenc                     | e Voltages                                                                               |                                                                  |                            |     | 1                          |      |

| Digital I/C                  | Os (TX, RX, NFAULT)                                                                      |                                                                  |                            |     |                            |      |

| V <sub>VIO_UV_</sub>         | VIO UV rising                                                                            | Hys = 200mV                                                      | 2.5                        |     | 3.1                        | V    |

| V <sub>OH</sub>              | Output as logic level high (TX)                                                          | FET pull up, lout=1mA, VIO = 3.3V or 5V                          | V <sub>VIO</sub> -0.1      |     |                            | V    |

| V <sub>OL</sub>              | Output as logic level low (TX)                                                           | FET pull down, lout=1mA, VIO = 3.3V or 5V                        |                            |     | 0.1                        | V    |

| V <sub>IH</sub>              | Input as logic level high (RX), requirement for user                                     | VIO = 3.3V or 5V                                                 | 0.75 x<br>V <sub>VIO</sub> |     |                            | V    |

| V <sub>IL</sub>              | Input as logic level low (RX), requirement for user                                      | VIO = 3.3V or 5V                                                 |                            |     | 0.25 x<br>V <sub>VIO</sub> | V    |

| R <sub>NFAULT</sub>          | NFAULT pull down impedance                                                               | Use 100kohm external pull up                                     |                            |     | 1000                       | Ω    |

| Daisy-cha                    | ain Communication Bus                                                                    |                                                                  |                            |     |                            |      |

| V <sub>DCCM_1</sub>          | Common mode voltage (COML and COMH)                                                      | ACTIVE mode                                                      |                            | 2.2 |                            | V    |

| V <sub>DCCM_2</sub>          | Common mode voltage (COML and COMH)                                                      | SLEEP or VALIDATE mode                                           |                            | 1   |                            | V    |

| V <sub>COMM_D</sub><br>ATA   | COMM port data receiver threshold range (V <sub>COMP</sub> -V <sub>COMN</sub> )          |                                                                  | 1.04                       |     | 1.75                       | V    |

| V <sub>COMM_T</sub>          | COMM port HB/FAULT tone receiver threshold range (V <sub>COMP</sub> -V <sub>COMN</sub> ) |                                                                  | 1.13                       |     | 1.94                       | V    |

# **6.6 Timing Requirements**

over operating free-air temperature range (unless otherwise noted)

| PARAMETER         | TEST CONDITIONS                                                                                                      | MIN | TYP | MAX | UNIT |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|--|

| OWER STATE TIMING |                                                                                                                      |     |     |     |      |  |

| POR2COM           | From V <sub>BAT</sub> (rising) > V <sub>POR</sub> to device ready to receive WAKE ping, ramp up VBAT and VIO in 10µs |     |     | 1   | ms   |  |

Submit Document Feedback

over operating free-air temperature range (unless otherwise noted)

|                                | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                                                      | MIN   | TYP  | MAX   | UNIT   |

|--------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|--------|

| t <sub>SU(WAKE_</sub><br>SHUT) | Startup from SHUTDOWN/VALIDATE to ACTIVE mode                                     | From receiving WAKE ping (RX ping going low-to-high) to device in ACTIVE mode (ready to do µART /SPI communication) (CVDD= 0.22µF capacitor DVDD = 0.22µF capacitor) |       | 2    | 3.5   | ms     |

| t <sub>SU(SLP2A</sub><br>CT)   | Startup from SLEEP to ACTIVE mode (with Sleep2active ping)                        | From receiving SLP2ACT ping (RX ping going low-to-high) to device in ACTIVE mode (ready to do UART / SPIcommunication)                                               |       |      | 260   | μs     |

| t <sub>SU(WAKE_</sub><br>SLP)  | Startup from SLEEP to ACTIVE mode (with WAKE ping)                                | From receiving WAKE ping (RX ping going low-to-high) to device in ACTIVE mode (ready to do UART / SPIcommunication)                                                  |       |      | 600   | μs     |

| t <sub>RST</sub>               | Reset time from ACTIVE mode to ACTIVE mode                                        | From receiving WAKE ping (RX ping going low-to-high) or CONTROL1[SOFT_RESET]=1 to device in ACTIVE mode (ready to do UART /SPI communication)                        |       |      | 600   | μs     |

| t <sub>SLP</sub>               | From ACTIVE to SLEEP mode                                                         | From receiving SLEEP entry condition to enter in SLEEP mode                                                                                                          |       |      | 100   | μs     |

| t <sub>SHTDN</sub>             | From ACTIVE/SLEEP/VALIDATE to SHUTDOWN mode                                       | From receiving SHUTDOWN entry condition to enter in SHUTDOWN mode (CVDD<1.2V)                                                                                        | 5     |      | ms    |        |

| t <sub>VALID_EN</sub>          | From SHUTDOWN to VALIDATE                                                         | From fault tone toggling on COM port to DVDD hit above 1.75V                                                                                                         | 10    |      | 10    | ms     |

| t <sub>VALID_TIM</sub>         | time to validate fault tone before transition to SHUTDOWN state                   | Start from DVDD out of reset                                                                                                                                         |       | 150  |       | ms     |

| INH Drive                      | r TIMING                                                                          |                                                                                                                                                                      |       |      |       |        |

| t <sub>INH_DLY</sub>           | After device enters VALIDATE, from first couplet of fault tone to INH pulled high |                                                                                                                                                                      |       | 720  |       | μs     |

| PING SIG                       | NAL TIMING                                                                        |                                                                                                                                                                      |       |      | L     |        |

| t <sub>HLD_WAK</sub>           | From user perspective, WAKE ping low time on MOSI/RX pin                          | VBAT > VPOR, RX pin (low-pulse width)<br>VIO = 3.3 or 5V                                                                                                             | 2.5   |      | 3     | ms     |

| t <sub>HLD_SD</sub>            | From user perspective, SHUTDOWN ping low time on MOSI/RX pin                      | VBAT > VPOR, RX pin (low-pulse width) VIO = 3.3 or 5V                                                                                                                | 12.5  |      |       | ms     |

| t <sub>StA</sub>               | From user perspective, SLEEPtoACTIVE ping low time on MOSI/RX pin                 | VBAT > VPOR                                                                                                                                                          | 250   |      | 300   | μs     |

| Daisy-cha                      | ain Communication Bus TIMING                                                      | -                                                                                                                                                                    |       |      |       |        |

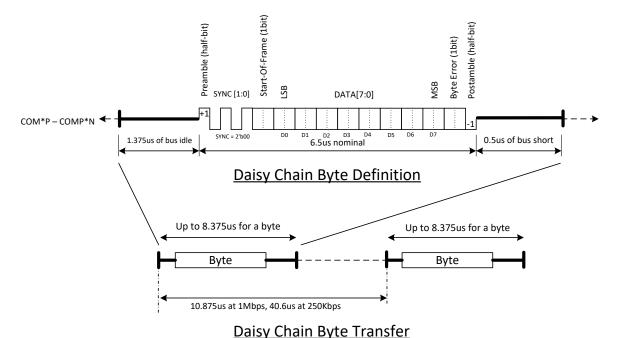

| t <sub>PW_DC</sub>             | COMM data Pulse width of data (half bit time) for communiction                    |                                                                                                                                                                      | 230   | 250  | 270   | ns     |

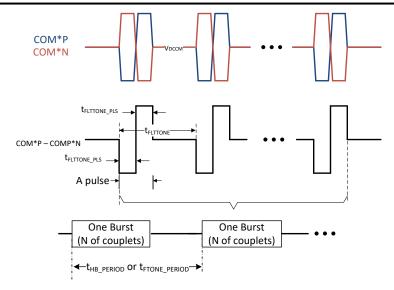

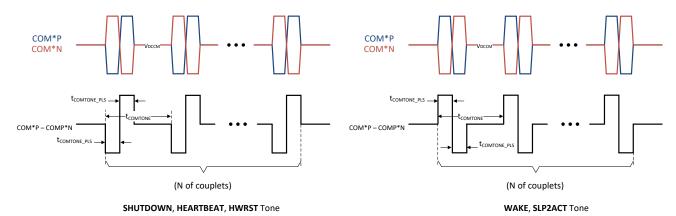

| t <sub>COMTONE</sub>           | Time between pulses within a comm tone (HFO based).                               | Transmit. From the beginning of a pulse until the beginning of the next pulse.                                                                                       | 10.67 | 11   | 11.33 | μs     |

| t <sub>COMTONE</sub><br>_PLS   | Comm tone pulse width(HFO based)                                                  | Transmit                                                                                                                                                             | 0.97  | 1    | 1.03  | μs     |

| t <sub>FLTTONE</sub>           | Time between pulses within a fault tone (LFO based).                              | Only transmit HB tone, not FAULT tone. From the beginning of a pulse until the beginning of the next pulse.                                                          | 10.3  | 11.5 | 12.7  | μs     |

| t <sub>FLTTONE_</sub><br>PLS   | Fault tone or HB tone pulse width (analog delay based)                            |                                                                                                                                                                      |       | 1    |       | μs     |

| n <sub>HBDET</sub>             | HEARTBEAT: Number of pulses to detect as a valid tone (dig counter)               | Detect                                                                                                                                                               |       | 16   |       | pulses |

| n <sub>FTONEDE</sub><br>T      | FAULT TONE: Number of pulses to detect as a valid tone (dig counter)              | Detect                                                                                                                                                               |       | 64   |       | pulses |

|                                | <del> </del>                                                                      | 1                                                                                                                                                                    |       |      |       |        |

over operating free-air temperature range (unless otherwise noted)

|                                | PARAMETER                                                                                                                 | TEST CONDITIONS                                                                                      | MIN  | TYP | MAX | UNIT       |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|-----|-----|------------|

| t <sub>HB_PERIO</sub><br>D     | HEARTBEAT: Period between HEARTBEAT Burst (from the beginning of a HEARTBEAT to the beginning of the next HEARTBEAT)      |                                                                                                      | 360  | 400 | 440 | ms         |

| t <sub>HB_TIMEO</sub><br>UT    | HEARTBEAT: Timeout to considered as not receving HEARTBEAT                                                                |                                                                                                      | 0.9  | 1   | 1.1 | s          |

| t <sub>HB_FAST</sub>           | HEARTBEAT: If HEARTBEAT is received within this time, it is considered receving HEARTBEAT too fast                        |                                                                                                      |      | 200 |     | ms         |

| t <sub>FTONE_PE</sub>          | Defined by BQ7961X, FAULT TONE:<br>Period between FAULT TONE Burst                                                        | From the beginning of a FAULT TONE to the beginning of the next FAULT TONE                           |      | 50  |     | ms         |

| t <sub>FT_LATEN</sub><br>CY    | Fault Tone latency in Base Device                                                                                         | From the time device receives the tone to the time asserts NFAULT                                    |      | 24  |     | μs         |

| I/O TIMIN                      | IG (TX, RX, NFAULT)                                                                                                       |                                                                                                      |      |     |     | I          |

| t <sub>RISE_TX</sub>           | Rise Time                                                                                                                 | C <sub>LOAD</sub> = 100pF, VIO=3.3V or 5V                                                            |      | 15  |     | ns         |

| t <sub>FALL_TX</sub>           | Fall Time                                                                                                                 | C <sub>LOAD</sub> = 100pF, VIO=3.3V or 5V                                                            |      | 15  |     | ns         |

| t <sub>FALL/</sub>             | RX pin rise/fall time                                                                                                     |                                                                                                      |      |     | 100 | ns         |

| UART TI                        | MING                                                                                                                      |                                                                                                      |      |     |     |            |

| UARTER<br>R_BAUD               |                                                                                                                           |                                                                                                      | -1.5 |     | 1.5 | %          |

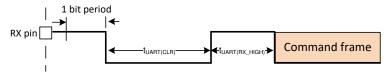

| t <sub>UART(CLR</sub>          | UART Comm Clear low time                                                                                                  |                                                                                                      | 15   |     | 20  | bit period |

| t <sub>UART(RX_</sub><br>HIGH) | UART high time after Comm Clear, before sending Clear or Reset                                                            |                                                                                                      | 1    |     |     | bit period |

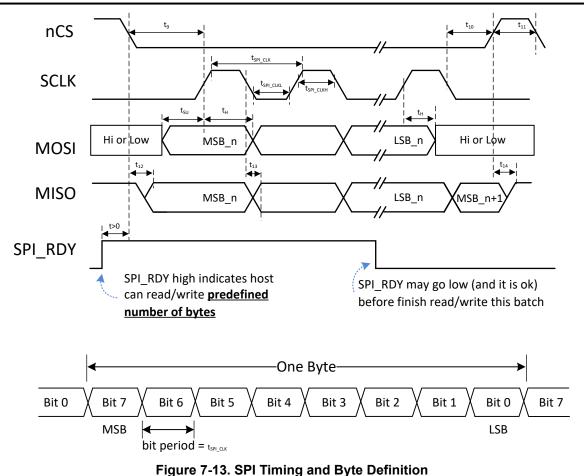

| SPI TIMIN                      | NG                                                                                                                        |                                                                                                      |      |     |     |            |

| SCLK                           | SPI clock freq                                                                                                            |                                                                                                      | 2    |     | 6   | MHz        |

| n <sub>SPI(CLR)</sub>          | SPI Comm Clear low time                                                                                                   |                                                                                                      |      | 8   |     | bit        |

| t <sub>SPI_R</sub>             | SPI clock rising edge                                                                                                     | 25% to 75%                                                                                           |      |     | 10  | ns         |

| t <sub>SPI_F</sub>             | SPI clock falling edge                                                                                                    | 25% to 75%                                                                                           |      |     | 10  | ns         |

| t <sub>SPI_CLKH</sub>          | SPI clock high time                                                                                                       |                                                                                                      | 70   |     |     | ns         |

| t <sub>SPI_CLKL</sub>          | SPI clock low time                                                                                                        |                                                                                                      | 70   |     |     | ns         |

| t <sub>8</sub>                 | Max SPI_RDY service interval. This time doesn't apply if total response bytes (payload + overhead) is less than 256 bytes | Read SCLK = 6MHz, with 30% SPI BUS idle time                                                         |      | 1   |     | ms         |

| t <sub>9</sub>                 | From nCS (25%) to SCLK rising (75%)                                                                                       |                                                                                                      | 500  |     |     | ns         |

| t <sub>10</sub>                | From SCLK falling (25%) to nCS (75%)                                                                                      |                                                                                                      | 500  |     |     | ns         |

| t <sub>11</sub>                | From nCS rising(75%) to nCS falling(25%)                                                                                  | Don't drop nCS while SPI_RDY is low                                                                  | 1    |     |     | μs         |

| t <sub>12</sub>                | From nCS falling (25%) to stable MISO(L:20% H:80%)                                                                        | Timing is defined at device pins, exclude propergation delay of PCB traces (from device perspective) |      |     | 42  | ns         |

| t <sub>13</sub>                | From SCLK falling (25%) to stable MISO(L:20% H:80%)                                                                       | Timing is defined at device pins, exclude propergation delay of PCB traces (from device perspective) |      |     | 42  | ns         |

| t <sub>14</sub>                | From nCS rising (75%) to MISO drive to '1' (80%)                                                                          | Timing is defined at device pins, exclude propergation delay of PCB traces (from device perspective) |      |     | 42  | ns         |

|                                | 1                                                                                                                         |                                                                                                      |      |     |     |            |

| t <sub>SU</sub>                | Setup time, refer to 75% of SCLK rising                                                                                   |                                                                                                      | 20   |     |     | ns         |

over operating free-air temperature range (unless otherwise noted)

|                        | PARAMETER                                                                | TEST CONDITIONS                                                      | MIN   | TYP | MAX   | UNIT   |

|------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------|-------|-----|-------|--------|

| n <sub>VALIDATE</sub>  | Number of pulses needed (digital counter) to transition to validate mode | Sniffer is enabled, and device is in SHUTDOWN mode                   | 64    |     |       | pulses |

| t <sub>SNIFFIDLE</sub> | Timer length. Once timer expired, it resets the 64 counter               | Sniffer is enabled, and device is in SHUTDOWN mode                   | 20    |     | 52    | μs     |

| OSCILLA <sup>*</sup>   | TOR                                                                      |                                                                      |       |     |       |        |

| f <sub>HFO</sub>       | HFO frequency                                                            |                                                                      | 31.52 | 32  | 32.48 | MHz    |

| t <sub>HFOWDG</sub>    | HFO watchdog time                                                        | Reset digital if HFO is stuck or period is > than the watchdog timer |       |     | 35    | μs     |

| f <sub>LFO</sub>       | LFO frequency                                                            |                                                                      | 235.8 | 262 | 288.2 | kHz    |

| t <sub>LFOWDG</sub>    | LFO watchdog time                                                        | Reset digital if LFO is stuck or period is > than the watchdog timer |       |     | 35    | μs     |

# **6.7 Typical Characteristics**

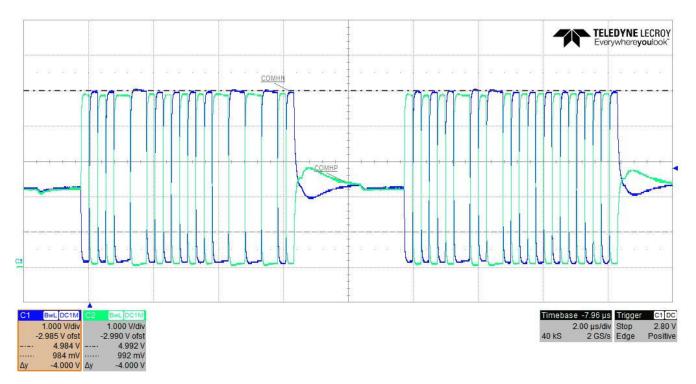

Figure 6-1. Typical COMHN and COMHP characteristic

# 7 Detailed Description

### 7.1 Overview

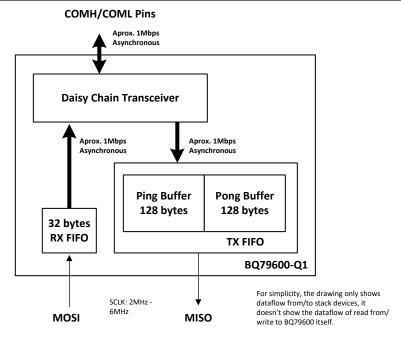

The BQ79600-Q1 is a bridge IC designed to interface between microcontroller (MCU) and TI battery monitoring ICs (BQ7961X-Q1 family). It translates between daisy chain interface and SPI/UART interface. It is fully compatible with BQ7961X-Q1 family. When working with BQ7961X-Q1 family, BQ79600-Q1 supports automatic host wakeup through INH pin when unmask fault is detected in high voltage battery pack. Details can be found in Section 7.3.4. For convenience of traceability, each device is marked by DIE IDs and PARTID which could be found in Section 7.5 Register Summary Table.

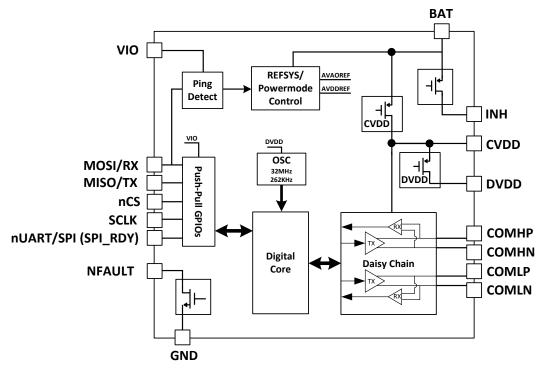

# 7.2 Functional Block Diagram

Figure 7-1. Functional Block Diagram

### 7.3 Feature Description

# 7.3.1 Functional Modes and Power Supply

#### 7.3.1.1 Power Mode

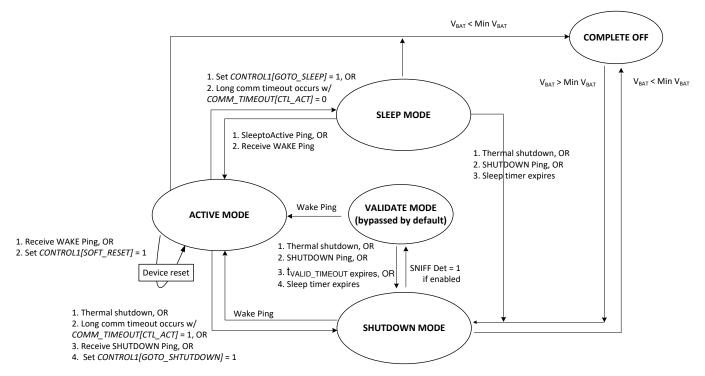

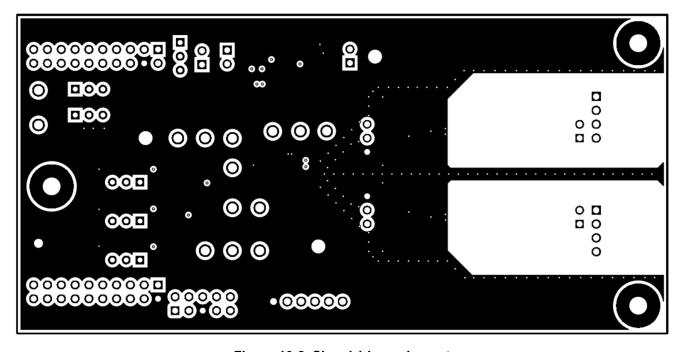

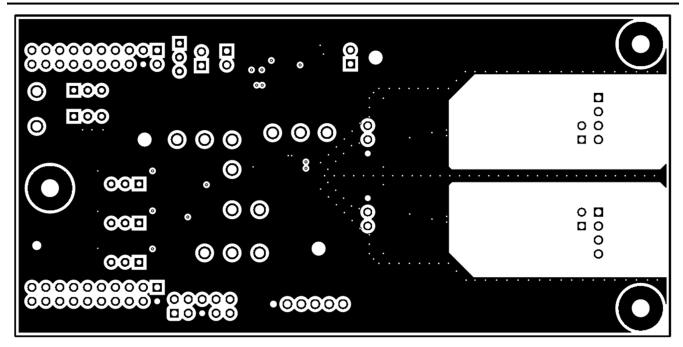

The device has four power modes plus an Complete Off state. The functions supported under each power modes are summarized in Table 7-1 and the power state diagram is shown in Figure 7-2.

- COMPLETE OFF: The voltage at the BAT pin is less than V<sub>BAT</sub> min, and all circuits are powered off.

- SHUTDOWN: The lowest power mode. Without VIO, device can only transition to VALIDATE. (If Sniffer used)

- SLEEP: A low power mode. Transition to ACTIVE is much faster compared to SHUTDOWN.

- ACTIVE: Full power mode. Device can communicate between MCU and daisy chain.

- VALIDATE: This state is to validate if there is real fault tone from stack devices. If fault tone is validated, drive INH pin towards VBAT (INH pin is latched until cleared by user). Device goes back to SHUTDOWN if t<sub>VALID\_TIMEOUT</sub> or sleep timer expires. (t<sub>VALID\_TIMEOUT</sub> timer is reset if fault tone is detected, detecting Heartbeat tone doesn't reset timer.) This state is bypassed if Section 7.3.5 is disabled (by default). Once entered this state, a status bit [VALIDATE\_DET] is set in next ACTIVE such that host knows what happened. Without VIO, device can only transition to SHUTDOWN. NFAULT pin is low in this mode.

**Table 7-1. Functions Summary**

| FUNCTIONAL BLOCK(1)                                        | SHUTDOWN                         | VALIDATE(3)     | SLEEP                                  | ACTIVE                               |

|------------------------------------------------------------|----------------------------------|-----------------|----------------------------------------|--------------------------------------|

| Data Communication RX/TX                                   |                                  |                 |                                        | If VIO_UV_R = 1                      |

| Time out                                                   |                                  | Sleep Timeout   | Sleep Timeout                          | Comm Timeout                         |

| Tone RX (HB/Fault)                                         |                                  | √               | Depends on [DIR_SEL                    | ] and [TONE_RX_EN]                   |

| Tone TX (WAKE/ SLP2ACT/<br>SHUTDOWN/ HWRST) <sup>(5)</sup> |                                  |                 |                                        | √                                    |

| Tone TX (HB)                                               |                                  |                 | Depends on [DIR_SEL]<br>and [HB_TX_EN] |                                      |

| COM embedded fault                                         |                                  |                 |                                        | [FCOMM_EN] =1                        |

| Sniff detector on COM*                                     | If host enables this feature (2) |                 |                                        |                                      |

| Wake/Shutdown Ping                                         | If VIO_UV_R = 1                  | If VIO_UV_R = 1 | If VIO_UV_R = 1                        | If VIO_UV_R = 1                      |

| SLP2ACT Ping                                               |                                  |                 | √                                      |                                      |

| NFAULT Driver                                              |                                  | √               | √                                      | √                                    |

| LFO                                                        |                                  | √               | √                                      | √                                    |

| HFO                                                        |                                  |                 |                                        | √                                    |

| INH Driver                                                 | Holds State                      | √               | INH_DIS[1:0] != 2'b11                  | INH_DIS[1:0] != 2'b11 <sup>(4)</sup> |

| CVDD/DVDD                                                  |                                  | √               | √                                      | √                                    |

| Thermal Shutdown                                           |                                  | √               | √                                      | √                                    |

- (1) Once device in SLEEP/ACTIVE, losing VIO doesn't directly cause change of state, it causes loss of data communication to MCU.

- (2) If host writes [SNIFDET\_EN] = 1 & [SNIFDET\_DIS] = 0 in ACTIVE mode, even device shuts down, enable signal is still valid. Sniff detector is enabled or disabled by a latch powered by always on power supply.

- (3) This mode is bypassed if sniff detector is not enabled, see register DEV\_CONF1.

- (4) INH can only be triggered by [INH\_SET\_GO] bit in ACTIVE.

- (5) Device does not recognize WAKE/ SLP2ACT/ SHUTDOWN/ HWRST tone sent by stack devices.

Figure 7-2. Power State Diagram

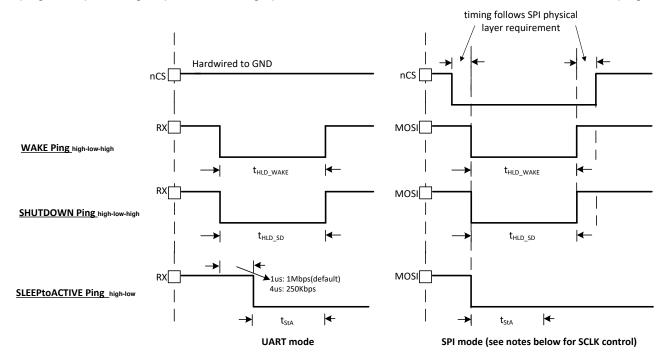

### 7.3.1.2 Pings

A "ping" is a specific signal pattern to change power mode of BQ79600-Q1. There are total of 3 different pings:

Figure 7-3. Communication Pings

- In SPI mode, ping can be sent without SCLK toggling or host can treat sending a ping like sending a series of logic '0' (drive nCS and SCLK properly, refer to SPI physical layer requirement, Section 7.3.2.1.2.2).

- Device does not transmit any tones to stack devices due to the receiving of pings.

- After sending in SHUTDOWN ping, host has to wait t<sub>SHTDN</sub> before sending another ping.

- If nCS = '1', all of the pings above are ignored by the device.

# **Note**

If device is shut down through SHUTDOWN ping (COMH RX and COML RX are disabled at next wake up), host needs to send 1st WAKE ping, wait t<sub>SU(WAKE SHUT)</sub>, and then send 2nd WAKE ping.

Table 7-2. Device Behavior when SLP2ACT Ping is Sent

|        | UART                                                       | SPI WITH SCLK TOGGLING                                            | SPI WITHOUT SCLK TOGGLING                                                |

|--------|------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------|

| ACTIVE | [COMMCLR_DET]=1, [STOP_DET] =1                             | [COMCLR_ERR]=1,<br>[COMMCLR_DET]=0                                | [FMT_ERR]=1, [COMCLR_ERR]=0,<br>[COMMCLR_DET]=0                          |

| SLEEP  | [COMMCLR_DET]=1, [STOP_DET] =0, transitions to active mode | [COMCLR_ERR]=0,<br>[COMMCLR_DET]=0, transitions to<br>active mode | [FMT_ERR]=0, [COMCLR_ERR]=0, [COMMCLR_DET]=0, transitions to active mode |

#### 7.3.1.3 SPI/UART Selection

The SPI or UART interface is selected through hardware: connect pin nUART/SPI to VIO through resistor for SPI or connect to GND for UART. Device determines UART or SPI mode every time it transitions from SHUTDOWN to ACTIVE mode. Before transitioning to ACTIVE, the mode selected is locked in. VIO has to be above V<sub>VIO LIV R</sub>. nUART/SPI pin is used as output indication of SPI RDY once in ACTIVE mode. See Section 7.3.2.1.2.2.1 for more information.

Product Folder Links: BQ79600-Q1

### 7.3.1.4 Digital Reset

Digital reset is when digital core of the device in reset mode. It is not a power mode. Once device comes out of digital reset, [DRST] bit is set to '1', registers that are not included in NVM are set to RESET VALUE, registers included in NVM would be NVM program value. There are several conditions in which the device will go through a digital reset:

- A WAKE ping is received.

- The CONTROL1 [SOFT RESET] = 1 command is sent in ACTIVE mode.

- Power supply faults. DVDD UV or CVDD UV is detected.

- A HFO or LFO watchdog fault will reset the digital.

# 7.3.1.5 Power Mode in BMS System

It is recommended to follow the power state combinations below to save system level power.

| iable i di i di di indad de indination danimary |            |                 |  |  |

|-------------------------------------------------|------------|-----------------|--|--|

| STACK MONITORING IC                             | BQ79600-Q1 | COMMENT         |  |  |

| ACTIVE                                          | ACTIVE     | Recommended     |  |  |

| SLEEP                                           | SLEEP      | Recommended     |  |  |

| SLEEP                                           | SHUTDOWN   | Recommended     |  |  |

| SHUTDOWN                                        | SHUTDOWN   | Recommended     |  |  |

| Other combinations                              |            | Not recommended |  |  |

# 7.3.1.6 Power Supply

This section provides an overview of each supplies for both user cases: without using Reverse Wakeup and with using Reverse Wakeup. See the Section 7.3.6 for diagnostic control and fault detection on the power supplies block.

**Table 7-4. Power Supply Summary**

| NAME    | W/O REVERSE WAKEUP USER CASE                                                                                             | W/ REVERSE WAKEUP USER CASE                                                                                                                                                                                                                         |  |

|---------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VIO     | This supply is powered by regulated 3.3V or 5V from SBC (F                                                               | PMIC), it powers UART/SPI interface pins.                                                                                                                                                                                                           |  |

| BAT     | This supply is powered by regulated 5V from SBC (PMIC).                                                                  | This supply is powered by unregulated 12V battery.                                                                                                                                                                                                  |  |

| AVAOREF | This supply is generated from VBAT. It is always on if VBAT block.                                                       | exists. It powers REFSYS and Power mode control                                                                                                                                                                                                     |  |

| AVDDREF | This supply is derived from AVAOREF. AVDDREF and AVAOREF are connected by a switch, the switch is open in SHUTDOWN mode. |                                                                                                                                                                                                                                                     |  |

| DVDD    | This supply is generated by the internal DVDD LDO. It is the from CVDD and generates a nominal 1.8V. It will not be used |                                                                                                                                                                                                                                                     |  |

| CVDD    | This supply is powered by regulated 5V from SBC(PMIC). It is the supply for daisy chain interface.                       | This supply is generated by the internal CVDD LDO. It is the supply for the daisy chain interface (or vertical interface, VIF). It takes the input voltage from VBAT and generates a nominal 5V. It will not be used to power any external circuit. |  |

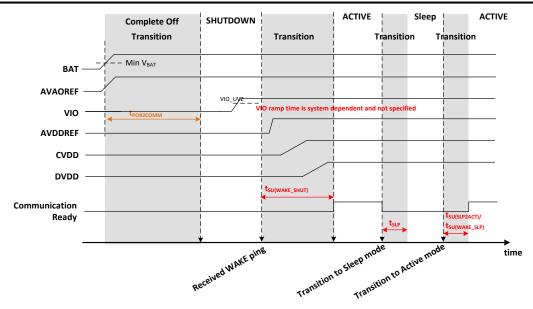

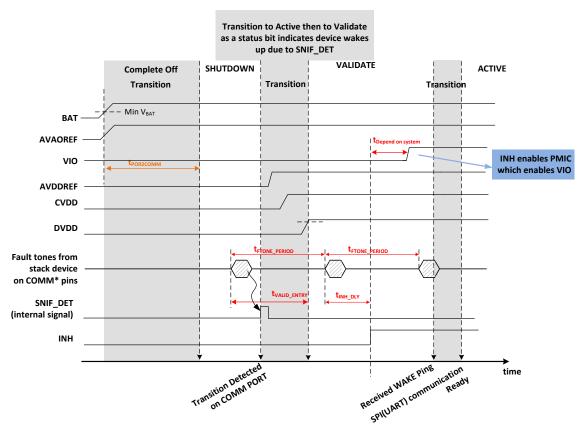

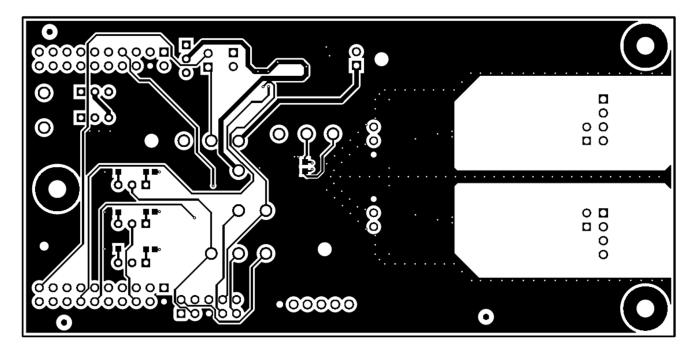

### 7.3.1.7 Shutdown

Power Mode Transition Example

Figure 7-4. Shutdown -> Active -> Sleep -> Active

Figure 7-5. Shutdown -> Validate -> Active

Submit Document Feedback

Copyright © 2020 Texas Instruments Incorporated

#### 7.3.2 Communication

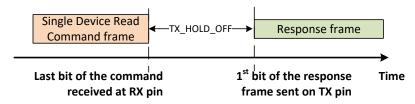

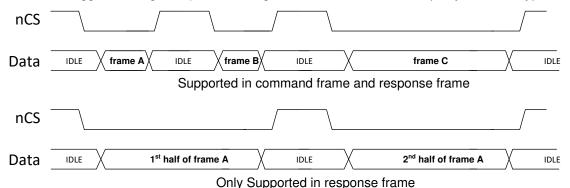

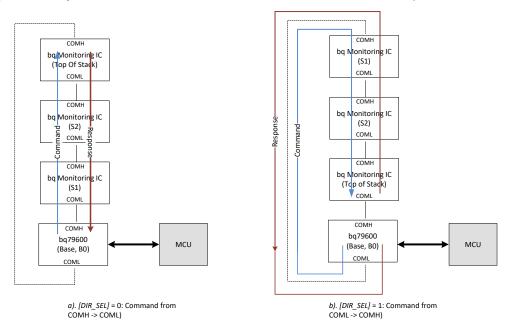

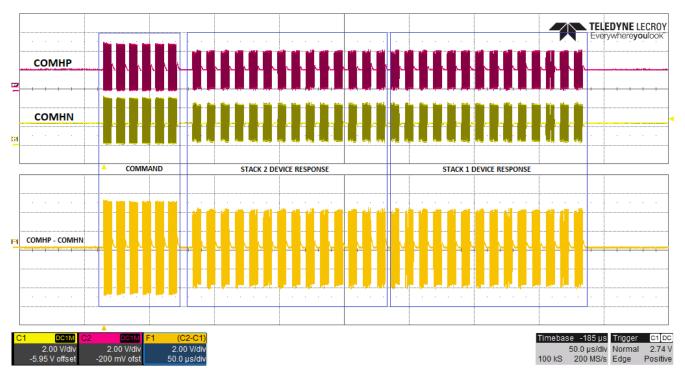

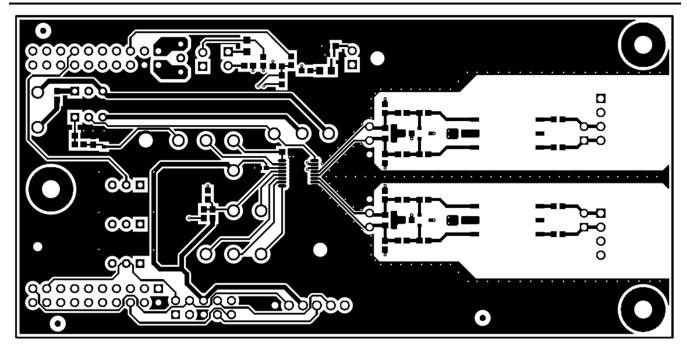

This device is used as a bridge (base) device in daisy chain configuration, as showed in figure below. It communicates with MCU through UART or SPI and communicates with stack devices through daisy chain (proprietary interface). MCU always initiates communication with a Command frame. In the system, BQ devices would never send data back to MCU before MCU requests. And MCU needs to wait all expected response frames before sending next command frame. Thus, communication scenarios can be put into 2 categories:

- MCU sends Write Command frames to BQ devices. Write Command frames don't incur Response frame.

- MCU sends one Read Command frame to BQ devices and waits till all Response frames are received.

Figure 7-6. System Communication Diagram

Rest of the section talks about how data and tone are communicated among host, bridge, and stack devices: Section 7.3.2.1 (Section 7.3.2.1.1 and Section 7.3.2.1.2 protocol), Section 7.3.2.2. It also talks about Section 7.3.2.3 and Section 7.3.2.4.

### 7.3.2.1 Data Communication Protocol

**INIT** [7:0]

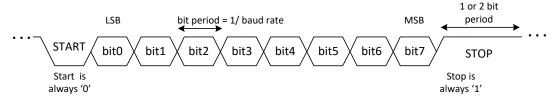

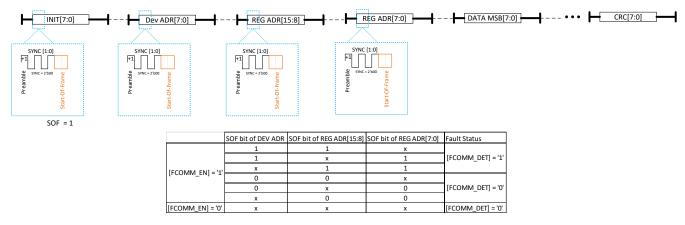

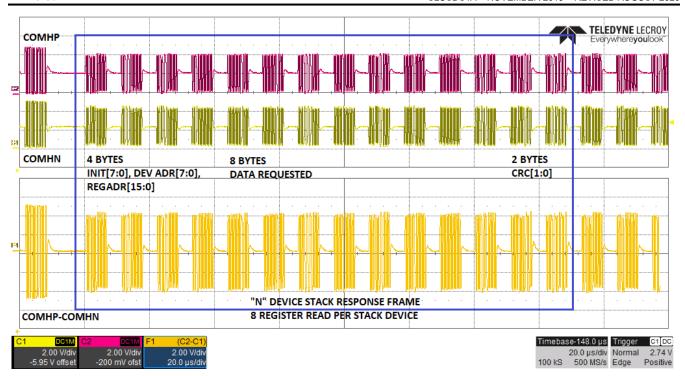

#### 7.3.2.1.1 Frame Layer

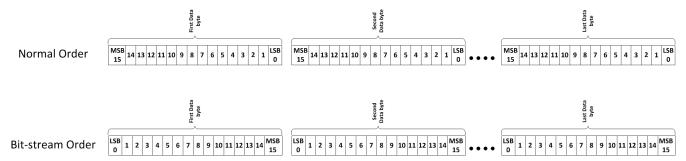

The communication frame is defined in figure below. It is made up of 5 types of information: initialization character (INIT), device address characters, register address character, data character(s) and CRC characters. Each character is transmitted at UART/ SPI/ Daisy Chain physical level, whose format is defined in following Section 7.3.2.1.2 section. There are 3 types of transaction frames: **Read Command Frames**, **Write Command Frames** and **Response Frames**. They follow the structure in the figure below.

DATA byte(s)

CRC [15:0]

DEV ADR [7:0] | REG ADR [15:0]

|            | Frames                                 | INIT             | DEV ADR                      | REG ADR          | DATA                           | CRC |

|------------|----------------------------------------|------------------|------------------------------|------------------|--------------------------------|-----|

| Read       | Single Device Read                     | Always 0x80      | Υ                            | Υ                | # of byte requested (max value | Υ   |

| Command    | Stack Read                             | Always 0xA0      | N                            | Υ                | 127, meaning 128)              | Υ   |

| Frame      | Broadcast Read                         | Always 0xC0      | N                            | Υ                |                                | Υ   |

| Write      | Single Device Write                    | Υ                | Υ                            | Υ                | Actual payload (1-8 bytes)     | Υ   |

| Command    | Stack Write                            | Υ                | N                            | Υ                | 1                              | Υ   |

| Frame      | Broadcast Write                        | Υ                | N                            | Υ                | 1                              | Υ   |

|            | Broadcast Write<br>Reverse (5)         | Y <sup>(5)</sup> | N                            | Y <sup>(5)</sup> | Y <sup>(5)</sup>               | Υ   |

| Response F | e Frame Y Y Y Actual payload (1-128 by |                  | Actual payload (1-128 bytes) | Υ                |                                |     |

Figure 7-7. Command/Response Frame Structure

# Notes:

- When BQ79600-Q1 is used as bridge device, to read BQ devices information, host SHALL NOT use

Broadcast Read command but only Single Device Read or Stack Read. The reason is BQ79600-Q1 register

address does not overlap with stack devices, it would only return 0x00 to Broadcast Read command.

- For Stack Read command, the response is broken into individual response frames from each device addressed. Each device (address N) in the stack waits until the device above it (address N+1) responds before device N sends its own data back.

- After a read command frame is transmitted, the host must wait for all expected responses to return (or timeout: t<sub>WAIT\_READ\_MAX</sub>) before initiating a new command frame.

- A response frame is not mandatary. A response frame is only received after a read command frame.

- Broadcast Write Reverse command frame should only be used to config [DIR\_SEL] bit, not for any other purposes. INIT byte is 0xE0, Reg address byte is 0x309 (BQ7961X-Q1), data byte is 0x80.

- Bytes received on COMH/COML are NOT propagated up to the stack; while bytes received on the SPI/UART

are propagated to COMH or COML depending on [DIR\_SEL].

- Even if there is a byte error, data is still forwarded from VIF to SPI (buffer)/UART; if there is a byte error, data doesn't forward from SPI/UART to VIF.

|   |     |            | Command Frame                                                            |               | Response Frame                  |

|---|-----|------------|--------------------------------------------------------------------------|---------------|---------------------------------|

|   | Bit | Bit Name   | Description                                                              | Bit Name      | Description                     |

|   | 7   | FRAME_TYPE | 1 = Command Frame                                                        | FRAME_TYPE    | 0 = Response<br>Frame           |

|   | 6   | REQ_TYPE   | 000 = Single Device Read<br>001 = Single Device Write                    | RESPONSE_BYTE | Number of the data<br>bytes     |

|   | 5   |            | 010 = Stack Read<br>011 = Stack Write<br>100 = Broadcast Read            |               | 0x00 = 1 byte<br>0x01 = 2 bytes |

| Ħ | 4   |            | 101 = Broadcast Write<br>110 = Broadcast Write Reverse<br>111 = RSVD (1) |               | :<br>0x7F = 128 bytes           |

| = | 3   | RSVD       | RSVD. This bit is ignored                                                |               |                                 |

|   | 2   | DATA_SIZE  | Number of data bytes, excluding                                          |               |                                 |

|   | 1   |            | device address, register<br>address or CRC                               |               |                                 |

|   | 0   |            | 000 = 1 byte<br>001 = 2 bytes<br>:<br>111 = 8 bytes                      |               |                                 |

|     |     |                | Command/Response Frame                         |

|-----|-----|----------------|------------------------------------------------|

|     | Bit | Bit Name       | Description                                    |

|     | 7   | RSVD           | Should always write "0"                        |

| DEV | 6   | RSVD           | Should always write "0"                        |

| ΒĀ  | 5:0 | Device Address | Set the device address range from 0x00 to 0x3F |

|     |     |                |                                                |

|              |     |                           | Command/Response Frame                      |

|--------------|-----|---------------------------|---------------------------------------------|

|              | Bit | Bit Name                  | Description                                 |

| REG_<br>ADR_ | 7:0 | Register<br>Address (MSB) | Target or beginning of the register address |

| RE           | 7:0 | Register<br>Address (LSB) | Target or beginning of the register address |

|     | Bit | Bit Name      | Description  |  |  |

|-----|-----|---------------|--------------|--|--|

| A   | 7:0 | Data Byte[0]  | Data Byte[0] |  |  |

| AT, |     |               |              |  |  |

| О   | 7:0 | Data Byte [n] | Data Byte[n] |  |  |

|     |     | Command/Response Frame |                                                                                                                                         |

|-----|-----|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|     | Bit | Bit Name               | Description                                                                                                                             |

| свс | 7:0 | CRC (MSB)              | CRC-16-IBM polynomial (x16<br>+ x15 + x2 + 1 or<br>11000000000000101)<br>with 0xFFFF initialization                                     |

| ö   | 7:0 | CRC (LSB)              | CRC-16-IBM polynomial (x <sub>16</sub><br>+ x <sub>15</sub> + x <sub>2</sub> + 1 or<br>11000000000000101)<br>with 0xFFFF initialization |

Figure 7-8. Frame Byte Definition

### Notes:

- INIT character: (1) No function to this selection, but this selection sets the [RC IERR] error flag.

- Device Address character: Bit 6 and 7 are reserved; 0x4F to 0xFF is decoded as 0x3F by device.

- Register Address characters: Register addresses are two bytes in length. They indicate the targeted register address on a single byte read/write, or the beginning of the register address on a multi-byte read/write. If an invalid register address is set on a write command, the command will be ignored. If an invalid register address is set on a read command, a 0x00 will be returned as response.

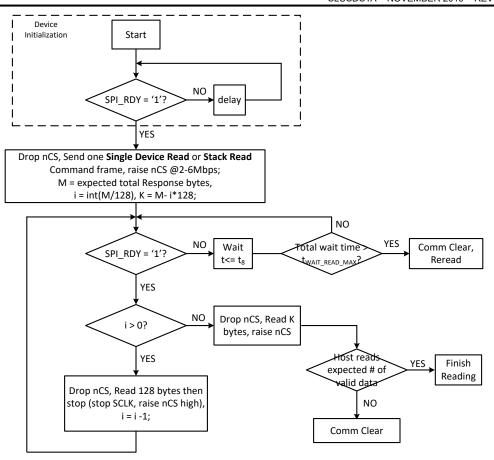

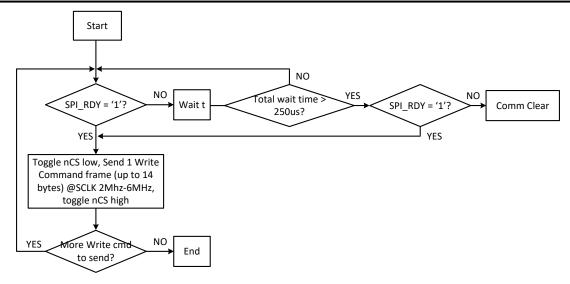

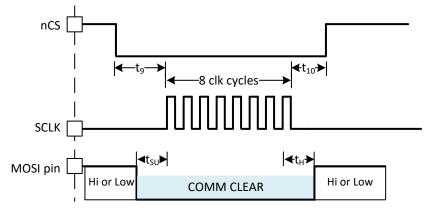

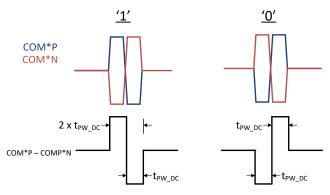

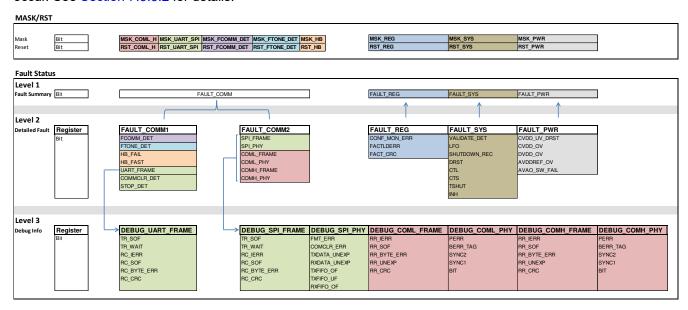

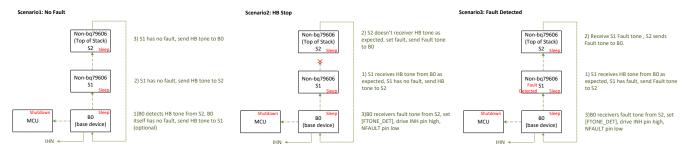

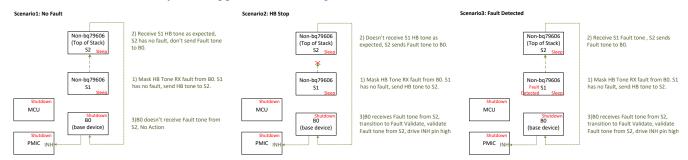

- · Data characters can be: