bq51010B

SLUSBB8A - DECEMBER 2012-REVISED JUNE 2016

# bg51010B Highly Integrated Wireless Receiver Qi (WPC v1.1) Compliant Power Supply

#### 1 Features

- Integrated Wireless Power Supply Receiver Solution With a 7-V Regulated Supply

- 93% Overall Peak AC-DC Efficiency

- Full Synchronous Rectifier

- WPC v1.1 Compliant Communication Control

- Output Voltage Conditioning

- Only IC Required Between RX Coil and 7-V

- WPC v1.1 Compliant (FOD Enabled) Highly Accurate Current Sense

- Dynamic Rectifier Control for Improved Load Transient Response

- Dynamic Efficiency Scaling for Optimized Performance Over Wide Range of Output Power

- Adaptive Communication Limit for Robust Communication

- Supports 20-V Maximum Input

- Low-power Dissipative Rectifier Overvoltage Clamp  $(V_{OVP} = 15 \text{ V})$

- Thermal Shutdown

- Multifunction NTC and Control Pin for Temperature Monitoring, Charge Complete and Fault Host Control

# 2 Applications

- WPC v1.1 Compliant Receivers

- Cell Phones and Smart Phones

- Headsets

- **Digital Cameras**

- Portable Media Players

- Hand-Held Devices

# 3 Description

The bq51010B is a family of advanced, flexible, secondary-side devices for wireless power transfer in portable applications. The bq51010B devices provide the AC-DC power conversion and regulation while integrating the digital control required to comply with the Qi v1.1 communication protocol. Together with the bq50xxx primary-side controller, the bq51010B enables a complete contact-less power transfer system for a wireless power supply solution. Global feedback is established from the secondary to the primary to control the power transfer process using the Qi v1.1 protocol.

The bq51010B devices integrate a low resistance synchronous rectifier, low-dropout regulator, digital control, and accurate voltage and current loops to ensure high efficiency and low power dissipation.

The bq51010B also includes a digital controller that can calculate the amount of power received by the mobile device within the limits set by the WPC v1.1 standard. The controller will then communicate this information to the transmitter to allow the transmitter to determine if a foreign object is present within the magnetic interface and introduces a higher level of safety within magnetic field. This Foreign Object Detection (FOD) method is part of the requirements under the WPC v1.1 specification.

#### Device Information (1)

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| bq51010B    | DSBGA (28) | 1.90 mm × 3.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

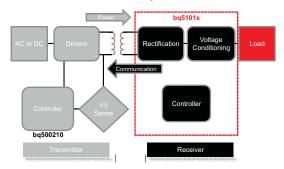

#### Wireless Power Consortium (WPC or Qi) Inductive **Power System**

#### **Table of Contents**

| 1 | Features 1                           |    | 8.4 Device Functional Modes                       | 23               |

|---|--------------------------------------|----|---------------------------------------------------|------------------|

| 2 | Applications 1                       | 9  | Application and Implementation                    | <mark>2</mark> 4 |

| 3 | Description 1                        |    | 9.1 Application Information                       | 24               |

| 4 | Revision History2                    |    | 9.2 Typical Applications                          | <mark>2</mark> 4 |

| 5 | Device Comparison Tables3            | 10 | Power Supply Recommendations                      | 31               |

| 6 | Pin Configuration and Functions3     | 11 | Layout                                            | 31               |

| 7 | Specifications5                      |    | 11.1 Layout Guidelines                            | 31               |

| • | 7.1 Absolute Maximum Ratings 5       |    | 11.2 Layout Example                               | 31               |

|   | 7.2 ESD Ratings                      | 12 | Device and Documentation Support                  | 32               |

|   | 7.3 Recommended Operating Conditions |    | 12.1 Device Support                               | 32               |

|   | 7.4 Thermal Information              |    | 12.2 Documentation Support                        | 32               |

|   | 7.5 Electrical Characteristics       |    | 12.3 Receiving Notification of Documentation Upda | ates 32          |

|   | 7.6 Typical Characteristics          |    | 12.4 Community Resources                          | <mark>32</mark>  |

| 8 | Detailed Description 10              |    | 12.5 Trademarks                                   | 32               |

| • | 8.1 Overview 10                      |    | 12.6 Electrostatic Discharge Caution              | 32               |

|   | 8.2 Functional Block Diagram11       |    | 12.7 Glossary                                     | 32               |

|   | 8.3 Feature Description              |    | Mechanical, Packaging, and Orderable Information  | 32               |

# 4 Revision History

# Changes from Original (December 2012) to Revision A

Page

- Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section

Product Folder Links: bq51010B

Submit Documentation Feedback

# 5 Device Comparison Tables

| DEVICE   | FUNCTION                             | V <sub>OUT</sub> (V <sub>BAT-REG</sub> ) | PROTOCOL              | MAXIMUM<br>P <sub>OUT</sub> | I <sup>2</sup> C |

|----------|--------------------------------------|------------------------------------------|-----------------------|-----------------------------|------------------|

| bq51003  | Wireless receiver                    | 5 V                                      | Qi v1.1               | 2.5 W                       | No               |

| bq51013B | Wireless receiver                    | 5 V                                      | Qi v1.1               | 5 W                         | No               |

| bq51010B | Wireless receiver                    | 7 V                                      | Qi v1.1               | 5 W                         | No               |

| bq51020  | Wireless receiver                    | 4.5 to 8 V                               | Qi v1.1               | 5 W                         | No               |

| bq51021  | Wireless receiver                    | 4.5 to 8 V                               | Qi v1.1               | 5 W                         | Yes              |

| bq51221  | Dual mode wireless receiver          | 4.5 to 8 V                               | Qi v1.1, PMA          | 5 W                         | Yes              |

| bq51025  | Wireless receiver                    | 4.5 to 10 V                              | Qi v1.1 (in 5 W mode) | 10 W                        | Yes              |

| bq51020B | Wireless receiver and direct charger | 4.2 V                                    | Qi v1.1               | 5 W                         | No               |

| bq51051B | Wireless receiver and direct charger | 4.35 V                                   | Qi v1.1               | 5 W                         | No               |

| bq51052B | Wireless receiver and direct charger | 4.4 V                                    | Qi v1.1               | 5 W                         | No               |

**Table 1. Device Options**

| DEVICE   | FUNCTION         | WPC<br>VERSION | V <sub>RECT-OVP</sub> | V <sub>OUT-(REG)</sub> | OVER<br>CURRENT<br>SHUTDOWN | AD-OVP   | TERMINATION | COMMUNICATION<br>CURRENT LIMIT <sup>(1)(2)</sup> |

|----------|------------------|----------------|-----------------------|------------------------|-----------------------------|----------|-------------|--------------------------------------------------|

| bq51010B | 7-V power supply | v1.1           | 15 V                  | 7 V                    | Disabled                    | Disabled | Disabled    | Adaptive + 1s Hold-Off                           |

- (1) Enabled if EN2 is low and disabled if EN2 is high

- (2) Communication current limit is disabled for 1 second at start-up

# 6 Pin Configuration and Functions

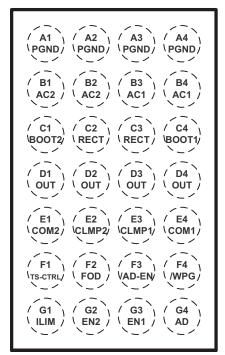

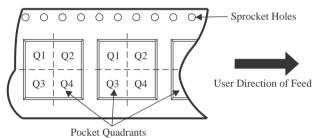

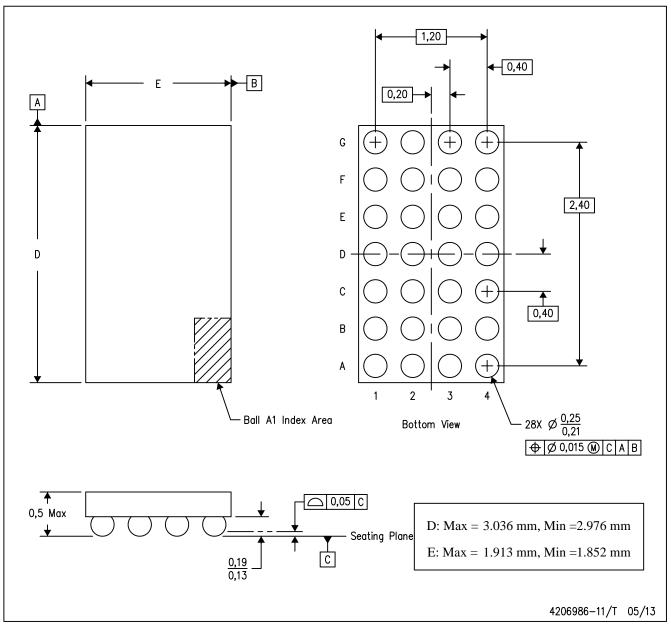

YFP Package 28-Pin DSBGA Top View

#### **Pin Functions**

|         | PIN               | 1/0 | DECORPORA                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME    | NO.               | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| AC1     | B3, B4            | ı   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| AC2     | B1, B2            | I   | AC input from receiver coil antenna.                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| AD      | G4                | 1   | Connect this pin to the wired adapter input. When a voltage is applied to this pin wireless charging is disabled and AD_EN is driven low. Connect to GND through a 1-µF capacitor. If unused, capacitor is not required and must be grounded directly.                                                                                                                                                                                                                            |  |  |  |

| AD-EN   | F3                | 0   | Push-pull driver for external PFET connecting AD and OUT. This node is pulled to the higher of OUT and AD when turning off the external FET. This voltage tracks approximately 4 V below AD when voltage is present at AD and provides a regulated VSG bias for the external FET. Float this pin if unused.                                                                                                                                                                       |  |  |  |

| BOOT1   | C4                | 0   | Bootstrap capacitors for driving the high-side FETs of the synchronous rectifier. Connect a                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| BOOT2   | C1                | 0   | 10-nF ceramic capacitor from BOOT1 to AC1 and from BOOT2 to AC2.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| CLMP1   | E3                | 0   | Open drain FETs are used for a non-power dissipative overvoltage AC clamp protection.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| CLMP2   | E2                | 0   | When the RECT voltage goes above 15 V, both switches is turned on and the capacitors acts as a low impedance to protect the IC from damage. If used, Clamp1 is required to be connected to AC1, and Clamp2 is required to be connected to AC2 through 0.47-µF capacitors.                                                                                                                                                                                                         |  |  |  |

| COM1    | E4                | 0   | Open-drain output used to communicate with primary by varying reflected impedance.                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| COM2    | E1                | 0   | Connect through a capacitor to either AC1 or AC2 for capacitive load modulation (COM2 must be connected to the alternate AC1 or AC2 pin). For resistive modulation connect COM1 and COM2 to RECT through a single resistor; connect through separate capacitors for capacitive load modulation.                                                                                                                                                                                   |  |  |  |

| EN1     | G3                | I   | Inputs that allow user to enable or disable wireless and wired charging <en1 en2="">:</en1>                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| EN2     | G2                | I   | <00> wireless charging is enabled unless AD voltage > 3.6 V <01> <u>Dynamic communication current limit disabled</u> <10> AD-EN pulled low, wireless charging disabled <11> wired and wireless charging disabled.                                                                                                                                                                                                                                                                 |  |  |  |

| FOD     | F2                | I   | Input for the received power measurement. Connect to GND with a 140- $\Omega$ resistor. See the FOD section for more detail.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ILIM    | G1                | I/O | Programming pin for the over current limit. Connect external resistor to VSS. Size $R_{\rm ILIM}$ with the following equation: $R_{\rm ILIM} = 314 \ I_{\rm IMAX}$ where $I_{\rm MAX}$ is the expected maximum output current of the wireless power supply. The hardware current limit (IILIM) is 20% greater than IMAX or 1.2 x $I_{\rm IMAX}$ . If the supply is meant to operate in current limit use: $R_{\rm ILIM} = 314 \ I_{\rm ILIM}$ , $R_{\rm ILIM} = R1 + R_{\rm FOD}$ |  |  |  |

| OUT     | D1, D2,<br>D3, D4 | 0   | Output pin, delivers power to the load.                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PGND    | A1, A2,<br>A3, A4 | _   | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| RECT    | C2, C3            | 0   | Filter capacitor for the internal synchronous rectifier. Connect a ceramic capacitor to PGND. Depending on the power levels, the value may be 4.7 $\mu$ F to 22 $\mu$ F.                                                                                                                                                                                                                                                                                                          |  |  |  |

| TS/CTRL | F1                | I   | Must be connected to ground through a resistor. If an NTC function is not desired connect to GND with a $10-k\Omega$ resistor. As a CTRL pin pull to ground to send end power transfer (EPT) fault to the transmitter or pull-up to an internal rail (that is, 1.8 V) to send EPT termination to the transmitter. Note that a 3-state driver must be used to interface this pin (see the 3-State Driver Recommendations For the TS-CTRL Pin section for further description)      |  |  |  |

| WPG     | F4                | 0   | Open-drain output – Active when the output of the wireless power supply is enabled.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       |                                            | MIN  | MAX | UNIT   |

|---------------------------------------|--------------------------------------------|------|-----|--------|

|                                       | AC1, AC2                                   | -0.8 | 20  |        |

|                                       | RECT, COM1, COM2, OUT, WPG, CLAMP1, CLAMP2 | -0.3 | 20  |        |

| Input voltage                         | AD, AD-EN                                  | -0.3 | 30  | V      |

|                                       | BOOT1, BOOT2                               | -0.3 | 26  |        |

|                                       | EN1, EN2, TERM, FOD, TS-CTRL, ILIM         | -0.3 | 7   |        |

| Input current                         | AC1, AC2                                   |      | 1.5 | A(RMS) |

| Output current                        | OUT                                        |      | 750 | mA     |

| Output sink surrent                   | WPG                                        |      | 15  | mA     |

| Output sink current                   | COM1, COM2                                 |      | 1   | А      |

| Junction temperature, T <sub>J</sub>  |                                            | -40  | 150 | °C     |

| Storage temperature, T <sub>stg</sub> |                                            | -65  | 150 | °C     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                            |                                                                     |                                                        | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|-------|------|

| V                                          | Floatroatatio dia abarra                                            | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | \/   |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500                                                   | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                    |       | MIN | MAX | UNIT |

|--------------------|------------------------------------|-------|-----|-----|------|

| $V_{RECT}$         | Voltage range                      | RECT  | 4   | 10  | V    |

| I <sub>RECT</sub>  | Current through internal rectifier | RECT  |     | 1   | Α    |

| I <sub>OUT</sub>   | Output current                     | OUT   |     | 750 | mA   |

| I <sub>AD-EN</sub> | Sink current                       | AD-EN |     | 1   | mA   |

| I <sub>COMM</sub>  | COMM sink current                  | COMM  |     | 400 | mA   |

| $T_{J}$            | Junction temperature               |       | 0   | 125 | °C   |

#### 7.4 Thermal Information

|                      |                                              | bq51010B    |      |

|----------------------|----------------------------------------------|-------------|------|

|                      | THERMAL METRIC (1)                           | YFP (DSBGA) | UNIT |

|                      |                                              | 28 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 58.9        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.2         | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 9.1         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 1.4         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 8.9         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> All voltages are with respect to the VSS terminal, unless otherwise noted.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

over operating free-air temperature range, 0°C to 125°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                | TEST CONDITIONS                                                                                               | MIN  | TYP                   | MAX  | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------|-----------------------|------|------|

| UVLO                   | Undervoltage lockout                                                                                                     | V <sub>RECT</sub> = 0 V to 3 V                                                                                | 2.6  | 2.7                   | 2.8  | V    |

| \/                     | Hysteresis on UVLO                                                                                                       | V <sub>RECT</sub> = 3 V to 2 V                                                                                |      | 250                   |      | mV   |

| V <sub>HYS</sub>       | Hysteresis on OVP                                                                                                        | V <sub>RECT</sub> = 16 V to 5 V                                                                               |      | 150                   |      | IIIV |

| V <sub>RECT</sub>      | Input overvoltage threshold                                                                                              | V <sub>RECT</sub> = 5 V to 16 V                                                                               | 14.5 | 15                    | 15.5 | V    |

|                        | Dynamic V <sub>RECT</sub> threshold 1                                                                                    | $I_{LOAD} < 0.1 \times I_{IMAX} (I_{LOAD} rising)$                                                            |      | 9.08                  |      |      |

|                        | Dynamic V <sub>RECT</sub> threshold 2                                                                                    | $0.1 \times I_{\text{IMAX}} < I_{\text{LOAD}} < 0.2 \times I_{\text{IMAX}}$ ( $I_{\text{LOAD}}$ rising)       |      | 8.28                  |      |      |

| V <sub>RECT-REG</sub>  | Dynamic V <sub>RECT</sub> threshold 3                                                                                    | $0.2 \times I_{IMAX} < I_{LOAD} < 0.4 \times I_{IMAX}$ ( $I_{LOAD}$ rising)                                   |      | 7.53                  |      | V    |

|                        | Dynamic V <sub>RECT</sub> threshold 4                                                                                    | $I_{LOAD} > 0.4 \times I_{IMAX} (I_{LOAD} rising)$                                                            |      | 7.11                  |      |      |

|                        | V <sub>RECT</sub> tracking                                                                                               | In current limit voltage above V <sub>OUT</sub>                                                               |      | $V_0 + 0.25$          |      |      |

| I <sub>LOAD</sub>      | $I_{LOAD}$ hysteresis for dynamic $V_{RECT}$ thresholds as a percentage of $I_{ILIM}$                                    | I <sub>LOAD</sub> falling                                                                                     |      | 4%                    |      |      |

| V <sub>RECT-DPM</sub>  | Rectifier undervoltage protection, restricts I <sub>OUT</sub> at V <sub>RECT-DPM</sub>                                   |                                                                                                               | 3    | 3.1                   | 3.2  | V    |

| V <sub>RECT-REV</sub>  | Rectifier reverse voltage protection at the output                                                                       | $V_{RECT-REV} = V_{OUT} - V_{RECT},$<br>$V_{OUT} = 10 \text{ V}$                                              |      | 8                     | 9    | V    |

| QUIESCENT              | CURRENT                                                                                                                  |                                                                                                               |      |                       |      |      |

|                        | Active chip quiescent current consumption                                                                                | $I_{LOAD} = 0 \text{ mA}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$                                 |      | 8                     | 10   | )    |

| I <sub>RECT</sub>      | from RECT                                                                                                                | $I_{LOAD} = 300 \text{ mA},$<br>$0^{\circ}\text{C} \leq T_{J} \leq 85^{\circ}\text{C}$                        |      | 2                     | 3    | mA   |

| I <sub>OUT</sub>       | Quiescent current at the output when wireless power is disabled (standby)                                                | V <sub>OUT</sub> = 7 V, 0°C ≤ T <sub>J</sub> ≤ 85°C                                                           |      | 28                    | 40   | μΑ   |

| I <sub>LIM</sub> SHORT |                                                                                                                          | 1                                                                                                             |      |                       |      |      |

| R <sub>ILIM</sub>      | Highest value of I <sub>LIM</sub> resistor considered a fault (short). Monitored for I <sub>OUT</sub> > 100 mA           | $R_{ILIM}$ = 200 $\Omega$ to 50 $\Omega$ . $I_{OUT}$ latches off, cycle power to reset                        |      |                       | 120  | Ω    |

| t <sub>DGL</sub>       | Deglitch time transition from I <sub>LIM</sub> short to I <sub>OUT</sub> disable                                         |                                                                                                               |      | 1                     |      | ms   |

| I <sub>LIM_SC</sub>    | $I_{\text{LIM-SHORT,OK}}$ enables the $I_{\text{LIM}}$ short comparator when $I_{\text{OUT}}$ is greater than this value | I <sub>LOAD</sub> = 0 mA to 200 mA                                                                            | 110  | 145                   | 165  | mA   |

|                        | Hysteresis for I <sub>LIM-SHORT,OK</sub> comparator                                                                      | I <sub>LOAD</sub> = 0 mA to 200 mA                                                                            |      | 30                    |      |      |

| I <sub>OUT</sub>       | Maximum output current limit, C <sub>L</sub>                                                                             | Maximum I <sub>LOAD</sub> that is delivered for 1 ms when I <sub>LIM</sub> is shorted                         |      |                       | 2.45 | Α    |

| OUTPUT                 |                                                                                                                          |                                                                                                               |      |                       |      |      |

| V                      | Pagulated output valtage                                                                                                 | $I_{LOAD} = 750 \text{ mA}$                                                                                   | 6.9  | 6.96                  | 7.02 | V    |

| V <sub>OUT-REG</sub>   | Regulated output voltage                                                                                                 | I <sub>LOAD</sub> = 10 mA                                                                                     | 6.9  | 6.95                  | 7.05 | V    |

| K <sub>ILIM</sub>      | Current programming factor for hardware protection                                                                       | $R_{LIM} = K_{ILIM} / I_{ILIM}$ , where $I_{ILIM}$ is the hardware current limit. $I_{OUT} = 750$ mA          | 303  | 314                   | 322  | ΑΩ   |

| K <sub>IMAX</sub>      | Current programming factor for the nominal operating current                                                             | $I_{IMAX} = K_{IMAX} / R_{LIM}$ , where $I_{MAX}$ is the maximum normal operating current. $I_{OUT} = 750$ mA |      | 262                   |      | ΑΩ   |

| I <sub>OUT</sub>       | Current limit programming range                                                                                          |                                                                                                               |      |                       | 1.5  | Α    |

|                        | Output Park days a M/DO                                                                                                  | I <sub>OUT</sub> > 300 mA                                                                                     |      | I <sub>OUT</sub> + 50 |      |      |

| I <sub>COMM</sub>      | Current limit during WPC communication                                                                                   | I <sub>OUT</sub> < 300 mA                                                                                     | 343  | 378                   | 425  | mA   |

| t <sub>HOLD</sub>      | Hold off time for the communication current limit during start-up                                                        |                                                                                                               |      | 1                     |      | S    |

# **Electrical Characteristics (continued)**

over operating free-air temperature range, 0°C to 125°C (unless otherwise noted)

|                        | PARAMETER                                                                                                                            | TEST CONDITIONS                                                              | MIN   | TYP   | MAX   | UNIT                 |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|-------|----------------------|

| TS / CTRL              |                                                                                                                                      |                                                                              |       |       |       |                      |

| V <sub>TS</sub>        | Internal TS bias voltage                                                                                                             | I <sub>TS-Bias</sub> < 100 μA (periodically driven see t <sub>TS-CTRL)</sub> | 2     | 2.2   | 2.4   | V                    |

| \ /                    | Rising threshold                                                                                                                     | V <sub>TS</sub> = 50% to 60%                                                 | 56.5% | 58.7% | 60.8% |                      |

| $V_{COLD}$             | Falling hysteresis                                                                                                                   | V <sub>TS</sub> = 60% to 50%                                                 |       | 2%    |       | $V_{TS-Bias}$        |

|                        | Falling threshold                                                                                                                    | V <sub>TS</sub> = 20% to 15%                                                 | 18.5% | 19.6% | 20.7% |                      |

| $V_{HOT}$              | Rising hysteresis                                                                                                                    | V <sub>TS</sub> = 15% to 20%                                                 |       | 3%    |       | $V_{TS\text{-Bias}}$ |

| .,                     | CTRL pin threshold for a high                                                                                                        | V <sub>TS/CTRL</sub> = 50 mV to 150 mV                                       | 80    | 100   | 130   |                      |

| $V_{CTRL}$             | CTRL pin threshold for a low                                                                                                         | V <sub>TS/CTRL</sub> = 150 mV to 50 mV                                       | 50    | 80    | 100   | mV                   |

| t <sub>TS-CTRL</sub>   | Time VTS-Bias is active when TS measurements occur                                                                                   | Synchronous to the communication period                                      |       | 24    |       | ms                   |

| t <sub>TS</sub>        | Deglitch time for all TS comparators                                                                                                 |                                                                              |       | 10    |       | ms                   |

| R <sub>TS</sub>        | Pullup resistor for the NTC network. Pulled up to the voltage bias                                                                   |                                                                              | 18    | 20    | 22    | kΩ                   |

| THERMAL PR             | ROTECTION                                                                                                                            |                                                                              |       |       |       |                      |

| _                      | Thermal shutdown temperature                                                                                                         |                                                                              |       | 155   |       | ۰.                   |

| $T_J$                  | Thermal shutdown hysteresis                                                                                                          |                                                                              |       | 20    |       | °C                   |

| OUTPUT LOG             | GIC LEVELS ON WPG                                                                                                                    |                                                                              |       |       | L     |                      |

| V <sub>OL</sub>        | Open drain WPG pin                                                                                                                   | I <sub>SINK</sub> = 5 mA                                                     |       |       | 500   | mV                   |

| l <sub>OFF</sub>       | WPG leakage current when disabled                                                                                                    | V WPG = 20 V                                                                 |       |       | 1     | μA                   |

| COMM PIN               |                                                                                                                                      |                                                                              |       |       | *     |                      |

| R <sub>DS(ON)</sub>    | COM1 and COM2                                                                                                                        | V <sub>RECT</sub> = 2.6 V                                                    |       | 1.5   |       | Ω                    |

| f <sub>COMM</sub>      | Signaling frequency on COMM pin                                                                                                      |                                                                              |       | 2     |       | Kb/s                 |

| I <sub>OFF</sub>       | Comm pin leakage current                                                                                                             | V <sub>COM1</sub> = 20 V, V <sub>COM2</sub> = 20 V                           |       |       | 1     | μA                   |

| CLAMP PIN              |                                                                                                                                      |                                                                              | 1     |       | '     |                      |

| R <sub>DS(ON)</sub>    | Clamp1 and Clamp2                                                                                                                    |                                                                              |       | 0.8   |       | Ω                    |

| ADAPTER EN             | IABLE                                                                                                                                |                                                                              |       |       |       |                      |

| v-                     | V <sub>AD</sub> rising threshold voltage. EN-UVLO                                                                                    | V <sub>AD</sub> = 0 V to 5 V                                                 | 3.5   | 3.6   | 3.8   | V                    |

| V AD-EN                | V <sub>AD-EN</sub> hysteresis, EN-HYS                                                                                                | V <sub>AD</sub> = 5 V to 0 V                                                 |       | 400   |       | mV                   |

| I <sub>AD</sub>        | Input leakage current                                                                                                                | V <sub>RECT</sub> = 0 V, V <sub>AD</sub> = 5 V                               |       |       | 60    | μА                   |

| R <sub>AD</sub>        | Pullup resistance from $\overline{\text{AD-EN}}$ to OUT when adapter mode is disabled and $V_{\text{OUT}} > V_{\text{AD}}$ , EN-OUT  | V <sub>AD</sub> = 0 V, V <sub>OUT</sub> = 5 V                                |       | 200   | 350   | Ω                    |

| $V_{AD}$               | Voltage difference between V <sub>AD</sub> and V $\overline{\text{AD}}$ . $\overline{\text{EN}}$ when adapter mode is enabled, EN-ON | V <sub>AD</sub> = 5 V, 0°C ≤ T <sub>J</sub> ≤ 85°C                           | 3     | 4.5   | 5     | V                    |

| SYNCHRONC              | OUS RECTIFIER                                                                                                                        |                                                                              | II.   |       |       |                      |

| lour                   | I <sub>OUT</sub> at which the synchronous rectifier enters half-synchronous mode, SYNC_EN                                            | I <sub>LOAD</sub> = 200 mA to 0 mA                                           | 80    | 100   | 130   | mA                   |

| Гоит                   | Hysteresis for I <sub>OUT,RECT-EN</sub> (full-synchronous mode enabled)                                                              | I <sub>LOAD</sub> = 0 mA to 200 mA                                           |       | 25    |       | шА                   |

| V <sub>HS-DIODE</sub>  | High-side diode drop when the rectifier is in half-synchronous mode                                                                  | $I_{AC\text{-VRECT}} = 250 \text{ mA}$ and $T_J = 25^{\circ}\text{C}$        |       | 0.7   |       | V                    |

| EN1 AND EN             | 2                                                                                                                                    |                                                                              |       |       |       |                      |

| V <sub>IL</sub>        | Input low threshold for EN1 and EN2                                                                                                  |                                                                              |       |       | 0.4   | V                    |

| V <sub>IH</sub>        | Input high threshold for EN1 and EN2                                                                                                 |                                                                              | 1.3   |       |       | V                    |

| R <sub>PD</sub>        | EN1 and EN2 pull down resistance                                                                                                     |                                                                              |       | 200   |       | kΩ                   |

|                        | ELATED MEASUREMENTS AND COEFFICI                                                                                                     | ENTS)                                                                        |       |       |       |                      |

| I <sub>OUT</sub> SENSE | Accuracy of the current sense over the load range                                                                                    | I <sub>OUT</sub> = 0 mA to 750 mA                                            | -1.5% | 0%    | 0.9%  |                      |

# TEXAS INSTRUMENTS

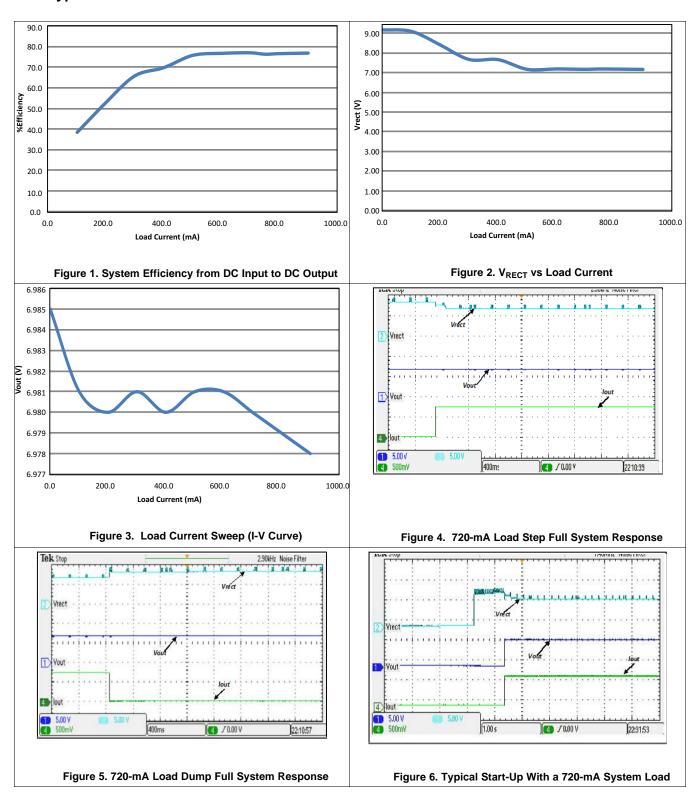

#### 7.6 Typical Characteristics

Submit Documentation Feedback

Copyright © 2012–2016, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

Copyright © 2012–2016, Texas Instruments Incorporated

Submit Documentation Feedback

# 8 Detailed Description

#### 8.1 Overview

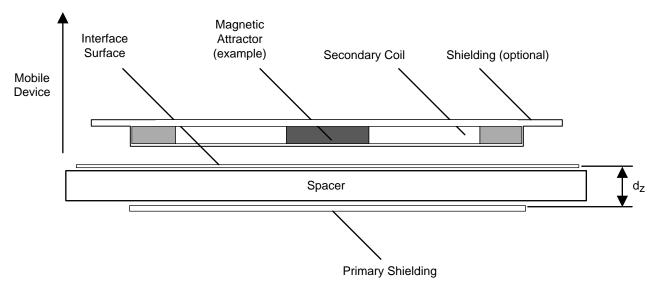

The principle of the bq51010B wireless power transfer devices are simply to provide an open-cored transformer consisting of transmitter and receiver coils. The transmitter coil and electronics are built into a charger pad, and the receiver coil and electronics are typically built into a portable device such as a cell phone. When the receiver coil is positioned on the transmitter coil, magnetic coupling occurs when the transmitter coil is driven. The flux is coupled into the secondary coil, which induces a voltage and current flows. The secondary voltage is rectified, and power can be transferred effectively to a load wirelessly. Power transfer can be managed through any of the various closed-loop control schemes.

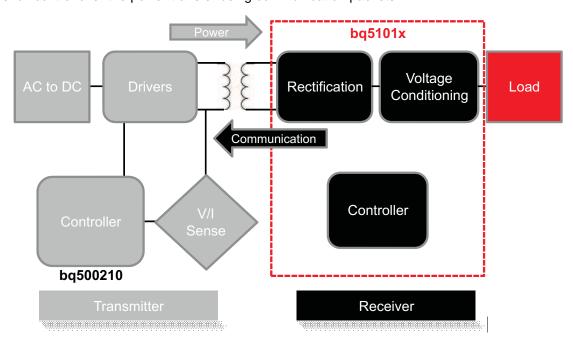

#### 8.1.1 A Brief Description of the Wireless System

A wireless system consists of a charging pad (transmitter or primary) and the secondary-side equipment (receiver or secondary). There is a coil in the charging pad and in the secondary equipment which are magnetically coupled to each other when the secondary is placed on the primary. Power is then transferred from the transmitter to the receiver through coupled inductors (for example, an air-core transformer). Controlling the amount of power transferred is achieved by sending feedback (error signal) communication to the primary (for example, to increase or decrease power).

The receiver communicates with the transmitter by changing the load seen by the transmitter. This load variation results in a change in the transmitter coil current, which is measured and interpreted by a processor in the charging pad. Communication is done through digital-packets which are transferred from the receiver to the transmitter. Differential biphase encoding is used for the packets. The bit rate is 2-kbps.

Various types of communication packets have been defined. These include identification and authentication packets, error packets, control packets, end power packets, and power usage packets.

The transmitter coil stays powered off most of the time. It occasionally wakes up to see if a receiver is present. When a receiver authenticates itself to the transmitter, the transmitter remains powered on. The receiver maintains full control over the power transfer using communication packets.

Figure 12. WPC Wireless Power System Indicating the Functional Integration of the bq51010B

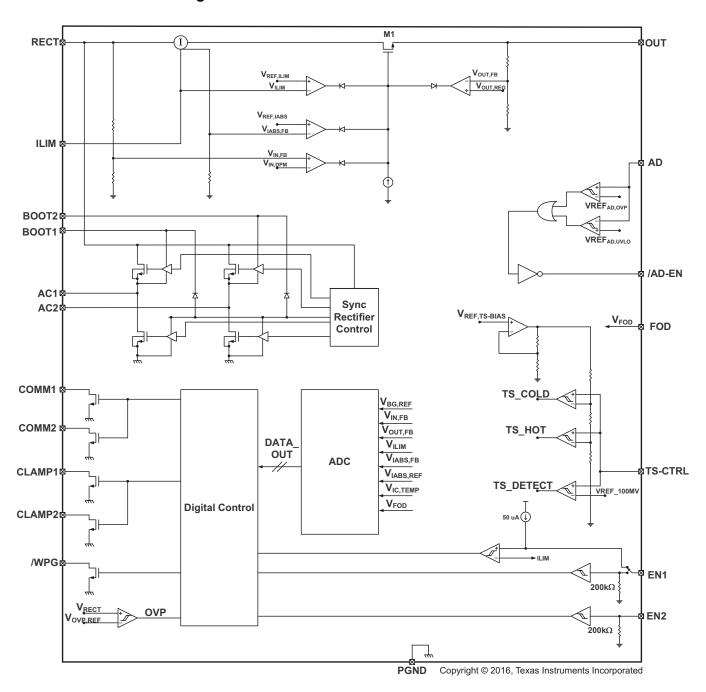

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Qi Wireless Power System and bq51010B Power Transfer Flow Diagrams

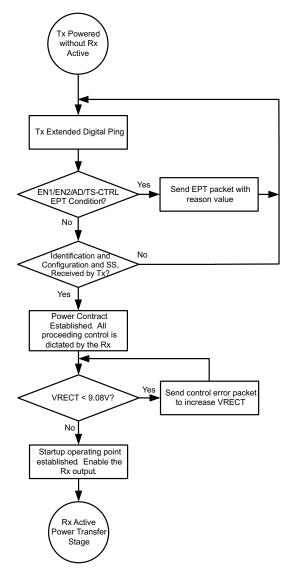

The bq51010B family integrates a fully compliant WPC v1.1 communication algorithm to streamline receiver designs (no extra software development required). Other unique algorithms such has Dynamic Rectifier Control are also integrated to provide best-in-class system performance. This section provides a high-level overview of these features by illustrating the wireless power transfer flow diagram from start-up to active operation.

#### **Feature Description (continued)**

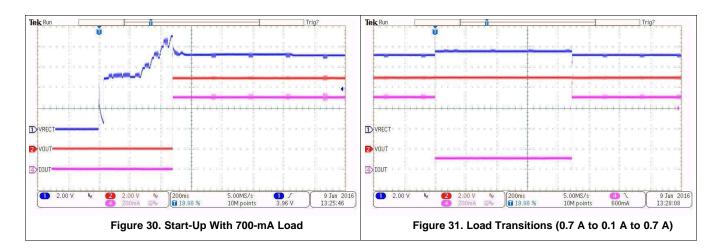

During start-up operation, the wireless power receiver must comply with proper handshaking to be granted a power contract from the TX. The TX initiates the hand shake by providing an extended digital ping. If an RX is present on the TX surface, the RX then provides the signal strength, configuration, and identification packets to the TX (see volume 1 of the WPC specification for details on each packet). These are the first three packets sent to the TX. The only exception is if there is a true shutdown condition on the EN1 or EN2, the AD, or the TS-CTRL pins where the RX shuts down the TX immediately (see Table 5 for details). Once the TX has successfully received the signal strength, configuration, and identification packets, the RX is granted a power contract and is then allowed to control the operating point of the power transfer. With the use of the Dynamic Rectifier Control algorithm, the RX informs the TX to adjust the rectifier voltage above 9 V prior to enabling the output supply. This method enhances the transient performance during system start-up (see Figure 13 for the start-up flow diagram details).

Figure 13. Wireless Power Start-Up Flow Diagram

Submit Documentation Feedback

Copyright © 2012–2016, Texas Instruments Incorporated

#### **Feature Description (continued)**

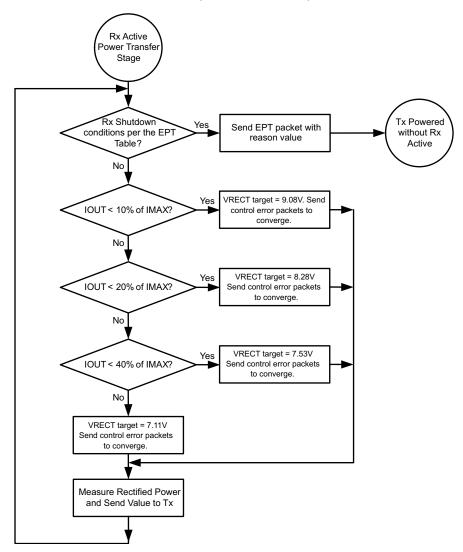

Once the start-up procedure has been established, the RX enters the active power transfer stage. This is considered the *main loop* of operation. The Dynamic Rectifier Control algorithm determines the rectifier voltage target based on a percentage of the maximum output current level setting (set by  $K_{IMAX}$  and the ILIM resistance to GND). The RX sends control error packets to converge on these targets. As the output current changes, the rectifier voltage target dynamically changes. As a note, the feedback loop of the WPC system is relatively slow where it can take up to 90 ms to converge on a new rectifier voltage target. It must be understood that the instantaneous transient response of the system is open loop and dependent on the RX coil output impedance at that operating point. The *main loop* also determines if any conditions in Table 5 are true to discontinue power transfer. See Figure 14 which illustrates the active power transfer loop.

Figure 14. Active Power Transfer Flow Diagram

Another requirement of the WPC v1.1 specification is to send the measured recieved power. This task is enabled on the IC by measuring the voltage on the FOD pin which is proportional to the output current and can be scaled based on the choice of the resitor to ground on the FOD pin.

#### **Feature Description (continued)**

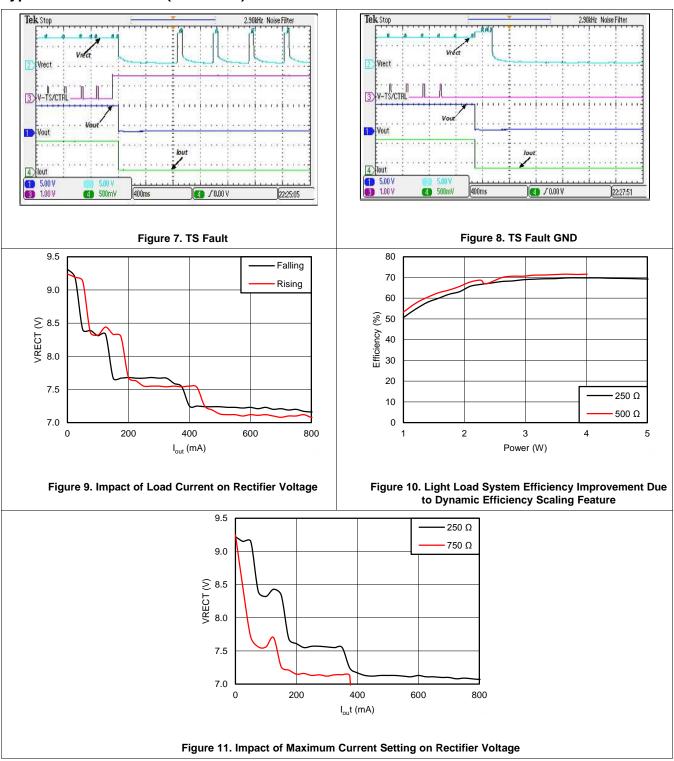

#### 8.3.2 Dynamic Rectifier Control

The dynamic rectifier control algorithm offers the end system designer optimal transient response for a given max output current setting. This is achieved by providing enough voltage headroom across the internal regulator at light loads to maintain regulation during a load transient. The WPC system has a relatively slow global feedback loop where it can take more than 90 ms to converge on a new rectifier voltage target. Therefore, the transient response is dependent on the loosely coupled transformers output impedance profile. The dynamic rectifier control allows for a 2-V change in rectified voltage before the transient response is observed at the output of the internal regulator (output of the bq51010B). A 720-mA application allows up to a  $1.5-\Omega$  output impedance.

#### 8.3.3 Dynamic Efficiency Scaling

The dynamic efficiency scaling feature allows for the loss characteristics of the bq51010B to be scaled based on the maximum expected output power in the end application. This effectively optimizes the efficiency for each application. This feature is achieved by scaling the loss of the internal LDO based on a percentage of the maximum output current. Note that the maximum output current is set by the  $K_{IMAX}$  term and the  $R_{ILIM}$  resistance (where  $R_{ILIM} = K_{IMAX} / I_{MAX}$ ). The flow diagram show in Figure 14 illustrates how the rectifier is dynamically controlled (*Dynamic Rectifier Control*) based on a fixed percentage of the  $I_{MAX}$  setting. Table 2 summarizes how the rectifier behavior is dynamically adjusted based on two different  $R_{ILIM}$  settings.

**OUTPUT CURRENT**  $R_{ILIM} = 890 \Omega$  $R_{ILIM}$  = 417  $\Omega$ **V**RECT  $I_{MAX} = 0.35 A$  $I_{MAX} = 0.75 A$ **PERCENTAGE** 0% to 10% 0 A to 0.035 A 0 A to 0.075 A 9.08 V 8.28 V 10% to 20% 0.035 A to 0.07 A 0.075 A to 0.150 A 20% to 40% 0.07 A to 0.14 A 0.150 A to 0.225 A 7.53 V >40% >0.14 A >0.225 A 7.11 V

**Table 2. Dynamic Efficiency Scaling**

#### 8.3.4 R<sub>ILIM</sub> Calculations

The bq51010B includes a means of providing hardware overcurrent protection by means of an analog current regulation loop. The hardware current limit provides an extra level of safety by clamping the maximum allowable output current (for example, a current compliance). The  $R_{\rm ILIM}$  resistor size also sets the thresholds for the dynamic rectifier levels and thus providing efficiency tuning per the maximum system current of each application. Calculate the total  $R_{\rm ILIM}$  resistance with Equation 1.

$$R_{ILIM} = \frac{262}{I_{MAX}}$$

$$I_{ILIM} = 1.2 \times I_{MAX} = \frac{314}{R_{ILIM}}$$

$$R_{ILIM} = R_1 + R_{FOD}$$

where

- I<sub>MAX</sub> is the expected maximum output current during normal operation

- I<sub>ILIM</sub> is the hardware over current limit

(1)

When referring to the application diagram shown in Figure 27,  $R_{ILIM}$  is the sum of  $R_{FOD}$  and the  $R_1$  resistance (for example, the total resistance from the ILIM pin to GND).

#### 8.3.5 Input Overvoltage

If the input voltage suddenly increases in potential (for example, due to a change in position of the equipment on the charging pad), the voltage-control loop inside the bq51010B becomes active, and prevents the output from going beyond  $V_{OUT\text{-}REG}$ . The receiver then starts sending back error packets to the transmitter every 30 ms until the input voltage comes back to the  $V_{RECT\text{-}REG}$  target, and then maintains the error communication every 250 ms.

If the input voltage increases in potential beyond  $V_{OVP}$ , the IC switches off the LDO and communicates to the primary to bring the voltage back to  $V_{RECT-REG}$ . In addition, a proprietary voltage protection circuit is activated by means of  $C_{CLAMP1}$  and  $C_{CLAMP2}$  that protects the IC from voltages beyond the maximum rating of the IC (for example, 20 V).

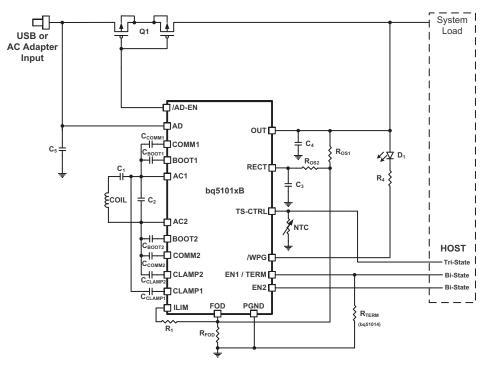

#### 8.3.6 Adapter Enable Functionality and EN1 or EN2 Control

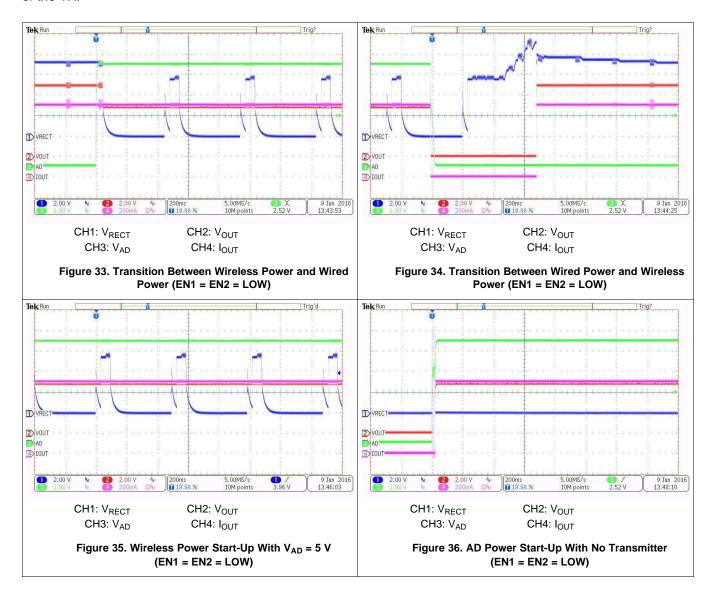

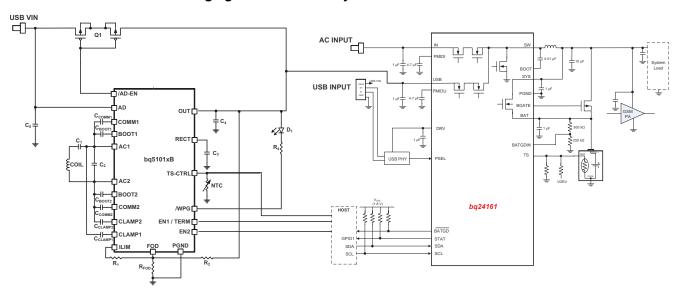

Figure 32 is an example application that shows the bq51010B used as a wireless power receiver that can power multiplex between wired or wireless power for the down-system electronics. In the default operating mode pins EN1 and EN2 are low, which activates the adapter enable functionality. In this mode, if an adapter is not present the AD pin is low, and  $\overline{\text{AD-EN}}$  pin is pulled to the higher of the OUT and AD pins so that the PMOS between OUT and AD is turned off. If an adapter is plugged in and the voltage at the AD pin goes above 3.6 V then wireless charging is disabled and the  $\overline{\text{AD-EN}}$  pin is pulled approximately 4 V below the AD pin to connect AD to the secondary charger. The difference between AD and AD-EN is regulated to a maximum of 7V to ensure the  $V_{GS}$  of the external PMOS is protected.

The EN1 and EN2 pins include internal 200-k $\Omega$  pulldown resistors, so that if these pins are not connected bq51010B defaults to  $\overline{\text{AD-EN}}$  control mode. However, these pins can be pulled high to enable other operating modes as described in Table 3.

| EN1 | EN2 | RESULT                                                                                                                                                                                                        |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Adapter control enabled. If adapter is present then secondary charger is powered by adapter, otherwise wireless charging is enabled when wireless power is available. Communication current limit is enabled. |

| 0   | 1   | Disables communication current limit.                                                                                                                                                                         |

| 1   | 0   | AD-EN is pulled low, whether or not adapter voltage is present. This feature can be used, for example, in USB OTG applications.                                                                               |

| 1   | 1   | Adapter and wireless charging are disabled, that is, power is never delivered by the OUT pin in this mode                                                                                                     |

Table 3. EN/EN2 Control

| Table 4. Adapt | er Enable | Functiona | lity |

|----------------|-----------|-----------|------|

|----------------|-----------|-----------|------|

| EN1 | EN2 | WIRELESS<br>POWER       | WIRED POWER             | OTG MODE ADAPTIVE COMMUNICATION LIMIT |          | EPT            |

|-----|-----|-------------------------|-------------------------|---------------------------------------|----------|----------------|

| 0   | 0   | Enabled                 | Priority <sup>(1)</sup> | Disabled                              | Enabled  | Not Sent to TX |

| 0   | 1   | Priority <sup>(1)</sup> | Enabled                 | Disabled                              | Disabled | Not Sent to TX |

| 1   | 0   | Disabled                | Enabled                 | Enabled <sup>(2)</sup>                | _        | No Response    |

| 1   | 1   | Disabled                | Disabled                | Disabled                              | _        | Termination    |

<sup>(1)</sup> If both wired and wireless power are present, wired power is given priority.

As described in Table 4, pulling EN2 high disables the adapter mode and only allows wireless charging. In this mode the adapter voltage is always blocked from the OUT pin. An application example where this mode is useful is when USB power is present at AD, but the USB is in suspend mode so that no power can be taken from the USB supply. Pulling EN1 high enables the off-chip PMOS regardless of the presence of a voltage. This function can be used in USB OTG mode to allow a charger connected to the OUT pin to power the AD pin. Finally, pulling both EN1 and EN2 high disables both wired and wireless charging.

#### **NOTE**

It is required to connect a back-to-back PMOS between AD and OUT so that voltage is blocked in both directions. Also, when AD mode is enabled no load can be pulled from the RECT pin as this could cause an internal device overvoltage in bq51010B.

#### 8.3.7 End Power Transfer Packet (WPC Header 0x02)

The WPC allows for a special command for the receiver to terminate power transfer from the transmitter termed End Power Transfer (EPT) packet. Table 5 specifies the v1.1 reasons column and their corresponding data field value. The condition column corresponds to the methodology used by bq51010B to send equivalent message.

<sup>(2)</sup> Allows for a boost-back supply to be driven from the output terminal of the RX to the adapter port through the external back-to-back PMOS FET.

| Table F | End    | Dowor | Transfer | Dacket |

|---------|--------|-------|----------|--------|

| lable : | ). Ena | Power | Transfer | Packet |

| MESSAGE          | VALUE | CONDITION                                                   |

|------------------|-------|-------------------------------------------------------------|

| Unknown          | 0x00  | AD > 3.6 V                                                  |

| Charge Complete  | 0x01  | TS/CTRL = 1, or EN1 = 1, or <en1 en2=""> = &lt;11&gt;</en1> |

| Internal Fault   | 0x02  | $T_J > 150$ °C or $R_{ILIM} < 100 \Omega$                   |

| Over Temperature | 0x03  | TS < $V_{HOT}$ , TS > $V_{COLD}$ , or TS/CTRL < 100 mV      |

| Over Voltage     | 0x04  | Not Sent                                                    |

| Over Current     | 0x05  | NOT USED                                                    |

| Battery Failure  | 0x06  | Not Sent                                                    |

| Reconfigure      | 0x07  | Not Sent                                                    |

| No Response      | 0x08  | VRECT target doesn't converge                               |

#### 8.3.8 Status Outputs

The bq51010B has one status output,  $\overline{\text{WPG}}$ . This output is an open-drain NMOS device that is rated to 20 V. The open-drain FET connected to the  $\overline{\text{WPG}}$  pin is turned on whenever the output of the power supply is enabled. The output of the power supply is not enabled if the  $V_{\text{RECT-REG}}$  does not converge at the no-load target voltage.

#### 8.3.9 WPC Communication Scheme

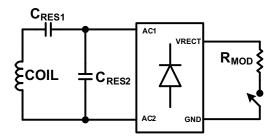

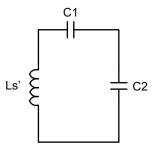

The WPC communication uses a modulation technique termed *back-scatter modulation* where the receiver coil is dynamically loaded to provide amplitude modulation of the coil voltage and current of the transmitter. This scheme is possible due to the fundamental behavior between two loosely coupled inductors (for example, between the TX and RX coil). This type of modulation can be accomplished by switching in and out a resistor at the output of the rectifier, or by switching in and out a capacitor across the AC1/AC2 net. Figure 15 shows how to implement resistive modulation.

Figure 15. Resistive Modulation

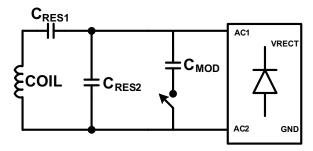

Figure 16 shows how to implement capacitive modulation.

Figure 16. Capacitive Modulation

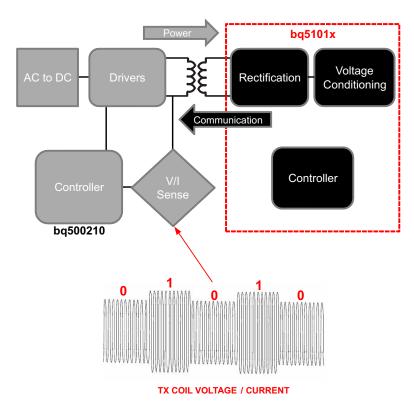

The amplitude change in TX coil voltage or current can be detected by the transmitters decoder. Figure 17 shows the resulting signal observed by the TX.

Figure 17. TX Coil Voltage and Current

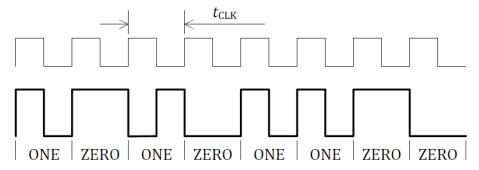

The WPC protocol uses a differential biphase encoding scheme to modulate the data bits onto the TX coil voltage and current. Each data bit is aligned at a full period of 0.5 ms ( $t_{CLK}$ ) or 2 kHz. An encoded ONE results in two transitions during the bit period and an encoded ZERO results in a single transition. See Figure 18 for an example of the differential biphase encoding.

Figure 18. Differential Biphase Encoding Scheme (WPC volume 1: Low Power, Part 1 Interface Definition)

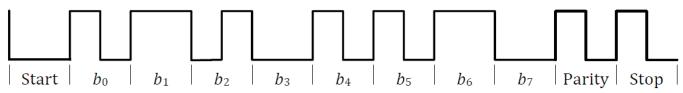

The bits are sent LSB first and use an 11-bit asynchronous serial format for each portion of the packet. This includes one start bit, n-data bytes, a parity bit, and a single stop bit. The start bit is always ZERO and the parity bit is odd. The stop bit is always ONE. Figure 19 shows the details of the asynchronous serial format.

Figure 19. Asynchronous Serial Formatting (WPC volume 1: Low Power, Part 1 Interface Definition)

Each packet format is organized as shown in Figure 20.

Figure 20. Packet Format (WPC volume 1: Low Power, Part 1 Interface Definition)

#### 8.3.10 Communication Modulator

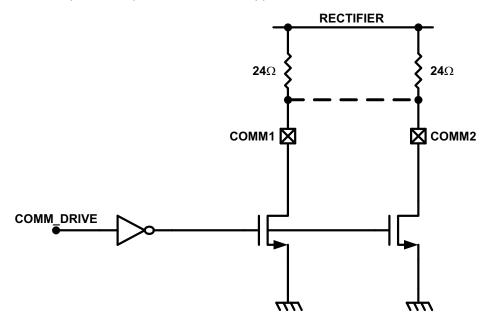

The bq51010B provides two identical, integrated communication FETs which are connected to the pins COM1 and COM2. These FETs are used for modulating the secondary load current which allows bq51010B to communicate error control and configuration information to the transmitter. Figure 21 below shows how the COMM pins can be used for resistive load modulation. Each COMM pin can handle at most a 24- $\Omega$  communication resistor. Therefore, if a COMM resistor between 12  $\Omega$  and 24  $\Omega$  is required COM1 and COM2 pins must be connected in parallel. bq51010B does not support a COMM resistor less than 12  $\Omega$ .

Figure 21. Resistive Load Modulation

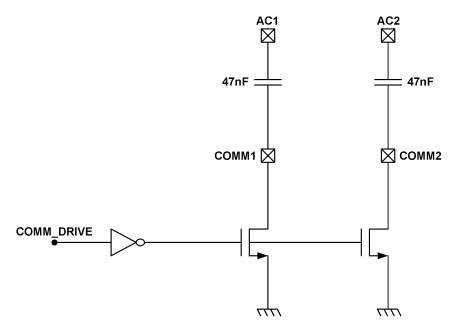

In addition to resistive load modulation, the bq51010B is also capable of capacitive load modulation as shown in Figure 22 below. In this case, a capacitor is connected from COM1 to AC1 and from COM2 to AC2. When the COMM switches are closed there is effectively a 22-nF capacitor connected between AC1 and AC2. Connecting a capacitor in between AC1 and AC2 modulates the impedance seen by the coil, which is reflected in the primary as a change in current.

Figure 22. Capacitive Load Modulation

#### 8.3.11 Adaptive Communication Limit

The Qi communication channel is established through backscatter modulation as described in the previous sections. This type of modulation takes advantage of the loosely coupled inductor relationship between the RX and TX coil. Essentially the switching in-and-out of the communication capacitor or resistor adds a transient load to the RX coil to modulate the TX coil voltage or current waveform (amplitude modulation). The consequence of this technique is that a load transient (load current noise) from the mobile device has the same signature. To provide noise immunity to the communication channel, the output load transients must be isolated from the RX coil. The proprietary feature *adaptive communication limit* achieves this by dynamically adjusting the current limit of the regulator. When the regulator is put in current limit, any load transients is offloaded to the battery in the system.

Note that this requires the battery charger IC to have input voltage regulation (weak adapter mode). The output of the RX appears as a weak supply if a transient occurs above the current limit of the regulator.

The adaptive communication limit feature has two current limit modes listed in Table 6.

Table 6. Adaptive Communication Limit

| I <sub>OUT</sub> | COMMUNICATION CURRENT LIMIT |

|------------------|-----------------------------|

| < 300 mA         | Fixed 400 mA                |

| > 300 mA         | I <sub>OUT</sub> + 50 mA    |

#### 8.3.12 Synchronous Rectification

The bq51010B provides an integrated, self-driven synchronous rectifier that enables high-efficiency AC to DC power conversion. The rectifier consists of an all NMOS H-Bridge driver where the backgates of the diodes are configured to be the rectifier when the synchronous rectifier is disabled. During the initial start-up of the WPC system the synchronous rectifier is not enabled. At this operating point, the DC rectifier voltage is provided by the diode rectifier. Once V<sub>RECT</sub> is greater than UVLO, half-synchronous mode is enabled until the load current surpasses 120 mA. Above 120 mA, the full synchronous rectifier stays enabled until the load current drops back below 100 mA where half-synchronous mode is enabled instead.

#### 8.3.13 Temperature Sense Resistor Network (TS)

bq51010B includes a ratiometric external temperature sense function. The temperature sense function has two ratiometric thresholds which represent a hot and cold condition. TI recommends an external temperature sensor to provide safe operating conditions for the receiver product. This pin is best used for monitoring the surface that can be exposed to the end user (for example, place the NTC resistor closest to the user).

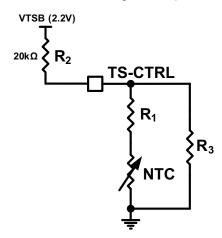

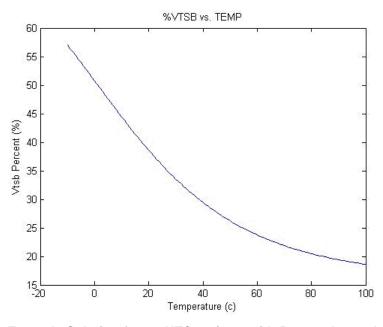

Figure 23 allows for any NTC resistor to be used with the given  $V_{HOT}$  and  $V_{COLD}$  thresholds.

Figure 23. NTC Circuit Used for Safe Operation of the Wireless Receiver Power Supply

The resistors  $R_1$  and  $R_3$  can be solved by resolving the system of equations at the desired temperature thresholds (see Equation 2 and Equation 3).

$$%V_{COLD} = \frac{\left(\frac{R_{3}(R_{NTC}|_{TCOLD} + R_{1})}{R_{3} + (R_{NTC}|_{TCOLD} + R_{1})}\right)}{\left(\frac{R_{3}(R_{NTC}|_{TCOLD} + R_{1})}{R_{3} + (R_{NTC}|_{TCOLD} + R_{1})}\right) + R2} \times 100}$$

$$%V_{HOT} = \frac{\left(\frac{R_{3}(R_{NTC}|_{THOT} + R_{1})}{R_{3} + (R_{NTC}|_{THOT} + R_{1})}\right)}{\left(\frac{R_{3}(R_{NTC}|_{THOT} + R_{1})}{R_{3} + (R_{NTC}|_{THOT} + R_{1})}\right) + R2}} \times 100}$$

$$R_{NTC}|_{TCOLD} = R_{0}e^{\beta(\frac{1}{T}_{TCOLD} - \frac{1}{T}_{TO})}$$

$$R_{NTC}|_{THOT} = R_{0}e^{\beta(\frac{1}{T}_{TOLD} - \frac{1}{T}_{TO})}$$

(2)

#### where

- $\bullet$   $\;\;$   $T_{COLD}$  and  $T_{HOT}$  are the desired temperature thresholds in degrees Kelvin

- R<sub>O</sub> is the nominal resistance

- β is the temperature coefficient of the NTC resistor

- $R_{\Omega}$  is fixed at 20  $k\Omega$  (3)

An example solution is provided:

- R1 =  $4.23 \text{ k}\Omega$

- R3 = 66.8 k $\Omega$

Where the chosen parameters are:

- $%V_{HOT} = 19.6\%$

- $\%V_{COLD} = 58.7\%$

- $T_{COLD} = -10^{\circ}C$

- T<sub>HOT</sub> = 100°C

- β = 3380

- R<sub>O</sub> = 10 kΩ

Figure 24 shows the plot of the percent  $V_{TSB}$  vs temperature.

Figure 24. Example Solution for an NTC resistor with R<sub>O</sub> = 10 k $\Omega$  and  $\beta$  = 4500

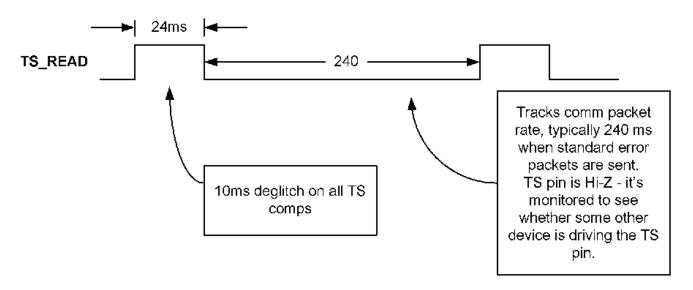

Figure 25 illustrates the periodic biasing scheme used for measuring the TS state. The TS\_READ signal enables the TS bias voltage for 24 ms. During this period the TS comparators are read (each comparator has a 10 ms deglitch) and appropriate action is taken based on the temperature measurement. After this 24 ms period has elapsed, the TS\_READ signal goes low, which causes the TS-Bias pin to become high impedance. During the next 35 ms (priority packet period) or 235 ms (standard packet period), the TS voltage is monitored and compared to 100 mV. If the TS voltage is greater than 100 mV then a secondary device is driving the TS or CTRL pin and a CTRL = 1 is detected.

Figure 25. Timing Diagram for TS Detection Circuit

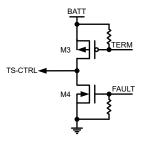

#### 8.3.14 3-State Driver Recommendations For the TS-CTRL Pin

The TS-CTRL pin offers three functions with one 3-state driver interface:

- 1. NTC temperature monitoring,

- 2. Fault indication,

- 3. Charge done indication

A 3-state driver can be implemented with the circuit in Figure 26 and the use of two GPIO connections.

Figure 26. 3-state Driver for TS-CTRL

Note that the signals *TERM* and *FAULT* are given by two GPIOs. The truth table for this circuit is found in Table 7.

**Table 7. Truth Table**

| TERM | FAULT | F (RESULT)      |

|------|-------|-----------------|

| 1    | 0     | Z (Normal mode) |

| 0    | 0     | Charge complete |

| 1    | 1     | System fault    |

The default setting is TERM = 1 and FAULT = 0. In this condition, the TS-CTRL net is high impedance (hi-z); therefore, the NTC is function is allowed to operate. When the TS-CTRL pin is pulled to GND by setting FAULT = 1, the RX is shutdown with the indication of a fault. When the TS-CTRL pin is pulled to the battery by setting TERM = 1, the RX is shutdown with the indication of a charge complete condition. Therefore, the host controller can indicate whether the RX is system is turning off due to a fault or due to a charge complete condition.

#### 8.3.15 Thermal Protection

The bq51010B includes a thermal shutdown protection. If the die temperature reaches  $T_J(OFF)$ , the LDO is shut off to prevent any further power dissipation. In this case bq51010B sends an EPT message of internal fault (0x02).

#### 8.3.16 WPC 1.1 Compliance - Foreign Object Detection

The bq51010B is a WPC 1.1 compatible device. To enable a power transmitter to monitor the power loss across the interface as one of the possible methods to limit the temperature rise of foreign objects, the bq51010B reports its received power to the power transmitter. The received power equals the power that is available from the output of the power receiver plus any power that is lost in producing that output power (the power loss in the secondary coil and series resonant capacitor, the power loss in the shielding of the power receiver, the power loss in the rectifier). In WPC1.1 specification, foreign object detection (FOD) is enforced. This means the bq51010B sends received power information with known accuracy to the transmitter.

WPC 1.1 defines received power as "the average amount of power that the power receiver receives through its interface surface, in the time window indicated in the configuration packet".

To receive certification as a WPC 1.1 receiver, the Device Under Test (DUT) is tested on a reference transmitter whose transmitted power is calibrated, the receiver must send a received power such that Equation 4.

$$0 < (TX PWR)_{REF} - (RX PWR out)_{DUT} < -250 \text{ mW}$$

$$\tag{4}$$

This 250-mW bias ensures that system remains interoperable.

WPC 1.1 transmitter is tested to see if they can detect reference foreign objects with a reference receiver.

WPC 1.1 specification allows much more accurate sensing of foreign objects.

#### 8.4 Device Functional Modes

The operational modes of the bq51010B are described in *Feature Description*. The bq51010B has several functional modes. Start-up refers to the initial power transfer and communication between the receiver (bq51010B circuit) and the transmitter. Power transfer refers to any time that the TX and RX are communicating and power is being delivered from the TX to the RX. Power transfer termination occurs when the RX is removed from the TX, power is removed from the TX or the RX requests power transfer termination.

# 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

The bq51010B is a fully integrated, wireless power receiver in a single device. The device complies with the WPC v1.1 specifications for a wireless power receiver. When paired with a WPC v1.1 compliant transmitter, the device can provide up to 5-W of power. There are several tools available for the design of the system. These tools may be obtained by checking the product page at www.ti.com/product/bq51010B.

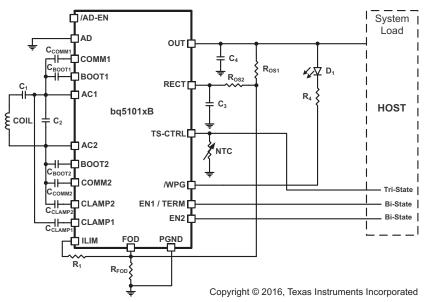

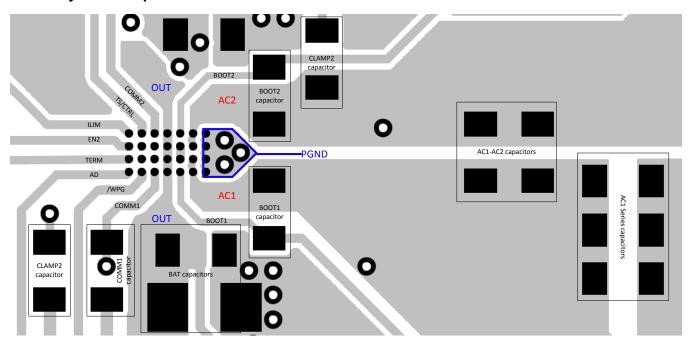

#### 9.2 Typical Applications

#### 9.2.1 bq51010B Wireless Power Receiver Used as a Power Supply

Only one of R<sub>OS1</sub> or R<sub>OS2</sub> required

Figure 27. bq51010B Used as a Wireless Power Receiver and Power Supply for System Loads

#### 9.2.1.1 Design Requirements

This application is for a system that has varying loads from less than 100 mA up to 1 A. The application must work with any Qi-certified transmitter. There is no requirement for any external thermal measurements. An LED indication is required to indicate an active power supply. Each of the components from the application drawing is examined.

#### 9.2.1.2 Detailed Design Procedure

#### 9.2.1.2.1 Using the bq51010B as a Wireless Power Supply

Figure 27 is the schematic of a system which uses the bq51010B as a power supply.

When the system shown in Figure 27 is placed on the charging pad, the receiver coil is inductively coupled to the magnetic flux generated by the coil in the charging pad, which consequently induces a voltage in the receiver coil. The internal synchronous rectifier feeds this voltage to the RECT pin, which has the filter capacitor C3.