# **NiCd/NiMH Fast-Charge Management ICs**

### **Features**

- Fast charge of nickel cadmium or nickel-metal hydride batteries

- ➤ Direct LED output displays charge status

- ➤ Fast-charge termination by -ΔV, maximum voltage, maximum temperature, and maximum time

- ➤ Internal band-gap voltage reference

- ➤ Optional top-off charge

- Selectable pulse trickle charge rates

- ➤ Low-power mode

- ➤ 8-pin 300-mil DIP or 150-mil SOIC

### **General Description**

The bq2002 and bq2002/F Fast-Charge ICs are low-cost CMOS battery-charge controllers providing reliable charge termination for both NiCd and NiMH battery applications. Controlling a current-limited or constant-current supply allows the bq2002/F to be the basis for a cost-effective stand-alone or system-integrated charger. The bq2002/F integrates fast charge with optional top-off and pulsed-trickle control in a single IC for charging one or more NiCd or NiMH battery cells.

Fast charge is initiated on application of the charging supply or battery replacement. For safety, fast charge is inhibited if the battery temperature and voltage are outside configured limits.

Fast charge is terminated by any of the following:

- Peak voltage detection (PVD)

- Negative delta voltage (-ΔV)

- Maximum voltage

- Maximum temperature

- Maximum time

After fast charge, the bq2002/F optionally tops-off and pulse-trickles the battery per the pre-configured limits. Fast charge may be inhibited using the INH pin. The bq2002/F may also be placed in low-standby-power mode to reduce system power consumption.

The bq2002F differs from the bq2002 only in that a slightly different set of fast-charge and top-off time limits is available. All differences between the two ICs are illustrated in Table 1.

### **Pin Connections**

### **Pin Names**

| TM       | Timer mode select input | TS       | Temperature sense input |

|----------|-------------------------|----------|-------------------------|

| LED      | Charging status output  | $V_{CC}$ | Supply voltage input    |

| BAT      | Battery voltage input   | INH      | Charge inhibit input    |

| $V_{SS}$ | System ground           | CC       | Charge control output   |

## bq2002/F Selection Guide

| Part No. | TCO                   | HTF  | LTF  | -∆ <b>V</b> | PVD | Fast Charge | t <sub>мто</sub> | Top-Off | Maintenance |

|----------|-----------------------|------|------|-------------|-----|-------------|------------------|---------|-------------|

|          |                       |      |      |             | ~   | C/2         | 160              | C/32    | C/64        |

| bq2002   | 0.5 * V <sub>CC</sub> | None | None |             | ~   | 1C          | 80               | C/16    | C/64        |

|          |                       |      |      | ~           |     | 2C          | 40               | None    | C/32        |

|          |                       |      |      |             | ~   | C/2         | 160              | C/32    | C/64        |

| bq2002F  | 0.5 * V <sub>CC</sub> | None | None |             | ~   | 1C          | 100              | C/16    | C/64        |

|          |                       |      |      | ~           |     | 2C          | 55               | None    | C/32        |

### **Pin Descriptions**

#### TM Timer mode input

A three-level input that controls the settings for the fast charge safety timer, voltage termination mode, top-off, pulse-trickle, and voltage hold-off time.

#### **LED** Charging output status

Open-drain output that indicates the charging status.

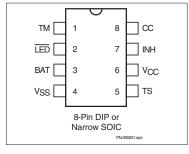

#### **BAT** Battery input voltage

The battery voltage sense input. The input to this pin is created by a high-impedance resistor divider network connected between the positive and negative terminals of the battery.

#### V<sub>SS</sub> System ground

### TS Temperature sense input

Input for an external battery temperature monitoring thermistor.

### V<sub>CC</sub> Supply voltage input

$5.0V \pm 20\%$  power input.

### INH Charge inhibit input

When high, INH suspends the fast charge in progress. When returned low, the IC resumes operation at the point where initially suspended.

### CC Charge control output

An open-drain output used to control the charging current to the battery. CC switching to high impedance (Z) enables charging current to flow, and low to inhibit charging current. CC is modulated to provide top-off, if enabled, and pulse trickle.

### **Functional Description**

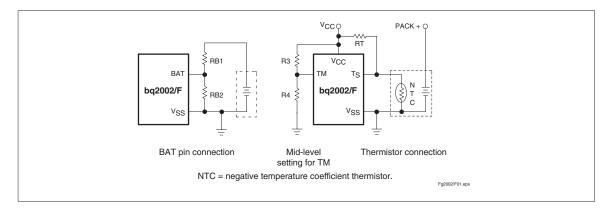

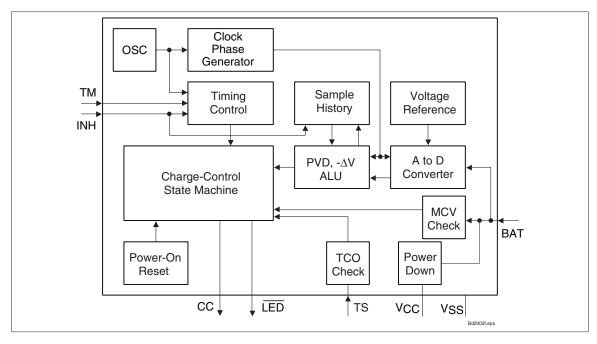

Figure 2 shows a state diagram and Figure 3 shows a block diagram of the bq2002/F.

# **Battery Voltage and Temperature Measurements**

Battery voltage and temperature are monitored for maximum allowable values. The voltage presented on the battery sense input, BAT, should represent a single-cell potential for the battery under charge. A resistor-divider ratio of

$$\frac{RB1}{RB2} = N - 1$$

is recommended to maintain the battery voltage within the valid range, where N is the number of cells, RB1 is the resistor connected to the positive battery terminal, and RB2 is the resistor connected to the negative battery terminal. See Figure 1.

Note: This resistor-divider network input impedance to end-to-end should be at least  $200k\Omega$  and less than  $1~M\Omega$ .

A ground-referenced negative temperature coefficient thermistor placed near the battery may be used as a low-cost temperature-to-voltage transducer. The temperature sense voltage input at TS is developed using a resistor-thermistor network between  $V_{CC}$  and  $V_{SS}$ . See Figure 1.

Figure 1. Voltage and Temperature Monitoring and TM Pin Configuration

Figure 2. State Diagram

Figure 3. Block Diagram

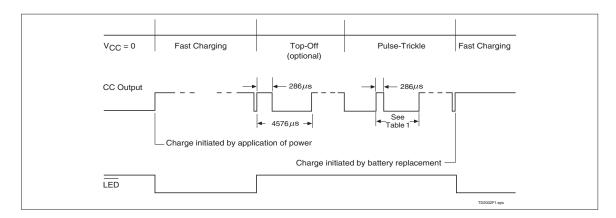

Figure 4. Charge Cycle Phases

### **Starting A Charge Cycle**

Either of two events starts a charge cycle (see Figure 4):

- 1. Application of power to  $V_{CC}\,\mbox{or}$

- 2. Voltage at the BAT pin falling through the maximum cell voltage  $V_{\mbox{\footnotesize{MCV}}}$  where

$$V_{MCV}=2V~\pm 5\%.$$

If the battery is within the configured temperature and voltage limits, the IC begins fast charge. The valid battery voltage range is  $V_{BAT} < V_{MCV}$ . The valid temperature range is  $V_{TS} > V_{TCO}$  where

$$V_{TCO} = 0.5 * V_{CC} \pm 5\%$$

.

If the battery voltage or temperature is outside of these limits, the IC pulse-trickle charges until the next new charge cycle begins.

Fast charge continues until termination by one or more of the five possible termination conditions:

- Peak voltage detection (PVD)

- Negative delta voltage (-∆V)

- Maximum voltage

- Maximum temperature

- Maximum time

Table 1. Fast-Charge Safety Time/Hold-Off Table

| Corresponding       |      |             | Typical Fast-Charge and Top-Off Time Limits (minutes)  bq2002 bq2002F |     | Typical PVD                        | Ton Off         | Pulse-          | Pulse-<br>Trickle |

|---------------------|------|-------------|-----------------------------------------------------------------------|-----|------------------------------------|-----------------|-----------------|-------------------|

| Fast-Charge<br>Rate | TM   | Termination |                                                                       |     | and -∆V Hold-Off<br>Time (seconds) | Top-Off<br>Rate | Trickle<br>Rate | Period<br>(ms)    |

| C/2                 | Mid  | PVD         | 160                                                                   | 160 | 600                                | C/32            | C/64            | 9.15              |

| 1C                  | Low  | PVD         | 80                                                                    | 100 | 300                                | C/16            | C/64            | 18.3              |

| 2C                  | High | -ΔV         | 40                                                                    | 40  | 150                                | Disabled        | C/32            | 18.3              |

**Notes:** Typical conditions = 25°C,  $V_{CC} = 5.0$ V.

$Mid = 0.5 * V_{CC} \pm 5V$

Tolerance on all timing is  $\pm 20\%$ .

### PVD and -∆V Termination

There are two modes for voltage termination depending on the state of TM. For - $\!\Delta V$  (TM = high), if  $V_{BAT}$  is lower than any previously measured value by 12mV  $\pm 3mV$ , fast charge is terminated. For PVD (TM = low or mid), a decrease of 2.5mV  $\pm 2.5mV$  terminates fast charge. The PVD and - $\!\Delta V$  tests are valid in the range  $1V < V_{BAT} < 2V$ .

### **Voltage Sampling**

Voltage is sampled at the BAT pin for PVD and - $\Delta V$  termination once every 17s. The sample is an average of voltage measurements taken 570 $\mu s$  apart.The IC takes 32 measurements in PVD mode and 16 measurements in - $\Delta V$  mode. The resulting sample periods (9.17 and 18.18ms, respectively) filter out harmonics centered around 55 and 109Hz. This technique minimizes the effect of any AC line ripple that may feed through the power supply from either 50 or 60Hz AC sources. Tolerance on all timing is  $\pm 20\%$ .

#### Voltage Termination Hold-off

A hold-off period occurs at the start of fast charging. During the hold-off time, the PVD and  $\mbox{-}\Delta V$  terminations are disabled. This avoids premature termination on the voltage spikes sometimes produced by older batteries when fast-charge current is first applied. Maximum voltage and temperature terminations are not affected by the hold-off period.

### Maximum Voltage, Temperature, and Time

Any time the voltage on the BAT pin exceeds the maximum cell voltage,  $V_{MCV}$ , fast charge or optional top-off charge is terminated.

Maximum temperature termination occurs anytime the voltage on the TS pin falls below the temperature cut-off threshold  $V_{\rm TCO}$ .

Maximum charge time is configured using the TM pin. Time settings are available for corresponding charge rates of C/2, 1C, and 2C. Maximum time-out termination is enforced on the fast-charge phase, then reset, and enforced again on the top-off phase, if selected. There is no time limit on the trickle-charge phase.

#### **Top-off Charge**

An optional top-off charge phase may be selected to follow fast charge termination for 1C and C/2 rates. This phase may be necessary on NiMH or other battery chemistries that have a tendency to terminate charge prior to reaching full capacity. With top-off enabled, charging continues at a reduced rate after fast-charge termination for a period of time selected by the TM pin. (See Table 1.) During top-off, the CC

pin is modulated at a duty cycle of  $286\mu s$  active for every  $4290\mu s$  inactive. This modulation results in an average rate 1/16th that of the fast charge rate. Maximum voltage, time, and temperature are the only termination methods enabled during top-off.

### **Pulse-Trickle Charge**

Pulse-trickle is used to compensate for self-discharge while the battery is idle in the charger. The battery is pulse-trickle charged by driving the CC pin active for a period of  $286\mu s$  for every 18.0ms of inactivity for 1C and 2C selections, and  $286\mu s$  for every 8.86ms of inactivity for C/2 selection. This results in a trickle rate of C/64 for the top-off enabled mode and C/32 otherwise.

#### TM Pin

The TM pin is a three-level pin used to select the charge timer, top-off, voltage termination mode, trickle rate, and voltage hold-off period options. Table 1 describes the states selected by the TM pin. The midlevel selection input is developed by a resistor divider between  $V_{CC}$  and ground that fixes the voltage on TM at  $V_{CC}/2\pm0.5V.$  See Figure 4.

### **Charge Status Indication**

$\frac{A \text{ fast}}{\text{LED}}$  pin goes low. The  $\overline{\text{LED}}$  pin is driven to the high-Z state for all conditions other than fast charge. Figure 2 outlines the state of the  $\overline{\text{LED}}$  pin during charge.

### **Charge Inhibit**

Fast charge and top-off may be inhibited by using the INH pin. When high, INH suspends all fast charge and top-off activity and the internal charge timer. INH freezes the current state of  $\overline{\text{LED}}$  until inhibit is removed. Temperature monitoring is not affected by the INH pin. During charge inhibit, the bq2002/F continues to pulse-trickle charge the battery per the TM selection. When INH returns low, charge control and the charge timer resume from the point where INH became active.

### **Low-Power Mode**

The IC enters a low-power state when  $V_{BAT}$  is driven above the power-down threshold ( $V_{PD}$ ) where

$$V_{PD} = V_{CC} - (1V \pm 0.5V)$$

Both the CC pin and the  $\overline{LED}$  pin are driven to the high-Z state. The operating current is reduced to less than  $1\mu A$  in this mode. When  $V_{BAT}$  returns to a value below  $V_{PD}$ , the IC pulse-trickle charges until the next new charge cycle begins.

## bq2002/F

## **Absolute Maximum Ratings**

| Symbol              | Parameter                                                             | Minimum | Maximum | Unit | Notes       |

|---------------------|-----------------------------------------------------------------------|---------|---------|------|-------------|

| Vcc                 | V <sub>CC</sub> relative to V <sub>SS</sub>                           | -0.3    | +7.0    | V    |             |

| $V_{\mathrm{T}}$    | DC voltage applied on any pin excluding $V_{CC}$ relative to $V_{SS}$ | -0.3    | +7.0    | V    |             |

| T <sub>OPR</sub>    | Operating ambient temperature                                         | 0       | +70     | °C   | Commercial  |

| T <sub>STG</sub>    | Storage temperature                                                   | -40     | +85     | °C   |             |

| T <sub>SOLDER</sub> | Soldering temperature                                                 | -       | +260    | °C   | 10 sec max. |

| T <sub>BIAS</sub>   | Temperature under bias                                                | -40     | +85     | °C   |             |

Note:

Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

## DC Thresholds (TA = 0 to 70 $^{\circ}\text{C}; \, \text{V}_{\text{CC}}\,\pm20\%)$

| Symbol           | Parameter                             | Rating                | Tolerance | Unit | Notes                                                                          |

|------------------|---------------------------------------|-----------------------|-----------|------|--------------------------------------------------------------------------------|

| V <sub>TCO</sub> | Temperature cutoff                    | 0.5 * V <sub>CC</sub> | ±5%       | V    | $V_{TS} \leq V_{TCO} \ \ inhibits/terminates \\ fast \ charge \ and \ top-off$ |

| V <sub>MCV</sub> | Maximum cell voltage                  | 2                     | ±5%       | V    | $V_{BAT} \geq V_{MCV} \ inhibits/terminates \\ fast \ charge \ and \ top-off$  |

| -Δ <b>V</b>      | BAT input change for -ΔV detection    | -12                   | ±3        | mV   |                                                                                |

| PVD              | BAT input change for<br>PVD detection | -2.5                  | ±2.5      | mV   |                                                                                |

# Recommended DC Operating Conditions (TA = 0 to 70°C)

| Symbol            | Condition                      | Minimum                           | Typical | Maximum                           | Unit | Notes                                                                                                                                       |

|-------------------|--------------------------------|-----------------------------------|---------|-----------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>   | Supply voltage                 | 4.0                               | 5.0     | 6.0                               | V    |                                                                                                                                             |

| V <sub>DET</sub>  | -ΔV, PVD detect voltage        | 1                                 | -       | 2                                 | V    |                                                                                                                                             |

| V <sub>BAT</sub>  | Battery input                  | 0                                 | -       | V <sub>CC</sub>                   | V    |                                                                                                                                             |

| V <sub>TS</sub>   | Thermistor input               | 0.5                               | -       | $V_{CC}$                          | V    | V <sub>TS</sub> < 0.5V prohibited                                                                                                           |

| *,                | Logic input high               | 0.5                               | -       | -                                 | V    | INH                                                                                                                                         |

| $V_{IH}$          | Logic input high               | V <sub>CC</sub> - 0.5             | -       | -                                 | V    | TM                                                                                                                                          |

| V <sub>IM</sub>   | Logic input mid                | $\frac{\mathrm{V_{CC}}}{2} - 0.5$ | -       | $\frac{\mathrm{V_{CC}}}{2} + 0.5$ | v    | TM                                                                                                                                          |

|                   | Logic input low                | -                                 | -       | 0.1                               | V    | INH                                                                                                                                         |

| $V_{\mathrm{IL}}$ | Logic input low                | -                                 | -       | 0.5                               | V    | TM                                                                                                                                          |

| Vol               | Logic output low               | -                                 | -       | 0.8                               | V    | TED, CC, I <sub>OL</sub> = 10mA                                                                                                             |

| $V_{PD}$          | Power down                     | V <sub>CC</sub> - 1.5             | -       | V <sub>CC</sub> - 0.5             | V    | $\begin{split} &V_{BAT} \geq V_{PD} \ max. \ powers \\ &down \ bq2002/F; \\ &V_{BAT} < V_{PD} \ min. = \\ &normal \ operation. \end{split}$ |

| $I_{CC}$          | Supply current                 | -                                 | -       | 250                               | μΑ   | Outputs unloaded, $V_{CC} = 5.1V$                                                                                                           |

| $I_{SB}$          | Standby current                | -                                 | -       | 1                                 | μA   | $V_{CC} = 5.1V$ , $V_{BAT} = V_{PD}$                                                                                                        |

| $I_{OL}$          | TED, CC sink                   | 10                                | -       | -                                 | mA   | $@V_{\rm OL} = V_{\rm SS} + 0.8V$                                                                                                           |

| $I_{L}$           | Input leakage                  | -                                 | -       | ±1                                | μА   | INH, CC, V = V <sub>SS</sub> to V <sub>CC</sub>                                                                                             |

| I <sub>OZ</sub>   | Output leakage in high-Z state | -5                                | -       | -                                 | μА   | LED, CC                                                                                                                                     |

# bq2002/F

## Impedance

| Symbol           | Parameter               | Minimum | Typical | Maximum | Unit      |

|------------------|-------------------------|---------|---------|---------|-----------|

| R <sub>BAT</sub> | Battery input impedance | 50      | -       | -       | ΜΩ        |

| R <sub>TS</sub>  | TS input impedance      | 50      | -       | -       | $M\Omega$ |

# Timing $(T_A = 0 \text{ to } +70^{\circ}\text{C}; V_{CC} \pm 10\%)$

| Symbol           | Parameter           | Minimum | Typical | Maximum | Unit | Notes |

|------------------|---------------------|---------|---------|---------|------|-------|

| d <sub>FCV</sub> | Base time variation | -20     | -       | 20      | %    |       |

Note: Typical is at  $T_A = 25$ °C,  $V_{CC} = 5.0$ V.

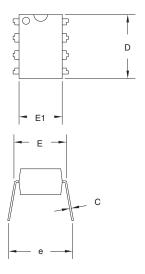

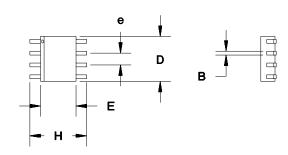

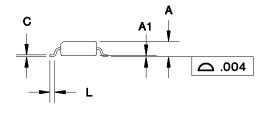

# 8-Pin DIP (PN)

## 8-Pin PN (0.300" DIP)

|           |       | ,     |        |        |

|-----------|-------|-------|--------|--------|

|           | Inc   | hes   | Millin | neters |

| Dimension | Min.  | Max.  | Min.   | Max.   |

| A         | 0.160 | 0.180 | 4.06   | 4.57   |

| A1        | 0.015 | 0.040 | 0.38   | 1.02   |

| В         | 0.015 | 0.022 | 0.38   | 0.56   |

| B1        | 0.055 | 0.065 | 1.40   | 1.65   |

| С         | 0.008 | 0.013 | 0.20   | 0.33   |

| D         | 0.350 | 0.380 | 8.89   | 9.65   |

| Е         | 0.300 | 0.325 | 7.62   | 8.26   |

| E1        | 0.230 | 0.280 | 5.84   | 7.11   |

| e         | 0.300 | 0.370 | 7.62   | 9.40   |

| G         | 0.090 | 0.110 | 2.29   | 2.79   |

| L         | 0.115 | 0.150 | 2.92   | 3.81   |

| S         | 0.020 | 0.040 | 0.51   | 1.02   |

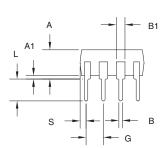

# 8-Pin SOIC Narrow (SN)

## 8-Pin SN (0.150" SOIC)

|           | Inc   | hes   | Millin | neters |

|-----------|-------|-------|--------|--------|

| Dimension | Min.  | Max.  | Min.   | Max.   |

| A         | 0.060 | 0.070 | 1.52   | 1.78   |

| A1        | 0.004 | 0.010 | 0.10   | 0.25   |

| В         | 0.013 | 0.020 | 0.33   | 0.51   |

| С         | 0.007 | 0.010 | 0.18   | 0.25   |

| D         | 0.185 | 0.200 | 4.70   | 5.08   |

| Е         | 0.150 | 0.160 | 3.81   | 4.06   |

| e         | 0.045 | 0.055 | 1.14   | 1.40   |

| Н         | 0.225 | 0.245 | 5.72   | 6.22   |

| L         | 0.015 | 0.035 | 0.38   | 0.89   |

# bq2002/F

### **Data Sheet Revision History**

| Change No. <sup>(1)</sup> | Page No. | Description                                                                                                                       | Nature of Change         |

|---------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1                         | 3        | Was: Table 1 gave the bq2002/F Operational Summary. Is: Figure 2 gives the bq2002/F Operational Summary.                          | Changed table to figure. |

| 1                         | 5        | Added Termination column to table and Top-off values.                                                                             | Added column and values. |

| 2                         | All      | Revised and expanded this data sheet to include bq2002F                                                                           |                          |

| 3                         | 1        | Revised and expanded this data sheet to include bq2002F                                                                           |                          |

| 4                         | 5        | Voltage Sampling — From: Average of voltage measurements taken 57us apart. To: Average of voltage measurements taken 570us apart. |                          |

Change 1 = Sept. 1996 changes from July 1994. Change 2 = Aug. 1997 changes from Sept. 1996. Change 3 = Jan. 1999 changes from Aug. 1997. Change 4 = April 2009 changes from Jan 1999.

www.ti.com 23-May-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|----------------|-----------------------|------|---------------|----------------------------|--------------|--------------|

|                       | (1)    | (2)           |                |                       | (3)  | Ball material |                            |              | (6)          |

|                       |        |               |                |                       |      | (4)           | (5)                        |              |              |

| BQ2002FSN             | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002F        |

| BQ2002FSN.B           | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002F        |

| BQ2002FSNTR           | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002F        |

| BQ2002FSNTR.B         | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002F        |

| BQ2002SN              | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002         |

| BQ2002SN.B            | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002         |

| BQ2002SNG4            | Active | Production    | SOIC (D)   8   | 75   TUBE             | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002         |

| BQ2002SNTR            | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002         |

| BQ2002SNTR.B          | Active | Production    | SOIC (D)   8   | 2500   LARGE T&R      | Yes  | NIPDAU        | Level-1-260C-UNLIM         | 0 to 70      | 2002         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

### PACKAGE OPTION ADDENDUM

www.ti.com 23-May-2025

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

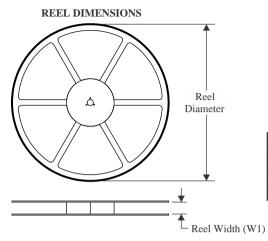

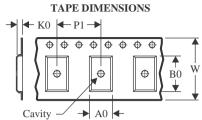

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

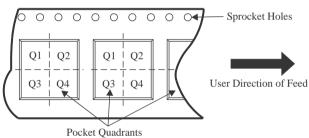

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |   |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| BQ2002FSNTR | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| BQ2002SNTR  | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 23-May-2025

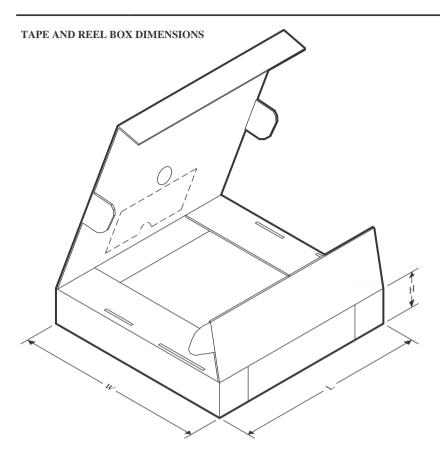

### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| BQ2002FSNTR | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| BQ2002SNTR  | SOIC         | D               | 8    | 2500 | 340.5       | 338.1      | 20.6        |

## **PACKAGE MATERIALS INFORMATION**

www.ti.com 23-May-2025

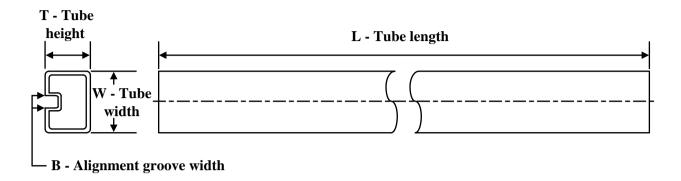

### **TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| BQ2002FSN   | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| BQ2002FSN.B | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| BQ2002SN    | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| BQ2002SN.B  | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

| BQ2002SNG4  | D            | SOIC         | 8    | 75  | 507    | 8      | 3940   | 4.32   |

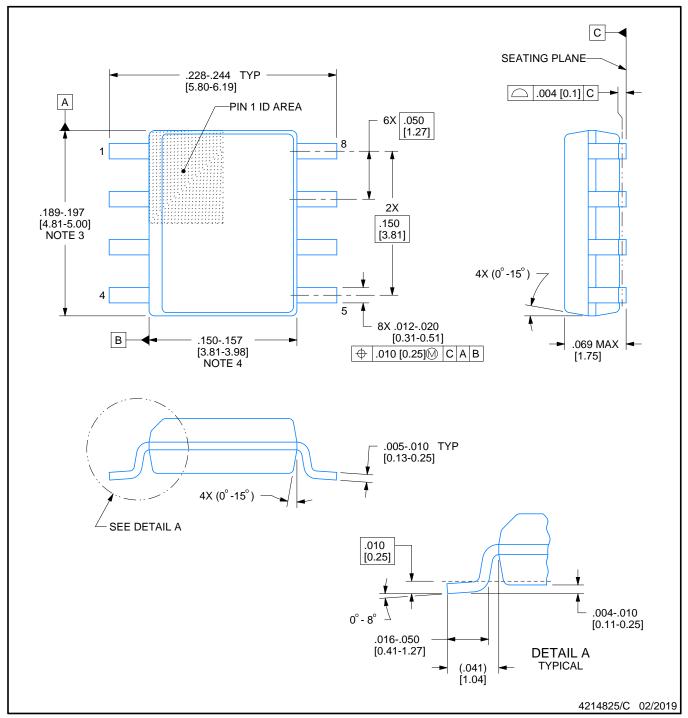

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES:

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

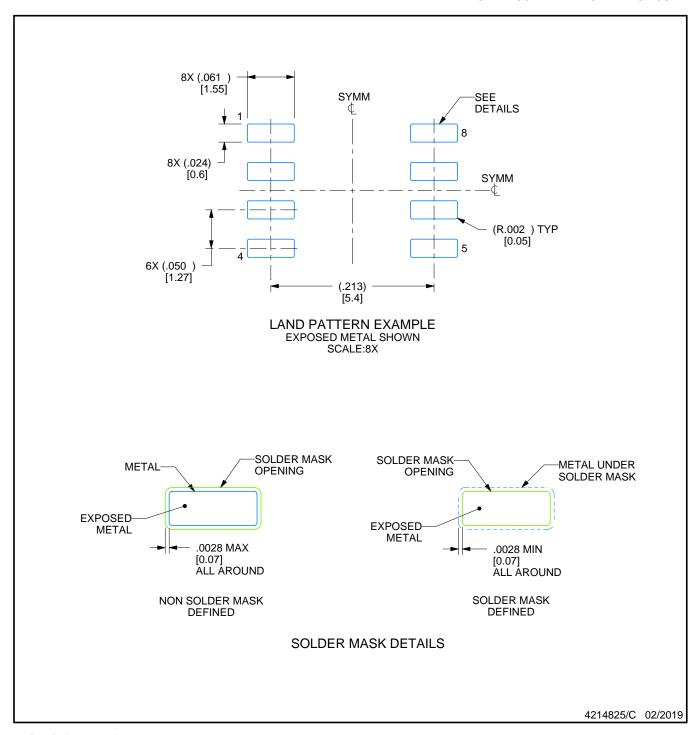

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

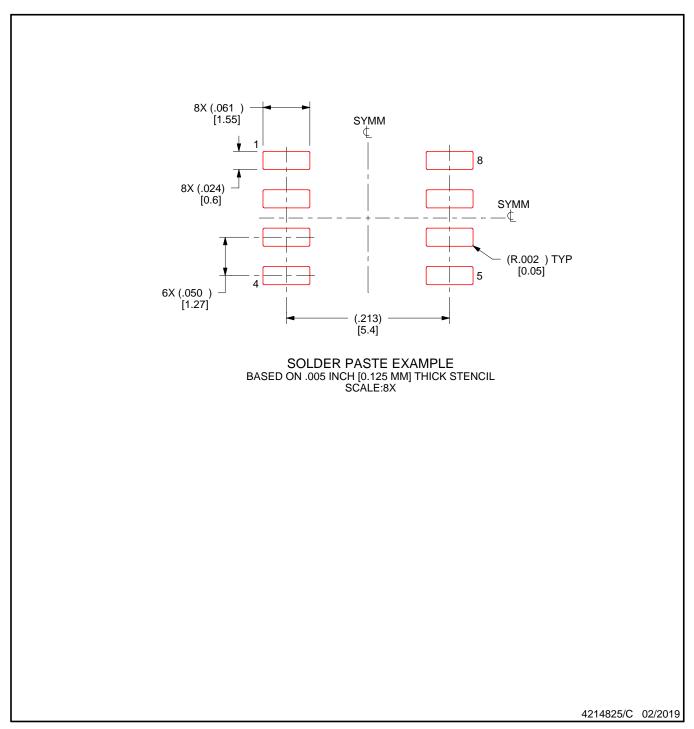

SMALL OUTLINE INTEGRATED CIRCUIT

### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025. Texas Instruments Incorporated