ADS8166, ADS8167, ADS8168

# SBAS817D - NOVEMBER 2017 - REVISED JUNE 2024

# ADS816x 8-Channel, 16-Bit, 1MSPS, SAR ADC With Direct Sensor Interface

### 1 Features

- Compact low-power data acquisition system:

- MUX breakout enables single external driver amplifier

- 16-bit SAR ADC

- Low-drift integrated reference and buffer

- 0.5 × V<sub>RFF</sub> output for analog input DC biasing

- Excellent AC and DC performance:

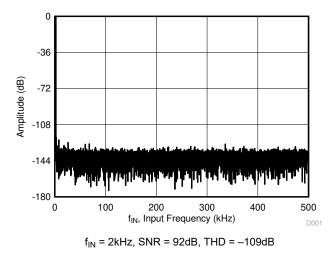

- SNR: 92dB, THD: –110dB

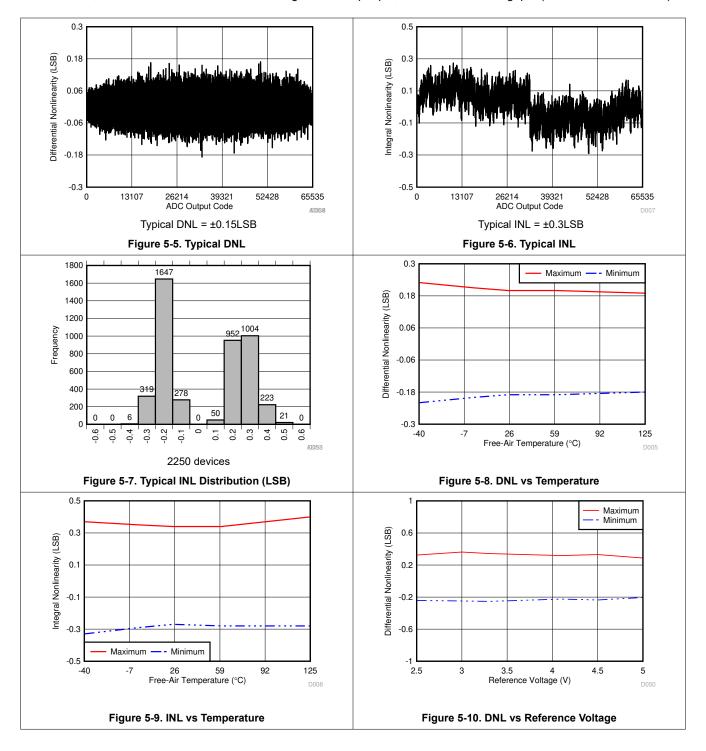

- INL: ±0.3LSB, 16-bit no missing codes

- Multiplexer with channel sequencer:

- Multiple channel-sequencing options:

- Manual mode, on-the-fly mode, auto sequence mode, custom channel sequencing

- Fast response time with on-the-fly mode

- System monitoring features:

- Per channel programmable window comparator

- False trigger avoidance with programmable hysteresis

- Enhanced-SPI digital interface:

- 1MSPS throughput with 16MHz SCLK

- High-speed, 50MHz digital interface

- Wide operating range:

- External V<sub>RFF</sub> input range: 2.5V to 5V

- AVDD from 3V to 5.5V

- DVDD from 1.65V to 5.5V

- -40°C to +125°C temperature range

# 2 Applications

- Chemistry, gas analyzers

- Anesthesia delivery systems

- Mixed modules (AI, AO, DI, DO)

- Intra-DC interconnects (metro)

# 3 Description

The ADS816x is a family of 16-bit, 8-channel, high-precision successive approximation register (SAR) analog-to-digital converters (ADCs). The ADCs operate from a single 5V supply with a 1MSPS (ADS8168), 500kSPS (ADS8167), and 250kSPS (ADS8166) total throughput.

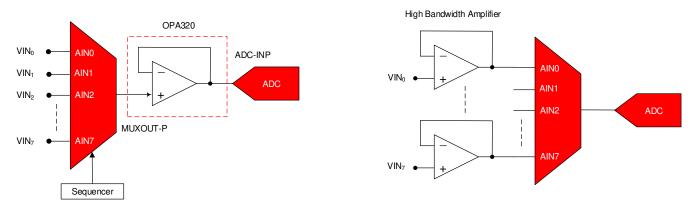

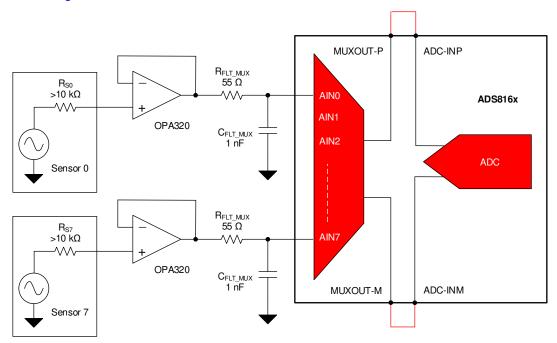

The input multiplexer supports extended settling time, which makes driving the analog inputs easier. The output of the multiplexer and ADC analog inputs are available as device pins. This configuration allows one ADC driver op amp to be used for all eight analog inputs of the multiplexer.

The ADS816x features a digital window comparator with programmable high and low alarm thresholds per analog input channel. The single op-amp solution with programmable alarm thresholds enables low power, low cost, and smallest form-factor applications.

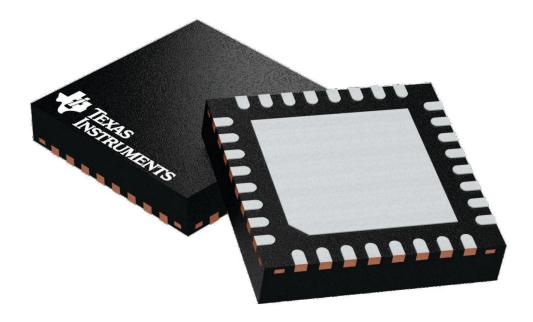

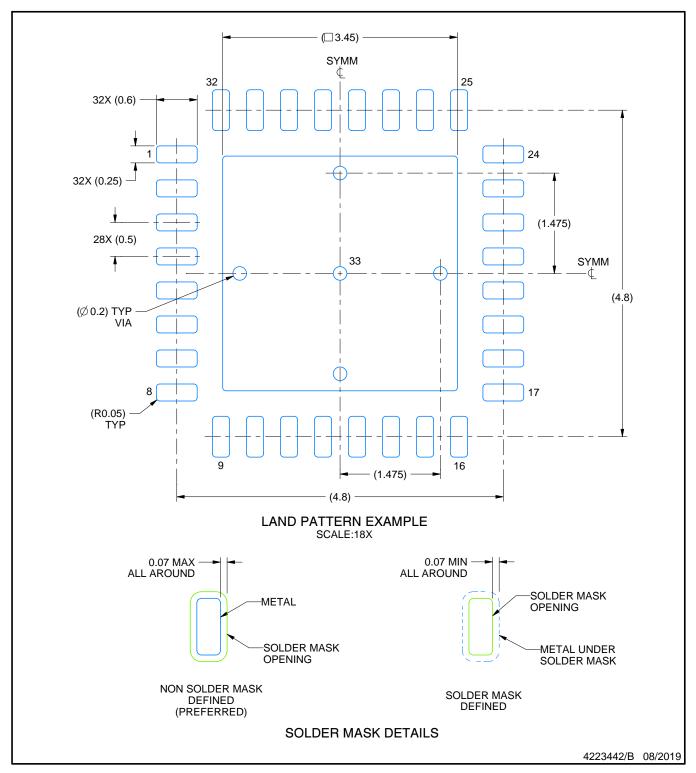

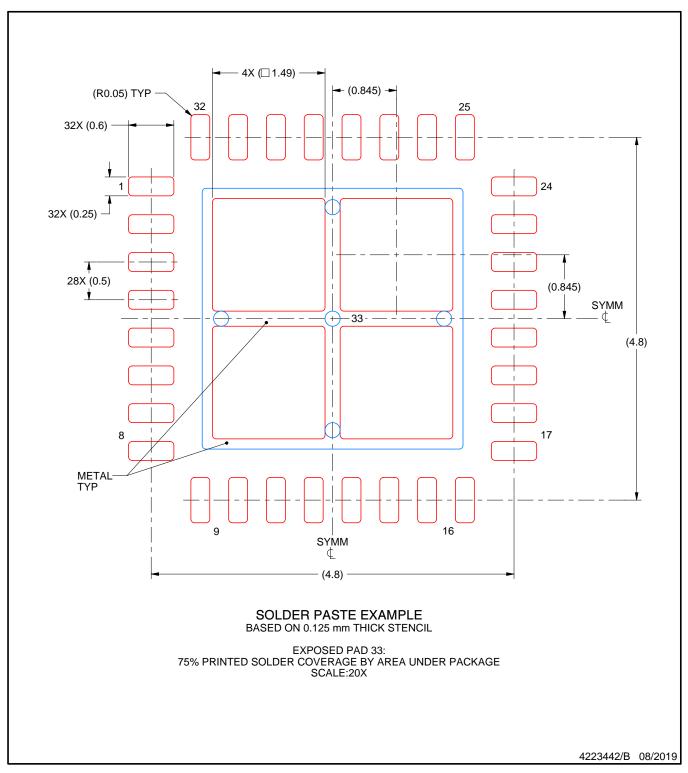

## **Package Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | PACKAGE SIZE <sup>(2)</sup> |

|-------------|------------------------|-----------------------------|

| ADS816x     | RHB (VQFN, 32)         | 5mm × 5mm                   |

- For more information, see the Mechanical, Packaging, and Orderable Information.

- The package size (length × width) is a nominal value and includes pins, where applicable.

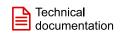

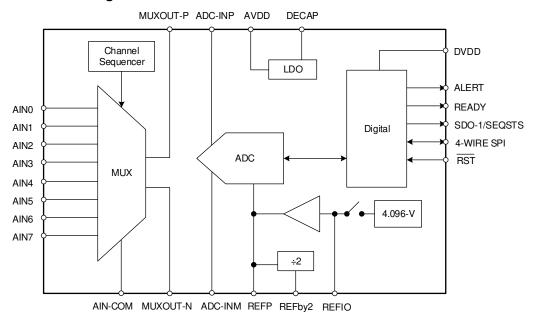

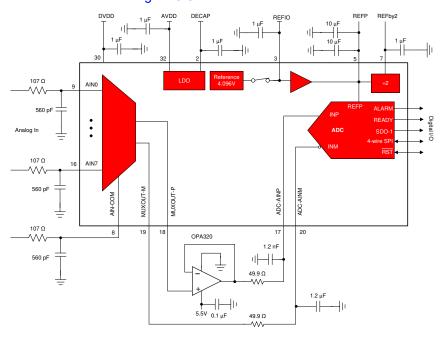

**ADS816x Block Diagram**

# **Table of Contents**

| 1 Features1                           | 7.1 Interface and Hardw                  |

|---------------------------------------|------------------------------------------|

| 2 Applications1                       | 7.2 Device Calibration F                 |

| 3 Description1                        | 7.3 Analog Input Config                  |

| 4 Pin Configuration and Functions3    | 7.4 Channel Sequence                     |

| 5 Specifications5                     | 7.5 Digital Window Com                   |

| 5.1 Absolute Maximum Ratings5         | Registers Map                            |

| 5.2 ESD Ratings5                      | 8 Application and Impler                 |

| 5.3 Thermal Information5              | 8.1 Application Informat                 |

| 5.4 Recommended Operating Conditions6 | 8.2 Typical Applications                 |

| 5.5 Electrical Characteristics7       | 8.3 Layout                               |

| 5.6 Timing Requirements9              | 9 Device and Documenta                   |

| 5.7 Switching Characteristics10       | 9.1 Documentation Sup                    |

| 5.8 Timing Diagrams11                 | 9.2 Receiving Notification               |

| 5.9 Typical Characteristics13         | <ol><li>9.3 Support Resources.</li></ol> |

| 6 Detailed Description18              | 9.4 Trademarks                           |

| 6.1 Overview                          | 9.5 Electrostatic Discha                 |

| 6.2 Functional Block Diagram18        | 9.6 Glossary                             |

| 6.3 Feature Description19             | 10 Revision History                      |

| 6.4 Device Functional Modes27         | 11 Mechanical, Packagin                  |

| 6.5 Programming35                     | Information                              |

| 7 Register Maps43                     |                                          |

| 7.1 Interface and Hardware Configuration Registers  | 43   |

|-----------------------------------------------------|------|

| 7.2 Device Calibration Registers                    | 48   |

| 7.3 Analog Input Configuration Registers            | . 51 |

| 7.4 Channel Sequence Configuration Registers Map    | 53   |

| 7.5 Digital Window Comparator Configuration         |      |

| Registers Map                                       | . 60 |

| 8 Application and Implementation                    | . 68 |

| 8.1 Application Information                         |      |

| 8.2 Typical Applications                            | . 70 |

| 8.3 Layout                                          | . 72 |

| 9 Device and Documentation Support                  | 75   |

| 9.1 Documentation Support                           | . 75 |

| 9.2 Receiving Notification of Documentation Updates | 75   |

| 9.3 Support Resources                               | . 75 |

| 9.4 Trademarks                                      | 75   |

| 9.5 Electrostatic Discharge Caution                 | 75   |

| 9.6 Glossary                                        | 75   |

| 10 Revision History                                 | . 76 |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 77 |

|                                                     |      |

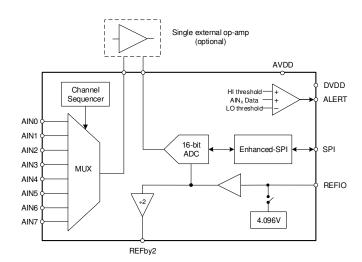

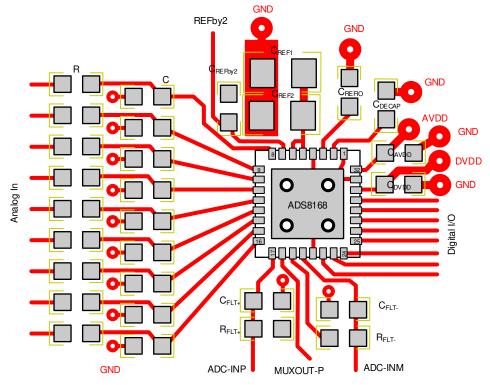

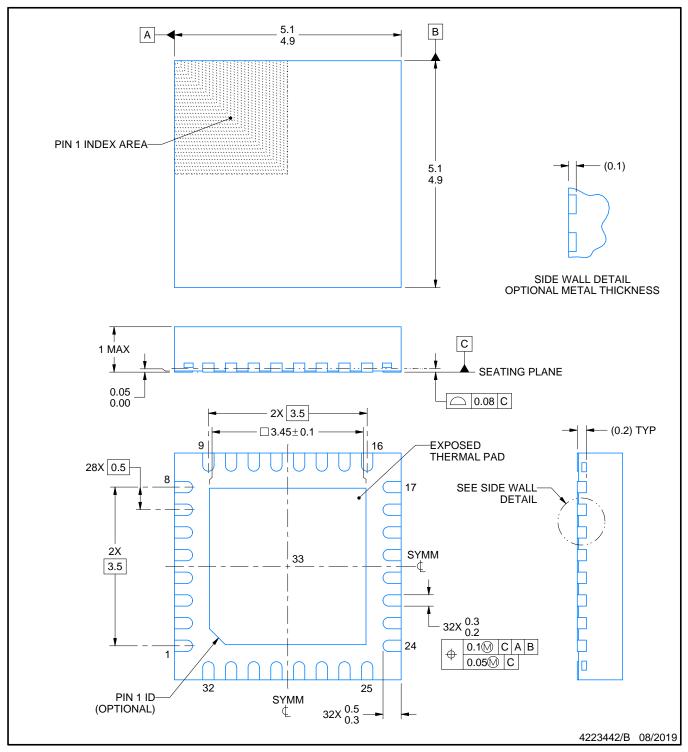

# **4 Pin Configuration and Functions**

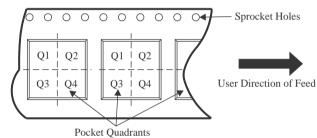

Figure 4-1. RHB Package, 32-Pin VQFN (Top View)

**Table 4-1. Pin Functions**

| PIN     |           |                |                                                                                                                                                                                                                                                             |

|---------|-----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO.       | FUNCTION       | DESCRIPTION                                                                                                                                                                                                                                                 |

| ADC-INM | 20        | Analog input   | Negative ADC analog input.                                                                                                                                                                                                                                  |

| ADC-INP | 17        | Analog input   | Positive ADC analog input.                                                                                                                                                                                                                                  |

| AIN0    | 9         | Analog input   | Analog input channel 0.                                                                                                                                                                                                                                     |

| AIN1    | 10        | Analog input   | Analog input channel 1.                                                                                                                                                                                                                                     |

| AIN2    | 11        | Analog input   | Analog input channel 2.                                                                                                                                                                                                                                     |

| AIN3    | 12        | Analog input   | Analog input channel 3.                                                                                                                                                                                                                                     |

| AIN4    | 13        | Analog input   | Analog input channel 4.                                                                                                                                                                                                                                     |

| AIN5    | 14        | Analog input   | Analog input channel 5.                                                                                                                                                                                                                                     |

| AIN6    | 15        | Analog input   | Analog input channel 6.                                                                                                                                                                                                                                     |

| AIN7    | 16        | Analog input   | Analog input channel 7.                                                                                                                                                                                                                                     |

| AIN-COM | 8         | Analog input   | Common analog input.                                                                                                                                                                                                                                        |

| ALERT   | 22        | Digital output | Digital ALERT output; active high. This pin is the output of the logical OR of the enabled channel ALERTs.                                                                                                                                                  |

| AVDD    | 32        | Power supply   | Analog power-supply pin. Connect a 1µF capacitor from this pin to GND.                                                                                                                                                                                      |

| CS      | 23        | Digital input  | Chip-select input pin; active low. The device starts converting the active input channel on the rising edge of $\overline{CS}$ . The device takes control of the data bus when $\overline{CS}$ is low. The SDO-x pins go Hi-Z when $\overline{CS}$ is high. |

| DECAP   | 2         | Power supply   | Connect a 1µF capacitor to GND for the internal power supply.                                                                                                                                                                                               |

| DVDD    | 30        | Power supply   | Interface power-supply pin. Connect a 1µF capacitor from this pin to GND.                                                                                                                                                                                   |

| GND     | 1, 21, 31 | Power supply   | Ground.                                                                                                                                                                                                                                                     |

# **Table 4-1. Pin Functions (continued)**

| PIN              |      |                     |                                                                                                                                                                                                                                                                  |  |

|------------------|------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | NO.  | FUNCTION            | DESCRIPTION                                                                                                                                                                                                                                                      |  |

| MUXOUT-M         | 19   | Analog output       | MUX negative analog output.                                                                                                                                                                                                                                      |  |

| MUXOUT-P         | 18   | Analog output       | MUX positive analog output.                                                                                                                                                                                                                                      |  |

| READY            | 28   | Digital output      | Multifunction output pin. When $\overline{\text{CS}}$ is held high, READY reflects the device conversion status. READY is low when a conversion is in process. When $\overline{\text{CS}}$ is low, the status of READY depends on the output protocol selection. |  |

| REFby2           | 7    | Analog output       | The output voltage on this pin is equal to half the voltage on the REFP pin. Connect a $1\mu F$ capacitor from this pin to GND.                                                                                                                                  |  |

| REFIO            | 3    | Analog input/output | External reference voltage input; internal reference is a 4.096V output. Connect a 1µF capacitor from this pin to GND.                                                                                                                                           |  |

| REFM             | 4    | Analog input        | Reference ground potential; short this pin to GND externally.                                                                                                                                                                                                    |  |

| REFP             | 5, 6 | Analog input/output | Reference buffer output, ADC reference input. Short pins 5 and 6 together.                                                                                                                                                                                       |  |

| RST              | 29   | Digital input       | Asynchronous reset input pin. A low pulse on the RST pin resets the device. All register bits return to the default states.                                                                                                                                      |  |

| SCLK             | 25   | Digital input       | Clock input pin for the serial interface. All system-synchronous data transfer protocols are timed with respect to the SCLK signal.                                                                                                                              |  |

| SDI              | 24   | Digital input       | Serial data input pin. This pin transfers data or commands into the device.                                                                                                                                                                                      |  |

| SDO-0            | 26   | Digital output      | Serial communication pin: data output 0.                                                                                                                                                                                                                         |  |

| SDO-1/<br>SEQSTS | 27   | Digital output      | Multifunction output pin. By default, this pin indicates the channel scanning status in the auto and custom channel sequence modes.  In dual SDO data transfer mode, this pin functions as a serial communication pin: data output 1.                            |  |

| Thermal pad      |      | Supply              | Exposed thermal pad; connect to GND.                                                                                                                                                                                                                             |  |

# 5 Specifications

# 5.1 Absolute Maximum Ratings

over operating ambient temperature range (unless otherwise noted)(1)

|                                                                     | MIN        | MAX        | UNIT |

|---------------------------------------------------------------------|------------|------------|------|

| AVDD to GND                                                         | -0.3       | 7          | V    |

| DVDD to GND                                                         | -0.3       | 7          | V    |

| AINx <sup>(2)</sup> , AIN-COM, MUXOUT-P, MUXOUT-M, ADC-INP, ADC-INM | GND – 0.3  | AVDD + 0.3 | V    |

| REFP                                                                | REFM - 0.3 | AVDD + 0.3 | V    |

| REFIO                                                               | REFM - 0.3 | AVDD + 0.3 | V    |

| REFM                                                                | GND – 0.1  | GND + 0.1  | V    |

| Digital input pins                                                  | GND – 0.3  | DVDD + 0.3 | V    |

| Digital output pins                                                 | GND – 0.3  | DVDD + 0.3 | V    |

| Input current to any pin except supply pins                         | -10        | 10         | mA   |

| Junction temperature, T <sub>J</sub>                                | -40        | 125        | °C   |

| Storage temperature, T <sub>stg</sub>                               | -65        | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 5.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

| \ /                | Floatroatatic disabores | Human body model (HBM), per ANSI/ESDA/<br>JEDEC JS-001, all pins <sup>(1)</sup>          | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

#### 5.3 Thermal Information

|                        |                                              | ADS816x    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC(1)                            | RHB (VQFN) | UNIT |

|                        |                                              | 32 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 29.5       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 18.6       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 10.2       | °C/W |

| $\Psi_{JT}$            | Junction-to-top characterization parameter   | 0.2        | °C/W |

| $\Psi_{JB}$            | Junction-to-board characterization parameter | 10.2       | °C/W |

| R <sub>θJC(bot)</sub>  | Junction-to-case (bottom) thermal resistance | 1.3        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application note.

<sup>(2)</sup> AINx refers to AIN0, AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, and AIN7 pins.

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **5.4 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER                | TEST CONDITIONS                                                  | MIN                        | TYP             | MAX                    | UNIT |  |

|--------------------|--------------------------|------------------------------------------------------------------|----------------------------|-----------------|------------------------|------|--|

| POWER              | SUPPLY                   |                                                                  | 1                          |                 |                        |      |  |

| AVDD               | Internal reference       |                                                                  | 4.5                        | 5               | 5.5                    | V    |  |

| AVDD               | External reference       |                                                                  | 3                          | 5               | 5.5                    | V    |  |

| Operating          |                          |                                                                  | 1.65                       | 3               | 5.5                    | V    |  |

| DVDD               | Specified throughput     |                                                                  | 2.35                       | 3               | 5.5                    | V    |  |

| ANALOG             | G INPUTS (Single-Ended C | Configuration)                                                   | <u> </u>                   |                 |                        |      |  |

| FSR                | Full-scale input range   |                                                                  | 0                          |                 | $V_{REF}$              | V    |  |

| V <sub>IN</sub>    |                          | AINx <sup>(1)</sup> to REFM and CHx_CHy_CFG <sup>(2)</sup> = 00b | -0.1                       | ,               | V <sub>REF</sub> + 0.1 |      |  |

|                    | Absolute input voltage   | AINy <sup>(3)</sup> to REFM and CHx_CHy_CFG = 01b                | -0.1                       |                 | 0.1                    | V    |  |

|                    |                          | AIN-COM                                                          | -0.1                       | ,               | 0.1                    |      |  |

| ANALOG             | G INPUTS (Pseudo-Differe | ntial Configuration)                                             | 1                          |                 |                        |      |  |

| FSR                | Full-scale input range   |                                                                  | -V <sub>REF</sub> / 2      |                 | V <sub>REF</sub> / 2   | V    |  |

|                    |                          | AINx to REFM and CHx_CHy_CFG = 00b                               | -0.1                       | ,               | V <sub>REF</sub> + 0.1 |      |  |

| $V_{\text{IN}}$    | Absolute input voltage   | AINy to REFM and CHx_CHy_CFG = 10b                               | V <sub>REF</sub> / 2 – 0.1 | V <sub>RE</sub> | <sub>F</sub> / 2 + 0.1 | V    |  |

|                    |                          | AIN-COM                                                          | V <sub>REF</sub> / 2 – 0.1 | V <sub>RE</sub> | <sub>F</sub> / 2 + 0.1 |      |  |

| EXTERN             | IAL REFERENCE INPUT      |                                                                  | •                          |                 |                        |      |  |

| V <sub>REFIO</sub> | REFIO input voltage      | REFIO configured as input pin                                    | 2.5                        | А               | VDD – 0.3              | V    |  |

| TEMPER             | RATURE RANGE             |                                                                  | •                          |                 |                        |      |  |

| T <sub>A</sub>     | Ambient temperature      |                                                                  | -40                        | 25              | 125                    | °C   |  |

<sup>(1)</sup> AINx refers to analog inputs AIN0, AIN1, AIN2, AIN3, AIN4, AIN5, AIN6, and AIN7.

<sup>(2)</sup> CHx\_CHy\_CFG bits set the analog input configuration as single-ended or pseudo-differential pair. See the AIN\_CFG register for more details.

<sup>(3)</sup> AlNy refers to analog inputs AlN1, AlN3, AlN5, and AlN7 when CHx\_CHy\_CFG = 01b or 10b. See the Multiplexer Configurations section for more details.

#### 5.5 Electrical Characteristics

at AVDD = 5V, DVDD = 1.65V to 5.5V, REFIO configured as output pin, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40$ °C to +125°C; typical values at  $T_A = 25$ °C

|                         | and maximum values at $T_A = -4$ PARAMETER | TEST CONDITIONS                                       | MIN    | TYP                   | MAX      | UNIT   |

|-------------------------|--------------------------------------------|-------------------------------------------------------|--------|-----------------------|----------|--------|

| ANALOG IN               | IPUTS                                      |                                                       |        |                       |          |        |

| C <sub>SH</sub>         | ADC Input capacitance                      |                                                       |        | 60                    |          | pF     |

| C <sub>INMUX</sub>      | MUX Input capacitance                      |                                                       |        | 13                    |          | pF     |

| I <sub>LMUX_ON</sub>    | MUX input on-channel leakage current       | REFM < V <sub>IN</sub> < REFP                         | -750   | ±10                   | 750      | nA     |

| DC PERFO                | RMANCE                                     | <u>I</u>                                              |        |                       |          |        |

|                         | Resolution                                 |                                                       |        | 16                    |          | Bits   |

| NMC                     | No missing codes                           |                                                       | 16     |                       |          |        |

| INL                     | Integral nonlinearity                      |                                                       | -0.8   | ±0.35                 | 0.8      | LSB    |

| DNL                     | Differential nonlinearity                  |                                                       | -0.5   | ±0.2                  | 0.5      | LSB    |

| V <sub>OS</sub>         | Input offset error                         |                                                       | -10    | ±0.5                  | 10       | LSB    |

| - 03                    | Input offset error match                   |                                                       | -1     | ±0.5                  | 1        | LSB    |

| dV <sub>OS</sub> /dT    | Input offset thermal drift                 |                                                       |        | 0.25                  | <u> </u> | μV/°C  |

| G <sub>E</sub>          | Gain error                                 | Referred to REFIO                                     | -0.06  | ±0.002                | 0.06     | •      |

| <u>UE</u>               | Gain error match                           | Referred to REFIO                                     | -0.005 | ±0.0025               | 0.005    |        |

| dG <sub>E</sub> /dT     | Gain error thermal drift                   | Referred to REFIO                                     | 0.000  | ±1                    | 0.000    | ppm/°C |

| TNS                     | Transition noise                           | $V_{IN} = V_{REF} / 2$                                |        | 0.6                   |          | LSB    |

| AC PERFO                |                                            | VIN - VREF / Z                                        |        | 0.0                   |          | LOD    |

| SINAD                   | Signal-to-noise + distortion               | f <sub>IN</sub> = 2kHz                                | 91.6   | 93.5                  |          | dB     |

| SNR                     | Signal-to-noise + distortion               | f <sub>IN</sub> = 2kHz                                | 91.8   | 93.6                  |          | dВ     |

| THD                     |                                            |                                                       | 91.0   |                       |          |        |

|                         | Total harmonic distortion                  | f <sub>IN</sub> = 2kHz                                |        | -110                  |          | dB     |

| SFDR                    | Spurious-free dynamic range                | f <sub>IN</sub> = 2kHz                                |        | 112                   |          | dB     |

| DEEEDEN 0               | Isolation crosstalk                        | f <sub>IN</sub> = 100kHz                              |        | -115                  |          | dB     |

| REFERENC                | E BUFFER                                   | I., ., ., <del>-</del>                                | I      |                       |          |        |

| V <sub>RO</sub>         | Reference buffer offset voltage            | $V_{RO} = V_{REFP} - V_{REFIO}, T_A = 25$ °C          | -250   |                       | 250      | μV     |

| C <sub>REFP</sub>       | Decoupling capacitor on REFP               |                                                       |        | 22                    |          | μF     |

| R <sub>ESR</sub>        | External series resistance                 |                                                       | 0      |                       | 1.3      | Ω      |

| REFby2 BU               | FFER                                       |                                                       |        |                       |          |        |

| $V_{REFby2}$            | REFby2 output voltage                      |                                                       |        | V <sub>REFP</sub> / 2 |          | V      |

| I <sub>REFby2</sub>     | DC sourcing current from REFby2            |                                                       |        |                       | 2        | mA     |

| C <sub>REFby2</sub>     | Decoupling capacitor on REFby2             |                                                       | 1      |                       |          | μF     |

| INTERNAL                | REFERENCE OUTPUT                           |                                                       |        |                       |          | I      |

| V <sub>REFIO</sub>      | REFIO output voltage <sup>(1)</sup>        | T <sub>A</sub> = 25°C, REFIO configured as output pin | 4.091  | 4.096                 | 4.101    | V      |

| dV <sub>REFIO</sub> /dT | Internal reference temperature drift       |                                                       |        | 4                     | 18       | ppm/°C |

| C <sub>REFIO</sub>      | Decoupling capacitor on REFIO              | REFIO configured as output                            | 1      |                       |          | μF     |

|                         | REFERENCE INPUT                            | 1 .                                                   | I      |                       |          |        |

| I <sub>REFIO</sub>      | REFIO input current                        | REFIO configured as input pin                         |        | 0.1                   | 1        | μA     |

| C <sub>REF</sub>        | Internal capacitance on REFIO pin          | REFIO configured as input pin                         |        | 10                    | <u> </u> | pF     |

|                         | P""                                        |                                                       |        |                       |          | ĺ      |

# 5.5 Electrical Characteristics (continued)

at AVDD = 5V, DVDD = 1.65V to 5.5V, REFIO configured as output pin, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}\text{C}$  to +125°C; typical values at  $T_A = 25^{\circ}\text{C}$

|                          | PARAMETER              | TEST CONDITIONS                                    | MIN | TYP  | MAX | UNIT   |

|--------------------------|------------------------|----------------------------------------------------|-----|------|-----|--------|

|                          | Aperture delay         |                                                    |     | 4    |     | ns     |

| t <sub>j-RMS</sub>       | Aperture jitter        |                                                    |     | 2    |     | ps RMS |

| f <sub>-3dB(small)</sub> | Small-signal bandwidth | Measured at ADC inputs                             |     | 23   |     | MHz    |

| POWER- SU                | JPPLY CURRENTS         |                                                    |     |      |     |        |

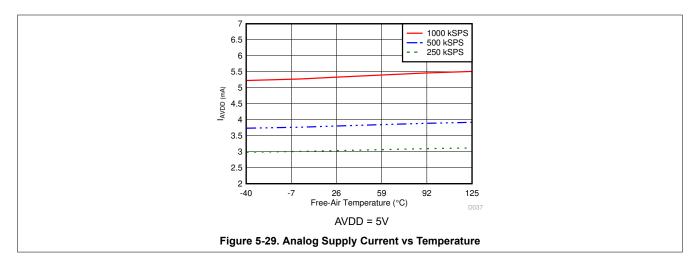

|                          |                        | ADS8168, AVDD = 5V                                 |     | 5.3  | 6.4 |        |

|                          |                        | ADS8167, AVDD = 5V                                 |     | 3.9  | 5   | ]      |

|                          |                        | ADS8166, AVDD = 5V                                 |     | 3    | 4.1 | mA     |

| I <sub>AVDD</sub>        | Analog supply current  | Static, no conversion                              |     | 2.3  |     |        |

| AVDD                     | , maiog cappiy carroin | Static, PD_REFBUF = 1                              |     | 1.6  |     |        |

|                          |                        | Static, PD_REF = 1                                 |     | 800  |     |        |

|                          |                        | Static, PD_REFBUF, PD_REF and PD_REFby2 = 1        |     | 180  |     | μA     |

| I <sub>DVDD</sub>        | Digital supply current | DVDD = 3V, C <sub>LOAD</sub> = 10pF, no conversion |     | 0.45 |     | μA     |

|                          |                        | I I                                                |     |      |     |        |

<sup>(1)</sup> Does not include the variation in voltage resulting from solder effects.

# 5.6 Timing Requirements

at AVDD = 5V, DVDD = 1.65V to 5.5V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_A = -40^{\circ}$ C to +125°C; typical values at  $T_A = 25^{\circ}$ C

|                       |                                               |                                                                                 | MIN                  | NOM | MAX  | UNIT             |

|-----------------------|-----------------------------------------------|---------------------------------------------------------------------------------|----------------------|-----|------|------------------|

| CONVERSI              | ON CYCLE                                      |                                                                                 |                      |     |      |                  |

|                       |                                               | ADS8168                                                                         |                      |     | 1000 |                  |

| f <sub>CYCLE</sub>    | Sampling frequency                            | ADS8167                                                                         |                      | ,   | 500  | kHz              |

|                       |                                               | ADS8166                                                                         |                      |     | 250  |                  |

|                       |                                               | ADS8168                                                                         | 1                    |     |      |                  |

| t <sub>CYCLE</sub>    | ADC cycle-time period                         | ADS8167                                                                         | 2                    |     |      | μs               |

|                       |                                               | ADS8166                                                                         | 4                    |     |      |                  |

| t <sub>wh_CSZ</sub>   | Pulse duration: $\overline{\text{CS}}$ high   | SDI contains command for register read or write                                 | 200                  |     |      | ns               |

|                       |                                               | no register read or write operation                                             | 30                   |     |      |                  |

| t <sub>wl_CSZ</sub>   | Pulse duration: $\overline{\text{CS}}$ low 30 |                                                                                 |                      | ns  |      |                  |

| t <sub>ACQ</sub>      | Acquisition time                              | Acquisition time                                                                |                      |     |      | ns               |

| t <sub>qt_ACQ</sub>   | Quite acquisition time                        | Quite acquisition time                                                          |                      |     |      | ns               |

| t <sub>d_CNVCAP</sub> | Quiet aperture time                           |                                                                                 |                      |     |      | ns               |

| ASYNCHRO              | NOUS RESET AND LOW POWER                      | MODES                                                                           |                      |     |      |                  |

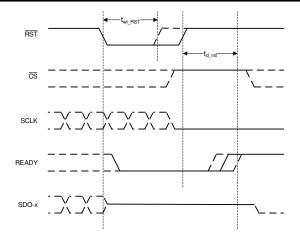

| t <sub>wl_RST</sub>   | Pulse duration: RST low                       |                                                                                 | 100                  |     |      | ns               |

| SPI-COMPA             | TIBLE SERIAL INTERFACE                        |                                                                                 |                      |     |      |                  |

|                       | Serial clock frequency                        | 2.35 ≤ DVDD ≤ 5.5V,<br>V <sub>IH</sub> > 0.7 DVDD, V <sub>IL</sub> < 0.3 DVDD   |                      |     | 50   | MHz              |

| f <sub>CLK</sub>      |                                               | 1.65V ≤ DVDD < 2.35V,<br>V <sub>IH</sub> ≥ 0.8 DVDD, V <sub>IL</sub> ≤ 0.2 DVDD |                      |     | 20   |                  |

|                       |                                               | 1.65V ≤ DVDD < 2.35V,<br>V <sub>IH</sub> ≥ 0.9 DVDD, V <sub>IL</sub> ≤ 0.1 DVDD |                      |     | 50   |                  |

| t <sub>CLK</sub>      | Serial clock time period                      |                                                                                 | 1 / f <sub>CLK</sub> |     |      | ns               |

| t <sub>ph_CK</sub>    | SCLK high time                                |                                                                                 | 0.45                 |     | 0.55 | $t_{CLK}$        |

| t <sub>pl_CK</sub>    | SCLK low time                                 |                                                                                 | 0.45                 |     | 0.55 | t <sub>CLK</sub> |

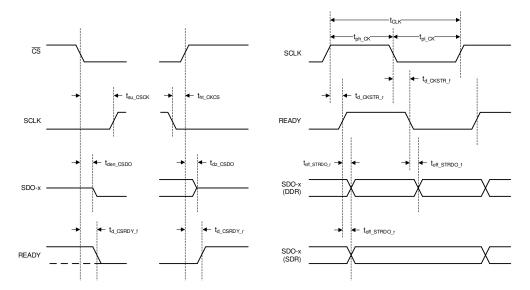

| t <sub>su_CSCK</sub>  | Setup time: CS falling to the first S         | CLK capture edge                                                                | 15                   |     |      | ns               |

| t <sub>su_CKDI</sub>  | Setup time: SDI data valid to the S           | CLK capture edge                                                                | 3                    |     |      | ns               |

| t <sub>ht_CKDI</sub>  | Hold time: SCLK capture edge to (             | previous) data valid on SDI                                                     | 4                    |     |      | ns               |

| t <sub>ht_CKCS</sub>  | Delay time: last SCLK falling to CS           | rising                                                                          | 7.5                  |     |      | ns               |

| SOURCE-S              | YNCHRONOUS SERIAL INTERFACI                   | <u> </u>                                                                        |                      |     | •    |                  |

| •                     |                                               | 2.35V ≤ DVDD ≤ 5.5V, SDR (DATA_RATE = 0b)                                       |                      |     | 70   |                  |

| f <sub>CLK</sub>      | Serial clock frequency                        | 2.35V ≤ DVDD ≤ 5.5V, DDR (DATA_RATE = 1b)                                       |                      |     | 35   | MHz              |

| t <sub>CLK</sub>      | Serial clock time period                      |                                                                                 | 1 / f <sub>CLK</sub> |     |      | ns               |

# **5.7 Switching Characteristics**

at AVDD = 5V, DVDD = 1.65V to 5.5V, and maximum throughput (unless otherwise noted); minimum and maximum values at  $T_{\Delta} = -40^{\circ}$ C to +125°C: typical values at  $T_{\Delta} = 25^{\circ}$ C

|                          | PARAMETER                                                   | TEST CONDITIONS             | MIN  | TYP MAX | UNIT             |

|--------------------------|-------------------------------------------------------------|-----------------------------|------|---------|------------------|

| CONVERSIO                | ON CYCLE                                                    |                             |      |         |                  |

|                          |                                                             | ADS8168                     |      | 660     |                  |

| t <sub>CONV</sub>        | Conversion time                                             | ADS8167                     |      | 1200    | ns               |

|                          |                                                             | ADS8166                     |      | 2500    | 1                |

| ASYNCHRO                 | NOUS RESET, AND LOW POWER MODES                             |                             |      |         |                  |

| t <sub>d_RST</sub>       | Delay time: RST rising to READY rising                      |                             |      | 4       | ms               |

| t <sub>PU_ADC</sub>      | Power-up time for converter module                          | Change PD_ADC = 1b to 0b    | 1    |         | ms               |

| t <sub>PU_REFIO</sub>    | Power-up time for internal reference                        | Change PD_REF = 1b to 0b    | 5    |         | ms               |

| t <sub>PU_REFBUF</sub>   | Power-up time for internal reference buffer                 | Change PD_REFBUF = 1b to 0b | 10   |         | ms               |

| t <sub>PU_Device</sub>   | Power-up time for device                                    |                             | 10   |         | ms               |

| SPI-COMPA                | TIBLE SERIAL INTERFACE                                      |                             | -    |         |                  |

| t <sub>den_CSDO</sub>    | Delay time: CS falling to data enable                       |                             |      | 15      | ns               |

| t <sub>dz_CSDO</sub>     | Delay time: CS rising to SDO going to Hi-Z                  |                             |      | 15      | ns               |

| t <sub>d_CKDO</sub>      | Delay time: SCLK launch edge to (next) data valid on SDO    |                             |      | 19      | ns               |

| t <sub>ht_CKDO</sub>     | Hold time: SCLK launch edge to (previous) data valid on SDO |                             | 2.5  |         | ns               |

| t <sub>d_CSRDY_t</sub>   | Delay time: CS falling to READY falling                     |                             |      | 15      | ns               |

| SOURCE-SY                | NCHRONOUS SERIAL INTERFACE (Exter                           | nal Clock)                  | -    |         |                  |

| t <sub>d_CKSTR_r</sub>   | Delay time: SCLK launch edge to READY rising                |                             |      | 23      | ns               |

| t <sub>d_CKSTR_f</sub>   | Delay time: SCLK launch edge to READY falling               |                             |      | 23      | ns               |

| t <sub>off_STRDO_f</sub> | Time offset: READY falling to (next) data valid on SDO      |                             | -2   | 2       | ns               |

| t <sub>off_STRDO_r</sub> | Time offset: READY rising to (next) data valid on SDO       |                             | -2   | 2       | ns               |

| t <sub>ph_STR</sub>      | Strobe output high time                                     | 2.35V ≤ DVDD ≤ 5.5V         | 0.45 | 0.55    | t <sub>STR</sub> |

| t <sub>pl_STR</sub>      | Strobe output low time                                      | 2.35V ≤ DVDD ≤ 5.5V         | 0.45 | 0.55    | t <sub>STR</sub> |

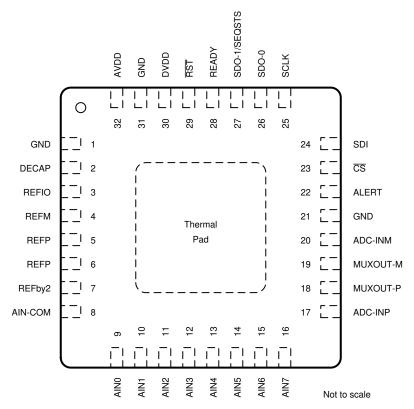

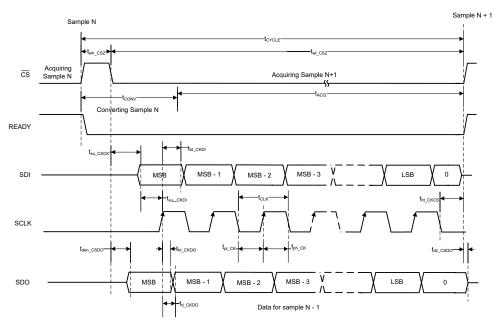

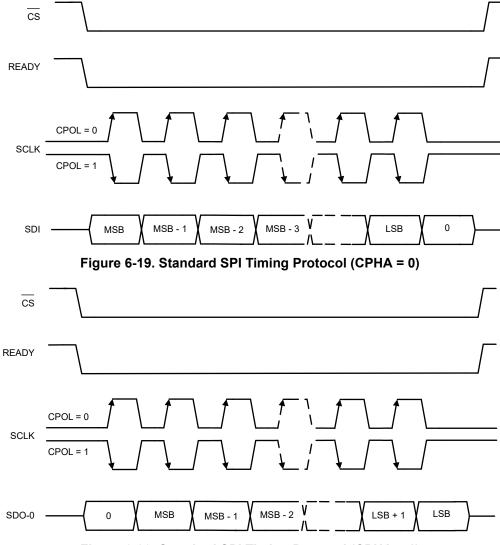

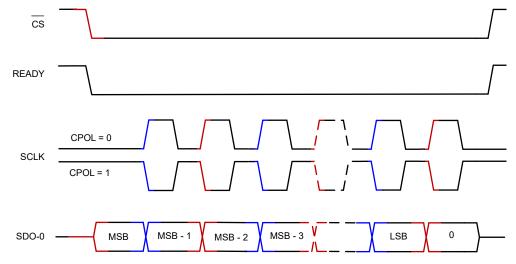

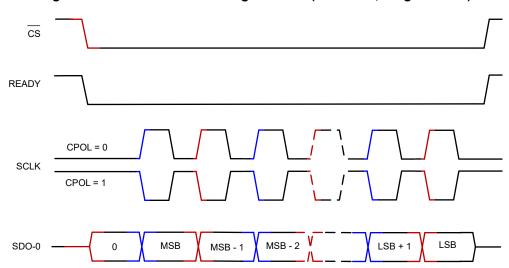

# 5.8 Timing Diagrams

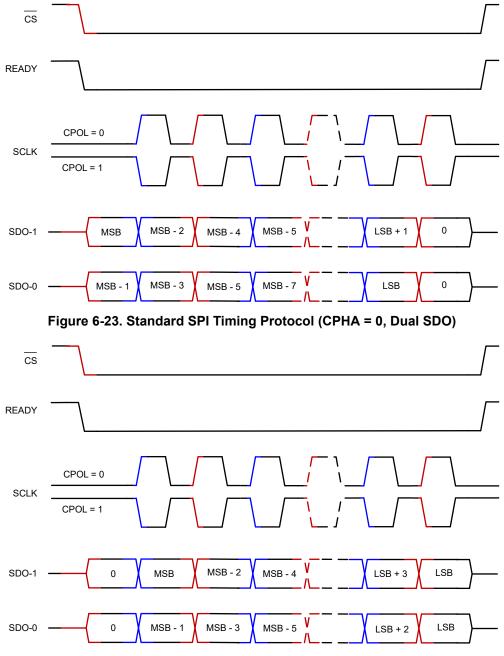

A. The SPI-00 interface mode is illustrated here. For SPI-01, -10, and-11 modes, see the Enhanced-SPI Interface section.

Figure 5-1. Conversion Cycle Timing:  $\overline{CS}$  = 1 Longer Than  $t_{CONV}$

A. The SPI-00 interface mode is illustrated here. For SPI-01, -10, and-11 modes, see the Enhanced-SPI Interface section.

Figure 5-2. Conversion Cycle Timing:  $\overline{CS}$  = 1 Shorter Than  $t_{CONV}$

Figure 5-3. Asynchronous Reset Timing

Figure 5-4. Clock Re-Timer Serial Interface Timing

# **5.9 Typical Characteristics**

# **6 Detailed Description**

#### 6.1 Overview

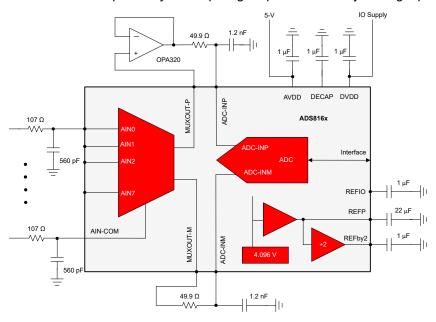

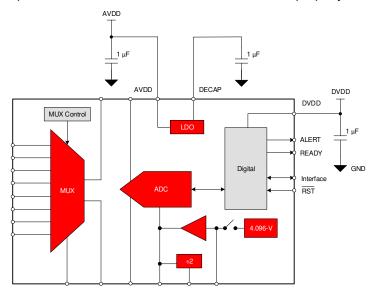

The ADS816x is a 16-bit successive approximation register (SAR) analog-to-digital converter (ADC) with an analog multiplexer. This device integrates a reference, reference buffer, REFby2 buffer, low-dropout regulator (LDO), and features high performance at full throughput and low power consumption.

The ADS816x supports unipolar, single-ended and pseudo-differential analog input signals. The analog multiplexer is optimized for low distortion and extended settling time. The internal reference generates a low-drift, 4.096V reference output. The integrated reference buffer supports burst mode for data acquisition of external reference voltages in the range 2.5V to 5V. For DC level shifting of the analog input signals, the device has a REFby2 output. The REFby2 output is derived from the output of the integrated reference buffer (the REFP pin).

When a conversion is initiated, the differential input between the ADC-INP and ADC-INM pins is sampled on the internal capacitor array. The device uses an internal clock to perform conversions. During the conversion process, both analog inputs of the ADC are disconnected from the internal circuit. At the end of conversion process, the device reconnects the sampling capacitors to the ADC-INP and ADC-INM pins and enters an acquisition phase.

The integrated LDO allows the device to operate on a single supply, AVDD. The device consumes only 26.5mW, 19.5mW, and 15mW of power when operating at 1MSPS (ADS8168), 500kSPS (ADS8167), and 250kSPS (ADS8166), respectively, with the internal reference, reference buffer, REFby2 buffer, and LDO enabled.

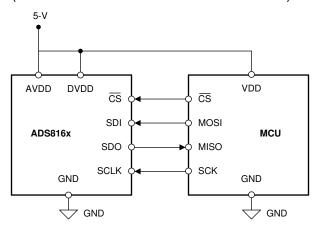

The enhanced-SPI digital interface is backward-compatible with traditional SPI protocols. Configurable features boost analog performance and simplify board layout, timing, firmware, and support full throughput at lower clock speeds. These features enable a variety of microcontrollers, digital signal processors (DSPs), and field-programmable gate arrays (FPGAs) to be used.

The ADS816x enables optical line cards, test and measurement, medical, and industrial applications to achieve fast, low-noise, low-distortion, and low-power data acquisition in a small form-factor.

# 6.2 Functional Block Diagram

### 6.3 Feature Description

The ADS816x is comprised of five modules: the converter (SAR ADC), multiplexer (MUX), the reference module, the enhanced-SPI interface, and the low-dropout regulator (LDO). See the *Functional Block Diagram* section.

The LDO module is powered by the AVDD supply, and generates the bias voltage for the internal circuit blocks of the device. The reference buffer drives the capacitive switching load present at the reference pins during the conversion process. The multiplexer selects among eight analog input channels as the input for the converter module. The converter module samples and converts the analog input into an equivalent digital output code. The enhanced-SPI interface module facilitates communication and data transfer between the device and the host controller.

# 6.3.1 Analog Multiplexer

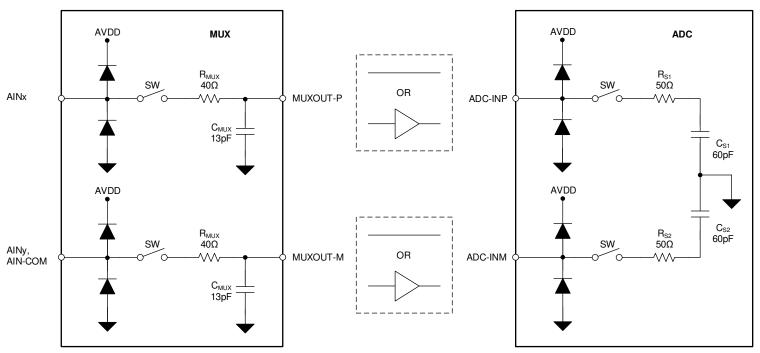

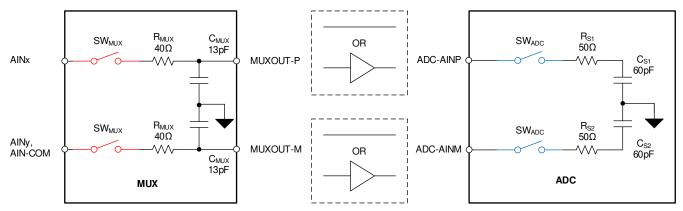

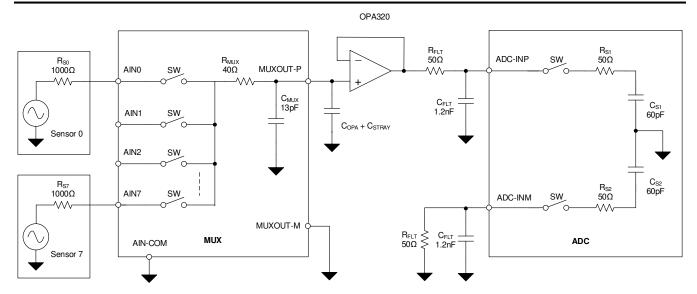

Figure 6-1 shows the small-signal equivalent circuit of the sample-and-hold circuit. Each sampling switch is represented by resistance ( $R_{S1}$  and  $R_{S2}$ , typically  $50\Omega$ ) in series with an ideal switch (SW). The sampling capacitors,  $C_{S1}$  and  $C_{S2}$ , are typically 60pF.

The multiplexer on-resistance ( $R_{MUX}$ ), is typically a 40 $\Omega$  resistor in series between the ON channel and the MUXOUT-P or MUXOUT-M pins. The multiplexer analog input typically has a 13pF on-channel capacitance ( $C_{MUX}$ ).

Figure 6-1. Input Sampling Stage Equivalent Circuit

During the input signal acquisition phase, the ADC-INP and ADC-INM inputs are individually sampled on  $C_{S1}$  and  $C_{S2}$ , respectively. During the conversion process, the device converts for the voltage difference between the two sampled values:  $V_{ADC-INP} - V_{ADC-INM}$ .

Each analog input pin has electrostatic discharge (ESD) protection diodes to AVDD and GND. Keep the analog inputs within the specified range to avoid turning the diodes on.

#### **6.3.1.1 Multiplexer Configurations**

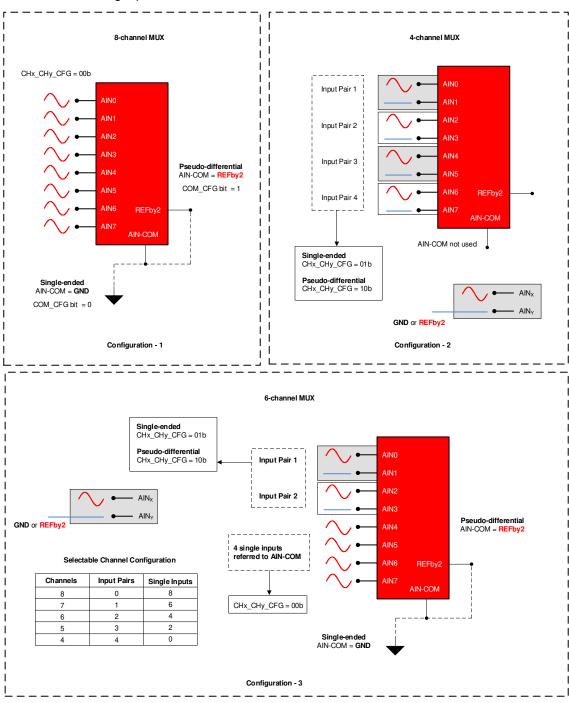

The ADS816x supports single-ended and pseudo-differential analog input signals. The flexible analog input channel configuration supports interfacing various types of sensors. Figure 6-2 shows how different configurations for the analog inputs.

Figure 6-2. Analog Input Configurations

The analog inputs configurations are:

- Configuration 1: Eight-channel MUX with the AIN\_CFG register set to 00h. The AIN-COM input range is

decided by the COM\_CFG register.

- Single-ended inputs with the AIN-COM input set to GND (set the COM\_CFG register to 00h).

- Pseudo-differential inputs with the AIN-COM input set to V<sub>REF</sub> / 2 (set the COM\_CFG register to 01h).

- Configuration 2: Four-channel MUX.

- As shown in Table 6-1, the AIN\_CFG register selects the analog input range of individual pairs.

- Configuration 3: Single-ended and pseudo-differential inputs.

- Among the eight analog inputs of the MUX, some inputs are configured as pairs and some inputs are configured as individual channels. Table 6-1 lists options for channel configuration.

- For channels configured as pairs, the AIN\_CFG register selects the single-ended or pseudo-differential configuration for individual pairs.

- For individual channels, the COM\_CFG register decides the single-ended or pseudo-differential configuration.

**Table 6-1. Channel Configuration Options**

| SERIAL NUMBER | TOTAL CHANNELS | INPUT PAIRS(1) (2) | INDIVIDUAL CHANNELS |

|---------------|----------------|--------------------|---------------------|

| 1             | 8              | 0                  | 8                   |

| 2             | 7              | 1                  | 6                   |

| 3             | 6              | 2                  | 4                   |

| 4             | 5              | 3                  | 2                   |

| 5             | 4              | 4                  | 0                   |

- (1) Channel pairs are formed as [AIN0 AIN1], [AIN2 AIN3], [AIN4 AIN5], and [AIN6 AIN7].

- (2) When channels are configured as pairs, AIN0, AIN2, AIN4, and AIN6 are positive inputs.

#### Note

The COM\_CFG register sets the input voltage range of the AIN-COM pin. Connect the AIN-COM pin to GND (set the COM\_CFG register to 0b) or REFby2 (set the COM\_CFG register to 1b) externally. When using the MUX in a four-channel configuration, the COM\_CFG register has no effect; connect the AIN-COM pin to GND to avoid noise coupling.

#### 6.3.1.2 Multiplexer With Minimum Crosstalk

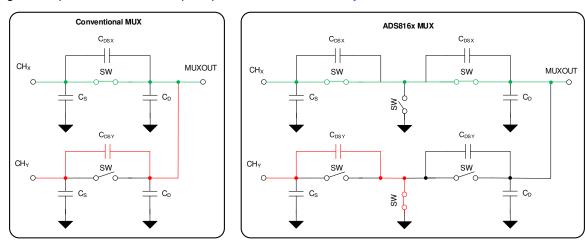

For precision measurement in a multichannel system, coupling (such as crosstalk) from one channel to another potentially distorts the measurement. In conventional multiplexers, as shown in Figure 6-3, the off channel parasitic capacitance between the drain and the source of the switch  $(C_{DSY})$  couples the off channel signal to the on channel.

Figure 6-3 shows that the ADS816x uses a T-switch structure. In this switch architecture, the off channel parasitic capacitance is connected to ground, which significantly reduces coupling. Make sure to avoid signal coupling on the printed circuit board (PCB), as described in the *Layout* section.

Figure 6-3. Isolation Crosstalk in a Conventional MUX versus the ADS816x

#### 6.3.1.3 Early Switching for Direct Sensor Interface

Figure 6-4 shows the small-signal equivalent model of the ADS816x analog inputs. The multiplexer input has a switch resistance ( $R_{MUX}$ ) and parasitic capacitance ( $C_{MUX}$ ). The parasitic capacitance causes a charge kickback on the MUX analog input at the same time as the ADC sampling capacitor causes a charge kickback on ADC inputs.

Figure 6-4. Synchronous and Timed Switching of the MUX and ADC Input Switches

In conventional multichannel SAR ADCs, the acquisition time of the ADC is also the settling time available at the analog inputs of the multiplexer because these times are internally connected. Thus, high-bandwidth op amps are required at the analog inputs of the multiplexer to settle the charge kickback. However, multiple high-bandwidth op amps significantly increase power dissipation, cost, and size of the solution.

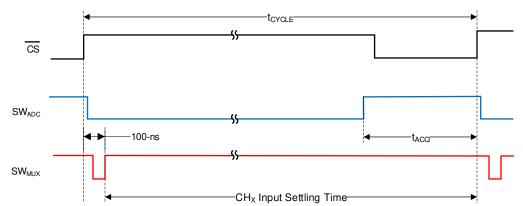

The analog inputs of the ADS816x provide a long settling time ( $t_{CYCLE} - 100$  ns), resulting in long acquisition time at the MUX inputs when using a driver amplifier between the MUX outputs and the ADC inputs. Figure 6-5 shows a timing diagram of this long acquisition phase. The low parasitic capacitance together with the enhanced settling time eliminate the need to use an op amp at the multiplexer input in most applications.

Figure 6-5. Early Switching of the MUX Enables a Long Acquisition Phase

#### 6.3.2 Reference

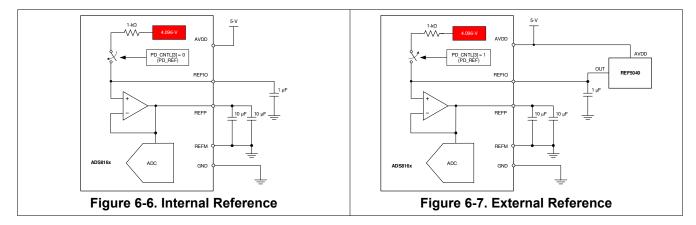

The ADS816x has a precision, low-drift reference internal to the device. The device features an internal reference source with a nominal output value of 4.096V. On power-up, the internal reference is enabled by default. Place a minimum  $1\mu\text{F}$  decoupling capacitor, as illustrated in Figure 6-6, between the REFIO and REFM pins.

Figure 6-7 shows the connections for using the device with an external reference. Use a reference without a low-impedance output buffer because the input leakage current of the internal reference buffer is less than 1µA.

For the minimum ADC input offset error ( $V_{OS}$ ), set the REF\_SEL[2:0] bits to the value closest to  $V_{REF}$  (see the OFST\_CAL register). Set the REF\_OFST[4:0] (see the REF\_MRG1 register) bits to add or subtract an intentional offset voltage as described in Table 7-14. Short the two REFP pins externally. Short the REFM pin to GND externally. Place a decoupling capacitor  $C_{REFP}$  between the REFP and the REFM pins as close to the device as possible; see the *Layout* section for layout recommendations.

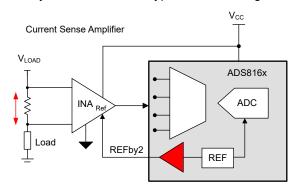

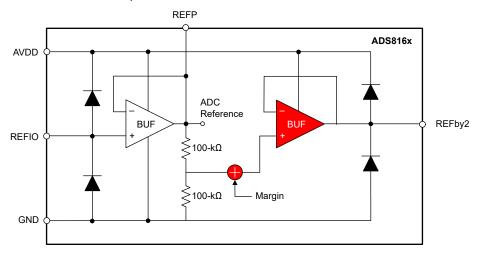

### 6.3.3 REFby2 Buffer

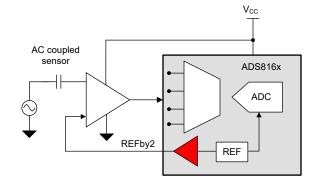

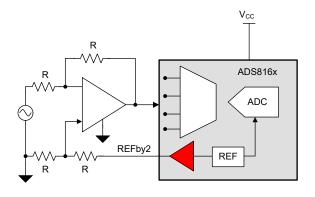

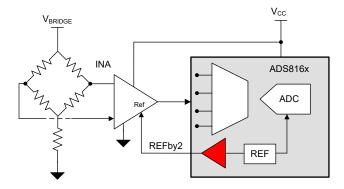

To use the maximum dynamic range of the ADC, bias the input signal around the mid-scale of the ADC input range. In the ADS816x, where the absolute input range is 0V to the reference voltage ( $V_{REF}$ ), mid-scale is  $V_{REF}$  / 2. The REFby2 buffer generates the  $V_{REF}$  / 2 signal for mid-scale shifting of the input signal. Figure 6-8 shows REFBy2 used in various types of sensor signal conditioning circuits.

Configuration 1: High-side / Low-side Current sensing

Configuration 2: AC Coupled Sensor Interface

Configuration 3:Unity Gain Sensor Interface

Configuration 4: High Impedance Sensor Interface with INA

Figure 6-8. Signal Conditioning With the REFby2 Buffer

A resistor divider at the output of the reference buffer, as shown in Figure 6-9, generates the  $V_{REF}$  / 2 signal. When not using the internal reference buffer (see the PD\_CNTL register), any voltage applied at the REFP pin is applied to the resistor divider. The output of the resistor divider is buffered and available at the REFby2 pin.

Figure 6-9. REFby2 Buffer Model

The REFby2 buffer is capable of sourcing up to 2mA of DC current. The REFby2 pin has ESD diode connections to AVDD and GND.

### 6.3.4 Converter Module

The converter module samples the analog input signal (provided between the ADC-INP and ADC-INM pins), compares this signal with the reference voltage (between the REFP pins and REFM pin), and generates an equivalent digital output code.

The converter module receives the  $\overline{RST}$  and  $\overline{CS}$  inputs from the interface module, and outputs the conversion result back to the interface module.

#### 6.3.4.1 Internal Oscillator

The device features an internal oscillator (OSC) that provides the conversion clock. Conversion duration varies, but is bounded by the minimum and maximum value of  $t_{conv}$ .

#### 6.3.4.2 ADC Transfer Function

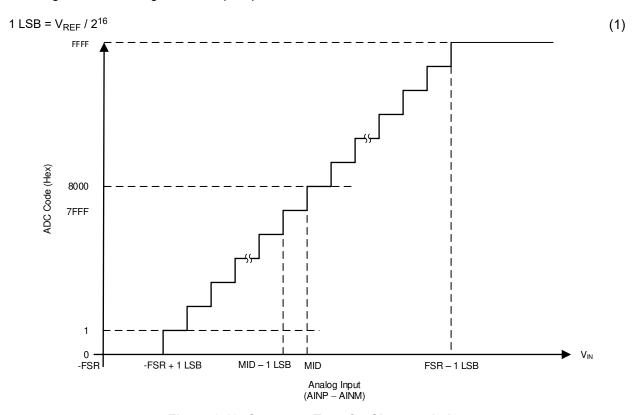

The device supports single-ended and pseudo-differential analog inputs. The device output is in straight binary format. Figure 6-10 and Table 6-2 show the ideal transfer characteristics for a 16-bit ADC with unipolar inputs.

Equation 1 gives the least significant bit (LSB) for the ADC:

Figure 6-10. Converter Transfer Characteristics

**Table 6-2. Transfer Characteristics**

| DESCRIPTION  | SINGLE-ENDED INPUT VOLTAGE<br>(V <sub>REF</sub> = 4.096V) | PSEUDO-DIFFERENTIAL INPUT VOLTAGE (V <sub>REF</sub> = 4.096V) | OUTPUT CODE<br>(HEX) |

|--------------|-----------------------------------------------------------|---------------------------------------------------------------|----------------------|

| FSR – 1 LSB  | 4.0959375V                                                | 2.0479375V                                                    | FFFF                 |

| MID + 1 LSB  | 2.0480625V                                                | 0.0000625V                                                    | 8001                 |

| MID          | 2.048V                                                    | 0V                                                            | 8000                 |

| MID – 1 LSB  | 2.0479375V                                                | -0.0000625V                                                   | 7FFF                 |

| –FSR + 1 LSB | 0.0000625V                                                | -2.0479375V                                                   | 0001                 |

| -FSR         | 0V                                                        | -2.048V                                                       | 0000                 |

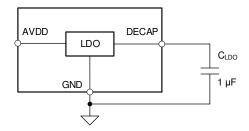

### 6.3.5 Low-Dropout Regulator (LDO)

To enable single-supply operation, the device features an internal low-dropout regulator (LDO). The LDO is powered by the AVDD supply, and the 2.85V (nominal) output is available on the DECAP pin. This LDO output powers the critical analog blocks within the device. Do not use this LDO output for any other external purposes.

Decouple the DECAP pin with the GND pin, as shown in Figure 6-11, by placing a  $1\mu$ F, X7R-grade, ceramic capacitor with a 6.3V rating from DECAP to GND. There is no upper limit on the value of the decoupling capacitor; however, a larger decoupling capacitor results in higher power-up time for the device. See the *Layout* section for layout recommendations.

Figure 6-11. Internal LDO Connections

#### 6.4 Device Functional Modes

The multiplexer includes a sequence control logic that supports various features as described in the *Channel Selection Using Internal Multiplexer* section.

### 6.4.1 Channel Selection Using Internal Multiplexer

The ADS816x includes an 8-channel, linear, and low-leakage current analog multiplexer. The multiplexer performs a break-before-make operation when switching channels. There are four modes of switching the multiplexer input channels: manual mode, on-the-fly mode, auto sequence mode, and custom channel sequencing mode.

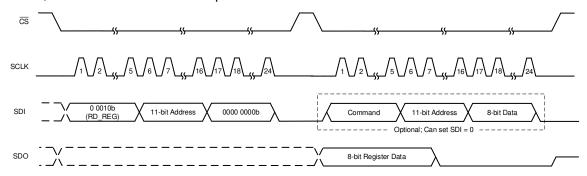

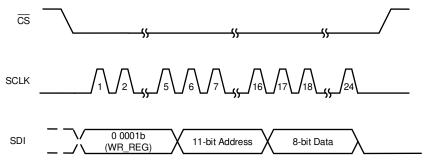

Select these modes by configuring the SEQ\_MODE[1:0] bits in the DEVICE\_CFG register. On power-up the default mode is manual mode, SEQ\_MODE[1:0] = 00b, and the default input channel is AIN0. The multiplexer configuration registers are accessible over the SPI; see Figure 6-18. The SPI interface eliminates the need for separate MUX control lines.

#### 6.4.1.1 Manual Mode

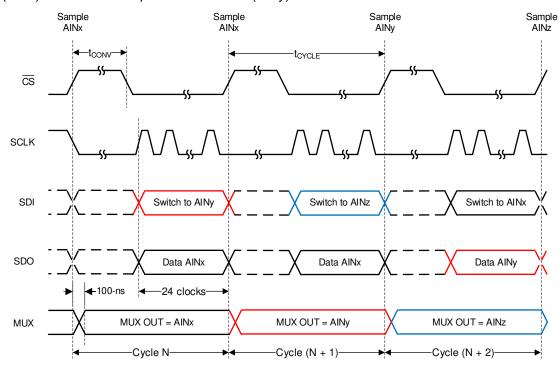

In manual mode, the channel ID of the desired analog input is configured in the CHANNEL\_ID register. On power-up or after device reset, AIN0 is selected and CHANNEL\_ID[2:0] = 000b. Enable manual mode from any other sequencing mode by programming the SEQ\_MODE[1:0] bits to 00b in the DEVICE\_CFG register. Figure 6-12 shows the timing information for changing channels in manual mode.

Update the channel information in a microcontroller (MCU)-friendly 3-byte access. Because the 24 bits of channel configuration are sent over SDI, conversion data are clocked out over SDO. The data on SDO are MSB aligned and the first 16 clocks correspond to 16 bits of conversion data. The last eight bits of the SDO are ignored by the MCU.

As shown in Figure 6-12, the command to switch to AINy is sent in the Nth cycle and the data corresponding to channel AINy is available in the (N + 2)th cycle. This switch occurs because the SDI commands are processed and the ADC starts conversions on the rising edge of  $\overline{CS}$ . Thus, the conversion is processed on the previous channel (AINx) and not on the updated channel ID (AINy).

Figure 6-12. Manual Mode Timing Diagram

#### 6.4.1.2 On-The-Fly Mode

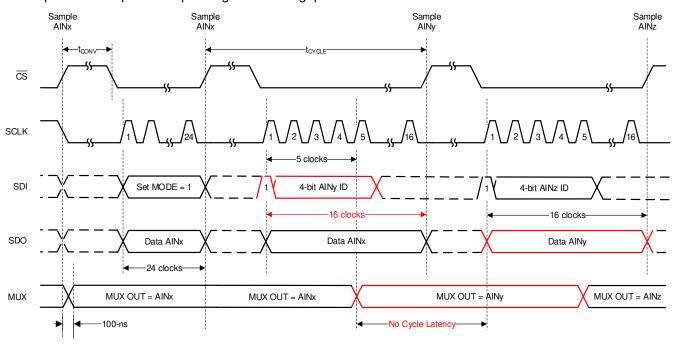

There is a latency of one cycle when switching channels using the register access, just as in manual mode. The newly selected channel data are available two cycles after selecting the desired channel. The ADS816x supports on-the-fly switching of the analog input channels of the multiplexer. Enable this mode by programming the SEQ\_MODE[1:0] bits to 01b in the DEVICE\_CFG register. When enabled, the analog input channel for the next conversion is determined by the first five bits sent over SDI. The desired analog input channel is selected by setting the MSB to 1 and the following four bits as the channel ID. If the MSB is 0 then the SDI bitstream is decoded as a normal frame on the rising edge of  $\overline{CS}$ . Table 6-3 lists the channel selection commands for this mode.

| Table 6-3. On-the-rig Mode Chainlet Selection Commands |                                         |                                         |  |  |

|--------------------------------------------------------|-----------------------------------------|-----------------------------------------|--|--|

| SDI BITS [15:11] SDI BITS [10:0]                       |                                         | DESCRIPTION                             |  |  |

| 1 0000                                                 | Don't care                              | Select analog input 0                   |  |  |

| 1 0001                                                 | 1 0001 Don't care Select analog input 1 |                                         |  |  |

| 1 0010                                                 | 1 0010 Don't care Select analog input 2 |                                         |  |  |

| 1 0011 Don't care Select analog input 3                |                                         | Select analog input 3                   |  |  |

| 1 0100                                                 | 1 0100 Don't care Select analog input 4 |                                         |  |  |

| 1 0101                                                 | Don't care                              | Select analog input 5                   |  |  |

| 1 0110 Don't care Select analog input 6                |                                         | Select analog input 6                   |  |  |

| 1 0111                                                 | Don't care                              | Select analog input 7                   |  |  |

| 1 1000 to 1 1111                                       | Don't care                              | Error bit is set; select analog input 0 |  |  |

Table 6-3. On-the-Fly Mode Channel Selection Commands

To set the device in on-the-fly mode, configure EN\_ON\_THE\_FLY to 1b in the ON\_THE\_FLY\_CFG register as shown in Figure 6-13 using a 3-byte register access. When in this mode, use the 16-bit data transfer to reduce the required clock speed for operating at full throughput.

Figure 6-13. On-the-Fly Mode With No MUX Channel Selection Latency

#### 6.4.1.3 Auto Sequence Mode

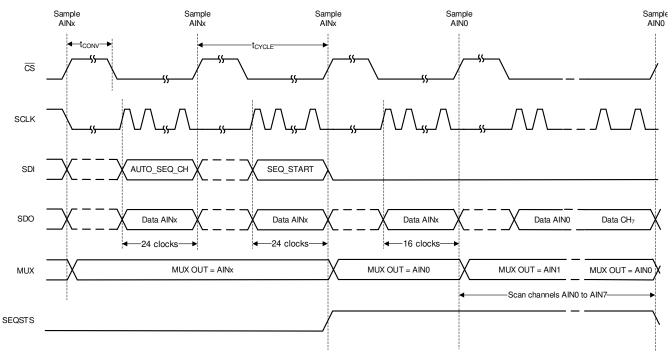

In auto sequence mode, the internal channel sequencer selectively scans channels from AIN0 through AIN7 in ascending order. To select auto sequence mode, configure SEQ\_MODE to 10b in the DEVICE\_CFG register using a 3-byte register access. Enable one or more channels among AIN[7:0] by configuring the AUTO\_SEQ\_CFG1 register. By default all analog input channels are enabled. After enabling the desired channels, start the sequence by setting SEQ\_START to 1b. The ADC auto-increments through the enabled channels after every  $\overline{\text{CS}}$  rising edge. Configure SEQSTS\_CFG bit to 1b in SDO\_CNTL4 register to indicate sequence status on SDO-1/SEQSTS pin. When SEQ\_START is set to 1b, the SDO-1/SEQSTS pin is at logic 1 as shown in Figure 6-14 until the last channel conversion frame is complete. After the last enabled channel conversion is complete, channel AIN0 is selected and SDO-1/SEQSTS is in a high-impedance state.

Figure 6-14. Starting a Sequence in Auto Sequence Mode

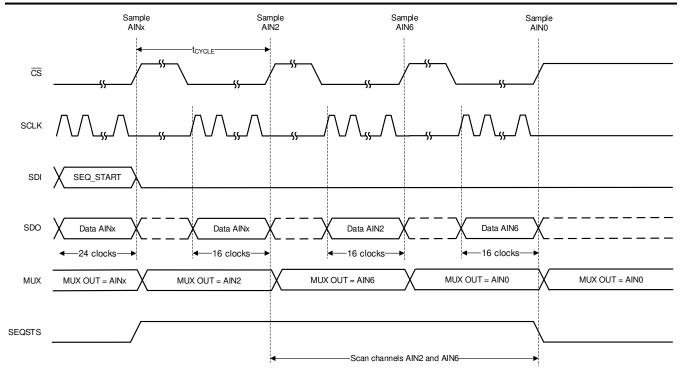

As an example, Figure 6-15 depicts a timing diagram for when the device is scanning AIN2 and AIN6 in auto sequence mode. When AIN6 is converted, SDO-1/SEQSTS is Hi-Z and AIN0 is selected as the active channel. At the end of sequence, if more conversion frames are launched the device returns valid data corresponding to AIN0.

To use the device in auto sequence mode follow these steps:

- Set the SEQ\_MODE[1:0] bits in the DEVICE\_CFG register to 10b.

- Configure the AUTO SEQ CFG1 register. In Figure 6-15, AUTO SEQ CFG1 = 0x44.

- Set the SEQ START bits in the SEQ START register to 1b to start executing the sequence.

- Optionally, configure SEQSTS\_CFG bit to 1b in SDO\_CNTL4 register to indicate sequence status on SDO-1/ SEQSTS pin.

Figure 6-15. Example: Scanning Channels 2 and 6 in Auto Sequence Mode

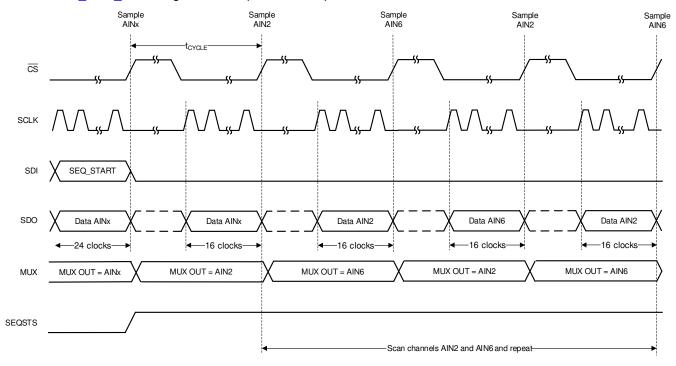

To repeat a channel sequence indefinitely, set the AUTO\_REPEAT bit in the AUTO\_SEQ\_CFG2 register to 1b. Figure 6-16 shows that when the AUTO\_REPEAT bit is enabled, the MUX scans through the channels enabled in the AUTO\_SEQ\_CFG1 register and repeats the sequence after the last channel data are converted.

Figure 6-16. Example: Scanning Channels 2 and 6 in Auto Sequence Mode With AUTO\_REPEAT = 1

Figure 6-16 provides a timing diagram for when the device is scanning AIN2 and AIN6 in auto sequence mode with AUTO\_REPEAT = 1b. When AIN6 is converted, AIN2 is selected as the active channel and the device continues scanning through the enabled channels again.

To use the device in auto sequence with the repeat mode enabled follow these steps:

- Set the SEQ\_MODE[1:0] bits in the DEVICE\_CFG register to 10b.

- Configure the AUTO SEQ CFG1 register. In Figure 6-15, AUTO SEQ CFG1 = 0x44.

- Set AUTO\_REPEAT to 1b.

- Set the SEQ\_START bit in the SEQ\_START register to 1b to start executing the sequence.

- Optionally, configure SEQSTS\_CFG bit to 1b in SDO\_CNTL4 register to indicate sequence status on SDO-1/ SEQSTS pin.

To terminate an ongoing channel sequence set the SEQ\_ABORT bit in the SEQ\_ABORT register 1. When SEQ ABORT is set, the auto sequence stops and AIN0 is selected as the active input channel.

# 6.4.1.4 Custom Channel Sequencing Mode

In this mode the internal channel sequencer selectively scans channels from AIN0 through AIN7 in any order as defined by a user-programmable look-up table. Table 6-4 describes the configurability of this look-up table. Configure the device in custom channel sequencing mode by programming the SEQ\_MODE[1:0] bits to 11b in the DEVICE\_CFG register using a 3-byte register access. Table 6-4 shows that the channel scanning sequence is programmed by configuring the channel IDs in the register as space. A channel sample count is also programmed and associated with every channel ID. By default the channel sample count is 1, which means the sequence executes in the order of programmed channel IDs. If the channel sample count is greater than 1 then the corresponding channel is sampled and converted for a programmed number of times before switching to the next channel.

Table 6-4. Custom Channel Sequencing Configuration Space

| rubio o in Guotom Chamber Coquencing Comigaration Opace |                                           |                     |                                                |  |

|---------------------------------------------------------|-------------------------------------------|---------------------|------------------------------------------------|--|

| REGISTER<br>ADDRESS                                     | CHANNEL ID[2:0]                           | REGISTER<br>ADDRESS | CHANNEL SAMPLE COUNT[7:0]                      |  |

| 0x8C                                                    | Index 0 : 3-bit channel ID (default = 0)  | 0x8D                | Index 0 : 8-bit sample count (default = 0xFF)  |  |

| 0x8E                                                    | Index 1 : 3-bit channel ID (default = 0)  | 0x8F                | Index 1 : 8-bit sample count (default = 0xFF)  |  |

| 0x90                                                    | Index 2 : 3-bit channel ID (default = 0)  | 0x91                | Index 2 : 8-bit sample count (default = 0xFF)  |  |

| 0x92                                                    | Index 3 : 3-bit channel ID (default = 0)  | 0x93                | Index 3 : 8-bit sample count (default = 0xFF)  |  |

| 0x94                                                    | Index 4 : 3-bit channel ID (default = 0)  | 0x95                | Index 4 : 8-bit sample count (default = 0xFF)  |  |

| 0x96                                                    | Index 5 : 3-bit channel ID (default = 0)  | 0x97                | Index 5 : 8-bit sample count (default = 0xFF)  |  |

| 0x98                                                    | Index 6 : 3-bit channel ID (default = 0)  | 0x99                | Index 6 : 8-bit sample count (default = 0xFF)  |  |

| 0x9A                                                    | Index 7 : 3-bit channel ID (default = 0)  | 0x9B                | Index 7 : 8-bit sample count (default = 0xFF)  |  |

| 0x9C                                                    | Index 8 : 3-bit channel ID (default = 0)  | 0x9D                | Index 8 : 8-bit sample count (default = 0xFF)  |  |

| 0x9E                                                    | Index 9 : 3-bit channel ID (default = 0)  | 0x9F                | Index 9 : 8-bit sample count (default = 0xFF)  |  |

| 0xA0                                                    | Index 10 : 3-bit channel ID (default = 0) | 0xA1                | Index 10 : 8-bit sample count (default = 0xFF) |  |

| 0xA2                                                    | Index 11 : 3-bit channel ID (default = 0) | 0xA3                | Index 11 : 8-bit sample count (default = 0xFF) |  |

| 0xA4                                                    | Index 12 : 3-bit channel ID (default = 0) | 0xA5                | Index 12 : 8-bit sample count (default = 0xFF) |  |

| 0xA6                                                    | Index 13 : 3-bit channel ID (default = 0) | 0xA7                | Index 13: 8-bit sample count (default = 0xFF)  |  |

| 0xA8                                                    | Index 14 : 3-bit channel ID (default = 0) | 0xA9                | Index 14 : 8-bit sample count (default = 0xFF) |  |

| 0xAA                                                    | Index 15: 3-bit channel ID (default = 0)  | 0xAB                | Index 15 : 8-bit sample count (default = 0xFF) |  |

For application-specific scanning requirements, use start and stop pointers to define the channel scanning sequence. Program the start index in the CCS\_START\_INDEX register and the stop index in the CCS\_END\_INDEX register. Table 6-4 shows that the 4-bit index corresponds to the configuration index. The sequence starts executing from the index programmed in CCS\_START\_INDEX (default 0) and stop or loop-back from CCS\_STOP\_INDEX (default 15). The channel scanning sequence is looped-back to the start index from the stop index by setting the CCS\_SEQ\_LOOP register to 1b.

After configuring the channel scanning order, start index, and stop index, initiate the scanning by setting the SEQ\_START bit to 1b. The ADC scans through the enabled channels after every  $\overline{\text{CS}}$  rising edge as defined by the channel scanning order. When SEQ\_START is set to 1b, the SDO-1/SEQSTS pin is pulled high until the last channel conversion frame is complete, as described in Figure 6-14. As illustrated in Figure 6-15, channel AIN0 is selected and SEQSTS/SDO-1 goes to Hi-Z after the last enabled channel conversion is complete.

As an example, Figure 6-15 provides a timing diagram for when the channel configuration is set as in Table 6-5. When AIN6 is converted, SEQSTS/SDO-1 goes to Hi-Z and AIN0 is selected as the active channel. If more conversion frames are launched at the end of the sequence, the device returns valid data corresponding to AIN0.

To use the device in easy capture mode follow these steps:

- Set the SEQ\_MODE[1:0] bits in the DEVICE\_CFG register to 3.

- Configure the channel sequence by setting registers 0x000C to 0x002B.

- Configure the CCS\_START\_INDEX and the CCS\_END\_INDEX registers. In Figure 6-15, CCS\_START\_INDEX = 0 and CCS\_STOP\_INDEX = 1.

- Configure the CCS\_SEQ\_LOOP register to 1 to indefinitely loop the sequence. In Figure 6-15, the CCS\_SEQ\_LOOP register = 0b.

- Set the SEQ START register to 1b to start executing the sequence.

**Table 6-5. Custom Channel Sequencing Configuration Example**

| REGISTER<br>ADDRESS | CHANNEL ID[2:0]  | REGISTER<br>ADDRESS | CHANNEL SAMPLE COUNT[7:0] |

|---------------------|------------------|---------------------|---------------------------|

| 0x8C                | 010b (channel 2) | 0x8D                | 1                         |

| 0x8E                | 110b (channel 6) | 0x8F                | 1                         |

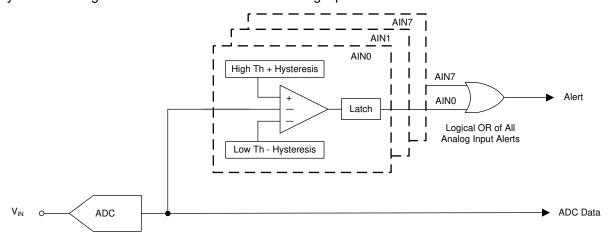

### 6.4.2 Digital Window Comparator

The ADS816x has a programmable digital window comparator for every analog input channel. The integrated digital window comparator allows the host to not read ADC data over the serial interface for comparison purposes. In monitoring applications, the ADC compares channel data with the set thresholds and alerts the system host using the ALERT pin. Furthermore, the digital window comparator does not require software high and low comparisons and thus saves processing cycles.